Bernd Schuscha, BSc

# Evaluation of electro-thermal influenced reliability effects in microelectronics

#### **MASTER'S THESIS**

to achieve the university degree of Diplom-Ingenieur

Master's degree programme: Technical Physics

submitted to Graz University of Technology

#### Supervisor

Univ.-Prof. Ph.D. Peter Hadley Institute for Solid State Physics

in cooperation with ams AG (R&D EDA)

Graz, August 2021

#### AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present master's thesis.

Graz, 13.07.2021

B. Schuscha

Date, Signature

### Acknowledgement

I would first like to thank my supervisor, Univ.-Prof. Peter Hadley, head of the Institute of Solid State Physics from the Technical University of Graz. His door was always open and I would like to thank him for providing guidance and feedback throughout this thesis.

I would like to acknowledge my colleagues from the Technology R&D EDA department at ams AG in Premstätten, managed by Ehrenfried Seebacher, it was a delight working with them. I would particularly like to single out my supervisors Alexander Steinmair and Chong Jin. They were both kind supervisors to whom I could always come with questions.

I would also like to thank Klaus Cerny and Evgeny Vlasov from Cadence Design Systems. Without their continuous technical support and them providing the licenses the project would not have been possible.

### Abstract

Temperature management is import for every high power device. Applying a temperature profile not only has an immediate effect on the electrical device characteristics but also causes long term changes through degradation. The two most important degradation effects which depend on electrical stress are Hot-Carrier-Injection (HCI) and Negative-Bias-Temperature-Instability (NBTI). This thesis aims to test one commercial solution, the Legato tool, to simulate the coupling of such effects.

To test this, simulations of test circuits have been performed. Typical reliability models used for the degradation effects were implemented, the model data was provided by ams AG. Because the tool only couples thermal and electrical properties, a provisional interface to the reliability simulation was made to evaluate whenever it is necessary in the future. A MOS driver was chosen as the main test circuit. The results for the MOS driver show a linear temperature dependence on the duty cycle, which suggests the heat sink at the bottom is functioning well. In addition, a spatially-dependence of electrical and reliability characteristics could be found, which is rooted in the temperature distribution of the chip.

The results show the importance of the device position of a chip, but also that reliability effects could be used to compensate for a difference in device location. Furthermore, the limit of the tool could be found which traded usability with customizability.

### Kurzfassung

Temperatur Management ist in Mikroelektronik-Anwendungen mit hoher Leistungsdichte von großer Bedeutung. Dies ist, aufgrund der Temperaturabhängigkeit von elektrische Eigenschaften von Schaltungen oder Bauteilen. Dabeo ist dies nicht nur einen kurzzeitigen und reversible Character, sondern es kann durch Degradierung (Alterung) auch zu dauerhaften Veränderung von Bauteilen kommen. Die zwei bedeutendsten Effekte in MOSFETs sind hierfür Hot-Carrier-Injection (HCI) und Negative-Bias-Temperature-Instability (NBTI). Das Ziel dieser Arbeit ist die Testung einer kommerziellen Lösung, das "Legato Tool", welches eine Kopplung solcher Effekte erlaubt.

Um dies zu testen, wurden Simulationen von Testschaltungen durchgeführt. Für die Degradationseffekte wurden typische Modelle implementiert, bereitstellt von der ams AG. Da das Tool nur thermische und elektrische Eigenschaften koppelt, wurde eine vorläufige Schnittstelle zur Degradierungssimulation erstellt. Dies erfolgte für eine Bewertung, ob eine Berücksichtigung von Temperatureffekten bei der Degradierungssimulation erforderlich ist. Für die Testung wurde ein MOS-Treiber als Haupttestschaltung gewählt. Die Ergebnisse für diesen MOS-Treiber zeigen eine lineare Temperaturabhängigkeit vom Duty-Cycle, was auf eine gute Funktion des Wärmesenke an der Unterseite des Bauteils schließen lässt. Außerdem konnte ein Ortabhängigkeit des Elektrischen- und Degradierungverhalten festgestellt werden, das in der Temperaturverteilung des Chips begründet ist.

Die Ergebnisse zeigen die Bedeutung der Geräteposition eines Mikroelektronikchips, aber auch, dass Degradierungeffekte verwendet werden könnten, um einen Unterschied vom Geräteposition auszugleichen. Darüber hinaus konnte die Grenze des Tools gefunden werden, das Benutzerfreundlichkeit mit Anpassbarkeit tauscht.

# Contents

| A  | cknov  | vledger | nent                                                  | iii |  |

|----|--------|---------|-------------------------------------------------------|-----|--|

| Al | ostrac | ct      |                                                       | iv  |  |

| Kı | urzfas | ssung   |                                                       | v   |  |

| 1  | Intr   | oductio | on                                                    | 1   |  |

|    | 1.1    | Basics  | s of MOSFETs                                          | 1   |  |

|    |        | 1.1.1   | Different Regimes, MOSFET Model and Characteristic    |     |  |

|    |        |         | Curves                                                | 2   |  |

|    | 1.2    | Power   | r-MOSFET                                              | 3   |  |

|    |        | 1.2.1   | Multi-Finger MOSFET                                   | 4   |  |

|    |        | 1.2.2   | LDMOS                                                 | 4   |  |

|    | 1.3    | Test C  | Circuits                                              | 5   |  |

|    |        | 1.3.1   | 29V HV pMOS                                           | 5   |  |

|    |        | 1.3.2   | Current Mirror                                        | 6   |  |

|    |        | 1.3.3   | MOS Driver                                            | 8   |  |

| 2  | Elec   | tro-Th  | ermal Simulation                                      | 10  |  |

|    | 2.1    | Temp    | erature Behavior of MOSFETs                           | 10  |  |

|    |        | 2.1.1   | Thermal Runaway                                       | 11  |  |

|    | 2.2    | Multi   | -Scale Simulation                                     | 18  |  |

|    | 2.3    | Simul   | Ilation Method                                        |     |  |

|    |        | 2.3.1   | Power Input Profile Legato vs Typical Standard FEM    |     |  |

|    |        |         | Simulation                                            | 20  |  |

|    |        | 2.3.2   | Thermic Connection to the Environment                 | 21  |  |

|    |        | 2.3.3   | Heat Equation                                         | 24  |  |

|    | 2.4    | Simul   | ation Results                                         | 26  |  |

|    |        | 2.4.1   | Electro Thermal Simulation of a Point Source with the |     |  |

|    |        |         | 180 nm Technology Layer Stack                         | 27  |  |

|    |       | 2.4.2<br>2.4.3<br>2.4.4<br>2.4.5 | Temperature Behaviour of a Single p-MOSFET Electro-Thermal Simulation of a Current Mirror Influence of Simulation Variables for the MOS Driver Simulation | 29<br>30<br>32<br>34 |

|----|-------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 3  | Age   | ing Sin                          | nulation                                                                                                                                                  | 40                   |

|    | 3.1   | Reliab                           | pility                                                                                                                                                    | 40                   |

|    |       | 3.1.1                            | Reliability Basics                                                                                                                                        | 40                   |

|    | 3.2   | Degra                            | dation Mechanism of MOSFET                                                                                                                                | 41                   |

|    |       | 3.2.1                            | Hot Carrier Injection (HCI)                                                                                                                               | 42                   |

|    |       | 3.2.2                            | Negative Bias Temperature Instability (NBTI)                                                                                                              | 43                   |

|    | 3.3   | Reliab                           | bilty Modeling                                                                                                                                            | 44                   |

|    |       | 3.3.1                            | Takeda Reliability Model                                                                                                                                  | 44                   |

|    |       | 3.3.2                            | HCI Model                                                                                                                                                 | 45                   |

|    |       | 3.3.3                            | NBTI model                                                                                                                                                | 46                   |

|    |       | 3.3.4                            | Implementation                                                                                                                                            | 46                   |

|    |       | 3.3.5                            | AC Stress and the BERT Algorythm                                                                                                                          | 47                   |

|    | 3.4   | Simul                            | ation Results                                                                                                                                             | 49                   |

|    |       | 3.4.1                            | 29V HV pMOS Reliability Simulation Results                                                                                                                | 50                   |

|    |       | 3.4.2                            | Current Mirror Reliability Simulation Results                                                                                                             | 51                   |

|    |       | 3.4.3                            | MOS Driver Reliability Simulation Results                                                                                                                 | 52                   |

| 4  | Con   | clusion                          |                                                                                                                                                           | 55                   |

|    | 4.1   | Legate                           | o Tool for Electro-Thermal Simulation                                                                                                                     | 55                   |

|    | 4.2   | Electro                          | o-Thermal Simulation Results                                                                                                                              | 56                   |

|    | -     | 4.2.1                            | Current Mirror                                                                                                                                            | 56                   |

|    |       | 4.2.2                            | MOS Driver                                                                                                                                                | 56                   |

|    | 4.3   | Electr                           | o-Thermal Aware Reliability Simulation Results                                                                                                            | 56                   |

| Bi | bliog | raphy                            |                                                                                                                                                           | 58                   |

|    |       |                                  |                                                                                                                                                           |                      |

# List of Tables

| 1.1 | Layouts                                                         | 8  |

|-----|-----------------------------------------------------------------|----|

| 2.1 | Used layer stack                                                | 26 |

| 2.2 | Thermal constants used for the simulation                       | 27 |

| 2.3 | Layout variants of the current mirror                           | 32 |

| 2.4 | Results for the symmetric layout                                | 32 |

| 2.5 | Electro thermal simulation result                               | 37 |

| 2.6 | Comparisson between Grpo and Grp3                               | 39 |

| 3.1 | Current mirror aging with temperature profile results for $T =$ |    |

|     | 25 °C                                                           | 51 |

| 3.2 | Current mirror aging with temperature profile results for T = - |    |

|     | 40 °C                                                           |    |

| 3.3 | Electro-thermal reliability simulation result                   | 53 |

# List of Figures

| 1.1  | Schematic of a p-MOSFET                                                                                                   | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Schematic of an p-MOSFET                                                                                                  | 3  |

| 1.3  | MOSFET with three fingers                                                                                                 | 4  |

| 1.4  | Cross-section of an LDMOS                                                                                                 | 5  |

| 1.5  | Circuit diagram for the p-MOSET test circuit                                                                              | 6  |

| 1.6  | Circuit diagram for the current mirror test circuit                                                                       | 7  |

| 1.7  | Layout of the current mirror                                                                                              | 7  |

| 1.8  | Most important components of the MOS driver                                                                               | 8  |

| 1.9  | Left: Most important components of the MOS driver group;                                                                  |    |

|      | Right: group Layout                                                                                                       | 9  |

| 2.1  | Charge carrier concentration for n-doped silicon with a doping                                                            |    |

|      | concentration of $10^{17} \text{ 1/cm}^3 \dots \dots \dots \dots \dots \dots \dots \dots \dots$                           | 13 |

| 2.2  | Left: Conducvity; Right: Resistivity                                                                                      | 14 |

| 2.3  | Temperature dependence of the diode current at $V = 0.5 V \dots$                                                          | 15 |

| 2.4  | Output characteristics and transfer characteristics of the 29V                                                            |    |

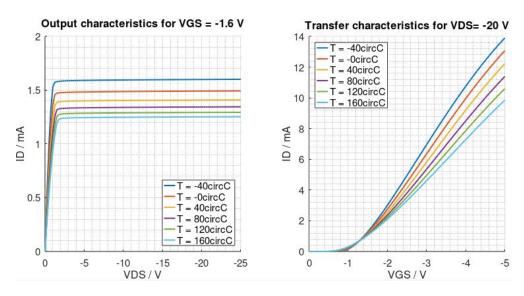

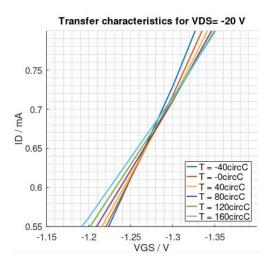

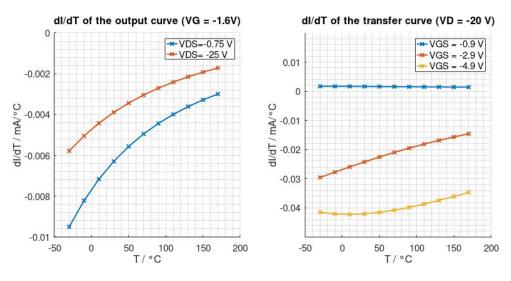

|      | HV pMOS transistor depending on the temperature                                                                           | 16 |

| 2.5  | Sketch of transfer characteristic visible in figure 2.4; Inversion                                                        |    |

|      | range of the IDS in dependence of the VGS                                                                                 | 17 |

| 2.6  | Partial derivation of IDS over T                                                                                          | 18 |

| 2.7  | Block diagramm for the general simulation flow                                                                            | 20 |

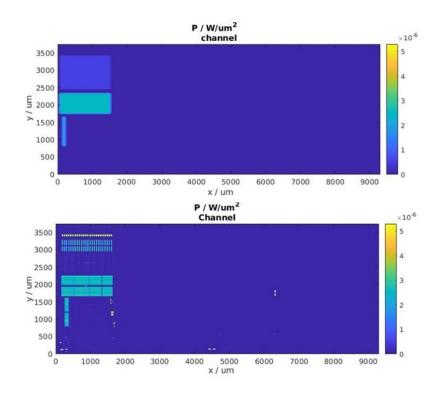

| 2.8  | Top: power profile of a standard FEM simulation; Bottom:                                                                  |    |

|      | Legato tool power profile                                                                                                 | 21 |

| 2.9  | Left: $\frac{R_{th}}{A}$ for radiation and convection; Right: $\frac{R_{th,ges}}{A}$ region for                           |    |

|      | different convection modes                                                                                                | 24 |

| 2.10 | Equilibrium temperature distribution of a point source with                                                               |    |

|      | $P = 1.94 W \dots $ | 27 |

|      | Temperature development of different elements/points with time                                                            | 28 |

| 2.12 | Tempeature profile at $y = 1875 \ \mu m$ for 40 ms at equilibrium .                                                       | 29 |

| 2.13       | Left: drain-source current for the operating points of the MOS      |          |

|------------|---------------------------------------------------------------------|----------|

|            | driver and the current mirror; Right: Perceptual change of the      |          |

|            | drain-source current with the current at 25 °C as a baseline        | 30       |

| 2.14       | Temperature profile of the current mirror                           | 31       |

| 2.15       | Left: mean finger temperature; right: finger current                | 31       |

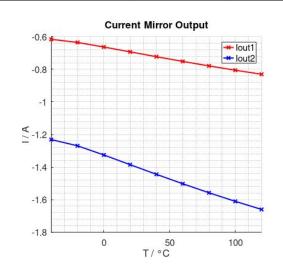

|            | Output current for different uniform temperatures                   | 32       |

| 2.17       | Temperature dependence of the thermal resistance for Grpo           | -        |

|            | and Grp3                                                            | 33       |

| 2.18       | Temperature dependence of the thickness of the glue layer of        |          |

|            | Grpo and Grp3                                                       | 33       |

| 2.19       | Temperature dependence of the thickness of the substrate of         |          |

|            | Grpo and Grp3                                                       | 34       |

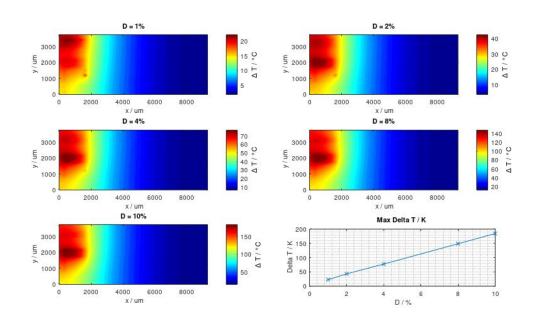

| 2.20       | Temperature distribution for different duty cycles                  | 35       |

| 2.21       | MOS current for different uniform temperatures and for the          |          |

|            | associated temperature profile for $T_{umg} = 29$ and $D = 10 \%$ . | 36       |

| 2.22       | Left: settling current with uniform temperature; Right: maxi-       |          |

|            | mum current with uniform temperature                                | 36       |

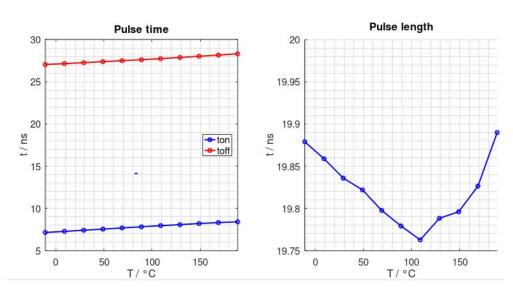

| -          | Left: pulse times, switch on and switch off; Right: pulse length    | 37       |

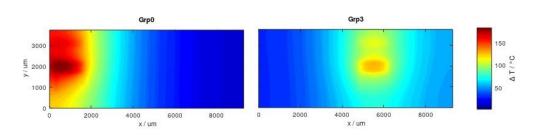

|            | Temperature distribution if Grpo or Grp3 is used with D = 10 $\%$   | 38       |

| 2.25       | Electro thermal simulation result of the MOS current for Grpo       |          |

|            | and Grp3                                                            | 38       |

| 3.1        | Failure rate over time, the typical bathtub curve                   | 41       |

| 3.2        | Schematic of the HCI [21]                                           | 41<br>42 |

|            | Schematic of the RD model of NBTI                                   |          |

| 3.3<br>3.4 | Reliability simulation workflow                                     | 44       |

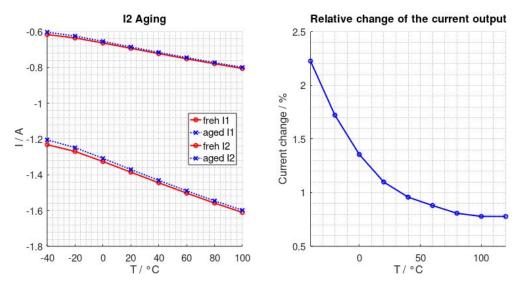

|            | Left: Change with operation point with temperature; Right:          | 49       |

| 3.5        | Change of Operation point due to NBTI ageing for an age time        |          |

|            | of 1 year                                                           | 50       |

| 3.6        | Change in output of the current mirror test circuit for age         | 90       |

| 9.0        | time of 10 years and uniform temperature; Left: current mirror      |          |

|            | outputs fresh and aged; Right: percentual change, equal for         |          |

|            | both outputs because of uniform temperature                         | 51       |

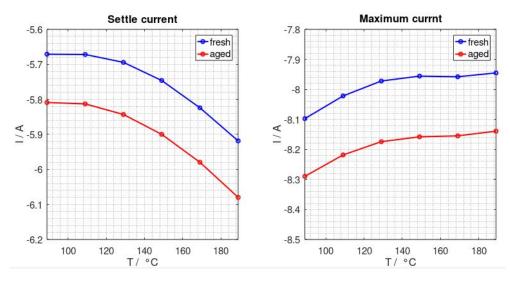

| 3.7        | Fresh vs aged results; Left: settle current with uniform temper-    | 5-       |

| 51         | ature; Right: maximum current with uniform temperature              | 52       |

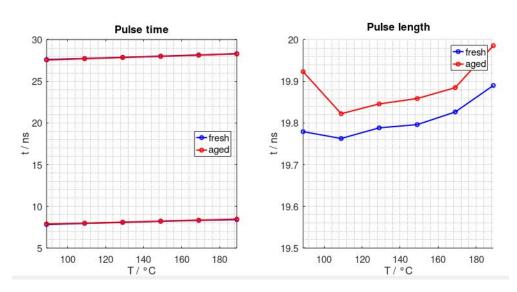

| 3.8        | Fresh vs aged results; Left: pulse times, switch on and switch      |          |

| 5          | off; Right: pulse length                                            | 53       |

|            |                                                                     |          |

| 3.9 | Driver current fresh and aged for different groups | 54 |

|-----|----------------------------------------------------|----|

|-----|----------------------------------------------------|----|

### **1** Introduction

#### 1.1 Basics of MOSFETs

The Metal-Oxide-Semiconductor Field-Effect-Transistor or MOSFET for short is a transistor widely used in microelectronics. [1] As the name suggests, the controlling of the transistor works with an electric field instead of a current flow. This allows a low power controlling of the transistor. The manipulation with an electric field is achieved via a capacitor at the connection between the source and drain called "gate".

The capacitor is built with the bulk connected to metal or for better processability with poly-silicon. A nonconductive layer is used as dielectrics, and the doped bulk silicon is connected to the bulk electrode. This structure allows change in resistance between the drain and source electrode by several orders of magnitude while keeping the current through the gate orders of magnitude lower than the drain-source-current.

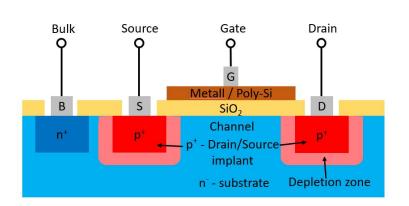

The area under the source- and drain-electrodes is p-doped (in the case of a p-MOSFET) while the rest of the bulk is n-doped, which results in a nonconduction depletion layer around the source and drain. The area near the silicon oxide between source and drain is called the "channel". Here most of the charge transport is taking place. The bulk also has a connection to prevent charging of the bulk; for that reason, it is often grounded. [1][2][3] This structure can be also seen in figure 1.1.

#### 1 Introduction

Figure 1.1: Schematic of a p-MOSFET

#### 1.1.1 Different Regimes, MOSFET Model and Characteristic Curves

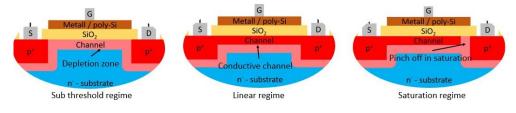

As explained, the MOSFET device uses the capacitor between gate and channel to manipulate the resistance between source and drain. This is done via the electric field of the capacitor. If the gate is biased negatively in the case of a p-MOSFET, an electric field is induced, which draws bulk holes to the interface between bulk and silicon oxide. As a result, a hole enriched channel between the p doped source and drain regions develops. Overall three different regimes can be seen if a MOSFET is biased in this way:

If the gate bias is smaller than a specific voltage called the threshold  $V_{th}$  voltage, this is called the subthreshold regime. In this regime, the applied bias is too small to fully invert the channel. Figure 1.2 shows the depletion zone in this regime for a p-MOSFETs. It is characterized by a small current between source and drain. This current can be approximated with o.

When the gate bias is increased by  $V_{th}$ , the operation area must also be divided with source-drain-bias. One where  $V_{DS} > V_{GS} - V_{th}$ , there the electric field is big enough for an inversion layer to be built, which means the two p-doped areas are also connected with a p-doped channel. That means the mobile holes can contribute to charge transfer. Figure 1.2 shows this conducting p-type channel for a p-MOSFET in the linear regime. In this region, the current goes linearly with the applied gate-bias and is called linear regime. The other case is  $V_{DS} < V_{GS} - V_T$ , there the source-drain current saturates, saturated regime. Here the holes accumulate at the interface, which cannot contribute to the drain current. [1][2][3] Figure 1.2 shows this pinch-off for the saturation of an p-MOSFET.

Figure 1.2: Schematic of an p-MOSFET

With the assumption that the inversion layer charge is proportional with the applied voltage this can also put in the form of equations[2]:

$$I_{D} = 0 \qquad \left\{ V_{GS} > V_{th} \\ I_{D,lin} = -\mu_{p} \cdot C_{ox} \frac{W}{L} (V_{GS} - V_{th} - \frac{V_{DS}}{2}) V_{DS} \\ I_{D,sat} = -\mu_{p} \cdot C_{ox} \frac{W}{2L} (V_{GS} - V_{T})^{2} \\ I_{D,sat} = -\mu_{p} \cdot C_{ox} \frac{W}{2L} (V_{GS} - V_{T})^{2} \\ I_{D,lin} \quad I_{D} \text{ linear regime [A]} \\ \mu_{p} \qquad \text{Electron Mobility } [\frac{m^{2}}{V_{s}}] \\ V_{GS} \quad \text{Gate-source potential [V]} \\ V_{DS} = V_{cox} \quad \text{Oxid capacitance [F]} \\ V_{DS} = V_{Cox} \quad \text{Oxid capacitance [F]} \\ V_{DS} = V_{DS} \quad \text{Drain-source potential [V]} \\ V_{DS} = V_{Cox} \quad \text{Oxid capacitance [F]} \\ V_{DS} = V_{DS} \quad \text{Oxid capacitance [F]} \\ V_{DS} = V_{DS} \quad \text{Oxid capacitance [F]} \\ V_{DS} = V_{Cox} \quad \text{Oxid capacitance [F]} \\ V_{DS} = V_{DS} \quad \text{Oxid capacitance [V]} \\ V_{DS} = V_{DS} \quad V_{DS}$$

This is one of the simplest models for the MOSFET device.

#### 1.2 Power-MOSFET

Depending on the application the basic MOSFET design was adopted to get a higher functionality. For high current/ high power applications, the relatively

high parasitic gate resistance had to be reduced. In the examples in this thesis, this is done in two ways.

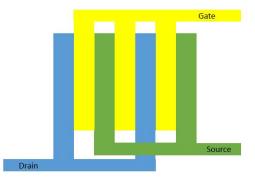

#### 1.2.1 Multi-Finger MOSFET

Here the width *W* of the MOSFET is split up *nf*-times, where *nf* is the number of fingers. Instead of a single transistor, nf parallel-connected smaller ones with the width W/nf are gotten, each drain and source is used doubled. The resulting structure is shown in figure 1.3. This has the advantage of a layout with an aspect ratio  $(\frac{W}{L})$  closer to one, which is easier to use. And it enhances the AC capabilities of the transistor by reducing the parasitic capacitance because of the parallel connection. [4]

Figure 1.3: MOSFET with three fingers

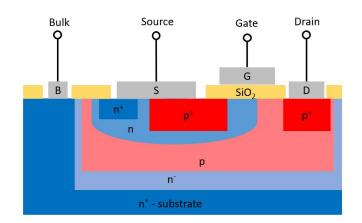

#### 1.2.2 LDMOS

An asymmetric variation of the standard MOSFET used in high voltage applications is called the Laterally Diffused MOSFET (LDMOS). It is designed for a low on-resistance and high blocking voltage. The cross-section can be seen in figure 1.4. The channel is short and not like a standard MOSFET a  $p^+-n^--p^+$  but a  $p^+-n-p-p^+$  transition in which the drain side is relatively weak doped. This results in a large depletion layer between the n-p and a small one between  $p^+-n$ . The consequence of this is a high blocking voltage with a short channel length because the diffused p-region results in a low on-resistance

and high current capability. The device got its name from the deep n-type region around the source and gate, made via diffusion. [1]

Figure 1.4: Cross-section of an LDMOS

#### **1.3 Test Circuits**

In this thesis, electro-thermal circuit simulation and its application in aging is investigated. For this reason, five example circuits were chosen. Because the investigation of the circuit extends over more than one chapter, this section will give an overview of the circuit and how they can be investigated.

#### 1.3.1 29V HV pMOS

The p-MOSFET of the current source in the MOS driver is a multi finger MOSFET with a width of 400 nm and a length of 1.8 um. It was chosen as a test circuit to assess if a finger resolved aging analysis adds value and for the investigation of the influence on boundary conditions of the thermal simulation.

#### 1 Introduction

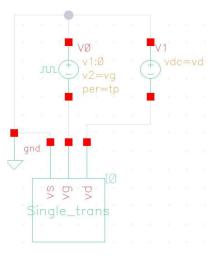

The circuit diagram for this can be seen in figure 1.5. The drain-source voltage will be held constant while the gate will be pulsed. This simulates the operation conditions into the driver circuit.

Figure 1.5: Circuit diagram for the p-MOSET test circuit

#### 1.3.2 Current Mirror

A current mirror is an elementary circuit that is used to generate currents out of a reference current. Application of it is analog-digital converter or current sources.

The goal was to demonstrate the layout dependent electrical performance of the circuit. There are multiple reasons why this structure was chosen. It is widely used in different variations, and it can be build up out of the same device blocks. Furthermore, the devices can be split up and placed independently in the layout. This is done to investigate the impact of the layout on the overall CM behaviour.

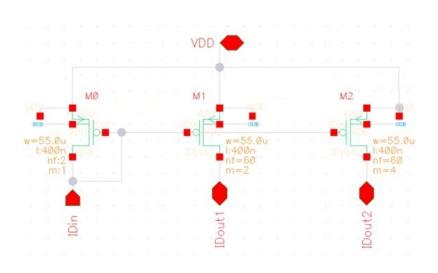

For this it is necessary to complete an electrothermal analysis and an electrothermal aware aging analysis. The circuit diagram can be seen in figure 1.6.

Figure 1.6: Circuit diagram for the current mirror test circuit

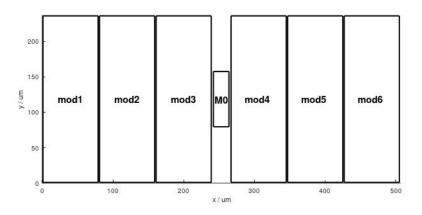

The transistors of the two outputs are divided into blocks of 60 fingers. Output 1 (M1) has two blocks, and output 2 (M2) has four. The way in which these six blocks are arranged can be seen in figure 1.7.

Figure 1.7: Layout of the current mirror

The division of the blocks for the two layouts can be seen in table 1.1.

#### 1 Introduction

| Table 1.1: Layouts |            |                         |  |  |  |

|--------------------|------------|-------------------------|--|--|--|

| Layout             | Mı         | M2                      |  |  |  |

| 1 (symetric)       | mod2, mod5 | mod1, mod3, mod 5, mod6 |  |  |  |

| 2 (staggerad)      | mod1, mod2 | mod3, mod4, mod 5, mod6 |  |  |  |

#### 1.3.3 MOS Driver

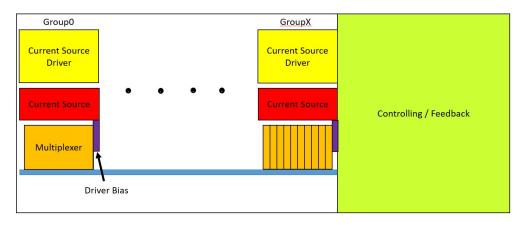

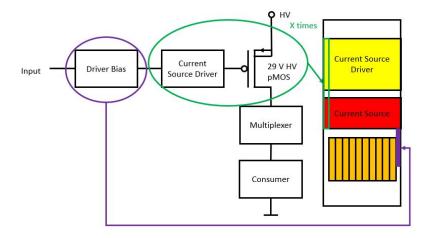

The MOS driver is part of a used case. It can supply pulses of a few hundred mA up to several A. This pulse can have a pulse length of hundred ns to several us.

As can be seen in figure 1.8 it consists of X identical groups next to a controlling and feedback area on the right side which is used to regulate the output (figure 1.8). The groups can be divided into four parts. The driver bias, which feeds into the current source driver, these two modules control the output current. The current source, the primary power consumer of the circuit and its main components, x 29V HV pMOS connected in parallel, can be electronically inserted and removed. After that, a output can be selected with a multiplexer (MUX). Under the multiplexer and in the controlling and feedback area, there are temperature sensors from which the temperature can be read out electronically.

Figure 1.8: Most important components of the MOS driver

In figure 1.9 a simplified schematic of one such module can be seen. The

output current is mainly produced with the drain-source resistance of the 29V HV pMOS. The high voltage on the source contact of the transistor is kept constant.

Figure 1.9: Left: Most important components of the MOS driver group; Right: group Layout

The goal is to find a relation between pulse length and channel temperature. The relationship between temperature and boundary condition will be analysed. This is necessary to give a confidence interval to be able to compare the result with measurement data from the temperature sensors. A comparison between the performance change of two groups will then be made. Lastly, the newly implemented temperature-sensitive aging workflow will be tested with this circuit. For this, an NBTI and HCI model was implemented. The result will be compared with the standard aging workflow.

## 2 Electro-Thermal Simulation

#### 2.1 Temperature Behavior of MOSFETs

A temperature change in the MOSFET area results in updated device characteristics. This is because of the temperature dependence of the band-gap  $E_g$  and an increase in phonons density. This higher phonon density results in more charge carrier scattering with the lattice, which decreases electron mobility. The outcome of this is that both the absolute value of the threshold voltage [5] and the charge carrier mobility decrease with temperature. As a simplified model, the threshold voltage can be assumed to depend linear on temperature.[6][7]

$$V_{th}(T) = V_{th}(T_0) + \alpha_{Vth}(T - T_0)$$

(2.1)

$\alpha_{Vth}$  Changing rate of threshold voltage with:  $sign(\alpha_{Vth}) = -sign(V_{th}(T_0))$

and for the mobility, a power law can be assumed [6][7]

$$\mu(T) = \mu(T_0)(T/T_0)^{\alpha_{\mu}}$$

(2.2)

$\mu(T_0)$  Charge carrier mobility  $[\frac{cm^2}{V_s}]$

$\alpha_{\mu}$  Constant dependent on the scattering in the inversion layer [] with  $\alpha_{\mu} < 0$  (typical values Si-Technology: -1.2 to -2.42) [6]

If (2.1) and (2.2) are substituted in (1.1) to get a temperature dependence for the first order equation of  $I_{D,sat}$  of a PMOS.[7]

$$I_{D,sat} = -\mu_0 (T/T_0)^{\alpha_{\mu}} \cdot C_{ox} \frac{W}{2L} (V_{GS} - V_{T0} - \alpha_{VT} (T - T_0))^2$$

(2.3)

10

#### 2.1.1 Thermal Runaway

Temperature-dependent device operation is inherent to every electrical device. This can be from a negative, in which the power decreases, or positive character, which leads to a power increase. Because consumed power also influences the temperature of a device, this results in a feedback loop. Negative feedback loops could be described as "self-cooling," while a positive feedback loop between consumed power and an increase in temperature is called thermal runaway. The temperature drift resulting from this feedback loop depends on the heat dissipation in the device area.

In MOSFETs, it is strongly gate-voltage dependent on which of the two processes occurs. If  $V_{GS}$  exceeds a specific range, the device reduces its current with rising temperature and acts as a negative feedback loop which reduces its power consumption. On the other side, if  $V_{GS}$  falls below a specific range, the opposite happens. The temperature increase is proportionate to the current increase. Thus, a positive feedback loop is in place.

#### Gradual channel approximation

The temperature dependence of the drain-source voltage of a MOSFET eq. 2.3 can be used to show this effect. By derivation the temperature dependency of the drain-source current can be obtained using the following formula:

$$\frac{\partial I_{D,sat}}{\partial T} = I_{D,sat} \cdot \left(\frac{\alpha_{\mu}}{T} - \frac{2\alpha_{VT}}{V_{GS} - V_{T0} - \alpha_{VT}(T - T_0)}\right)$$

(2.4)

For thermal runaway, the second term must be greater than zero.

$$\left(\frac{\alpha_{\mu}}{T} - \frac{2\alpha_{VT}}{V_{GS} - V_{T0} - \alpha_{VT}(T - T_0)}\right) > 0$$

(2.5)

Which can be reshaped into

$$V_{GS} > V_{T0} - \left(\frac{2}{\alpha_{\mu}} + 1\right) T \alpha_{VT} - \alpha_{VT} T_0$$

(2.6)

11

With the fact in mind that with a PMOS, both  $I_{D,sat}$  and  $V_{GS}$  are negative, that means thermal runaway can only occur with a small gate voltage. That also means because  $P \propto -V_{GS}$  the overall power consumption and the gradient is low in this range of gate voltage which again implies that thermal runaway is unlikely.

The point in which  $\frac{\partial I_{D,sat}}{\partial T}$  is equal to zero is called zero temperature coefficient (ZTC) point and only exists if  $\alpha_{\mu}$  is exactly -2 if not, this point expands to a small range where the derivation changes signs.

The same thing can, of course, be done with the equation of an NMOS with the same result.

#### Thermal activated carrier

If failures in microelectronics are analysed, it is found that silicon melts sometimes. This means that thermal runaway leads sometimes to temperatures above the melting temperature of Silicon (1414  $^{\circ}$ C). This section demonstrates a thermal runaway mechanism that can lead to device failure. The onset of it is where there are more thermally activated carriers than there are carriers due to doping, hence in the range of 600 - 8000  $^{\circ}$ C depending on the doping. The initial heating to this point might be caused by some other mechanism such as impact ionization, but if it is reached, the resistivity of the silicon drops and thermal runaway is initiated.

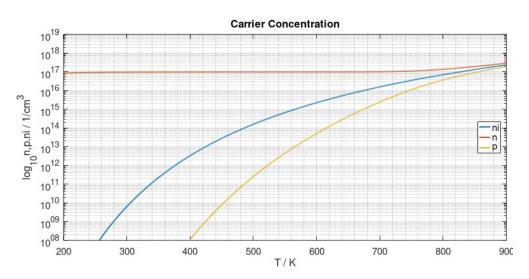

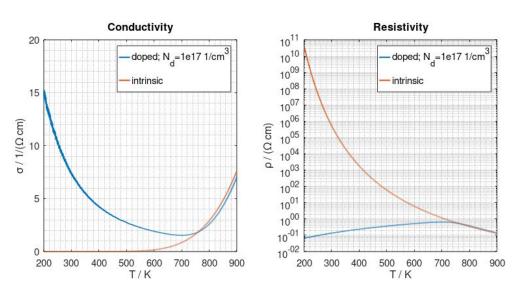

If the temperature in a semiconductor is raised, electrons can be thermally activated and go from the valence band to the conduction band, which produces a free electron and a hole. The resulting density of the carrier of n-doped silicon with a donor density  $10^{17} \frac{1}{\text{cm}^3}$  can be seen in figure 2.1. The carrier density is almost constant until 750 °C because of the donors and then approaches the intrinsic carrier density.

Figure 2.1: Charge carrier concentration for n-doped silicon with a doping concentration of  $10^{17} \ 1/cm^3$

With the carrier density a conductivity and resistivity can be defined:

$$\sigma = \frac{1}{\rho} = e(p\mu_p + n\mu_n) \tag{2.7}$$

| $\sigma$ | Conductivity $\left[\frac{1}{\Omega cm}\right]$       | $\sigma$ | Resistivity [Ωcm]                                 |

|----------|-------------------------------------------------------|----------|---------------------------------------------------|

| п        | electron density $\left[\frac{1}{\text{cm}^3}\right]$ | р        | hole density $\left[\frac{1}{\text{cm}^3}\right]$ |

| $\mu_n$  | electron mobility $\left[\frac{cm^2}{Vs}\right]$      | $\mu_p$  | hole mobility $\left[\frac{cm^2}{Vs}\right]$      |

Together with the model of the temperature dependence of the mobility from eq. (2.2) a conductivity/resistivity of silicon can be calculated. The resistivity is, at constant voltage, proportional to the consumed power. If you look at figure 2.2 that means that above 750 °C, the silicon is prone to thermal runaway. This form of the conductivity curve is dominated at low temperature by the temperature dependence of the mobility while the carrier density stays roughly constant, whereas at high temperatures the carrier density dominates. This leads to a maximum in resistivity curve, which is dependent on the doping concentration.

#### 2 Electro-Thermal Simulation

Figure 2.2: Left: Conducvity; Right: Resistivity

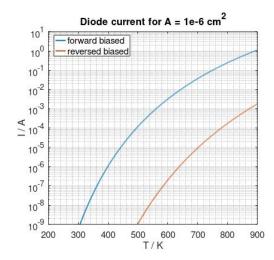

In a MOSFET, the current path through the channel is, as demonstrated, above thermal stable. Another possible paths are when the current goes through the reverse biased drain-bulk-diode and then either to the bulk or through the forward-biased bulk-source diode. A diode can be described with the diode equation:

$$I(V) = I_S\left(\exp(\frac{eV}{k_BT}) - 1\right)$$

(2.8)

With an saturation current:

$$I_S = A\sqrt{e}n_i^2 \left(\frac{\sqrt{\mu_p k_B T}}{\sqrt{\tau_p N_d}} + \frac{\sqrt{\mu_n k_B T}}{\sqrt{\tau_n N_a}}\right)$$

(2.9)

$\tau_n$  Minority carrier lifetime for electrons [s]  $\tau_p$  Minority carrier lifetime for holes [s] If *V* is much larger than  $\frac{k_B T}{e}$  ( $\frac{k_B 200}{e} = 0.077$  to  $\frac{k_B 900}{e} = 0.017$ ) the reserve biased current can be approximated as the saturation current  $I_S$  and as therefore independent of the applied voltage. This means the current of the other

14

paths is limited by the saturation current of the drain-bulk diode. In figure 2.3, the temperature dependence of the diode current of a forward and a reserve biased diode can be seen. The current rises with temperature, which leads to higher power consumption and thermal runaway.

Figure 2.3: Temperature dependence of the diode current at V = 0.5 V

#### 29V HV pMOS

While a typical SPICE (Simulation Program with Integrated Circuit Emphasize) model of a MOSFET has the effect described in chapter 2.1.1 the thermal runaway is because of thermally activated carrier not modeled. Figure 2.4 shows the result of a simulation of the output transconductance curve of the 29V HV pMOS depending on the temperature with a width of  $W = 55 \ \mu m$  and a length of  $L = 400 \ nm$  at a drain voltage of  $V_{DS} = -20 \ V$ .

#### 2 Electro-Thermal Simulation

Figure 2.4: Output characteristics and transfer characteristics of the 29V HV pMOS transistor depending on the temperature

Just as derived in the gradual channel approximation, it has an intersection range from  $V_{GS}$  -1.26 V to 1.29 V. A Sketch for better visibility can be seen in figure 2.5.

Figure 2.5: Sketch of transfer characteristic visible in figure 2.4; Inversion range of the IDS in dependence of the VGS

The other result derived from the gradual channel approximation is that sign of  $\frac{\partial I_{D,sat}}{\partial T}$  is not or is only weakly dependent on the drain-source voltage. In figure 2.6 the numerical derivation of the output and transconductance curve can be seen. Only the derivation of the transconductance curve has a range where the derivation is rising.

Figure 2.6: Partial derivation of IDS over T

#### 2.2 Multi-Scale Simulation

The behaviour of an electronic device like a MOSFET can be described as dependent on the number of scattering events during the transport. For a low number or no scattering events, the Drift-Diffusion equation can be taken, and in the case of many scattering processes, the Boltzmann transport equation can be used. These two equations can be solved with numerical methods like Finite Element Methods (FEM) for a low number of devices. The problem arises with the simulation of complex devices consisting of thousands or millions of single devices. If this is attempted, the number of grid points needed is determined by the length cubed, which means the numerical method quickly reaches its limits.

To counter this, the assumption is made that devices do not influence each other electrically on a chip. This assumption is needed either way to make chip development possible. With his in mind, single device models are made via empirical data and the numerical solution of the earlier equation. To give examples a couple of examples, HiSIM2[8] uses the surface-potential, and BSIM4[9] is a modification of the result from the gradual channel approximation combined with several empirical relations. Another example of this

would be a solution with the gradual channel approximation of a MOSFET on page 3.

These models translate the inner working of the devices to a relationship between currents and voltages on different terminals. With this, the devices on a chip can be seen as a location-independent network, which allows the representation via conductivity matrix  $G_{ij}$ . The electrical behaviour of the circuit can be gotten with:

$$G_{ij} \cdot V_j = I_i \tag{2.10}$$

With these equations, the calculation of the behaviour of large circuits is possible by combining the device equations to a set of coupled (differential) equations for which standard numerical solution methods are available (eq. Newton-Rapson). [10]

#### 2.3 Simulation Method

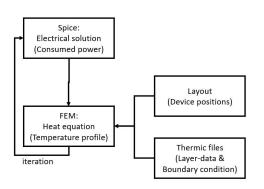

The simulation is done with the Legato Reliability Solution, a tool from Cadence. This tool combines the SPICE analog electronic circuit simulator [10] spectre(@TM) with a FEM simulation for the heat equation via a cosimulation. As the SPICE simulation has inherently unconsidered of device positions, the circuit layout is needed to map the consumed power of the devices to a cuboid FEM model. This 3D model consists of a layered structure with an active material, instances, wires, and a passive dielectric material. The connection to the environment in this tool is modeled by a constant thermal resistance and thermal capacity for each side, which simulates a package. This constant thermal connection is a disadvantage of this tool. An analysis of the dependence of the result on the thermal resistance is undertaken in chapter 2.4.5.

With this information, the FEM model is solved. This result can be plugged in the electrical simulation again to update the temperature dependent model parameter of the compact models to iterate until the solution converges.

The simulation flow can be seen in figure 2.7.

Figure 2.7: Block diagramm for the general simulation flow

# 2.3.1 Power Input Profile Legato vs Typical Standard FEM Simulation

If this workflow is compared with a standard FEM simulation, the advantage is the detailed power profile obtained from the SPICE simulation. An example of this can be seen in figure 2.8.

Figure 2.8: Top: power profile of a standard FEM simulation; Bottom: Legato tool power profile

#### 2.3.2 Thermic Connection to the Environment

As described above the environment connection must be inputted via heat capacity *C* and thermal resistance  $R_{th}$ .

$$C = \frac{dQ}{dT} \tag{2.11}$$

$$R_{th} = \frac{\Delta T}{\dot{Q}} \tag{2.12}$$

21

| С | heat capacity $\left[\frac{1}{K}\right]$ |  |

|---|------------------------------------------|--|

|---|------------------------------------------|--|

- $R_{th}$  thermal resistance  $[\frac{K}{W}]$  $\dot{Q}$  heat transfer rate [W]

- Q heat energy [J] temperature difference [K]  $\Delta T$

For environment connection, three cases would be defined.

#### **Heat Sink**

In the case of a heat sink, the boundary temperature of the chip is equal to the ambient temperature, which is equal to  $R_{th} = C_p = 0$ .

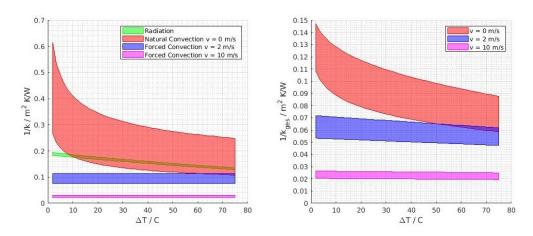

#### **Radiation and Convection**

The second one is no package, connection with thermal radiation, and natural or forced convection. Here, on the one hand, the power dissipation via radiation is described with the Stefan-Boltzmann law.

$$\dot{Q} = \epsilon A \sigma \left( T^4 - T_a^4 \right) \tag{2.13}$$

Stefan-Boltzmann constant  $\left[\frac{W}{m^4K^2}\right]$ emissivity []  $\epsilon$  $\sigma$ Т  $T_a$ ambient temperature [K] temperature [K]

Α surface area [m<sup>2</sup>]

The only variable here is the emissivity of the surface which describes the effectiveness of emitting but also absorbing radiation. It is a number between o, perfect reflection or transmission of all incoming radiation, and 1, perfect absorption. The difficulty here is that this value depends not only on the material and material structure but also on the topology of the surface. There are three sur-

|                                    | $S_1O_2$ coated on $S_1$ : | $\epsilon = 0.88$ to 0.9 | [11] |

|------------------------------------|----------------------------|--------------------------|------|

| face material used in this thesis: | Fr-4:                      | $\epsilon = 0.8$ to 0.9  | [12] |

|                                    | Copper oxide:              | $\epsilon = 0.6$ to 0.7  | [13] |

On the other hand convective heat transfer can be described with

$$\dot{Q} = k A \Delta T \tag{2.14}$$

heat transfer coefficient  $\left[\frac{W}{m^2 K}\right]$ k

22

In this formula, all dependencies are put into the transfer coefficient such as temperature difference, thermal proprieties of the fluid, boundary conditions e.g. room height, and the fluid velocity and angle of this velocity to the surface. The heat transfer coefficient is definition by related to the thermal resistance as,

$$R_{th,conv} = \frac{1}{A k}$$

(2.15)

Because of the many system dependencies, an accurate value can only be obtained for each case with computational fluid dynamics. There are also some more sophisticated empirical equations for specific cases [14] [15], but they are only valid for these defined conditions. Because of this, it was decided to take a more rudimentary approach to experimentally find relations and make a simulation with the lowest and highest heat transfer coefficient.

In principle, there are two types of convective heat transfers: Convective heat transport is called natural, where the motion of the fluid is only caused by buoyancy resulting from the temperature dependency on density variation of the fluid. Here the heat transfer coefficient can be described with the empirical formula.

$$k_{conv,nat} = C(\Delta T)^n \tag{2.16}$$

Here *n* is 0.25 and C depending on the direction between 1.319 and 3.158.[16]

On the other hand, if the external fluid flow is present, it is called forced convection. Here the heat transfer coefficient can be approximated for air linearly with air velocity, with a and b as constants. [17]

$$k_{conv,forced} = a + b v \tag{2.17}$$

v fluid velocity

with constant set  $a_1 = 5.7$ ,  $b_1 = 3.8$  or  $a_2 = 2.8$   $b_2 = 3.0$ .

The thermal resistances from radiation and convection add up like two electrical resistances. In figure 2.9 the equation of this chapter for the thermal resistances are visualised  $\left(\frac{R_{th}}{A} = \frac{1}{k}\right)$ .

$$R_{ges} = \frac{1}{A \ k_{ges}} = \frac{1}{\frac{1}{\frac{1}{R_{rad}} + \frac{1}{R_{conv}}}}$$

(2.18)

#### 2 Electro-Thermal Simulation

Figure 2.9: Left:  $\frac{R_{th}}{A}$  for radiation and convection; Right:  $\frac{R_{th,ges}}{A}$  region for different convection modes

#### 2.3.3 Heat Equation

The inhomogeneous heat equation 2.19 describes the time development of the temperature in the presence of a heat source and is solved in a dynamical run of the tool.

$$\frac{\partial T(\vec{x},t)}{\partial t} - \frac{\lambda(\vec{x})}{c(\vec{x})\rho(\vec{x})}\vec{\nabla}^2 T(\vec{x},t) = \frac{\omega(\vec{x},t)}{c(\vec{x})\rho(\vec{x})}$$

(2.19)

$\begin{array}{ll} \lambda & \text{thermal conductivity } [\frac{W}{m K}] & c & \text{specific heat capacity } [\frac{J}{kg K}] \\ \rho & \text{density } [\frac{kg}{m^3}] & \dot{Q} & \text{heat transfer rate } [W] \\ \omega & \text{heat source density } [\frac{J}{s m^3}] & \end{array}$

#### **Example Solution: 1D**

One way to analytically solve the equation given in eq. 2.19 is via folding the Green's function of eq. 2.25 [18] for one dimension:

24

$$T(x,t) = \int_{-\infty}^{\infty} f(\zeta)G(x,\zeta,t)d\zeta + \int_{0}^{t} \int_{-\infty}^{\infty} \frac{\omega(\zeta,\tau)}{c\rho} G(x,\zeta,t-\tau)d\zeta dt \quad (2.20)$$

Where f(x) is the initial temperature distribution at t = 0 and G is the Green's function. For a domain of x from  $-\infty$  to  $\infty$ :

$$G(x,\zeta,t) = \frac{1}{2\sqrt{\pi at}} \exp(-\frac{(x-\zeta)^2}{4at})$$

(2.21)

where *a* is the thermal diffusivity  $a = \frac{\lambda}{c\rho}$  with a point power source of  $\omega = \delta(x) \cdot C$  and a starting temperature profile of f(x) = 0 first part of 2.20 is zero and the rest can be solved with the result

$$T(x,t) = \frac{C}{2\lambda\sqrt{\pi}} \left[ \sqrt{4at} \exp(-\frac{x^2}{4at}) - |x|\sqrt{\pi} \left(1 - \operatorname{erf}(\frac{|x|}{2\sqrt{at}})\right) \right] \quad (2.22)$$

For both therms, similar to the diffusion equation, a characteristic length and time scale can be defined. The diffusion length  $l_{diff}$  and characteristic time  $t_{diff}$ :

$$l_{diff} = 2\sqrt{at} \tag{2.23}$$

$$t_{diff} = \frac{\Delta x^2}{4a} \tag{2.24}$$

These two parameters can be used to describe the transition to the equilibrium. If it holds in a system for every point  $t >> t_{diff}$  and  $x << l_{diff}$  a static solution can be assumed.

#### **Example Solution: Equilibrium Solutions**

In the case of  $\frac{\partial T(\vec{x},t)}{\partial t} = 0$  the heat equation for the equilibrium conditions is obtained, which is a Poisson equation.

$$-\vec{\nabla}^2 T(\vec{x}) = \frac{\omega(\vec{x})}{\lambda(\vec{x})}$$

(2.25)

In the case of cylindrical and spherical coordinates the equation becomes:

| cylindrical symmetry                                                    | spherical symmetry                                                      |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------|

| $\frac{d}{dr}\left(r\frac{dT}{dr}\right) + \frac{r\omega}{\lambda} = 0$ | $rac{d}{dr}\left(r^2rac{dT}{dr} ight) + rac{r^2\omega}{\lambda} = 0$ |

|                                                                         | with the solutions                                                      |

| $T = -\frac{\omega r^2}{4k} + A \ln r + B$                              | $T = -\frac{\omega r^2}{6k} + \frac{A}{r} + B$                          |

## 2.4 Simulation Results

As the experiment circuits first, a single p-MOSFET was chosen to introduce effects without the influence of the circuit. Next, the influence of different layouts on a chip will be shown with a current mirror. Finally the influence of a temperature profile on the operation of a circuit will be shown in the example of the MOS driver.

The layer stack used in this simulation can be seen in table 2.1

| Table 2.1: Used layer stack   |                                                          |          |               |  |  |

|-------------------------------|----------------------------------------------------------|----------|---------------|--|--|

| Layer name                    | Layer name   layer thickness / $\mu$ m   active material |          |               |  |  |

| 180 nm technology layer stack | 7.36                                                     | silicon  | silicon oxide |  |  |

| Channel                       | 0.33                                                     | silicon  |               |  |  |

| Substrate                     | 350                                                      | silicon  |               |  |  |

| Glue                          | 100                                                      | glue     |               |  |  |

| PCB                           | 500                                                      | TR4      |               |  |  |

| Glue                          | 50                                                       | glue     |               |  |  |

| Heatsink                      | 1500                                                     | aluminum |               |  |  |

| Table 2.2: Thermal constants used for the simulation |                 |                           |                                     |  |  |  |

|------------------------------------------------------|-----------------|---------------------------|-------------------------------------|--|--|--|

|                                                      | Material        | $\lambda / \frac{W}{m K}$ | $\rho \cdot c_p / \frac{J}{m^{3}K}$ |  |  |  |

|                                                      | silicon         | 148                       | 1658960                             |  |  |  |

|                                                      | silicon oxide   | 12.4                      | 2440000                             |  |  |  |

|                                                      | glue            | 1.6                       | 1658960                             |  |  |  |

|                                                      | TR <sub>4</sub> | 30                        | 2090000                             |  |  |  |

|                                                      | aluminum        | 204                       | 2434498                             |  |  |  |

The thermal conductivity  $\lambda$  and the volumetric heat capacity  $\rho \cdot c_v$  at room temperature for the materials listed in table 2.1 can be seen in 2.2.

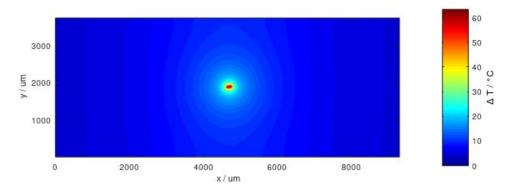

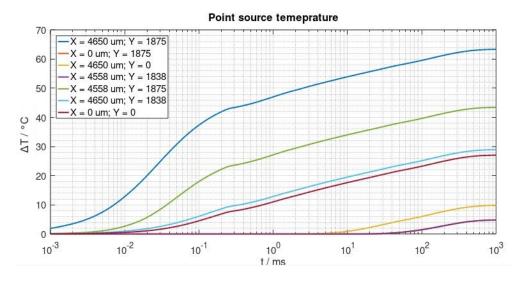

#### 2.4.1 Electro Thermal Simulation of a Point Source with the 180 nm Technology Layer Stack

In order to judge if a dynamical electro-thermal simulation to equilibrium can be achieved, the power input of the MOS driver at D = 2 % of P = 1.94 Wwas taken and placed in the middle of a chip at the same size as the MOS driver (9300  $\mu$ m x 3750  $\mu$ m). Then a dynamical simulation was made with a 101x101 grid. The associated equilibrium profile of the discussion can be seen in figure 2.10.

Figure 2.10: Equilibrium temperature distribution of a point source with P = 1.94 W

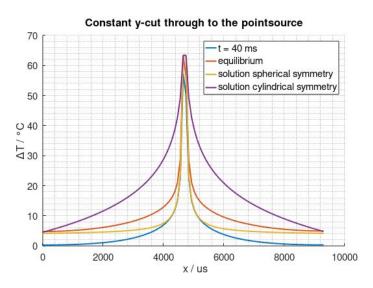

In figure 2.11 the temperature development with time can be seen for selected grid points. The middle point, the adjacent points left, right, and diagonal of it, and the border points were taken. It can be seen that each element initially has a heating-up phase, which then turns into a process where the heating rate of the elements is roughly the same. This can be seen in figure 2.12 where a temperature profile at  $y=1875 \mu$  at a time of 30 ms and equilibrium can be seen. After this 40 ms, the chip warms up at an almost constant rate until the equilibrium is reached at roughly 700 ms. In comparison the characteristic time  $t_{diff}$  defined in eq. 2.24 with a thermal diffusivity  $a = 86 \frac{\text{mm}^2}{\text{s}}$  and the furthest away from the power source is  $t_{diff} = 62 \text{ ms}$ , which is twice as high as the measured 30 ms for the heat to reach the same border. The equilibrium solutions for radial and spherical symmetry are plotted in the figure for comparison.

Figure 2.11: Temperature development of different elements/points with time

Figure 2.12: Tempeature profile at  $y = 1875 \ \mu m$  for 40 ms at equilibrium

#### 2.4.2 Temperature Behaviour of a Single p-MOSFET

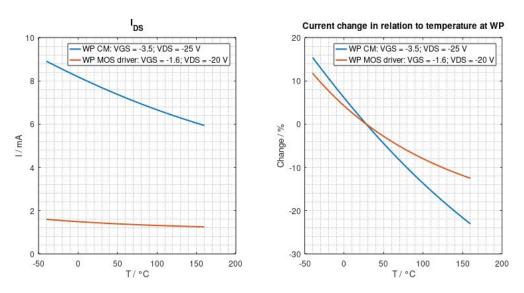

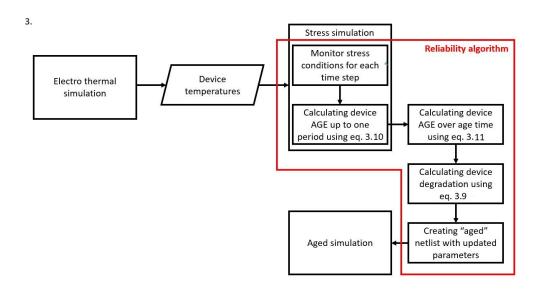

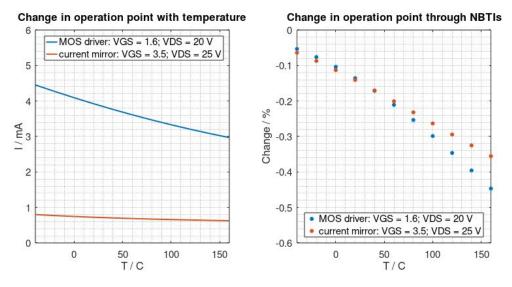

To analyse the behaviour of other test circuits, a temperature dependent simulation of the main transistor (29V HV pMOS) with one finger was made. The results of this can be seen in figure 2.13.

Figure 2.13: Left: drain-source current for the operating points of the MOS driver and the current mirror; Right: Perceptual change of the drain-source current with the current at 25  $^{\circ}$ C as a baseline

As expected, the current is falling with temperature and the relative change is proportional to the gate voltage. With this also the behaviour of a multi finger transistor can be calculated which is:

$$I_{DS,ges} = \sum_{i=0}^{nf} I_{DS,i}(T_i)$$

(2.26)

### 2.4.3 Electro-Thermal Simulation of a Current Mirror

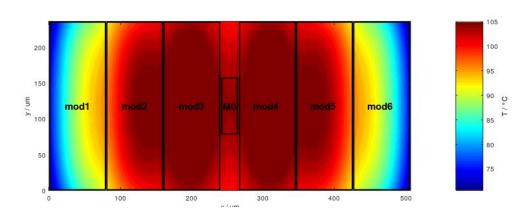

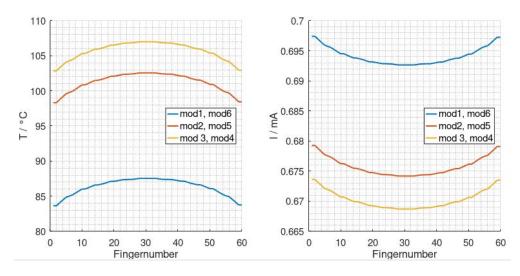

The current mirror was simulated with an input pulse of 10 mA and a duty cycle from 10 %. The supply voltage was chosen with -25 V. The difference between the two test layouts is only the swapped modules that means that the temperature profile is identical and can be seen in figure 2.14.

For the electrical simulation, the tool takes the mean temperature of the position of the associated transistor. The temperature taken for the simulation and the resulting current can be seen in figure 2.15.

30

Figure 2.14: Temperature profile of the current mirror

Figure 2.15: Left: mean finger temperature; right: finger current

The division between the two output transistors can be seen in table 2.3. The resulting output currents for the two layouts are listed in table 2.4.

For comparison, the circuit was also simulated with different uniform temperatures (T(x, y, z) = const). The resulting currents can be seen in figure 2.16.

| Table 2.3: Layout variants of the current mirror |            |                         |  |  |  |

|--------------------------------------------------|------------|-------------------------|--|--|--|

| Layout M1 M2                                     |            |                         |  |  |  |

| 1 (symetric)                                     |            | mod1, mod3, mod 4, mod6 |  |  |  |

| 2 (staggerad)                                    | mod1, mod2 | mod3, mod4, mod 5, mod6 |  |  |  |

| Table 2.4. Results for the symmetric layout         |        |        |  |  |  |

|-----------------------------------------------------|--------|--------|--|--|--|

| $T_{umg} = 25 \text{ °C}  T_{umg} = -40 \text{ °C}$ |        |        |  |  |  |

| IDout1 (symmetric Layout)                           | -0.828 | -0.720 |  |  |  |

| IDout2 (symmetric Layout)                           | -1.636 | -1.454 |  |  |  |

| IDout1 (staggered Layout)                           | -0.810 | -0.738 |  |  |  |

| IDout2 (staggered Layout)                           | -1.635 | -1.457 |  |  |  |

Table 2.4: Results for the symmetric layout

Figure 2.16: Output current for different uniform temperatures

# 2.4.4 Influence of Simulation Variables for the MOS Driver Simulation

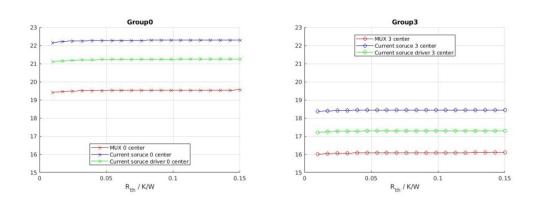

For the influence of the simulation variables, the three most important results are listed below. The thermal resistance has only limited influence on the temperature, as it can be seen in figure 2.17. This indicates that most of the heat dissipation of the chip is done through the heat sink at the bottom.

Figure 2.17: Temperature dependence of the thermal resistance for Grpo and Grp3

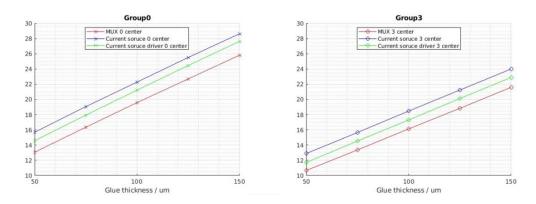

The glue thickness shows a linear dependence on the temperature.

Figure 2.18: Temperature dependence of the thickness of the glue layer of Grpo and Grp3

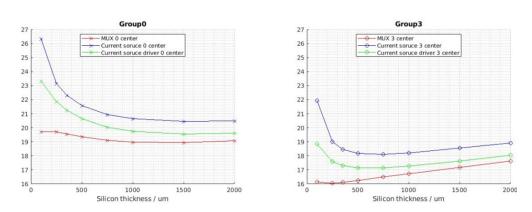

The substrate causes dependent on the thickness two effects, a heat spread which causes a temperature decrease, and thermal resistance to the heat sink, which causes a temperature increase. If these two effects for some substrate thickness, a minimum in temperature occurs.

#### 2 Electro-Thermal Simulation

Figure 2.19: Temperature dependence of the thickness of the substrate of Grpo and Grp3

#### 2.4.5 Electro-Thermal Simulation of a MOS driver

For the simulation of the MOS driver an inverse heat transfer coefficient of  $\frac{1}{k} = 0.01 \frac{\text{m}^2 \text{ K}}{\text{W}}$  was taken. The boundary temperature for the bottom side of the heat sink was set at room temperature. Then first temperature profile depended on the duty cycle was simulated at an environment temperature of T = 29 °C and T = -40 °C. For a duty cycle of D = 10 % the electrical output of this electro-thermal simulation can then be compared to the simulation of uniform temperature.

#### Thermal Results of the MOS Driver

The result of electro-thermal simulation for different duty cycles can be seen in figure 2.20. For lower duty cycles, a hotspot at  $x = 1580 \ \mu m$  and  $y = 1200 \ \mu m$  was identified. The maximum temperature is linear dependent on the duty cycle.

Figure 2.20: Temperature distribution for different duty cycles

#### **Electrical Results of the MOS Driver**

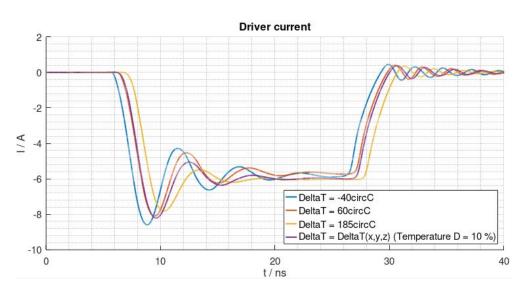

For the electro-thermal result, the pulse at D = 10 % is compared against the simulation with different uniform temperatures. The overall pulse can be seen in figure 2.21. Also, five different parameters were compared: the maximum current, the settling current at the end of the pulse, the on-time and off-time, which is defined when the current falls below -4 A, and the pulse length, which is the difference between the two.

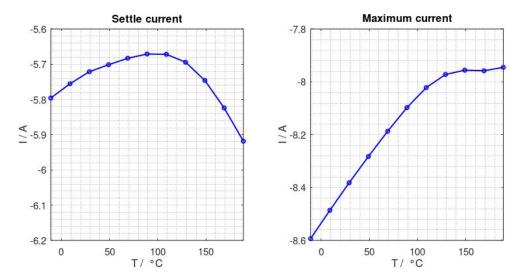

The two current parameters can be seen in figure 2.22. The settling current has its minimum at 100°C and falls at higher temperatures, while the maximum current decreases with rising temperature but has a plateau at 150 °C.

The time characteristics of the pulse are depicted in figure 2.23. Both the start and end time of the pulse is linear with the temperature while the pulse length varies by 0.1 ns.

#### 2 Electro-Thermal Simulation

Figure 2.21: MOS current for different uniform temperatures and for the associated temperature profile for  $T_{umg}~=~29$  and D~=~10~%

Figure 2.22: Left: settling current with uniform temperature; Right: maximum current with uniform temperature

Figure 2.23: Left: pulse times, switch on and switch off; Right: pulse length

The result of the electrical characteristics of the electro-thermal simulation can be seen in figure 2.5

| Table 2.5. Electro mermai simulation result |                |                     |                         |                       |               |  |

|---------------------------------------------|----------------|---------------------|-------------------------|-----------------------|---------------|--|

|                                             | $-I_{max}$ / A | $-I_{settling}$ / A | t <sub>start</sub> / ns | t <sub>end</sub> / ns | $t_{PL}$ / ns |  |

| Grpo, $T_{umg}$ = -40 °C                    | 8.09           | 5.76                | 7.22                    | 27.01                 | 19.80         |  |

| Grpo, $T_{umg} = 29 ^{\circ}\mathrm{C}$     | 8.22           | 5.98                | 7.87                    | 27.78                 | 19.92         |  |

| Grpo, $T_{umg}$ = -40 °C                    | 8.31           | 5.78                | 6.95                    | 26.79                 | 19.84         |  |

| Grpo, $T_{umg} = 29 ^{\circ}\mathrm{C}$     | 8.13           | 5.74                | 7.70                    | 27.49                 | 19.79         |  |

| Grp3, $T_{umg}$ = -40 °C                    | 8.61           | 5.87                | 6.68                    | 26.58                 | 19.98         |  |

| Grp3, $T_{umg}$ = 29 °C                     | 8.38           | 5.77                | 7.42                    | 27.25                 | 19.83         |  |

Table 2.5: Electro thermal simulation result

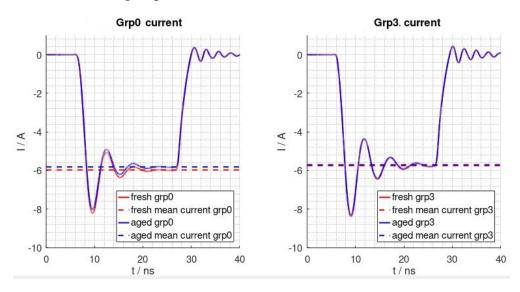

#### **Comparison between Groups**

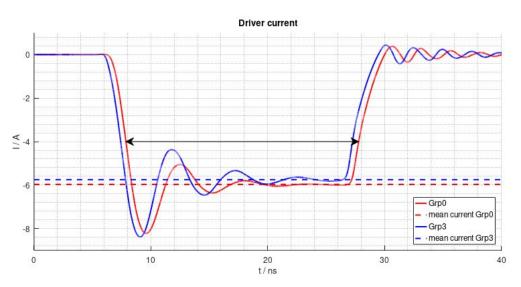

While the electrical construction of the groups of the MOS driver is the same, the difference in power dissipation because of the different positions causes them to behave differently. The different temperature profile for ten % duty cycle is shown in figure 2.24 and the resulting pulse is shown in figure 2.25.

#### 2 Electro-Thermal Simulation

Figure 2.24: Temperature distribution if Grpo or Grp3 is used with D = 10 %

Figure 2.25: Electro thermal simulation result of the MOS current for Grpo and Grp3

The characteristics resulting from this are listed in table 2.6.

| O3         Grpo - Grp3           0         54 |

|-----------------------------------------------|

| 54                                            |

|                                               |

| 23                                            |

| 0.34                                          |

| 8 -0.17                                       |

| 7 0.20                                        |

| 0.08                                          |

| 2 0.45                                        |

|                                               |

Table 2.6: Comparisson between Grpo and Grp3

Here it can be seen that even if electrically identical circuit parts are used their behaviour changes dependent on the layout around of them.

## **3 Ageing Simulation**

## 3.1 Reliability

#### 3.1.1 Reliability Basics

Reliability [19] [20] is the quality of a device to have defined properties for a certain amount of time until it has inevitable degrades and it ends its lifetime. This degradation is a statistical process because of the slight process variation in the production of devices, a difference in stress, and the probabilistic nature of physical processes responsible for degradation.

In general, the equation which describes survivors after a specific time is given by:

$$\frac{dM}{dt} = -\lambda(t)M(t) \tag{3.1}$$

M(t) describes the number of survivors at the specific time *t* and  $\lambda(t)$  is the rate of failure to this particular time.

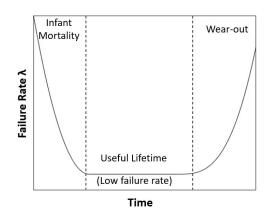

Typically this failure rate has the form of a bathtub curve shown in figure 3.1. In the figure, three regions can be seen. The failure rate is high at the beginning because not all of the significant production errors have been found, however it falls while this happens. Then there is a long time with a constant small failure rate. This is the area where devices degrade slowly, which is an interesting area for this thesis. At the rapid rise of failure rate, in the end, is the wear out and marks the end of the lifetime of a device.

In addition to the failure rate also a degradation rate *k* can be defined which describes how fast the physical process of degradation is progressing. This is

40

Figure 3.1: Failure rate over time, the typical bathtub curve

related to the time to failure (*TF*) in the way that failure is reached when a critical parameter  $p_{krit}$  is exceeded.

$$p_{krit} = p_0 \cdot e^{-\int_0^{1F} k(t)dt}$$

(3.2)

With this, a *TF* for a device can be calculated, which is the time until  $p_{krit}$  is reached.

The standard reliability time frames are often around ten years, therefore the constants for reliability models can not be obtained from regular measurements following has to be done. Extrapolation from shorter time frames under the assumption that the degradation mechanism does not change. And accelerated testing, a greater than usual stress is applied so that the devices age faster. The result is then calculated back to normal stresses. This works under the assumption that the ageing mechanism does not change with stress.

## 3.2 Degradation Mechanism of MOSFET

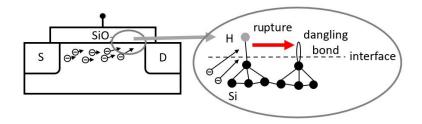

The shift of the characteristic curves characterises the reliability performance of a MOSFET. Different stresses on mechanisms lead to the shifting of each device until the circuit can no longer perform its task. In the simulation of this thesis, two of these degradation mechanisms will be considered. For both of them, Si-H bounds at the Si-SiO<sub>2</sub> interface play an important role. These bonds exist because, in modern CMOS technology, the material for the gate dielectric is almost always amorphous silicon dioxide. This amorphousness results in dangling bonds at the interface, which, if left alone, would be electrically active and capture the charge. To prevent this, hydrogen is used to bind these dangling bonds.

#### 3.2.1 Hot Carrier Injection (HCI)

Hot carriers emerge in a MOSFET trough the acceleration of carriers by the drain-source voltage. These hot electrons can produce through impact ionization an electron whose momentum is directed to the dielectric (figure 3.2). This is non-uniform because the electrons first need the build up the required kinetic energy.

Figure 3.2: Schematic of the HCI [21]

There are three different damaging modes of hot carriers on MOSFET:

- interface trap creation: The dissociation energy of the Si-H bond at the interface is as low as 2eV. [22] If such a bond is broken, it can act as a trap for electrons.

- hot electron injection: If the momentum of an electron is directed to the bulk oxide and it can overcome the potential barrier of 3.1 eV, it can be injected into the oxide.

- hole injection: This is the same as electron injection; potential barrier 4.8 eV

The occurrence of these modes dependents on the type of MOSFET (n,p) and the voltage between Gate and Source ( $V_G$ ), and they influence the MOSFET characteristics due to their electrostatic effects. [23][24]

There are three different ways to generate an interface trap: First, the electron has the required energy to break the Si-H bond. This is the governing mechanism if the gate-drain voltage is higher than the needed 2 V. Second, an electron can obtain the necessary energy through exchange mechanisms (electron-electron scattering). Third subsequent collisions of lower energy electrons can excitation to bond until it breaks. These two mechanisms are more relevant for  $V_D < 2V$ . The interplay between these two cases gives a dependence on channel length. The HCI is related to the maximum average energy for longer channel devices, and for short channel length, the carrier flux is more important. A consequence of this is a different temperature dependent on the degradation because of the HCI effect. For devices with higher  $V_D$  and longer channels, the degradation decreases with increased temperature, while for devices  $V_D$  and short channels, the degradation becomes more severe. [22]

#### 3.2.2 Negative Bias Temperature Instability (NBTI)

NBTI, first discovered in 1966 [25], is a fundamental degradation mechanism in MOSFET devices. The effect occurs because of a build-up of positive charges in the Si-SiO<sub>2</sub> interface and the Sio<sub>2</sub> dielectric when a negative gate bias stress is applied. This results in a shift of device parameters like the threshold voltage  $V_{th}$  or the saturated source-drain current  $I_{Dsat}$  with time and is enhanced with higher temperatures. [26] [27] Another aspect of NBTI is that some of this shift will recover if the stress is turned off. While the mechanism can be observed in both p- and n-channel devices, it is much more prominent in p-channel MOSFETs [28][26], for this reason NBTI is mainly considered an issue of p-channel MOSFETs.

At present, no consensus for a theory of the underlying physical mechanisms was found. The main focus of this thesis is not NBTI modelling, so the main approach will be introduced shortly below.

#### **Reaction Diffusion Model**

The reaction-diffusion model approaches NBTI as the overlap of two processes. At the interface, the Si-H bond can be broken through an electrochemical reaction with an electric field which results in a dangling bond and a mobile hydrogen atom. The hydrogen atom is then transported into the dielectric through diffusion and the dangling bond can catch a hole which leads to a positively charged interface. If the electric field is turned off the concentration gradient of hydrogen leads to a back transport of the hydrogen atoms through diffusion. At the interface they can recombine with a dangling bound while emitting a hole, which explains the recovery.[27] An illustration of this can be seen in figure 3.3.

Figure 3.3: Schematic of the RD model of NBTI

## 3.3 Reliabilty Modeling

#### 3.3.1 Takeda Reliability Model

In 1983 E. Takeda and N. Suzuki published "An Empirical Model for Device Degradation due to Hot Carrier Injection". While devices scaled down and materials and processes change, this model is still used as an industry standard. The reason for this is the easy set up process, the relative accuracy, and the computational inexpensiveness.

They found the relationship between the degradation of a parameter eg. the threshold voltage ( $V_{th}$ ) can be expressed with a simple power function:

$$\Delta Par = A \cdot t^n \tag{3.3}$$

$\Delta Par$  change design parameter

*A* model constant for scaling

- *t* aging time [s]

- *n* model constant for exponent

And while *n* is nearly independence on  $V_G$  which suggest that n changes according of the hot carrier mechanism, for *A* a strong dependency on  $V_D$  was found:

$$A \propto e^{\frac{-\alpha}{V_D}} \tag{3.4}$$

*VD* Drain-source voltage [V]  $\alpha$  constant [V]

This is the same dependence as the peak substrate current, which can be taken as a measure for the number of electron-hole pairs generated. From it can be deduced that *A* is the number of excess carriers due to impact ionization. This model makes it possible to predict long therm degradation with short therm measurements by fitting the model and extrapolating.

#### 3.3.2 HCI Model

Based on the Takeda model the quality department at ams AG in Prämstätten has implemented their own empirical model:

$$\Delta Par = \Delta_0 \cdot \left(\frac{t}{t_{ref}}\right)^n \tag{3.5}$$

$\Delta Par$  change design parameter

$\Delta_0$  modelling constant for scaling the model[]

*t* stress time [s]

$t_{ref}$  scaling factor for including temperature, geometry and stress voltage [s]

The scaling factor  $t_{ref}$  is a variation of the voltage dependency of the Takeda model, an Arrhenius equation for the temperature dependency, and an experimental relation for the transistor length.

$$t_{ref} = A \cdot e^{\frac{B}{V_D}} \cdot L^C \cdot e^{-\frac{E_a}{k_b T}}$$

(3.6)

- $k_B$  Boltzmann constant  $\left[\frac{eV}{K}\right]$

- A model constant for scaling all dependencies [s]

- *V<sub>D</sub>* DC Drain-source voltage [V]

- *B* model constant for voltage scaling [V]

- *L* transistor length  $[\mu m]$

- *C* model constant for lenght scaling []

- *T* transistor temperature [K]

- *Ea* model constant for temperature scaling [eV]

#### 3.3.3 NBTI model

For NBTI a power model can be used [29]. At ams AG Premstätten, this is combined with an Arrhenius model for the temperature dependence and an exponential model for voltage dependence.

$$\Delta V_{th0} = A \cdot e^{k_V V_G} \cdot e^{-\frac{E_a}{k_b T}} \cdot t^n$$

(3.7)

- $k_B$  Boltzmann constant [ $\frac{eV}{K}$ ]

- A model constant for scaling all dependencies [s]

- $V_G$  DC Gate-source voltage [V]

- $k_V$  model constant for voltage scaling  $\left[\frac{1}{V}\right]$

- *T* transistor temperature [K]

- *Ea* model constant for temperature scaling [eV]

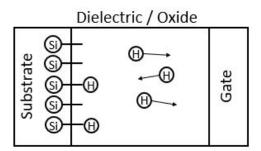

#### 3.3.4 Implementation