**MORITZ LIPP**

# Exploiting Microarchitectural Optimizations Gron Software

**Illustration** Natascha Eibl

## **Exploiting Microarchitectural Optimizations from Software**

by

Moritz Lipp

Ph.D. Thesis

Assessors

Daniel Gruss (Graz University of Technology) Thomas Eisenbarth (University of Lübeck)

August 2021

Institute for Applied Information Processing and Communications Faculty of Computer Science

Graz University of Technology

#### AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present doctoral thesis.

Date, Signature

### Abstract

With abstraction layers, the implementation details of software and hardware components are hidden away to deal with the complexity of modern computer systems. While the Instruction Set Architecture (ISA) serves as an interface between the CPU and the software running on it, the computer microarchitecture is the actual hardware implementation of the ISA. The clearly defined interfaces do not only cover up the complexity but also allow different variants of the microarchitecture to be built. While they all fulfill the contract defined by the ISA, they can differ in other aspects, such as performance, security, energy efficiency, or other physical properties. Microarchitectural attacks exploit these variations occurring on the microarchitectural level of modern CPUs. With side-channel attacks and fault attacks, there are different ways that allow learning from and tampering with the actual implementation. These attacks allow adversaries to extract sensitive information processed on the system, e.g., cryptographic keys or user behavior.

In this thesis, we expand the landscape of software-based microarchitectural attacks and defenses. By exploring the security implications of different optimizations, we identify previously unknown attack vectors, allowing us to circumvent the most fundamental security guarantees of modern processors. We combine traditional physical side-channel analyses with software-based microarchitectural attack techniques to leak sensitive information processed on the CPU. We enlarge our understanding of which settings and circumstances facilitate different existing attacks and give new insights into developing effective and efficient mitigations.

In the first part of this thesis, we discuss the contributions of this thesis and provide background on CPU architecture and memory organization, as well as side-channel attacks and fault attacks. Furthermore, we discuss the state of the art of software-based microarchitectural attacks and defenses. In the second part, a selection of my peer-reviewed publications is provided without modification from their original versions.

## Acknowledgements

First and foremost, I want to thank my advisor, long-time office colleague and friend, Daniel Gruss, who initially sparked my keen interest in microarchitectural attacks. While I have always considered side-channel attacks as black magic and, therefore, have been very reluctant to learn about them, working with Daniel on my master thesis ignited my fascination for this research field. I want to thank you for your continuous support, the freedom you granted me in my research, the endless effort you invest in everything, and your openness for different opinions.

I would especially like to thank Michael Schwarz for his friendship, tireless support, and ambition to work on all those different projects with me. I really enjoyed our time working together, discussing all kinds of ideas while keeping the caffeine level at a healthy high, and discovering parts of the world after conferences. I will miss the late-night debugging sessions, ambitious paper sprints, and presenting our work together.

Looking back over the last years, I want to thank you both, Daniel and Michael, for this incredible journey. I really enjoyed sharing the office with you, all the discussions, and the endless effort we put in as a team. The ups and downs we faced together make this roller coaster ride unforgettable for me.

I want to thank Thomas Eisenbarth for valuable feedback, interesting discussions and taking the time and effort to assess my thesis.

Furthermore, I would really like to thank Stefan Mangard for giving me the opportunity to pursue a Ph.D. in the first place. Thank you for your support and advice over the years.

Over the last couple of years, I had the honor to meet, work and make friends with incredibly kind and talented people worldwide. While the list would be endless, I want to especially thank Jo van Bulck and Daniel Moghimi for insightful discussions and the great teamwork. Likewise, I want to thank Anders Fogh, David Oswald, Berk Sunar, Julian Stecklina, and Thomas Prescher for great discussions and fruitful collaborations. I am further grateful to all my (former) colleagues at the institute for insightful discussions and for creating such an enjoyable working environment, in particular, Martin Schwarzl, Claudio Canella, Lukas Giner, Catherine Easdon, Andreas Kogler, Clémentine Maurice, Robert Schilling, Mario Werner, Peter Pessl, Stefan More and Sebastian Ra-macher.

I want to thank my parents, Peter and Michaela, and my siblings, Ilona, Lukas, and Nikolaus, for all their love and support throughout my entire life. I would like to thank my loving family, Gertraud, Eva, Helga, Gerhard, Heidrun, and Renate, for their support.

A special thanks goes to all my friends; without their support, I could not have completed this thesis. Thank you for meaningful discussions, even late at night, and providing the necessary distractions to the working life. Furthermore, I want to thank Yuki, Rasputin, and my bees for always helping me to find tranquilness even in the most stressful times.

Finally, I want to be grateful to my better half, Natascha, for her neverending supporting love and patience. Thank you for tolerating all *following deadlines* and supporting me throughout all those years. This work could not have been done without you.

## Contents

| Afl                               | fidavit                                                                                                                                                                                                               | iii                               |  |  |  |  |    |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|----|

| Abstract                          |                                                                                                                                                                                                                       |                                   |  |  |  |  |    |

| Acknowledgements vi<br>Contents i |                                                                                                                                                                                                                       |                                   |  |  |  |  |    |

|                                   |                                                                                                                                                                                                                       |                                   |  |  |  |  | I. |

| 1.                                | Introduction and Contribution1.1. Main Contributions                                                                                                                                                                  | <b>3</b><br>7<br>12<br>17         |  |  |  |  |    |

| 2.                                | Background         2.1. Architecture and Microarchitecture                                                                                                                                                            | <b>19</b><br>19<br>34<br>44       |  |  |  |  |    |

| 3.                                | State of the Art3.1. Software-based Microarchitectural Side-Channel Attacks .3.2. Transient-Execution Attacks .3.3. Software-based Microarchitectural Fault Attacks .3.4. Software-based Power Side-Channel Attacks . | <b>49</b><br>49<br>60<br>71<br>74 |  |  |  |  |    |

| 4.                                | Conclusion                                                                                                                                                                                                            | 77                                |  |  |  |  |    |

| Re                                | ferences                                                                                                                                                                                                              | 79                                |  |  |  |  |    |

| 11.                               | Publications                                                                                                                                                                                                          | 105                               |  |  |  |  |    |

| 5.                                | Take A Way                                                                                                                                                                                                            | 107                               |  |  |  |  |    |

| 6.                                | Meltdown                                                                                                                                                                                                              | 149                               |  |  |  |  |    |

| 7. | Nethammer                      | 195 |

|----|--------------------------------|-----|

| 8. | Keystroke Timing Attacks       | 225 |

| 9. | PLATYPUS                       | 251 |

| 10 | KASLR is Dead: Long Live KASLR | 301 |

## Part I.

## **Exploiting Microarchitectural Optimizations from Software**

1

### Introduction and Contribution

In software engineering and computer science, interfaces are defined boundaries that are shared between two or more components enabling them to interact with each other. These components exist in software and hardware, can be a combination of both, or in fact, even peripheral devices or human beings interacting with a device [108]. By specifying how components are supposed to interact with each other, what the expected behavior of the other component is, interfaces grant great flexibility in the implementation of the component as long as the expected behavior is maintained.

By abstracting away components of a system, simple interfaces do not only cover up the complexity of the system but allow different variants of a component to be implemented. For example, in a software project, a new, more performant algorithm is implemented for a defined interface. Conforming to the interface's specification, this allows it to easily replace the old implementation without the need to modify the rest of the system. However, these interfaces do not only exist within software projects but also between applications and the operating system or between developers and the actual hardware. While the implementations all fulfill the same purpose, they can differ in other aspects like the performance.

#### Architecture vs. Microarchitecture

In computing, an architecture typically refers to the instruction set architecture (ISA), also called computer architecture. While the ISA serves as an interface between the CPU and the software running on it, the computer microarchitecture is the actual hardware implementation of the architecture [103]. Thus, the complexity of the implementation is abstracted away by the (less complex) architecture specification. With different microarchitectures implementing the same architectural specification, the same application can perform differently on them, *i.e.*, while the computed results are the same, the runtime performance, energy efficiency, or other physical properties may vary. However, this view is not limited to the central processing unit alone but can be applied to every abstraction layer. This includes other hardware interfaces, e.g., the DRAM, as well [154, 267]. As long as the memory module conforms to the specification, the manufacturer can carry out its implementation in different ways. Furthermore, this view is not limited to hardware alone. For instance, the operating system provides an interface for user space applications to interact with it, *i.e.*, system calls and signals. Thus, different versions of an operating system can be seen as different microarchitectures as well, as the internal workings of the operating system might differ while the functional correctness remains.

#### **Optimizing Behind Closed Doors**

In the past, modern processors have been solely optimized for performance and power consumption. As end customers demand faster and faster processors, manufacturers have to improve and optimize their processors as much as possible. In a benchmark-defined world, every cycle counts and plays a role in the market shares of manufacturers. Moreover, operating systems and user-space applications try to get the most out of the platform they are running on.

One typical way to increase the performance is to optimize for the common case, which is the case that occurs the most frequently. If the common case how an interface is used can be handled more efficiently, forming a fast path of its execution, than uncommon cases (like corner cases or runtime errors), it results in a better performance.

The clear abstraction boundaries defined by interfaces enable us to *do* whatever we want in the underlying implementation as long as the behavior visible to the user of the interface meets the definition of the interface. This grants developers endless possibilities of implementing the interface and, thus, how they can optimize the microarchitecture for different factors.

There are many different ways and locations that allow improving the performance of an application running on a system: With *compiler op-timizations*, the source code is transformed and optimized for different attributes [200]. With *runtime optimizations*, different interpreters, e.g., JavaScript engines [291], or other runtime environments, e.g., Java vir-

tual machines [301], optimize the program during runtime depending on the workload. The *operating system* the application is running on can be tuned to not only give an application more resources but also in the way these resources and the communication from the application is handled. For instance, one of the main tasks of the operating system is to manage the memory of the system. To do that, it needs to create the necessary structures for processes to assign segments of the memory. While several optimization techniques, e.g., copy-on-write, demand paging, swapping or memory deduplication, allow optimizing the memory consumption of applications and increase the performance of the system, they are not visible to the user space application itself [281]. The hardware, *i.e.*, the processor, that executes the software allows for optimizations. Besides the CPUs clock rate, there are many factors that influence the performance of the processor. Different sizes and properties of caches play a role, as well as if the processor has out-of-order or in-order execution [268]. Furthermore, the use of various predictors can increase the performance drastically [103].

Thus, in order to speed up the overall performance of the system, security guarantees of the architecture have often been ignored on a microarchitectural level. As the inner workings of the microarchitecture are hidden and cannot be inspected from the outside, and as long as these assumptions are guaranteed to hold on an architectural level, the systems behave as expected.

In this thesis, we focus on the security implications these types of optimizations can yield.

#### Shining light through the opaque

Clearly, defining interfaces and abstracting away complexity led us to believe that the implementation appears to be an opaque black box and that its inner workings cannot be inspected from the outside. This assumption even allows to ignore security guarantees on the microarchitectural level in order to improve the performance [105, 244, 272]. However, information can not only be transmitted over *legitimate channels* by the specified interfaces, but an implementation can reveal additional information over so-called *incidental channels* [127], e.g., the response time or the energy consumed by the implementation. These channels serve as *side channels* if the victim leaks information over this channel, enabling *side-channel attacks* if the leaked information can be exploited by an adversary. With *side-channel attacks* and *fault attacks*, there are non-invasive and respectively invasive ways allowing to learn from and tamper with the actual implementation of a device to deduce sensitive information [184]. While these attacks typically require physical access to the hardware, we want to focus on similar techniques, however, by mounting attacks against these interfaces from software only.

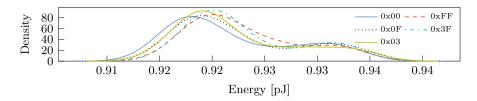

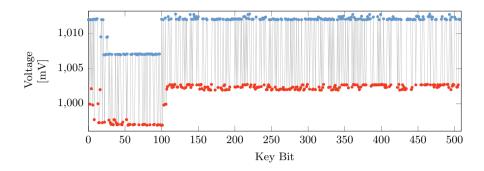

Side-Channel Attacks. With the assumption that the inner workings of the microarchitecture can not be inspected, side-channel attacks are usually not taken into account in the processor's threat model. Side-channel attacks exploit information leakage of a system's implementation in hardware and software. Typically, physical properties like power consumption or magnetic radiation are monitored, and the obtained measurements are used to deduce otherwise inaccessible information. As an example, when executing a cryptographic operation, in some algorithms, the processor has to perform a more power-consuming operation when processing a '1' key-bit than when processing a '0' [254]. By monitoring the power consumption, an attacker can correlate the power trace with the operations performed and, thus, recover the entire key [184]. Here, the attacker observes indirect information about the key, *i.e.*, metadata. More specifically, with knowledge of the power consumption of specific operations, this information can be mapped to the key, but the key cannot be read out directly.

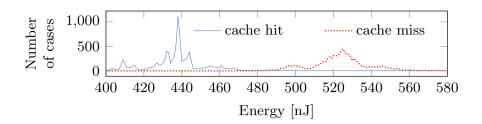

Historically, side-channel attacks required physical access to the target under attack to either connect probes or other peripherals to perform the measurements [184]. However, in recent years, many different softwarebased attacks surfaced, thus, lifting the requirement of physical access [275]. Many microarchitectural side-channel attacks target the cache of the processor. As a transparent optimization technique in the microarchitecture, caches are small but fast memory, allowing the processor to access recently-used data faster. The timing difference introduced by data being cached or not allows an attacker to build software-based side-channel attacks. These so-called cache attacks allow attacking cryptographic algorithms [287, 334, 335], monitor user behavior [94, 174, 220], spy on virtual machines [114, 131], or attack ASLR [79] and kernel ASLR (KASLR) [89, 110, 140, 320].

Fault Attacks. With fault attacks, an adversary intentionally brings devices for a short time into physical conditions which are outside the device's specification. This can be achieved by temporarily using incorrect supply voltages, exposing the device to high or low temperature. radiation, or by dismantling the chip and shooting at it with lasers. If software can bring the device to the border or outside of the specified operational conditions, software-induced hardware faults are possible [153, 282]. With the Rowhammer bug, Kim et al. [153] demonstrated a hardware reliability issue in DRAM where repeatedly accessing a specific memory location flips bits in physically adjacent memory locations. These bit flips have been exploited to obtain arbitrary write primitives [266], root privileges [91, 300] or to read inaccessible memory locations [161]. CLKSCREW [282] exploited software-exposed energy management mechanisms to induce faults during computations on ARM-based devices. By undervolting the CPU [53, 150, 202, 203, 230–232] through a software interface, faulty computations allow to leak sensitive data.

#### 1.1. Main Contributions

The main contributions of this thesis demonstrate the security implications of various microarchitectural optimizations by exploiting them through software-accessible interfaces.

The contributions of this thesis advance the state of the art of microarchitectural attacks and defenses by:

- Discovering Transient-Execution Attacks. With Meltdown (Chapter 6), we exploit the transient execution of instructions before a fault is actually handled in out-of-order CPUs, while with Spectre [156], we exploit the transient execution of instructions caused by mispredictions. This attack does not only bypass the most fundamental security guarantees of modern processors by circumventing memory isolation, but it allows, in contrast to classical side-channel attacks, to leak data processed on the machine *directly*. With Meltdown and Spectre, a whole new research field emerged in the area of microarchitectural attacks, namely transient-execution attacks.

- Identifying previously unknown attack vectors. With Takeaway (Chapter 5), we reverse-engineer the cache way predictor of AMD CPUs and present two new attack techniques leaking metadata to recover sensitive information.

- Exploring if different existing attacks can be mounted remotely. With Nethammer (Chapter 7), we show that Rowhammer faults can be induced on commodity hardware through network requests alone, enabling adversaries to induce bit-flips without any control over the code executed on the target machine. We show that the interrupt-based attack vector described in KeyDrown can also be mounted from JavaScript within a browser, enabling a remote way to observe inter-keystroke timings. By targeting the interrupt handling, we observe inter-keystroke timings of a user's PIN or password in sandboxed JavaScript and infer URLs entered by a user on personal computers and smartphones (Chapter 8).

- Combining traditional physical side-channel analysis with modern software-based microarchitectural attack techniques. With PLATY-PUS (Chapter 9), we exploit the processor's energy consumption available to software to infer data and extract cryptographic keys. While the update interval of the interface is low compared to traditional oscilloscopes used for physical side-channel attacks, we use techniques from microarchitectural attacks to control the execution of SGX enclaves and overcome these limitations to extract cryptographic keys.

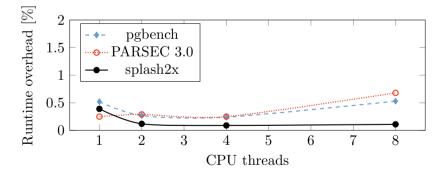

- Giving new insights into efficiently mitigating attacks. Discovering new attack vectors and studying existing ones in more depth allows us to better understand the requirements for efficient mitigations. With KAISER (Chapter 10), we initially proposed a stronger page-table isolation for operating systems to mitigate various side-channel attacks on KASLR. In addition, it turned out that the design of KAISER offered a software-only defense to protect against the Meltdown attack and, thus, has been adopted in every major operating system.

The rest of this section briefly describes the individual contributions of this thesis, while Part II includes the corresponding peer-reviewed publications. However, as only a subset of the contributions conducted during my Ph.D. is included within this thesis, a brief description of other results can be found in Section 1.2.

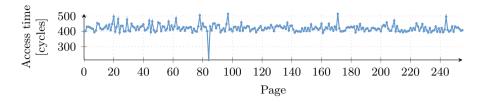

Take a Way: Exploring the Security Implications of AMD's Cache Way Predictors. To optimize the energy consumption and performance of their processors, AMD deploys a way predictor for the L1 data cache to predict in which way of the cache a certain address is stored. The implementation tags each cache line with a linear-address-based microtag that is computed using an undocumented hash function. In this work, we first reverse-engineer this hash function in microarchitectures from 2011 to 2019 and present two new attack techniques using the way predictor as a side channel: Collide+Probe and Load+Reload. Based on these techniques, we demonstrate a covert channel, reduce the entropy of ASLR on the kernel (KASLR) and in the browser, recover cryptographic keys and exfiltrate secret data from the kernel using a Spectre attack.

The paper "Take a Way: Exploring the Security Implications of AMD's Cache Way Predictors" was published at *AsiaCCS* 2020 in collaboration with Vedad Hadžić, Michael Schwarz, Arthur Perais, Clémentine Maurice, and Daniel Gruss.

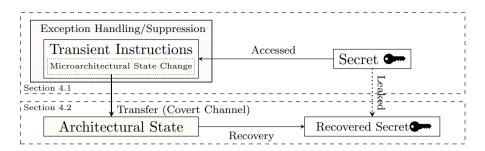

**Meltdown: Reading Kernel Memory from User Space.** Under the assumption that the microarchitectural state is invisible and that microarchitectural state changes cannot be observed, security guarantees could be ignored during transient execution as they have no visible consequences. As microarchitectural side-channel attacks have been limited to leak only metadata about the execution of a program, *i.e.*, executed instructions or data accesses, they are usually not taken into account in the processor's threat model. With Meltdown, however, we exploit that during transient execution, the permission check required by the page tables is deferred on some microarchitectures. Thus, architecturally inaccessible data is forwarded to the adversary in the transient domain. Using a microarchitectural covert channel, the adversary can transmit the data to the architectural domain leaking arbitrary memory.

Together with Spectre [156], Meltdown describes a new class of microarchitectural attacks and paved the way for a variety of transient-execution attacks and their necessary mitigations. With Foreshadow [293], Zombieload [262], RIDL [251], Fallout [46], CrossTalk [236], LazyFP [276], CacheOut [248, 252], and Medusa [197] many other Meltdown-type attacks followed, highlighting the importance and research interest in the new field of transient-execution attacks. We discuss the state of the art and, thus, the immense research efforts that followed our discovery in Section 3.2.

The paper "Meltdown: Reading Kernel Memory from User Space" was published at USENIX Security Symposium 2018 in collaboration with Michael Schwarz, Daniel Gruss, Thomas Prescher, Werner Haas, Anders Fogh, Jann Horn, Stefan Mangard, Paul Kocher, Daniel Genkin, Yuval Yarom, and Mike Hamburg.

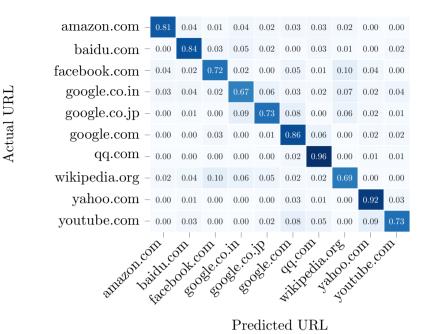

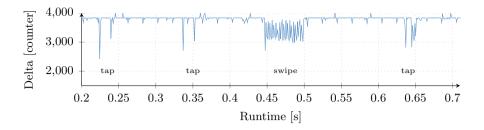

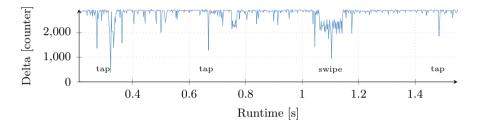

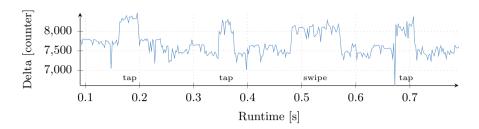

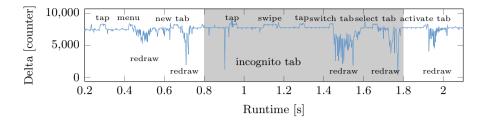

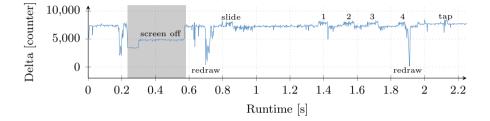

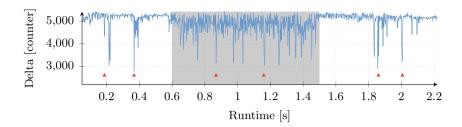

**Practical Keystroke Timing Attacks in Sandboxed JavaScript.** To mount a keystroke timing attack, an attacker so far either requires physical access to the device under attack [199], or local code execution [94, 199, 261]. We investigated whether the interrupt-based attack vector described in our paper "KeyDrown: Eliminating Software-Based Keystroke Timing Side-Channel Attacks" [261] can also be mounted from JavaScript within a browser. We showed that we could not only successfully spy on keystrokes on desktop machines but also on touches and swipes on mobile phones. We showed that an attacker could distinguish between website URLs a user entered in the browser bar and between users time-sharing a machine.

The paper "Practical Keystroke Timing Attacks in Sandboxed JavaScript" was published at *ESORICS* 2017 in collaboration with Daniel Gruss, Michael Schwarz, David Bidner, Clémentine Maurice, and Stefan Mangard.

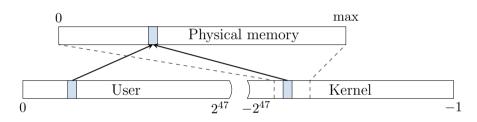

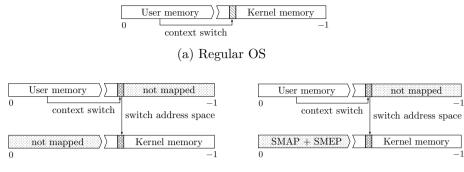

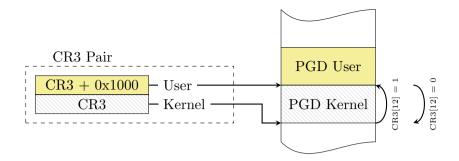

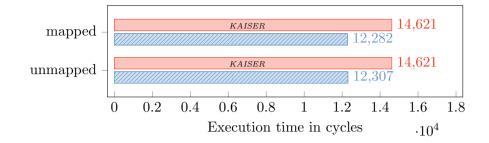

**KASLR is Dead: Long Live KASLR.** As recommended by Intel [118], the kernel should be mapped into the address space for every user application. However, for kernel pages, the userspace-accessible bit in the page tables is not set. Therefore, the address space is separated into virtually two; one for user mode and one for kernel mode.

However, this single mapping enabled various side-channel attacks breaking KASLR [89, 110, 140]. In 2016, we already proposed a change to operating systems to mitigate prefetch side-channel attacks [89] that sets up two mappings, one for the kernel and one for the user space application. We implemented this idea as a proof-of-concept patch for the Linux kernel and evaluated that it successfully impedes the attacks. In the meantime, the stricter isolation provided by KAISER proved itself useful as it also protects against the Meltdown attack [177] and, thus, has been adopted in every major operating system by now.

The paper "KASLR is Dead: Long Live KASLR" was published at *ES-SoS* 2017 in collaboration with Daniel Gruss, Michael Schwarz, Richard Fellner, Clémentine Maurice, and Stefan Mangard.

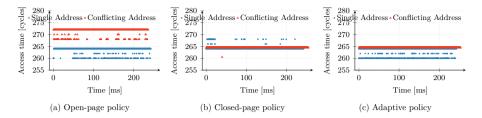

**Nethammer: Inducing Rowhammer Faults through Network Requests.** The Rowhammer attack has always been considered a local attack where the attacker requires access to the machine to execute code or has to trick a victim into accessing a malicious website that induces bit flips via JavaScript [88]. With *one-location hammering* [88], the question arises whether it is possible to trigger bit flips remotely over the network without the execution of attacker-controlled code. By simply crafting minimal packets and sending them as fast as possible to the victim machine, we showed that bit flips can be induced remotely on commodity hardware. We demonstrated a series of remote attacks leading to temporary or persistent errors in the system. Furthermore, we demonstrated that the hardware countermeasure target-row-refresh (TRR) is insufficient to protect against local and remote Rowhammer attacks.

The paper "Nethammer: Inducing Rowhammer Faults through Network Requests" was published at the *SILM Workshop* 2020 in collaboration with Michael Schwarz, Lukas Raab, Lukas Lamster, Misiker Tadesse Aga, Clémentine Maurice, and Daniel Gruss.

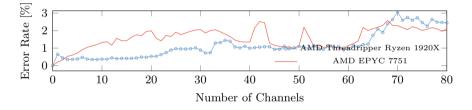

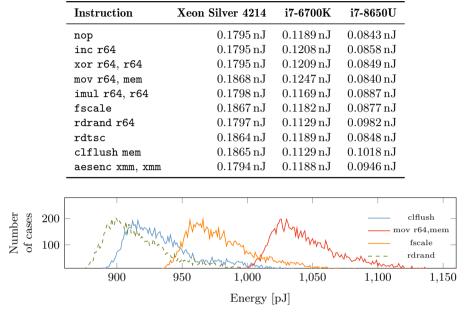

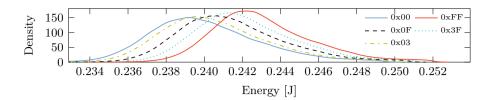

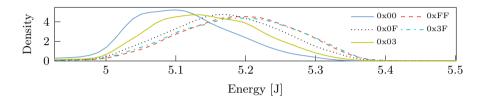

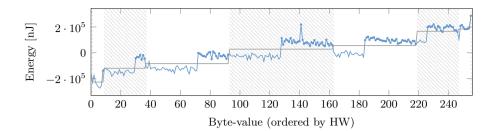

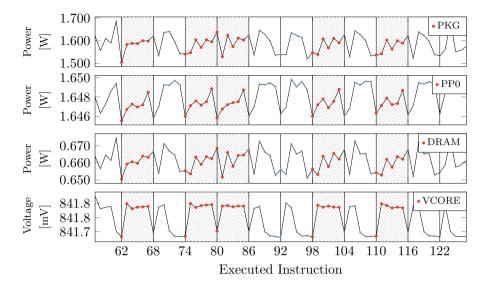

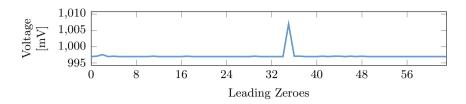

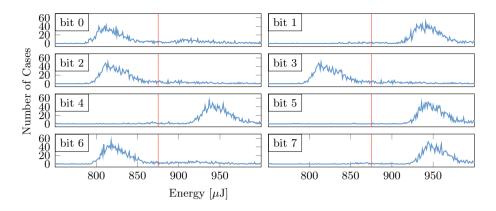

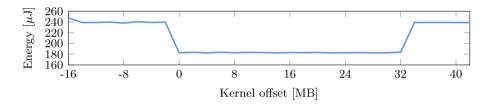

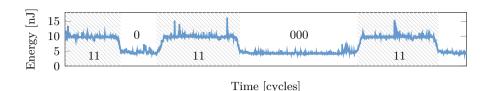

**PLATYPUS:** Software-based Power Side-Channel Attacks on x86. In a classical power side-channel attack setting, an adversary requires physical access to the device to monitor the energy consumption using an oscilloscope. To remain within power constraints, CPU vendors provide an interface to internal power meters allowing to obtain the energy consumption of the core, main memory, or the entire package. On Intel CPUs, the Intel Running Average Power Limit (RAPL) grants software access to these energy measurements. While the update interval of RAPL is rather low in contrast to real oscilloscopes, we show that with sufficient statistical evaluation, we can observe variations in the power consumption. This does not only allow us to distinguish between different instructions but also between different Hamming weights of operands and memory loads.

With PLATYPUS, we exploit the unprivileged access to this interface to leak AES-NI keys from Intel SGX and the Linux kernel, break KASLR and establish a timing-independent covert channel. Furthermore, we leverage tools from microarchitectural attacks to precisely control the execution of an Intel SGX enclave in combination with the RAPL interface to recover RSA keys processed within the enclave.

The paper "PLATYPUS: Software-based Power Side-Channel Attacks on x86" was published at  $I\!E\!E\!E$  S&P 2021 in collaboration with An-

dreas Kogler, David Oswald, Michael Schwarz, Catherine Easdon, Claudio Canella, and Daniel Gruss.

#### 1.2. Other Contributions

In this section, we want to briefly discuss other publications I have contributed to during my Ph.D. that are not included within this thesis.

**KeyDrown.** While in many cases where the implementation of a cryptographic algorithm can be attacked with a side-channel attack, the actual implementation can be protected by modifying the code or switching to other implementation primitives. However, protecting against attacks monitoring user input by observing keystrokes is more difficult. Our idea to mitigate such attacks is to artificially generate fake interrupts that introduce indistinguishable behavior in the observed side channel. User keystrokes are treated as noise on their own and are blended in the noise of the generated artificial keystrokes such that an attacker cannot distinguish between real and fake key strokes. While introducing noise as a countermeasure against side-channel attacks usually increases the number of measurements required to mount the attack successfully, the introduced noise renders keystroke attacks in this scenario infeasible.

The paper "KeyDrown: Eliminating Software-Based Keystroke Timing Side-Channel Attacks" was published at *NDSS* 2018 in collaboration with Michael Schwarz, Daniel Gruss, Samuel Weiser, Clementine Maurice, Raphael Spreitzer, and Stefan Mangard.

JavaScript Zero. With "Practical Keystroke Timing Attacks in Sandboxed JavaScript" [173], we proposed a fine-grained permission system in JavaScript for browsers to mitigate browser-based side-channel attacks. Typically, attacks in web browsers exploit primitives that are either rarely used or used in an unintended way. We checked how many of the primitives that have been used to mount side-channel attacks or exploits in browsers are used on the 10 most popular websites [14]. We figured out that many of them are not used at all. While some sites rely on some features, they do not necessarily rely on the high resolution a feature provides. The idea of this work is to introduce a dynamic approach that removes these features or modifies their behavior in a way that mitigates the attacks but does not influence the usability of the websites.

The paper "JavaScript Zero: Real JavaScript and Zero Side-Channel Attacks" was published at NDSS 2018 in collaboration with Michael Schwarz and Daniel Gruss.

**Another Flip.** The Rowhammer bug [153] is a disturbance error in DRAM where repeatedly accessing a memory location leads to bit flips in physically adjacent locations. This hardware issue can be triggered from software and, thus, has been exploited in various attack settings [69, 91, 179, 299]. In this work, we propose a new hammering technique where we repeatedly only access a single memory location. Furthermore, we showed that using this technique in combination with Intel SGX and by inducing bit flips in the program code; we can circumvent all existing Rowhammer defenses.

The paper "Another Flip in the Wall of Rowhammer Defenses" was published at *IEEE S&P* 2018 in collaboration with Daniel Gruss, Michael Schwarz, Daniel Genkin, Jonas Juffinger, Sioli O'Connell, Wolfgang Schoechl, and Yuval Yarom.

**Use-After-FreeMail.** Another class of attacks is use-after-free attacks, where an application attempts to access a recently freed memory location. We generalized these attacks and demonstrate that they can be applied to different settings, e.g., to email addresses.

The paper "Use-after-freemail: Generalizing the use-after-free problem and applying it to email services" was published at *AsiaCCS* 2018 in collaboration with Daniel Gruss, Michael Schwarz, Matthias Wübbeling, Simon Guggi, Timo Malderle, and Stefan More.

**Double-Fetch Bugs.** Double-fetch bugs are an exploitable race condition where a privileged context accesses an unprivileged external resource multiple times. If the content of the external resource can be modified in between accesses, the other access to a now different value can be exploitable, e.g., time-of-check to time-of-use (TOCTTOU). We showed that cache side channels allow detecting such bugs in code and that they can be used as a trigger signal, outperforming state-of-the-art exploitation techniques. Furthermore, we showed that Intel TSX can be used to mitigate the exploitation of double-fetch bugs automatically. The paper "Automated Detection, Exploitation, and Elimination of Double-Fetch Bugs using Modern CPU Features" was published at AsiaCCS 2018 in collaboration with Michael Schwarz, Daniel Gruss, Clémentine Maurice, Thomas Schuster, Anders Fogh, and Stefan Mangard.

**Spectre.** Simultaneously to our work on Meltdown [177], we identified issues with speculative execution in modern processors caused by the mispredictions of branch predictors in the CPU. We showed that we can influence the predictors to speculatively execute code that would architecturally never be executed and, consequently, leak sensitive data accessed by the victim.

The paper "Spectre Attacks: Exploiting Speculative Execution" was published at *IEEE S&P* 2019 in collaboration with Paul Kocher, Daniel Genkin, Daniel Gruss, Werner Haas, Mike Hamburg, Stefan Mangard, Thomas Prescher, Michael Schwarz, and Yuval Yarom.

**NetSpectre.** With the same question as with Nethammer [179], we wanted to investigate if it is possible to exploit Spectre attacks over the network. We demonstrated how an attacker can leak data remotely over a network-accessible API by measuring the response time of network packets. Furthermore, we presented a novel side channel abusing Intel AVX instructions.

The paper "NetSpectre: Read Arbitrary Memory over Network" was published at *ESORICS* 2019 in collaboration with Michael Schwarz, Martin Schwarzl, Jon Masters, and Daniel Gruss.

A Systematic Evaluation of Transient Execution Attacks and Defenses. After Meltdown [177] and Spectre [156], a new research field of transientexecution attacks opened up. After the disclosure of Foreshadow [293] and Foreshadow-NG [292], we systematically analyzed all the remaining bits in the page tables as well as other exceptions that can be exploited with Meltdown-type attacks as well as predictors exploited with Spectre-type attacks. This uncovered 6 new attacks.

The paper "A Systematic Evaluation of Transient Execution Attacks and Defenses" was published at *USENIX Security Symposium* 2019 in collaboration with Claudio Canella, Jo Van Bulck, Michael Schwarz, Benjamin

von Berg, Philipp Ortner, Frank Piessens, Dmitry Evtyushkin, and Daniel Gruss.

**ConTExT.** In order to fully defend against transient-execution attacks, we investigated if a software-hardware co-design is possible that would protect sensitive data but keep the performance gain introduced by speculative execution. Thus, we proposed ConTExT, which makes the hardware aware of secrets by annotating them in code and passing this information on to the lower levels, and forcing the hardware not to use secrets when speculating.

The paper "ConTExT: A Generic Approach for Mitigating Spectre" was published at *NDSS* 2020 in collaboration with Michael Schwarz, Claudio Canella, Robert Schilling, Florian Kargl, and Daniel Gruss.

**ZombieLoad.** Within our Meltdown research [177], we discovered a variant that allowed leaking values not only from the cache but also from the Line Fill Buffer (LFB). With ZombieLoad, we continued in that direction to leak data from the load buffers. We were able to leak currently processed data of a thread running in parallel or previously processed data on the same core. With those techniques, we can leak loads and stores from load ports, the line fill buffer, and the store buffer. With one particular variant, called TSX Asynchronous Abort (TAA), we demonstrated that these attacks even work on CPUs that already have hardware mitigations against the other variants. We further demonstrate that the initial microcode mitigations by Intel were insufficient, and L1D Eviction Sampling (L1DES) still allows to leak sensitive data.

The paper "ZombieLoad: Cross-Privilege-Boundary Data Sampling" was published at *ACM CCS* 2019 in collaboration with Michael Schwarz, Daniel Moghimi, Jo Van Bulck, Julian Stecklina, Thomas Prescher, and Daniel Gruss.

**Fallout.** Another optimization technique to resolve data hazards is storeto-load forwarding, where the CPU passes data from previous stores onto subsequent loads. With Fallout, we show that we can exploit this behavior and trick the CPU into forwarding previous stores from the victim to the attacker as long as they are in the store buffer. The paper "Fallout: Leaking Data on Meltdown-resistant CPUs" was published at *ACM CCS* 2019 in collaboration with Claudio Canella, Daniel Genkin, Lukas Giner, Daniel Gruss, Marina Minkin, Daniel Moghimi, Frank Piessens, Michael Schwarz, Berk Sunar, Jo Van Bulck, and Yuval Yarom.

**LVI.** With Load Value Injection (LVI), we turn around previous transientexecution attacks directly extracting data [46, 177, 251, 293]. Rather than directly leaking the data from the victim, we inject data into the victim to hijack transient execution leaking sensitive information. We show that LVI is harder to mitigate as it requires expensive software patches to prevent transient execution after every load operation.

The paper "LVI: Hijacking Transient Execution through Microarchitectural Load Value Injection" was published at *IEEE S&P* 2020 in collaboration with Jo Van Bulck, Daniel Moghimi, Michael Schwarz, Marina Minkin, Daniel Genkin, Yuval Yarom, Berk Sunar, Daniel Gruss, and Frank Piessens.

**Medusa.** With Medusa, we investigated whether a fuzzing-based approach allows us to find new Meltdown subvariants. All existing variants of Meltdown have been found with the manual effort by experts in the field and fixed, either using microcode updates or for upcoming CPU microarchitectures directly in silicon. However, certain subvariants like TAA [122] or L1DES [124] demonstrated that not all paths had been covered in hardware and, thus, were applicable to even the latest generation of CPUs. We introduce Transynther, an automatic approach that allows reproducing, analyzing, and classifying existing variants and also generating new variants and regression testing. Based on our findings, we identify a new variant called Medusa that leaks data from write-combining memory operations. Furthermore, Transynther synthesized a variant of Fallout [46] that worked even on the most recent Intel Ice Lake microarchitecture [196].

The paper "Medusa: Microarchitectural Data Leakage via Automated Attack Synthesis" was published at USENIX Security Symposium 2020 in collaboration with Daniel Moghimi, Berk Sunar, and Michael Schwarz.

#### 1.3. Outline

The remainder of this thesis is structured as follows. Chapter 2 provides background on the architecture, microarchitecture, and memory organization of a modern CPU. Furthermore, it introduces side-channel attacks, fault attacks, and microarchitectural attacks. Chapter 3 gives an overview of the state of the art in software-based microarchitectural side-channel attacks, fault attacks, and power side-channel attacks. Chapter 4 concludes this work and gives an outlook on ongoing and future research.

## 2 Background

#### In this chapter, we provide the necessary background for this thesis. In Section 2.1, we explain architecture and microarchitecture and describe trusted-execution environments. In Section 2.2, we explain how memory is organized in modern processors, covering the concepts of virtual memory and caches. We discuss the basic concepts of side-channel attacks and fault attacks in Section 2.3.

#### 2.1. Architecture and Microarchitecture

In this section, we discuss the importance of abstraction to deal with complexity in computing by means of computer architecture and microarchitecture. We briefly introduce the concepts of pipelined processors and superscalar techniques of modern processors.

#### 2.1.1. Instruction-Set Architecture

By using abstraction layers, one needs to take care only of the interface or specification of each layer. Thus, higher levels do not necessarily need to know the details of lower levels. In computer science, abstraction layers play an important role in managing the complexity of modern systems, and, therefore, they do not only exist between hardware and software but basically everywhere.

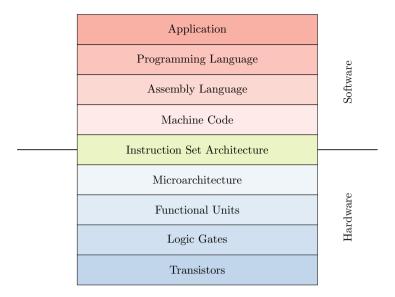

**Levels of Abstraction.** Every abstraction level in a modern computer system, as illustrated in Figure 2.1, is implemented on top of another level and utilizes the well-defined functions of the lower level. While the implementation of each layer is not interested in the upper layers, it hides the unnecessary details of the lower layers. Starting with atoms, this allows us to build complex applications.

Figure 2.1.: Abstraction layers enable building complex processors from the bottom up. The ISA connects the hardware to the software level.

Transistors built from silicon atoms are used for amplification and to build switches. By combining these switches, boolean logic gates (such as or, xor, and or not) can be built. Using multiple gates, functional blocks, such as latches, flip-flops, and registers, are built. On the next level, they can be chained together to build more complex logical functions that perform computations, like arithmetical logical units (ALU). To design an entire processor, multiple complex processing elements are built and connected together to enable complex computations. This includes register files, different buffers, and execution units that together represent the microarchitecture that fetches instructions from memory, decodes and executes them, and stores the results back to memory. The computer architecture (or Instruction Set Architecture (ISA)) is an abstract model of the machine and connects hardware and software. A compiler uses the ISA to translate a high-level programming language to the machine code the processor can process. This allows applications to be executed on the CPU. Typically, an operating system manages how the system is used and enables user space applications to run on top of it that operate on data we provide.

**Instruction-Set Architecture (ISA).** The ISA, or computer architecture, is an abstract model of the computer. It defines not only the instruction a processor can execute as well as their behavior but also registers, data types, and the memory model. With x86, A64, POWER, RISC-V, or SPARC, there are many different instruction sets that are typically classified in their complexity. A complex-instruction-set computer (CISC), like x86, supports many special (and hence, complex) instructions. On the other hand, a reduced-instruction-set computer (RISC), like A64 or POWER, has a smaller set of instructions and, thus, requires more instructions to perform tasks than some of the complex instructions would cover.

Usually, a RISC instruction set uses fixed-length instructions. This means, as an example with the ARM A64 instruction set, that all instructions are 32 bits in length [24]. In contrast, CISC instruction may have instructions of varying lengths. For instance, instructions on x86 can be between 1 and 15 bytes long [123]. Hence, parsing an instruction stream is more complex, as the actual length of the next instruction can only be determined by parsing byte by byte.

With computer architecture, one usually refers to the Instruction-Set Architecture (ISA) of a processor and, thus, the processor's interface as the programmer sees it. From the hardware perspective, the ISA serves as the design specification for the microarchitecture. This enables different microarchitectures (from different companies) for the same ISA, allowing to run applications compiled for one instruction set to run on all of these microarchitectures. However, based on the actual implementation of the microarchitecture, the program's execution can vary in side effects, such as performance or energy consumption.

While we focus on the CPU microarchitecture in Section 2.1.2, the distinguishing view between the architecture and microarchitecture applies to abstraction levels in general. An architecture always describes the interface to the underlying microarchitecture. For example, the operating system provides a clear interface for applications via specified system calls and signals. Different versions of an operating system can be seen as different microarchitectures as well; however, if an application adheres to the interface, it can be executed on different implementations of the operating system. For instance, while the internal workings – including different optimizations – of the operating systems, can change, an application can still be executed correctly if the guarantees of the interfaces are kept.

#### 2.1.2. CPU Microarchitecture

The microarchitecture of a processor is an implementation of an architecture. While the ISA serves as a reference for software developers, it serves as the interface specification for CPU designers that the microarchitecture must meet.

In this section, we briefly discuss some fundamental techniques of modern microarchitectures. We outline pipelined designs, as well as superscalar techniques like out-of-order execution. In addition, we examine performance optimization techniques like hardware-based speculation.

For a more in-depth compendium of these topics, we refer the reader to Computer Architecture: A Quantitative Approach [103] and Modern Processor Design: Fundamentals of Superscalar Processors [268].

#### 2.1.2.1. Pipelining

Pipelining allows increasing the throughput of a system, *i.e.*, the number of tasks a system can perform per time unit. Thus, it plays an important role in the design of modern processors to increase their performance.

With pipelining, the execution of a task is split into multiple stages (subtasks) with buffers between each stage. This allows a new task to start as soon as the previous task has completed the first stage of the pipeline.

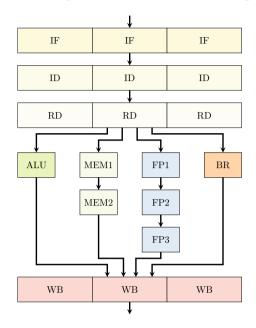

Pipelines are not only used to perform arithmetic operations (*arithmetic pipelines*), e.g., floating-point multiplications, but also to pipeline the instructions the processor should perform in each instruction cycle (*instruction pipelines*). A simple RISC pipeline, as illustrated in Figure 2.2, consists of the following 5 stages:

- 1. Instruction Fetch (IF)

- 2. Instruction Decode (ID)

- 3. Execute (EX)

- 4. Memory Access (MEM)

- 5. Write-back (WB)

In the first stage (IF), the next instruction to be executed is fetched. Then, the instruction is decoded (ID) to determine the work the instruction should perform. In the execute stage (EX), the actual computation is performed. If the operation needs to access memory, this is handled in the memory stage (MEM). Finally, in the write-back stage (WB), the

| IF | ID | EX | MEM | WB  |     |     |     |    |

|----|----|----|-----|-----|-----|-----|-----|----|

|    | IF | ID | EX  | MEM | WB  |     |     |    |

|    |    | IF | ID  | EX  | MEM | WB  |     |    |

|    | ,  |    | IF  | ID  | EX  | MEM | WB  |    |

|    |    |    |     | IF  | ID  | EX  | MEM | WB |

computed results are written to the register file.

Figure 2.2.: A RISC Pipeline consisting of 5 stages Instruction fetch (IF), Instruction decode (ID), Execute (ED), Memory Access (MEM), and Write Back (WB).

In an *n*-stage pipeline, n different instructions can be processed at the same time. If these instructions do not depend on each other, instructions can continue through the pipeline without any stalls. However, when there are dependencies between instructions within the pipeline, they have to be detected and resolved. Conditional branches cause pipeline hazards (problems that occur when the next instruction cannot execute in the following clock) as the outcome of a conditional branch is unknown until the execution stage, but its result is already required in the instruction fetch stage to load the next instruction. A simple solution is to assume that the branch falls through and continue fetching the next instruction speculatively but stalling at the decode stage. If the predictions turn out to be correct and the branch is not taken, only a single cycle is lost. However, if the branch has been taken and the assumption was incorrect, the new target has to be fetched and, thus, two cycles have been lost. While this simple prediction allows gaining performance over stalling completely, there are more sophisticated prediction techniques discussed in Section 2.1.2.3.

Hazards cannot only occur on the instruction flow but also on the data flow. If there are two pipeline stages in the pipeline that can simultaneously access the same variable, different data hazards can occur. For example, one instruction could need the value that is computed by a previous instruction in the pipeline. With this read-after-write (RAW) hazard, the following instruction must be prevented from entering the pipeline. Thus, the pipeline must stall until the preceding operation has finished. However, the performance of resolving pipeline hazards can be improved. Using forwarding paths, the result of the preceding operation could be forwarded to the depending operation, reducing the penalty that would be necessary if the pipeline needed to be stalled completely.

**Precise and non-precise exceptions.** In every pipeline stage, different exceptions can interrupt the execution of several instructions. For instance, a page fault or a memory-protection violation could occur in the instruction fetch stage. In the decoding stage, the decoder could fail to decode the instruction, or the instruction cannot be executed with the current privilege level. In the execution stage, the actual computation could raise an exception, *i.e.*, if a number is divided by 0. Similar to the instruction-fetch stage, page faults or protection violations could occur in the memory access stage.

If an exception occurs, the pipeline must squash all following instructions and should let all preceding instructions complete. If these conditions are met and, thus, the machine state aligns with the sequential execution of the instruction stream, exceptions are called precise. If, however, these conditions are not met, e.g., preceding instructions are not completed if an exception occurs, the exceptions are called non-precise. Typically, modern processors support precise exceptions.

Furthermore, it can happen that multiple exceptions occur simultaneously in more than one pipeline stage. If an exception occurs, the pipeline started to perform operations that should not have been executed and, thus, has to make sure that these have no architectural effect.

To handle exceptions on the architectural level, the operating system must provide entry points for *exception and interrupt handlers* in a so-called interrupt descriptor table (IDT). If an exception is architecturally raised (when the instruction would be committed and, thus, the architectural state be updated), the processor calls the procedure for the exception from the IDT [118].

#### 2.1.2.2. Superscalar Execution

With superscalar execution, pipelines are parallelized so that multiple instructions can be processed in every cycle. They are further diversified by using multiple different functional units in the execution stage and by implementing dynamic pipelines; out-of-order execution allows maximizing the utilization of all execution units. **Parallel and Diversified Pipelines.** A simple approach to increase the performance of a pipelined CPU is to create multiple copies of the same pipeline to run in parallel. However, this does not only increase the complexity but also the required hardware resources significantly.

Figure 2.3.: In the execution stage of diversified pipelines, multiple functional units are implemented [268].

With diversified pipelines, however, not every stage in the pipeline is duplicated. Instead, in the execution stage, diversified execution pipelines using multiple functional units are implemented, e.g., for ALU, memory, branch (BR), or floating-point operations, as illustrated in Figure 2.3. Thus, individual pipelines customized for instruction types can be built, and, thus, the latency for each instruction type can be minimal. For instance, the ALU pipeline finishes with a single cycle and does not have to wait for the completion of all floating-point stages.

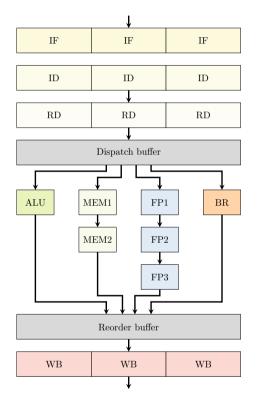

**Dynamic Pipelines.** For instructions to complete in the same order as defined by the instruction stream of the program in a scalar pipeline, the preceding pipeline stages must also be stalled whenever an instruction must be held back in a pipeline buffer. For parallel pipelines, multi-entry buffers are necessary. If the entire multi-entry buffer is, like a single-entry buffer, either stalled or clocked in each cycle, multiple instructions that

in theory require no stalling would also be blocked, inducing unnecessary performance loss. To minimize the latency, subsequent instructions must be able to bypass stalled instructions. Hence, with dynamic pipelines, instructions can be executed out-of-order, *i.e.*, the order instructions are executed deviates from the order defined by the instruction stream. Thus, instructions are executed as soon as their operands are ready. Using complex multi-entry reordering buffers, as shown in Figure 2.4, the instructions are first brought in order to the dispatch buffer, where they are dispatched to the execution units as soon as their operands are ready. With the reorder buffer, while finishing out-of-order, they are reordered back in order to be written back and committed to the architectural state.

Figure 2.4.: Dynamic Pipelines use complex buffers to enable out-of-order execution [268].

In 1967, Tomasulo [286] developed an algorithm that enabled dynamic scheduling of instructions to allow out-of-order execution. It introduces a reservation station, a common data bus, and register tags. A reservation station is a buffer attached to each execution unit that holds the currently

executed instructions of that instruction type. This allows dispatching instructions to execution units as long as there are free reservation stations, even if the execution unit is busy executing a different instruction and even if their operands are not available yet. Thus, instructions can wait in the reservation station until the operands become ready. The common data bus connects the outputs of the execution units to the reservation stations, allowing the instructions waiting to load their required operands from the bus. Similarly, the destination registers of these instructions are also updated. To implement this, register renaming is used. The register contains either a real value or a tag that indicates which execution unit will compute the value. This tag, along with its corresponding result, is broadcast on the common data bus by the producing execution unit, and instructions waiting for their operands are monitoring for their tags on the bus. If an instruction is dispatched, the tag of its output register is stored with the id of the execution unit. Likewise, if a following instruction with the same output register is dispatched, the tag will be updated with the id of the execution unit of the new instruction. Thus, the tag will always contain the id of the execution unit of the last instruction. Thus, only the latest instruction can therefore update the value of the register, resolving write-after-write hazards. However, with Tomasulo's design alone, precise exceptions cannot be handled as the register file is not updated by all instructions. For precise exceptions, modern CPU designs use a *reorder buffer*, as discussed in Section 2.1.2.4.

Out-of-order designs allow to execute operations *speculatively* to the extent that instructions can be processed before the processor is certain that they are actually needed and their results committed to the architectural state. While the out-of-order design enables the execution of instructions that lie completely outside of the program's order, note that Tomasulo's algorithm, in his nature, does not perform anything speculatively. We briefly discuss performance optimizations using speculative execution techniques like branch predictors in Section 2.1.2.3 and further building blocks in Section 2.1.2.4.

#### 2.1.2.3. Speculative Execution

The instruction streams that a processor is executing are usually not only linear but rather contain branches diverting the control flow. To improve the performance, different prediction mechanisms are implemented that try to make an educated guess, which instruction will be executed next. Besides branch prediction and branch-target prediction, explainmed below, other prediction-based techniques increasing the performance have been proposed and deployed on modern systems. Examples include data prefetching [142], way prediction [227], or value speculation [218].

**Branch Prediction and Branch-Target Prediction.** With branch predictors, the processor tries to determine in which direction a branch is taken before its condition has been evaluated. Instructions on the predicted path can be executed in advance, and their results used if the prediction turns out to be correct. However, if the prediction was incorrect, the wrongly computed results are discarded, and execution is continued from the correct path.

There are different ways to predict a conditional branch: Using *static* branch prediction [103], the outcome is predicted based on the instruction itself. For instance, every conditional branch is predicted to be taken. With dynamic branch prediction [54], information is gathered during the run-time enabling an educated guess for the outcome. For instance, one-level branch prediction uses a 1-bit or 2-bit counter to record the last outcome of a branch [268]. Two-level adaptive predictors [337] use the branch history to look up the saturating counter in a pattern-history table (PHT). With local branch predictors, a separate history is kept for each conditional jump instruction, while global predictors share the history of all conditional jumps. With neural branch prediction [143, 284, 304], ideas from machine learning have been integrated into CPU architectures [18, 245].

If the direction of a branch is known (or predicted), the address of the next instruction must be determined. The same applies to unconditional branches that are always taken. For conditional branches, if the branch is not taken, the next instruction is simply the one following the current branch instruction. If a branch is taken, however, the address can either be given (direct branch) or computed at runtime (indirect branch). With branch-target prediction, the processor tries to predict the target address of the branch. The branch target buffer (BTB) is used to store the best-predicted target address for a branch instruction and is consulted to predict the target of the next instruction that should be fetched.

Not only calls into a function can be predicted, but also the return address can be predicted using a return-stack buffer (RSB) [106, 144]. If a function is called, the return address is pushed onto the RSB. When returning from the function, the last entry of the RSB serves as a target prediction from where the processor should continue executing. However, as the return stack has a limited size, an overflow can overwrite the oldest return address, yielding a misprediction. Intel's return-stack buffers are implemented as a circular array, while AMD's RSBs have overflow and underflow checking [322].

Uzelac and Milenkovic [290] presented experiments to reverse-engineer the structures of branch predictors on the Intel Pentium M. Kocher et al. [156] reverse-engineered the BTB from Intel's Haswell microarchitecture. Bhattacharya et al. [34] aimed to reverse-engineer the prediction model of Intel's branch predictors. Wong micro-benchmarked the return-stack buffer on different microarchitectures [322]. We discuss many other works that exploit these predictors to leak sensitive data in Section 3.1.

### 2.1.2.4. Modern Microarchitecture

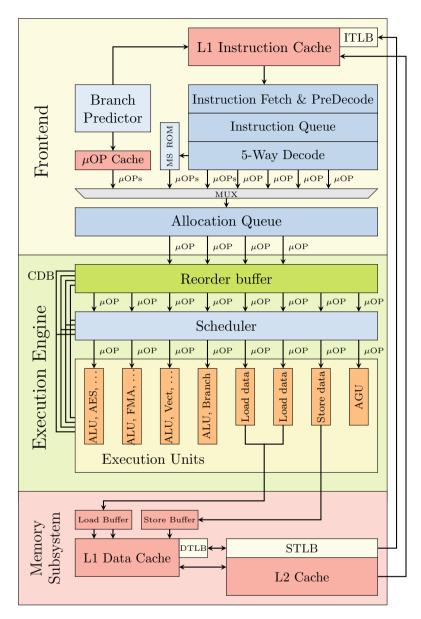

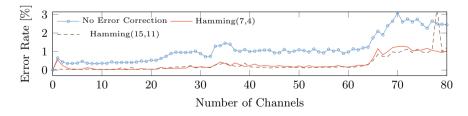

Most superscalar processors consist of a front-end, fetching and dispatching instructions in order, an out-of-order execution engine, and a back end that retires instructions in order, as well as the memory subsystem. In this section, we briefly discuss state-of-the-art microarchitectures based on Intel's Skylake core architecture [255], as illustrated in Figure 2.5.

**Front End.** In the front-end, x86 instructions are fetched from memory, decoded to micro-operations ( $\mu$ OPs) and sent to the execution engine. The *branch predictors* decide which instructions are fetched as macro-ops from the L1 instruction cache (L1I) and sent to the pre-decode buffer. As x86 instructions are complex and of varying length, their boundaries are marked in the pre-decode phase. In the *instruction queue*, the pre-decode distructions are further optimized by macro-op fusion, where two macro-ops are combined into a single complex operation.

Using multiple, simple and complex *decoders* macro-operations are decoded into fixed-length  $\mu$ OPs. While simple decoders can only emit single  $\mu$ OPs, the complex decoder can decode up to four  $\mu$ OPs. For instructions that require more than 4  $\mu$ OPs and cannot be decoded by the complex decoder, the *microcode sequencer* (MS ROM) is queried. While it emits the required  $\mu$ OPs, the decoders are inactive.

Finally, the decoded  $\mu$ OPs are send to the *Allocation Queue* that serves as an interface between the front end and the execution engine. There,

Figure 2.5.: A simplified view of the Intel Skylake microarchitecture [255].

additional optimizations take place: A loop stream detector detects loops and sends the  $\mu$ OPs directly to the execution engine bypassing the rest of the front end [117]. Furthermore, micro-fusion allows fusing multiple  $\mu$ OPs from the same instruction into a single complex instruction [117]. To improve the performance and avoid repeatedly decoding the same instructions, a  $\mu OP$  cache is used to store the  $\mu OPs$  of already decoded instructions. If there is a hit in the  $\mu OP$  cache, the  $\mu OPs$  can be directly emitted to the allocation queue avoiding the pre-decode and decoding stage.

**Execution Core.** The superscalar execution core of the Skylake microarchitecture can process instructions out of order. The instructions arrive in the reorder buffer (ROB) from the allocation queue of the front end. The reorder buffer holds  $\mu$ OPs in different stages of completion. First, if necessary, additional resources for the  $\mu$ OPs are allocated, e.g., entries in the load or store buffer. The source and destination registers are mapped to physical registers, and the register alias table performs register renaming to enable out-of-order execution as described in Section 2.1.2.

The reservation station (or scheduler) queues  $\mu$ OPs until their operands are ready, schedules and dispatches them to the corresponding execution units. The reservation station is connected (via ports) to execution units performing different instructions like ALU operations, floating-point operations, multiplications, memory loads, and stores. For instance, port 0 is capable of integer and vector arithmetic operations as well as AES instructions. Port 2 and 3 are for memory loads, while port 7 is for memory stores. If an execution unit finishes executing one instruction, it broadcasts the result on the common data bus such that depending instructions can fetch the results they require to be executed directly.

The reorder buffer contains all *in-flight* instructions that have been dispatched but not yet retired, including instructions that are waiting for their operands and instructions that have been completed out of order but are not yet committed. The reorder buffer also makes sure that instructions retire in order and, thus, makes it appear that the instructions have been executed as specified by the instruction stream. With Tomasulo's algorithm, the register file is updated once an instruction finishes, and subsequent instructions can hence find the result there. However, with the reorder buffer, the register file is not updated until the instruction retires, thus, allowing the core to execute instructions speculatively.

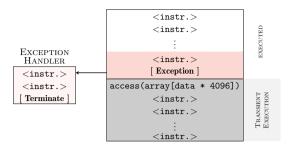

Furthermore, precise exceptions are implemented with the reorder buffer. If an exception occurs, the entry of the instruction that triggered the exception is marked in the reorder buffer. While completing instructions, the reorder buffer checks whether the instruction has been marked and, thus, is not allowed to complete. Therefore, instructions that preceded the faulting instruction can still retire in order. The results of instructions that have been executed out of order that follow the faulting instructions are discarded.

**Memory Subsystem.** The memory subsystem is responsible for load and store instructions as well as the ordering of memory accesses. While we discuss the memory organization, including caches, virtual memory, and DRAM, in more depth in Section 2.2, we give a short overview of the steps performed by the core for memory operations as well as the involved hardware blocks.

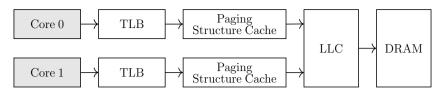

The execution of a memory instruction consists of three steps: the memory address generation, the address translation and the actual memory access. There are different modes how memory addresses can be computed. If an instruction uses an absolute memory address, it uses it directly. Otherwise, using a base and index register as well as a scale and displacement value, based on the form  $base + index \cdot scale + displacement$ , different combinations are possible [118]. Thus, in the first step, the actual memory address is computed based on the provided values for the used mode. If virtual memory (see Section 2.2.2) is used, the computed virtual address has to be translated to a physical address that is used to access the physical memory. Using so-called page tables, the address translation is performed. Furthermore, translations are cached in translation-lookaside buffers (TLB), speeding up subsequent accesses to the same virtual addresses.

After computing and translating the virtual address, the actual memory access can be performed. The data is retrieved from the data cache and stored in the renamed register or the reorder buffer. Note that the architectural register is only updated if the load instruction completes in the reorder buffer [268]. If the data is not cached in the data cache, a cache miss occurs, and the data is requested from the main memory, inducing a longer delay for the instruction to finish. Store instructions are handled differently than load instructions, as store instructions finish as soon as the address has been translated [268]. However, the data is only stored in memory iff the store completes in the reorder buffer. Thus, speculatively but erroneously executed instructions cannot affect the actual memory contents.

Similar to registers, dependencies between two load or store instructions

can exist if they refer to the same memory location. With the execution core we described above, also memory instructions can be performed out of order; thus, special care has to be taken to tackle possible data hazards. Using *load bypassing*, loads can be executed earlier than preceding stores if there is no data dependence between the stores and load. However, if there is a read-after-write (RAW) dependency between a store and a load, using *load forwarding*, the load retrieves its data directly from the store instead of accessing the memory. The memory-order buffer (MOB), consisting of a load buffer and store buffer, is used to handle the memory requests. The load buffer queues loads that could not complete when they were dispatched by the reservation station. It also snoops for stores of other cores against completed loads to maintain memory ordering. The store buffer, on the other hand, queues all stores before they are dispatched to memory in order (when they are no longer speculative). If a load is issued, the store buffer is checked for a potential address match, e.g., using the lower 12 bits, such that data from a previous store operation could be directly forwarded to the load operation [105, 107].

#### 2.1.2.5. Trusted-Execution Environments

Trusted-Execution Environments (TEE) are a secure and isolated environments in CPUs that protect code and data from an otherwise untrusted system. Different CPU manufacturers provide different TEEs: ARM's TrustZone [25] is probably the most widely-used TEE as it is available in most mobile phones. With the Armv9-A architecture, ARM introduced the Confidential Compute Architecture (CCA) [23] that builds upon TrustZone to provide additional execution environments, so-called realms. With Secure Encrypted Virtualization [146] and Secure Nested Paging [17], AMD provides different technologies to isolate virtual machines from the hypervisor. With Secure Execution [112], IBM enables running protected Linux virtual machines in the cloud.

With Software Guard Extension (SGX), Intel provides an x86 instructionset extension protecting applications in so-called enclaves [59]. By encrypting the memory, neither applications nor the operating system can inspect the memory used by an enclave. In addition, this successfully protects against cold-boot attacks [121]. Furthermore, local and remote attestation ensures the integrity of an enclave before it is loaded and executed. To communicate with enclaves, applications can use ecalls to call functions provided by the enclave. Using ocalls, an enclave can request

| CPU Registers $\longrightarrow$ L1 Cache | → L2 Cache → | → Memory → | Disk Storage |

|------------------------------------------|--------------|------------|--------------|

|------------------------------------------|--------------|------------|--------------|

Figure 2.6.: Memory hierarchy shows different locations where data can reside. The closer to the CPU core, the faster the access time, e.g., loading data from one of the cache levels is faster than accessing the data from the main memory.

functionality provided by the operating system, as an enclave itself is restricted in its functionality. For instance, an enclave can not perform any I/O operations or system calls by itself.

We discuss microarchitectural attacks targeting trusted-execution environments in Chapter 3.

# 2.2. Memory Organization

The performance of modern processors does not only depend on the clock frequency but is also influenced by the latency of instructions and, especially, the interaction with other components such as the main memory or hard drives. In this section, we discuss the memory hierarchy, caches, TLBs, and DRAM. We further explain the concept of virtual memory and ASLR.

## 2.2.1. Memory Hierarchy

To serve memory requests as fast as possible, a memory hierarchy as illustrated in Figure 2.6 is deployed. Frequently used data is buffered in multiple layers that differ in capacity and speed. Closer to the core, the memory becomes smaller but faster using different storage technologies:

## Disk Storage

Usually, the slowest but largest memory is the disk storage, e.g., a hard disk, at the end of the hierarchy. While the capacity of hard disks and SSDs reaches multiple terabytes, the latency of a hard disk is around 4 ms [167] while the latency of an SSD can be as low as 250 µs [246].

## Memory

Typically, DRAM is used for the main memory that is discussed

in greater detail in Section 2.2.5. Modern systems deploy multiple gigabytes of memory with latencies around 60 ns [168].

## Caches

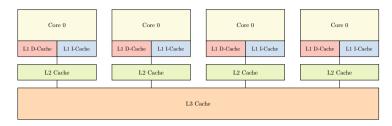

Modern microarchitectures deploy multiple levels of cache, typically using SRAM. The lower the level, the smaller it's capacity and lower its latency. For instance, the L1 cache has a latency of 4 cycles. The L2 needs 12 cycles, and the L3 around 30 cycles to serve the requests [117]. We discuss caches in greater detail in Section 2.2.3.

### **CPU** Registers

Register files hold the general-purpose registers and are built using multi-ported SRAM. Typically, moving a register to another register has a latency of 1 cycle [2]. However, using move elimination [182], the register renaming performs the move and, thus, no latency is induced.

Usually, programs tend to reuse the same memory locations over time repeatedly as well as memory locations that are close to each other, forming two aspects of locality [272]: With *temporal locality*, if one memory location is accessed at a particular time, then it is likely that it will be referenced again soon. With *spatial locality*, if one memory location is accessed at a particular time, then it is likely that nearby locations will be used soon as well. These two principles play an important role in the design of caches to hold frequently used data close to the core.

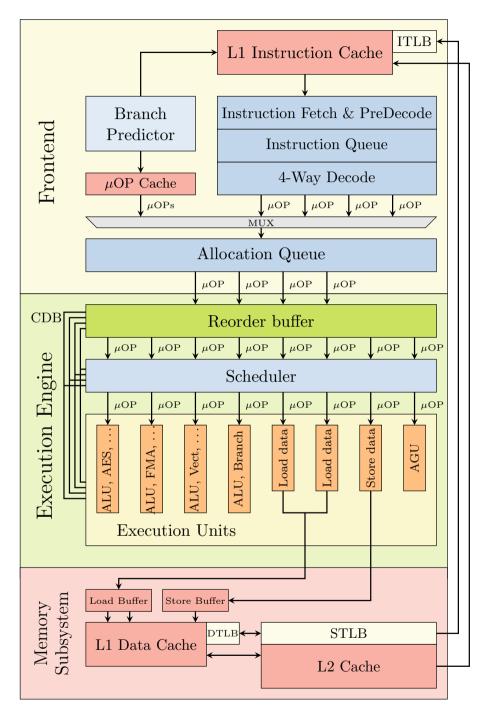

## 2.2.2. Virtual Memory

For memory isolation, processors support *virtual memory* as an abstraction layer for the physical memory of the system. Instead of assigning the physical address space to each process, each process has its own *virtual address space* organized in *pages*. The physical memory is divided into fixed-size continuous blocks, so-called *page frames*. Using multi-level page-translation tables, the operating system maps virtual pages to page frames. When accessing a virtual address of a process, the CPU resolves the mapping to operate on the actual physical address. The root of a translation table for a process is stored in a dedicated register, e.g., the CR3 register on x86 architectures. When switching processes, the operating system switches to the address space of the next process by updating this register.

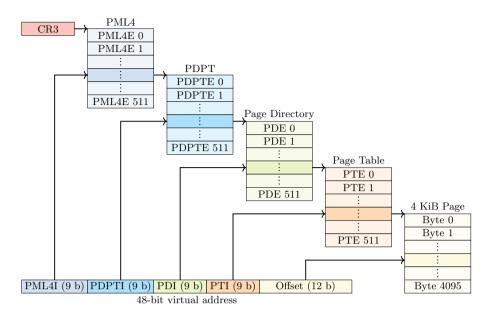

On modern processors, these translation tables typically have 4 levels,

as illustrated in Figure 2.7. However, with the recent Ice Lake microarchitecture, Intel supports another level and, thus, 5-level paging. Every paging structure has a size of 4 kB and consists of 512 entries of each 8 B. Therefore, with 4 levels, 48 bit of the virtual address are used to index the different page table levels (with 5 levels, 57 bits are used).

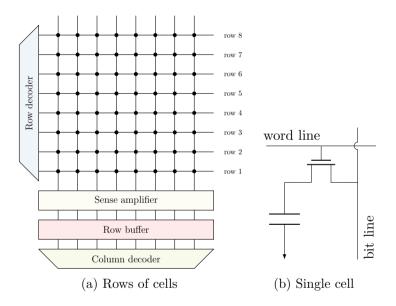

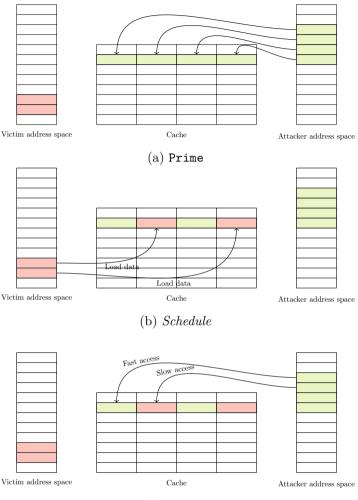

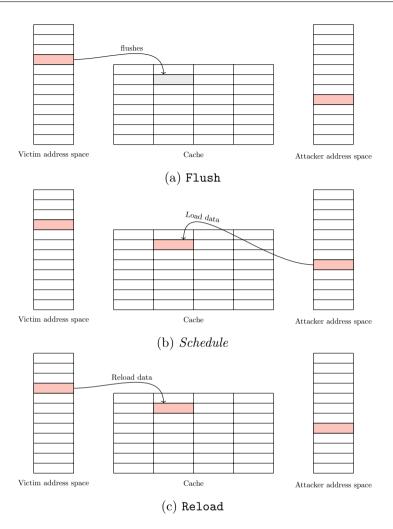

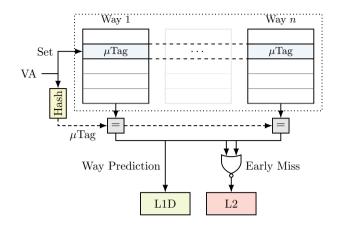

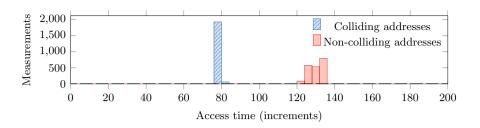

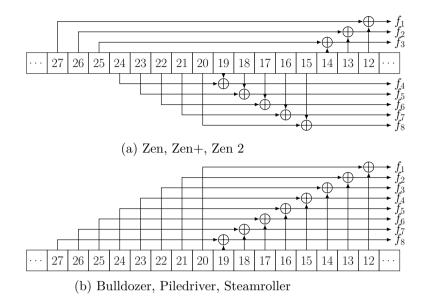

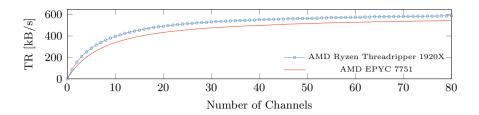

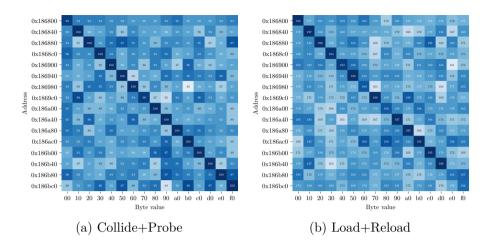

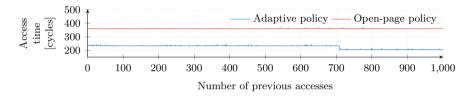

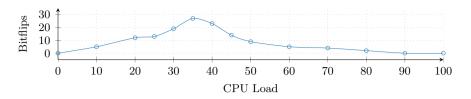

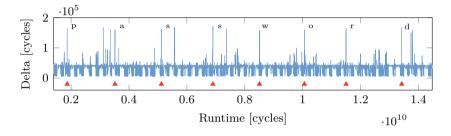

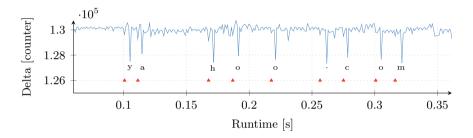

The CR3 register points to the top-most page map level 4 (PML4). Bits 39 to 47 of the virtual address are used to select one of the 512 entries of the PML4, pointing to the page directory pointer table (PDPT). Bits 30 to 38 of the address determine which of the PDPT entries is selected. A PDPT entry either defines a 1 GB region of physical memory (a 1 GB page) or points to a page directory (PD). Bits 21 to 29 of the address define the PD index. Similarly, a PD entry either maps to a 2 MB region of physical memory (a 2 MB or huge page) or maps again to a so-called page table (PT). Bits 12 to 20 select the page table entry that then maps to a 4 kB page of physical memory. With 5-level paging, an additional table, page map level 5 (PML5), is used.