Ko Odreitz, BSc

# Power MOSFET Modeling for EMC Simulation

### **MASTER'S THESIS**

to achieve the university degree of Diplom-Ingenieur

Master's degree programme: Elektrotechnik

submitted to

Graz University of Technology

#### Supervisor

Univ.-Prof. Dipl.-Ing. Dr.techn. Bernd Deutschmann Institute of Electronics

#### Mentor

Dipl.-Ing. Michael Fuchs, BSc

Graz, May 2021

#### AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present master's thesis.

Date, Signature

# ABSTRACT

This master thesis presents a universal behavioral SPICE model for power field-effect transistors. The proposed method allows to create simulation models very quickly by only using parameters which can be found in datasheets. In case no datasheet is available, measurement methods are presented in order to capture all required characteristics. Besides output and transfer characteristics, the body diode, the temperature behavior, the voltage-dependent stray capacitances and the bonding wires are taken into consideration as well. The suggested model is applied for modeling a superjunction and a silicon carbide MOSFET. For validation, the switching behavior of the generated models is compared to measurements, taking parasitic elements of the measurement setup into account. The manufacturer's SPICE models are included in the comparisons as well. The proposed model shows a good agreement and convinces especially with its simple structure, the flawless convergence behavior and short simulation times while maintaining complete control over the simulation model.

Keywords: SPICE model, behavioral model, superjunction, silicon carbide, power MOSFET

In dieser Masterarbeit wird ein universelles SPICE Modell von Leistungsfeldeffekttransistoren präsentiert, ohne dass Kenntnisse des internen Aufbaus oder der verwendeten Materialien von Nöten sind. Die vorgeschlagene Methode ermöglicht das Erstellen von individuellen Simulationsmodellen in kürzester Zeit, lediglich anhand von Parametern, die in üblichen Datenblättern zu finden sind. Messmethoden werden präsentiert, um die Modellierung auch gänzlich ohne Datenblatt zu ermöglichen. Neben der Ausgangs- und der Steuerkennlinie werden im Modell auch die Inversdiode, das Temperaturverhalten, die spannungsabhängigen Streukapazitäten und die Bonddrähte abgebildet. Anhand der empfohlenen Methode werden Modelle zu einem Superjunction- und einem Siliciumcarbid-MOSFET erstellt. Zur Validierung wird das Schaltverhalten der generierten Modelle mit Messungen verglichen, wobei parasitäre Elemente des Messaufbaus mitberücksichtigt werden. Die SPICE Modelle des Herstellers werden bei den Vergleichen miteinbezogen. Das vorgeschlagene Modell zeigt dabei eine gute Übereinstimmung und überzeugt vor allem mit dem simplen Aufbau, dem einwandfreien Konvergenzverhalten und kurzen Simulationszeiten bei gleichzeitiger vollständiger Kontrolle über das Simulationsmodell.

Schlagwörter: SPICE Modell, Verhaltensmodell, Superjunction, Siliciumcarbid, Leistungs-MOSFET

# CONTENTS

| 1 Introduction                                                   | 1  |

|------------------------------------------------------------------|----|

| 1.1 Motivation                                                   | 1  |

| 1.2 Power MOSFET technology                                      | 2  |

| 1.3 MOSFET models                                                |    |

| 1.3.1 SPICE software                                             |    |

| 1.3.2 Level 1 MOSFET model                                       | 5  |

| 1.3.3 Behavioral MOSFET model                                    |    |

| 1.3.4 Survey of existing approaches                              | 6  |

| 1.4 Objective of this thesis                                     | 7  |

| 2 Methods                                                        | 9  |

| 2.1 Universal test circuit                                       |    |

| 2.2 DC characteristics                                           |    |

| 2.3 AC characteristics                                           | 14 |

| 2.4 Simulation test benches                                      |    |

| 3 Model Creation                                                 | 21 |

| 3.1 DC characteristics cont'd                                    | 22 |

| 3.2 AC characteristics cont'd                                    | 27 |

| 4 Model Verification                                             | 31 |

| 4.1 Characterization of passive components                       |    |

| 4.2 Gate-charge simulations                                      |    |

| 4.3 Transient simulations                                        |    |

| 4.3.1 Superjunction MOSFET                                       | 35 |

| 4.3.2 Silicon carbide MOSFET                                     |    |

| 4.3.3 Possible error in the measuring system                     | 39 |

| 4.3.4 Influence of the gate-source voltage on the Miller plateau |    |

| 5 Discussion                                                     | 43 |

| 5.1 Outlook and challenges                                       |    |

| 5.2 Conclusion                                                   | 45 |

| 6 Bibliography                                                   | 47 |

| 7 Appendix                                                       | 51 |

| 7.1 Transient simulations cont'd                                 |    |

| 7.1.1 Superjunction MOSFET                                       | 52 |

| 7.1.2 Silicon carbide MOSFET                                     |    |

| 7.2 Model parameters                                             | 56 |

| 7.2.1 Superjunction IPL65R070C7 datasheet model                  | 56 |

| 7.2.2 Superjunction IPL65R070C7 measurement model                | 57 |

| 7.2.3 Silicon carbide IMZ120R060M1H datasheet model              | -  |

| 7.2.4 Silicon carbide IMZ120R060M1H measurement model            |    |

# LIST OF FIGURES

| Figure 1: Two equivalent versions of the n-channel power MOSFET circuit symbol2                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: n-channel power MOSFET structure. (a) Planar gate. (b) Trench gate                                                                                                                                                                                                                                                          |

| Figure 3: n-channel superjunction MOSFET structure. (a) Planar gate. (b) Trench gate according to Udrea et al. [11]                                                                                                                                                                                                                   |

| Figure 4: Simple behavioral model of a power MOSFET 6                                                                                                                                                                                                                                                                                 |

| Figure 5: Exemplary gate-charge curve when switching on a MOSFET6                                                                                                                                                                                                                                                                     |

| Figure 6: Proposed power MOSFET model9                                                                                                                                                                                                                                                                                                |

| Figure 7: Schematic of the proposed test circuit10                                                                                                                                                                                                                                                                                    |

| Figure 8: Exemplary layout for the proposed test circuit on both planes. Zoom level: 150%. Dark red arrows indicate the current path of the main current side. (a) Top plane. Additional light blue arrows highlight the current path of the driving signal. (b) Bottom plane containing the six current sensing resistors            |

| Figure 9: Typical DC behavior of a MOSFET. Red markings show the points to extract for the modeling process. (a) Transfer characteristics when a MOSFET is in saturation mode. (b) Output characteristics                                                                                                                             |

| Figure 10: Typical body diode behavior of a MOSFET. Red markings show the points to extract for the modeling process                                                                                                                                                                                                                  |

| Figure 11: Equivalent circuit of a power MOSFET 15                                                                                                                                                                                                                                                                                    |

| Figure 12: Typical voltage-dependent behavior of the parasitic capacitors of a power MOSFET. A superjunction MOSFET typically shows more complex curves as explained by Castro et al. [12]                                                                                                                                            |

| Figure 13: Setup to capture the AC characteristics of a MOSFET                                                                                                                                                                                                                                                                        |

| Figure 14: Simplified two-port network of the setup shown in Figure 13 considering ideal filter components                                                                                                                                                                                                                            |

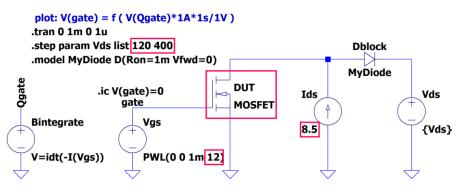

| Figure 15: Proposed LTspice schematic to simulate the gate-charge plot. The red markings need to be adapted according to the gate-charge plot given in the datasheet                                                                                                                                                                  |

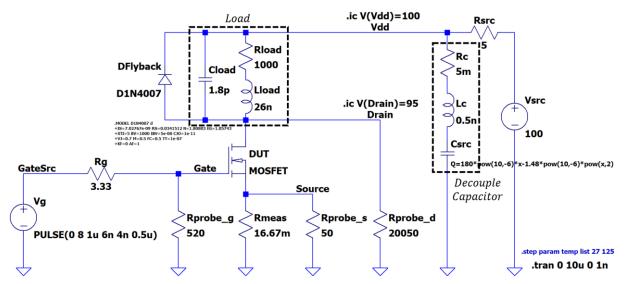

| Figure 16: Proposed LTspice test bench to allow comparison between simulated and measured values.<br>Exemplary lumped-element models for the load and the decouple capacitor are shown                                                                                                                                                |

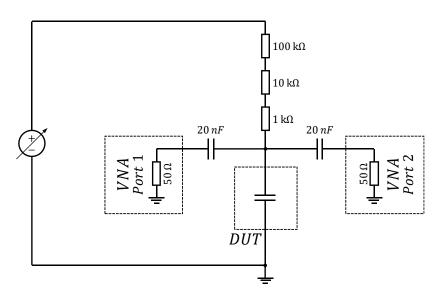

| Figure 17: Setup to perform a 2-port shunt measurement with a variable bias voltage 20                                                                                                                                                                                                                                                |

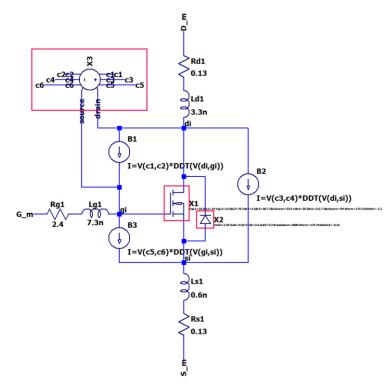

| Figure 18: Proposed power MOSFET model in LTspice. Red rectangles indicate symbols which contain voltage-controlled subcircuits. The model for the IMZ120R060M1H SiC FET created via measurements is shown as an example. Note that the capacitances are determined using the voltage drop U <sub>DG</sub> instead of U <sub>DS</sub> |

| Figure 19: Arbitrary behavioral current source in LTspice in order to output the proposed formula for the DC current                                                                                                                                                                                                                  |

| Figure 20: Characteristics of the simulated SJ MOSFET model based on the datasheet. (a) Transfer characteristics. (b) Output characteristics                                                                                                                                                                                          |

| Figure 21: Transfer characteristics of the SJ MOSFET. (a) Measured at five different temperatures with the proposed test circuit. Average of 3 samples. (b) Plot taken from the datasheet at U <sub>DS</sub> =                                                                                                                        |

| 20 V [33] with red markings located at exemplary positions to extract the required information.<br>Note that the drain-source voltage and the maximum temperature differs between the plots23                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 22: Output characteristics of the SJ MOSFET. (a) Measured at five different temperatures with the proposed test circuit. Average of 3 samples. (b) Plot taken from the datasheet at 25°C [33] with red markings located at exemplary positions to extract the required information23                      |

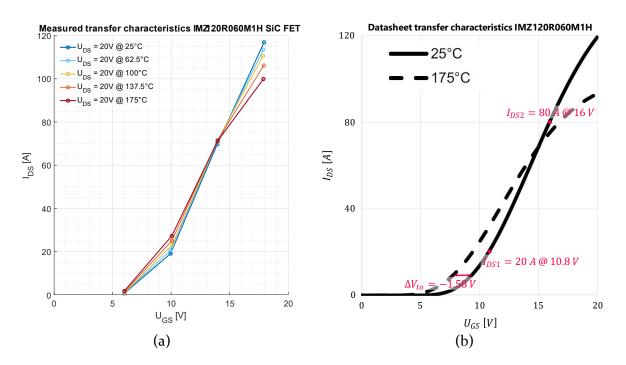

| Figure 23: Transfer characteristics of the SiC MOSFET. (a) Measured at five different temperatures with the proposed test circuit. (b) Plot taken from the datasheet at $U_{DS} = 20 \text{ V}$ [34] with red markings located at exemplary positions to extract the required information                        |

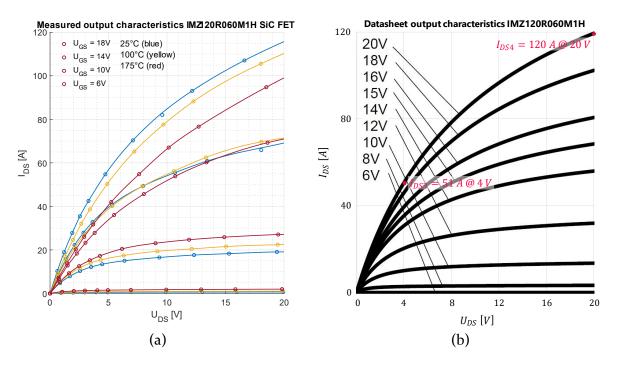

| Figure 24: Output characteristics of the SiC MOSFET. (a) Measured at three different temperatures with the proposed test circuit. (b) Plot taken from the datasheet at 25°C [34] with red markings located at exemplary positions to extract the required information                                            |

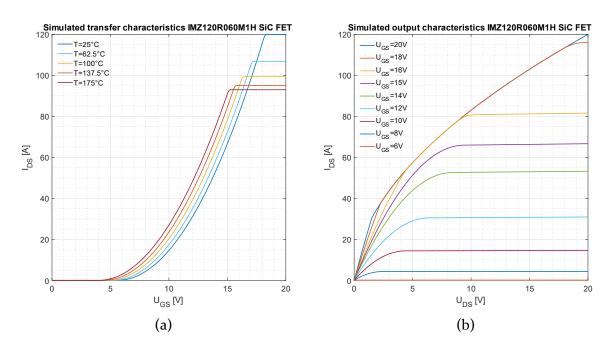

| Figure 25: Characteristics of the simulated SiC MOSFET model based on the datasheet. (a) Transfer characteristics. (b) Output characteristics                                                                                                                                                                    |

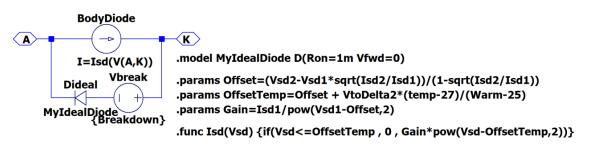

| Figure 26: Arbitrary behavioral current source in LTspice as a representation for the body diode. The biased diode defines the breakdown voltage25                                                                                                                                                               |

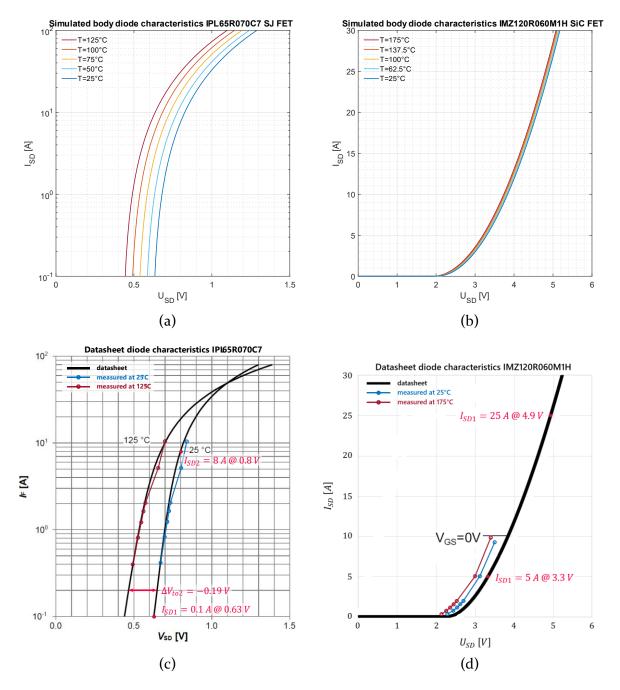

| Figure 27: Characteristics of the body diode. The top graphs show the simulated models based on the datasheet. The bottom graphs show the measurement results overlayed on the datasheets [33], [34] with red markings located at exemplary positions to extract the required information. (a, c) SJ. (b, d) SiC |

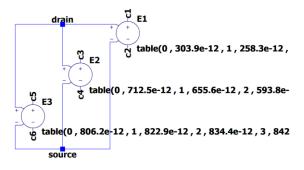

| Figure 28: Voltage-dependent voltage sources in LTspice to output the capacitance values stored within their tables. Only a snippet of the tables is shown. Note that although the net is named "source", it is linked to the gate connection in Figure 18                                                       |

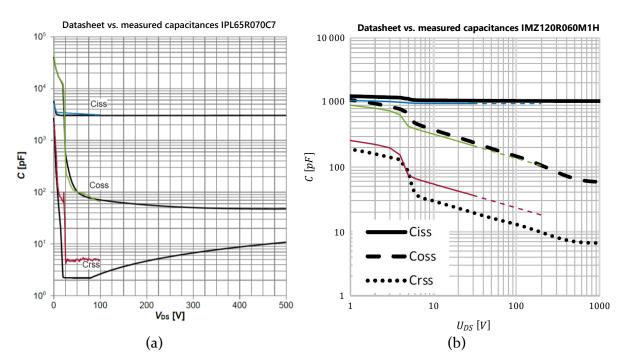

| Figure 29: AC characteristics. The measurement results are overlayed on the datasheets. (a) SJ [33]. (b) SiC [34]. The dashed lines show an extrapolation of the measured values                                                                                                                                 |

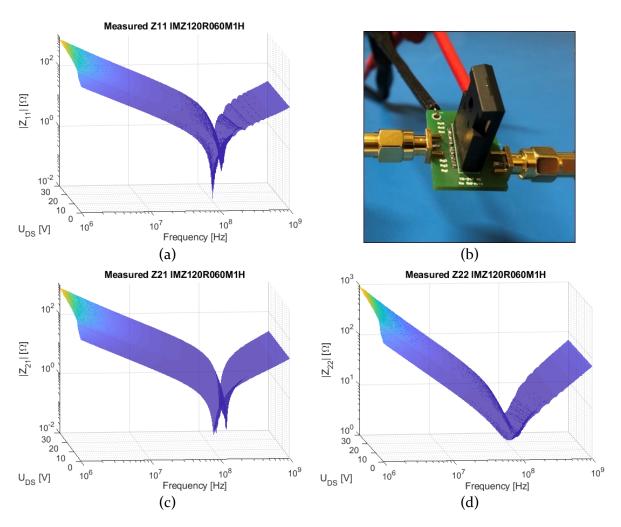

| Figure 30: Measurement of the SiC FET AC characteristics. (a) Z11. (b) IMZ120R060M1H soldered on the test PCB presented in Figure 13 and connected to the VNA and power supply. (c) Z21. (d) Z22 28                                                                                                              |

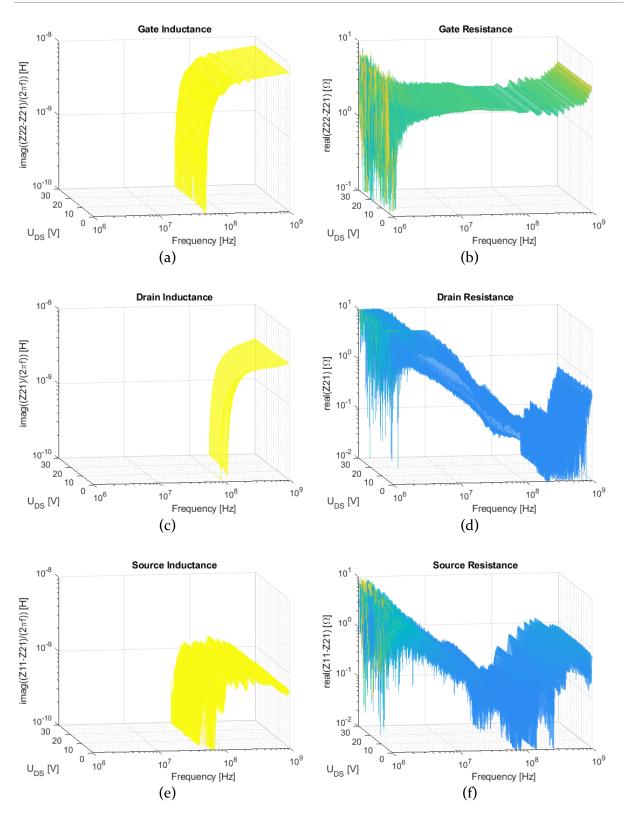

| Figure 31: Calculation of the SiC FET characteristics of the bonding wires. (a) Gate inductance. (b)<br>Gate resistance. (c) Drain inductance. (d) Drain resistance. (e) Source inductance. (f) Source<br>resistance                                                                                             |

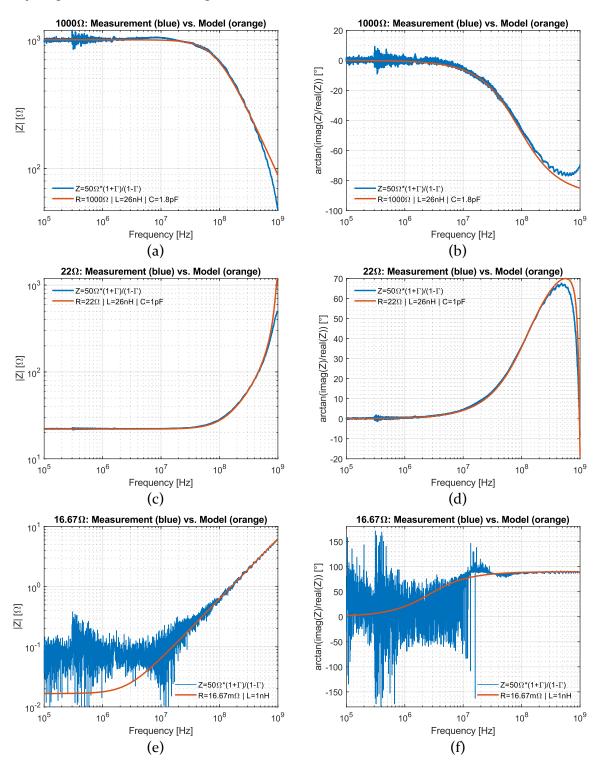

| Figure 32: 1-port characterizations; left: impedance curves, right: phase plots. (a, b) 1000 $\Omega$ load. (c, d) 22 $\Omega$ load. (e, f) 16.67 m $\Omega$ current sensing resistor                                                                                                                            |

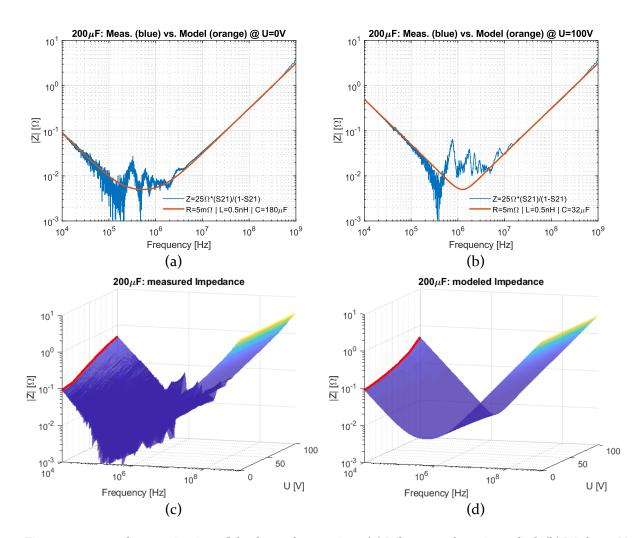

| Figure 33: 2-port characterization of the decouple capacitor. (a) When no voltage is applied. (b) With 100 V applied. (c) Measured impedance; the voltage dependency at 10 kHz is of interest. (d) Modeled impedance                                                                                             |

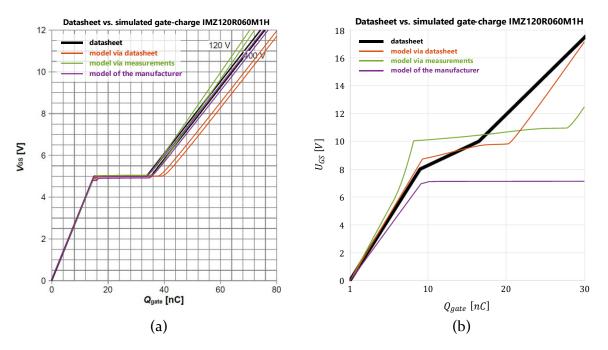

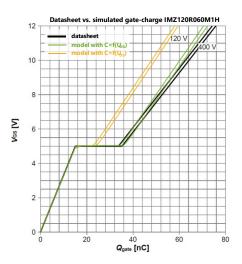

| Figure 34: Simulated gate-charge plot compared with the datasheet. Green: model via measurements.<br>Orange: model via datasheet. Purple: model from the manufacturer. (a) SJ [33]. (b) SiC [34]34                                                                                                               |

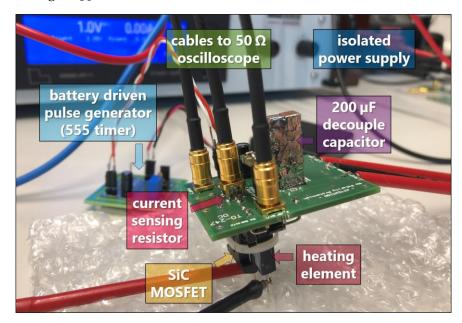

| Figure 35: Photo of the universal test setup to capture the switching behavior of the SiC MOSFET                                                                                                                                                                                                                 |

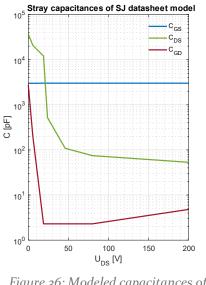

| Figure 36: Modeled capacitances of the SJ datasheet model                                                                                                                                                                                                                                                        |

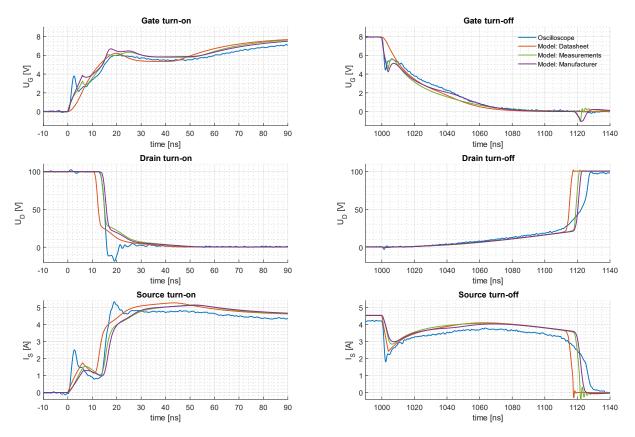

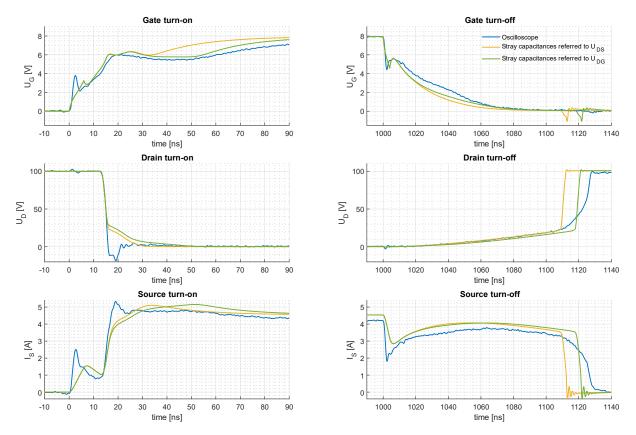

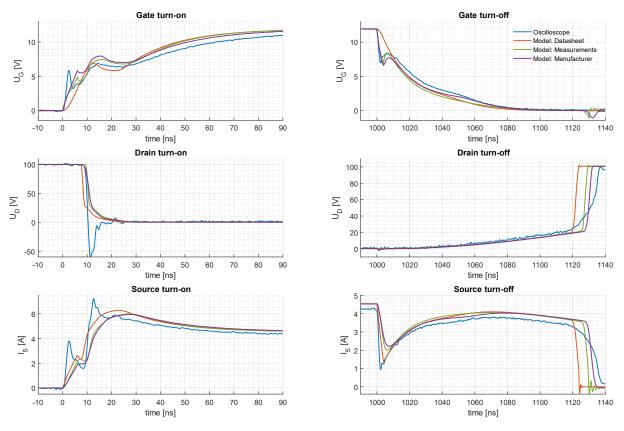

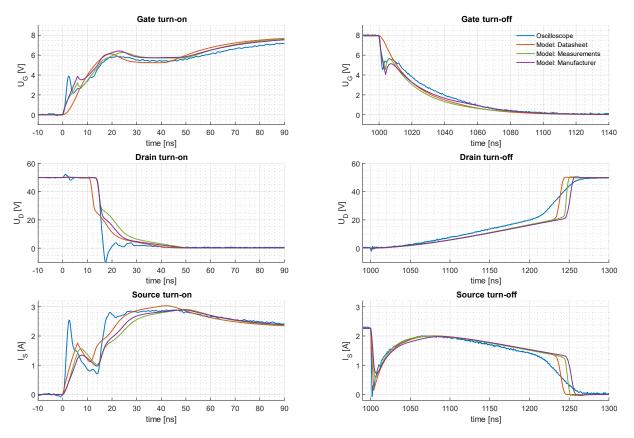

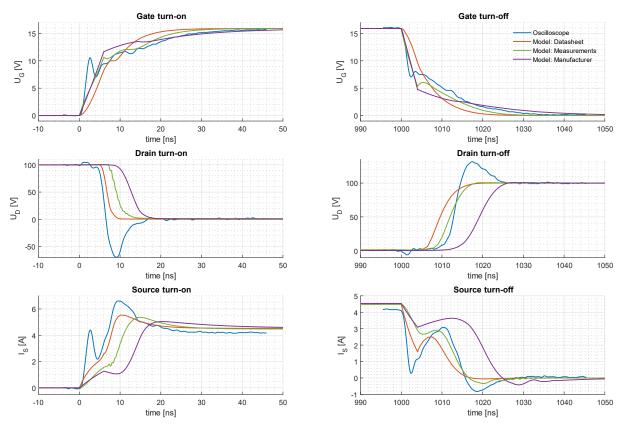

| Figure 37: SJ FET transient simulations; $U_{main} = 100 \text{ V}$ , $U_{gate} = 8 \text{ V}$ , $R_{gate} = 3.3 \Omega$ , $R_{load} = 22 \Omega$                                                                                                                                                                |

| Figure 38: SJ FET transient simulations; $U_{main} = 100 \text{ V}$ , $U_{gate} = 8 \text{ V}$ , $R_{gate} = 3.3 \Omega$ , $R_{load} = 1000 \Omega$                                                                                                                                                              |

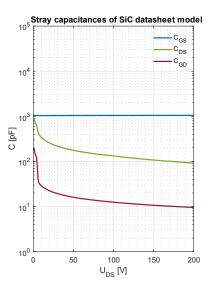

| Figure 39: Modeled capacitances of the SiC datasheet model                                                                                                                                                                                                                                                       |

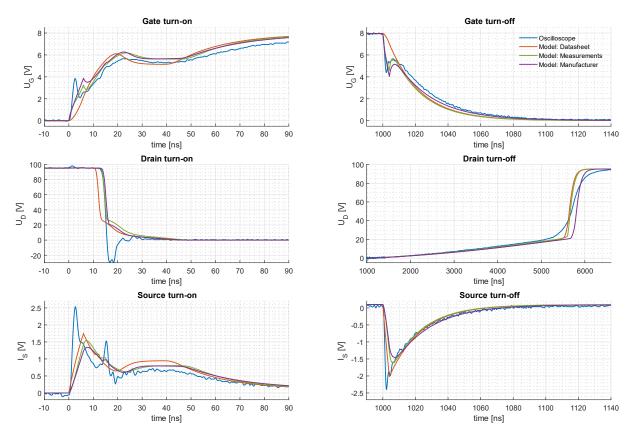

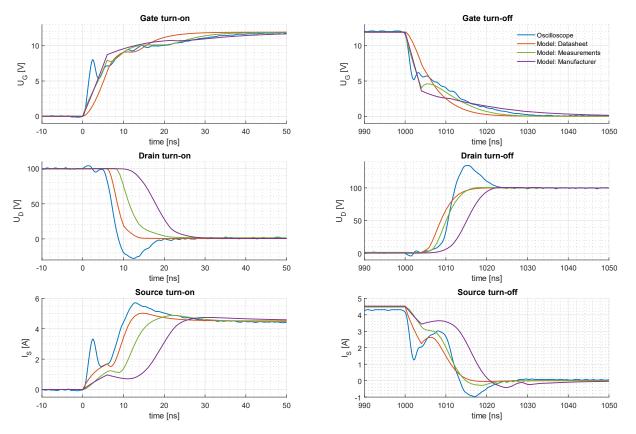

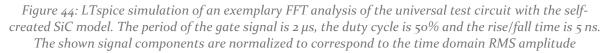

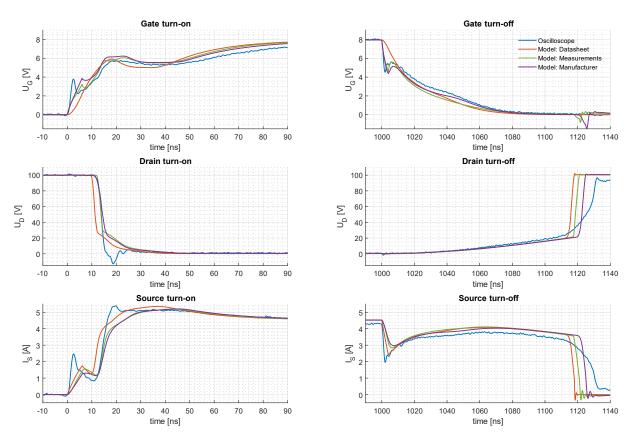

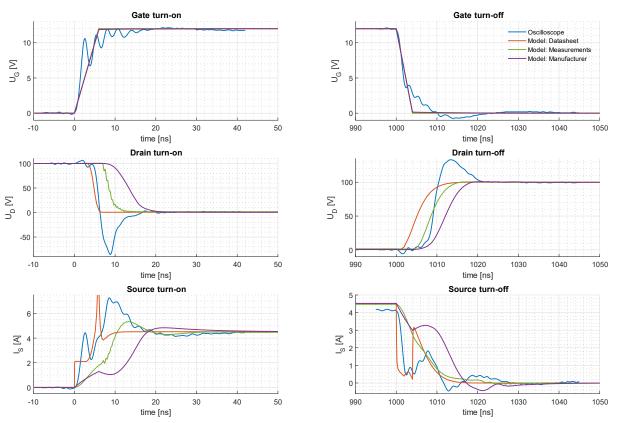

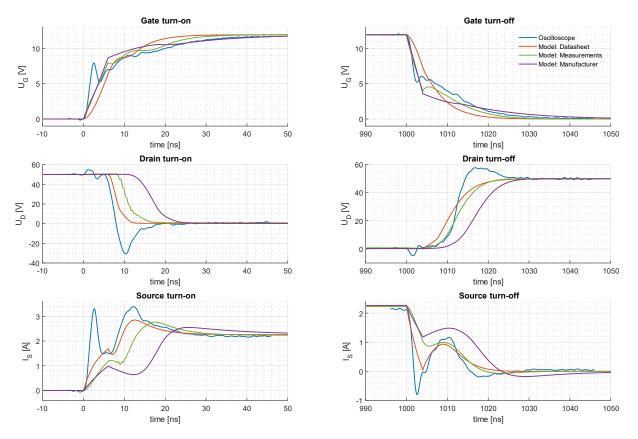

| Figure 40: SiC FET transient simulations; $U_{main} = 100 \text{ V}$ , $U_{gate} = 12 \text{ V}$ , $R_{gate} = 3.3 \Omega$ , $R_{load} = 22 \Omega$                                                                                                                                                              |

| Figure 41: SiC FET transient simulations; $U_{main} = 100 \text{ V}$ , $U_{gate} = 12 \text{ V}$ , $R_{gate} = 3.3 \Omega$ , $R_{load} = 1000 \Omega$                                                                                                                                                            |

| Figure 42: Simulated SJ gate-charge plot with different stray capacitances compared. Black: datasheet [33]. Green: depending on U <sub>DG</sub> . Yellow: depending on U <sub>DS</sub>                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

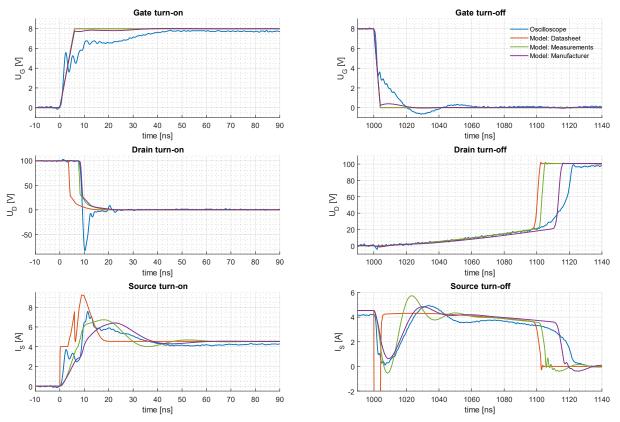

| Figure 43: SJ FET transient simulations of the model created via measurements similar to Figure 37.<br>The yellow curve models the stray capacitances depending on U <sub>DS</sub> instead of U <sub>DG</sub>                                                                                                              |

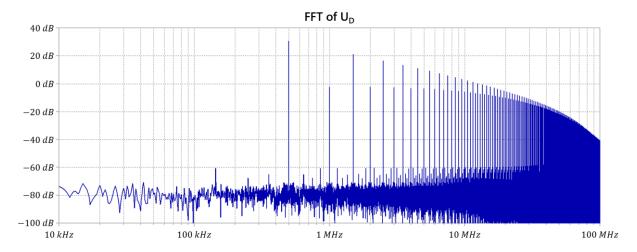

| Figure 44: LTspice simulation of an exemplary FFT analysis of the universal test circuit with the self-<br>created SiC model. The period of the gate signal is 2 µs, the duty cycle is 50% and the rise/fall time<br>is 5 ns. The shown signal components are normalized to correspond to the time domain RMS<br>amplitude |

| Figure 45: Transient simulations of the SJ FET with $R_{gate} = o \Omega$                                                                                                                                                                                                                                                  |

| Figure 46: Transient simulations of the SJ FET with $U_{gate}$ = 12 V                                                                                                                                                                                                                                                      |

| Figure 47: Transient simulations of the SJ FET with $U_{main} = 50$ V                                                                                                                                                                                                                                                      |

| Figure 48: Transient simulations of the SJ FET with $T = 125^{\circ}C$                                                                                                                                                                                                                                                     |

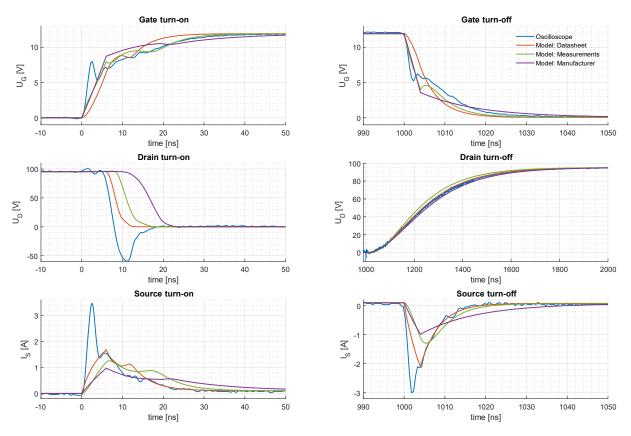

| Figure 49: Transient simulations of the SiC FET with $R_{gate} = o \Omega$                                                                                                                                                                                                                                                 |

| Figure 50: Transient simulations of the SiC FET with $U_{gate} = 16 \text{ V}$                                                                                                                                                                                                                                             |

| Figure 51: Transient simulations of the SiC FET with U <sub>main</sub> = 50 V                                                                                                                                                                                                                                              |

# LIST OF ABBREVIATIONS, ACRONYMS AND SYMBOLS

| DUT                      | Device under test                                  |

|--------------------------|----------------------------------------------------|

| EMC                      | Electromagnetic compatibility                      |

| FET                      | Field-effect transistor; equivalent to MOSFET      |

| MOSFET                   | Metal-oxide-semiconductor field-effect transistor  |

| RF                       | Radio frequency; frequencies typically above 9 kHz |

| SiC                      | Silicon carbide                                    |

| SJ                       | Superjunction                                      |

| VNA                      | Vector network analyzer                            |

|                          |                                                    |

| <i>U</i> in [ <i>V</i> ] | Used for both voltage and electric potential       |

| ٨                        | Logical AND                                        |

| V                        | Logical OR                                         |

| j                        | Imaginary unit                                     |

| $\Re$                    | Real part of a complex number                      |

| J                        | Imaginary part of a complex number                 |

|                          |                                                    |

#

# 1.1 Motivation

In modern days, EMC (electromagnetic compatibility) simulations have become crucial in the field of power electronics. Considering EMC during the development process reduces the number of hardware prototypes since unexpected effects can be detected before manufacturing an electronic system. International regulations demand for EMC tests before selling an electronic device. Thus, a failed EMC test, which is both expensive and time consuming, can be avoided by performing EMC simulations beforehand.

During the current COVID-19 pandemic, the demand not just increased for consumer electronics, but the interest also surged for the electric vehicle industry [1], [2]. It is expected that the demand on electrical vehicles will further increase if governments will put more effort in order to reach international climate goals by encouraging consumers to buy new vehicles [3]. The electrical vehicle stock is just one example for the growing demand for power electronics. Different power semiconductor devices such as an insulated-gate bipolar transistor (IGBT) or a power metal–oxide–semiconductor field-effect transistor (MOSFET) are necessary to control high electric voltages and currents. The later one excels with high switching speeds to increase the efficiency. However, high du/dt and di/dt are also a root cause for conducted and radiated emissions which make a device less electromagnetic compatible.

According to CAM [4], 2.66 times more cars are recalled than newly registered in the first half of 2020. Often, the root cause is uncertain, but EMC problems are a realistic assumption [5]. In a typical scenario, an integrated circuit (IC) which is performing a fast switching digital operation is the source of electromagnetic emissions (EME) whereas sensible analog circuits like operational amplifiers (opamp), analog-to-digital converters (ADC) or digital-to-analog converters (DAC) are electromagnetically susceptible [6]. Often, the designer of an instrument must represent economic interests and thus shielding measures, additional PCB layers or even filter components are avoided. As the time to market is shrinking as well, the product should pass EMC tests at the first attempt. This makes highly accurate simulation models even more essential to help designers to estimate possible sources of EME. In a typical production cycle nowadays, several prototypes are fabricated until an electronic system is both efficient and electromagnetically compatible; in a future scenario, a simulation should provide a good preliminary estimate of the required filtering and shielding measures in advance in order to reduce the number of prototypes significantly.

# **1.2 Power MOSFET technology**

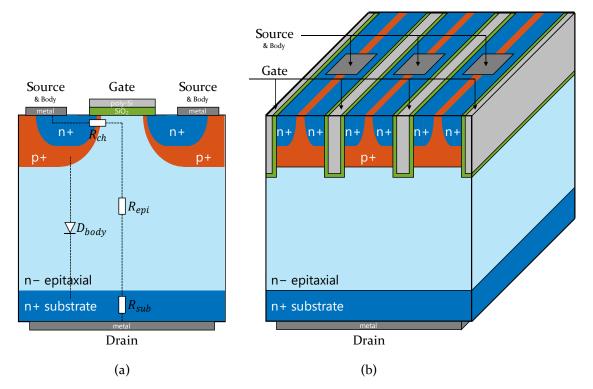

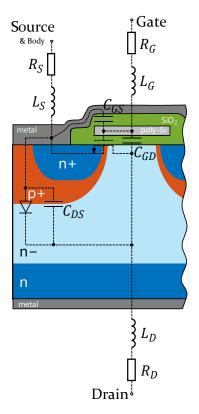

In general, the power MOSFET and the ordinary MOSFET, which is mainly used in digital applications because of its high integrity, operate according to the same physical principles but differ in their geometrics [7]. As illustrated in Figure 2, a power MOSFET's source and drain connection are placed vertical from each other and add an additional lightly doped n– layer.

In this way, the structure behaves like a p-i-n diode, and the breakdown capability depends on the thickness and the doping level of the n- epitaxial layer (drift region). The thicker and more lightly doped, the higher voltages can be blocked [8]. In addition, a low on-resistance can be achieved due to numerous MOSFET cells connected in parallel while the vertical structure keeps the area consumption low. Therefore, a power MOSFET is an asymmetrical device but uses the same electrical symbol as the ordinary MOSFET in Figure 1 with the limitation that the source contact is always connected to bulk respectively body. The power MOSFET is described in great detail in chapter 6 in "Fundamentals of Power Semiconductor Devices" [9].

Figure 1: Two equivalent versions of the n-channel power MOSFET circuit symbol

In recent years, new power MOSFET technologies were established like superjunction (SJ), silicon carbide (SiC) and gallium nitride (GaN). The later ones replace the base material of pure silicon by a blend of silicon and carbon in the case of SiC. A variety of crystalline structures exist, but in general both SiC and GaN are considered as a wide-bandgap material. Therefore, higher electric field strengths are necessary to force these components into a breakdown condition. For this reason, SiC and GaN MOSFETs are capable to switch very high voltages.

Figure 2: n-channel power MOSFET structure. (a) Planar gate. (b) Trench gate

The SJ technology on the other hand is a structural improvement of the power MOSFET. One drawback of the original power MOSFET is the high contribution of the epitaxial layer to the onresistance due to its low doping profile. To overcome this problem, the epitaxial layer must be doped more heavily. However, by doing this, the breakdown capability decreases tremendously. So, power MOSFETs bring a tradeoff relationship between on-resistance and breakdown capability. As shown in Figure 3, the SJ FET replaces this epitaxial layer and utilizes alternating p-type and n-type regions with relatively high doping profile [10]. The higher doping reduces the on-resistance significantly whereas the stacked stripes guarantee a high breakdown capability.

A MOSFET should be in a high ohmic state if  $U_{GS} = 0$ . If  $U_{DS} > 0$  is still applied, the drain connection becomes positively charged and afflicts free electrons in the adjacent n-regions. Those electrons get attracted and drift to the drain connection. At the same time, the source connection becomes negatively charged. Because source and body are shorted, the mobile holes inside the adjacent p-regions get attracted and drift towards the body connection. Therefore, the reversed biased body diode becomes depleted and no free charge carriers are available for conducting a current; not until a gate-source voltage  $U_{GS}$  is applied or breakdown occurs.

Figure 3: n-channel superjunction MOSFET structure. (a) Planar gate. (b) Trench gate according to Udrea et al. [11]

The gradient on how the depletion region expands differs in an SJ MOSFET. In normal power MOSFETs, the n– layer depletes vertically and a gradient of the potential can be recognized. The closer to the junction, the faster the potential changes because of the nonuniform distribution of the charge carriers. In contrast, SJ FETs use p-doped columns between the n-regions. Because these columns go down to the highly doped substrate, the depletion region expands laterally as well until all n-columns and p-columns become fully depleted. This leads to a uniform distribution of the electric field which is necessary to obtain a high breakdown capability [11], [12]. For this reason, a higher doping level in SJ MOSFETs reduces the on-resistance but does not reduce the achievable breakdown capability anymore [13]. At the time this thesis is written, there are no SiC MOSFETs with superjunction technology developed in a market ready state.

# 1.3 MOSFET models

For a microelectronic developer it is crucial to work with electronic simulation tools to spot design errors during the development phase. Semiconductor devices are usually described by a single model which consists out of the most relevant information. Most power MOSFET manufacturers provide such a model. However, those models are sometimes encrypted and non-editable. In addition, the provided models are often not accurate in their radio frequency (RF) behavior. So, a more suitable model is necessary for developers to increase the efficiency of their products and to pass EMC tests at the first go. This is the reason why a universal power MOSFET model is in demand.

In general, two different approaches exist when creating a MOSFET model. Historically first, the analytical approach was introduced which is more calculation intense. These first models are developed in parallel to the improvements in the semiconductor industry and deliver a physical representation of a semiconductor device [14]. Numerous parameters are needed to model the device based on formulas; a finite element analysis based on the MOSFETs geometry and material might be executed to estimate those parameters. However, such an analysis could be very time consuming, and a large number of parameters could significantly increase the simulation time which is an important factor in EMC simulations. Besides that, power MOSFET manufacturers usually do not provide detailed information about the semiconductor interiority of their products which complicates this modeling approach from a customer's perspective.

Therefore, the scope of this thesis is on behavioral models. In this approach, the device is treated as a black box where only the provided pins are accessible [14]. Thus, knowledge of the internal structure and the used materials is not required for modeling. However, this lack of linkage to the physical structure is also seen as a disadvantage. In addition, behavioral models could suffer from longer simulation times and could provoke convergence issues [15]. Moreover, the success of this approach highly depends on the datasheet information provided by the manufacturer and the accuracy of additional measurements if necessary.

#### 1.3.1 SPICE software

The circuit simulation software SPICE (Simulation Program with Integrated Circuit Emphasis) was released by the University of California, Berkeley in 1973 [16]. Its newest version SPICE 3f.5 was released as open-source software back in 1993 [17]. The SPICE simulation software is still widely used but not as the original software. A lot of free and non-free software spinoffs extended the original SPICE core with numerous features at the expense of compatibility problems between different SPICE simulators. PSpice (PSpice, Cadence Design Systems, Inc., California, US), HSPICE (PrimeSim HSPICE, Synopsys, Inc., California, US) and LTspice (LTspice XVII, Analog Devices, Inc., Massachusetts, US) are some prominent examples for commonly used software tools. But other prominent software bundles utilize the SPICE core as well; like Advanced Design System (PathWave Advanced Design System (ADS) 2021, Keysight Technologies, Inc., California, US), SIMetrix (SIMetrix/SIMPLIS, SIMetrix Technologies Ltd., GB), PSIM (PSIM 2021A, Powersim, Inc., Maryland, US), or the circuit simulation tool of Altium Designer (Altium Designer 21, Altium Ltd., California, US).

In this thesis, all simulations are done in LTspice since this program is updated regularly and is available as freeware without restrictions to its features [18]. These properties make LTspice one of the most widely distributed SPICE software tools.

#### 1.3.2 Level 1 MOSFET model

Just a few years after the MOSFET was invented in Bell Labs back in 1959 [19], H. Shichman and D. A. Hodges proposed a new equivalent circuit in 1968 [20]. This analytical model is nowadays known as Shichman-Hodges model or level 1 model which separates three modes of operation: the cutoff region (where  $U_{GS} \le U_{th}$ ), the linear region (where  $U_{GS} > U_{th}$  and  $U_{DS} < U_{GS} - U_{th}$ ) and the saturation region (where  $U_{GS} > U_{th}$  and  $U_{DS} \ge U_{GS} - U_{th}$ ).

$$I_{DS(cutoff)} = 0.$$

$$I_{DS(lin)} = \frac{\mu \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot \left[2 \cdot (U_{GS} - U_{th}) \cdot U_{DS} - U_{DS}^{2}\right] \cdot (1 + \lambda \cdot U_{DS}).$$

1.2

$$I_{DS(sat)} = \frac{\mu \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot (U_{GS} - U_{th})^2 \cdot (1 + \lambda \cdot U_{DS}).$$

1.3

Due to the time in which their paper has been published, this model is not applicable for submicron channel lengths. However, it is still commonly used today as long as the channel length is not too short. This model considers the dimensions of the transistor by its width W and length L, the capacitance of the oxide layer  $C_{ox}$ , the mobility of the charge-carriers  $\mu$  (electrons or holes) and the effect of the channel length modulation by the parameter  $\lambda$ . As source and bulk connections are shorted within a power MOSFET, the body effect is not considered in the formulas shown.

A large number of different analytical MOSFET models have been developed over the years (e. g. BSIM [21]), and to list and describe all of them would extend beyond the scope of this work. As it is impossible for a customer to estimate all parameters of a more complex analytical model, a universal behavioral model is in demand.

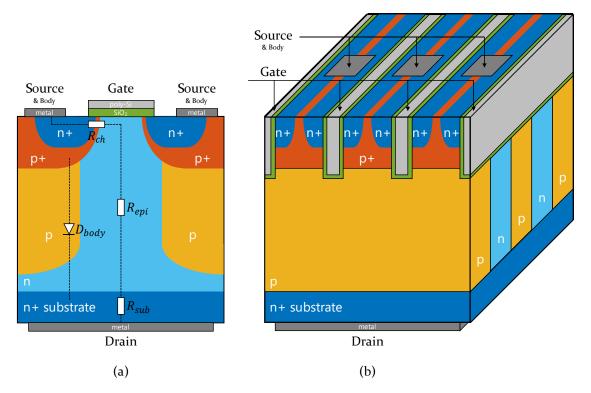

#### 1.3.3 Behavioral MOSFET model

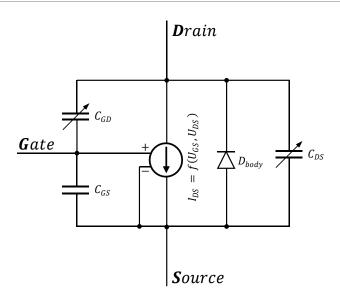

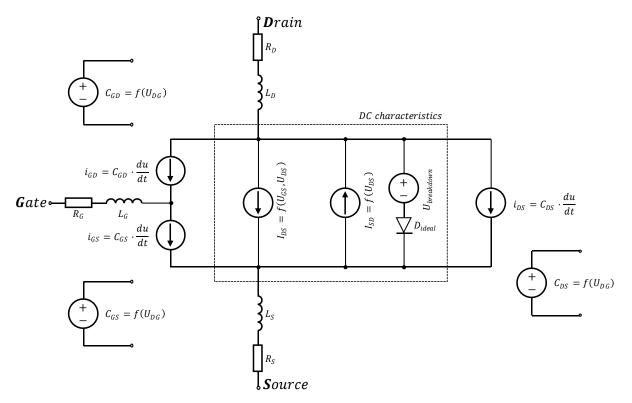

Looking at Figure 2, it can be seen that applying a drain-source voltage causes the corresponding majority charge carriers to drift towards the corresponding terminals. Thus, the non-conducting depletion region expands which reduces the capacitances  $C_{DS}$  and  $C_{GD}$ . This behavior is modeled by the very simple lumped-element model depicted in Figure 4. It consists out of a voltage-controlled current source, a diode and two voltage-dependent capacitors. Whereas  $C_{GD}$  and  $C_{DS}$  decrease the higher  $U_{DS}$  is,  $C_{GS}$  stays constant. Those capacitors are representing the stray capacitances between the connections and are essential to take the switching behavior of the MOSFET into account. As it is described in detail by McArthur [22] or Cittanti et al. [23], these capacitances will be charged and discharged during the switching process.

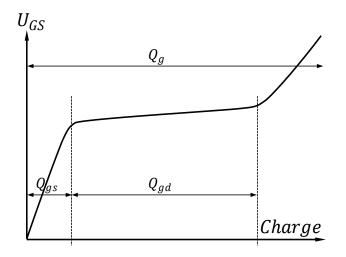

When switching on a MOSFET (i. e. to bring the MOSFET in its low-ohmic state), its gate-source voltage  $U_{GS}$  is not instantly changed, but the parasitic capacitances will be charged first as shown in Figure 5. During the subthreshold phase,  $C_{GS}$  is significantly larger than  $C_{GD}$  and thus more drive current will flow into  $C_{GS}$ . When the threshold voltage  $U_{th}$  is reached, the flow of the drain-source current  $I_{DS}$  increases rapidly and the drain-source voltage  $U_{DS}$  starts to decrease. As long  $U_{DS}$  decreases,  $C_{GD}$  increases. Therefore, most of the gate driving current will flow into the Miller capacitance  $C_{GD}$  which leads to the plateau region in Figure 5. Once  $U_{DS}$  reaches its minimum,  $C_{GD}$  is not changing anymore. So, further gate drive current will flow into both gate capacitances according to their values.

Figure 4: Simple behavioral model of a power MOSFET

Figure 5: Exemplary gate-charge curve when switching on a MOSFET

#### 1.3.4 Survey of existing approaches

An analytical model representing the switching losses of superjunction MOSFETs was elaborated in March 2016 [12]. Although this is not a complete SPICE model, it is worth mentioning because it addresses the special field distribution in superjunction MOSFETs and analyzes the switching behavior in detail.

Another analytical approach to model superjunction MOSFETs has been elaborated by Fairchild Semiconductor International, Inc. in May 2014 [15]. This model is fully SPICE compatible; however, this approach is based on the knowledge about various process parameters. Since this information is usually unknown to product developers, this thesis focuses on the creation of a universal behavioral model.

Researchers from the University of Stuttgart proposed a behavioral model for the use in transient EMC simulations in September 2017 [24]. The parasitic elements are determined via 3D simulations. Such a simulation, however, would require knowledge of the chip geometry. Hence, this approach employs a combined behavioral-analytic model.

One promising approach for modeling GaN high-electron-mobility transistors (HEMT) was presented by a group of German scientists in September 2019 [25]. The Curtice model [26] is adapted to fit the static characteristics. Further improvements are presented in order to include, for example, the temperature dependency, and the parasitic capacitances are modeled via lookup tables. The authors present a universal modeling procedure, but validation measurements are shown for a single GaN HEMT device only.

Another approach for modeling SiC MOSFETs was published by a Chinese research group in March 2018 [27]. The static characteristics are modeled using a modified version of the Shichman-Hodges model. The stray capacitances are determined using tangent functions since the capacitance changes of SiC FETs are not as complex as those of superjunction FETs.

The "Power Function Power MOSFET" (PFPM) model is an approach to create a more universal SPICE model by picking some coordinate points from the output-, transfer-, capacitances- and diode characteristics; proposed in August 2013 [28], [29]. This approach replaces the iconic formulas of the Schichman-Hodges model for the linear and saturation region by

$$I_{DS(lin)} = \frac{\sqrt{U_{DS}}}{R_{DS(on)}},$$

$$I_{DS(sat)} = c \cdot (U_{GS} - U_{th})^r$$

respectively. The differentiation between those regions is not given by  $U_{DS} = U_{GS} - U_{th}$  anymore but will be determined by the smaller number of Equation 1.4 and 1.5. One disadvantage of the PFPM model is that the parasitic capacitances shown in Figure 4 are formed by a simple power function which ensures convergence in SPICE but may not be a good enough approximation for the complex capacitance behavior of a superjunction MOSFET.

The Institute of Electronics at Graz University of Technology has published a way to generate behavioral superjunction MOSFET models in December 2020 [30], [31]. This method generates the static behavior similar to suggested in the PFPM model but uses lookup tables to include the parasitic capacitances. A model verification is only given by a simulation which compares the proposed model with the SPICE model provided by the manufacturer.

An LTspice online user group is working on power MOSFET models as well [32]. This community exploits the VDMOS model of LTspice and has developed a program which automatically generates a model after some inputs from the datasheet. However, this method is limited to the parameters which are specified within the LTspice model. For instance, the voltage-dependent capacitors of an SJ field-effect transistors usually show a more complex curve than the VDMOS model supports. Furthermore, this thesis approaches a more general SPICE model which does not ultimately depend on the predefined LTspice models.

#### **1.4 Objective of this thesis**

This thesis presents a new and easy way to create a universal behavioral model for power MOSFETs applied on a superjunction FET (IPL65R070C7 [33], Infineon Technologies AG, DE) and a silicon carbide FET (IMZ120R060M1H [34], Infineon Technologies AG, DE). Two different approaches are used to create a suitable SPICE model for simple circuit analyses which depicts the most important transient effects for further EMC considerations. First, by taking datasheet values only and second by capturing values with simple measurements.

The proposed model is created and simulated in LTspice and represents the following characteristics:

#### Static characteristics:

- Transfer characteristics

- Output characteristics

- Diode characteristics

- Temperature dependency

#### Dynamic elements:

- Voltage-dependent stray capacitances

- The inductive effect of the bonding wires

Both the generation of the proposed model and the recommended measurement methods are remarkable for their simplicity. If no datasheet is available, the MOSFET can be characterized by methods where only a few electronic instruments are needed, namely:

- two test circuits (explained in Chapter 2)

- a vector network analyzer (VNA)

- an oscilloscope (50 Ω inputs are required for transient verification measurements)

- a pulse generator

- an isolated power supply

Chapter 2 explains the general modeling procedure on the basis of an unknown DUT (device under test) to enable the reader to create their own model in their preferred SPICE software. Formulas are presented to reflect the static characteristics via controlled current sources while the dynamic elements are modeled via simple SPICE components and lookup tables. In addition, measurement setups to capture all relevant information are shown and explained in case no datasheet is available. Furthermore, LTspice test setups are illustrated to verify the created model.

Chapter 3 applies the proposed modeling procedure to create two models each for the SJ and the SiC MOSFET in LTspice. First, according to its datasheet parameters and second by the measured values. The measurement setups from Chapter 2 are applied to capture both static and dynamic behavior of the DUT. The measurement results are then compared with the graphs from the datasheets.

Chapter 4 validates the proposed power MOSFET model by comparing the simulations of the created models with measurements; gate-charge plots are created and transient measurements are performed. Comparisons are also made with the manufacturer's model. This chapter closes with two questions that can be explored in future studies.

Chapter 5 concludes this thesis and discusses the results obtained. Both, the areas of application of the model but also its limitations, are discussed; suggestions for future improvements of the model are noted. Advantages and disadvantages are summarized, and future challenges are explored.

# **2** Methods

The first part of this chapter describes a universal circuit which is used to capture the static and transient behavior of a power MOSFET. After that, the general modeling procedure for any unknown DUT is presented to generate the proposed model illustrated in Figure 6. The last part shows the simulation test benches to validate the proposed models.

Section 2.1 starts off by presenting the universal test board which is regularly referenced in this thesis. An exemplary layout is given to highlight the special requirements to optimize this circuit in its radio frequency behavior.

Section 2.2 explains the procedure to model the static behavior by adapting the level 1 model.

Section 2.3 shows the depiction of the dynamic behavior with the help of lookup tables. A special property of the proposed model is that all stray capacitances depend on the drain-gate voltage. A measurement setup is presented in order to capture these capacitances, but also the parasitic elements of the bonding wires, through a single series of measurements.

Section 2.4 presents simulation test benches in order to verify the created models.

Figure 6: Proposed power MOSFET model

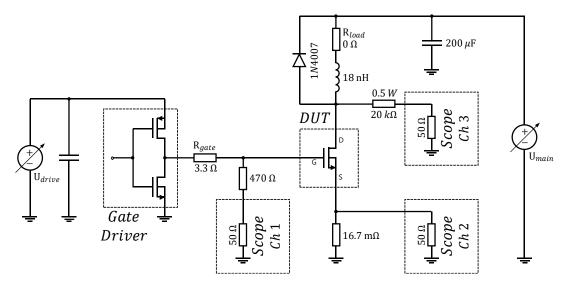

# 2.1 Universal test circuit

The basic circuit illustrated in Figure 7 is used to monitor gate, source and drain voltage potential of the power MOSFET, the device under test (DUT). Since the DUT is capable to switch very high currents above 100 A while withstanding more than 1000 V, special measures are necessary to capture RF components of the switching process. In addition, when the load  $R_{load}$  is shorted, it is necessary to keep the ON-time (i. e. the time span where the MOSFET is low-ohmic) very short. Otherwise, the very high currents would overheat the power MOSFET as no cooling device is attached to it. A proper heat sink could solve the heat problem but could cause unwanted RF coupling effects as well. This thesis concerns the modeling of the MOSFET including its package; the influence of a heat sink must be modeled separately, since its coupling behavior depends on the potential to which the heat sink is connected.

To keep the ON-time short, a pulse generator like an arbitrary waveform generator (AWG) is used to generate a short pulse with a pulse length of a few  $\mu s$ . This controlling signal is forwarded to the input pins of a gate driver to switch on a power MOSFET for just a few  $\mu s$ . A very large decoupling capacitor (200  $\mu F$  in Figure 7) is needed to serve as a large charge carrier reservoir since very high currents may flow within the main current loop. By placing this decoupling capacitor as close as possible to the load and the 16.7  $m\Omega$  current sensing resistor, the loop area of the flowing current is kept as small as possible and thus keeps the inductance in the main current loop low. The flyback diode is a necessary safety measure.

A main selection criterion for the gate driver IC is that the device is capable to drive high currents of at least 4 *A* within very short rise and fall times in the *ns* range. Because of the steep edges, a high usable measuring bandwidth is necessary. This is the reason why an oscilloscope with 50  $\Omega$  termination resistors is used. Through the use of 50  $\Omega$  wave impedance cables, oscilloscope and cable are matched, and (ideally) no RF reflections occur at the termination resistor.

Figure 7: Schematic of the proposed test circuit

Channel 2 of the oscilloscope captures the voltage  $U_{source}$  across the 16.7  $m\Omega$  current sensing resistor. The current is then determined by Ohm's law; the resulting error caused by the 50  $\Omega$  input impedance is negligible. The selection of this sensing resistor is crucial. First, the resistance must be constant through a broad frequency range. This is achieved by connecting six 100  $m\Omega$  resistors in parallel which reduce the parasitic inductance [35]. Those resistors are placed symmetrically around an SMA connector, and the whole current sense construction is placed

directly on the opposite plane beneath the source pin of the DUT. Second, the current sensing resistor must survive short pulses with a lot of power. If the resistor dies with high resistance, the oscilloscope can be damaged irreparably.

Channel 1 of the oscilloscope must be protected with a 470  $\Omega$  resistor since the input power of an 50  $\Omega$  oscilloscope must not exceed 0.5 *W*. Therefore, the measured value must be converted according to the voltage divider. One disadvantage of the simple circuit shown in Figure 7 is that the driving electronic is coupled galvanically with the main side. This leads to an interaction, and the voltage drop across the current sensing resistor is necessary to take into account by

$$U_{GS} = U_{gate(meas)} \frac{520}{50} - U_{source}.$$

2.1

Channel 3 of the oscilloscope must be protected as well. This resistor must be dimensioned considering the power consumption since a considerable amount of current will flow through the oscilloscope when the power MOSFET is in its OFF state. By placing a 20  $k\Omega$  resistor, this resistor must be capable to withstand 0.5 *W* when 100 *V* are applied. Here, a tradeoff must be done by sacrificing resolution of the measured signal. The drain-source voltage is calculated by

$$U_{DS} = U_{drain(meas)} \frac{20050}{50} - U_{source}.$$

2.2

Since this thesis pursues the goal of enabling EMC simulations, the layout must be optimized with respect to its RF behavior in order to be able to make better statements between simulation and measurement. Figure 8 shows an example where traces between decouple capacitors and components are designed as short as possible to keep the resulting loop areas as small as possible. With the help of vias, larger loops can be avoided. In addition, the power supply connections are placed next to each other to further minimize parasitic inductances. Also, the GND plane is designed over a large area on both planes to keep that plane as low-impedance as possible. If it is planned to heat up the DUT by an additional heating element, it is highly recommended to use a shielded component and to place an additional insulator within the thermal paste layer, and its voltage source should be isolated from the rest of the network. In general, the resulting parasitic inductances show a greater influence the faster the gate signal is switched, i. e. the lower the gate resistor is selected.

Figure 8: Exemplary layout for the proposed test circuit on both planes. Zoom level: 150%. Dark red arrows indicate the current path of the main current side. (a) Top plane. Additional light blue arrows highlight the current path of the driving signal. (b) Bottom plane containing the six current sensing resistors

### 2.2 DC characteristics

The basic formulas of the Shichman-Hodges model are utilized to represent the transfer and output characteristics. Due to the fact that the internal geometry of a MOSFET is usually unknown from a customer's perspective, Equation 2.3 introduces  $\beta = \mu \cdot C_{ox} \cdot W/L$ . To achieve the saturation kink at high  $U_{GS}$  in Figure 9a, the Shichman-Hodges equations are expanded with Equations 2.4 and 2.5. While the former equation limits the rise of  $I_{DS}$ , the later equation smooths the kink by averaging the values within the range  $U_{GS} \pm C$ , e. g. C = 0.1. Regardless of whether the model is created via the datasheet or via measurements, the final model outputs the current from Equation 2.5 which is composed of Equations 2.3 and 2.4.

$$I_{DS(1)} = \begin{cases} 0, & U_{GS} \leq U_{th} \\ \frac{\beta}{2} \left[ 2(U_{GS} - U_{th})U_{DS} - U_{DS}^{2} \right] (1 + \lambda U_{DS}), & U_{GS} > U_{th} \wedge U_{DS} < U_{GS} - U_{th} \\ \frac{\beta}{2} (U_{GS} - U_{th})^{2} (1 + \lambda U_{DS}), & U_{GS} > U_{th} \wedge U_{DS} \geq U_{GS} - U_{th} \\ \end{cases}$$

$$(T_{C} = R_{constraints})$$

$$I_{DS(2)} = \min\left\{\frac{U_{DS}}{A}, I_{DS(1)}\right\}.$$

2.4

$$I_{DS(3)} = f(U_{DS}, U_{GS}) = \frac{I_{DS(2)}(U_{DS}, U_{GS} - C) + I_{DS(2)}(U_{DS}, U_{GS}) + I_{DS(2)}(U_{DS}, U_{GS} + C)}{3}.$$

2.5

Figure 9: Typical DC behavior of a MOSFET. Red markings show the points to extract for the modeling process. (a) Transfer characteristics when a MOSFET is in saturation mode. (b) Output characteristics

The following twelve key values (eight if temperature dependency is neglected) must be captured from the graphs depicted in Figure 9. Such a diagram of the transfer and output characteristics can be found in any usual datasheet. If no datasheet is provided, the test circuit explained in Section 2.1 can be used to extract the needed values.

Grid points, which must be extracted from the transfer characteristics:

- $I_{DS1}$  at  $U_{GS1}$  a bit after the threshold voltage

- $I_{DS2}$  at  $U_{GS2}$  when a high amount of current flows but before the kink appears

- (optional) *warm* as variable for specifying a second temperature in °C

- (optional)  $\Delta U_{th1}$  as an approximated difference of the threshold voltage between *warm* and "room" temperature. In general, this quantity contains a negative number.

Grid points, which must be extracted from the output characteristics:

- $I_{DS3}$  at  $U_{DS3}$  within the linear region at very high  $U_{GS}$

- (optional) *I*<sub>DS3(warm)</sub> at *U*<sub>DS3</sub>; same as before but at *warm* temperature

- $I_{DS4}$  at  $U_{DS4}$  within the beginning of the saturation region with the same  $U_{GS}$  as before

- (optional) *I*<sub>DS4(warm)</sub> at *U*<sub>DS4</sub>; same as before but at *warm* temperature

Analyzing the saturation region in Equation 2.3, the three unknown parameters  $\beta$ ,  $U_{th}$  and  $\lambda$  must be determined from two measuring points from the transfer characteristics in Figure 9a. So, the channel length modulation factor  $\lambda$  must be assumed first to obtain an explicit result for the other two variables. A simple estimation can be  $\lambda = 0.001$ . Thereafter, having two values for  $I_{DS}$  for two different  $U_{GS}$  allows to determine the unknown parameters

$$U_{th(cold)} = \frac{U_{GS2} - U_{GS1} \sqrt{\frac{I_{DS2}}{I_{DS1}}}}{1 - \sqrt{\frac{I_{DS2}}{I_{DS1}}}},$$

$$\beta = \frac{2 \cdot I_{DS1}}{\left(U_{GS1} - U_{th(cold)}\right)^2}.$$

2.6

The optional temperature dependency can be reflected by adapting  $U_{th}$  with the modification factor  $\Delta U_{th1}$ . The amplification factor  $\beta$  remains unaffected from this modification. Equation 2.8 is obtained after introducing the variable *temp* as the actual temperature and assuming "room" temperature at 25°*C*.

$$U_{th} = U_{th(cold)} + \Delta U_{th1} \cdot \frac{(temp - 25)}{(warm - 25)}.$$

Analyzing Equation 2.4, the two unknown parameters A and B must be determined from two measuring points from the output characteristics in Figure 9b. Having two values for  $I_{DS}$  for two different  $U_{DS}$  allows to determine these unknown parameters by

$$B_{(cold)} = \frac{\log\left(\frac{I_{DS4}}{I_{DS3}}\right)}{\log\left(\frac{U_{DS4}}{U_{DS3}}\right)},$$

$$A_{(cold)} = \frac{U_{DS3}^{B_{(cold)}}}{I_{DS3}}.$$

2.9

~ - >

The optional temperature dependency can be reflected by applying Equations 2.9 and 2.10 again but replacing  $I_{DS3}$  by  $I_{DS3(warm)}$  and  $I_{DS4}$  by  $I_{DS4(warm)}$ . This leads to a new  $B_{(warm)}$  to calculate a new  $A_{(warm)}$ . Equations 2.11 and 2.12 show the final temperature dependent variables A and B.

$$A = A_{(cold)} + (A_{(warm)} - A_{(cold)}) \cdot \frac{(temp - 25)}{(warm - 25)}.$$

2.11

$$B = B_{(cold)} + (B_{(warm)} - B_{(cold)}) \cdot \frac{(temp - 25)}{(warm - 25)}.$$

2.12

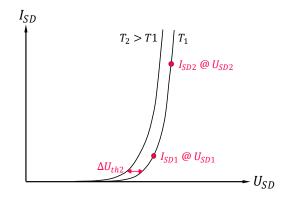

The body diode behavior shown in Figure 10 is modeled very similar to the transfer characteristics and is defined by

$$I_{SD} = \begin{cases} 0 & U_{SD} \le U_{th2} \\ D \cdot (U_{SD} - U_{th2})^2 & U_{SD} > U_{th2} \end{cases}.$$

2.13

Grid points, which must be extracted from the body diode characteristics:

- *I*<sub>SD1</sub> at *U*<sub>SD1</sub> a bit after the threshold voltage

- *I*<sub>SD2</sub> at *U*<sub>SD2</sub> when a high amount of current flows

- (optional)  $\Delta U_{th2}$  as an approximated difference of the threshold voltage between *warm* and "room" temperature. In general, this quantity contains a negative number.

Figure 10: Typical body diode behavior of a MOSFET. Red markings show the points to extract for the modeling process

The parameter  $U_{th2}$  in Equation 2.13 is evaluated in the same way as shown in Equation 2.6 by just replacing  $U_{GS}$  by  $U_{SD}$  and  $I_{DS}$  by  $I_{SD}$ . The same is true for the amplification factor D which is evaluated as shown in Equation 2.7 after additionally inserting  $U_{th2}$  instead of  $U_{th(cold)}$  and removing the multiplication factor 2. The optional temperature dependency is calculated in the same way as shown in Equation 2.8 by further replacing  $\Delta U_{th1}$  by  $\Delta U_{th2}$ .

Finally, the breakdown voltage is modeled by a series connection of an ideal diode and an ideal voltage source as it can be seen in Figure 6. This voltage source outputs the breakdown voltage. When  $U_{DS}$  exceeds that breakdown voltage, the ideal diode becomes conductive.

#### 2.3 AC characteristics

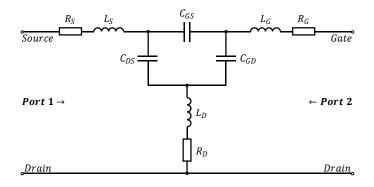

The power MOSFET illustrated in Figure 11 shows the dynamic elements, i. e. the parasitic capacitors and inductances. Usually, power MOSFET datasheets provide the information of the stray capacitances with the parameters  $C_{iss}$  (input capacitance),  $C_{oss}$  (output capacitance) and  $C_{rss}$  (feedback capacitance). Therefore, if the datasheet values are taken to model the parasitic capacitances, these must be converted first according to Equations 2.14-2.16. Unfortunately, most datasheets do not provide information about the parasitic inductance of a power MOSFET since inductance generally appears as a phenomenon when current is flowing in loops.

$$C_{iss} = C_{GS} + C_{GD}.$$

$$C_{oss} = C_{DS} + C_{GD}.$$

2.15

$$C_{rss} = C_{GD}.$$

Figure 11: Equivalent circuit of a power MOSFET

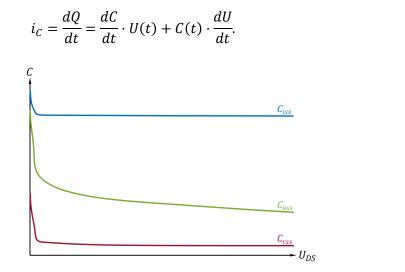

The voltage-dependent capacitances  $C_{GD}$ ,  $C_{DS}$  and  $C_{GS}$  are modeled via lookup tables. For this, Figure 6 shows the three voltage-controlled voltage sources, exceptionally<sup>1</sup> with the formula character C,  $C_{GD} = f(U_{DG})$ ,  $C_{DS} = f(U_{DG})$  and  $C_{GS} = f(U_{DG})$  where the capacitance information to a specific  $U_{DG}$  is saved within a table. This approach is rather unique since usually these capacitances are set in dependence of the drain-source voltage. However, experiments in Subsection 4.3.4 indicate that the stray capacitances are not only dependent on the drain-source voltage but also whether the MOSFET is switched on or not. When  $C_{iss}$ ,  $C_{oss}$ , and  $C_{rss}$  are measured with an LCR meter, the gate and source connection are usually shorted DC-wise while capacitances are shorted AC-wise depending on which parameter is measured. Datasheets thus specify stray capacitances with the MOSFET turned off, e. g. in [36]. This thesis assumes a linear dependency on the gate-source voltage, so that the stray capacitances depend on  $U_{DG} = U_{DS} - U_{GS}$ . The capacitances are treated as commonly seen in industry and literature<sup>2</sup>; only in SPICE the gate potential is used instead of the source potential. Capacitance values to voltages below  $U_{DS} = 0 V$  are assumed to be constant without slope which is performed by LTspice as default.

For instance, if  $U_{GS} = 0 V$  and  $U_{DS} = 10 V$  are applied, the voltage sources in SPICE look up in their tables to output the voltage defined by the user, e. g.  $C_{GD} = 100 pV$ ,  $C_{DS} = 200 pV$  and  $C_{GS} = 300 pV$ . These voltages are passed to the three voltage-controlled current sources  $i_{GD}$ ,  $i_{DS}$ and  $i_{GS}$  which multiply these voltages by the time derivative of the corresponding voltage drop. As an example,  $i_{GD}$  takes the value from  $C_{GD}$  and multiplies this voltage with the time derivative of the voltage drop between gate and drain. In this way, the electric current in Equation 2.17 is modeled under the assumption that the capacitance is not changing over time.

<sup>&</sup>lt;sup>1</sup> In this thesis, voltage sources are usually identified by the formula symbol U. However, the lookup tables are an exception here; capacitance values are stored but these are output as voltage.

<sup>&</sup>lt;sup>2</sup> Datasheets usually specify  $C_{iss}$ ,  $C_{oss}$  and  $C_{rss}$  as a function of  $U_{DS}$ . In academic papers,  $C_{GS}$  is often assumed to be constant while  $C_{GD}$  depends on either  $U_{DG}$  or  $U_{DS}$ . However,  $C_{DS}$  is usually always expressed as a function of  $U_{DS}$ .

If parasitic resistances and inductances are modeled, the inner voltage drops must be considered because these elements are representing the bonding wires of the DUT. It should be noted that the use of lookup tables could negatively affect the convergence behavior of SPICE since a linear interpolation between the points results in non-differentiable points.

2.17

Figure 12: Typical voltage-dependent behavior of the parasitic capacitors of a power MOSFET. A superjunction MOSFET typically shows more complex curves as explained by Castro et al. [12]

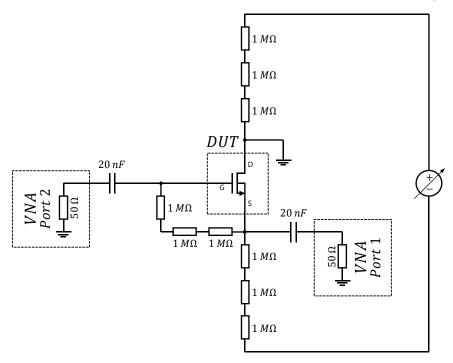

If no datasheet is available or the information within the datasheet is not satisfying, the dynamic elements can be measured according to Liu et al. [37] and Fuchs et al. [31]. The measurement setup proposed by Fuchs et al. is implemented as shown in Figure 13. This setup has the advantage that a single measurement provides information about all stray capacitances and parasitic inductances. An isolated power supply is increasing  $U_{DS}$  stepwise whereas a VNA is capturing the scattering parameters (S-parameters) at gate and source for each step of  $U_{DS}$ . The captured S-parameters are then converted into impedance parameters (Z-parameters) by applying Equations 2.18 to 2.21. The transmission lines between VNA and DUT must show a 50  $\Omega$  wave impedance to avoid reflections. For safety reasons, each of the VNA input ports are secured by a 20 *nF* capacitor (DC block) which is capable to sustain high voltages up to 500 *V*.

$$Z_{11} = 50 \,\Omega \cdot \frac{\left((1+S_{11})(1-S_{22})+S_{12}S_{21}\right)}{(1-S_{11})(1-S_{22})-S_{12}S_{21}}.$$

2.18

$$Z_{12} = 100 \,\Omega \cdot \frac{S_{12}}{(1 - S_{11})(1 - S_{22}) - S_{12}S_{21}}.$$

2.19

$$Z_{21} = 100 \,\Omega \cdot \frac{S_{21}}{(1 - S_{11})(1 - S_{22}) - S_{12}S_{21}}.$$

$$Z_{22} = 50 \,\Omega \cdot \frac{\left((1 - S_{11})(1 + S_{22}) + S_{12}S_{21}\right)}{(1 - S_{11})(1 - S_{22}) - S_{12}S_{21}}.$$

Resistors with 1  $M\Omega$  are used as RF filters to guide the RF testing signals to the DUT. For accurate measurements, the filter elements must have a higher impedance than the internal stray capacitances. Experiments have shown that even geometrically small inductors exhibited their first resonance at relatively low frequencies and are thus unsuitable for the use up to the GHz range. That is why simple resistors are used as RF filter components in Figure 13. The parasitic capacitance of the filter is reduced by connecting the resistors in series.

The filter connecting the gate and source terminals of the MOSFET guarantees that the DUT remains turned off throughout the measurement. Nevertheless, a very small leakage current flows through the high-impedance drain-source channel. This current causes a voltage drop across the other two filters which must be taken into account when determining  $U_{DS}$ .

Figure 13: Setup to capture the AC characteristics of a MOSFET

All four Z-parameters show the shape of a typical RLC series connection impedance curve, i. e. at low frequencies, mainly the capacitances determine the impedance whereas the inductances dominate at high frequencies. Therefore, by inspecting the measuring points at low frequencies, the inductances and resistances shown in the simplified two-port network in Figure 14 can be neglected. The remaining capacitors form a delta ( $\Delta$ ) circuit. Thus, a  $\Delta$ -Y transform is necessary to simplify the calculation [37]. If the measuring points are inspected at high frequencies, the inductances dominate which are already in Y configuration. In either case, as explained by Fuchs et al. [31], the Z-parameters can further be rewritten to determine  $Z_D$ ,  $Z_G$  and  $Z_S$  respectively by

$$Z_D = Z_{12} \vee Z_{21}$$

, 2.22

$$Z_G = Z_{22} - Z_{21} \vee Z_{22} - Z_{12}, \qquad 2.23$$

$$Z_S = Z_{11} - Z_{21} \vee Z_{11} - Z_{12}.$$

Figure 14: Simplified two-port network of the setup shown in Figure 13 considering ideal filter components

By taking the measurement points at low frequencies, the voltage-dependent capacitances can be calculated by putting  $Z_D$ ,  $Z_G$  and  $Z_S$  into the Equations 2.25, 2.26 and 2.27.

$$C_{GD} = \frac{1}{2\pi f} \cdot \Im \left\{ \frac{Z_S}{Z_G Z_D + Z_D Z_S + Z_G Z_S} \right\}.$$

2.25

$$C_{DS} = \frac{1}{2\pi f} \cdot \Im \left\{ \frac{Z_G}{Z_G Z_D + Z_D Z_S + Z_G Z_S} \right\}.$$

2.26

$$C_{GS} = \frac{1}{2\pi f} \cdot \Im \left\{ \frac{Z_D}{Z_G Z_D + Z_D Z_S + Z_G Z_S} \right\}.$$

2.27

The parasitic inductances can be calculated by taking the measurement points at high frequencies and putting  $Z_D$ ,  $Z_G$  and  $Z_S$  into the Equations 2.28, 2.29 and 2.30.

$$L_D = \frac{1}{2\pi f} \cdot \Im\{Z_D\}.$$

2.28

$$L_G = \frac{1}{2\pi f} \cdot \Im\{Z_G\}.$$

2.29

$$L_S = \frac{1}{2\pi f} \cdot \Im\{Z_S\}.$$

2.30

Although parasitic resistances are not part of the AC characteristics, it is worth mentioning here as these can be calculated by taking the real part of  $Z_D$ ,  $Z_G$  and  $Z_S$ .

$$R_D = \Re\{Z_D\}.$$

$$R_G = \Re\{Z_G\}.$$

$$R_S = \Re\{Z_S\}.$$

#### 2.4 Simulation test benches

The generated models need to be verified. The following characteristics can be quickly checked via simulations since this information is usually available in datasheets:

- Output characteristics:  $I_{DS} = f(U_{DS}, U_{GS})$

- Transfer characteristics:  $I_{DS} = f(U_{GS})$

- Diode characteristics:  $I_{SD} = f(U_{SD})$

- Capacitances:  $C_{iss} = f(U_{DS}), C_{oss} = f(U_{DS}), C_{rss} = f(U_{DS})$

- Gate-charge:  $U_{GS} = f(Q_G)$

While the first characteristics have already been clearly described, the gate-charge plot requires further explanation. Figure 5 shows a typical gate-charge curve which can be achieved by the simple simulation setup shown in Figure 15 [32]. A typical datasheet clearly states at which  $I_{DS}$  and  $U_{DS}$  the gate-charge plot was recorded, and the setup in Figure 15 must be adapted accordingly.

The voltage at the gate connection is increased linearly. As long as the MOSFET is in its subthreshold region, nearly all current from the current source flows through the diode. If the MOSFET is then switched on, exactly as much current is driven through the MOSFET as it is defined in its current source. At the latest when the entire current of the current source flows through the DUT, the potential at the drain connection drops from the predefined test voltage  $U_{DS}$  down to  $R_{DS(on)} \cdot I_{DS}$ . For the final gate-charge plot, the current through the voltage source  $U_{GS}$  is integrated and plotted as x-axis.

Figure 15: Proposed LTspice schematic to simulate the gate-charge plot. The red markings need to be adapted according to the gate-charge plot given in the datasheet

Whether or not a datasheet is provided, the following measurements are strongly recommended. The universal test circuit shown in Figure 7 can be adapted for different values (e. g. for  $R_{load}$ ,  $R_{gate}$ ,  $U_{gate}$  or  $U_{src}$ ) to create different test conditions. The captured values for  $U_G$ ,  $U_S$  and  $U_D$  can then be compared with the simulated values obtained by the test bench shown in Figure 16. The gate driver is assumed to be an ideal voltage source in this work. Both rise and fall time were analyzed with an oscilloscope and checked with the datasheet beforehand. However, if the manufacturer provides a model for the gate driver, it is recommended to use this model instead.

Figure 16: Proposed LTspice test bench to allow comparison between simulated and measured values. Exemplary lumped-element models for the load and the decouple capacitor are shown

Since this thesis pays special attention to the intended use for EMC simulations, the load and the decouple capacitor must be further analyzed by its frequency behavior. For this, 1-port and 2-port measurements according to Sandler [38] must be accomplished with a VNA.

In the case of the load, a simple 1-port measurement can be performed. In a 50  $\Omega$  system, the impedance can be calculated from the measured reflection coefficient  $\Gamma$  by using Equation 2.34. Further, the impedance can be utilized to find an appropriate equivalent lumped-element model.

$$Z_{DUT} = 50 \,\Omega \cdot \frac{1+\Gamma}{1-\Gamma}.$$

In the case of the decouple capacitor, a 2-port shunt measurement is recommended. In a 50  $\Omega$  system, the impedance can be calculated from the measured S-parameters by

$$Z_{DUT} = 25 \,\Omega \cdot \frac{S_{21}}{1 - S_{21}}.$$

In this thesis, multilayer ceramic chip capacitors (MLCC) are used because they usually exhibit a low inductance. However, since normally a power MOSFET is operated at 100 *V* or higher, the voltage dependency of the ceramic decouple capacitor must be taken into account. A setup to capture the S-parameters with simultaneous change of the bias voltage of the capacitor is given in Figure 17. The resistors form an RF filter similar to the setup in Figure 13. However, the values for the resistances cannot be chosen higher without sacrificing additional waiting time because of the high capacitance of the DUT. According to Vishay Intertechnology, Inc. [39], surfacemounted resistors with high resistances tend to have higher parasitic capacitances. Therefore, the smallest 1  $k\Omega$  resistor is placed closest to the DUT because it has a larger impedance at very high frequencies than the largest 100  $k\Omega$  resistor. Ultimately, the capacitor can be modeled voltage-dependent by specifying the capacitance with an expression for the charge  $Q = C \cdot U$ .

Figure 17: Setup to perform a 2-port shunt measurement with a variable bias voltage

# **B** Model Creation

In this chapter, the presented method is applied to create models for the superjunction [33] and the silicon carbide [34] field-effect transistor. Two versions are presented; first, a version by utilizing the key information of a datasheet, and second, by performing measurements with the test structure explained in Section 2.1. For the measurements, a 50  $\Omega$ , 500 *MHz* oscilloscope (MSO6054A, Agilent Technologies, Inc., California, US) was used. To power up the test circuit, two power supplies are required. The first power supply (SM660-AR-11, Delta Elektronika B.V., NL) was used for the main side and the other power supply (EL302T, Thurlby Thandar Instruments Ltd., GB) was supplying the gate driver (EiceDRIVER [40], Infineon Technologies AG, DE). A 555 timer IC (LMC555, Texas Instruments, Inc., Texas, US) configured as monostable multivibrator was used to generate the pulse for the gate driver. The current sensing resistor (ERJL03KF10CV, Panasonic Corp., JP) and the inductive load, an air coil (0806SQ-12NGLC, Coilcraft, Inc., Illinois, US), are characterized in Section 4.1. The models are created within the simulation software LTspice but MATLAB (MATLAB R2019a, The MathWorks, Inc., Massachusetts, US) is used to generate all plots. Figure 18 presents a created model from the proposed model in Figure 6. All model parameters can be found in the Appendix 7.2 in detail.

Figure 18: Proposed power MOSFET model in LTspice. Red rectangles indicate symbols which contain voltage-controlled subcircuits. The model for the IMZ120R060M1H SiC FET created via measurements is shown as an example. Note that the capacitances are determined using the voltage drop U<sub>DG</sub> instead of U<sub>DS</sub>

# 3.1 DC characteristics cont'd

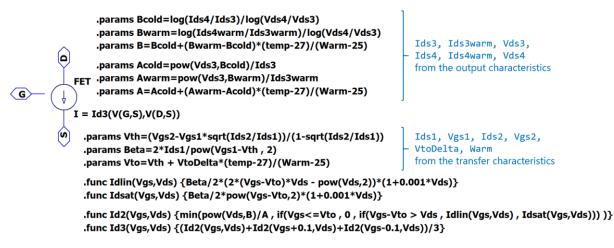

In Figure 18, the two subcircuits relevant for the static characteristics are X1 and X2. The first subcircuit X1 contains an arbitrary behavioral current source which is responsible to output the current in Equation 2.5 and is depicted in Figure 19.

Figure 19: Arbitrary behavioral current source in LTspice in order to output the proposed formula for the DC current

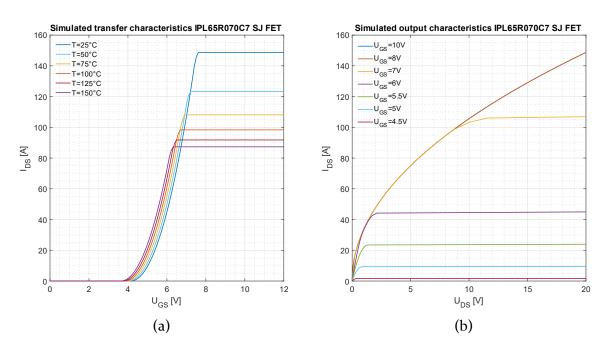

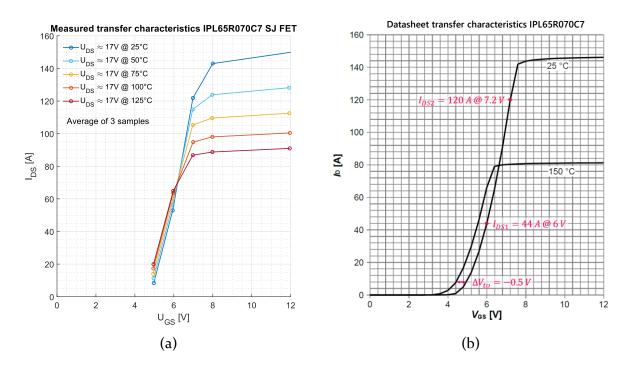

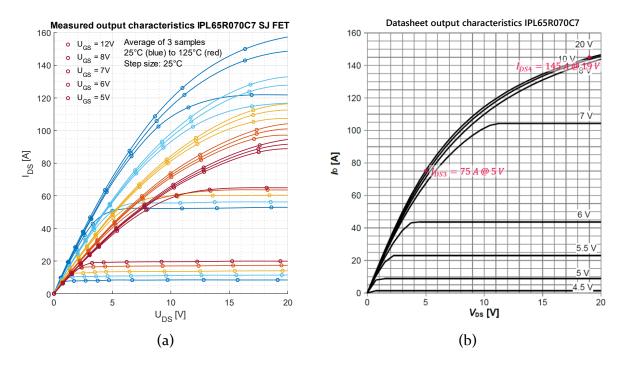

As it is explained in Section 2.2, twelve parameters (eight if temperature dependency is neglected) are passed to the subcircuit. Figure 21 to Figure 24 show the corresponding graphs from where these parameters are taken from. The plots from the datasheets are additionally labeled in red at those locations where the corresponding parameters were extracted. Figure 20 and Figure 25 show the characteristics of the generated datasheet models. This model could be further expanded, e. g. by including the dependence of  $R_{DS(on)} = f(I_{DS})$  mapped within the variable *A* in Equation 2.11 to provoke a slope in the saturated transfer characteristics.

Figure 20: Characteristics of the simulated SJ MOSFET model based on the datasheet. (a) Transfer characteristics. (b) Output characteristics

Figure 21: Transfer characteristics of the SJ MOSFET. (a) Measured at five different temperatures with the proposed test circuit. Average of 3 samples. (b) Plot taken from the datasheet at  $U_{DS} = 20 V [33]$  with red markings located at exemplary positions to extract the required information. Note that the drain-source voltage and the maximum temperature differs between the plots

Figure 22: Output characteristics of the SJ MOSFET. (a) Measured at five different temperatures with the proposed test circuit. Average of 3 samples. (b) Plot taken from the datasheet at 25°C [33] with red markings located at exemplary positions to extract the required information

Figure 23: Transfer characteristics of the SiC MOSFET. (a) Measured at five different temperatures with the proposed test circuit. (b) Plot taken from the datasheet at  $U_{DS} = 20 V [34]$  with red markings located at exemplary positions to extract the required information

Figure 24: Output characteristics of the SiC MOSFET. (a) Measured at three different temperatures with the proposed test circuit. (b) Plot taken from the datasheet at 25°C [34] with red markings located at exemplary positions to extract the required information

Figure 25: Characteristics of the simulated SiC MOSFET model based on the datasheet. (a) Transfer characteristics. (b) Output characteristics

Comparing Figure 20 (SJ) with Figure 25 (SiC), the limitations of the proposed model become apparent. Since the superjunction MOSFET is modeled very well right away, the SiC MOSFET model would require further finetuning. In this case, a higher channel length modulation factor  $\lambda$  would increase the slope of the output characteristics.