Michael Stefan Maierhofer, BSc

# Automated generation of a Module Protection Unit for RISC-V based SoCs following the Model-driven Architecture principle

### MASTER'S THESIS

to achieve the university degree of Diplom-Ingenieur Master's degree programme: Information and Computer Engineering

submitted to

Graz University of Technology

Supervisor

Univ.-Prof. Dipl.-Inf. Dr.rer.nat. Marcel Carsten Baunach Institute of Technical Informatics Dipl.-Ing. Heimo Hartlieb Infineon Technologies Austria AG

Graz, October 2020

This document is set in Palatino, compiled with  $pdf \mbox{\tt Biber}.$

The LATEX template from Karl Voit is based on KOMA script and can be found online: https://github.com/novoid/LaTeX-KOMA-template

### AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present master's thesis.

Date, Signature

# Abstract

The number of transistors in ICs is still steadily growing despite Moore's law being declared dying numerous times. The productivity is trailing behind with an increase by factor 20, leading to an ever-expanding 'design-productivity gap'. The closing of this gap has led to the introduction of a novel hardware generation flow based on a model-driven architecture (MDA) principle.

Prior to this thesis, a CPU core generator for the hardware MDA flow had been developed, based on the RISC-V ISA. Said core had support for interrupts and exceptions but was missing means to restrict accesses to memory and peripherals. Such restrictions are crucial to ensure freedom from interference between subsystems in functional safety systems. This work looks into the generation of a memory protection unit (MPU) as an extension to the MDA flow for RISC-V based SoCs.

The MPU presented in this work is fully incorporated into the core and enables effective memory protection and isolation with a minimal performance overhead.

# Kurzfassung

Die Anzahl an Transistoren in ICs steigt trotz dem mehrfach erklärten Ende des Mooreschen Gesetz stetig weiter. Gleichzeitig fällt die Produktivität immer weiter zurück. Bereits jetzt ist das Produktivitätsdefizit um mehr als das 20fache gestiegen, und es wird immer größer. Um diesen "Design-Productivity Gap" zu schließen wurde ein neuartiger Ansatz für die Generierung von Hardware basierend auf dem Prinzip einer Modell-getriebenen Architektur (MDA) entwickelt.

Vor dieser Masterarbeit wurde bereits ein Generator für eine CPU mit dem RISC-V Instruktionssatz für den Hardware MDA-Flow entwickelt. Diese CPU unterstützte Interrupts und Exceptions, eine Möglichkeit Zugriffe auf Speicher sowie Peripherie zu beschränken waren allerdings nicht gegeben. Derartige Zugriffsbeschränkungen sind allerdings notwendig um die Rückwirkungsfreiheit (engl. "freedom from interference") zwischen Subsystemen in Systemen mit Anforderungen an Funktionaler Sicherheit zu garantieren. Weswegen sich diese Arbeit nun damit beschäftigt eine Memory Protection Unit (MPU) als Erweiterung des MDA-Flow für RISC-V basierte SoCs zu realisieren.

Die im Zuge dieser Arbeit entworfene MPU ist vollständig in die CPU integriert, und ermöglicht einen effektiven Speicherschutz und Isolation mit minimalen Leistungseinbußen.

# Acknowledgements

I want to thank both Univ.-Prof. Dipl.-Inf. Dr.rer.nat. Marcel Carsten Baunach and Dipl.-Ing. Heimo Hartlieb for the supervision and the opportunity to write this Master's Thesis in cooperation with Infineon Technologies AG. Thank you for sharing your expertise and experience in the field as well as the guidance during the creation of this work.

I also want to thank all my friends and colleagues I met during my studies or that accompanied me during this time. Studying would not have been the same without you and your support.

Furthermore, I especially want to thank Paul and Dominic. You helped me stay positive and sane over the emotional rollercoaster that was finding and creating a Master's Thesis.

Last but not least, I want to thank my family and parents. Thank you for your continuous support and for always letting me pursue my dreams.

# Contents

| 1. | Introduction                                     | 1          |

|----|--------------------------------------------------|------------|

|    | 1.1. Background                                  | 1          |

|    | 1.2. Objective and Motivation                    | 2          |

|    | 1.3. Related Work                                | 4          |

|    | 1.4. Outline                                     | 6          |

| 2. | Model Driven Architecture                        | 7          |

|    | 2.1. Model Driven Architecture Concept           | 7          |

|    | 2.2. Metagen and MetaRTL                         | 11         |

| 3. | Hard- and Software Assumptions and Constraints 1 | 13         |

|    | 3.1. Software Assumptions                        | 13         |

|    | 3.2. Hardware Assumptions and Constraints        | 14         |

|    | 3.3. Memory Partitioning and MPU Registers 1     | 15         |

| 4. | Extension to the CSR model 2                     | 22         |

|    | 4.1. CSR Template and Model of Design            | 23         |

|    | 4.2. MPU Extension                               | 29         |

| 5. | MDA based MPU generation 3                       | 33         |

|    | 5.1. MPU Placement in the RISC-V Model of Things | 33         |

|    | 5.2. MPU Template and Model of Design            | 35         |

|    |                                                  | <b>1</b> 8 |

| 6. | Evaluation and Results 5                         | 50         |

|    | 6.1. Behavioural Tests                           | 50         |

|    | 6.2. Resource Requirements                       | 55         |

|    | *                                                | 59         |

|    |                                                  | 59         |

|    |                                                  | 51         |

|    | Contents                                                                                                                |                             |

|----|-------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|    | 6.3.3. Results                                                                                                          | 64                          |

| 7. | Summary and Future Work                                                                                                 | 68                          |

| Bi | bliography                                                                                                              | 70                          |

| Α. | Behavioural Test Source CodeA.1. Kernel and Exception HandlerA.2. Exception Handling TestA.3. Configuration Change Test | <b>75</b><br>75<br>78<br>80 |

| B. | Application Performance Test Source CodeB.1. Dhrystone Source CodeB.2. Kernel and Exception HandlerB.3. MPU Management  | 100                         |

# List of Figures

| 1.1.  | SoC architecture overview of the 'RiVal' test chip     | 3  |

|-------|--------------------------------------------------------|----|

| 2.1.  | MDA as Y-Chart                                         | 8  |

| 2.2.  | MDA for hardware generation                            | 10 |

| 2.3.  | Metamodel of Metapad                                   | 11 |

| 3.1.  | MPU configuration CSR layout                           | 16 |

| 3.2.  | MPU address register format                            | 17 |

| 3.3.  | MPU configuration entry $(cfg)$ layout                 | 17 |

| 3.4.  | MPU control register format                            | 21 |

| 3.5.  | MPU status CSR layout                                  | 21 |

| 4.1.  | Extended UML diagram of the CSR classes                | 24 |

| 4.2.  | CSR RegisterFile Structure                             | 26 |

| 4.3.  | CSR Structure with no Bitfields                        | 27 |

| 4.4.  | CSR Structure with Bitfields                           | 28 |

| 4.5.  | Address Register Structure                             | 30 |

| 4.6.  | Configuration Register Bitfield Structure              | 31 |

| 5.1.  | Schematic metamodel of RISC-V core (MetaRISC) expanded |    |

|       | with MPU                                               | 34 |

| 5.2.  | UML diagram of the MPU classes                         | 35 |

| 5.3.  | MPU toplevel Structure                                 | 38 |

| 5.4.  | MPU Status Structure                                   | 39 |

| 5.5.  | MPU Decoder Structure                                  | 40 |

| 5.6.  | MPU TOR Structure                                      | 41 |

| 5.7.  | MPU NAPOT Structure                                    | 42 |

| 5.8.  | MPU Access Check Structure                             | 44 |

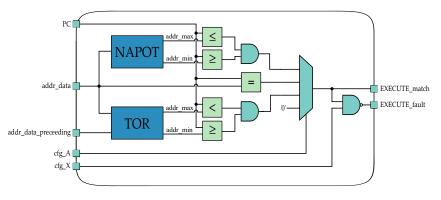

| 5.9.  | MPU Execute Access Structure                           | 45 |

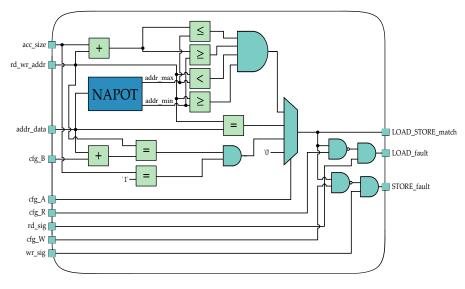

| 5.10. | . MPU Read/Write Access Structure                      | 46 |

| 1.1  |      |           |

|------|------|-----------|

| 1 15 | t ot | ures      |

|      |      | <br>ui CJ |

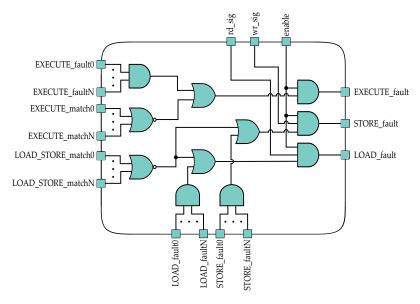

| 5.11. | MPU Fault Logic Structure                 | 47 |

|-------|-------------------------------------------|----|

| 6.1.  | Decoder test                              | 50 |

| 6.2.  | Waveform of the exception handling test   | 52 |

| 6.3.  | Waveform of the configuration change test | 54 |

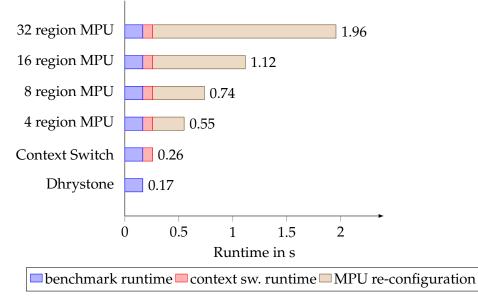

| 6.4.  | Dhrystone Benchmark runtimes              | 66 |

# **List of Tables**

| 'A' field encoding of configuration registers of MPU        | 18                                                                                                                                         |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| NAPOT range encoding in address and configuration registers |                                                                                                                                            |

| of MPU                                                      | 19                                                                                                                                         |

| 'B' field encoding of configuration registers of MPU        | 20                                                                                                                                         |

|                                                             |                                                                                                                                            |

| Timing report of MPU                                        | 55                                                                                                                                         |

| Cell report of MPU                                          | 57                                                                                                                                         |

| Area report of MPU                                          | 57                                                                                                                                         |

| Cell report of 'RiVal' w/wo MPU                             | 58                                                                                                                                         |

| Area report of 'RiVal' w/wo MPU                             | 58                                                                                                                                         |

| Dhrystone Benchmark Results                                 | 64                                                                                                                                         |

|                                                             | <ul> <li>'A' field encoding of configuration registers of MPU NAPOT range encoding in address and configuration registers of MPU</li></ul> |

# List of Listings

| 2.1. | MetaRTL example of a half adder structure |

|------|-------------------------------------------|

| 6.1. | MPU region structure                      |

| 6.2. | MPU configuration structure               |

| 6.3. | MPU configuration load function           |

|      | MPU address write function                |

| A.1. | kernel.c for behavioural tests            |

| A.2. | kernel.S                                  |

|      | exception_test.c                          |

| A.4. | change_test.c                             |

| B.1. | dhry_1.c                                  |

| B.2. | dhry_2.c                                  |

|      | kernel.c for Dhrystone                    |

| B.4. | kernel.S for Dhrystone                    |

| B.5. | mpu.h                                     |

| B.6. | mpu.c                                     |

# **Terms and Abbreviations**

- AHB Advanced High-performance Bus

- **API** application programming interface

- ASIC application specific integrated circuit

- **ASIL** automotive safety integrity level

- **AST** abstract syntax tree

- CIM computation independent model

- CISC complex instruction set computer

- CPU central processing unit

- **CSR** control status register

- ECU electronic control unit

- FPGA field programmable gate array

- HDL hardware description language

- HGL hardware generation language

- HW hardware

- IC integrated circuit

- **IDE** integrated development environment

- **IO** input/output

- **IoT** Internet-of-Things

- IP Intellectual Property

- **ISA** instruction set architecture

- ISO International Organization for Standardization

- LSB least significant bit

- LuT lookup table

- MDA model-driven architecture

- MMU memory management unit

- MoC Model of Computation

- MoD Model of Design

- MoT Model of Things

- MoV Model of View

Terms and Abbreviations

- MPU memory protection unit

- MSB most significant bit

- **NoC** network-on-chip

- OMG Object Management Group

- **OS** operating system

- PC program counter

- **PIM** platform independent model

- **PM** platform model

- PMA physical memory attribute

- PMP physical memory protection

- **PSM** platform specific model

- **PTS** powertrain and safety

- RAM random access memory

- **RISC** reduced instruction set computer

- **ROM** read only memory

- **RTL** register transfer level

- **RTOS** real time operating system

- SoC system-on-chip

- SW software

- TLB translation lookaside buffer

- **ToD** Template of Design

- ULP ultra-low power

- UML unified modelling language

- **UUT** unit under test

- XML extended modelling language

# 1. Introduction

### 1.1. Background

The number of transistors in integrated circuit (IC) is still steadily growing despite Moore's law being declared dying numerous times. According to a study by McKinsey in 2013, the number of transistors that can be manufactured increased by factor 100 per decade, while productivity is trailing behind with an increase by factor 20, leading to an ever-expanding 'design-productivity gap' [CP13]. Closing this gap is essential for all leading companies in the industry.

An approach commonly used in practice is 'IP-reuse'. Rather than a (re-)development from scratch, pre-existing blocks or whole systems are adapted or used without further modifications in the new system. Typical examples are RAM or ROM modules. This leads to an increase in productivity as well as possible lower development costs.

The evolution to the aforementioned method is complete system or code generation from abstract descriptions. This hardware generation approach was named as the next disruptive productivity improvement after IP-reuse by leading research groups in the industry [ES16]. This code and system generation approach is continuously evolving. At the same time, it was shown that a 20x increase in productivity in particular design tasks and 3x higher productivity during implementation from specification freeze to tape-out can be achieved [Eck+14]. A well-known example of the usage of code generation was the development of a hardware generation language (HGL) called Chisel by Bachrach et al. [Bac+12]. The approach taken by Chisel demonstrated a 10-fold code reduction compared to Verilog code.

This development has led to the creation of Infineon's hardware generation flow, replacing the manual hardware description language (HDL) generation with a high-level generator [Zap18] (see Chapter 2 for details).

With Infineon's approach to hardware generation, a wide variety of components and peripherals (e.g., RAM, ROM, interrupt controller, timer, etc.) have been implemented. The newest addition to this list is a fully verified RISC-V core [Sch16], enabling the creation of a fully customisable embedded systemon-chip (SoC). Logically, the next step for Infineon as a company is to evaluate if it is possible and feasible to develop chips using only its in-house generation methodology and have them manufactured in silicone.

This has lead to the creation of a test chip (i.e. a ISO 26262 compliant (as defined by the International Organization for Standardization (ISO) [ISO18]) SoC for the powertrain and safety (PTS) automotive market) featuring an open-source RISC-V ISA core called 'RiVal' (RISC-V test chip for ASIL compliant applications).

A study conducted prior to the creation of this thesis revealed that in order to allow for functional safety compliant software development the test chip is missing means to restrict accesses to memory and peripherals.

### 1.2. Objective and Motivation

Functional safety certification standards such as IEC 61508 and domain-specific derivatives such as ISO 26262 require that a failure in one application cannot influence the behaviour of another. This freedom of influence is especially important for safety-critical systems. Such systems often use shared-memory architectures, while convenient to use, resource sharing constitutes a problem when separation is required. For example, in such architectures without protection, each application can access and manipulate the data of other applications [HRK12].

To prevent processes or applications from interfering with each other, a common approach is to have a memory protection unit (MPU) or memory management unit (MMU) included in the central processing unit (CPU). MPUs are used to restrict access to predefined memory regions, which are usually configured by an operating system (OS). This region partitioning also partitions the software stack (e.g., in safety-related software and non-safety-related software) as required by functional safety standards [YN14]. The MPU then

#### 1. Introduction

verifies that the currently running process only accesses the address space it is eligible to access. Upon the context switch to another process, the OS updates the MPU configuration for the new process. Instead of the necessary configuration changes when using MPUs, MMUs can be used. In MMU based systems each process has its own virtual address space. When a process tries to access a virtual address, the MMU looks it up in the page table and translates it to a physical address. During context switches the OS only needs to write the page address of the next process to the MMU [HRK12].

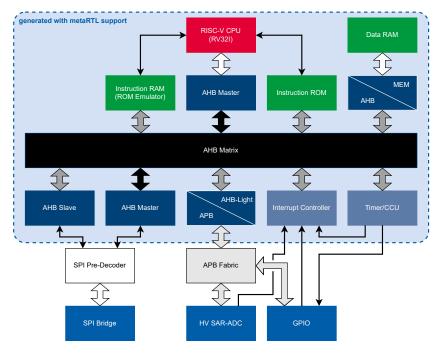

Figure 1.1.: SoC architecture overview of the 'RiVal' test chip

To allow process separation on the 'RiVal' platform, the objective of this thesis is to create a memory protection module (either an MMU or MPU) with the help of Infineon's hardware generation flow. A depiction of this platform can be seen in Figure 1.1. Each of the blocks depicted in this figure was created with metaRTL support (details regarding metaRTL can be found in Section 2.2). These blocks are called modules in Infineon's terminology. Therefore, the proposed unit in this thesis to protect these modules from illegal accesses is named module protection unit (MPU). In the context of this thesis, the terms memory protection unit and module protection unit are both abbreviated with MPU and used interchangeably.

MMUs offer greater flexibility and more access control features compared to MPUs. This increase in performance and flexibility, however, comes at the cost of an increase in area size. They require for their address translation a translation lookaside buffer (TLB) to cache table entries as well as MMU translation tables. To keep the increase in area size and therefore the cost of the future SoC at a minimum it was consequently decided to go with an MPU instead.

### 1.3. Related Work

Various authors leverage pre-existing protection units such as the MPU contained in ARM Cortex-M and Cortex-A [19a], or Infineon AURIX [19b] processors, to isolate and/or protect memory.

Pan and Parmer [PP19] propose an MxU to provide memory protection and allocation abstraction. This MxU enables both tightly-bounded execution and dynamic memory management of portable code on Internet-of-Things (IoT) devices. Lopriore [Lop16] presented a model of a protection system based on passwords for embedded systems. To reduce the overhead, the model leverages an MPU interposed between the processor and memory. The proposed system's focus is on system security and less on system safety. The authors of [FDM19] and [YN14] focus on memory protection mechanisms in real time operating systems (RTOSs) using the MMU in ARM processors. The presented approaches try to minimise the overhead imposed by context switches between tasks and to provide a hardware abstraction interface to the operating system. Rivera [Riv18] describes how an MPU can be used to provide runtime data protection and isolation within a single address space of an embedded system using bare-metal software written in Ada.

IO and peripheral virtualisation is another approach commonly used to encapsulate each device into its own address space. This virtualisation is used by the operating system to protect itself against buggy drivers or malicious devices. Malka et al. [Mal+15] showed an approach aimed at high-performance

#### 1. Introduction

IO devices such as 1000 Gbps network controllers. The described IOMMU only makes sense to be included in desktop computers or powerful ECUs since low-power embedded systems usually do not have such powerful peripheral devices. A lightweight IO virtualisation which leverages the MPU of ARM Cortex-M MCUs was described by Paci, Brunelli and Benini [PBB18]. Their virtualisation layer integrates with FreeRTOS and supports dynamic linking of new user code.

Ultra-low power (ULP) processors have special requirements when it comes to memory management and protection. Such ULP systems (e.g., sensor node networks) are often distributed heterogeneous multiprocessor systems with shared memory. The stringent low-power constraint often means that the processor design cannot be changed. For such networks an MMU or MPU can be used that is embedded in a network-on-chip (NoC). Multiple systems which use this approach have been proposed, most notably by Jang et al. [Jan+19], Porquet, Greiner and Schwarz [PGS11] and Hattendorf, Raabe and Knoll [HRK12]. For other devices that do not share memory (e.g., IoT devices, microcontrollers, etc.) a more classical approach of integrating an MPU or MMU into the processor can be taken. Stecklina, Langendoerfer and Menzel [SLM13] propose an MPU design for a low power 16-bit microcontroller (IHP430x) with only a 7% increase in total chip area. The small size, however, comes at the cost that it only supports up to 16 protection regions with limited flexibility in terms of usage of those regions and no execution protection. A similar approach was also taken by Lopriore [Lop14]. Shamani et al. [Sha+16] described a 64 region MMU that was integrated into the COFFEE core (i.e., a RISC processor developed by a group at Tampere University of Technology, Finland).

MMUs and MPUs have been of interest for both academia and industry for many years. As expected, a lot of architectures and implementations were proposed for different use cases and applications. Nevertheless, no publication was found on model-driven architecture (MDA) driven automated MPU generation during the creation of this work. Therefore, the proposed approach of this thesis is a novelty.

## 1.4. Outline

The remainder of this work is structured as follows: Chapter 2 describes the principles of model-driven architecture (MDA) and the metamodelling approach for hardware generation. In Chapter 3, the set constraints and assumptions made to the framework, hardware platform, and expected software usage are looked into.

The required changes to models, characteristics, and detailed descriptions of the implementations are discussed in Chapters 4 and 5. The former covers the extension to the control status register (CSR) model for the configuring of the new module, while the latter addresses the generation of the MPU.

The tests and evaluations of the implementation are discussed in Chapter 6. And finally, current limitations and possible enhancements as future work are looked into in Chapter 7.

# 2. Model Driven Architecture

### 2.1. Model Driven Architecture Concept

Model-driven architecture (MDA) is a vision coined by the Object Management Group (OMG), an international industrial consortium that creates and maintains specifications for software interoperability [MCF03]. The OMG also addresses future software design aiming to reduce the growing productivity gap (i.e., the available workforce versus the required workforce). In an MDA development flow, the primary artefacts throughout the development cycle are models [KM05]. By capturing these artefacts in a formalised way, automated processing, starting from very abstract specification all the way to the actual implementation, is enabled. This formalisation is called Metamodelling and is, therefore, an integral part of MDA. Doing so a way is provided to automatically transform and refine models into more specific and fine-grained models. Eventually, the most granular model is used to generate the intended target.

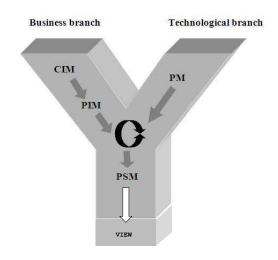

Figure 2.1 shows the three abstraction layers originally introduced in MDA, as well as a forth, PM, containing details of the target platform. These layers are defined in such a way that the target code is generated starting from a high-level human-elaborated definition (diagrams, models, etc.). The models on each of these layers are formalised by a metamodel they are an instance of. It should be noted that the metamodel is a model as well and is formalised by a so-called meta-metamodel. Metametamodels are used, for example, to generate metamodels. It is used to generate parts of the metamodelling approach applied to this thesis. Discussion and further details go beyond the scope of this work, as such, the interested reader is referred to [ES16]. The aforementioned layers are:

• Computation independent model (CIM) is very abstract and close to the

specification. Neither details about algorithm implementation nor architecture are considered.

- *Platform independent model (PIM)* avoids platform details, but already defines the architecture and therefore sets constraints for the implementation at a high level of abstraction.

- *Platform model (PM)* contains details of the target platform and the technology being used.

- *Platform specific model (PSM)* adds the utilised platform to the PIM and therefore, is platform-dependent and closest to the target code (also referred to as view). From this model, the view (i.e., e.g. target code) is generated.

Figure 2.1.: MDA as Y-Chart (reprinted from [ES16])

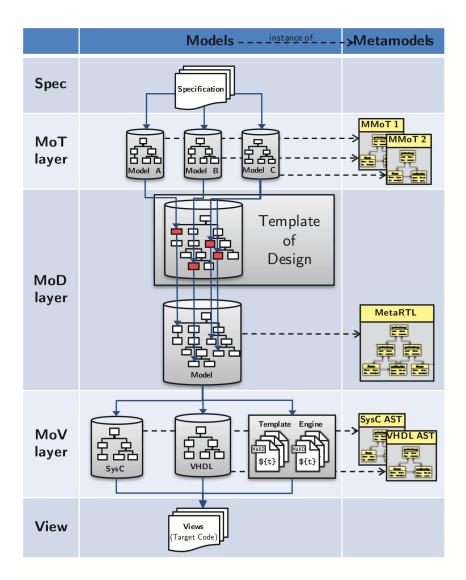

The vanilla MDA approach itself does not map that well to hardware design, which is why an adaptation for digital hardware generation was necessary. The adoption done by Ecker and Schreiner [ES16] follows the conceptual three-layer model of the already described MDA but enhances it to support hardware design. This is achieved by introducing new terms that describe the involved hardware related models, as seen in Figure 2.2. Again, every model on each layer is formalised by its corresponding metamodel.

• *Model of Things (MoT)* corresponds to the level of the CIM as it is intended to formally capture requirements and specifications. It describes

the functionality an implementation provides while leaving out implementation details such as system architecture. One example of an MoT is an instruction set architecture (ISA) of a CPU.

- *Model of Design (MoD)* corresponds to the level of the PIM and could be described as the core model of this methodology. Its goal is to define the architecture using the designer's terms. It models the intended functionality in the MoT. It should be noted that the MoD does not include information on how individual components are provided on a particular target platform. Doing so avoids the introduction of artefacts from simulation or synthesis. For example, the MoD of a memory subsystem will describe its components and characteristics of read and write ports; it will not, however, describe how those are implemented [Sch16].

- *Model of View (MoV)* corresponds to the level of the PSM since it is the least abstract model. It has a straight forward mapping to the target view. Implementation details such as target hardware dependencies or technologies from FPGAs or ASICs are added during the transformation from MoD to MoV. The MoV corresponds to a language-specific abstract syntax tree (AST), from which RTL files can be generated. Furthermore, it also implicitly determines the Model of Computation (MoC) as this is inherently defined by the target view.

Figure 2.2.: MDA for hardware generation (reprinted from [Sch16])

### 2.2. Metagen and MetaRTL

Metagen is Infineon's framework, implementing the three modelling layers of Metamodelling and code generation described in Section 2.1. The framework uses a UML subset to specify metamodels. These class diagrams are extended utilising XML-like specifications of alternatives, subsequently allowing for the specification of objects, attributes, and their relations between them. Metametamodels are used to relate and combine known metamodels. They are also used to generate metamodels from other formalisms such as XML schemata.

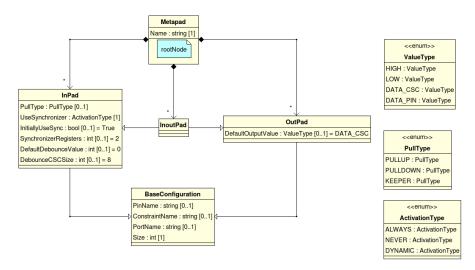

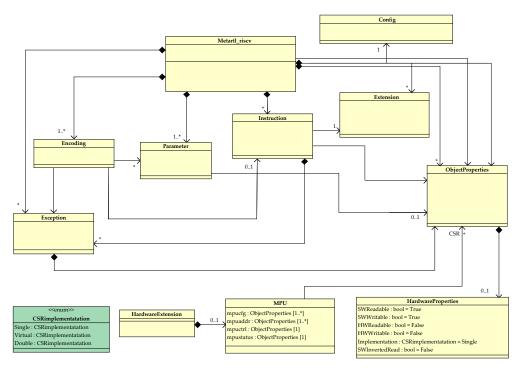

Figure 2.3.: Metamodel of Metapad (reprinted from [Pau18])

Metamodels can be captured both graphically and textual. The infrastructure generated by the Metagen framework supports the generation of extensible application programming interfaces (APIs), code generation for persistent storage, etc. As the framework is written entirely in Python, it takes advantage of numerous Python libraries and tools, including the Mako template engine for MoV generation [ES16]. An example MoT metamodel can be seen in Figure 2.3. This model shows the UML representation of Metapad (i.e., a model representing a pad).

MetaRTL is the metamodel developed to formalise the model of the MoD layer.

It provides a set of components (e.g., multiplexer, register, etc.), as well as methods of various types needed to generate RTL structures (the output can be either VHDL or Verilog), thus building a Template of Design (ToD). This ToD is part of MoD layer (as seen in Figure 2.2) consisting of a set of constructors for the MoD, where each constructor instantiates a specific component depending on the data and information contained in the MoT. It describes a blueprint on how the MoD can be built.

Infineon's implementation of the ToD is pure Python code, using a set of predefined packages and classes. Python environments give the ability to use numerous libraries, modern programming concepts, and to utilise Python IDEs. An example of a half adder structure written as part of a ToD can be seen in Listing 2.1.

```

class halfAdder(Structure):

1

def __init__(self, parent=None):

2

super(halfAdder, self).__init__(

3

4

5

{'Name': 'sum', 'Direction': 'OUT'},

6

{'Name': 'carry', 'Direction': 'OUT'}], parent=parent)

7

self['sum'].connect(LXOR(self['in0'], self['in1']))

8

self['carry'].connect(LAND(self['in0'], self['in1']))

9

```

Listing 2.1.: MetaRTL example of a half adder structure

# 3. Hard- and Software Assumptions and Constraints

Before any implementation can be written, constraints and assumptions to hardware as well as software need to be examined. These constraints and assumptions are analysed in this chapter.

### 3.1. Software Assumptions

The first assumption in regards to software is that all code is generally trusted, immutable, and not self-modifying. This also implies that there will be no possibility of binary changes during runtime. Those assumptions are easily justified when writing software in accordance with functional safety standard ISO 26262, as those requirements ease certification [ISO18]. The trusted code requirement can be achieved through code review, which is also commonly used as a best practice in software development.

The next assumption regards the platform (i.e., the hardware that software is run on) the software is created for. It is assumed that the platform is a baremetal embedded system. Effectively meaning that the software stack will be as slim as possible with no, or minimal, support of an operating system (OS) or real time operating system (RTOS). This assumption is made as during the creation of this thesis the SoCs developed at the respective Infineon department were mainly used as a hardware controller with a communication interface to a more powerful (automotive) electronic control unit (ECU).

Often, controllers in such systems only support a single privilege or execution mode, meaning that all software is run at the same (highest) privilege level. For security and safety reasons, however, it is assumed that multiple privilege

levels are available, e.g., machine and user mode. The official RISC-V definition can be found in [WA19a] and [WA19b]. Having multiple modes available allows the software flow to be split into multiple tasks or modes (e.g., boot, test, mission mode, etc.) all running at the same low privilege level (i.e., user-level), with only one task as central trusted entity running at a higher privilege level (i.e., machine level). Such a trusted entity could, for example, be the kernel of an (RT)OS. The kernel task's responsibility is to load the corresponding MPU configuration of a task during the task dispatching. These configurations are stored in a read-only memory section (e.g., read only memory (ROM)), thus being not modifiable. The other tasks (i.e., user-mode tasks) do not modify the currently loaded MPU themselves. This behaviour can be further enforced using hardware locking the currently loaded configuration. Once a configuration is locked in place only a task running at a higher privilege level (i.e., machine mode task) or a system reboot can unlock it. See Section 3.3 for details.

### 3.2. Hardware Assumptions and Constraints

In regards to hardware constraints, the most important one is that the MPU will be integrated seamlessly into the MetaRISC metamodel (as seen in Figure 5.1) and will be generated on demand with Infineon's MDA flow described in Chapter 2. This results in several implications. Most importantly, the MPU will be part of the CPU, and not connected as an external module via a bus interface such as Advanced High-performance Bus (AHB). The CPU design during the time of writing this thesis is a 5-stage pipelined CPU design that only supports the RV32I instruction set (version 2.1). Therefore, the CPU pipeline needs to be considered for the MPU placement. Furthermore, an exception unit has been built for the used RISC-V core by Zappia [Zap18], and thus the MPU should work with this exception unit. Finally, the number of possible MPU registers is constrained by the fact that they have to be mapped into the custom control status register (CSR) address space according to the RISC-V ISA (see [WA19b] for details).

The next assumptions effect the number of potential protection regions. Given the dynamic potential of the MDA flow, it is assumed that it would be beneficial to have a flexible number of possible MPU protection regions. Just as many as required for a specific application. When choosing the number of required regions it should be kept in mind that if an access control granularity of 1 byte is necessary, each 1 byte region needs its MPU region. The modules to and from which the access shall be controlled are assumed to be memory-mapped into the databus address space.

The MPU usage and specification should follow the physical memory protection (PMP) and physical memory attribute (PMA) specifications from the privileged RISC-V ISA specification (Version 1.11) (see [WA19b] for details) as closely as possible. Therefore, allowing for Intellectual Property (IP) reuse in case an MMU in accordance to the RISC-V ISA is needed in future. The MMU described by the RISC-V specification is powerful indeed. However, its complete implementation would result in an excessive overhead in terms of features and more important area size. This is because the implementation or usage of a single PMP or PMA register requires the implementation of all other registers as well. The inclusion of these registers is not generally necessary, but rather it is an explicit requirement from the RISC-V specification. The MMU described in the RISC-V specification also supports advanced features such as virtual memory, which is something that is hardly ever seen and used in bare-metal embedded systems and as such would waste precious chip area.

Lastly, at the time of writing this thesis, no other privilege modes other than machine mode of the core was available. The lack of privilege modes directly contradicts the software assumptions made in Section 3.1, leading to a restriction in possible use cases. Nevertheless, it was decided to go forward with the system at hand.

### 3.3. Memory Partitioning and MPU Registers

With the help of the MPU, the accessible memory range can be partitioned. Those partitions are called regions in the context of this thesis. To control the size and access permissions of those regions, there are two registers required: configuration and address registers.

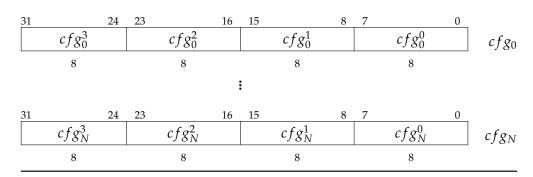

A single MPU configuration entry has a width of 8-bit, which is densely packed together with other configuration entries into single word-sized (32-bit) configuration registers ( $cfg_0$ - $cfg_N$ ). This minimises the required number of registers

and the required context-switch time. Each entry together with its corresponding address register forms a configuration tuple, which describes the size and access permission of a region. As described in Section 3.2, the number of registers is not fixed.<sup>1</sup> Instead, the number of possible and available configuration CSRs depends on the required granularity of the address space partitioning and use case for which the MPU shall be used for. Configuration and address registers are modelled in the MoT and the number of registers can be changed freely to accommodate the needs of the target application (see Chapter 4 for details regarding this process). A larger number of registers allows for smaller granularity, flexibility, and more flexible configuration. The layout (i.e., the placement within the CSR address space) of the configuration registers can be seen in Figure 3.1.

The reason to have a flexible number of regions is to accommodate for as many use cases as possible. Some applications might just want to prohibit a single address region from accessing input/output (IO) at all, while others need an elaborate access control scheme.

Figure 3.1.: MPU configuration CSR layout (adapted from [WA19b])

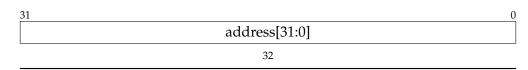

The address CSRs hold the base addresses of regions (i.e., the addresses where regions start). The address encoding used for those registers can be seen in Figure 3.2. This format is used for all address registers ( $addr_0-addr_N$ ).

<sup>&</sup>lt;sup>1</sup>The number of registers may only change during the design phase. The number of register cannot be modified after synthesis.

Figure 3.2.: MPU address register format (adapted from [WA19b])

The layout of each configuration entry (cfg) from Figure 3.1 is shown in Figure 3.3. The 'R' and 'W' bits indicate, when set, whether read (i.e., load instructions) or writes (i.e., store instructions) are permitted respectively. Logically this also implies that a cleared bit denies the corresponding access type. A set 'X' bit indicates that an instruction fetch is allowed from the corresponding memory region.

The other fields, 'A', 'B', and 'L' are described in the following sections.

| 7 | 6 5 | 4 3 | 2 | 1 | 0 |

|---|-----|-----|---|---|---|

| L | В   | А   | Х | W | R |

| 1 | 2   | 2   | 1 | 1 | 1 |

Figure 3.3.: MPU configuration entry (*cfg*) layout (adapted from [WA19b])

#### Address and Byte Ranges

As described in the paragraphs before, a region is determined by a configuration entry and its associated address register. The 'A' field in the MPU configuration entries encodes the address-matching mode of a region. This means that this field determines how the address register is interpreted (i.e., the start- and end address of a region and whether it is active). As shown in Table 3.1, there are five matching modes available in total.

The simplest case is A = 0. For this case, the entry is disabled, and no matching occurs (i.e., all accesses to this region are forbidden). The four other access modes are:

- 1. naturally aligned power-of-2 (NAPOT) region;

- 2. naturally aligned word (4 byte) region (NA4);

- 3. top boundary of an arbitrary range (TOR) (available only for execution control); and

- 4. Byte Mode, which replaces the TOR mode for read and write accesses.

| Α | Name   | Description                                    |

|---|--------|------------------------------------------------|

| 0 | OFF    | Disabled region                                |

| 1 | BM/TOR | Byte Mode (for R/W)/Top of Range (for X)       |

| 2 | NA4    | Naturally aligned word (4 byte) region         |

| 3 | NAPOT  | Naturally aligned $2^n$ byte region, $n \ge 3$ |

Table 3.1.: 'A' field encoding of configuration registers of MPU (adapted from [WA19b])

A more detailed description of each mode is given in the following paragraphs.

These modes support a granularity down to four bytes for instruction memory regions, and down to 1 byte for data memory regions. It should be noted that the assumed four-byte granularity of instruction memory regions is inconsistent with the compressed instruction set specification, which supports 16 bit granularity [WA19a]. However, as mentioned in Section 3.2, the instruction format this work is based on is the RV32I format. In this format, each instruction is exactly 32 bit wide, therefore fulfilling the assumption.

The size of a naturally aligned power-of-2 (NAPOT) region is encoded in the low-order bits (i.e., the least significant bits (LSBs)) of the associated address register. By fixing the LSBs, all possible address variations fall into the specified range. Which means that the address stored in the address register is the encoded start address (i.e., the lowest possible address) of a region. The encoding can be seen in Table 3.2.

It should be pointed out, that this is only possible because the address encoded in the address registers corresponds to bits 33 to 2 of an address. Meaning that the effective address (i.e., the resulting address) will be obtained by logically left-shifting the encoded address by two. The value to store in the address register for a specific region can be calculated: given the start address of the region *a*, and the supposed size of the region *s*, the value *v* to store is

$$v = (a + \frac{s}{2}) \gg 2$$

where  $\gg$  denotes a logical right shift.

For regions that use the top of range (TOR) mode, the address range is determined with the associated address register which contains the top of an address range (i.e., the highest address), and the preceding address register which contains the bottom of an address range (i.e., the lowest address). If the 'A' field of a configuration entry *i* is set to TOR, an address *x* will fall within the determined range when  $addr_{i-1} \le x < addr_i$ . In case there is no preceding register available, 0 will be used for the lower bound, thus, an address *x* will fall into the region when  $x < addr_0$ .

| addr cfg.A |       | Match type and size               |  |  |

|------------|-------|-----------------------------------|--|--|

| xxxxxxxx   | NA4   | 4-byte NAPOT range                |  |  |

| xxxxxxx0   | NAPOT | 8-byte NAPOT range                |  |  |

| xxxxxx01   | NAPOT | 16-byte NAPOT range               |  |  |

| xxxxx011   | NAPOT | 32-byte NAPOT range               |  |  |

| xx011111   | NAPOT | 2 <sup>32</sup> -byte NAPOT range |  |  |

Table 3.2.: NAPOT range encoding in address and configuration registers of MPU (adapted from [WA19b])

The easiest mode to understand is the naturally aligned word (4 byte) (NA4) mode. When the 'A' field of a configuration entry *i* is set up to use this mode an address *x* falls within the range, if and only if, the address matches the value of the associated address register. Formally fulfilling the following requirement  $x \stackrel{!}{=} addr_i$ .

For regions on which load and store instructions could be executed (i.e., data memory), TOR mode is replaced by Byte Mode (BM). In this mode, the address is matched as an NA4 region; however, the granularity is lowered to byte accuracy. This lower granularity is achieved with the 'B' field in the configuration entries. The encoding of the 'B' field can be seen in Table 3.3.

When the 'A' field of a configuration entry *i* is set to Byte Mode then the entry matches any address *x* with the value *b* from the 'B' field such that  $x = addr_i + b$ . This approach requires unaligned data memory access support, which was available during the creation of this thesis. Furthermore, it should be pointed out that separate configuration tuples are required for each region to be controlled in BM.

| B | Field   | Description                 |

|---|---------|-----------------------------|

| 0 | [7:0]   | Access to bit 7 down to 0   |

| 1 | [15:8]  | Access to bit 15 down to 8  |

| 2 | [23:16] | Access to bit 23 down to 16 |

| 3 | [31:24] | Access to bit 31 down to 24 |

3. Hard- and Software Assumptions and Constraints

Table 3.3.: 'B' field encoding of configuration registers of MPU

#### **Register locking**

The 'L' bit indicates whether the configuration entry is locked, and thus writes to the configuration (e.g.,  $cfg_0$ ) and to the associated address register (e.g.,  $addr_0$ ) are ignored. When entries are locked, they can only be unlocked through a system reset or reboot.

### **Priority and Matching Logic**

All configuration tuples are not prioritised meaning that all tuples contribute to whether an access succeeds or fails. For an access to succeed, the access address must entirely fall within the range of at least one configured region. Otherwise, the access will fail, regardless of the 'L', 'R', etc. bits. This behaviour can be observed, for example, in case of operations that exceed the protected region, e.g., a half-word (16 bit) read from a Byte Mode protected region which only allows single byte accesses.

If a region is successfully matched, then the 'L', 'R', 'W', and 'X' bits determine whether the access is granted (success) or denied (fail). In case no entry is matched, but at least one region is implemented, the access will always result in a fail. However, in case there are two conflicting matching regions (e.g., one allowing stores and the other one does not) the access will succeed.

Failed accesses generate the respective exception (load, store, or instruction access fault) which must be handled in software through, e.g., an exception handler.

### **MPU Operation and Status**

The MPU operation can be controlled by setting or clearing the 'E' bit of the *mpuctrl* register (the layout can be seen in Figure 3.4). No fault will be generated as long as this bit is not set. It should be noted that this bit should be cleared before attempting to change the currently loaded configuration.

| 31       | 1 | 0 |

|----------|---|---|

| reserved |   | Е |

| 31       |   | 1 |

| Figure 3.4.: MPU contro | l register format |

|-------------------------|-------------------|

|-------------------------|-------------------|

Figure 3.5 shows the layout of the *mpustatus* register. In this register, the number of currently unconfigured and overall available regions (i.e., the number of configuration tuples) is encoded. This information could be used to ease configuration changes during a context switch.

| 31 16        | 15 0         |

|--------------|--------------|

| availregions | totalregions |

| 16           | 16           |

Figure 3.5.: MPU status CSR layout

# 4. Extension to the CSR model

In the previous chapters, hard- and software assumptions of a module protection unit and the concept of Infineon's HDL generator 'metaRTL' was presented. This chapter focuses on the extension of the CSR model and implementation. Previous work already created a metamodel of CSRs, which made these registers visible in the MoT of the CPU core itself. Prior to the work of Zappia [Zap18] the CSRs were not modelled and directly specified in the implementation, i.e., the MoD layer of the core. While this contribution was sufficient for exception handling, it does not provide the flexibility required by the concept described in Chapter 3. To accommodate the dynamic nature during the creation of the protection unit, several changes and additions where necessary. The focus of this chapter is the implementation of these changes.

To make use of the metaRTL HDL generation flow, the specification (i.e., the metamodel) has to be changed. As described in Section 2.1, the ToD consists of multiple Python scripts which transform the MoT into the MoD. Starting from the MoD, the remaining generation flow is executed automatically, and HDL code is subsequently output, for example, VHDL or Verilog code. This code can then, in turn, be synthesised, and either run on a simulation testbench or a field programmable gate array (FPGA).

For the sake of clarity, the actual Python code in this chapter will largely be omitted, focusing on the structure, while still giving an overview of the CSR implementation and highlighting the changes made.

The remainder of this chapter is split into two parts: 1. in Section 4.1 an overview to the CSR metamodel, the ToD, and thus the implemented classes, is given. Their corresponding hardware architecture is given as well, and; 2. the MPU specific changes are discussed in Section 4.2.

# 4.1. CSR Template and Model of Design

The CSRs are defined in the MoT of the CPU. They were modelled using the 'StateObject' reference to the 'ObjectProperties' class of the CPU core metamodel. See Figure 5.1 [p. 34] in the following chapter for a depiction.

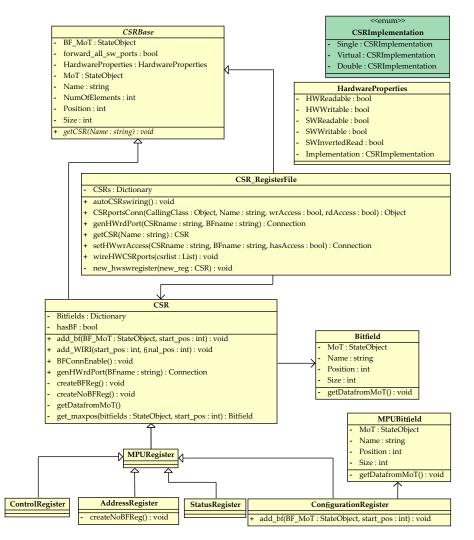

The actual implementation of the CSRs is specified as discussed above in the Template of Design (ToD). The in the generation involved classes of the MoD in the form of a unified modelling language (UML) diagram is illustrated in Figure 4.1. This section gives an overview of the ToD and a description of each class involved.

## **CSRBase**

This class serves, as the name suggests, the purpose of having a default template for CSR related classes. By inheriting the class attributes, code duplication is reduced.

All CSR related information from the MoT and a reference to the specific MoT instance are stored in variables. Furthermore, an abstract function *getCSR* provides a standardised interface of accessing the underlying CSR structures.

This base class behaviour could not be achieved with the 'CSR' class described later in this section, because of the extended functionality (e.g., the generation of hardware structures) of the aforementioned class.

#### **CSR\_RegisterFile**

The 'CSR\_RegisterFile' class is a structural class (i.e., a class that generates hardware). It reads the MoT and generates CSR instances accordingly. Each CSR object is saved into a dictionary and accessible through the methods provided:

• *autoCSRswiring()* hardwires all unconnected hardware ports of all CSRs to '0'.

Figure 4.1.: Extended UML diagram of the CSR classes (adapted from [Zap18])

• *CSRportsConn()* generates external ports connected to the hardware ports of the CSR, as they are not generated by default (only the software access ports are). This method generates the hardware read, write, and enable ports for both specified CSR or Bitfield. The generated ports are

subsequently also connected with the ports of the CSR or Bitfield. By specifying the 'CallingClass' argument, this method's behaviour is the same as just described, but the ports are generated in the 'CallingClass'.

- *genHWrdPort()* helper function of *CSRportsConn()* which creates the hardware read ports.

- *getCSR()* overrides the method from the base class and returns the specific CSR associated to its name.

- setHWwrAccess() helper function of wireHWCSRports() which creates the hardware write and enable ports or connects the underlying ports of the CSR to '0' in case 'hasAccess' is not specified.

- wireHWCSRports() this function creates and connects the required hardware ports to connect them to an external unit (e.g., the exception unit).

- *new\_hwswregister*: internally connects the instantiated registers depending on the in the MoT specified access permissions [Zap18].

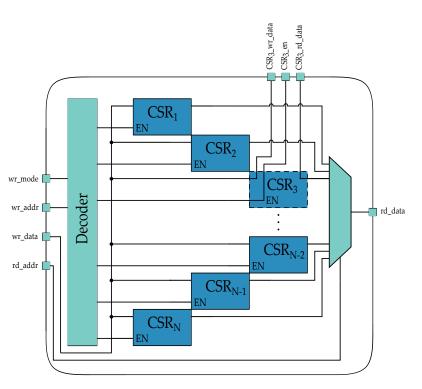

Figure 4.2 shows the main components of the CSR register file structure (i.e., the equivalent digital logic circuit).<sup>1</sup> The focus of this particular figure lies on the visualisation of the components and ports required to accommodate software (SW) accesses; therefore, the hardware (HW) access ports were omitted.

The main component of this structure is the decoder which takes the write mode ( $wr\_mode$ ) and write address ( $wr\_addr$ ) to set the enable signal of the specified CSR to HIGH. When the enable signal is set, the data from the write data ( $wr\_data$ ) port is written to the CSR. Similarly, data can be read from a particular CSR by setting the read address ( $rd\_addr$ ) to a valid value. Both read and write addresses are checked for validity in the lookup table (LuT) of the decoder during the 'decode' stage of the pipeline. The CSR's content can then be read from the read data ( $rd\_data$ ) port [Zap18].

The connections between instantiated registers, decoder, and read multiplexer are created if the access permissions were granted in the MoT. Currently, violations of these permissions will not cause any fault that is forwarded to the *error* port (omitted in Figure 4.2 as it is unused), because the CSRs implemented as 'Single' are registers specified in the privileged RISC-V ISA specification by Waterman and Asanović [WA19b], and as such defined as 'write any, read legal (WARL)'. Meaning that all write operations are allowed, although they may

<sup>&</sup>lt;sup>1</sup>All registers are implemented as clocked and rising edge sensitive; the clock signal input, however, was omitted in all depictions following to improve readability.

Figure 4.2.: CSR RegisterFile Structure

not necessarily modify any content, and any read operation will return a legal value. Similarly, illegal instructions that occur on 'Virtual' CSRs of the MPU follow the same behaviour.

## **CSR**

In this class, all hardware components are generated during instantiation, and it holds all CSR specific information defined in the MoT. The hardware components are generated with two methods:

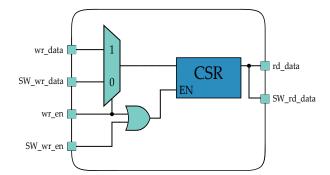

- *createNoBFReg()* is called when there are no bitfields defined in the MoT generating the structure visualised in Figure 4.3.

- *createBFReg()* is called when there are bitfields defined in the MoT. It calls the *addBF()* and *addWIRI()* ('write ignored, read ignored (WIRI)') methods

to instantiate and generate a new Bitfield class or a permanently disabled register respectively. Thus, the overall register structure will consist of multiple smaller internal registers. This can be seen in Figure 4.4 [Zap18].

Figure 4.3.: CSR Structure with no Bitfields (adapted from [Zap18])

If there are no bitfields defined in the MoT the *createNoBFReg()* method is called, which generates the structure shown in Figure 4.3.

The structure is quite simple as it consists only of a few components. The input multiplexer selects between the write signal (*wr\_data*) of the CPU internal logic and the write signal of the software (*SW\_wr\_data*) (i.e., access through CSR instructions defined in the ISA). The register is written to if either the hardware enable signal (*wr\_en*) or the software enable signal (*SW\_wr\_en*) is HIGH. However, as the selector signal of the multiplexer is connected to *wr\_en* the HW access is prioritised over the SW access in case both enable signals are active [Zap18].

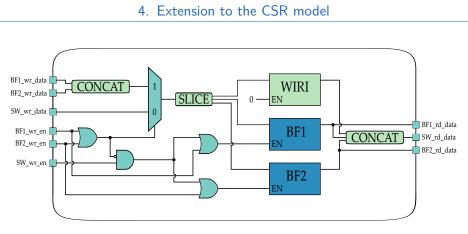

If there are bitfields defined in the MoT the *createBFRef()* method is called. Internally, this method calls the *addBF()* and *addWIRI()* methods respectively, dependent on the order the bitfields were specified in the MoT. The overall register structure will consist of multiple smaller internal registers which can be accessed individually.

An example of a resulting structure is shown in Figure 4.4. For each bitfield, one write and read data port (\*\_*wr\_data* and \*\_*rd\_data*) as well as an enable port (\*\_*wr\_en*) is created for HW accesses. The hardware data ports are concatenated and passed to the input multiplexer, similarly to the CSR without bitfields. The output from the input multiplexer is split so that only the corresponding input data is passed the underlying bitfield register. To facilitate a SW read of

Figure 4.4.: CSR Structure with Bitfields (adapted from [Zap18])

all bitfields at once, the output of all bitfields is concatenated, and its output connected to the SW read port (*SW\_rd\_data*).

The hardware write priority is achieved with an 'OR' reduction of all HW enable signals that are connected to a negated port of an 'AND' gate. The other port of said gate is connected to the software enable port. This connection makes sure that software access will only happen if there is currently no ongoing hardware access. The signal selection also uses the output of the 'OR' gate. The underlying bitfields are either enabled all simultaneously through a SW access, or individually with a HW access.

In case some bitfields are left undefined in the MoT a WIRI register is generated automatically. Such a register has its enable port hardwired to '0', therefore disabling it permanently [Zap18].

#### **HardwareProperties**

This class holds the hardware properties for each CSR.

As seen in the UML diagram in Figure 4.1 these are: access permissions (HW/SW read and write permissions), and implementation mode ('Single', 'Virtual', and 'Double').

'Single' is the default implementation mode, in which case the CSR is instantiated in place as part of the register file structure. This implementation mode is visualised with solid line borders of the CSRs in Figure 4.2. When this mode is used, accesses to the CSR can be made as described previously. All registers of the exception unit are implemented using this mode (as seen in [Zap18]). 'Virtual' is functionally identical to 'Single' in terms of accesses; however, the actual instantiation of the CSR is done externally (i.e., the register is part of some other structure). When this mode is used, the read, write, and enable ports are created on the top level of the register file structure. The ports will be automatically connected externally during the pipeline creation. For this to happen, the ports at the register file top level must have the same name as the corresponding ports on the external structure. Internally, these ports are connected to decoder and read de-multiplexer the same way 'Single' registers are. This extension to implementation modes allows having various CSR instances (of multiple CSR classes), which, for example, could be structured differently internally than the default implementation. This way, a backwards-compatible interface is providing allowing accesses to happen as if they were 'Single' CSRs. This implementation mode was used for all MPU registers and can be seen in Figure 4.2 of CSR<sub>3</sub> (the register with a slotted line).

In 'Double' mode, a CSR bus interface is added to the register file top level. All accesses to and from an address range specified in the MoT are routed to this interface. This approach has similar benefits as the 'Virtual' mode. One advantage of this mode is that the number of ports is reduced because access ports are only added for address ranges instead of individual registers. However, the structure with the counterpart bus interface and CSR instances needs to implement a decoder, because the outgoing bus interface at the register file structure is connected directly to all in-ports (*wr\_mode, wr\_addr,* etc.). This implementation mode is not shown in Figure 4.2, as it was not used for this thesis. It was, nevertheless, created for possible future work.

The importance of the access permissions was already explained previously in the CSR register file class description; as such, it will be left out from this section.

# 4.2. MPU Extension

This section is about the required extensions to the CSR ToD to ease the hardware implementation of the requirements described in Chapter 3. As in the previous section, this section gives an overview of the ToD and a description of each class involved.

## **MPURegister**

The 'MPURegister' class is used as a parent class for all inheriting classes ('ConfigurationRegister', 'AddressRegister', etc.). It has the same functions and attributes as its parent. The only difference being the initialization routine, as this class does not differentiate between various implementation modes. This can be left out because it assumed that all registers are instantiated as 'Virtual'.

#### **AddressRegister**

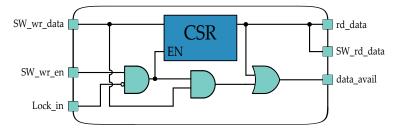

This class implements, as the name implies, a register that holds a 32-bit address. It uses the same structure and layout as regular CSRs without bitfields but has an extra port for a lock signal. This signal is input from the lock field ('L' field) from the corresponding configuration, as explained in Section 3.3.

Figure 4.5.: Address Register Structure

As seen in Figure 4.5, this locking mechanism is implemented by connecting the lock signal to a negated in-port of an 'AND' gate. The other input of this gate is connected to the 'OR' reduction of both enable ports, and the gate's output is connected to the enable port of the register. That way, the register will be permanently disabled when the lock signal is set to HIGH. This locked state stays active until the lock signal goes back to LOW.

Furthermore, a port which shows whether data will be written to or is already available was added as well (*data\_avail*). This port is used as input for the MPU status register, allowing atomic updates.

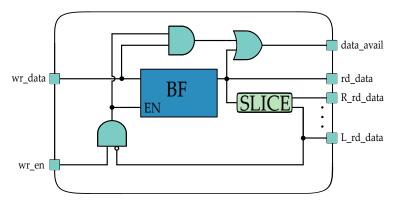

## ConfigurationRegister

The in Section 3.3 described configuration entries are encoded in the class 'ConfigurationRegister'. This class is a variation of a CSR with bifields, as visualised in Figure 4.6. It should be noted that said figure only shows the structure of a single underlying bitfield, a fully filled register can hold up to four of such configurations in parallel.

Figure 4.6.: Configuration Register Bitfield Structure

One modification to the configuration entry register ('Bitfield' class) was necessary to implement the locking mechanism. As soon as the 'L' bit is set, the register will lock itself automatically. This is done by permanently disabling the enable port of the register with the help of an 'AND' gate. A negated port is connected to the lock bit, and the other port connected to write enable signal ( $wr_en$ ). The class that implements this change is called 'MPUBitfield'. This class is not a generalisation of the 'Bitfield' class, because it would have caused errors during the instantiation, because of an inheritance problem.

Similarly, to the 'AddressRegister', a *data\_avail* port was added as well, for the same reason already described.

#### **StatusRegister**

This class is used to store the current and total available number of configurable MPU regions. No specific changes were made in terms of structure, as such a

figure was omitted from this thesis.

# ControlRegister

This class is used to control the MPU operation, i.e., whether it is enabled or not. The underlying structure uses a default CSR with bitfields layout.

# 5. MDA based MPU generation

In the previous chapters, the model-driven architecture (MDA) and the required extension to the CSR model were presented. This chapter focuses on the generation of an MPU within Infineon's MDA framework (see Section 2.2 for details).

# 5.1. MPU Placement in the RISC-V Model of Things

In this section, an overview of the core metamodel used for this work is given. The original metamodel by Schreiner [Sch16] was extended with a new node ('MPU') to allow for the modelling of an MPU. This extension is the centrepiece of the subsequent sections and will be described thoroughly. All other parts of the model will be described just briefly, as they are out of the scope of this thesis. A very detailed description and discussion of these parts can be found in [Sch16].

Figure 5.1 shows a UML class diagram of the CPU metamodel. This model can be split into five component groups. The added node 'MPU' will be discussed in more detail in the paragraphs following. The other aforementioned component groups are:

- *Architectural State* contains all stateful elements of the CPU that a compiler needs to be aware of (e.g., registers, memories, and flags).

- *Encoding Tree* 'describes how individual instructions are encoded in the instruction words the CPU can execute. This also includes the description of how parameters such as register addresses and immediate operands are encoded in the instruction word.' [Sch16, p. 46]

- *Instruction* models the instructions and the instruction behaviour, i.e., how the architectural state of the CPU is influenced by instructions.

• *Exception Node* models which exceptions can occur and how those influence the architectural state of the CPU [Zap18].

Figure 5.1.: Schematic metamodel of RISC-V core (MetaRISC) expanded with MPU

As depicted in Figure 5.1 the 'MPU' node was modelled as part of a 'Hard-wareExtension' in such a way that the system may, or may not, have exactly one MPU. The MPU model itself only consists of the registers described in Section 3.3. As these registers are implemented as CSRs, a reference between the MPU and the 'ObjectProperties' class is necessary to keep the resulting metamodel (the MoT) consistent.

# 5.2. MPU Template and Model of Design

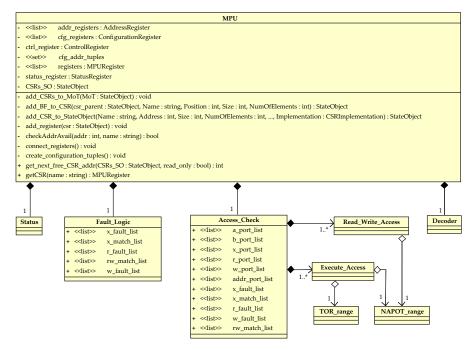

The MPU implementation is specified, similarly to the CSRs described in Section 4.1, in the Template of Design (ToD). A UML diagram of the MPU related classes of the MoD is shown in Figure 5.2. The implementation is specified in the ToD that is part of the MoD layer, as described in Section 2.1. This section gives an overview of how the ToD of the MPU is constructed and a description of each class involved.

For the sake of clarity, in this section the actual Python code (i.e., the code describing the ToD) will be omitted, focusing on the resulting hardware structures.

Figure 5.2.: UML diagram of the MPU classes

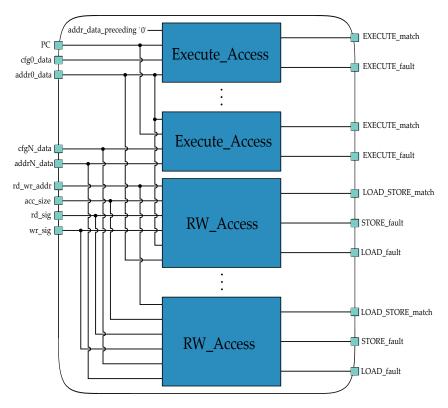

# MPU

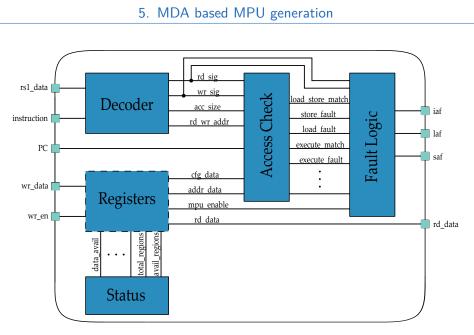

The 'MPU' class is a structural class (i.e., a class that generates hardware) which reads the MoT and generates the MPU instance accordingly. The resulting structure is the MPU toplevel, whose ports are connected to the exception unit and placed within the CPU pipeline (see Section 5.3 for details). A depiction of the MPU toplevel structure is shown in Figure 5.3.

The responsibility of this class is, apart from serving as MPU toplevel, to instantiate the required (sub-)structures as well as to modify the core MoT. With this modification, the MPU registers are added as CSRs. Finally, the MPU has to function as a CSR manager. A number of lists, tuples, and dictionaries are used to keep track of the instantiated structures and their ports. These objects are then used by both the MPU class itself and its child components to, for example, create connections between said ports. This is achieved with the following methods:

- *getCSR()* overrides the method from the CSR base class (see Section 4.1 for details), and returns the specific MPU-CSR associated to its name.

- add\_CSRs\_to\_MoT() adds, as the name implies, the specified CSRs from the MPU to the MoT instance. This function does this by reading the register information from the MoT. The register data from the MoT includes the register name and size. The CSRs are then added depending on the data read. For example, a configuration register in the MoT with size 3 and the name 'mpucfg0', will be added as CSR with the specified name and its three configuration entries are added as bitfields.

- add\_BF\_to\_CSR() is a helper function of add\_CSRs\_to\_MoT(). It adds the required bitfields to a CSR. For example, the bitfields of a configuration entry ('A', 'B', 'R', 'W', etc.).

- get\_next\_free\_CSR\_addr() another helper function of add\_CSRs\_to\_MoT(). This function returns the next available address (i.e., an address where no other CSR has been placed) from the custom CSR address range as specified in the privileged RISC-V ISA specification by Waterman and Asanović [WA19b].

- add\_CSR\_to\_StateObject() this function is used by add\_CSRs\_to\_MoT() to add a specified CSR to the MoT. As described in Section 4.1 the CSRs are modelled as StateObjects, therefore the MPU registers have to be added

to the CSR StateObject.

- *add\_register()* instantiates the register structures. The reference to each register instance is saved to the corresponding list. For example, an address register instance is saved to the *addr\_registers* list.

- checkAddrAvail() this function is used by add\_CSR\_to\_StateObject() to verify that there is no address collision (i.e., multiple CSRs at the same address).

- create\_configuration\_tuples() generates a list of tuples in the form

<cfg<sub>0</sub>, addr<sub>0</sub>>, ..., <cfg<sub>N</sub>, addr<sub>N</sub>> to easily find the corresponding address register to a configuration entry (and vice versa). This list is used extensively throughout the generation process of the MPU.

- *connect\_registers()* this function has multiple responsibilities. Most importantly it sets up the required connection between the registers, e.g., the 'L'-bit of a configuration entry to the lock port of the corresponding address registers.

Furthermore, it connects the unused hardware ports of the CSR instances to '0' in order to permanently disabling them. This is necessary because some hardware ports (e.g.,  $hw_wr$ ) are a byproduct of the CSR instantiation. These ports are unused but need to be connected because unconnected ports would generate errors during synthesis.

Lastly, this function also is in charge to make the connections between the other instantiated components, e.g. the connection between the fault logic and access check component.

Figure 5.3 shows an overview of all instantiated components that are generated by the MPU. Each of these components will be described in detail in the sections following. It should be noted that the registers (the block with the dashed line) are not single entities (as shown in Figure 5.3), but rather multiple individual structures. They are depicted that way because it helps to clean up the figure, and they do not add any necessary additional information to the overall picture.

As depicted in Figure 5.3, several external ports are added during the generation of the MPU. The most important ports are the register source data (*rs1\_data*), the instruction currently being executed (*instruction*), and the address of the instruction currently being fetched from (*PC*, i.e., the program counter (PC)). The data from those ports is taken in and evaluated by the underlying instantiated components. These components then generate fault

Figure 5.3.: MPU Top Structure

signals in case unallowed accesses occur. The resulting fault signals are connected to the respective fault ports (instruction access fault: *iaf*, load access fault: *laf*, and store access fault: *saf*).

The remaining ports are necessary to allow accesses to and from the registers. Each register has its own read data ( $rd_data$ ), write data ( $wr_data$ ), and enable ( $wr_en$ ) port. Those ports are then connected to the CSR\_RegisterFile structure described in Section 4.1.

#### **Status**

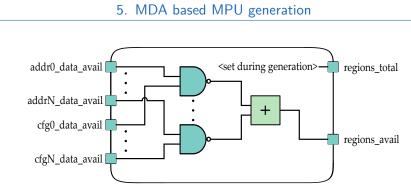

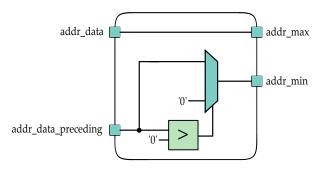

This class encodes the number of possible protection regions as well as how many of those are currently available (i.e., unset regions). The output ports of the corresponding structure (*regions\_avail* and *regions\_total*) are connected to the write data ports of the equally named bitfields that are part of the 'mpustatus' register. A depiction of the resulting structure can be seen in Figure 5.4.

The total number possible protection regions (*regions\_total*) is set to a literal (i.e., a constant) during the generation of the MPU. The currently unset regions

Figure 5.4.: MPU Status Structure

(*regions\_avail*) are updated every clock cycle. The available data ports from the address and configuration registers (*addr\*\_data\_avail* and *cfg\*\_data\_avail*) are used as input to 'NAND' gates. Each configuration tuple (address and configuration) has its gate. A region is only used when both configuration and address register are set to a value greater zero. Which means, in turn, that a region is unset if the opposite is true. Therefore, a negated 'AND' or 'NAND' gate has to be used. The output of these gates is then added. The sum is the number of regions that are currently unset.

#### Decoder

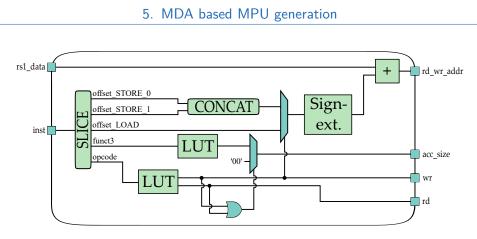

The decoder is used to decode the current instruction and register data to output whether relevant access (read or write) is occurring and its effective address. A depiction of the generated structure to do this can be seen in Figure 5.5.

The main component of the decoder is the slicer which separates the instruction applied to its port (*inst*) into individual signals.

The load and store ports (*rd* and *wr*) are set to HIGH in case the opcode is set to the corresponding value. This is done with the help of a LuT. The load and store signals are used to determine whether the access size (*acc\_size*) is output or set to zero. Similarly to the read and write signals a LuT is used to get the current access size encoded in the instruction 'funct3' (as defined in the unprivileged RISC-V ISA specification by Waterman and Asanović [WA19a]). The access size is only yielded when either a load or store occurs. As such, those two signals are used as input to an 'OR' gate. The output of this gate is used as a select signal of the multiplexer which switches between the value of

Figure 5.5.: MPU Decoder Structure

the LuT and a default value (i.e., '0').

The write signal is also used as a select signal of the offset multiplexer to select the correct offset. The address offset in case of a store instruction needs to be concatenated first since it is not encoded continuously within the instruction. After the selection process, a sign extension in accordance with the unprivileged RISC-V ISA specification is required in case bit 11 of the offset is set to '1'. In any case, the 12-bit offset is extended to a 32-bit value which is added to the value applied to the register data port ( $rs1_data$ ). The output of this operation is the effective access address. This output is directly connected to the output port ( $rd_wr_addr$ ).

The previously described structure is only required for the decoding of load or store (i.e., read or write) instructions, and not for the address of the current instruction. The effective access address of execute accesses is kept track with the PC and as such does not need further processing.

# TOR\_range

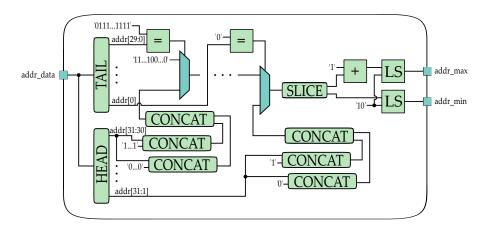

The 'TOR\_range' class generates the structure for the top boundary of an arbitrary range (TOR) address matching mode described in Section 3.3. As seen in the UML class diagram in Figure 5.2, this class is instantiated only as part of the 'Execute\_Access' class, since this mode is only supported for execution control. A depiction of the TOR structure can be seen in Figure 5.6.

Figure 5.6.: MPU TOR Structure