Markus Feldbacher, BSc

### Design and Implementation of Sensor-based Covert Channels

### Master's Thesis to achieve the university degree of Diplom-Ingenieur

Master's degree programme: Computer Science

submitted to

### Graz University of Technology

Supervisor Ass.Prof. Dipl.-Ing. Dr.techn. Steger Christian

Institute of Technical Informatics

Graz, May 2020

### Affidavit

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present master's thesis.

Date

Signature

### Abstract

Every year, the number of devices that are connected to the Internet rises significantly, especially in the so-called Internet of Things- and Smart Home sector. Most of those devices have some kind of sensor embedded and applications range from environmental monitoring, over healthcare, to industrial applications. This thesis presents multiple concepts that exploit unsecured embedded sensors to build covert channels. These concepts range from very simple ideas, such as abusing unused sensor register to transfer data, to more complex covert channels that are often hard to distinguish from normal user behavior and therefore much harder to detect. To emphasize the significance of the issue, furthermore, two additional approaches are introduced that exploit the sensor stack of Android, a very common operating system for modern smartphones. For each covert channel concept various countermeasures are introduced and discussed. For the evaluation, the proposed concepts are implemented using a modular testbed application, which is extendable to different sensor- and interface hardware. As these channels are very prone to user-generated noise, a request-response packet system is used to combat the errors resulting from the noise. The evaluation shows that all of the proposed approaches are able to successfully establish a covert channel between two isolated processes. While simple channels reach a throughput of 4.8kbit/s, the more complex designs are only able to transmit data at a rate of up to 20bit/s. Because no assumptions about the target platforms are made for the design concepts, these covert channels can pose a security risk for any sensor-equipped device.

### Kurzfassung

Jedes Jahr steigt die Zahl der Geräte, die an das Internet angeschlossen sind deutlich an. Insbesondere im so genannten Internet der Dinge und im Bereich Smart Home ist ein solcher Anstieg zu beobachten. Die meisten dieser Geräte haben eine Art eingebetteten Sensor und die Anwendungen reichen von der Umweltüberwachung über das Gesundheitswesen bis hin zu industriellen Anwendungen. In dieser Arbeit werden mehrere Konzepte vorgestellt, die ungesicherte eingebettete Sensoren zum Aufbau verdeckter Kanäle nutzen. Diese Konzepte reichen von sehr einfachen Ideen, wie dem Missbrauch ungenutzter Sensorregister zur Datenübertragung, bis hin zu komplexeren verdeckten Kanälen, die oft schwer vom normalen Nutzerverhalten zu unterscheiden und daher viel schwieriger zu erkennen sind. Um die Bedeutung des Themas zu unterstreichen, werden darüber hinaus zwei weitere Ansätze vorgestellt, die den Sensor-Stack von Android, einem weit verbreiteten Betriebssystem für moderne Smartphones, ausnutzen. Für jedes Konzept werden verschiedene Gegenmaßnahmen vorgestellt und diskutiert. Für die Auswertung werden die vorgeschlagenen Konzepte mit Hilfe einer modularen Testbed-Applikation umgesetzt. die auf unterschiedliche Sensor- und Schnittstellen-Hardware erweiterbar ist. Da diese Kanäle sehr anfällig für benutzergeneriertes "Rauschen" sind, wird ein Request-Response-Paket-System zur Bekämpfung der aus dem "Rauschen" resultierenden Fehler eingesetzt. Die Evaluation zeigt, dass alle vorgeschlagenen Ansätze erfolgreich in der Lage sind, einen verdeckten Kanal zwischen zwei isolierten Prozessen aufzubauen. Während einfache Kanäle einen Durchsatz von 4.8kbit/s erreichen, können die komplexeren Designs nur Daten mit einer Rate von bis zu 20bit/s übertragen. Da bei den Designkonzepten keine Annahmen über die Zielplattformen getroffen werden, können diese verdeckten Kanäle ein Sicherheitsrisiko für jedes mit Sensoren ausgestattete Gerät darstellen.

### Acknowledgments

This master thesis was written during the year 2019/2020 at the Institute of Technical Informatics at Graz University of Technology.

First and foremost, I want to thank my supervisor Christian Steger for his support throughout the process of researching and writing my thesis. He gave me all the freedom I needed and pointed me in the right direction whenever I felt lost. I would also like to thank Thomas Ulz for his excellent guidance during the most important parts of this thesis. His door was always open whenever I had questions or needed feedback and a lot of great discussions and new ideas were the result. Further, I want to thank Rainer Hofmann for proofreading my master thesis.

Finally, I want to thank my parents for their unwavering support and encouragement throughout my studies. They were always understanding and without their help, I would not have been able to accomplish this goal.

Graz, May 2020

Markus Feldbacher

### Danksagung

Diese Diplomarbeit wurde im (Studien)Jahr 2019/2020 am Institut für Technische Informatik an der Technischen Universität Graz durchgeführt.

Zuallererst möchte ich meinem Betreuer Christian Steger für seine hilfreiche Unterstützung beim Verfassen dieser Masterarbeit danken. Von Beginn an hatte ich alle Freiheiten die benötigte und wenn ich unentschlossen war oder Probleme hatte half er mir stets die richtige Richtung zu finden und meine Arbeit fortzusetzen. Einen besonderen Dank möchte ich auch an Thomas Ulz richten, der mich gerade in den wichtigsten Abschnitten der Arbeit hervorragend unterstützt hat. Seine Tür war immer offen wenn ich Fragen hatte oder Feedback benötigte und durch die konstruktiven Diskussionen entstanden viele neue Ideen. Außerdem möchte ich Rainer Hofmann für das Korrekturlesen meiner Masterarbeit danken.

Abschließend möchte mich bei meinen Eltern bedanken, die mich während des gesamten Studiums unterstützten und ermutigten. Sie zeigten stets Verständnis und ohne sie wäre es mir nicht möglich gewesen dieses Ziel zu erreichen.

Graz, Mai 2020

Markus Feldbacher

## Contents

| 1 | Intr              | oducti         | on          |           |                        |        |       |     |     |     |     |     |   |     |   |     |   |     |     | 11              |

|---|-------------------|----------------|-------------|-----------|------------------------|--------|-------|-----|-----|-----|-----|-----|---|-----|---|-----|---|-----|-----|-----------------|

|   | 1.1               | Proble         | m Statem    | nent      |                        |        |       |     |     |     |     |     |   |     |   |     |   | •   | •   | 12              |

|   | 1.2               | Thesis         | Contribu    | tions .   |                        |        |       |     |     |     |     |     |   |     |   |     | • | •   |     | 14              |

|   | 1.3               | Thesis         | Structure   | е         |                        |        |       |     |     |     |     |     | • |     |   |     | • | •   | • • | 14              |

| 2 | Rol               | ated W         | /ork        |           |                        |        |       |     |     |     |     |     |   |     |   |     |   |     |     | 15              |

| 4 | 2.1               |                | Side-Cha    | nnol At   | toeks                  |        |       |     |     |     |     |     |   |     |   |     |   |     |     | 15<br>15        |

|   | $\frac{2.1}{2.2}$ |                | ry Side-Cla |           |                        |        |       |     |     |     |     |     |   |     |   |     |   |     |     | $\frac{10}{21}$ |

|   | $\frac{2.2}{2.3}$ |                | rk Side-C   |           |                        |        |       |     |     |     |     |     |   |     |   |     |   |     |     | $\frac{21}{24}$ |

|   | $\frac{2.3}{2.4}$ |                | Side-Ch     |           |                        |        |       |     |     |     |     |     |   |     |   |     |   |     |     | $\frac{24}{27}$ |

|   | 2.4               | 2.4.1          | Wireless    |           |                        |        |       |     |     |     |     |     |   |     |   |     |   |     |     | $\frac{27}{27}$ |

|   |                   | 2.4.1<br>2.4.2 |             |           |                        |        |       |     |     |     |     |     |   |     |   |     |   |     |     | $\frac{27}{28}$ |

|   |                   | 2.4.2          | Smartph     | ones .    |                        |        |       | • • | • • | • • | • • | • • | • | • • | • | • • | • | • • | •   | 20              |

| 3 | Cov               | vert Ch        | annels I    | Design    |                        |        |       |     |     |     |     |     |   |     |   |     |   |     |     | 31              |

|   | 3.1               | Direct         | -Access S   | ensors    |                        |        |       |     |     |     |     |     | • |     |   |     | • | •   | •   | 31              |

|   |                   | 3.1.1          | Platform    | ns        |                        |        |       |     |     |     |     |     | • |     | • |     | • | •   | •   | 31              |

|   |                   |                | 3.1.1.1     | Texas     | Instrun                | nents  |       |     |     |     |     |     | • |     | • |     | • | •   |     | 31              |

|   |                   |                | 3.1.1.2     | Linux     |                        |        |       |     |     |     |     |     | • |     | • |     | • | •   |     | 35              |

|   |                   | 3.1.2          | Attack I    | Design .  |                        |        |       |     |     |     |     |     | • |     | • |     | • | •   | ••• | 36              |

|   |                   |                | 3.1.2.1     | Unused    | l Regis                | ter At | tack  |     |     |     |     |     | • |     | • |     | • | •   |     | 36              |

|   |                   |                | 3.1.2.2     | Bit Ma    | nipulat                | tion A | ttacl | κ.  |     |     |     |     | • |     | • |     | • | •   |     | 40              |

|   |                   |                | 3.1.2.3     | Read (    | Only At                | ttack  |       |     |     |     |     |     | • |     | • |     |   | •   |     | 42              |

|   | 3.2               | Manag          | ged-Access  | s Sensor  | s                      |        |       |     |     |     |     |     | • |     |   |     |   | •   | •   | 48              |

|   |                   | 3.2.1          | Platform    | ı - Goog  | gle And                | roid   |       |     |     |     |     |     | • |     | • |     |   | •   |     | 48              |

|   |                   | 3.2.2          | Interval    | Attack    |                        |        |       |     |     |     |     |     |   |     |   |     |   | •   | •   | 50              |

|   |                   | 3.2.3          | Subscrip    | tion At   | tack .                 |        |       |     |     |     |     |     |   |     |   |     |   | •   | •   | 53              |

|   | 3.3               | Packet         | System      |           |                        |        |       |     |     |     |     |     |   |     |   |     |   | •   | •   | 54              |

|   |                   | 3.3.1          | Error De    | etection  | $\operatorname{Codes}$ |        |       |     |     |     |     |     |   |     |   |     |   | •   | •   | 55              |

|   |                   | 3.3.2          | Error Co    | orrection | ı Codes                | 5      |       |     |     |     |     |     |   |     |   |     |   | •   |     | 56              |

|   |                   | 3.3.3          | Adaptive    | e Packet  | Size .                 |        |       |     |     |     |     |     | • |     |   |     | • |     | •   | 59              |

| 4 | Imr               | olemen         | tation      |           |                        |        |       |     |     |     |     |     |   |     |   |     |   |     |     | 61              |

| 4 | 4.1               | Testbe         |             |           |                        |        |       |     |     |     |     |     |   |     |   |     |   |     |     | 61              |

|   | 4.1               | 4.1.1          | Architec    |           |                        |        |       |     |     |     |     |     |   |     |   |     |   |     |     | 63              |

|   |                   | 4.1.1<br>4.1.2 | Hardwar     |           |                        |        |       |     |     |     |     |     |   |     |   |     |   |     |     | 65              |

|   |                   | 4.1.2<br>4.1.3 |             |           |                        | -      |       |     |     |     |     |     |   |     |   |     |   |     |     | 67              |

|   |                   | 4.1.3          | Sensor A    | DSTRACT   | юп Lay                 | ver .  |       | • • | • • | • • | • • | • • | • | • • | • | • • | • | •   | • • | 07              |

|                   |       | 4.1.4  | Attack Abstraction Layer                         | 68 |

|-------------------|-------|--------|--------------------------------------------------|----|

|                   |       | 4.1.5  | Packet Layer                                     | 69 |

|                   | 4.2   | Hardw  | are                                              | 74 |

|                   |       | 4.2.1  | Texas Instruments                                | 74 |

|                   |       |        | 4.2.1.1 MSP430 LaunchPad and Sensors BoosterPack | 74 |

|                   |       |        | 4.2.1.2 CC2650 SensorTag                         | 75 |

|                   |       | 4.2.2  | Raspberry Pi                                     | 76 |

|                   | 4.3   | Evalua | tion                                             | 79 |

|                   |       | 4.3.1  | Throughput                                       | 79 |

|                   |       | 4.3.2  | Adaptive Packet Size                             | 80 |

|                   |       | 4.3.3  | Error Correction & Error Detection               | 82 |

|                   |       | 4.3.4  | Managed-Access                                   | 82 |

| 5                 | Con   | clusio | n and Future Work                                | 85 |

|                   | 5.1   | Conclu | usion                                            | 85 |

|                   | 5.2   |        | Work                                             |    |

| $\mathbf{A}$      | App   | oendix |                                                  | 87 |

|                   |       |        |                                                  | 87 |

| $\mathbf{Li}_{1}$ | terat | urverz | eichnis                                          | 91 |

|                   |       |        |                                                  |    |

# List of Figures

| 1.1                                                                                                                                                                           | Number of devices connected to the Internet [49]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2                                                                                                                                                                           | Basic concept of a covert channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13                                                                                                                                                       |

| 1.3                                                                                                                                                                           | Simple system model with two processes in isolation using a sensor as to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                          |

|                                                                                                                                                                               | build a covert channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13                                                                                                                                                       |

| 2.1                                                                                                                                                                           | Simplified view of a modern CPU architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15                                                                                                                                                       |

| 2.2                                                                                                                                                                           | Schematics of cache states for the Prime+Probe attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16                                                                                                                                                       |

| 2.3                                                                                                                                                                           | Timing diagram for the Flush+Reload attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17                                                                                                                                                       |

| 2.4                                                                                                                                                                           | Memory covert channel overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19                                                                                                                                                       |

| 2.5                                                                                                                                                                           | TCP connection over a cache based covert channel $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20                                                                                                                                                       |

| 2.6                                                                                                                                                                           | System model including main memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                                                                                                                       |

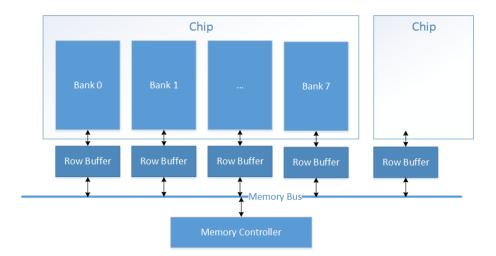

| 2.7                                                                                                                                                                           | Simple view of the organization of DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22                                                                                                                                                       |

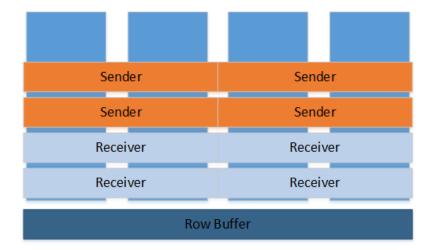

| 2.8                                                                                                                                                                           | Covert channel using DRAM row buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                                                                                                                       |

| 2.9                                                                                                                                                                           | Covert channel using DRAM row buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24                                                                                                                                                       |

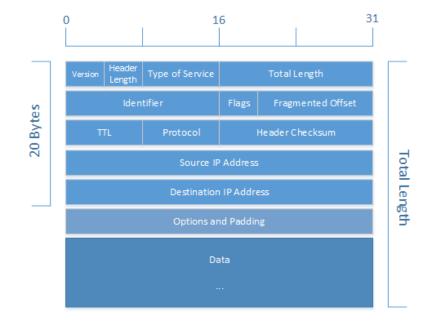

| 2.10                                                                                                                                                                          | IP header format with additional options, padding and data sections $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25                                                                                                                                                       |

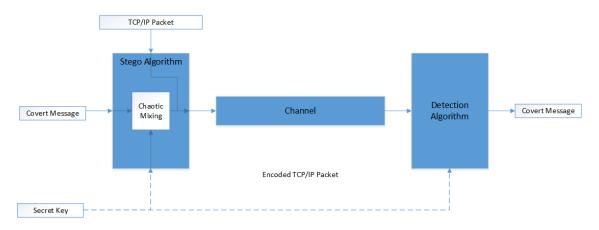

| 2.11                                                                                                                                                                          | Block diagram for the proposed covert channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26                                                                                                                                                       |

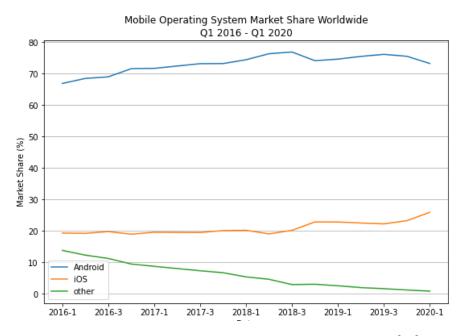

| 2.12                                                                                                                                                                          | Market Share of mobile Operating Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                                                                                       |

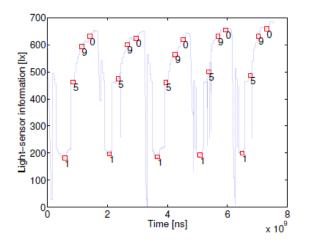

| 2.13                                                                                                                                                                          | Ambient light level during PIN entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29                                                                                                                                                       |

|                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                          |

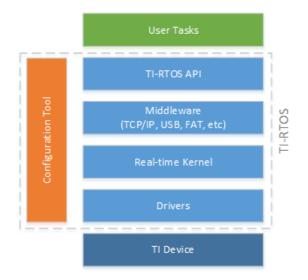

| 3.1                                                                                                                                                                           | TI-RTOS: graphical overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34                                                                                                                                                       |

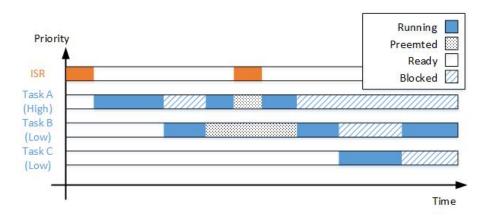

| $3.1 \\ 3.2$                                                                                                                                                                  | TI-RTOS: graphical overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\frac{34}{34}$                                                                                                                                          |

|                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34                                                                                                                                                       |

| 3.2                                                                                                                                                                           | TI-RTOS: scheduling example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34                                                                                                                                                       |

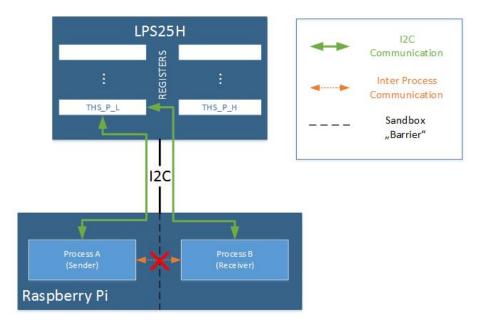

| $3.2 \\ 3.3$                                                                                                                                                                  | TI-RTOS: scheduling example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\frac{34}{36}$                                                                                                                                          |

| $3.2 \\ 3.3 \\ 3.4$                                                                                                                                                           | TI-RTOS: scheduling example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\frac{34}{36}$                                                                                                                                          |

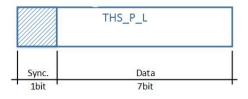

| $3.2 \\ 3.3 \\ 3.4$                                                                                                                                                           | TI-RTOS: scheduling example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34<br>36<br>38                                                                                                                                           |

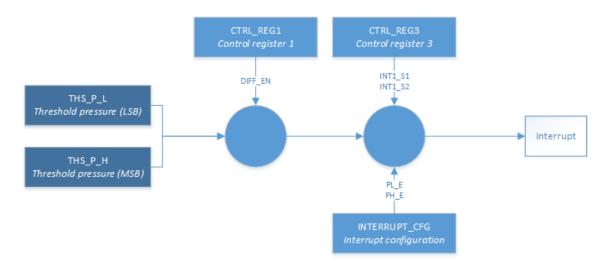

| $3.2 \\ 3.3 \\ 3.4 \\ 3.5$                                                                                                                                                    | TI-RTOS: scheduling example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34<br>36<br>38<br>39                                                                                                                                     |

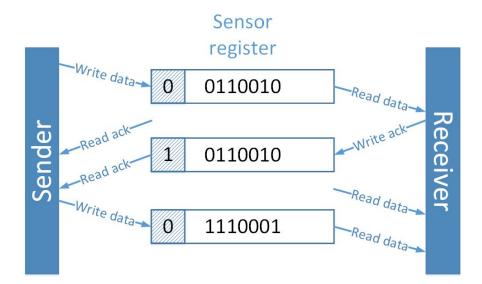

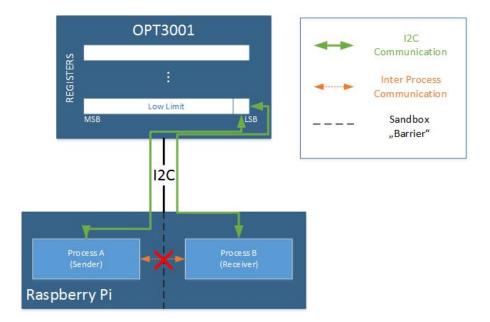

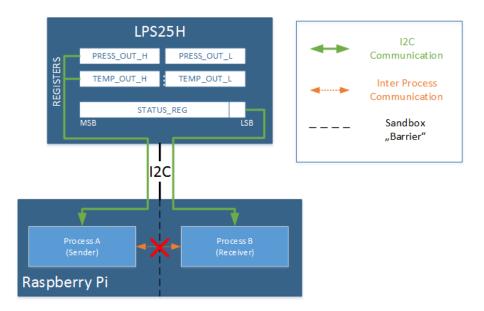

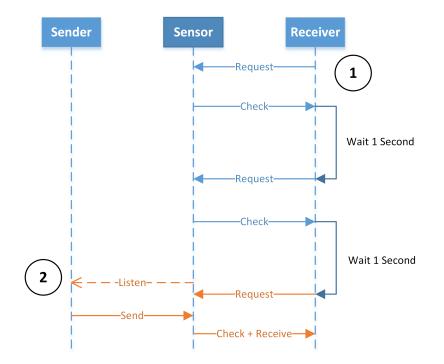

| <ol> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ol>                                                                                                   | TI-RTOS: scheduling example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34<br>36<br>38<br>39<br>40<br>41                                                                                                                         |

| <ol> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ol>                                                                                                   | TI-RTOS: scheduling exampleSchematic overview: sender and receiver communicating over unused registerRegister structure, for the 8bit THS_P_L register with synchronization bitSynchronization procedure between sender and receiver to initialize a newchannelLPS25H Thresshold LogicSchematic overview: sender and receiver communicating over one thresholdbitProposed "read only" covert channel                                                                                                                                                                                                                                                       | 34<br>36<br>38<br>39<br>40                                                                                                                               |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                                                                                                                        | TI-RTOS: scheduling exampleSchematic overview: sender and receiver communicating over unused registerRegister structure, for the 8bit THS_P_L register with synchronization bitSynchronization procedure between sender and receiver to initialize a newchannelChannelLPS25H Thresshold LogicSchematic overview: sender and receiver communicating over one thresholdbitDifferenceRegister overview: sender and receiver communicating over one thresholdbitDifferenceInitialization procedure for the read-only method                                                                                                                                    | 34<br>36<br>38<br>39<br>40<br>41                                                                                                                         |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                                                                                                                                 | TI-RTOS: scheduling exampleSchematic overview: sender and receiver communicating over unused registerRegister structure, for the 8bit THS_P_L register with synchronization bitSynchronization procedure between sender and receiver to initialize a newchannelLPS25H Thresshold LogicSchematic overview: sender and receiver communicating over one thresholdbitDitProposed "read only" covert channelInitialization procedure for the read-only methodOne read cycle                                                                                                                                                                                     | $34 \\ 36 \\ 38 \\ 39 \\ 40 \\ 41 \\ 43 \\ 46 \\ 46 \\ 46 \\ 46 \\ 46 \\ 8 \\ 40 \\ 8 \\ 40 \\ 8 \\ 40 \\ 8 \\ 8 \\ 8 \\ 8 \\ 8 \\ 8 \\ 8 \\ 8 \\ 8 \\ $ |

| $\begin{array}{c} 3.2 \\ 3.3 \\ 3.4 \\ 3.5 \\ \end{array}$ $\begin{array}{c} 3.6 \\ 3.7 \\ 3.8 \\ 3.9 \\ 3.10 \\ 3.11 \end{array}$                                            | TI-RTOS: scheduling exampleSchematic overview: sender and receiver communicating over unused registerRegister structure, for the 8bit THS_P_L register with synchronization bitSynchronization procedure between sender and receiver to initialize a newchannelLPS25H Thresshold LogicSchematic overview: sender and receiver communicating over one thresholdbitDitProposed "read only" covert channelInitialization procedure for the read-only methodOne read cycleLayers of the Android sensor stack and their respective owners [20]                                                                                                                  | $34 \\ 36 \\ 38 \\ 39 \\ 40 \\ 41 \\ 43 \\ 46 \\ 46 \\ 48 \\ 48 \\ $                                                                                     |

| $\begin{array}{c} 3.2\\ 3.3\\ 3.4\\ 3.5\\ \end{array}$ $\begin{array}{c} 3.6\\ 3.7\\ \end{array}$ $\begin{array}{c} 3.8\\ 3.9\\ 3.10\\ 3.11\\ \end{array}$                    | TI-RTOS: scheduling exampleSchematic overview: sender and receiver communicating over unused registerRegister structure, for the 8bit THS_P_L register with synchronization bitSynchronization procedure between sender and receiver to initialize a newchannelLPS25H Thresshold LogicSchematic overview: sender and receiver communicating over one thresholdbitDitProposed "read only" covert channelInitialization procedure for the read-only methodOne read cycleLayers of the Android sensor stack and their respective owners [20]Timing differences between application and sensor for different CPU usages                                        | $\begin{array}{c} 34\\ 36\\ 38\\ 39\\ 40\\ 41\\ 43\\ 46\\ 46\\ 48\\ 51\\ \end{array}$                                                                    |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13                                                                                          | TI-RTOS: scheduling exampleSchematic overview: sender and receiver communicating over unused registerRegister structure, for the 8bit THS_P_L register with synchronization bitSynchronization procedure between sender and receiver to initialize a newchannelLPS25H Thresshold LogicSchematic overview: sender and receiver communicating over one thresholdbitDitProposed "read only" covert channelInitialization procedure for the read-only methodOne read cycleLayers of the Android sensor stack and their respective owners [20]Timing differences between application and sensor for different CPU usagesTimestamp variation for small intervals | $\begin{array}{c} 34\\ 36\\ 38\\ 39\\ 40\\ 41\\ 43\\ 46\\ 46\\ 48\\ 51\\ 52\\ \end{array}$                                                               |

| $\begin{array}{c} 3.2\\ 3.3\\ 3.4\\ 3.5\\ \end{array}\\ \begin{array}{c} 3.6\\ 3.7\\ \end{array}\\ \begin{array}{c} 3.8\\ 3.9\\ 3.10\\ 3.11\\ 3.12\\ 3.13\\ 3.14 \end{array}$ | TI-RTOS: scheduling exampleSchematic overview: sender and receiver communicating over unused registerRegister structure, for the 8bit THS_P_L register with synchronization bitSynchronization procedure between sender and receiver to initialize a newchannelLPS25H Thresshold LogicSchematic overview: sender and receiver communicating over one thresholdbitDitProposed "read only" covert channelInitialization procedure for the read-only methodOne read cycleLayers of the Android sensor stack and their respective owners [20]Timing differences between application and sensor for different CPU usages                                        | $\begin{array}{c} 34\\ 36\\ 38\\ 39\\ 40\\ 41\\ 43\\ 46\\ 46\\ 48\\ 51\\ \end{array}$                                                                    |

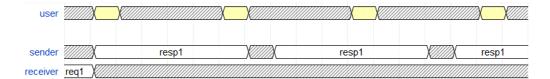

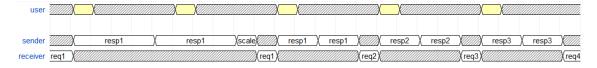

| 3.16 | Structure of a response packet (RES)                                            | 54 |

|------|---------------------------------------------------------------------------------|----|

| 3.17 | Code size comparison between Berger and Hadamard codes                          | 57 |

| 3.18 | Packet size is too big, which causes many retransmissions                       | 59 |

| 3.19 | Packet size is too big, so the sender starts to scale down                      | 60 |

| 3.20 | Packet size is too small, so the sender starts to scale up                      | 60 |

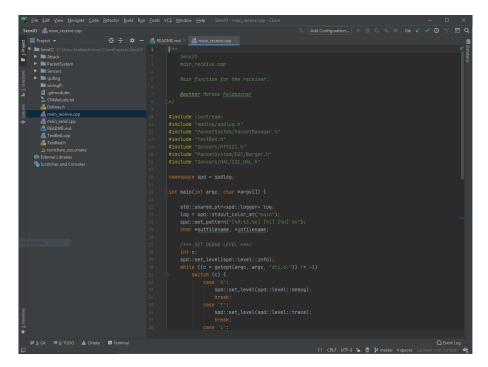

| 4.1  | Jetbrains CLion IDE                                                             | 62 |

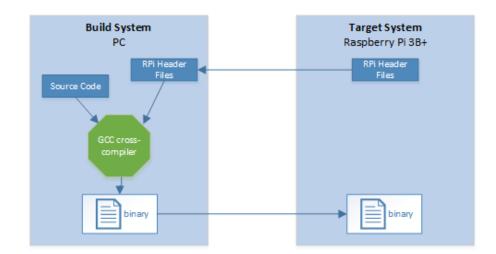

| 4.2  | Cross-compilation procedure                                                     | 63 |

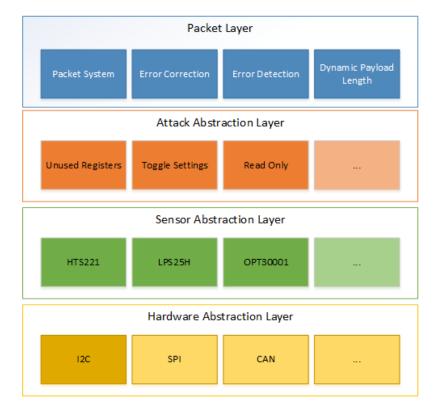

| 4.3  | The testbed consists of four layers that abstract various parts of the system.  | 64 |

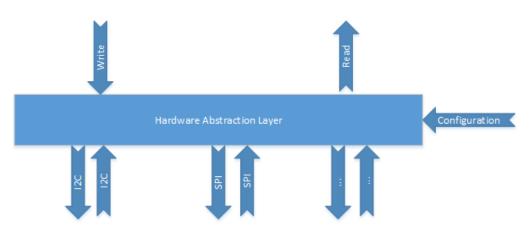

| 4.4  | Hardware abstraction layer.                                                     | 65 |

| 4.5  | The testbed consists of four layers that abstract various parts of the system.  |    |

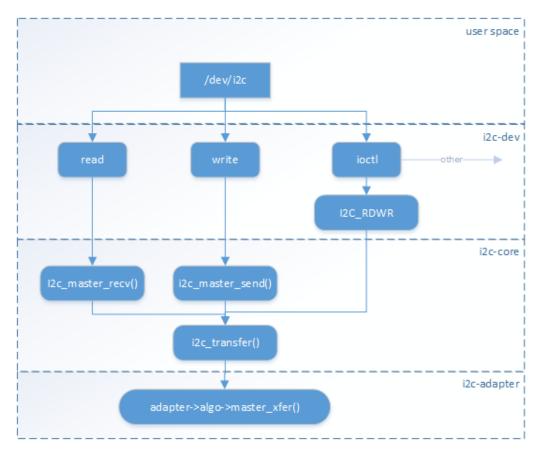

|      | [4]                                                                             | 66 |

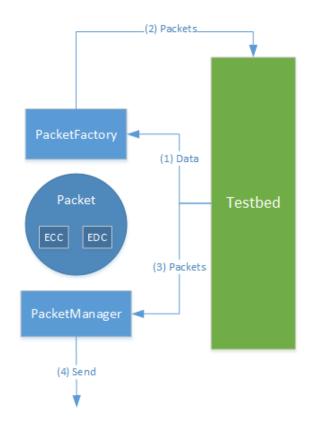

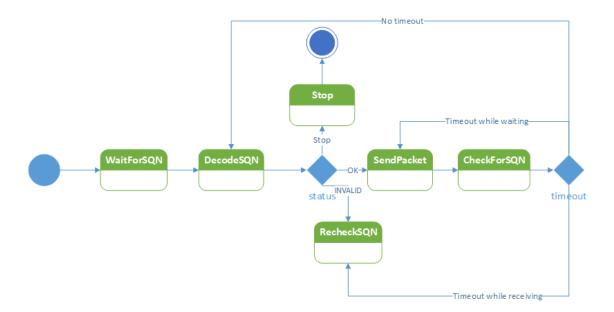

| 4.6  | Module interactions in the packet layer for the sender                          | 69 |

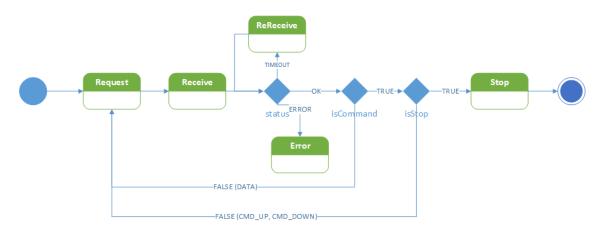

| 4.7  | State diagram for the sender.                                                   | 73 |

| 4.8  | State diagram for the receiver.                                                 | 73 |

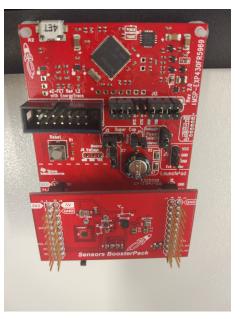

| 4.9  | MSP430 dev board                                                                | 74 |

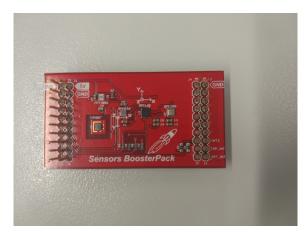

| 4.10 | Available sensors on the TI BoosterPack extension board                         | 76 |

| 4.11 | Raspberry Pi $3B+[59]$                                                          | 77 |

| 4.12 | Raspberry Sense HAT [59]                                                        | 77 |

| 4.13 | Raspberry Pi Testsetup                                                          | 78 |

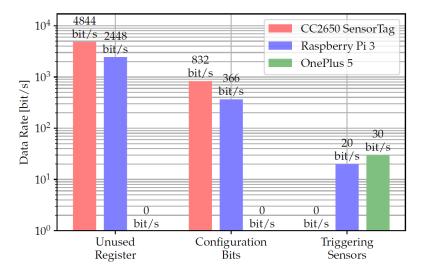

| 4.14 | Throughput comparison between different platforms [56]                          | 80 |

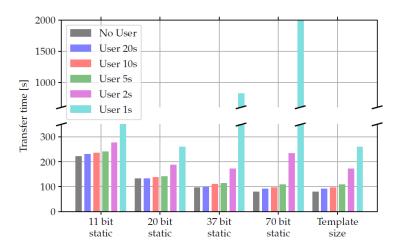

| 4.15 | Transfer time differences for various packet sizes and user access timings [56] | 81 |

| 4.16 | Comparison between static and dynamic packets sizes with noise [56]             | 81 |

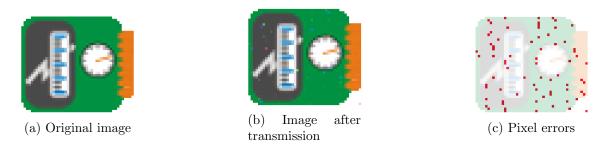

| 4.17 | Errors resulting in a transmission without EDC and ECC enabled [56]             | 82 |

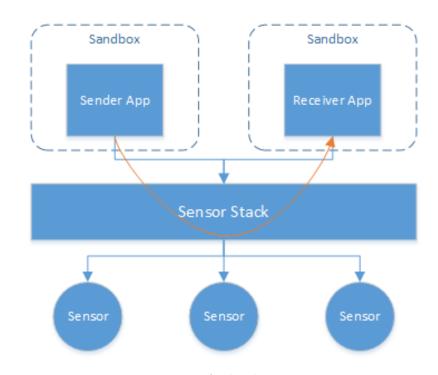

| 4.18 | Android test setup                                                              | 83 |

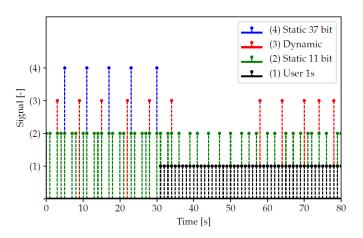

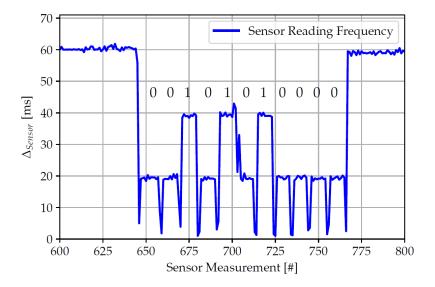

| 4.19 | Received transmission of a test patter over the covert channel [56]             | 84 |

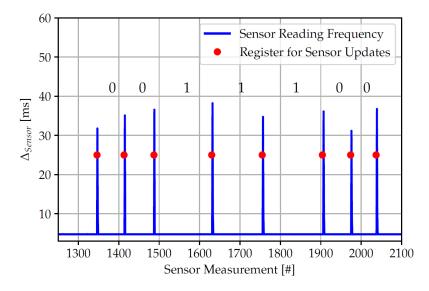

| 4.20 | Correlation between sensor reading frequency and registering a sensor event     |    |

|      | listener [56]                                                                   | 84 |

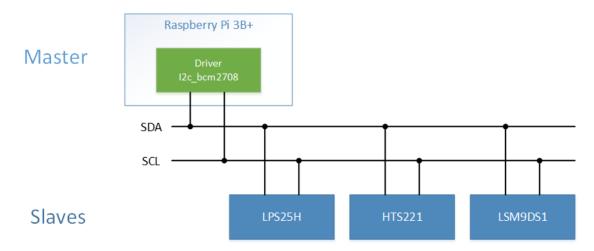

| A.1  | Example I2C setup                                                               | 87 |

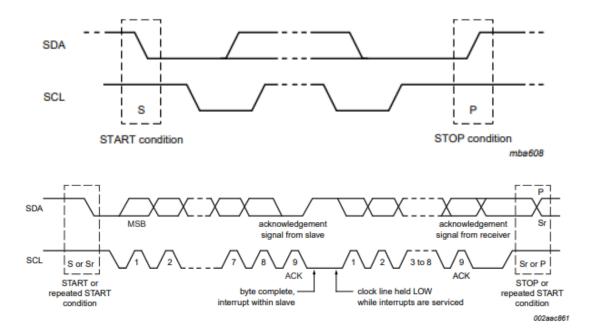

| A.2  | I2C START and STOP conditions [50]                                              | 88 |

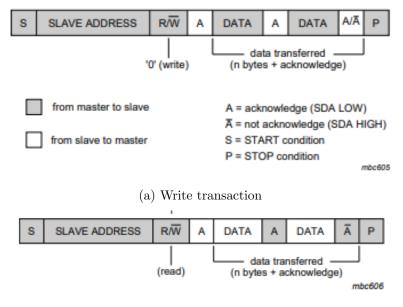

| A.3  | Structure of an I2C transaction [50]                                            | 89 |

## List of Tables

| 2.1        | Comparison of the performance counters when performing 256 million en-       |                 |

|------------|------------------------------------------------------------------------------|-----------------|

|            | cryptions with different cache attacks                                       | 18              |

| 2.2        | Comparison of the size differences between Hadamard and Berger codes         | 19              |

| 2.3        | Sensor network layers, attacks and defences [58]                             | 27              |

| 3.1        | THS_P_H and THS_P_L: threshold pressure registers                            | 37              |

| 3.1<br>3.2 | CTRL_REG1: Control register 1                                                | $\frac{37}{37}$ |

| 3.2<br>3.3 | -                                                                            | 37<br>40        |

|            | OPT3001 operational modes                                                    |                 |

| 3.4        | Theoretical throughput for different delta values                            | 44              |

| 3.5        | Information encoded into status bits                                         | 45              |

| 3.6        | SensorEvent fields [20]                                                      | 50              |

| 3.7        | Available commands                                                           |                 |

| 3.8        | Example encodings/decodings of a $(3,1)$ repetition code                     | 57              |

| 4.1        | Selected products from TI                                                    | 74              |

| 4.2        | TI BoosterPack extension board and its application                           | 75              |

| 4.3        | Available sensors on the CC2650 SensorTag                                    | 76              |

| 4.4        | Hardware sensors on the Raspberry Sense HAT                                  | 78              |

| 4.5        | Results for the transmission times using the Raspberry Pi $3B$ +             | 79              |

| 4.6        | Resulting maximum packet sizes based on berger code size                     | 80              |

| A.1        | Transfer when master is writing one byte to slave $[46]$                     | 90              |

| A.1<br>A.2 | Transfer when master is writing multiple bytes to slave [46]                 | 90              |

| A.2<br>A.3 |                                                                              |                 |

|            | Transfer when master is receiving (reading) one byte of data from slave [46] | 90              |

| A.4        | Transfer when master is receiving (reading) multiple bytes of data from      | 00              |

|            | slave $[46]$                                                                 | 90              |

# Chapter 1 Introduction

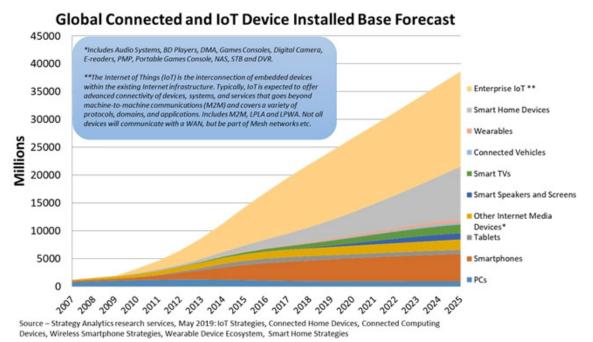

Every year, the number of devices that are connected to the Internet rises significantly. Especially the number of Internet of Things (IoT)- and Smart Home devices started to grow recently. Most of those devices have some kind of sensor embedded and applications for enterprise IoT range from environmental monitoring [53], over healthcare [42] to industrial applications [7]. On the consumer side, smartphones and wearables are very common items and include a wide range of different sensors, such as accelerometers and ambient light sensors. The later is often used to automatically adjust the screen brightness, based on the ambient light level, while accelerometers are needed to recognize motion and wake up the device. In Figure 1.1, a forecast is given with multiple categories.

Figure 1.1: Number of devices connected to the Internet [49]

Sensors are observing the physical properties of their environment. As such properties are often private, i.e., health care data [62] or industrial espionage [48], there are some major privacy concerns. If an attacker is able to access such private data, the victim can be harmed in a personal or financial manner. For companies, it can result in significant damage to their reputation if any customer data is leaked. Therefore, it is considered a high priority to keep the private data safe and secure. Another important aspect is the trustworthiness of data [55]. Using false data injection attacks, attackers are able to manipulate cyber-physical systems by tampering with the sensor-data [34]. If the targeted systems are medical devices, such attacks could possibly threaten human lives [11]. To counteract such attacks, modern mobile operating systems are using a permission system to secure sensors interfaces. Unfortunately, these systems are often too coarse or do not apply to all sensors and therefore also present security issues [53]. These problems with the permission system are mostly associated with privacy concerns, but can also be used to build so-called covert channels, which are the main topic of this thesis.

### 1.1 Problem Statement

The confinement problem is a well-known topic. It describes the problem of preventing an entity (physical or software) from leaking any kind of confidential information. To achieve this goal, the entities are put into isolation. For software isolation, the most common ways are either Virtual Machines (VMs) or so-called Sandboxes. VMs simulate hardware such that the isolated program can perform like on a physical system, but without being able to break out of the VM. Furthermore, a program is not able to distinguish between a physical and a simulated system. Nevertheless, there still exists the problem of shared resources like CPU, memory, sensors, etc. Some of the related work covered in Chapter 2, shows that it is still possible to leak data across Virtual Machines. The other common technique to confine a program is sandboxing. A sandbox creates a controlled environment in which the program is executed. One of the most prominent examples is Google Android, which implements an "Application Sandbox" [22] into the kernel and uses a permission system to control all of the interactions with elements outside of the sandbox.

Side Channels. A side channel is considered information, which is leaked intentional or unintentional by an entity while performing operations and can be observed by others. For example, if a program is executing multiple calculations with different processing complexities, based on the CPU usage, other programs may be able to distinguish between the different calculations. Some effects are even observable from outside, such as timing, power consumption, or electromagnetic emanation [32, 37, 39]. For intentional side channels, also called active side channels, the attacker requires physical access to the device [17]. These channels can be used to encode data which can be observed by another process, effectively building a communication channel or so-called covert channel.

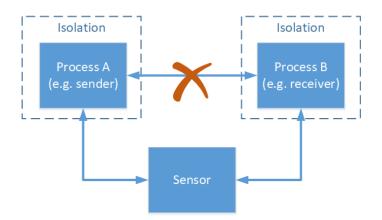

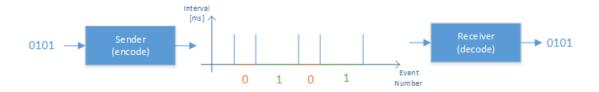

**Covert Channels.** In 1973, Butler W. Lampson defined covert channels as channels, which are not intended for information transfer at all [35]. These channels are built using side-channel information that is observable by at least one of the applications and can be manipulated by the other application. Covert channels can be used by two isolated

processes, which are normally prohibited to interact with each other, to communicate. A basic graphical representation of a covert channel is given in Figure 1.2.

Figure 1.2: Basic concept of a covert channel

For all covert channel concepts presented in this thesis, the system model shown in Figure 1.3 applies. It is comprised of two processes which are both isolated. Direct communication between isolated processes is prohibited by a strict permission model. Both processes require access to the same sensor as part of their normal tasks. This sensor is therefore considered a shared resource that can be used to build a covert channel if not secured correctly. The model assumes that one of the processes (sender) is in possession of confidential information and the attacker wants to transmit this information to another process (receiver). Using its ability to control the behavior of the sensor, the sender encodes this information into a side channel. The receiver is able to observe the encoded information by monitoring the sensor.

Figure 1.3: Simple system model with two processes in isolation using a sensor as to build a covert channel

### **1.2** Thesis Contributions

In this thesis, five covert channel concepts are presented. The first three exploit the unsecured registers of an embedded sensor. The channels allow different data rates with a trade-off in the likelihood of being detected. For each of the channels, countermeasures are proposed which have to be either implemented in hardware or software. To allow the evaluation of the covert channels on different sensors, a modular application was developed. This test application can be extended to support other sensors, hardware interfaces, and attacks. The application also integrates a packet system, which is used to control the data flow and enables error correction. To show the viability of covert channels on modern operating systems, two additional concepts are introduced that exploit the android sensor stack. These concepts are evaluated using both, the Android simulator and a real-world device. The results are compared with the other covert channel designs. This master thesis was part of the IoSense project. <sup>1</sup>

### **1.3** Thesis Structure

This thesis is structured into five chapters. In Chapter 2, related work is presented, which is split into four sections, each covering a different side-channel category: cache-, memory-, network-, and sensor-based. For each section, a few selected publications are explained to give some insight into other popular covert channel ideas and designs. Following up, in Chapter 3, the side-channel concepts developed during this thesis are introduced and explained in more detail. The designs are split into two major categories: direct-access and managed-access. For each category, some relevant platforms and operating systems are discussed first, followed by the covert channel concepts in increasing complexity, including initialization and synchronization. For each design, ideas for countermeasures are presented as well. These designs are implemented using a layered abstraction approach that is discussed in more detail in Chapter 4. Using this implementation, the designs are evaluated in terms of throughput. Finally, in Chapter 5, a conclusion is given followed by an outlook and ideas for future work.

<sup>&</sup>lt;sup>1</sup>The IoSense project has received funding from the Electronic Component Systems for European Leadership Joint Undertaking under grant agreement No 692480. This Joint Undertaking receives support from the European Unions Horizon 2020 research and innovation programme and Germany, Netherlands, Spain, Austria, Belgium, Slovakia.

### Chapter 2

### **Related Work**

This chapter introduces some important publications of multiple closely related fields. These range from very fast side-channel attacks that target the cache or memory of a device, covered in Section 2.1 and Section 2.2, to considerably slower attacks on sensor-systems, covered in Section 2.4. In Section 2.3 network-based side-channels are discussed, which can be a big threat in typical IoT applications.

### 2.1 Cache Side-Channel Attacks

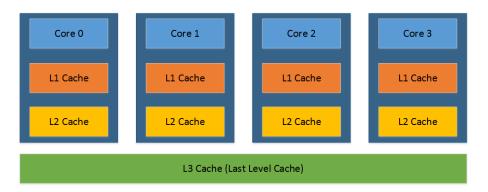

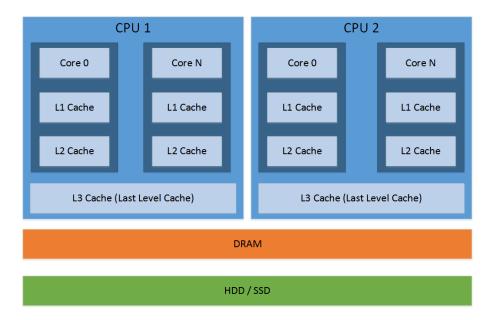

In modern processor architectures different levels of caches are used to achieve a good balance between speed and cost. The cost rises exponentially in regards to throughput, therefore the usage of the highest-speed cache is kept to a minimum. The cache hierarchy of a modern Intel CPU is shown in Figure 2.1. The CPU consists of four cores, of which each has a separate L1 and L2 cache. The L3 cache is shared between all cores and also know as Last-Level-Cache (LLC).

Figure 2.1: Simplified view of a modern CPU architecture.

As most systems cannot be influenced in a way that programs run on a specific core, the attacker tries to focus its exploits on the LLC which can be accessed from all cores. In modern Intel systems, the LLC is an inclusive cache, which means it contains copies of the

data stored in all L1 and L2 caches. If some of the data is removed from the LLC cache it gets also removed from the corresponding L1 and L2 cache.

Another important concept that enables the cache attacks is page sharing. This technique is implemented in modern operating systems to reduce the memory footprint of running processes. For example, if multiple processes use the same shared library, the operating system keeps only one instance of this library in memory and shares the corresponding pages with all processes. There is also a more aggressive approach of page sharing called memory de-duplication which is implemented in widely used hypervisors like VMware ESX [57]. If this form of page sharing is enabled, the system tries to find pages in memory that contain the exact same content. All but one of those pages get evicted and all references are updated to use the single remaining instance. This comes with security issues as a malicious process can alter the shared pages. To circumvent this, shared pages are mapped as copy-on-write. If a process tries to modify the contents of the page, a copy of the page is created and mapped to this process instead of the shared page. That process introduces a delay which can be exploited by the following attacks.

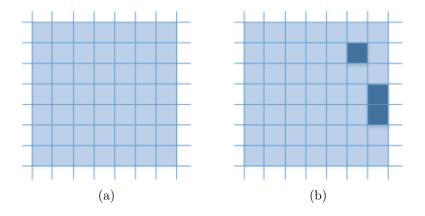

**Prime+Probe:** The Prime+Probe attack [63] was proposed in 2005 and is one of the first sophisticated cache side-channel attacks. The goal was to learn about the memory access patterns of another process and therefore to be able to perform a full key extraction during or after an encryption.

Figure 2.2: Schematics of cache states for the Prime+Probe attack

To perform the attack, first a contiguous byte array A is allocated by the attacker. Then, for each encryption of a plaintext p the attacker performs the following steps:

- (prime) Read at least one value from each memory block in A. This fills the cache with the attacker's data. See Figure 2.2a

- Trigger an encryption of p, which will cause some eviction of the attacker's memory blocks. See Figure 2.2b

• (probe) Read data from array A to check which cache sets were evicted by the victim. If a cache set was accessed during the encryption, it will contain the victim's data. Therefore the read action of the attacker will take more time as the attacker's data has to be loaded into the cache again. This timing difference is monitored and evaluated.

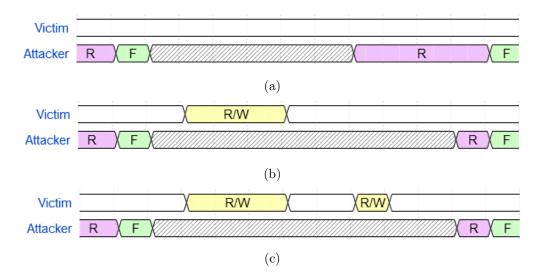

**Flush+Reload:** The Flush+Reload attack [61] is an extension of the Gullasch et al. attack [24], that allows cross-core and even cross-VM attacks by focusing the LLC. The second advantage in contrast to prior methods is the high fidelity and the resistance to false positives. This is very important, as a low-resolution attack is not able to provide the fine granularity that is required for tasks like cryptanalysis. This attack is a variant of the Prime+Probe attack described in the previous paragraph. Like Prime+Probe it consists of three phases per attack cycle:

- Flush the monitored cache lines to prepare the attack.

- Trigger an encryption of p, which will cause the victim to reload some of the previously evicted data back into the cache.

- Read the cache lines to check which cache lines were reloaded by the victim. If a cache set was accessed during the encryption, it will contain the victim's data. Therefore the read action of the attacker will take less time as the requested data is already in the cache. See Figure 2.3b Otherwise, the data has to be loaded into the cache which takes more time. This timing difference is monitored and evaluated. See Figure 2.3b

Figure 2.3: Timing diagram for the Flush+Reload attack

As pictured in Figure 2.3c, the reload time does not depend on the number of memory accesses. This means, an attacker is only able to tell if the cache line was read by one of

the victims, but not how often it was read. With this approach, the authors were able to successfully reveal 90% of the victim's key bits during a cross-VM attack. If both processes run on the same core it is even possible to recover the whole key by observing two or more signatures.

**Flush+Flush:** The Flush+Flush attack [23] exploits the same properties as the previously introduced Flush+Reload attack. In contrast to Flush+Reload, Flush+Flush only uses the *clflush* command and exploits the difference in execution times between data that is present in the cache and data that is not. Further, the authors implemented a monitoring tool using performance counters, that monitors cache references and cache misses of the LLC. This tool was able to detect other existing attacks as shown in Table 2.1. When an attack is mounted using Flush+Reload or Prime+Probe, the number of cache references and most important the number of cache misses skyrockets.

| Technique    | Cache references | Cache misses | Execution (s) | Stealthy |

|--------------|------------------|--------------|---------------|----------|

| Flush+Reload | $1000 * 10^6$    | 16284602     | 215           | No       |

| Prime+Probe  | $4222 * 10^6$    | 294897508    | 235           | No       |

| Flush+Flush  | $768 * 10^6$     | 1741         | 163           | Yes      |

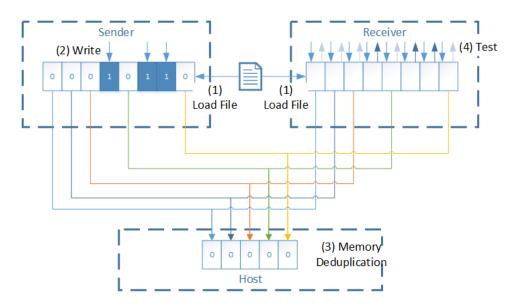

Table 2.1: Comparison of the performance counters when performing 256 million encryptions with different cache attacks

Jidong Xiao et al [60] investigated the implications of memory deduplication which was already explained in the beginning of this Section. Using memory deduplication, hypervisors try to merge identical pages into one single page to increase memory efficiency. This comes with drawbacks in security as it creates a "shared medium" between multiple different processes or even different virtual machines. The goal of the authors was to design, implement and evaluate a cross-VM covert channel that is resilient to noise and ensures a high bit rate. As mentioned in Section, when a process performs a write operation on a shared page, the hypervisor first creates a copy of the original page and redirects the write operation to this new page. While this ensures that other processes that currently use the shared page are not affected, it introduces a short delay. This delay is used to build the covert channel. In the first step, both the sender and the receiver open the same file. This file is loaded into memory and the sender changes some parts based on a "protocol". Some parts of the file are still the same for both processes, so the hypervisor uses memory deduplication. Now, the receiver overwrites the whole file and therefore forces the hypervisor to perform copy-on-write operations on shared pages. The whole process is monitored by the receiver, which is now able to identify based on timing which pages the sender had accessed before. The whole procedure is visualized in Figure 2.4.

Figure 2.4: Memory covert channel overview

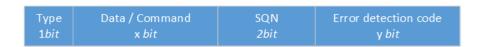

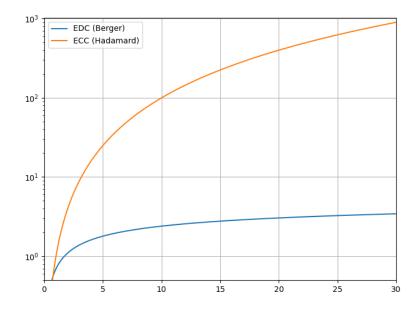

One of the biggest problems cache side-channels are facing is the aggressive noise introduced by other processes, the operating systems and hypervisors. Therefore, it was assumed that the noise effectively prevents attackers from using cache side-channels as functional covert channels. The research work "Hello from the Other Side: SSH over Robust Cache Covert Channels in the Cloud" [41] tackles that assumption and introduces the concept of error-correcting codes to cache based side-channels. They implement a packet system using a request-response architecture. Request packets only contain the id of the requested data packet. This means, the packet is really small and an algorithm with error-correction can be used. As these error-correcting codes (ECC) need to encode the input, which results in an exponential message length of  $m = 2^k$  for the Hadamard code for example, they would introduce too much overhead for the data packets. Error-detecting codes (EDC), like Berger codes, calculate a checksum that is appended on the end of a packet. This adds a much lower overhead resulting in a logarithmic message length of m = k + log(k + 1). Table 2.2 shows the size difference of Hadamard and Berger codes for different input lengths.

| Input length | Hadamard (ECC) | Berger (EDC) |

|--------------|----------------|--------------|

| 1            | 2              | 2            |

| 2            | 4              | 3            |

| 5            | 32             | 6            |

| 10           | 1024           | 12           |

| 20           | 1048576        | 22           |

Table 2.2: Comparison of the size differences between Hadamard and Berger codes

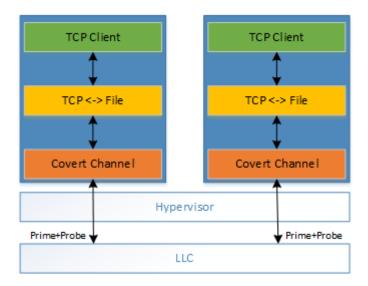

The packet system, ECC and EDC codes are described in more detail in Section 3.3. Because they still experienced some errors, in addition to the EDC and ECC in their physical layer, the authors also introduced a data-link layer. This layer contains another error-correcting code. To achieve fast encoding and decoding speeds, Reed-Solomon codes (RS codes) with a 10% error-correction were chosen. This resulted in a channel with an achievable 0.00% error rate. For their experiments Maurice et.al implemented an SSH channel over the proposed covert channel 2.5. Other state-of-the-art channels are not able to provide the reliability required for TCP, as it expects the physical layer to transmit the data without errors. They tested the stability of the channel during different server loads and found that the connection was unstable only in high load scenarios. This shows that, given the correct implementation, covert-channels can be a real threat in cloud environments.

Figure 2.5: TCP connection over a cache based covert channel

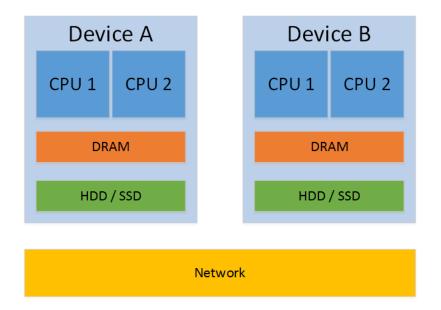

### 2.2 Memory Side-Channel Attacks

Memory side-channel attacks follow a very similar pattern like the cache side-channel attacks discussed in Section 2.1. Instead of L1, L2 or the last-level cache, memory sidechannel attacks target either the DRAM directly or files and variables present in the DRAM or saved to the hard drive disks (HDD) of a system. In general, these channels are much slower because the physical hardware has a much lower throughput. Current generation DRAM delivers raw speeds of up to 25GB/s whereas last-level-caches are able do achieve 150+GB/s. Conventional HDDs are even slower, reaching 100MB/s. Looking at the system model shown in Figure 2.6, it can be seen that memory is the next layer on top of the CPU. The memory is shared between multiple CPUs in dual-socket systems, which enables cross-CPU attacks. Modern Servers often use such a dual CPU design because of the space restrictions in datacenters. An attack that is able to establish a sidechannel across different CPUs is therefore a realistic threat for modern cloud applications.

Figure 2.6: System model including main memory

Gruss et al. [43] presented methods to reverse engineer the memory address mapping of DRAM in regards to DRAM channels, ranks and banks. Using the gained knowledge, they introduce an attack that exploits the shared DRAM row buffer. The DRAM row buffer is one of the core elements in the storage organization. Other elements from high- level to low-level are: channel, DIMM, rank, chip, bank, row, column, and memory cell. The channels are the physical links between the memory controller and the DIMM modules. Multiple channels can be accessed in parallel, which speeds up the data transmission. Dual Inline Memory Modules (DIMMs) are the actual physical PCB modules that contain the DRAM chips on both sides. These chips are grouped into ranks, where each side of the DIMM represents a single rank. Each of the ranks consists of 8 banks (16 for DDR4)

which are also used in parallel for a significant speed increase on a memory level. Finally the banks consist of memory cells which are grouped into rows and columns. To further speed up multiple accesses to the same memory location, the memory modules contain row buffers that act as a cache within the DRAM. Figure 2.7 shows the location of the row buffer in the organization hierarchy. It sits directly between the individual banks and the memory bus. The access times vary between  $\sim 20$ ns for cached rows,  $\sim 40$ ns for empty row buffer access and  $\sim 60$ ns for conflicts. A conflict happens when a row other than the cached row is accessed. The row buffer has to close the active row and activate the requested row. This procedure introduces the  $\sim 40$ ns delay.

Figure 2.7: Simple view of the organization of DRAM

To be able to exploit the DRAM row buffer and build a covert channel, the attacker has to know the memory address mapping function. This function varies between different memory types and systems, so the authors introduced a fully automatic reverse engineering method. First a list of address pairs that use the same bank must be determined. This is done by accessing two addresses in an alternating fashion and measuring the access time. If the time is significantly higher, the addresses belong to the same bank but not the same row, as the delay comes from the row conflicts. With the known address pairs, the addressing functions can be reconstructed. Depending on the page size, either all partial functions up to  $a_{20}$  for 2MB pages or up to  $a_{30}$  for 1GB pages can be recovered. Bits above  $a_{30}$  or below  $a_5$  can be ignored as they are not used for bank addressing. With a brute-force approach, the authors generated all possible linear functions for the remaining bits. These functions are then tested and filtered using the list of address pairs. Only if both addresses of a pair result in the same bank, the function is added to a list of possible addressing functions. The resulting list can then be used in the next step to build a cross-CPU covert channel.

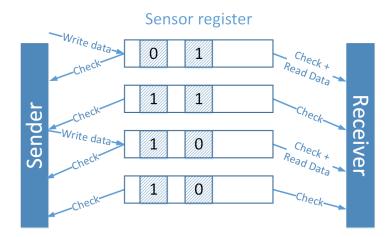

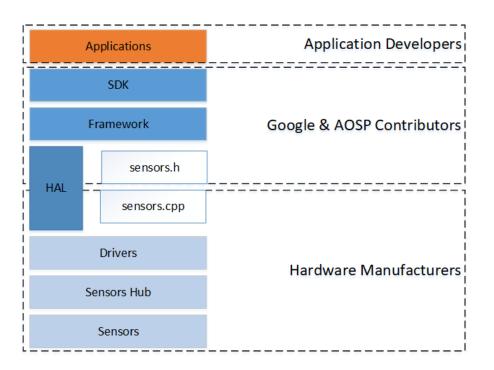

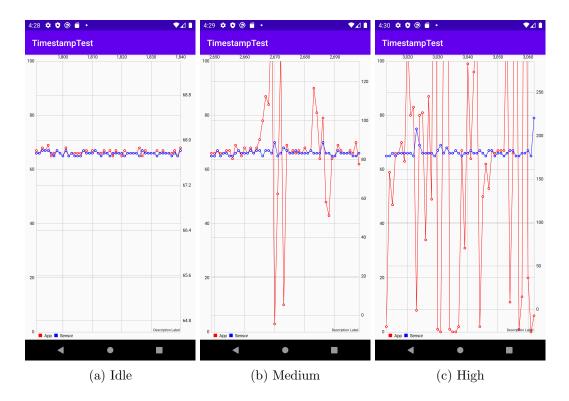

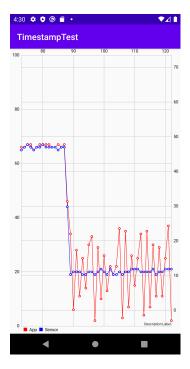

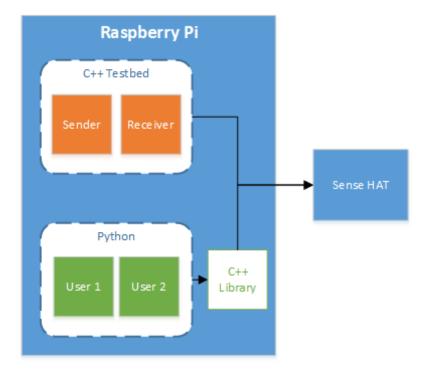

Figure 2.8: Covert channel using DRAM row buffer