Dominik Zupan, BSc

# Design of an Integrated Switched Capacitor DC-DC Converter for Negative Supply Voltage Generation

Master's Thesis

to achieve the university degree of Diplom-Ingenieur Master's degree programme: Information and Computer Engineering

submitted to

Graz University of Technology

Supervisor Ass.Prof. Dipl.-Ing. Dr.techn. Peter Söser

Institute of Electronics

Faculty of Electrical and Information Engineering

Graz, February 2018

This document is set in Palatino, compiled with  $pdf \ensuremath{\texttt{AT}_{\!E\!}} X ze$  and  $\ensuremath{\texttt{Biber}}.$

The  $LAT_EX$  template from Karl Voit is based on KOMA script and can be found online: https://github.com/novoid/LaTeX-KOMA-template

#### Affidavit

# Affidavit

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZONLINE is identical to the present master's thesis.

Date

Signature

# Abstract

This thesis describes a development flow for a Switched-Capacitor DC-DC converter creating a negative voltage. This includes conceptual considerations, such as topology and approximate performance calculations, as well as the design of the circuit in Bipolar-CMOS-DMOS (BCD) technology and the verification of the design in comparison to the conceptual approximations.

The use of triple-well NMOS and DeMOS devices is reviewed. Additionally, needed circuits such as level shifters and voltage buffers are explained. Furthermore, an approach for area optimisation of the used switch transistors is presented. Other considerations such as external devices and the introduced parasitics and their effects are also modelled and discussed.

Keywords: switched capacitor; DC-DC converter; charge pump; seriesparallel topology; negative voltage creation; switches; triple-well NMOS; DeMOS; area optimisation; external capacitor; parasitics.

# Kurzfassung

Diese Masterarbeit beschreibt den Entwicklungsprozess eines Switched-Capacitor DC-DC Konverters, zum Erzeugen einer negativen Spannung. Dies inkludiert konzeptionelle Betrachtungen, wie die Topologie und rechnerische Abschätzungen der Leistung, als auch das Design der Schaltung in Bipolar-CMOS-DMOS (BCD) Technologie und die Verifikation des Designs im Vergleich zu den konzeptuellen Abschätzungen.

Die Verwendung von triple-well NMOS und DeMOS wird aufgearbeitet. Zusätzlich benötigte Schaltungen wie Levelshifter und Spannungsbuffer werden erklärt. Weiters wird ein Ansatz zur Flächenoptimierung der verwendeten Transistorschalter präsentiert. Andere Betrachtungen, wie externe Komponenten und deren parasitäre Effekte, werden modelliert und diskutiert.

Stichworte: switched capacitor; DC-DC converter; charge pump; seriesparallel topology; negative voltage creation; switches; triple-well NMOS; DeMOS; area optimisation; external capacitor; parasitics.

# Acknowledgement

I would like to thank everyone who helped me creating this thesis. In particular I would like to thank:

- **Prof. Peter Söser** for being my supervisor for my master's thesis as well as for my seminar project and for being my mentor in my master's programme,

- **Infineon Technologies** for making it possible to work in a highly professional environment during the time of my study,

- Dr. Gerhard Maderbacher for being my supervisor at Infineon Technologies, guiding me into the right direction and

- all my **family and friends** for supporting me and for helping making all of this possible.

# Contents

| Т | itle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | i                                                                     |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| A | ffidavit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | iii                                                                   |

| Α | bstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | iv                                                                    |

| ĸ | urzfassung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | iv                                                                    |

| A | cknowledgement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | v                                                                     |

| C | ontents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | vii                                                                   |

| 1 | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                     |

| 2 | <ul> <li>Literature Research</li> <li>2.1 Level Shifters</li> <li>2.2 Gate Driving Circuits</li> <li>2.3 Drain Extended MOS Transistors</li> <li>2.4 Analysis and Optimization of Switched-Capacitor DC-DC Converters</li> <li>2.4.1 Slow Switching Limit</li> <li>2.4.2 Fast Switching Limit</li> <li>2.4.3 Combining SSL and FSL</li> <li>2.4.4 Comparison of SC Converter Topologies</li> <li>2.5 Triple-Well NMOS Switch</li> <li>2.6 Voltage Buffers</li> <li>2.7 Gate Drivers for Stacked MOSFETs</li> <li>2.8 DC Voltage Dependent Capacitor</li> </ul> | <b>3</b><br>4<br>6<br>7<br>8<br>9<br>10<br>11<br>11<br>13<br>14<br>15 |

| 3 | Concept<br>3.1 Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>18</b><br>18                                                       |

### Contents

| Conclusion                                            | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.5.2 Resonant Switched Capacitor Converter           | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

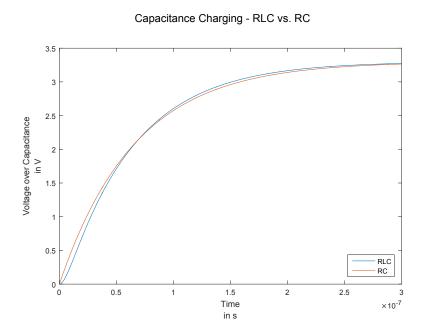

| 5.5.1 Linear Charging of Capacitance                  | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

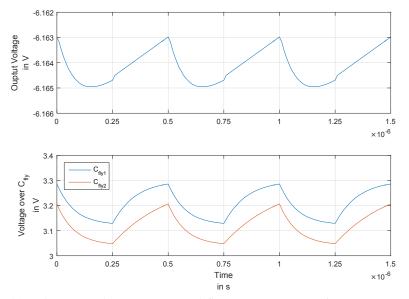

| 5.5 Simulation with Bond Wire and External Parasitics | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

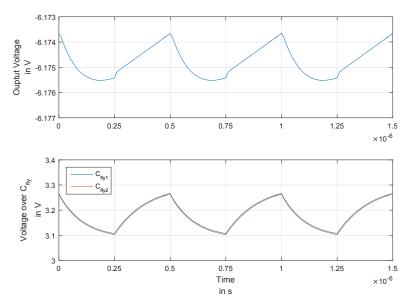

| 5.4 Ripple on Output and Flying Capacitances          | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.3 Corner Simulations                                | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.2.3 Charging Losses                                 | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.2.2 Design 2                                        | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.2.1 Design 1                                        | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| •                                                     | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Verification                                          | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

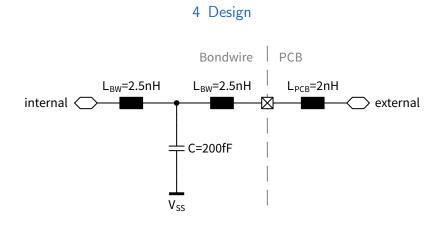

| 4.5.2 Modelling Bond Wires                            | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.5 Externals                                         | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 40<br>43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                       | 39<br>40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                       | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| •                                                     | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.2 Phase Selection                                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                       | <ul> <li>3.3 Slow and Fast Switching Limits <ul> <li>3.3.1 Slow Switching Limit</li> <li>3.3.2 Fast Switching Limit</li> <li>3.3.3 Results</li> </ul> </li> <li>3.4 External Capacitances <ul> <li>3.4.1 DC Voltage Dependency</li> </ul> </li> <li>Design <ul> <li>4.1 Phase Creation</li> <li>4.2 Switches <ul> <li>4.2.1 Switch One (S1)</li> <li>4.2.2 Switch Two (S2)</li> <li>4.2.3 Switch Three (S3)</li> <li>4.2.4 Switch Four (S4)</li> <li>4.2.5 Switch Five (S5)</li> <li>4.2.6 Switch Six (S6)</li> <li>4.2.7 Switch Seven (S7)</li> </ul> </li> <li>4.3 Complementary Source Follower <ul> <li>4.4 Level Shifter</li> <li>4.5 Externals</li> <li>4.5.1 Modelling External Capacitances</li> <li>4.5.2 Modelling Bond Wires</li> </ul> </li> <li>Verification <ul> <li>5.1 Output Resistance</li> <li>5.2 Area Consumption and Optimisation</li> <li>5.2.1 Design 1</li> <li>5.2.2 Design 2</li> <li>5.2.3 Charging Losses</li> </ul> </li> <li>5.3 Corner Simulations</li> <li>5.4 Ripple on Output and Flying Capacitances</li> <li>5.5 Simulation with Bond Wire and External Parasitics</li> </ul></li></ul> |

### Contents

| List of Figures |    |

|-----------------|----|

| List of Tables  | 75 |

| Acronyms        | 78 |

| Bibliography    | 79 |

# 1 Motivation

Most integrated circuits require different voltage levels for different modules to increase efficiency and performance, e.g. 1.5 V for digital supply, 3.3 V for analog domain, I/O supply voltages,...

Nevertheless, there are basically two possibilities, that these voltages can be provided:

- The first option is to externally place separate power supplies for all the different voltages needed. However this leads to higher costs, as additional external components are needed, in system integration.

- The second option therefore is to create different voltage domains internally, by deriving all voltages from a single supply voltage. This of course leads to higher design efforts, but is beneficial in having a more compact design and lower costs in system integration, if the needed power is not too high.

For today's system integration density it is important to focus on the second possibility mentioned. This of course includes downscaling as well as upscaling the given supply voltage. For upscaling, the use of Switched-Capacitor (SC) approaches is very common.

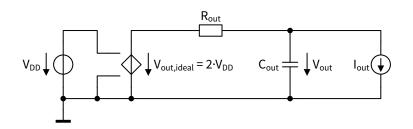

In this thesis the development of a Switched-Capacitor DC-DC (SC DC-DC) converter is explained, which is capable of creating an output voltage of ideally  $-2 \cdot V_{DD}$  from a positive supply voltage (V<sub>DD</sub>). In general the principles for positive and negative charge pumps, that have to be applied, are the same. However, there are a few more things to consider for dealing with node voltages below substrate voltage, that will also be explained in this thesis.

#### 1 Motivation

Additionally, the use of mathematical models for estimating the circuits performance is convenient, as this allows to determine the circuit's performance beforehand. By this, the influence of the circuit parameters such as flying capacitance values, switch on-resistances and switching frequency on the output resistance can be approximated in an easy way.

The main goal of this thesis is to provide a full development flow, starting from conceptual considerations, design and implementation of these concepts in Bipolar-CMOS-DMOS (BCD) technology and ending with verification of the concept by simulation results. Another important topic in IC development is saving area, therefore considerations of how to size the switches should also not be neglected. Considering the most important switches of the Switched-Capacitor (SC) design, there is quite a big potential in saving area, however keeping same circuit performance.

Before starting with the analog design of the SC DC-DC converter it is important to do some literature research in order get an overview of similar projects. From these projects some approaches respectively some ideas might also be applicable to this project.

Basically the research covers different parts of the circuit. This includes the overall design of the SC DC-DC converter, as well as smaller parts. For instance also level shifters will be needed for both shifting the phases for a full positive supply voltage ( $V_{DD}$ ) as well as transferring voltage levels from digital domain to analog domain. Furthermore, voltage buffers are needed in order to maintain appropriate gate voltages on the transistors during switching.

Therefore, mainly IEEE Xplore Digital Library has been searched for appropriate papers and the following documents have been selected and analysed.

## 2.1 Level Shifters

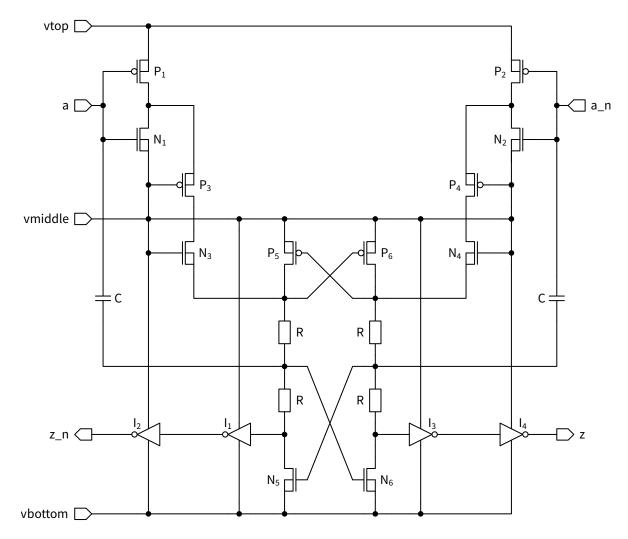

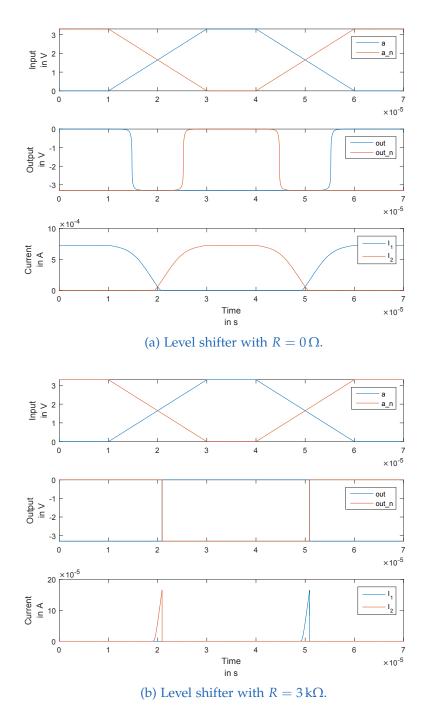

It is expected that level shifters will be needed in order to be able to properly drive some switches of the Switched-Capacitor DC-DC. In [1] the authors present a level shifting circuit that is capable of shifting the input voltage by  $V_{DD}$  respectively a multiple of  $V_{DD}$ . Firstly, a standard level shift circuit is explained. In this they introduce capacitances that couple the gates of the two input transistors with the gates of the output transistors and explain the influence of these capacitances.

Furthermore, a different approach is presented, having only one coupling capacitor but an additional inverter between the two output gates. Simulations show that this led to smaller rise and fall times. In the next steps, approaches for reaching higher offsets with multiples of  $V_{DD}$  are explained, based on the presented level shift circuit.

In the SC DC-DC converter design the following things can be considered from this paper:

- Designs for shifting by one time as well as two times of V<sub>DD</sub> are presented. It is also expected that the design will need both approaches in order to properly drive the gates of the transistors. The main difference is that in this case the voltages do not have to be shifted up, but they need to be shifted down, which leads to mirroring of the whole circuit.

- For the examples the authors use standard 1.2 V technologies in order to compare the differences. However, the approaches should be generally applicable in the 3.3 V domain too, as the explanation can be generalised to shifting multiples of V<sub>DD</sub>.

- The paper assumes a triple well process, such that every bulk can be directly connected to the source of the n-channel MOSFET (NMOS), in order to omit substrate losses. This might not be possible in other processes. However, as a triple well process is fundamentally needed in this project because the drain or source voltages of some NMOS are below substrate potential, this does not represent a problem.

## 2.2 Gate Driving Circuits

Apart from using level shifters, there are also other options for gate-control circuits of the switches. In [2] the authors are implementing an SC DC-DC converter that is capable of creating an output voltage that is about three times higher than the given input voltage. The converter should be able to start up without additional power sources. Converters that are based on inductors could omit this problem, but have the disadvantage of needing external inductive components that could cause interference. Furthermore the Dickson charge pump is mentioned as possible solution, however requiring a minimum start-up voltage [3].

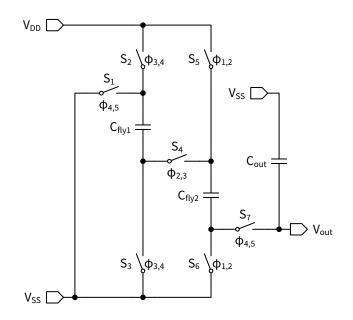

In [2] the series-parallel approach is used, where in one phase all capacitances are charged to  $V_{DD}$  and in the other phase these capacitances are connected in series on top of  $V_{DD}$ , in order to reach three times  $V_{DD}$ . Altogether seven switches are needed. Four are used for charging the two capacitances, two for each capacitor, so for the parallel connection. The other three are needed for the series connection in order to charge the output capacitance.

A main issue in both either the series-parallel or the Dickson type approach is the design of the switches. In general, the highest voltage that is applied to either drain or source terminal of a metal-oxide-semiconductor fieldeffect-transistor (MOSFET), which is used as a switch, needs to be available for properly driving the gate. Therefore, usually a separate power supply is needed, in order to turn the switches on or off.

Basically there are different possibilities to drive the gates of the switches.

- On the one hand, an additional step-up converter can be applied to supply the gates, which reduces the efficiency of the design. These could be for example created by either of the previously mentioned approaches.

- On the other hand, the needed gate voltages can be taken from the created output voltage, which implies that there is energy stored or it needs another circuit to ensure start-up.

In this paper the authors explain the control of the gate voltages of the nontrivial cases. Therefore, they mainly focus on the switches to  $V_{DD}$  as well as to the output switch. For the  $V_{DD}$ -switches they simply use an inverting structure.

The output switch needs to be off in one phase having  $V_{DD}$  and  $3 \cdot V_{DD}$  on its drain, respectively source and it needs to be on in the second phase when on both pins  $3 \cdot V_{DD}$  is applied. In this case, they make use of the voltages that are available on the flying capacitors during the two phases, to avoid the issue of having to create separate gate voltages.

The proposed series-parallel topology itself can be applied in this thesis, as the output voltage needs to be shifted by two times of  $V_{DD}$  too. The difference lies in the direction the voltage needs to be shifted. Therefore, the author's circuit can be used, mirrored to negative voltage direction.

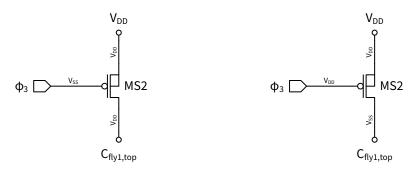

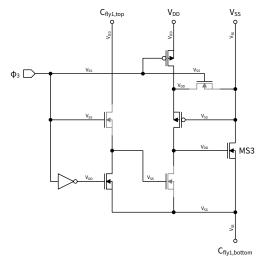

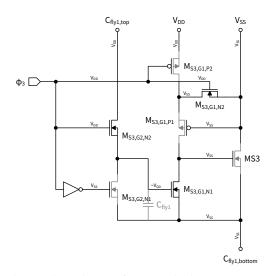

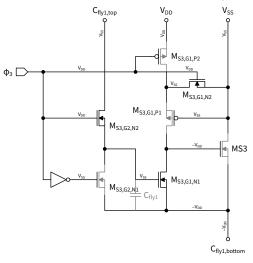

However, in this thesis the design of the switches is not as trivial as in the paper as there is a limit to the maximum drain-source voltage, that is applied to a single transistor. The authors do not face this problem as their  $V_{DD}$  is smaller referred to the used technology, so that they do not exceed the save operating area (SOA) when applying two times  $V_{DD}$  as drain-source voltage ( $V_{DS}$ ).

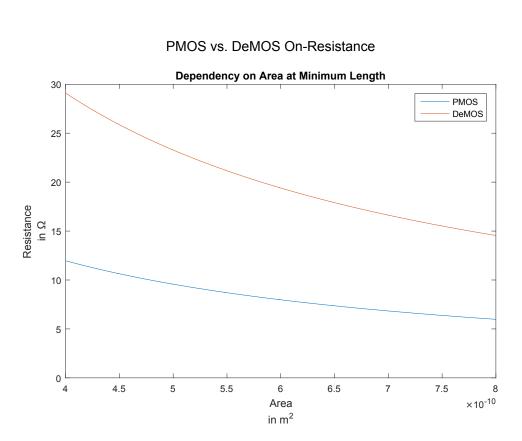

In the SC DC-DC design,  $V_{DD}$  is defined as 3.3 V and also the SOA is fixed to  $3.3 V \pm 10 \%$ . This means that the allowed maximum voltages are easily exceeded when only using single devices. To circumvent this problem either the transistors have to be cascoded or so-called drain-extended MOSFET (DeMOS) [4] [5] have to be used. The disadvantage in all these ideas comes with the increased R<sub>ON</sub>. However, also in the paper R<sub>ON</sub> is not at a minimum as the gate-source voltage is not at the transistor's extremum.

## 2.3 Drain Extended MOS Transistors

Papers [4] and [5] explain the advantages of drain-extended MOSFET (De-MOS). In general, transistors are designed for specific operating voltages. Digital parts of an integrated circuit usually have voltages of about 1.2 V or even lower, whereas analog circuits are commonly operated with 3.3 V or 5 V. In order to save costs, for these different voltages transistors have to be used accordingly. Commonly, the allowed drain-source voltage is the limiting factor in a circuit. This is also the case in the SC DC-DC design. Standard NMOS and p-channel MOSFET (PMOS) are available in this technology for the digital as well as for the analog (3.3 V) domain.

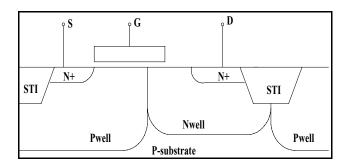

Presumably, there will be voltages of about two times  $V_{DD}$  on some transistors which usually makes the usage of a single transistor impossible. Therefore so called drain-extended MOSFET (DeMOS) can be used. Unlike standard MOSFETs, these have a prolonged drain region, that allows them withstand higher voltages. Taking an NMOS as an example the n+ doped area, where the drain is usually connected is moved further away from the gate oxide. In the gap below the gate oxide and the n+ drain region an n-well is placed, in order to prolong the channel. This is visible in figure 2.1.

Figure 2.1: Cross section of a DeMOS-NMOS [4].

The same is also valid for PMOS by interchanging p-doped and n-doped regions.

Another possibility to increase the operating voltage is the use of two gate oxides and two lightly-doped drain (LDD) implants, but this might not be available in every process as it leads to higher costs due to increased complexity. This approach is working in such a way that the LDD extension reduces the electric field below the gate at the drain end. Therefore, a higher drain breakdown voltage is achieved.

The authors mainly focus on the creation of the DeMOS without introducing additional process steps. Mainly, there are three parameters that can be chosen: the length of the gate, the overlap of the gate and the drain well and the distance between gate and drain edge.

As DeMOS transistors are available in this thesis' technology the use of these for some switches might be taken into consideration. However, the performance between these and cascaded MOSFETs has to be compared first.

# 2.4 Analysis and Optimization of Switched-Capacitor DC-DC Converters

In papers [6] and [7] the output impedance and therefore the performance of an SC converter is calculated. Therefore, the converter is modelled as an

ideal converter with an additional output impedance that represents the voltage drop from the ideal result. The authors analyse a two phase 3 V to 1 V ladder circuit. On this topology they determine the maximum limits that can be reached depending on the capacitor size, the switches' on-resistance (R<sub>ON</sub>) and the switching frequency (f<sub>sw</sub>).

The equivalent output resistance is calculated based on the charge flow during both phases. Therefore charge multiplier vectors are defined that describe the charge flow over the parts that cause efficiency loss. Further information can also be found in [8], [9] and [10].

#### 2.4.1 Slow Switching Limit

For the slow switching limit (SSL) the charge flow over all capacitors and voltage sources is looked at [7, pp. 8-10]. Here it is assumed that these ideal voltage sources are similar to precharged capacitors with infinitely high values of capacitance. For every phase the charge flow over every capacitor is written into a vector. This vector is normalised to the charge that is flowing into the output voltage source respectively out of the converter. Equation 2.1 shows the definition of such a vector for a specific phase  $\Phi$ , containing *n* capacitors.

$$a^{\Phi} = \begin{pmatrix} q^{\Phi}_{out} & q^{\Phi}_{1} & \cdots & q^{\Phi}_{n} & q^{\Phi}_{in} \end{pmatrix}^{T} \cdot \frac{1}{q_{out}}$$

$$= \begin{pmatrix} a^{\Phi}_{out} & a^{\Phi}_{c,1} & \cdots & a^{\Phi}_{c,n} & a^{\Phi}_{in} \end{pmatrix}^{T}$$

$$= \begin{pmatrix} a^{\Phi}_{out} & a^{\Phi}_{C} & a^{\Phi}_{in} \end{pmatrix}^{T}$$

(2.1)

Furthermore, one comes to the conclusion that  $a_C^{\Phi_1} = -a_C^{\Phi_2}$ , which obviously means that the sum of the charges that is flowing in and out of the capacitors in both phases is equal to zero. In a two phase system the vector  $a_C^{\Phi}$  only needs to be determined for one phase as the other vector can be achieved by changing the sign of every element. With given charge flow through every capacitor, the corresponding capacitor size and the switching frequency, the

slow switching limit can be determined by equation 2.2.

$$R_{SSL} = \sum_{\substack{i \\ capacitances}} \frac{a_{c,i}^2}{C_i \cdot f_{sw}}$$

(2.2)

By equation 2.2 also a suggestion of choosing the capacitances is given. In order to keep the resistance  $R_{SSL}$  low the capacitance should be chosen larger if more charge is flowing over this specific capacitance. Therefore, it is important to note that not every capacitance must necessarily have the same influence on the efficiency of the circuit. This is depending on the used topology.

#### 2.4.2 Fast Switching Limit

The other restriction is the fast switching limit (FSL) [7, pp. 10-12]. It depends on the charge that is flowing over the switches. Here it is not distinguished between phases, as only the charge flow over switches in their respective conducting phase is important. This yields a vector containing the charge flow over every switch (1 to *m*) as shown in equation 2.3. This vector can be simply derived from the capacitance charge vectors from the slow switching limit. Here it is important to notice that this vector is normalised to output charge flow too.

$$a_r = (q_{r,1} \cdots q_{r,m}) \cdot \frac{1}{q_{out}}$$

=  $(a_{r,1} \cdots a_{r,m})$  (2.3)

By having this vector the output impedance of fast switching limit (FSL) can be derivated. The result is shown in equation 2.4.

$$R_{FSL} = 2 \cdot \sum_{\substack{i \\ switches}}^{i} R_i \cdot a_{c,i}^2$$

(2.4)

Again it is obvious that best results will be achieved by appropriate choice of the switches' on-resistance ( $R_{ON}$ ). The more charge is flowing over the switch the smaller the on-resistance should be made.

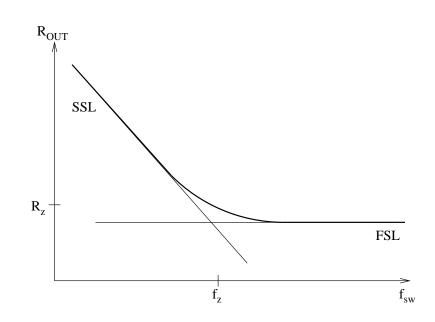

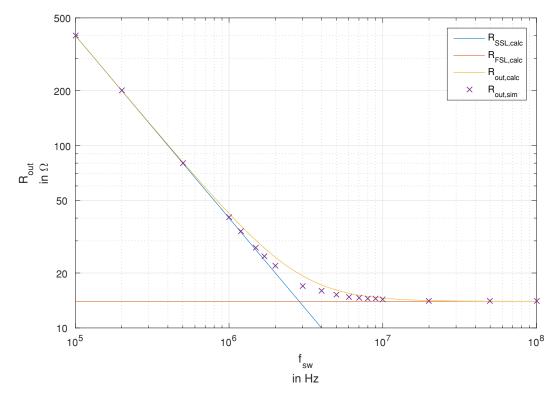

Figure 2.2: Output impedance depending on the switching frequency (f<sub>sw</sub>) showing the slow switching limit and fast switching limit [7, p. 19].

### 2.4.3 Combining SSL and FSL

The results of SSL and FSL can be approximated by a curve that is described by equation 2.5 [7, p. 19].

$$R_{out} = \sqrt{R_{SSL}^2 + R_{FSL}^2} \tag{2.5}$$

Figure 2.2 shows the approximated curve for the output impedance. At low frequencies the slow switching limit is dominating which is inversely proportional to switching frequency ( $f_{sw}$ ). For higher frequencies the fast switching limit becomes more important, as  $R_{FSL}$  is independent of  $f_{sw}$  and therefore a constant. Therefore, the best result, when operating the charge pump in open loop, is achieved by selecting a switching frequency that is at the intersection of the two curves at  $f_z$ .

### 2.4.4 Comparison of SC Converter Topologies

In [7, pp. 20-23] five different step-up converter topologies are evaluated:

- 1. Ladder,

- 2. Dickson Charge Pump,

- 3. Fibonacci,

- 4. Series-Parallel and

- 5. Doubler.

The topologies are compared for different conversion ratios. The seriesparallel converter performs well in SSL, but has drawbacks in FSL, whereas the Dickson Charge Pump and Ladder topology are better in FSL, but worse in SSL. Exponential converters (Fibonacci, Doubler) perform well in both cases, but would require devices that have different voltage ratings, which is usually not the case when using standard complementary metal-oxidesemiconductor (CMOS) processes.

# 2.5 Triple-Well NMOS Switch

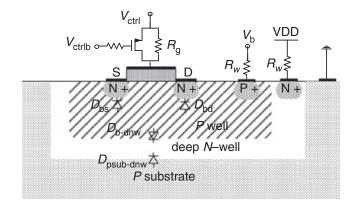

Standard NMOS transistors in CMOS have no isolation between substrate and the bulk terminal, as the bulk only represents a p+ doped region within the p-substrate. Therefore, it is not possible to put the bulk to another potential different than substrate potential. Triple-well NMOS transistors have a different structure. Based on a standard NMOS transistor two additional wells are added. The inner well is p-doped (p-well) whereas the outer well is n-doped (deep n-well) [11].

This leads to some advantages compared to standard NMOS transistors.

- The bulk terminal can be put to potentials that differ from the substrate, which can be beneficial in two ways.

- Firstly, the body-effect (change in threshold voltage as effect of non-zero bulk-source voltage) can be avoided, by connecting the bulk on the source terminal, as this can also be done in PMOS transistors.

Figure 2.3: Cross section of a triple-well NMOS transistor [11].

- Secondly, the drain- respectively source-terminal of the transistor may go below substrate potential. With a standard NMOS this would not be possible without forward biasing the bulksource diode. In triple-well transistors the bulk voltage can be set accordingly not to forward bias the mentioned diode.

- Furthermore, the triple-well structure also reduces substrate coupling effects, leading to a higher isolation of the transistor channel. Of course this is only the case if the well is set to a fixed and stable potential (AC ground).

The introduction of two additional wells also leads to two new well diodes, which are a diode from p-substrate to deep n-well and another diode from p-well to deep n-well. Therefore the n-well has to be set to a potential that is higher or equal than the bulk and the substrate potential. These diodes are also visible in figure 2.3.

As in this project a negative output voltage has to be generated and NMOS transistors will be needed as switches, it is inevitable to make use of NMOS devices whose bulk can be set to a different potential than substrate. However the main reason lies in preventing the forward biasing of the bulk-source diode and not in reducing substrate coupling effects.

## 2.6 Voltage Buffers

In paper [12] the authors describe different ways of implementing voltage buffers. One standard way is to use a two-stage operational amplifier (OPAMP) with negative feedback that is operated as voltage follower. However, when designing an OPAMP bandwidth and stability considerations have to be made. Therefore, another approach is described in this paper, which is the use of a complementary source follower, that has no closed loop feedback.

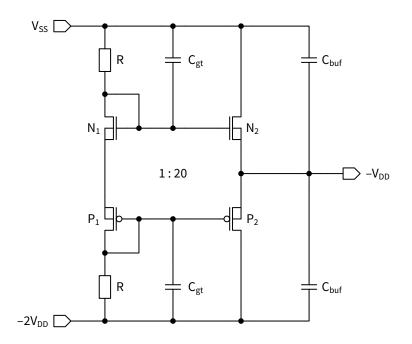

The first circuit that is presented is a simple complementary source follower. This circuit basically consists of two current paths. One path is responsible for biasing. Furthermore, all gate voltages of the diode connected transistors have to be kept at a reasonable operating point by the input voltage. The bias current is then mirrored by a predefined factor of the bias current to the second path. It is very effective as it has low quiescent current, good frequency characteristics and low voltage offset.

The other two circuits are a combination of the previously mentioned complementary source follower combined with a common source stage, that is driven by two error OPAMPs or by internal feedback. This topology combines the advantages of the two topologies, resulting in a higher voltage swing. The drawback lies in higher power and current consumption.

Basically, in this project the voltages  $V_{DD}$ ,  $V_{SS} = 0 \cdot V_{DD}$  and  $-2 \cdot V_{DD}$  will be available during all phases as these are either provided by the power supply or by the output capacitance. However, it is to be expected that a voltage buffer will be needed for creating  $-1 \cdot V_{DD}$  in order to correctly drive the gates of some switches. In some phases it might be possible to use the voltages that are provided by the flying capacitance.

There is no possibility to use additional capacitances as only four external capacitors are allowed to be used. These are two flying capacitors, one input and one output capacitor. Furthermore, also internal capacitances are restricted to a size of about 1 pF which should obviously not be sufficient for charging and discharging the gates of the switches without significant spikes on that voltage domain. Too large voltage spikes might cause problems when exceeding save operating area (SOA) as the allowed voltages

might be transcended. Furthermore, it would be of advantage if the current consumption during non-switching could be lower than during switching of phases.

The authors also mention the possible voltage or current swing. However, this is not important in this case, as the input voltage will not vary and stay constantly at negative supply voltage or at the output voltage. Furthermore, also good linearity can be put aside. As the voltage buffer has to be fast it is important to have a low output resistance, that is why the third proposal seems most useful.

Further voltage buffers, including enabling and power-down circuits with high-voltage switches can be found in [13].

# 2.7 Gate Drivers for Stacked MOSFETs

Nowadays, manufacturing processes are optimised towards, less power consumption, higher speed and maximum integration density. Therefore, also the operating voltage as well as the breakdown voltage is decreased. However, there are still many applications that require higher voltages. In general, there are two different possibilities to deal with high-voltage switching. One could either use specific devices, that can withstand these voltages, or the circuit can be adjusted so that the SOA is not exceeded [14].

Paper [14] presents a circuit technique of using stacked MOSFETs, where high voltages are equally split on all transistors. It is important that a minimum number of devices is used. If there were too many MOSFETs connected in series, this would unnecessarily increase the on-resistance of the switches and therefore lead to slower charging of the capacitances.

Basically, two MOSFETs are connected in series, where the gate of the lower NMOS is controlled by a control signal and the other NMOS is controlled by a voltage divider and with an additional capacitor. Furthermore, this capacitor needs to be scaled according to the gate-source capacitance ( $C_{GS}$ ) of the upper transistor and the switching frequency. The lower the switching frequency, the higher  $C_2$  has to be made. Even though the authors explain

their derivations only on a circuit with a multiplication factor of 2 the same can also be applied for a factor of *n* reaching  $n \cdot V_{DD}$ .

Finally, the authors prove their equations in a process rated for 5 V operation using 2 and 8 stacked devices. This is done by simulation as well as by experimental results.

As the devices in this project's technology are only specified for about  $3.3 \text{ V} \pm 10\%$  (with the exception of DeMOS, see section 2.3), it is therefore necessary to think about stacked MOSFETs that are used as switches, that can handle voltages of about 6.6 V.

However the following problems could arise:

- The voltage divider that is located between the output voltage and ground consumes current all the time. This reduces the efficiency of the converter. This current can be decreased by increasing the resistor values, but then the voltage drop increases, when current is taken from the voltage divider.

- To counteract this problem the capacitor for keeping the gate voltage stable could be increased, but it has to be considered, that the size of the integrated capacitors is limited and additional external ones may not be used.

The same principle for five stacked MOSFETs is also analysed in [15].

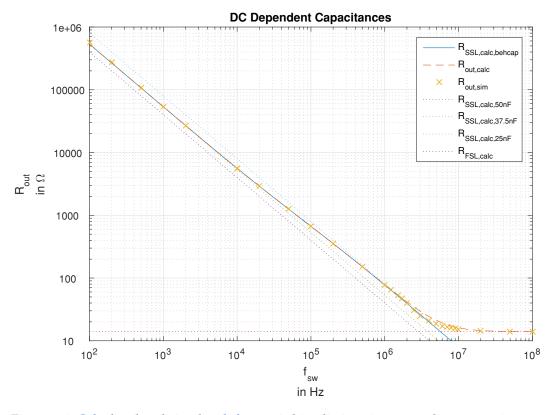

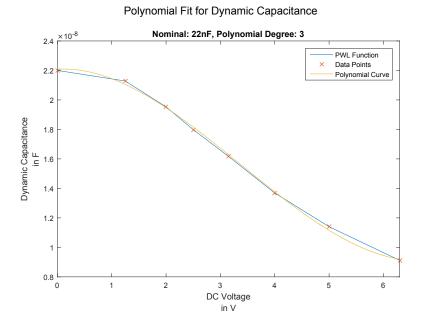

## 2.8 DC Voltage Dependent Capacitor

The capacitance value of a real capacitor can be described either as a static capacitance ( $C_S$ ) or a dynamic capacitance ( $C_D$ ). The difference between these lies in their definitions.  $C_S$  is defined as the ratio of charge (Q) and voltage (V) as shown in equation 2.6.

$$C_{\rm S} = \frac{Q}{V} \tag{2.6}$$

On the other hand  $C_D$  is defined as the differential change of charge for a change in voltage as described in equation 2.7.

$$C_{\rm D} = \frac{\mathrm{d}Q}{\mathrm{d}V} \tag{2.7}$$

For an ideal capacitor that is independent in terms of DC voltage or other effects the static capacitance and the dynamic capacitance are equal ( $C_S = C_D$ ) and therefore also the energy stored in such a capacitor can be calculated easily by equation 2.8.

$$E_{C,ideal} = \frac{C_{\rm S} \cdot V^2}{2} = \frac{C_{\rm D} \cdot V^2}{2}$$

(2.8)

However if the capacitance depends on the applied voltage this equation is not valid any more. By transforming equation 2.7 and taking the integral an equation for the charge at a specific voltage can be derived [16].

$$C_{\rm D}(V) = \frac{dQ}{dV}$$

$$dQ = C_{\rm D}(V) dV$$

$$\int_{q=0}^{Q(V)} dQ = \int_{v=0}^{V} C_{\rm D}(v) dv$$

$$Q(V) = \int_{v=0}^{V} C_{\rm D}(v) dv$$

(2.9)

Inserting equation 2.6 into 2.9 yields a relation between static capacitance and dynamic capacitance that is shown in equation 2.10.

$$C_{\rm S}(V) = \frac{Q(V)}{V} = \frac{\int_{v=0}^{V} C_{\rm D}(v) \, \mathrm{d}v}{V}$$

(2.10)

In general the dynamic capacitance  $(C_D)$  and not the static capacitance  $(C_S)$  is given in a datasheet. It is specified depending on the DC voltage applied to the capacitance.

In order to calculate the stored energy the power needs to be integrated over time, starting with the initial voltage on the capacitor until the desired voltage is reached. Inserting the I-V relation  $I = \frac{dQ}{dt} = C_D(V) \cdot \frac{dV}{dt}$  for capacitors gives equation 2.12. It is visible that the energy is depending on the voltage (V) over the capacitor and the dynamic capacitance (C<sub>D</sub>) function.

$$E(V) = \int_{t=t(v=0)}^{t=t(v=V)} v \cdot I \, \mathrm{d}t =$$

$$= \int_{v=0}^{v=V} v \cdot C_{\mathrm{D}}(v) \cdot \frac{\mathrm{d}v}{\mathrm{d}t} \, \mathrm{d}t \qquad (2.11)$$

$$E(V) = \int_{v=0}^{v=V} v \cdot C_{\mathrm{D}}(v) \cdot \mathrm{d}v \qquad (2.12)$$

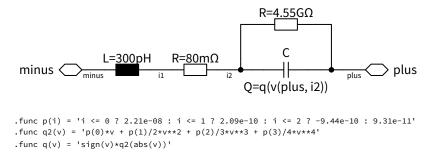

These considerations in terms of DC dependency of the external capacitors have to be taken into account in order make good estimates in terms of slow switching limit. that ensures accurate simulation results. Furthermore it is also important to use capacitance models with whom the simulator is able to model charge conservation [17]. Basically there are two possible capacitance models. One is capacitance based where the capacitance is described as a function of voltage. In this case the function for dynamic capacitance is needed. The second model is charge based where the charge needs to be described by static capacitance function and applied voltage [18, pp. 167-176].

Only the charge based model is capable of charge conservation. If charge conservation is not considered, this could lead to wrong results as there might be charge appearing or disappearing at a change in capacitance without any physically possible explanation.

In this section the basic, ideal concept of the Switched-Capacitor DC-DC converter is described. Furthermore also some calculations are explained that are used for estimating and optimising the overall performance. Moreover also the influence of flying capacitor sizes as well as different switch on-resistances is discussed.

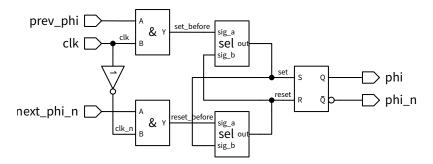

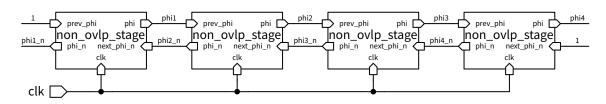

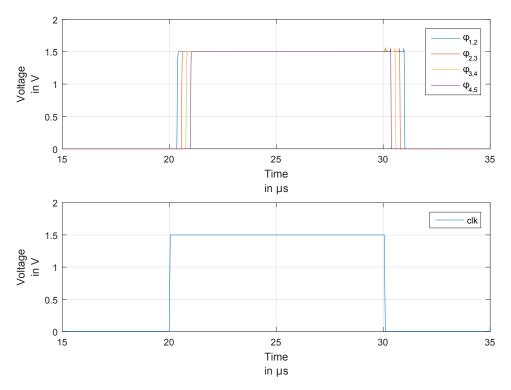

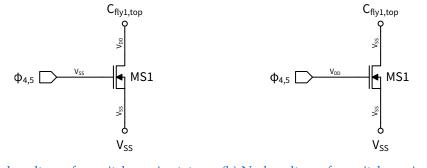

# 3.1 Topology