Samuel Weiser

## Enclave Security and Address-based Side Channels

### DOCTORAL THESIS

to achieve the university degree of Doctor of Technical Sciences; Dr. techn.

submitted to

Graz University of Technology

Assessors

Prof. Stefan Mangard Institute of Applied Information Processing and Communications Graz University of Technology

> Prof. Thomas Eisenbarth Institute for IT Security Universität zu Lübeck

> > Graz, June 2020

### AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present doctoral thesis.

Date, Signature

## Prologue

### Everyone has the right to life, liberty and security of person. Universal Declaration of Human Rights, Article 3

Our life turned digital, and so did we. Not long ago, the globalized communication that we enjoy today on an everyday basis was the privilege of a few. Nowadays, artificial intelligence in the cloud, smartified handhelds, low-power Internet-of-Things gadgets, and self-maneuvering objects in the physical world are promising us unthinkable freedom in shaping our personal lives as well as society as a whole. Sadly, our collective excitement about the "new", the "better", the "more", the "instant", has overruled our sense of security and privacy. New features, better design, more resources and instant satisfaction make us happily pay for it with our own data. To phrase it differently: technology sells, security does not. But what is our digital society worth if it not only fails to protect our privacy but seeks to intrude our most intimate moments? "Study after study has show [*sic*] that human behavior changes when we know we're being watched. Under observation, we act less free, which means we effectively *are* less free." [Sno19].

Providing a solid basis for a privacy-friendly future is and should be core motivation of security research. Unfortunately, we live in a highly fragmented ecosystem where each device and every piece of code exposes its users to distinct security issues. Even worse, huge amounts of new code are being produced day by day; and tons of insecure legacy software have not yet reached their natural decay. Today, managing the sheer complexity is by far one of the most pressing issues. As Bruce Schneier phrased it: "Complexity is the worst enemy of security, and our systems are getting more complex all the time." [Sch15]. Research today literally shouts for more principled security technologies.

The Herculean task of securing our systems inevitably needs to be broken down into small manageable pieces. To this end, *enclaves* are a promising candidate. Enclaves are a recent technology built into our computers that can effectively shield our sensitive data from adversarial access, even remotely. Studying their security guarantees, precise capabilities, and limitations form an exciting and active field of research with enough substance to not only fill this thesis with hopefully valuable insight.

### Acknowledgements

We should really care about what we really care about.  $A \ student$

My first expression of gratitude is devoted to all the great people at university and in school who passed on both their knowledge and passion to me. Starting with my class teachers, Mrs. Rief and Mrs. Hackl in elementary and middle school, respectively, also my high school class teacher Mr. Friedl established an environment in which I could develop my strengths. They stand as representatives for many more in school who invested not only thought and time into us "kids" but helped us grow mature. Special thanks need to be given to my maths teacher. Mrs. Gabriel, and my electronics teacher, Mr. Töglhofer, who laid a solid ground for my entrance to Graz University of Technology. Many professors at university would deserve similar credit for their passion for teaching and the high quality of content mediated to us. As representatives I would like to thank Prof. Brenner for giving me a smooth start into the world of information and computer engineering, Prof. KC Posch for lively yet in-depth discussions on university and society as a whole, and my supervisor Prof. Mangard for igniting my fervor to work on IT security and providing an open playground for research. Being part of the IAIK institute fills me with deep gratitude, not least because of the encouraging and employee-friendly working environment but mainly because of the people, be it our ingenious system administrators, our supportive secretaries, friendly cleaning personnel and – of course – our professors who conduct this whole show through technical guidance as well as personal and group leadership, investing countless hours of thought and work – many of which are unseen!

Introducing my companions, it feels hard to divide between colleagues and friends. Mastering the university competition collaboratively, I owe to – without particular order – Christian, Julia, Tino, the two Stefans, Michael, Manuel, Richard, and Philipp. Guiding me in crossing the finish line of my master's studies and introducing me to the world of research – Mario, this was your fault. Bear the honor of a hero! Also, I owe big thanks to Anders Fogh, who initiated the idea of differential address trace analysis, and to Andi for pursuing this idea together with me. My Ph.D. would not have been possible without the help and advice of Raphael in bringing our results to the "research market". Countless discussions, not only transient speculations but for sure fruitful exchange of ideas are attributed to our ingenious "attack office". I very much appreciate sharing the "defense office" with David, authentic coffee breaks within and beyond our SESYS group, and the last Corona months with my great flatmate, Supermario.

I am thankful to many more fellows who became good friends, both within the university and outside. Special appreciation goes to Karli, whose friendship, joyful character, and straightforwardness companions me since high school, Reinhard for our thoughtful and deep conversations as well as inspiring bouldering trips, Kree for sharing life outside university, be it nature or game board evenings, and JP for continuing our uplifting "meetings" remotely, and Raphael for many late-night battles in who is the last man working. I want to especially thank Thomas for our early-day visions in school and our longstanding friendship since then, and to Lisa for our profound encounters and close amity, which evolved out of our shared pursuit towards a Ph.D. I feel very grateful to Chris for sharing his passion about and enlightening my way into student ministry, Tom for countless times of making music together and having dignified conversations, the Blooming team for dreaming big and influencing Graz for good, Berny for his invaluable encouragements, humor, and his beard, Josh for all the nuggets of wisdom he shared, Bernd for ingenious jam sessions and longstanding friendship, Ann-Sophia for enriching my research stay in Darmstadt and bringing joy in the little matters, Mathias for our friendly and profound coffee meetings, Tabsi for releasing joy in our student group in a unique way, Johannes for bringing together people from different backgrounds, Timna for creating a welcoming atmosphere much like a close family, Lukas for bringing consistency and fun into our group, and his inner beard, and Elsie for many encouraging hours spent together. Words are not enough to express my gratitude to Fabi for sharing life and becoming best friends over the last three years, sharpening and shaping each other's lives. I am more than thankful to Stefan for countless valuable reflections on personality, while establishing a decent apple strudel tradition, Lea for brightening the lives of so many around her, Anna for spreading important news to us, Jonatan for his energy in organizing events and loving people into our group, Iris for her deep passion and love for people around her. Oliver for cheering us up with his artistic vein, Matthias for many late-night considerations on the core values of life and faith we share, Benji for spending three exciting months of our lives together, and all the other precious people enriching my ways during the last years, whom I cannot mention by name. I am looking forward to many more valuable encounters with you that are yet to come.

To save the best for last, I want to sincerely thank my family for the supportive and healthy environment I grew up and live in: my dad for putting family first in so many decisions, my mom for waiving her job as teacher to all the more teach us kids true love, my brothers for bearing with me and sharing not only a great childhood together, and for my grandparents, uncles and aunts for supporting us in every aspect possible. I thank my parents, Siegfried, and many others for conveying to me the beauty of faith, and John Lennox and William Lane Craig for giving me unshakable reason to believe. Your reward will be eternal! Finally, I want to express sincerest thanks to my God for giving me the gift of life, the beauty of nature, the peace of heart, the joy of fellowship; for carrying me through illnesses, for manifesting His completeness in my insufficiency. Heavenly dad, your goodness in blessing me with all those people surpasses my understanding!

### Abstract

Enclaves are a recent security technology for processors capable of safeguarding sensitive programs from malware and untrusted system operators alike. To understand the precise security properties of enclaves, we need more research. In this thesis, we study enclaves from two viewpoints. First, we take an outside perspective on the underlying hardware and effectively expand state-of-the-art enclave technology towards a broader range of application scenarios. Second, we inspect enclave's inner behavior with respect to side channels, showing novel attacks, and improving the automated search for unknown vulnerabilities.

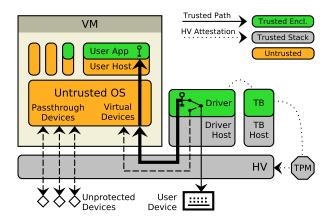

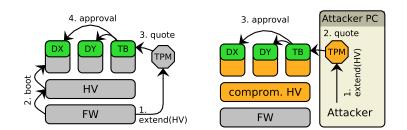

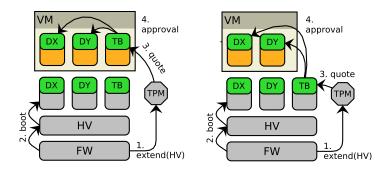

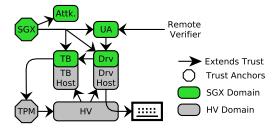

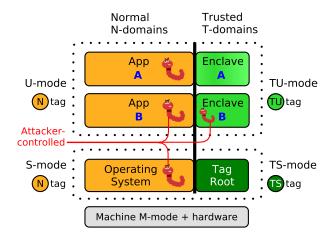

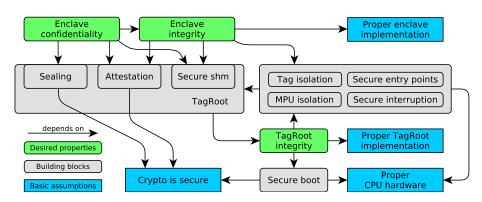

For the first part of this thesis, we ask ourselves three questions: (i) How can enclaves securely interact with their (physical) environment? (ii) How can enclaves be realized on tiny resource-constrained devices? (iii) How can we prevent enclaves from running wild? For (i) we give theoretical results and show how a trusted hypervisor can provide secure enclave interaction in a generic way. Connecting enclaves with hypervisors yields subtle but fatal attack vectors, which we address by using a Trusted Platform Module. For (ii) we design and prototype enclaves on the open RISC-V architecture. Our system dubbed TIMBER-V makes use of a specially tagged memory to provide tighter integration and higher flexibility than comparable schemes. For (iii) we encapsulate enclaves themselves within a sandbox called SGXJail to contain potential misbehavior.

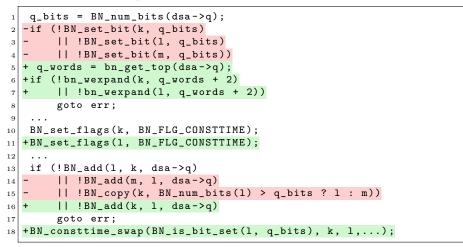

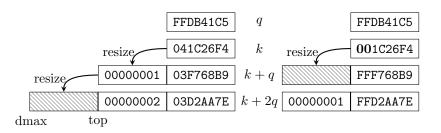

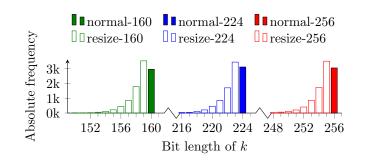

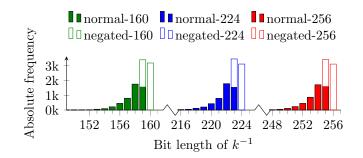

In the second part, we study side-channel attacks on enclaves with a focus on cryptographic software, again with three contributions. As shown by others, enclaves face stronger page-based side-channel attacks than previous systems. (i) We demonstrate that these attacks also directly affect the generation of cryptographic key material. To that end, we successfully attack RSA key generation in OpenSSL and provide patches to close the vulnerability. (ii) To automate sidechannel analysis, we develop Differential Address Trace Analysis (DATA). DATA covers not only classical cache attacks but also fine granular single-instruction or single-byte leakage, which was believed impractical to exploit until very recently. DATA helped discover previously unknown leakage in OpenSSL. (iii) For a systematic study, we adapt DATA to detect leakage of secret nonces in DSA-like cryptosystems. Our analysis reveals known and several unknown vulnerabilities in all essential DSA computation steps of OpenSSL and others, many of which allow full key recovery. Our reports helped fix many of the issues.

# Table of Contents

| Prologue         |                                                    |                                                                                                                                                                                           |                                                                                                                        |  |  |  |  |  |

|------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Acknowledgements |                                                    |                                                                                                                                                                                           |                                                                                                                        |  |  |  |  |  |

| Abstract         |                                                    |                                                                                                                                                                                           |                                                                                                                        |  |  |  |  |  |

| 1                | <b>Intr</b><br>1.1<br>1.2                          | Deduction<br>Challenges                                                                                                                                                                   | <b>1</b><br>2<br>3                                                                                                     |  |  |  |  |  |

| Ι                | En                                                 | clave Security                                                                                                                                                                            | <b>5</b>                                                                                                               |  |  |  |  |  |

| 2                | <ul><li>From 2.1</li><li>2.2</li><li>2.3</li></ul> | Intel Software Guard Extensions (SGX)                                                                                                                                                     | <b>7</b><br>7<br>8<br>9<br>10<br>10<br>13<br>14<br>15<br>17<br>17<br>19<br>20                                          |  |  |  |  |  |

| 3                | <b>SG2</b><br>3.1<br>3.2<br>3.3                    | Trusted Paths       Threat Model and Challenges         3.2.1       Distinction from SGX         3.2.2       Threat Model         3.2.3       Challenges         SGXIO       Architecture | <ul> <li>23</li> <li>24</li> <li>27</li> <li>27</li> <li>28</li> <li>29</li> <li>30</li> <li>30</li> <li>31</li> </ul> |  |  |  |  |  |

|   |      | 11 0                                                                                                                                                        | 32<br>33   |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   |      | 0                                                                                                                                                           | 34         |

|   | 3.4  | <i>v</i> 1 0                                                                                                                                                | 35         |

|   | 0.1  | 0                                                                                                                                                           | 35         |

|   |      | 8                                                                                                                                                           | 36         |

|   |      | 01                                                                                                                                                          | 37         |

|   |      |                                                                                                                                                             | 39         |

|   |      |                                                                                                                                                             | 40         |

|   | 3.5  |                                                                                                                                                             | 40         |

|   | 3.6  | v 1                                                                                                                                                         | 42         |

|   | 3.7  | 8 8                                                                                                                                                         | ±2<br>44   |

|   | 3.8  |                                                                                                                                                             | ±4<br>44   |

|   | 3.0  |                                                                                                                                                             | 14         |

| 4 |      | 00 V                                                                                                                                                        | 15         |

|   | 4.1  | 0                                                                                                                                                           | 47         |

|   | 4.2  | 2 0                                                                                                                                                         | 48         |

|   | 4.3  | 0                                                                                                                                                           | 19         |

|   |      |                                                                                                                                                             | 49         |

|   |      |                                                                                                                                                             | 52         |

|   |      | 4.3.3 Trusted Services                                                                                                                                      | 53         |

|   | 4.4  | TagRoot Trust Manager                                                                                                                                       | 54         |

|   |      | 4.4.1 Trusted OS Services                                                                                                                                   | 55         |

|   |      | 4.4.2 Trusted Enclave Services                                                                                                                              | 56         |

|   | 4.5  | Dynamic Memory Management                                                                                                                                   | 58         |

|   |      |                                                                                                                                                             | 58         |

|   |      |                                                                                                                                                             | 59         |

|   |      |                                                                                                                                                             | 61         |

|   | 4.6  |                                                                                                                                                             | 61         |

|   | 4.7  | -                                                                                                                                                           | 64         |

|   | 4.8  |                                                                                                                                                             | 67         |

|   |      |                                                                                                                                                             | 67         |

|   |      | 07                                                                                                                                                          | 58         |

|   |      |                                                                                                                                                             | 71         |

|   |      |                                                                                                                                                             | 73         |

|   | 4.9  | ·                                                                                                                                                           | 74         |

|   | 1.0  |                                                                                                                                                             | 74         |

|   |      |                                                                                                                                                             | 74         |

|   | 1 10 |                                                                                                                                                             | 75         |

|   |      |                                                                                                                                                             | 76         |

|   | 4.11 |                                                                                                                                                             | 0          |

| 5 |      |                                                                                                                                                             | 7 <b>7</b> |

|   | 5.1  |                                                                                                                                                             | 79         |

|   | 5.2  |                                                                                                                                                             | 80         |

|   |      |                                                                                                                                                             | 81         |

|   |      | 5.2.2 Attack Vectors $\ldots \ldots \ldots$ | 81         |

|          |               | 5.2.3 API attacks                                                                        | 83        |

|----------|---------------|------------------------------------------------------------------------------------------|-----------|

|          | 5.3           | SGXJail                                                                                  | 83        |

|          |               | 5.3.1 SGXJail via Software Confinement                                                   | 83        |

|          |               | 5.3.2 Implementation Details                                                             | 86        |

|          |               | 5.3.3 Evaluation                                                                         | 87        |

|          |               | 5.3.4 HSGXJail via Hardware Confinement                                                  | 91        |

|          | 5.4           | Related Work                                                                             | 94        |

|          | 5.5           | Discussion                                                                               | 95        |

|          | 5.6           | Summary                                                                                  | 96        |

|          | 0.0           | Summary                                                                                  | 00        |

| II       | Α             | ddress-based Side Channels                                                               | 97        |

| 0        | а <b>с</b>    |                                                                                          | 00        |

| 6        |               | ware Side Channels                                                                       | <b>99</b> |

|          | 6.1           | Side-channel Attacks                                                                     | 100       |

|          |               | 6.1.1 Microarchitectural Attacks                                                         | 101       |

|          | 0.0           | 6.1.2 Attacks in SGX Settings                                                            | 101       |

|          | 6.2           | Side-channel Vulnerabilities                                                             | 103       |

|          |               | 6.2.1 Modular Exponentiation                                                             | 103       |

|          |               | 6.2.2 ECDSA Scalar Multiplication                                                        | 105       |

|          |               | 6.2.3 GCD                                                                                | 105       |

|          |               | 6.2.4 Modular Inversion                                                                  | 105       |

|          |               | 6.2.5 Modular Reduction                                                                  | 106       |

|          | 6.3           | Side-channel Defenses                                                                    | 106       |

|          |               | 6.3.1 Closing Side Channels                                                              | 106       |

|          |               | 6.3.2 Closing Side-channel Vulnerabilities                                               | 108       |

|          |               | 6.3.3 Detecting Side-channel Vulnerabilities                                             | 110       |

| <b>7</b> | $\mathbf{RS}$ |                                                                                          | 115       |

|          | 7.1           | Threat Model                                                                             | 118       |

|          | 7.2           | RSA Key Generation                                                                       | 118       |

|          |               | 7.2.1 Binary Euclidean Algorithm                                                         | 119       |

|          | 7.3           | Attacking RSA Key Generation                                                             | 121       |

|          |               | 7.3.1 Idealized Attacker                                                                 | 121       |

|          |               | 7.3.2 Controlled-channel Attacker                                                        | 122       |

|          |               | 7.3.3 Exploiting the Information Leak                                                    | 124       |

|          |               | 7.3.4 Generalization                                                                     | 126       |

|          | 7.4           | Attack Evaluation                                                                        | 127       |

|          |               | 7.4.1 Implementation Details                                                             | 127       |

|          |               | 7.4.2 Mounting the Attack $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 128       |

|          |               | 7.4.3 Key Recovery Complexity                                                            | 129       |

|          | 7.5           | Patching OpenSSL                                                                         | 131       |

|          | 7.6           | Further Vulnerabilities                                                                  | 132       |

|          |               | 7.6.1 Responsible Disclosure                                                             | 133       |

|          | 7.7           | Summary                                                                                  | 133       |

| 8                     | DA'   | A: Differential Address Trace Analysis              | 135   |  |  |  |

|-----------------------|-------|-----------------------------------------------------|-------|--|--|--|

|                       | 8.1   | Related Work                                        | . 138 |  |  |  |

|                       | 8.2   | Differential Address Trace Analysis                 | . 139 |  |  |  |

|                       |       | 8.2.1 Threat Model                                  | . 139 |  |  |  |

|                       |       | 8.2.2 Methodology                                   | . 140 |  |  |  |

|                       |       | 8.2.3 Address-based Information Leakage             | . 140 |  |  |  |

|                       |       | 8.2.4 Recording Address Traces                      | . 143 |  |  |  |

|                       |       | 8.2.5 Finding Trace Differences                     |       |  |  |  |

|                       | 8.3   | Implementation and Optimizations                    | . 146 |  |  |  |

|                       | 8.4   | Evaluation and Results                              | . 147 |  |  |  |

|                       |       | 8.4.1 Analysis Results                              |       |  |  |  |

|                       |       | 8.4.2 Performance                                   |       |  |  |  |

|                       |       | 8.4.3 Discussion                                    | . 152 |  |  |  |

|                       | 8.5   | Summary                                             | . 153 |  |  |  |

|                       |       |                                                     |       |  |  |  |

| 9                     | -     | Numbers – Big Troubles. On Nonce Leakage in (EC)DSA |       |  |  |  |

|                       | 9.1   | Background                                          |       |  |  |  |

|                       |       | 9.1.1 Digital Signatures                            |       |  |  |  |

|                       |       | 9.1.2 The Hidden Number Problem                     |       |  |  |  |

|                       | 9.2   | Automated Nonce Leakage Detection                   |       |  |  |  |

|                       |       | 9.2.1 Methodology                                   |       |  |  |  |

|                       |       | 9.2.2 Detecting Nonce Leakage                       |       |  |  |  |

|                       |       | 9.2.3 DATA GUI                                      |       |  |  |  |

|                       | 9.3   | Vulnerability Analysis Overview                     |       |  |  |  |

|                       | 9.4   | Detailed Analysis                                   |       |  |  |  |

|                       |       | 9.4.1 Nonce Representation                          |       |  |  |  |

|                       |       | 9.4.2 Nonce Generation                              |       |  |  |  |

|                       |       | 9.4.3 DSA Exponentiation                            |       |  |  |  |

|                       |       | 9.4.4 ECDSA Scalar Multiplication                   |       |  |  |  |

|                       |       | 9.4.5 Modular Inversion                             |       |  |  |  |

|                       |       | 9.4.6 Modular Multiplication (V10)                  |       |  |  |  |

|                       | 9.5   | SGX Controlled-Channel Attack on (V5)               |       |  |  |  |

|                       | 9.6   | Evaluation                                          |       |  |  |  |

|                       | 9.7   | Discussion                                          |       |  |  |  |

|                       | 9.8   | Summary                                             | . 184 |  |  |  |

| С                     | onclu | sion and Outlook                                    | 185   |  |  |  |

| EĮ                    | pilog | le                                                  | 187   |  |  |  |

| List of Contributions |       |                                                     |       |  |  |  |

| Bi                    | bliog | raphy                                               | 191   |  |  |  |

# Introduction

### Trust takes years to build, seconds to break, and forever to repair. *Abraham Lincoln*

Software vulnerabilities are a prevalent issue for the security of computing devices. More than 17.000 software vulnerabilities were reported within the last year<sup>1</sup> [NIS], 57% of which are ranked with high or critical severity. As distributed, networked computing becomes omnipresent in the Internet of Things (IoT), the risk of damage even increases, allowing remote exploits on a large scale. In the recent past, we have been witnessing attacks on million devices, like cameras and routers [NJC16], cars [MV15], cardiac devices [Lar17], and light bulbs [Ron+17], to name a few. Also, due to long service life, the security of such devices becomes decisive, making exploitation only a matter of time. A significant reason for this threat is code complexity, which makes traditional secure design paradigms like software verification or testing reach its limits. These security issues attenuate future use cases in the cloud or the IoT dealing with sensitive corporate or personal data since a compromise could have immediate monetary, legal, or privacy consequences [Hel17].

Rather than trying to achieve full system security, a promising line of research shifted the focus on securing sensitive code only and executing it in architecturally isolated containers, often referred to as enclaves. An enclave is protected against all non-enclave code by the hardware. Thus, the security of an enclave solely relies on the computing hardware and the enclave code itself. At the same time, the whole operating system can be safely considered untrusted from an enclave's perspective.

<sup>&</sup>lt;sup>1</sup>This refers to the period between 01/01/2019 and 31/12/2019.

Intel SGX [Int16a] made enclaves available to the public via its x86 mainline CPUs. SGX targets high-performance cloud computing, where the cloud provider currently needs to be trusted entirely, as well as Digital Rights Management (DRM). Research has devised various scenarios of SGX, ranging from generic containers [BPH15; Arn+16; Shi+17b; TPV17] to specific application scenarios [Sch+15; PVC18; Lin+16; Bre+17]. Being relatively new, the security of enclaves is not as well understood as traditional concepts. In the following, we discuss open challenges and present our contributions.

### 1.1 Challenges

Despite the ability of enclaves to significantly improve application security, various new challenges arise. In this thesis, we address the following challenges:

- 1. Secure I/O. While Intel SGX securely shields a piece of code inside an enclave, it does not provide means for enclaves to communicate with an end user securely. This lack of secure I/O renders many potential application scenarios impractical, as sensitive user input like passwords or credit card information could be eaves-dropped before it arrives in the enclave. Also, presenting enclave output securely to the end user faces similar issues.

- 2. Small and Open Systems. Second, enclave technology is not yet as open as required for supporting a diverse ecosystem. While Intel SGX is the culmination of a long history of research on enclaves, its proprietary nature prohibits more in-depth security analysis. Attack scenarios range from speculation-based vulnerabilities [Bul+18] to deliberate backdoors [Dom18]. Open enclave systems, e.g., for the RISC-V [Ris] processor architecture, are necessary for transparent security analysis. Enclaves have been brought to larger RISC-V processors [CLD16] as well as to embedded systems [Eld+12; Noo+13; Göt+15; Noo+17; Koe+14; Bra+15; Arm17]. However, prior to our research, no enclave system existed for small RISC-V microcontrollers useful for deeply embedded IoT applications.

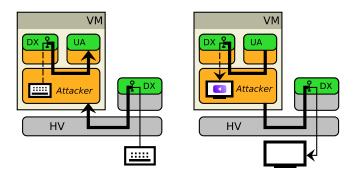

- 3. Enclave Malware. There is a flip side to enclave technology, as one can misuse them for malicious activity. Similar to rootkits [Kin+06; MY07], enclaves can effectively hide malware [Rut13; DF14; CD16]. Currently, no reasonable defense against enclave malware has been proposed or implemented.

- 4. Side Channels. Enclave technology does not solve the issue of software side-channel attacks [Sch+17; Bra+17b]. Even worse, Intel SGX aggravates this threat via novel deterministic side channels [XCP15]. While the research community is exploring these new attack techniques, it is unclear how popular cryptographic libraries such as OpenSSL and SGX-SSL [Int19] are affected by those attacks. Finally, searching for side-channel vulnerabilities in production software such as OpenSSL is not only tedious but also error-prone. This is mainly due to a lack of proper tool support side-channel analysis tools suffer from imprecision, accuracy, and performance issues.

### **1.2** Contributions and Outline

This thesis is split into two parts, where each contribution is represented by one chapter. We preface each part with an introductory chapter covering background information and related work. We list our publications as well as further collaborations in the end.

**Part I** discusses enclaves from an architectural perspective (challenge 1–3):

In Chapter 3, we develop the first concept for secure and generic user interaction with Intel SGX enclaves called SGXIO. To do so, we augment SGX with a small and trusted hypervisor. The key contribution is a proper binding of enclaves with the trusted hypervisor by utilizing a Trusted Platform Module (TPM). This work was published at CODASPY'16 [WW17a].

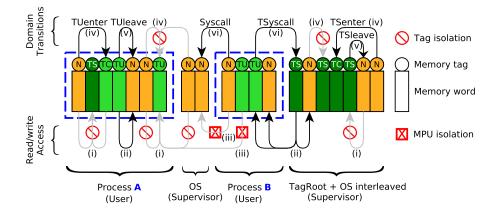

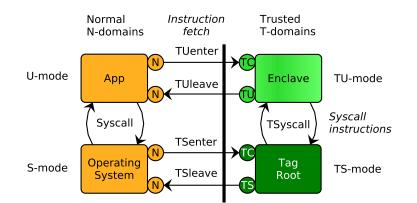

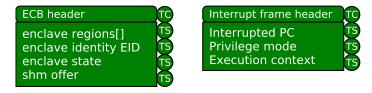

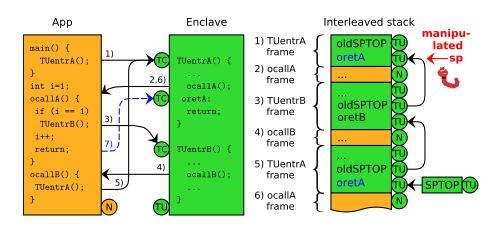

In Chapter 4, we, for the first time, bring enclaves to small RISC-V microcontrollers. To address the issue of limited memory, we devise novel tag-based isolation, which allows dynamic enclave memory management. Our scheme further enables novel use cases, such as interleaving of trusted and untrusted data on the same application stack or heap, thus reducing overall memory fragmentation. This work was published at NDSS'19 [Wei+19b].

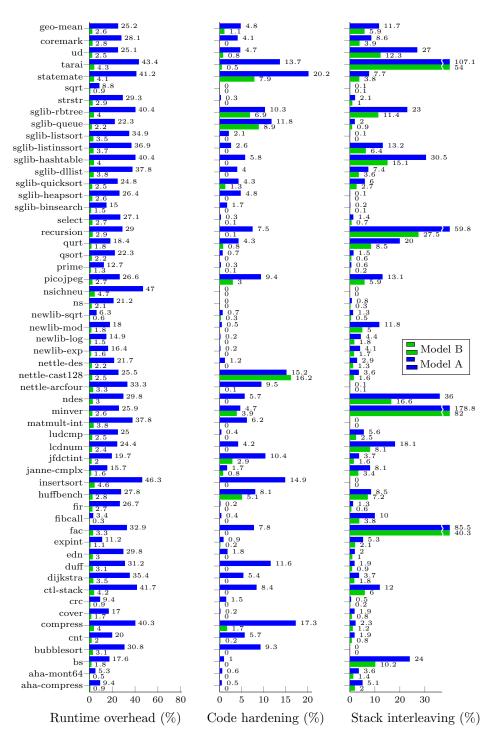

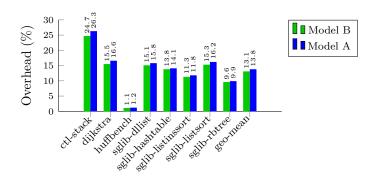

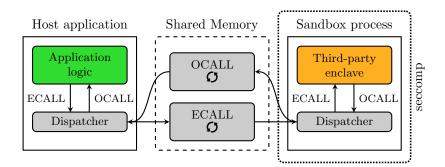

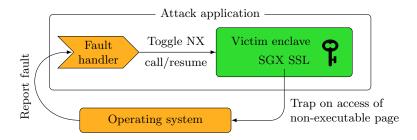

In Chapter 5, we show how to prevent potential enclave malware from attacking the system. Enclave malware might attack its host application due to a lack of bi-directional isolation between enclaves and applications [SWG19]. We propose enclave sandboxing as a generic defense against enclave malware and show how enclave sandboxing can be efficiently instantiated both in software and in hardware. This work was published at RAID'19 [Wei+19a].

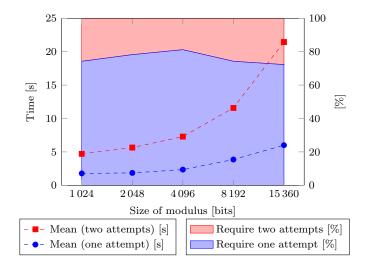

Part II discusses enclaves concerning side-channel vulnerabilities (challenge 4): In Chapter 7, we demonstrate novel side-channel attacks on cryptographic key generation. The use of SGX exposes key-generation algorithms to side-channel attacks, which had been overlooked so far. To highlight this issue, we demonstrate the first single-trace attack on RSA key generation in SGX-SSL [Int19] and recover the secret key in 100% of the cases. Our proposed countermeasures helped fix the vulnerability. This work was published at ASIACCS'18 [WSB18a].

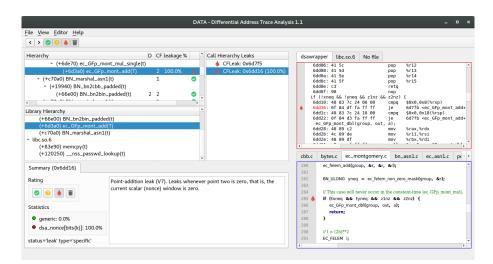

In Chapter 8, we develop Differential Address Trace Analysis (DATA). Rather than addressing specific attacks only, DATA is capable of uncovering arbitrary software side-channel vulnerabilities that rely on address information, including cache attacks [Per05], controlled-channel attacks [XCP15], DRAM-based attacks [Pes+16], and branch shadowing attacks [Lee+17b]. We implement DATA in a fully automated evaluation tool and use it to discover vulnerabilities in OpenSSL and PyCrypto. This work was published at USENIX'18 [Wei+18a].

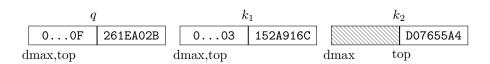

In Chapter 9, we refine DATA towards detecting nonce leakage vulnerabilities in (EC)DSA-like cryptosystems. We systematically analyze the whole lifetime of nonces in OpenSSL, LibreSSL, and BoringSSL. We report various side-channel vulnerabilities across all essential computation steps, most of which stem from leaky Bignumber implementations. Our work helped fix many of the issues and was accepted for publication at USENIX'20 [Wei+20].

To make our results reproducible and help other researchers advance upon it, we open-sourced various code developed for this thesis.

# Part I

# **Enclave Security**

# From Bugs to Enclaves. A Primer

Whoever is careless with the truth in small matters cannot be trusted with important matters.

Albert Einstein

Everything in a computer system is built on trust: trust in individual components, trust in their composition, and trust in the humans interacting with the system. A minor inadvertence inside a single core component, a wrong assumption about the user, and all trust might collapse like a house of cards. Ideally, the construction of components into a complete system is such that trust can be reduced to the bare minimum necessary, that is, to the piece of code and hardware responsible for managing critical tasks.

In this chapter, we first introduce the reader to two broad classes of attacks, which help understand the ideas and concepts presented later on. Afterward, we discuss the history of isolation technologies and finally introduce enclaves, the core subject for this part of the thesis.

### 2.1 Attack Scenarios

The landscape of attack scenarios is almost as diverse as the number of protection mechanisms. For this work, we cluster them into attacks on the inner behavior of a program and attacks on a program's environment in a larger system. While the first group of attacks exploit software vulnerabilities *within* a single program, the second group of attacks are performed *across* different programs by tampering with their execution environment. Often, a single software vulnerability in one program serve as an entry point into the whole system. Security architectures

shall uphold security guarantees of the system – even in case a program is compromised. Our actual contribution lies in the latter – security architectures. Although many security architectures involve trusted code components that need to be free of vulnerabilities, we focus on the design of security architectures rather than their correct implementation. Nevertheless, in the following, we outline both scenarios. We first discuss software vulnerabilities by touching on their threat models, describing prominent attacks, and giving countermeasures. Next, we discuss security architectures by elaborating on their responsibilities and the underlying threat model, introducing the trusted computing base, and highlighting important research goals to put this thesis into context.

### 2.1.1 Bug Alert! On Software Vulnerabilities

Software security focuses on analyzing the security of a given program with respect to its intended behavior. In this setting, one considers the whole operating environment – including the operating system and hardware – as secure. However, an attacker might play with the program's legitimate communication interface to trick the program into misbehaving. Typically, one precludes malicious intent of the programmer, such as backdoors coded into the program. Instead, one assumes that an honest but imperfect programmer made some inadvertent programming bugs. If those bugs affect the security of the system, they are called vulnerabilities. An attacker might exploit such a vulnerability by providing specially crafted input to the program.

Early attacks managed to directly inject or modify code at runtime, e.g., via a buffer overflow. However, this is not possible anymore with current systems. Instead, an attacker nowadays typically tries to manipulate control data and, thus, change the control flow of an application. By overwriting a code pointer, an attacker can divert the control flow to existing code snippets, resulting in so-called control-flow hijacking attacks. This gives an attacker the capability to perform touring-complete computation. From a functional perspective, an attacker has managed to transform the normal state machine of a program into a more expressive *weird machine* [Bra+11]. In its strongest form, a control-flow hijacking attack allows arbitrary code execution at the attacker's discretion. One of the most generic and powerful control-flow hijacking attacks is return-oriented programming (ROP) [Sha07], which overwrites return addresses to create arbitrary attack payloads. Similar attacks exist for overwriting function pointers [Che+10; Ble+11; Lan+15; CW14; Gök+14; Sch+15] or signal handlers [BB14].

Research on vulnerability defenses covers a wide range of strategies. The ultimate goal is to prove a program free of bugs, *i.e.*, verify its functionality against a given model. Typically, one matches software against a formal model, specified in some abstract language. Writing such a verification code can easily outweigh the effort for coding the program itself. For example, the development effort for the seL4 microkernel took 2.2 person-years, whereas the correctness proof took 20.5 person-years [Kle+14]. Hence, one tends to invest such costs only in high assurance systems [Kle+18]. Moreover, many program verification

techniques suffer from complexity issues such as state explosion [Val96]. Software testing reduces the state space at the expense of looser guarantees [MSB11].

Rather than analyzing precise functionality, a different line of research focuses on invariants that are inherent to most programs. For example, memory safety tackles the semantic gap between a programming language and the compiled binary from the perspective of objects in memory. The goal is to maintain invariants such as spatial memory safety, temporal memory safety, and type safety across the compilation step. These safety properties eradicate buffer overflow attacks, dangling pointers, or type confusion attacks. Rust already integrates memory safety in the language design [Rus]. Unfortunately, a large body of legacy code remains unprotected, and one resorts to weaker protection schemes, such as address-space layout randomization (ASLR) [PaX03], stack canaries [Cow98; PaX15], and shadow stacks [CH01]. While stronger control-flow integrity (CFI) [Aba+05; Kuz+14] can eradicate control-flow attacks, they leave data-only attacks [Car+15; Isp+18] unaddressed. A good overview of the struggle towards memory safety is given in [Sze+14].

### 2.1.2 Intrusion Alert! On Security Architectures

Having dug into the security of a single program, we now look at a complete system of multiple interacting components. In particular, we are interested in cases where not all components are behaving well. Such misbehavior might be due to the exploitation of software vulnerabilities. Alternatively, the user might unwittingly have installed malicious software. In many cases, the execution of potentially untrusted code is even unavoidable (cf. JavaScript execution in browsers) or part of the business model (cf. cloud computing). No matter how an attacker might infiltrate a system, security architectures shall maintain the secure operation of the other components in this case.

In light of powerful control-flow hijacking attacks, one typically assumes that an attacker has *arbitrary code execution*. That is, the attacker can execute arbitrary CPU instructions on the victim system an unlimited number of times, and interact with the victim system to exfiltrate gained information, or inject new instructions. It is the goal of the attacker to illegitimately access sensitive data, e.g., by elevating privileges and bypassing protection mechanisms. Note that the availability of the system is not necessarily the goal of security architectures, and the attacker might successfully mount denial-of-service attacks. Instead, security architectures shall protect the secrecy (or confidentiality) and integrity (or authenticity) of sensitive data even in case of intrusion. Protection involves proper isolation of different security domains and safeguarding their interaction.

Each security architecture builds upon a core set of components that are crucial for security and, hence, need to be trusted. Those components are also referred to as the trusted computing base (TCB). Any vulnerability inside the TCB is considered fatal for overall security. The TCB typically includes CPU hardware but also software components such as the operating system and user programs that are entrusted access to sensitive data. Research on security architectures is two-fold. First, one studies the precise security guarantees an architecture offers, together with the underlying mechanics. While some systems focus on the isolation of data only, others also attest or authenticate code operating on it. An important question is also how a program can securely interact with the user, should the system be compromised. Security architectures range from trusted software running on commodity hardware down to specialized hardware extensions. Second, one needs to study the security of the TCB itself. Trusting the TCB is not necessarily based on security reasoning but an inevitable obligation to anyone using the system. Research shall provide convincing arguments that the TCB is also secure and, thus, trustworthy. This links back to our previous discussion on how to prevent (software) vulnerabilities. A mature security architecture shall provide its services at the smallest possible complexity. To phrase it differently: an important goal in designing security architectures is to minimize their TCB. A minimal TCB decreases the likelihood of bugs in the TCB and paves the way for full verification.

As mentioned before, our focus is not on vulnerability analysis of the TCB but its complexity reduction. Plus, we are interested in studying existing architectures in terms of their security properties.

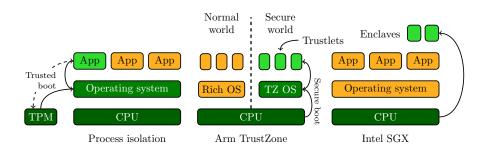

### 2.2 A History of Isolation Technology

A fundamental building block for securing systems is isolation. The goal is to prevent compromised code from harming the rest of a system, which requires partitioning of memory into security domains. Isolation can be realized on various layers. Figure 2.1 depicts the most widely used schemes. In traditional process isolation, each application process belongs to a different security domain and cannot access the memory of other domains. Also, the operating system forms its own security domain, which is isolated from the rest. To protect against untrusted operating systems, Arm TrustZone runs so-called trustlets on top of a small, trusted operating system inside a *secure world*. One can bootstrap trust in software via secure boot, or with the help of a Trusted Platform Module (TPM) via trusted boot. Intel SGX integrates those concepts inside the CPU, allowing enclaves to run securely on a compromised operating system. In the following, we explain those concepts and their evolution in more detail.

### 2.2.1 Process Isolation

Process isolation is a fundamental security concept that combines hardware and software techniques to isolate the memory of processes from each other. Resource-constrained devices use physical memory protection for that purpose, while large systems isolate processes in separate virtual address spaces. Isolation is usually enforced by the operating system taking advantage of the processor's privilege levels.

**Physical Memory Protection.** Highly embedded systems, such as the Arm Cortex M series [Armb], operate on a single flat address space called physical mem-

Figure 2.1: Process isolation is built on top of the operating system, which could be verified via a TPM and trusted boot. Arm TrustZone provides a so-called secure world for executing trustlets atop of a TrustZone operating system. Trust is typically established via secure boot. Intel SGX runs enclaves within an untrusted application, and trust is directly bootstrapped by the CPU. The TCB is colored green, including trusted components (dark green) and secured code (light green). Potentially malicious code is orange.

ory. Typically, part of this address space is used for read-only memory (ROM), random-access memory (RAM), and memory-mapped input/output devices denoted as MMIO. In such systems, memory isolation is achieved via a so-called Memory Protection Unit (MPU), a hardware module that safeguards access to physical memory. For the RISC-V architecture, MPU's are even called physical memory protection (PMP). An MPU sanitizes the address bus for malicious accesses, *i.e.*, accesses that do not belong to the current security domain. In case malicious access is detected, the MPU issues an exception that interrupts normal program execution and hands over control to the operating system. An MPU offers a fixed number of slots, each one holding a single contiguous memory range (e.g., the Arm Cortex M0+ offers eight MPU slots [Armb]). Only if a memory location belongs to the memory range of at least one MPU slot, access is allowed. In order to schedule multiple applications, the operating system is responsible for loading and unloading MPU slots upon each context switch. Due to the fragmentation of memory, an application might comprise a higher number of memory ranges than there are available MPU slots. In this case, the operating system can lazily swap MPU slots whenever the application accesses memory that is currently not loaded in the MPU.

In general, an MPU slot holds the start and end address of a memory range, but more optimized designs are possible by requiring memory ranges to be aligned. To increase security, MPUs can hold additional metadata for distinguishing readonly, writable, and executable memory regions, typically denoted as **rwx** bits. **Memory Segmentation.** Having a single flat address space for all applications comes with its drawbacks. For example, the more applications are executed, the more tedious memory partitioning becomes. In particular, all memory addresses need to be known a priori, that is, at compile/link time, impeding dynamic

need to be known a priori, that is, at compile/link time, impeding dynamic memory management. For that reason, memory segmentation was invented. A memory segment is represented by a base address and a size, similar to an MPU slot. Applications can reference any memory relative to a memory segment rather than via an absolute address. Thus, the application becomes position independent, and the operating system can decide at runtime at which memory location to load a particular application. Similar to an MPU, segmentation can also be used as an isolation technique by making an application's memory segments immutable and disjoint to other applications.

**Virtual Memory.** For mid and high-class application processors [Arma; Int16a; AMD20b], memory is virtualized, solving not only the fragmentation issue but also offering a strong primitive for isolation. For this, each application is given its own virtual view on the full memory range. E.g., on systems with 32-bit addresses, this covers  $2^{32} = 4$ GB of memory. This virtual address space is created atop of a 1:n address translation mechanism which transforms virtual addresses to physical ones. To simplify translation, both virtual and physical memory is split into chunks of pages (e.g., 4KB). A translation table maps virtual pages to physical pages. These translations are denoted as Page Table Entries (PTE). Each PTE is indexed by the virtual page address, and contains the corresponding physical page address (e.g., all but the lower 12 address bits for 4KB pages). Moreover, a PTE holds metadata such as permission bits (rwx) and access history bits. In order to increase efficiency, modern systems use a hierarchy of translation tables with up to five layers [Int16a].

As address translations are an expensive operation, a dedicated module called Memory Management Unit (MMU) does them in hardware. Moreover, successful translations are cached in the so-called translation lookaside buffer (TLB). On every context switch, the operating system not only switches translation tables, but it also needs to invalidate the corresponding TLB entries.

**Privilege Levels.** In all the above scenarios, the operating system is responsible for partitioning and, thus, isolating memory between applications. Obviously, the operating system needs to protect its own memory as well. It does so by the same means of physical or virtual memory protection used to protect applications. However, isolation alone does not suffice to defend against malicious applications bypassing it (e.g., by reconfiguring the MPU or MMU). Privilege levels are needed in hardware to constrain sensitive operations to the legit operating system. For example, the privileged kernel mode has access to the MPU or MMU. In contrast, the unprivileged user mode provides a constrained environment for executing potentially malicious application code. That is, specific CPU instructions are disallowed in user mode. Modern systems have more than two privilege levels. For example, x86 features four so-called protection rings indexed from 3 to 0, a separate virtualization layer informally indexed with -1, and a system management mode indexed with -2 for low-level hardware control. RISC-V provides a user mode for applications, a supervisor mode for the operating system, and a machine mode for emulating missing hardware features.

#### 2.2.2 Bootstrapping Trust

Process isolation fundamentally relies on the correct operation of the operating system. If an attacker manages to compromise the operating system, e.g., by corrupting the boot images, all security guarantees are lost. Secure boot prevents compromised components from being loaded. An attacker might also trick a remote user into communicating with a compromised device controlled by the attacker instead of the legit device. Here, we need a trusted boot mechanism proving the device configuration to the outside world.

**Secure Boot.** A simple yet powerful method for bootstrapping trust is secure boot. Here, the first piece of software executed at power on - the so-called first-stage bootloader - will perform checks on the code of the next stage before actually invoking it. Only if the next stage matches an expected signature, it will be handed over control. Signatures are typically based on cryptographic hashes over the code. To increase flexibility, the hash itself is usually cryptographically signed, and the signature key is embedded in the code of the respective boot stage. By iteratively checking the boot process, trust can eventually be extended to a full operating system. Secure boot can be purely implemented in software, assuming the first stage bootloader can be trusted as is. To do so, one typically places the first stage bootloader in read-only memory. Secure boot is used for bootstrapping the Arm TrustZone [Arm09] and UEFI [UEF19]. On Android, secure boot is called *verified boot* [Edg15].

**Trusted Boot.** According to Casper et al. [CP11], "Trusted Boot refers to the ability to have confidence or trust in the security of a system startup, beginning with the initial configuration boot of the system." Secure boot alone does not provide a mechanism to verify remotely whether a device was initialized securely. Hence, trusted boot combines secure boot with a concept called authenticated boot [Arb05]. On Windows, authenticated boot is called measured boot [Sat18].

Authenticated boot generates an "[...] accurate record of the way that the platform booted" [Tru12]. This record might involve relevant software and the hardware configuration. In any case, it shall reveal whether security mechanisms are present and initialized correctly. Similar to secure boot, authenticated boot scans each successive boot stage before running it. The resulting signatures are called measurements. However, rather than aborting in case of a signature mismatch, the obtained signatures are accumulated into one signature, e.g., via a chain of hashes. Verification of signatures is deferred to the future, where an external verifier checks signatures in a process called attestation.

**Trusted Platform Module.** Authenticated boot requires secure storage for signatures (*i.e.*, measurements). The Trusted Platform Module (TPM) [TCG14] is a dedicated security co-processor built into a tamper-proof hardware chip that offers secure storage alongside various cryptographic services. It allows software to accumulate signatures, that is, extend measurements, but not revert them. One can also bind TPM key material to a particular measurement such that keys are only unlocked if the boot process was performed correctly. This is used for full disk encryption, such as BitLocker, amongst others.

Bootstrapping trust with a TPM is prone to cold-boot attacks [Hal+08] and cuckoo attacks [Par08], assuming an attacker intercepts the communication interface between TPM and the CPU. Also, a major disadvantage of trusted boot is that the trusted computing base might become significantly large. E.g., when using the TPM from a user application, the whole operating system needs to be measured and trusted as well (cf. Figure 2.1). Even worse, if a single component in the trust chain is compromised, there is no way to re-establish trust other than a complete reboot of the system. Since trust is derived from a single static component, namely the first-stage bootloader, it is also entitled *static root of trust*.

**Dynamic Root of Trust.** Intel Trusted Execution Technology (TXT) [Int15] is a CPU extension that tackles the inflexibility issues of a static root of trust. TXT allows freezing execution of whatever software might be running, and bootstrap into a fresh environment, effectively giving a dynamic root of trust. Inside this environment, one can load a small security kernel and perform security-critical tasks. Once finished, TXT switches back to the original context and resumes normal execution. The open-source theor project builds upon Intel TXT to provide trusted boot for an operating system.<sup>1</sup>

### 2.2.3 Untrusted Operating Systems

We have seen that operating systems can be securely bootstrapped, and provide process isolation towards user applications. However, the amount of code that needs to be trusted (the TCB) comprises the whole operating system. Unfortunately, most widely used operating systems rely on a monolithic design, where a single bug can suffice to undermine process isolation completely. Microkernels, on the other hand, take the opposite approach by reducing kernel complexity.

Monolithic Kernels. Monolithic kernels perform all kernel-related tasks in a single security domain. This includes various forms of resource management as well as device drivers. Since monolithic kernels tend to have a large code base (e.g., the Linux kernel 5.6-rc4 comprises more than 18.5mio lines of code), the chance for unknown bugs is huge. For example, a total of 2300 vulnerabilities were reported for the Linux kernel within the last two decades, 246 of which are labeled as dangerous code execution bugs.<sup>2</sup> Finding such bugs in an automated way is a highly active line of research [Gen+18; Jeo+19; Yav19; LPW19b; Zha+19; Son+19; WLY18; LPW19a; Sri+19].

To reduce the attack surface, Linux randomizes the kernel layout via KASLR [Edg13]. Furthermore, it leverages supervisor mode access/execution prevention (SMAP and SMEP) to avoid misinterpretation of user memory as kernel memory. Also, other hardware features can be used to confine kernel operation further [GEL16; Pom+19; Gra+19].

<sup>&</sup>lt;sup>1</sup>http://sourceforge.net/projects/tboot. (Accessed 05/03/2020)

<sup>&</sup>lt;sup>2</sup>https://www.cvedetails.com/product/47/Linux-Linux-Kernel.html (Accessed 02/03/2020)

**Microkernels.** Unlike monolithic kernels, a microkernel attempts to reduce kernel complexity and, thus, the attack surface, to a bare minimum.<sup>3</sup> Typically, drivers are run in user mode, and resource management is handed over to userspace via so-called capabilities. A prominent example is the seL4 microkernel. The developers of seL4 reduced kernel code size to 8700 lines of C code and conducted formal verification to prove its correctness [Kle+09]. Designing a fully-featured, secure OS on top of a microkernel is a challenge on its own [Jac+15]. Nevertheless, Google is currently developing a capability-based operating system called Fuchsia atop of the Zirkon microkernel as a long-term replacement for Android.<sup>4</sup>

### 2.2.4 Towards Enclaves

Operating systems are arguably a weak link for the security of the overall system. We rely on them mainly because we have to. Removing the operating system from the trusted computing base (TCB) sounds appealing but impractical. To give an analogy in the physical world: one could barely remove the motor of a car and still expect it to move. Nevertheless, researchers asked the question to what extent one can distrust the operating system and still guarantee security. As a result, enclaves were developed. Enclaves are small containers that shield a piece of unprivileged code from the outside. The "outside" covers *all* code running outside of the enclave, including the operating system.

Enclaves evolved during a long journey of research and industry efforts, of which a partial, yet informative overview is given in [Mae+18]. Various terminologies related to enclaves exist such as trusted, secure, isolated, or shielded execution. In this thesis, we will use the term *enclave* as follows: an enclave is an *unprivileged* execution environment that allows one to securely execute a piece of code on a compromised system. We assume that the operating system and other software is untrusted and under control by an attacker. That is, the TCB only covers enclaves and the hardware (cf. Intel SGX in Figure 2.1). In contrast, the more general term *trusted execution environment (TEE)* may be used not only for enclaves but also for *privileged* execution environments that are shielded from a compromised operating system. In these privileged environments the TCB also covers a trusted operating system kernel (cf. Arm TrustZone in Figure 2.1).

Enclaves (as well as TEEs) are built upon three security primitives: memory isolation for protecting their code and data, entry point protection to prevent control-flow hijacking attacks, and attestation for bootstrapping trust. Furthermore, enclaves are unprivileged. The operating system can decide on their management.

Enclaves evolved from various techniques for secure code execution. Early designs put critical computation in a separate security co-processor [SW99]. The co-processor features cryptographic operations similar to a TPM but can also run a full general-purpose software stack, authenticated with a secure boot mechanism,

<sup>&</sup>lt;sup>3</sup>For a list of popular microkernels see http://www.microkernel.info/

<sup>&</sup>lt;sup>4</sup>https://fuchsia.dev (Accessed 02/03/2020)

and an attestation scheme. XOM explores execute-only memory [Lie+00], based on previous work on transparent memory encryption et al. [GLQ98; GLQ99]. AEGIS is a hardware-software co-design based on memory encryption and an optional security kernel [Suh+03].

Arm TrustZone. Arm developed TrustZone in 2008 [Arm09], which since then, became a de-facto industry standard. As shown in Figure 2.1, TrustZone provides a secure world for running secure software alongside an untrusted rich operating system, running in the normal world. This world split is orthogonal to the processor's privilege levels and effectively creates a secure virtual CPU. The secure world can access all system resources, while the non-secure world can only access non-secure memory regions. Moreover, the secure world can be extended to security-critical hardware peripherals. TrustZone demands a security kernel (e.g., a microkernel) which is responsible for running so-called trustlets, small user programs that shall be shielded against software attacks. The trusted computing base (TCB) covers all secure world code plus the hardware.

**Other Isolation Techniques.** Flicker bootstraps secure applications with the help of Intel TXT and the TPM [McC+08] and a small privileged bootstrapping code. However, during the execution of the secure application, Intel TXT suspends all other applications. Hypervisors have been used to separate secure applications from an untrusted operating system [TLL06; Che+08; YS08; CL10; McC+10; Chh+11; Hof+13]. Virtual ghost isolates sensitive memory via compiler transformations on the untrusted kernel [CDA14]. SICE uses system management RAM on x86 for creating a secure environment [ANZ11]. CARMA [Vas+12] and Oasis [Owu+13] create a secure environment purely inside CPU caches.

**Enclave Architectures.** IBM SecureBlue++ [WB11; BW12] is an extension to the Power architecture, which reduces the trusted computing base to the enclave (denoted as secure executable) and hardware only. It is compatible with existing software, protects enclaves also in the file system via encryption, and provides enclaves with shared memory and multithreading. Intel SGX [McK+13] brings enclaves to x86 off-the-shelf CPUs. SGX embeds enclaves in ordinary application processes and comes with an enclave-to-enclave and a remote attestation scheme. SGX outsources memory mapping to the untrusted operating system and also encrypts all enclave memory in DRAM. For this, enclave memory has to be allocated inside a pre-defined portion of DRAM, and the memory mapping is verified against an SGX shadow structure. We discuss SGX in detail in Section 2.3. Unlike SGX, Iso-X [Evt+14] allows using any memory for enclaves, however, without memory encryption. Also, Iso-X does not prevent the operating system from remapping enclave memory, which could lead to runtime attacks. Sanctum [CLD16] brings the SGX concept to the RISC-V architecture and uses a memory coloring scheme that is more resistant to side-channel attacks.

In order to isolate whole virtual machines rather than enclaves only, AMD added full memory encryption in their CPUs called Secure Encrypted Virtualization (SEV) [KPW16]. To address attacks tampering with encrypted memory [Mor+18], AMD recently integrated a memory integrity scheme for SEV, called Secure Nested Paging (SEV-SNP) [AMD20a]. Enclaves were also ported to small embedded systems via dedicated hardware support [Eld+12; Noo+13; Göt+15; Noo+17; Koe+14; Bra+15; Arm17]. We will discuss them in Section 4.9. MultiZone and Keystone both provide a TrustZone-like software stack for RISC-V MPU-based systems [Hex; Lee+20].

### 2.3 Intel Software Guard Extensions (SGX)

Intel Software Guard Extensions (SGX) are an x86 instruction-set extension that has been rolled out with the Skylake microarchitecture. SGX first introduced the term *enclave* for running trusted code isolated from the remaining system. Enclaves opened a wide range of new application scenarios, such as trusted cloud computing [BPH14; Sch+15; Gje+17], protection of web browser input fields [Esk+19; Dha+20a] copyrighted material [BL16] or cryptocurrencies [Lia+17], secure networking [MAP18], and many more. Also, programs that were not intended for enclave execution can benefit from enclave-based container approaches. Haven shifts a whole Windows 8 library into an SGX enclave [BPH14], and SCONE [Arn+16], Panoply [Shi+17b], and Graphene-SGX [TPV17] provide such an abstraction for Linux.

In the following, we focus on SGX features and discuss attacks on SGX. For more details, we refer to the available literature [McK+13; Ana+13; Hoe+13; XSL16; Cha+17a; Fer+17; Ana+15; CD16; Int16a; Int16b; Int17b].

### 2.3.1 Basic SGX Features

The central concept of SGX is a hardware-isolated enclave container in which sensitive parts of an application are placed. Unlike TrustZone, an enclave directly resides in the address space of an untrusted user application (cf. Figure 2.1). Only the enclave itself can access its memory while the hardware prevents any other access to it. SGX does not rely on any privileged software (trusted kernel, hypervisor, etc.) to isolate enclaves, thus reducing the TCB to only the CPU and enclaves themselves.<sup>5</sup> To protect against physical attackers, SGX encrypts and integrity-protects all enclave memory on the fly when written to DRAM using a dedicated hardware encryption module.

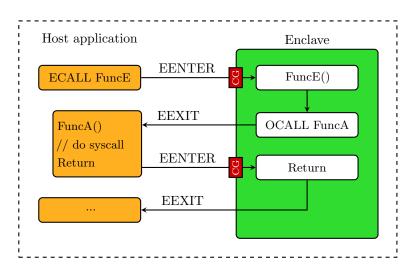

**Enclave Interaction.** Figure 2.2 shows the process of invoking an enclave. The enclave defines secure functions denoted as ECALLs, which the application can call with the EENTER instruction. Call gates (CG) restrict ECALLs to valid entry points. This prevents simple control-flow attacks from the application. To further reduce the TCB, syscalls are disallowed from within enclaves. Instead, enclaves can request OS services such as syscalls via OCALLs. In order to leave the enclave, it can issue the EEXIT instruction.

Intel assists enclave developers with a so-called Enclave Definition Language (EDL). The EDL file is used to specify the ECALL/OCALL interface of

$<sup>{}^{5}</sup>$ SGX relies on CPU microcode, which is considered part of the hardware. For remote attestation, SGX interacts with the Intel Management Engine (ME) [Rua14b] as a trusted component.

Figure 2.2: SGX enclaves are tightly integrated in a host application. The application can invoke the enclave via ECALLs while the enclave can perform OCALLS. Enclaves can only be entered via the EENTER instruction at dedicated call gates (CG) and can only be left via EEXIT.

a particular enclave. As such, it contains function signatures of the enclave's ECALLs and OCALLs, augmented with additional security attributes (e.g., in, out). Intel provides developers with an SDK [Int16b] that automatically generates glue code from the EDL file with appropriate parameter validation and buffer copying inside the enclave. The glue code is also responsible for maintaining CPU state across EENTER and EEXIT by saving and restoring CPU registers appropriately.

Shielding against the OS. In SGX, the operating system is entirely distrusted. Nevertheless, it is responsible for managing enclaves. The CPU safeguards all such enclave management operations and prevents the enclave from executing in case of operating system misbehavior. This affects three areas: enclave launch, memory mapping, and interruption.

Enclave Launch. To launch an enclave, SGX provides new initialization instructions to the operating system. ECREATE initializes a fresh, empty enclave. EADD lets the operating system load memory pages into the enclave. EEXTEND can be used to measure those enclave pages in a chained cryptographic hash log, stored in a register called MRENCLAVE. This process of hashing is comparable to a TPM [TCG14]. Not only the enclave page content is measured, but also the exact sequence of SGX initialization instructions. When completing initialization via EINIT, the CPU verifies the value of MRENCLAVE against a vendor-signed version and aborts on a mismatch. Only if the operating system has loaded the enclave in the intended way, this verification will succeed. Hence, MRENCLAVE vouches for the integrity of the enclave startup; it serves as load-time attestation. **Memory Mapping.** In SGX, memory management is solely done by the operating system, as opposed to TrustZone. SGX does not prevent an operating system from mapping enclave pages in an illegitimate way. However, the CPU will refuse to run enclaves with an incorrect mapping. The corresponding checks are implemented in the virtual-to-physical address translation mechanism. A so-called Enclave Page Cache Map (EPCM) keeps a copy of the intended page mappings specified during EADD. This includes the virtual address, the permission bits, and the enclave this page belongs to. The EPCM can also be seen as a table of inverse PTEs, mapping physical enclave pages back to virtual ones. If any of the EPCM checks fail, an exception is triggered. Checks only need to be done once, as successful translations are cached in the TLB. However, the TLB needs to be flushed when entering an enclave with EENTER, causing a noticeable slowdown [WBA17].

**Interruption.** For normal ECALLs and OCALLs, the enclave software preserves the CPU register state. However, an enclave might get interrupted, e.g., via an external interrupt or an exception. This is called Asynchronous Exit Event (AEX). Upon an AEX, the CPU suspends enclave execution and stores its CPU state inside a special State-Save Area (SSA) in the enclave. Moreover, it will clear registers to avoid information leakage and hand over control to the operating system. To resume from interruption, SGX provides an ERESUME instruction that restores the CPU state from the SSA.

An enclave might want to handle some AEXs, such as floating point exceptions, itself. To do so, the application can re-enter an interrupted enclave via EENTER. Once the AEX is resolved and the enclave issued EEXIT, the OS can resume the enclave via ERESUME. Also, nested AEX are possible. For this, the SSA is organized as stack, and enclaves can be re-entered until the SSA is full.

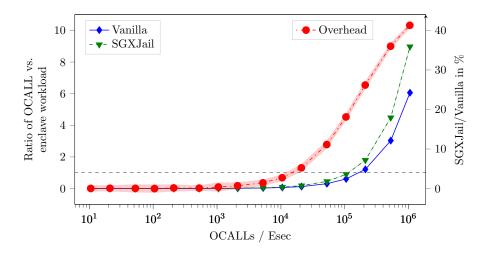

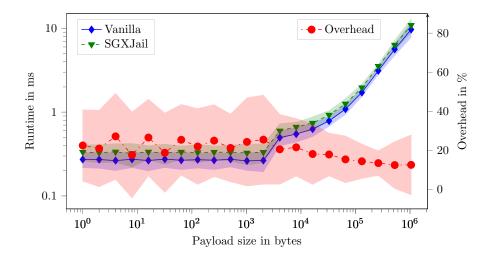

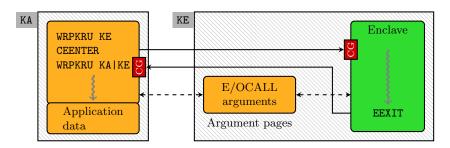

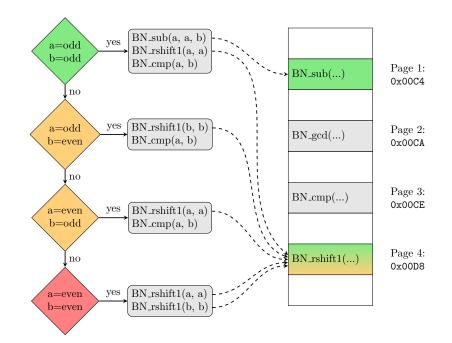

### 2.3.2 Advanced SGX Features