Sebastian Krell, BSc

## Design and Implementation of Real-time Histogramming for LiDAR

### MASTER'S THESIS

to achieve the university degree of Diplom-Ingenieur

Master's degree programme: Telematics

submitted to

## Graz University of Technology

Supervisor

Ass.Prof. Dipl.-Ing. Dr.techn. Christian Steger

Institute for Technical Informatics (ITI)

### Advisor

Ass.Prof. Dipl.-Ing. Dr.techn. Christian Steger Dr. Norbert Druml (Infineon Technologies Austria AG)

## AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present master's thesis dissertation.

Date

Signature

## Kurzfassung

Light Detection and Ranging (LiDAR) ist ein bildgebendes Verfahren, welches eine dreidimensionale Repräsentation der Umgebung abbilden kann. In den letzten Jahren gewann es immer mehr an Beliebtheit, sowohl in der Unterhaltungs- als auch in der Industrieelektronik. Es deckt ein breites Spektrum an Anwendungsfällen ab und wird sowohl vom Boden als auch aus der Luft betrieben. Es können sowohl topographische Vermessung als auch Dokumentation von lokalen Szenerien erstellt werden. Die Signalanalyse als auch -verarbeitung wurden in den letzten Jahren so weit vorangetrieben, dass auch Eigenschaften wie Reflektivität oder Geschwindigkeit von Objekten klassifiziert werden können. Es können auch strukturelle Schwächen in Betongebäuden gefunden und analysiert werden. Durch den immer kleiner werdenden Formfaktor findet diese Technologie auch Einzug in die Robotik und den autonomen Fahrassistenzsystemen. Diese Bereiche benötigen auch Echtzeit Signalverarbeitung der gelieferten Daten, da Entscheidungsfindungen Systemund Sicherheitskritisch sind.

Diese Masterarbeit präsentiert ein Echtzeit-Datenverarbeitungssystem inklusive Signalanalyse eines 1bit diskreten LiDAR Systems. Dies ist möglich unter der Verwendung der Xilinx Artix 7 FPGA Plattform. Hardware-beschleunigte Komponenten sind mit VHDL entwickelt und in einem Artix 7 FPGA umgesetzt. Diese Art der Hardwareintegration ermöglicht high-speed Datenverarbeitung. Ein integrierter MicroBlaze Mikroprozessor wird verwendet, um die entwickelten Komponenten zur Laufzeit zu steuern. Durch die Analyse der abgetasteten Lichtreflexionen können verschiedene Attribute wie relative Reflektivität, Pulsbreite und Distanz zum Objekt extrahiert werden. Die daraus resultierenden Daten werden danach mittels Ethernet und USB an eine PC Software übertragen. Dieses Hardware-beschleunigte System ermöglicht zusätzliche Informationsextraktion und gleichzeitige Datenreduktion bei gleichzeitiger Beibehaltung von höchstem Datendurchsatz.

In dieser Masterarbeit wird ein bereits bestehender Prototyp eines LiDAR Systems verwendet, um Messdaten mit dem erstellten System zu generieren. Der Prototyp besteht aus einem Empfangsboard mit 32 Avalanche Photo Dioden (APDs), einem mikroelektromechanischem Spiegel, Empfangsoptik und einer Steuerplatine. Sämtliche Komponenten des Prototyps wurden von der Firma Infineon Technologies entwickelt. Die Empfangsleitungen der 32 APDs werden zu den Anschlüssen des Artix 7 FPGA geführt und danach von dem in der Masterarbeit entwickelten System abgetastet. Das präsentierte System ist ansonsten unabhängig von der verwendeten Hardware und kann in jeglichem FPGA-basierten LiDAR System verwendet werden. Mit den bestehenden Hardwarelimitierungen kann das implementierte System 40 000 Messungen pro Sekunde verarbeiten. Dies entspricht, angewendet auf den Prototypen, 300 Bildern pro Sekunde.

Das erarbeitete System wird unter Verwendung von verschiedenen Materialien mit unterschiedlicher Reflektivität evaluiert. Sowohl das Rauschen in den resultierenden Daten als auch das Sensor Übersprechverhalten werden dabei analysiert. Extrahierte Attribute aus dem Signal werden verwendet um die Qualität der produzierten Bilddaten zu verbessern. Ein weiterer LiDAR Prototyp wird verwendet um ein möglichst störendes Umfeld zu generieren und das System darin zu testen. Die Signalmittelung wurde dabei evaluiert und zeigt sehr stabile Resultate.

### Abstract

Light Detection and Ranging (LiDAR) is a 3D imaging technique to generate a representation of the surrounding environment. It has become very popular during the last year in consumer and industrial electronics. It covers a wide variety of applications, ranging from airborne to terrestrial assemblies. It is used for topographical survey as well as documentation of local scenes. Signal analysis and processing of LiDAR data have advanced so far, that nowadays features like reflectance and velocity of objects can be determined. It is even used for finding structure integrity problems of concrete buildings. Due to the decreasing form factor of LiDAR systems, it is also applied to robotic and automotive areas for navigation assistance and similar systems. The application fields of automated driving and robotics require real time data analysis since fast decision making may be crucial for functional safety.

This thesis presents a novel real-time signal analyzing system capable of extracting features out of 1bit LiDAR data. This is accomplished by using the Xilinx Artix 7 platform. Hardware-accelerated components are designed in VHDL and implemented into the Artix 7 FPGA. The hardware-integrated solution allows high speed processing. An integrated MicroBlaze micro controller is used for configuration of the developed components during run-time. Feature extraction in form of pulse width, position and assumed relative reflectance is accomplished by analyzing the incoming digitalized light reflections. Additionally, a new technique for signal averaging is performed. The resulting data is then transmitted over Ethernet or USB to PC software. This powerful hardware system enables feature extraction while reducing required data throughput and still achieving essential speed-up in hardware.

In this work an existing prototype is extended in order to also gather real-world data with the proposed system. The prototype consists of a receiver board containing 32 Avalanche Photo Diodes (APDs), a microelectromechanical mirror system (MEMS), receiver optics and an controller board. All of these components are developed by Infineon Technologies. The 32 Low Voltage Differential Signal (LVDS) lines are fed into the Artix 7 FPGA and are then controlled by the system developed in this work. The presented algorithms can be applied to any generic LiDAR system with FPGA unit. In the existing system, the resulting work is capable of processing 40 000 measurements per second. With system specific settings, this corresponds to 300 FPS.

The system is tested with materials of different reflectivity at a variety of distances. Noise levels and cross talk phenomena are analyzed, while extracted features are used to improve the image quality. A second LiDAR prototype is used to create a noisy environment. Under these conditions, the signal averaging is analyzed and shows stable results.

## Danksagung

Diese Diplomarbeit wurde am Institut für Technische Informatik an der Technischen Universität Graz durchgeführt. Der praktische Teil der Arbeit konnte bei Infineon Technologies Austria AG in Graz absolviert werden. Allen voran möchte ich mich bei all jenen bedanken, die am Entwicklungsprozess dieser Arbeit beteiligt waren.

Ich möchte mich für die Bemühungen und die Unterstützung meines Betreuers Ass.Prof. Dipl.-Ing. Dr.techn. Christian Steger bedanken. Durch hilfreiche Anmerkungen und Ratschläge hat er nicht nur zur Qualitätsverbesserung dieser Arbeit beigetragen, sondern hat auch dadurch erst einen positiven Abschluss möglich gemacht. Weiters bin ich dankbar für die Unterstützung und Hilfe meines Betreuers Dipl.Ing. Dr. Norbert Druml bei Infineon Technologies. Durch ihn habe ich nicht nur die Möglichkeit erhalten, eine Masterarbeit im Bereich LiDAR durchzuführen, sondern konnte darüber hinaus noch viel tiefer in diese Thematik eintauchen. Dank der stets konstruktiven Ratschläge und der professionellen Unterstützung konnte diese Arbeit erfolgreich zum Abschluss gebracht werden.

Weiters möchte ich mich bei meinen Freunden und Studienkollegen bedanken. Ohne die anhaltenden Ermutigungen und auch Ablenkungen wäre das Studium nicht zu so einem bemerkenswerten Erlebnis geworden. Hierbei freut mich besonders, dass aus Studienkollegen mit der Zeit Freunde fürs Leben wurden. Besonderer Dank gilt meiner Lebensgefährtin Theresa, der ich mehr zu verdanken habe als ein paar Zeilen fassen könnten. Danke für die unablässige Unterstützung und dein endloses Verständnis.

Schließlich möchte ich auch noch einen großen Dank meiner Familie aussprechen, ohne deren Geduld und letzten Endes auch finanzielle Unterstützung mein Studium nicht möglich gewesen wäre. Obwohl das Studium eine beträchtliche Distanz zwischen uns gebracht hat, so hat es dem Zusammenhalt nicht geschadet. Und ein Besuch im schönen Niederösterreich brachte immer wieder den notwendigen Ausgleich, durch den ich mein Studium mit Erfolg abschließen konnte. Vielen Dank.

Graz, im Mai 2018

Sebastian Krell

## Contents

| 1        | Intr | oducti | ion                                                                                             | <b>21</b> |

|----------|------|--------|-------------------------------------------------------------------------------------------------|-----------|

|          | 1.1  | Motiv  | ation $\ldots$ | 21        |

|          | 1.2  | Objec  | tives                                                                                           | 23        |

|          | 1.3  | Outlin | ne                                                                                              | 23        |

| <b>2</b> | Rel  | ated V | Vork                                                                                            | 25        |

|          | 2.1  | Laser  | ranging principle                                                                               | 25        |

|          | 2.2  | LiDAI  | R Systems - State-of-the-Art                                                                    | 26        |

|          |      | 2.2.1  | Field of Application                                                                            | 26        |

|          |      | 2.2.2  | Time-of-Flight Measuring                                                                        | 26        |

|          |      | 2.2.3  | Illumination/Sensing                                                                            | 26        |

|          |      | 2.2.4  | Receiver                                                                                        | 27        |

|          |      | 2.2.5  | Signal Processing                                                                               | 29        |

|          | 2.3  | State- | of-the-Art                                                                                      | 30        |

|          |      | 2.3.1  | Calibration for Reflectance                                                                     | 31        |

|          |      | 2.3.2  | Fog classification                                                                              | 34        |

|          |      | 2.3.3  | Wavelet-Based Echo Detector                                                                     | 37        |

|          |      | 2.3.4  | TOF-LIDAR signal processing using the CFAR detector                                             | 39        |

| 3        | Des  | ign    |                                                                                                 | 45        |

|          | 3.1  | Requi  | rements                                                                                         | 45        |

|          | 3.2  | Existi | ng Platform                                                                                     | 46        |

|          |      | 3.2.1  | LiDAR System Hardware                                                                           | 46        |

|          |      | 3.2.2  | System Software                                                                                 | 49        |

|          | 3.3  | Histog | gramming                                                                                        | 50        |

|   |                          | 3.3.1                                                                                                               | Principle                                                                                                                                                                                                                                                                                                                                                                    | 51                                                                                                                                                                     |

|---|--------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                          | 3.3.2                                                                                                               | Algorithm Evaluation                                                                                                                                                                                                                                                                                                                                                         | 51                                                                                                                                                                     |

|   |                          | 3.3.3                                                                                                               | Memory Consumption                                                                                                                                                                                                                                                                                                                                                           | 52                                                                                                                                                                     |

|   |                          | 3.3.4                                                                                                               | Confidence                                                                                                                                                                                                                                                                                                                                                                   | 54                                                                                                                                                                     |

|   | 3.4                      | Encod                                                                                                               | ling                                                                                                                                                                                                                                                                                                                                                                         | 55                                                                                                                                                                     |

|   |                          | 3.4.1                                                                                                               | Principle                                                                                                                                                                                                                                                                                                                                                                    | 56                                                                                                                                                                     |

|   |                          | 3.4.2                                                                                                               | Memory reduction                                                                                                                                                                                                                                                                                                                                                             | 57                                                                                                                                                                     |

|   | 3.5                      | Comm                                                                                                                | nunication $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                    | 58                                                                                                                                                                     |

|   |                          | 3.5.1                                                                                                               | Ethernet                                                                                                                                                                                                                                                                                                                                                                     | 58                                                                                                                                                                     |

|   |                          | 3.5.2                                                                                                               | USB                                                                                                                                                                                                                                                                                                                                                                          | 60                                                                                                                                                                     |

|   |                          | 3.5.3                                                                                                               | UART                                                                                                                                                                                                                                                                                                                                                                         | 61                                                                                                                                                                     |

|   | 3.6                      | PC So                                                                                                               | $ m ftware \ldots $                                                                                                                                                                                                                                                 | 52                                                                                                                                                                     |

|   |                          | 3.6.1                                                                                                               | ROS / RVIZ                                                                                                                                                                                                                                                                                                                                                                   | 52                                                                                                                                                                     |

|   |                          | 3.6.2                                                                                                               | USB to PCL2                                                                                                                                                                                                                                                                                                                                                                  | 53                                                                                                                                                                     |

|   |                          | 3.6.3                                                                                                               | UDP to PCL2                                                                                                                                                                                                                                                                                                                                                                  | 64                                                                                                                                                                     |

|   |                          | 3.6.4                                                                                                               | ROS Filter                                                                                                                                                                                                                                                                                                                                                                   | 64                                                                                                                                                                     |

|   |                          |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                        |

| 4 | Imn                      | lemen                                                                                                               | tation                                                                                                                                                                                                                                                                                                                                                                       | 37                                                                                                                                                                     |

| 4 | -                        |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                              | <b>87</b><br>67                                                                                                                                                        |

| 4 | <b>Imp</b><br>4.1        | Develo                                                                                                              | ppment                                                                                                                                                                                                                                                                                                                                                                       | 67                                                                                                                                                                     |

| 4 | -                        | Develo<br>4.1.1                                                                                                     | opment                                                                                                                                                                                                                                                                                                                                                                       | 67<br>67                                                                                                                                                               |

| 4 | 4.1                      | Develo<br>4.1.1<br>4.1.2                                                                                            | opment                                                                                                                                                                                                                                                                                                                                                                       | 67<br>67<br>69                                                                                                                                                         |

| 4 | 4.1<br>4.2               | Develo<br>4.1.1<br>4.1.2<br>Overal                                                                                  | opment                                                                                                                                                                                                                                                                                                                                                                       | 57<br>57<br>59<br>70                                                                                                                                                   |

| 4 | 4.1                      | Develo<br>4.1.1<br>4.1.2<br>Overal<br>Encod                                                                         | opment                                                                                                                                                                                                                                                                                                                                                                       | 57<br>57<br>59<br>70<br>71                                                                                                                                             |

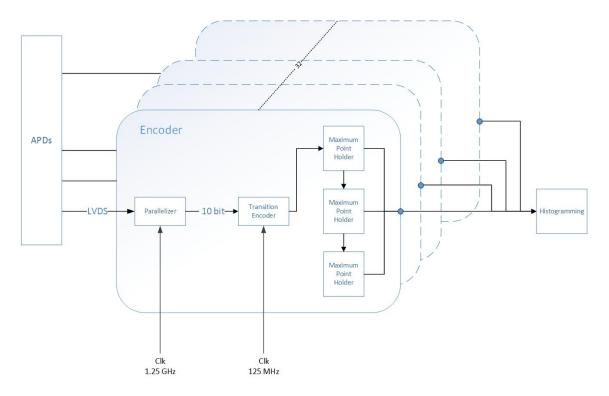

| 4 | 4.1<br>4.2               | Develo<br>4.1.1<br>4.1.2<br>Overal<br>Encod<br>4.3.1                                                                | opment    6      Tools    6      Work-flow    6      Il System Architecture    7      ling    7      Parallelizer    7                                                                                                                                                                                                                                                       | <ul> <li>37</li> <li>37</li> <li>37</li> <li>39</li> <li>70</li> <li>71</li> <li>72</li> </ul>                                                                         |

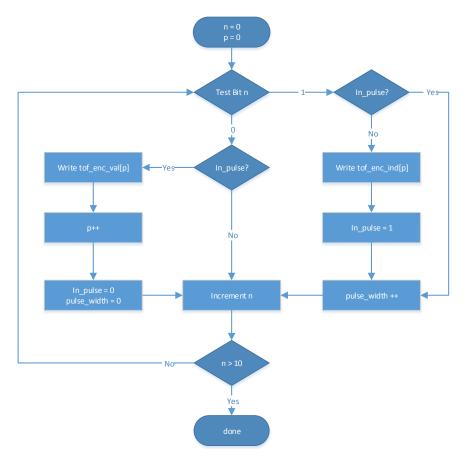

| 4 | 4.1<br>4.2               | Develo<br>4.1.1<br>4.1.2<br>Overal<br>Encod<br>4.3.1<br>4.3.2                                                       | opment       6         Tools       6         Work-flow       6         Ill System Architecture       7         ling       7         Parallelizer       7         Transition Encoder       7                                                                                                                                                                                  | <ul> <li>57</li> <li>57</li> <li>59</li> <li>70</li> <li>71</li> <li>72</li> <li>73</li> </ul>                                                                         |

| 4 | 4.1<br>4.2<br>4.3        | Develo<br>4.1.1<br>4.1.2<br>Overal<br>Encod<br>4.3.1<br>4.3.2<br>4.3.3                                              | opment       6         Tools       6         Work-flow       6         Ill System Architecture       7         ing       7         Parallelizer       7         Transition Encoder       7         Maximum Point Holder       7                                                                                                                                              | <ul> <li>37</li> <li>37</li> <li>37</li> <li>37</li> <li>70</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> </ul>                                                 |

| 4 | 4.1<br>4.2               | Develo<br>4.1.1<br>4.1.2<br>Overal<br>Encod<br>4.3.1<br>4.3.2<br>4.3.3<br>Histog                                    | opment 6   Tools 6   Work-flow 6   Il System Architecture 7   ling 7   Parallelizer 7   Transition Encoder 7   Maximum Point Holder 7   grammer 7                                                                                                                                                                                                                            | <ul> <li>57</li> <li>57</li> <li>59</li> <li>70</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> <li>75</li> </ul>                                                 |

| 4 | 4.1<br>4.2<br>4.3        | Develo<br>4.1.1<br>4.1.2<br>Overal<br>Encod<br>4.3.1<br>4.3.2<br>4.3.3<br>Histog<br>4.4.1                           | opment 6   Tools 6   Work-flow 6   Il System Architecture 7   ing 7   Parallelizer 7   Transition Encoder 7   Maximum Point Holder 7   Grammer 7   Computation 7                                                                                                                                                                                                             | <ul> <li>57</li> <li>57</li> <li>57</li> <li>70</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> <li>75</li> <li>77</li> </ul>                                     |

| 4 | 4.1<br>4.2<br>4.3        | Develo<br>4.1.1<br>4.1.2<br>Overal<br>Encod<br>4.3.1<br>4.3.2<br>4.3.3<br>Histog<br>4.4.1<br>4.4.2                  | opment       6         Tools       6         Work-flow       6         Il System Architecture       7         ing       7         Parallelizer       7         Transition Encoder       7         Maximum Point Holder       7         Computation       7         Data structure       7                                                                                    | <ul> <li>57</li> <li>57</li> <li>59</li> <li>70</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> <li>75</li> </ul>                                                 |

| 4 | 4.1<br>4.2<br>4.3        | Develo<br>4.1.1<br>4.1.2<br>Overal<br>Encod<br>4.3.1<br>4.3.2<br>4.3.3<br>Histog<br>4.4.1<br>4.4.2<br>4.4.3         | opment       6         Tools       6         Work-flow       6         Ill System Architecture       7         ling       7         Parallelizer       7         Transition Encoder       7         Maximum Point Holder       7         crammer       7         Data structure       7         State machine       8                                                        | <ul> <li>57</li> <li>57</li> <li>59</li> <li>70</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> <li>75</li> <li>77</li> <li>79</li> </ul>                         |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Develo<br>4.1.1<br>4.1.2<br>Overal<br>Encod<br>4.3.1<br>4.3.2<br>4.3.3<br>Histog<br>4.4.1<br>4.4.2<br>4.4.3<br>Comm | opment       6         Tools       6         Work-flow       7         Il System Architecture       7         ling       7         Parallelizer       7         Transition Encoder       7         Maximum Point Holder       7         Computation       7         Data structure       7         State machine       8         unication       8                           | <ul> <li>37</li> <li>37</li> <li>37</li> <li>70</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> <li>75</li> <li>77</li> <li>79</li> <li>30</li> </ul>             |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | Develo<br>4.1.1<br>4.1.2<br>Overal<br>Encod<br>4.3.1<br>4.3.2<br>4.3.3<br>Histog<br>4.4.1<br>4.4.2<br>4.4.3         | oppment       6         Tools       6         Work-flow       6         Il System Architecture       7         ing       7         Parallelizer       7         Transition Encoder       7         Maximum Point Holder       7         Computation       7         Data structure       7         State machine       8         nunication       8         Ethernet       8 | <ul> <li>37</li> <li>37</li> <li>37</li> <li>39</li> <li>70</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> <li>77</li> <li>79</li> <li>30</li> <li>30</li> </ul> |

|              |       | 4.5.3   | UART                              | 86  |

|--------------|-------|---------|-----------------------------------|-----|

|              | 4.6   | Softwa  | re                                | 86  |

|              |       | 4.6.1   | Receiving                         | 87  |

|              |       | 4.6.2   | ROS Filter                        | 89  |

| 5            | Res   | ults    |                                   | 91  |

|              | 5.1   | Impler  | nentation                         | 91  |

|              |       | 5.1.1   | Utilization                       | 91  |

|              |       | 5.1.2   | Throughput                        | 92  |

|              | 5.2   | Time-o  | of-Flight Processing Measurements | 94  |

|              |       | 5.2.1   | Testing environment               | 94  |

|              |       | 5.2.2   | Pulse Width                       | 95  |

|              |       | 5.2.3   | Confidence                        | 97  |

|              |       | 5.2.4   | Histogram                         | 98  |

| 6            | Con   | clusior | n and Future Work                 | 101 |

|              | 6.1   | Conclu  | sion                              | 101 |

|              |       | 6.1.1   | Future Work                       | 102 |

| $\mathbf{A}$ | Teri  | ninolo  | gy                                | 105 |

| Bi           | bliog | raphy   |                                   | 107 |

# List of Figures

| 1.1  | Sensor equipment of an Audi to cover 360 degree around the car [AG.17].                                                                                                                                                                                                                                                                                                                                                            | 21 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

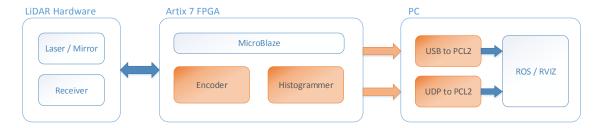

| 1.2  | Overview of the LiDAR system implemented in this thesis. Orange blocks are extended to an already existing system.                                                                                                                                                                                                                                                                                                                 | 22 |

| 2.1  | Direct time-of-flight principle.                                                                                                                                                                                                                                                                                                                                                                                                   | 25 |

| 2.2  | Two different illumination/sensing technologies for LiDAR systems [CC13].                                                                                                                                                                                                                                                                                                                                                          | 27 |

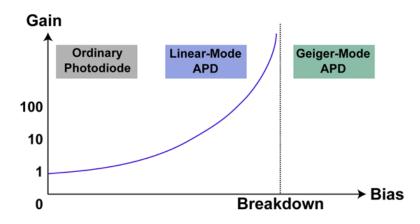

| 2.3  | Comparison of ordinary photo diode, linear mode and Geiger mode Avalanche<br>Photo Diode (APD)s [Lab].                                                                                                                                                                                                                                                                                                                             | 28 |

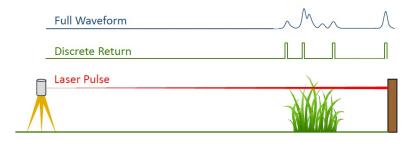

| 2.4  | Illustration of analog discrete return and full-waveform return LiDARs [HGF13]                                                                                                                                                                                                                                                                                                                                                     | 29 |

| 2.5  | The system response (green line) of a received signal can be described as convolution of emitted laser pulse (red line) and target signature (black line) [UP11].                                                                                                                                                                                                                                                                  | 30 |

| 2.0  |                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 2.6  | A typical waveform of a response of the VZ-400 [HGF13]                                                                                                                                                                                                                                                                                                                                                                             | 32 |

| 2.7  | The collected measured waveforms are aligned using a cubic spline fit in order to receive a 3D representation for each response pulse [HGF13]                                                                                                                                                                                                                                                                                      | 32 |

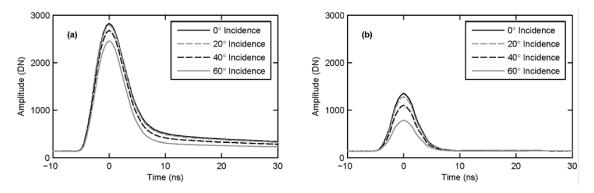

| 2.8  | Waveforms of backscattered signals with different incident angles (on the left side with a distance of 32 m, on the right side with 160 m). The amplitude does not change as much, regarding to the changing incident angle, as expected [HGF13]                                                                                                                                                                                   | 33 |

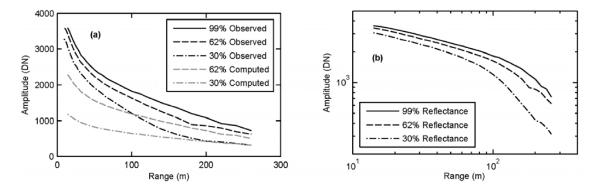

| 2.9  | Amplitude peaks for the three different reflectance targets covering the en-<br>tire distance range. The black lines on the left side show the measured<br>results for the three targets while the gray lines show estimated peak values<br>for reflectances of 30% and 62% depending on the measured values for 99%<br>reflectance. The image on the right side shows the same results but plotted<br>on logarithmic axes [HGF13] | 34 |

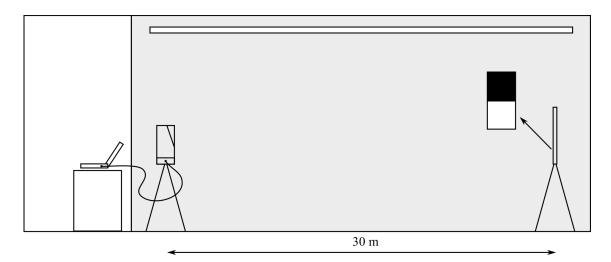

| 2.10 | Setup of the experiment for measuring inside a fog chamber $[\mbox{PWWU14}].$                                                                                                                                                                                                                                                                                                                                                      | 35 |

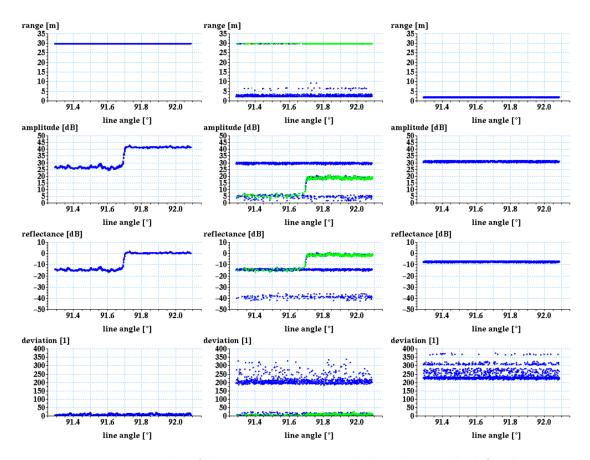

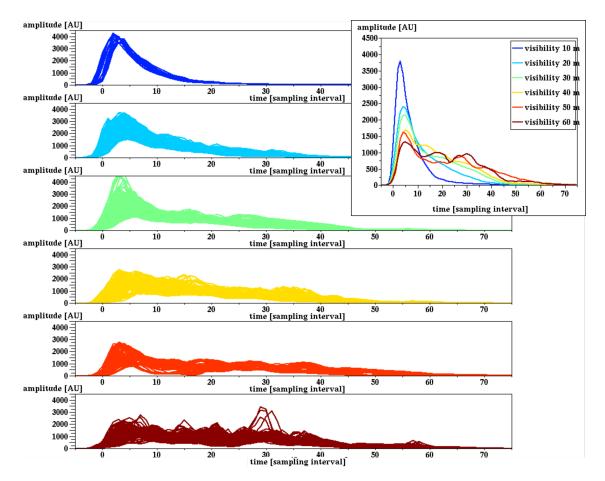

| 2.11 | Results of the experiment in a turbid medium. The left column shows the results without fog, the middle column for a fog density with 40 m visibility and the right column with 10 m visibility. The blue points show first hit targets, the green points second targets. [PWWU14]                                                                                                                                                 | 36 |

|      | o, o rimini andiri i interneti                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 2.12 | Recording of the waveform of fog at different visibility ranges [PWWU14].                                                                                                                                                                                                                                                                | 37 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

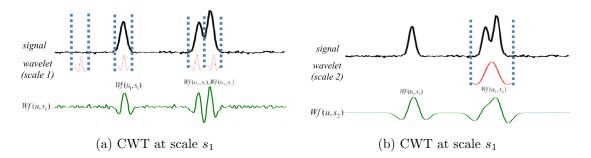

| 2.13 | Example for echo detection using continuous wavelet transformation [Wan12].                                                                                                                                                                                                                                                              | 38 |

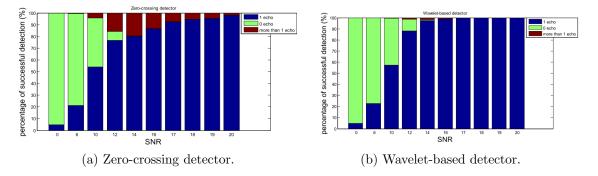

| 2.14 | Results for echo detection with different SNR levels for the zero-crossing and wavelet-based detectors [Wan12]                                                                                                                                                                                                                           | 39 |

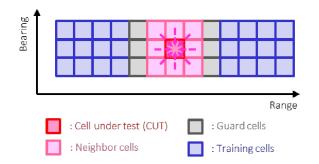

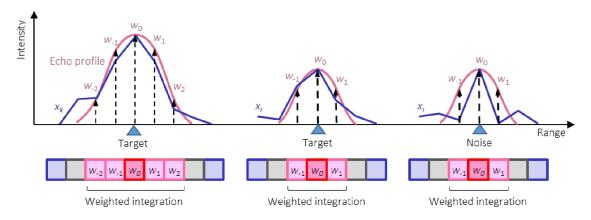

| 2.15 | Basic design of a CFAR operator [OW16]                                                                                                                                                                                                                                                                                                   | 40 |

| 2.16 | Design of the extended CFAR operator [OW16].                                                                                                                                                                                                                                                                                             | 40 |

| 2.17 | Intensity integration over neighboring cells [OW16]                                                                                                                                                                                                                                                                                      | 41 |

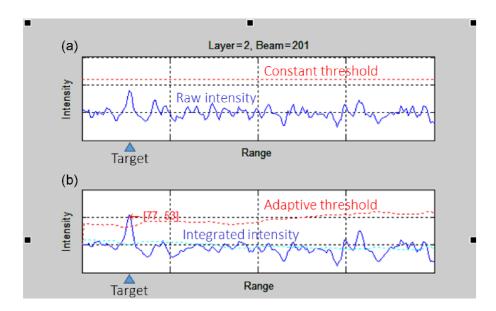

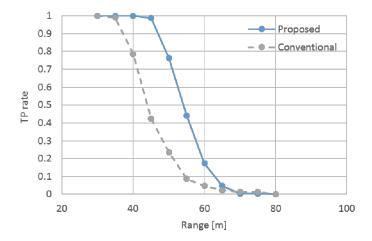

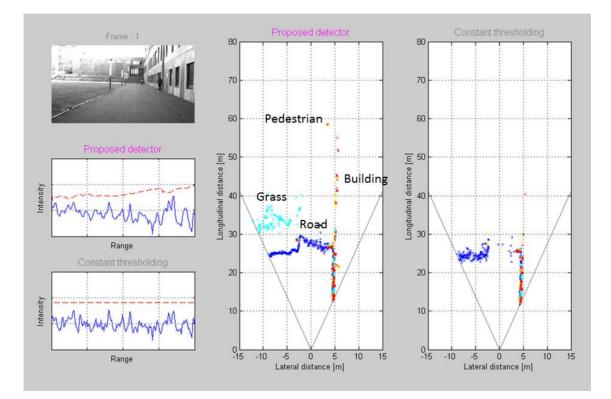

| 2.18 | Example results showing the difference between a constant and an adaptive threshold for the detector [OW16].                                                                                                                                                                                                                             | 41 |

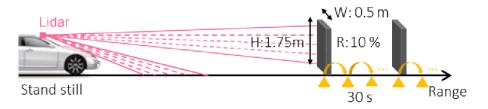

| 2.19 | Experimental setup [OW16]                                                                                                                                                                                                                                                                                                                | 42 |

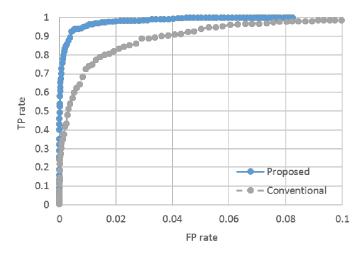

| 2.20 | ROC curves for both detectors [OW16]                                                                                                                                                                                                                                                                                                     | 42 |

| 2.21 | TP rates for both detectors at varying ranges [OW16]                                                                                                                                                                                                                                                                                     | 43 |

| 2.22 | Recording of a scene for comparison of the conventional and the proposed detector [OW16]                                                                                                                                                                                                                                                 | 44 |

| 3.1  | Overview of the LiDAR system and its interconnections. Orange components and interfaces are designed and implemented in this work.                                                                                                                                                                                                       | 45 |

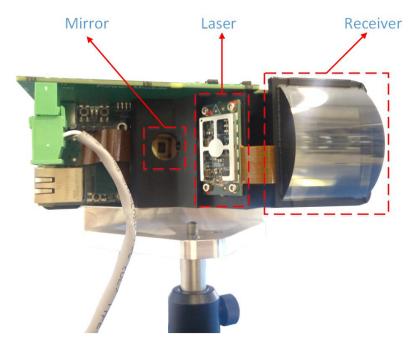

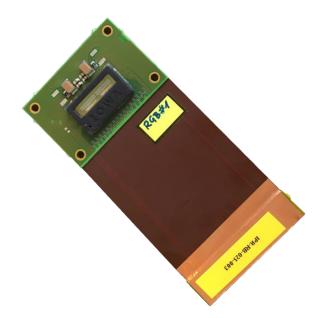

| 3.2  | The existing LiDAR prototype and its components                                                                                                                                                                                                                                                                                          | 47 |

| 3.3  | Receiver board with 32 APDs and LVDS lines                                                                                                                                                                                                                                                                                               | 48 |

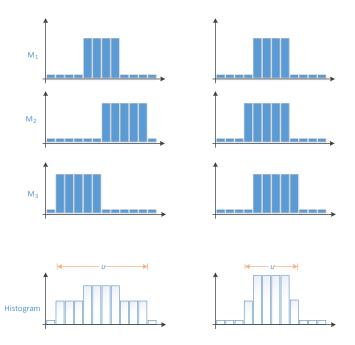

| 3.4  | Illustration of 3 measurements being accumulated into one histogram                                                                                                                                                                                                                                                                      | 51 |

| 3.5  | Left: Uncertain measurements with high time distribution. Right: Time distribution is narrow, therefore a lower uncertainty factor $U$                                                                                                                                                                                                   | 55 |

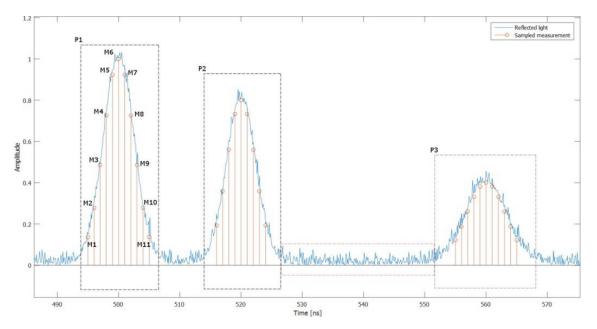

| 3.6  | A simulated reflection signal with the encoding scheme. In blue, the cap-<br>tured signal is presented. The red stems represent sampled measurements.<br>The rectangles $P_1$ to $P_3$ mark valid peaks which informations needs to be<br>preserved. The rectangle between $P_2$ and $P_3$ marks the signal part which<br>can be omitted | 56 |

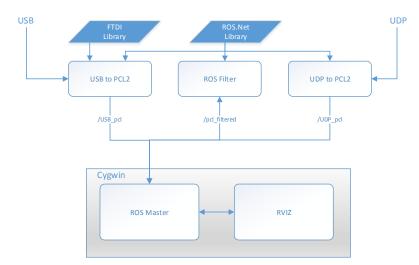

| 3.7  | Illustration of he developed software components and their interaction through the ROS system.                                                                                                                                                                                                                                           | 63 |

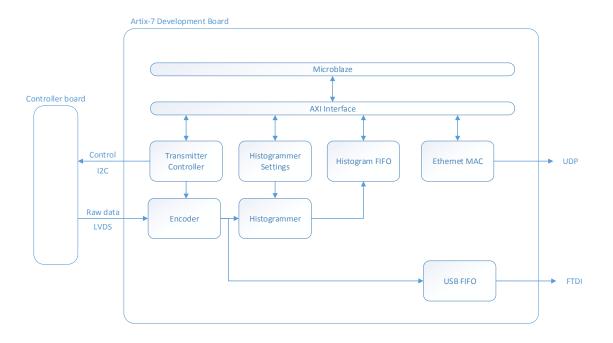

| 4.1  | System architecture illustrated for the hardware modules in the FPGA.<br>Most components are interconnected via an AXI bus and controlled by the<br>MicroBlaze. The USB communication is independent of the micro controller.                                                                                                            | 71 |

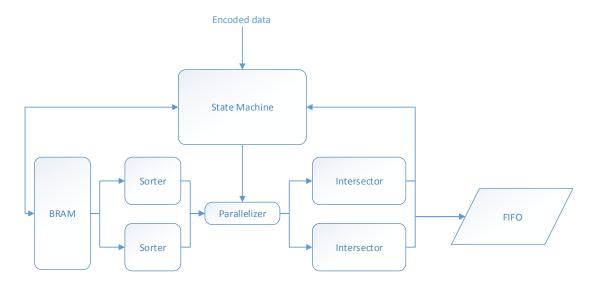

| 4.2  | Overview of the encoder module                                                                                                                                                                                                                                                                                                           | 72 |

| 4.3  | Flowchart of the transition encoder algorithm. It analyzes a 10bit input stream and detects pulse start indexes and their width in it                                                                                                                                                                                                    | 74 |

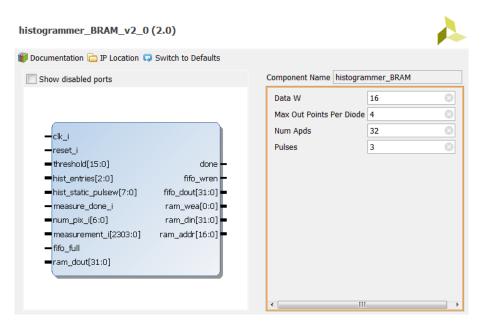

| 4.4  | Interface of the implemented histogrammer module including input/output signals as well as generic component options.                                                                                                                                                                                                                    | 76 |

|      |                                                                                                                                                                                                                                                                                                                                          |    |

| 4.5  | Overview of the inner structure of the histogrammer module. With receiv-<br>ing the encoded data the state machine starts and controls the computation<br>of the histogram                                               | 77 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

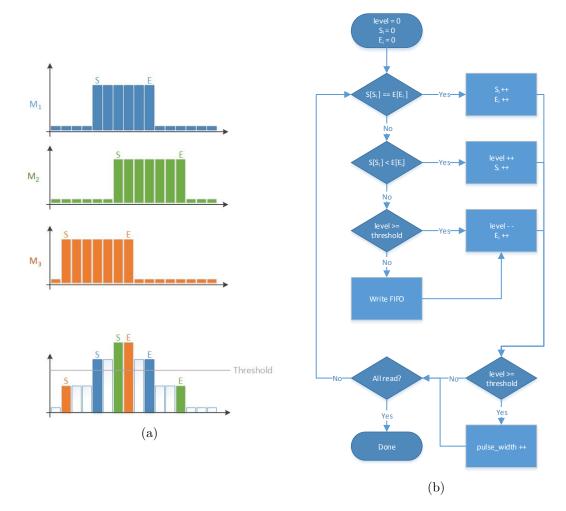

| 4.6  | (a) Sample measurements with highlighted start and end samples for accumulation. (b) Flowchart of the intersection evaluation algorithm                                                                                  | 78 |

| 4.7  | Memory layout for storing multiple measurements per shot line                                                                                                                                                            | 79 |

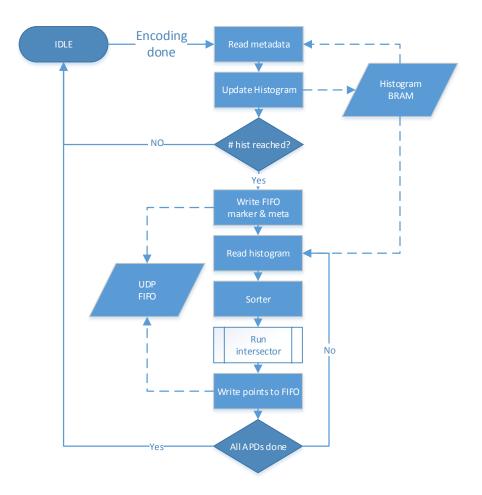

| 4.8  | Flow diagram for the histogram state machine.                                                                                                                                                                            | 81 |

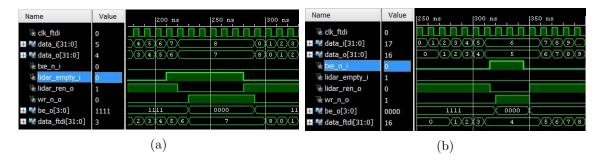

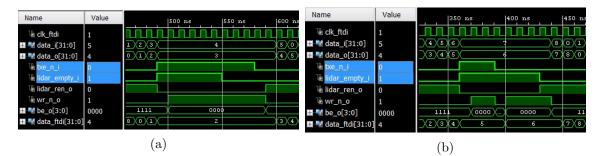

| 4.9  | (a) Signal waveforms in case of an empty FIFO buffer. (b) Signal waveforms in case of full internal FT601 chip memory.                                                                                                   | 85 |

| 4.10 | Signal waveforms in case of concurrent FIFO buffer empty and chip memory full scenario. (a) shows the signals when FIFO buffer empty signal is high shorter, (b) when it is high longer then the chip memory full signal | 85 |

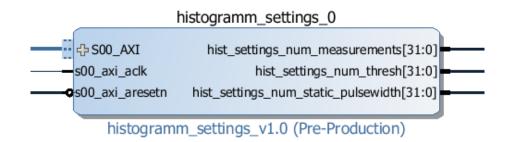

| 4.11 | Instantiation interface of the histogram settings block                                                                                                                                                                  | 86 |

| 4.12 | Graphical user interface of the ROS_Filter program.                                                                                                                                                                      | 89 |

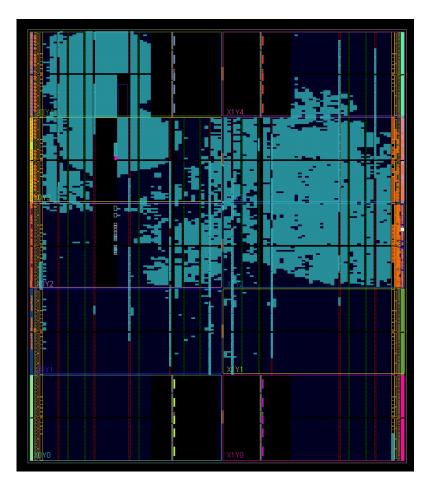

| 5.1  | Implemented design utilization from Vivado placement view. Blue cells mark used resources like flip flops (FF) or BRAM.                                                                                                  | 93 |

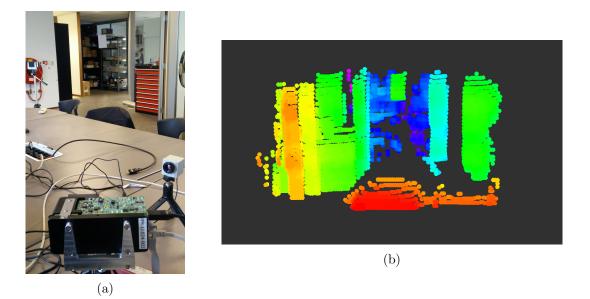

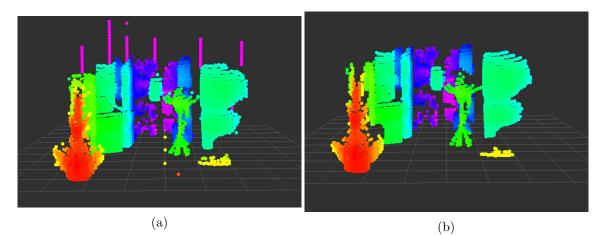

| 5.2  | In (a), a RGB-picture of the environment seen from the LiDAR perspective is shown. (b) shows the point-cloud of the scene.                                                                                               | 95 |

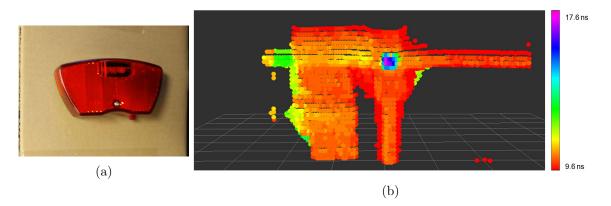

| 5.3  | Pulse width representation of a bike reflector. (a) shows the object itself,<br>(b) the point-cloud of a pedestrian holding the object                                                                                   | 96 |

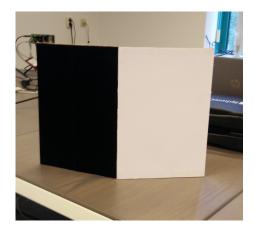

| 5.4  | Used target consisting of black felt and white paper to analyze confidence feature.                                                                                                                                      | 96 |

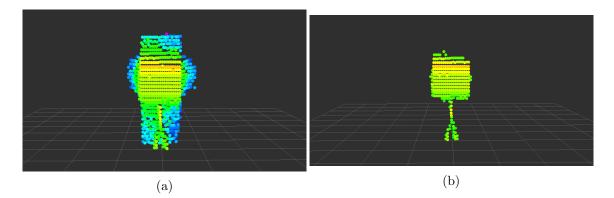

| 5.5  | Point cloud representation of carboard target on a tripod. (a) without filtering, (b) with filtered pulses below 18 clock ticks                                                                                          | 97 |

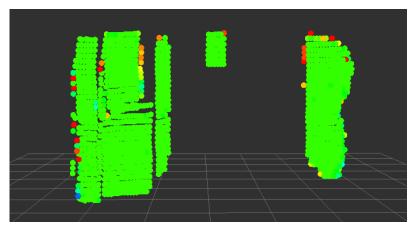

| 5.6  | Point cloud representing the testing environment color encoded with confi-<br>dence factor.                                                                                                                              | 98 |

| 5.7  | On the left side, the raw output of a scene with a second LiDAR is repre-<br>sented. On the right, a histogram of the same measurement is displayed                                                                      | 98 |

## List of Tables

| 2.1 | Specifications of the VZ-400                                                                                                                                      | 31 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Needed memory for different numbers of measurements per histogram $M_h$ .                                                                                         | 54 |

| 3.2 | Needed memory for different numbers of measurements per histogram $M_h$<br>and number of pulses <i>P</i> . $I_{bit} = 16bit$ , $L = 128$ , $A = 32$               | 58 |

| 3.3 | Data structure of one measurement packet. This packet contains data from histogrammed points of one line. Multiple measurement packets are part of one UDP packet | 59 |

| 3.4 | Data structure of one USB raw measurement packet. Each bit in a 32bit time field represents a corresponding sample of an $APD_x$                                  | 61 |

| 3.5 | Data structure of one USB encoded measurement packet. Each measurement of one APD is represented by 3 points, containing time index and pulse length.             | 62 |

| 4.1 | FIFO buffer settings for the Ethernet transferring FIFO                                                                                                           | 82 |

| 4.2 | FIFO buffer settings for storing and transferring USB data                                                                                                        | 84 |

| 4.3 | Packet format of a PointCloud2 message in ROS                                                                                                                     | 87 |

| 5.1 | Used resources of FPGA implementation.                                                                                                                            | 92 |

## Chapter 1

## Introduction

## 1.1 Motivation

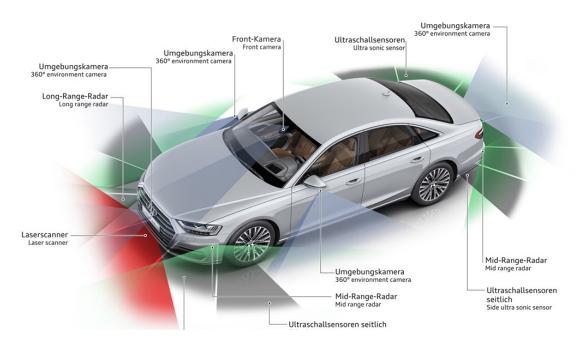

In the last years, the interest in automated driving has increased enormously. Due to technological progress, basic sensors and algorithms are already available and automated driving is not a futuristic idea anymore. But in order to accomplish reliable decision making by these algorithms, reliable data of the surroundings is required. Ideally, the sensors are able to reconstruct the entire environment of the car. State-of-the-art implementations therefore work with multiple sensors in order to generate a 360 degree coverage surrounding the car. In Figure 1.1, the sensor equipment of a level 3 automated driv-

Figure 1.1: Sensor equipment of an Audi to cover 360 degree around the car [AG.17].

ing car is illustrated. As it can be seen, multiple different sensors are used to generate multiple sources of data for analyzing. The sensors used are radar, camera, ultra sonic and Light Detection and Ranging (LiDAR). These are mounted on different sides of the car and cover a different, sometimes overlapping area. For ensuring the functionality of automated assistance functionality, the system requires both redundancy and diversity. Further, the system needs robust sensor data.

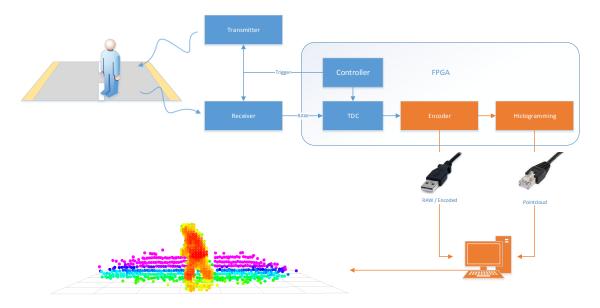

In order to be capable of processing all the sensor data and fuse them, the noise of the sources needs to be kept as low as possible. Another key aspect is the ability of processing the data in real time. In this thesis, a real-time data processing LiDAR system is presented. This system reduces the data to the essential information as well as increases the Signal-Noise Ratio (SNR) through signal averaging. All these processing steps are performed in real-time on a Field Programmable Gate Array (FPGA). Figure

Figure 1.2: Overview of the LiDAR system implemented in this thesis. Orange blocks are extended to an already existing system.

1.2 illustrates an overview of the system presented in this thesis. Blue components are already present in the existing prototype while orange colored modules are designed and implemented in this work. Generally, as in most existing LiDAR systems, a transmitter illuminates a scene, while a receiver samples the reflected light. The location of objects in the scene can be computed with a time-to-digital converter (TDC). The developed encoder then extracts all necessary information. This is passed on to the histogramming module, which performs signal averaging in order to increases SNR. Both components can transmit their data via an interface to a post-processing system. It is then possible to generate a 3D representation of the observed scene.

## 1.2 Objectives

This thesis focuses on the signal processing of 1bit LiDAR system. The signal processing techniques are designed and implemented for real-time processing and evaluated in a working prototype. The main goals of this work are:

- Extension of an existing 1bit LiDAR prototype implementation by adding encoding and histogramming to the signal processing path.

- Development of a data compression encoding on a FPGA meeting real-time constraints.

- Transfer and visualization of the gathered encoded data-stream

- Development and implementation of a histogramming module to increase the SNR.

- Provision of a software capturing and displaying histogrammed data.

- Evaluation of feature extraction of 1bit LiDAR data.

The implementation of the encoding and histogramming module will evaluate the usability of feature extraction on 1bit LiDAR data. In case of succeeding, LiDAR systems without analog-to-digital converter (ADC)s and therefore with lower costs could be constructed. Due to the real-time computation and the lower data rate, algorithms can provide decision making in automated driving systems faster.

## 1.3 Outline

The structure of this thesis is as follows. In Chapter 2, the theoretical part of this work is covered. The current state-of-the-art of LiDAR signal processing is described. The principle of time-of-flight as well as its current applications is presented. Additionally, different methods of feature extraction and their interpretation are explained. Chapter 3 contains the requirements for the work in this thesis. Further, it gives an overview of the components this work is split into. It also describes the structure of the processing algorithms used in detail. The workflow of the development as well as implementation related details are explained in Chapter 4. It also presents the implemented modules and their behavior. In Chapter 5, the results of this thesis are documented and discussed. It analyzes the implemented system regarding its performance and its limits. Finally, Chapter 6 summarizes the results while suggestions for further work based on this thesis are presented.

## Chapter 2

## **Related Work**

This chapter starts with an introduction to LiDAR technology and gives an overview of related topics. First, the concept of 3D imaging based on time of flight is explained. Next, possible features are listed and analyzed that can be extracted out of these measurements. Finally, certain state-of-the-art applications and currently investigated research topics are introduced.

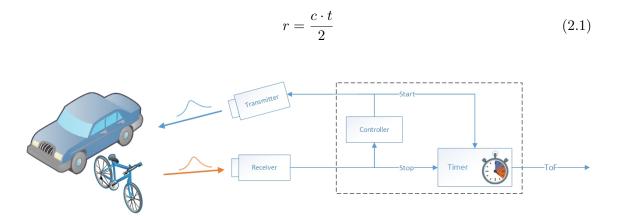

## 2.1 Laser ranging principle

Light detection and ranging (LiDAR), also known as laser detection and ranging (Ladar), relies on the time-of-flight principle (see Figure 2.1). Therefore, light pulses are emitted by the illumination unit of the LiDAR, reflected by the scene, travel back to the LiDAR and are detected by its receiving unit. The time t between emission and receiving of the light pulses is measured. By knowing the propagation speed of light c, the distance r can be derived according to Formula 2.1 [CC13].

Figure 2.1: Direct time-of-flight principle.

### 2.2 LiDAR Systems - State-of-the-Art

In the following Section, different state-of-the-art technologies for LiDAR systems are introduced. These include different technologies regarding the illumination unit, the receiving unit and signal processing approaches. Additionally, LiDAR systems can be distinguished by their field of application.

#### 2.2.1 Field of Application

Depending on the field of application, mainly three different types of LiDAR systems are distinguished. These are: terrestrial, airborne and mobile LiDARs. Terrestrial LiDARs are mounted on a tripod and usually perform a 3D scanning with one range measurement and two angle measurements. Airborne LiDARs are mounted on an aircraft and mobile LiDARs on a ground-based vehicle. Usually, airborne and mobile LiDARs perform two dimensional scanning with one line scan in one scan angle. [UPb]

#### 2.2.2 Time-of-Flight Measuring

In general, there exist three different approaches for the time-of-flight measurement. For the first one, *pulsed modulation*, discrete light pulses are emitted and the time-of-flight is directly measured by measuring the passing time between emission and receiving of the light pulses. With the second approach, *continuous wave modulation*, a continuous waveform is modulated onto the emitted light signal and the phase shift between outgoing and incoming signal is measured. A pseudo-random number sequence is encoded with the third approach, *pseudo-random number modulation*, and then an autocorrelation is performed with the received signal. [CC13]

#### 2.2.3 Illumination/Sensing

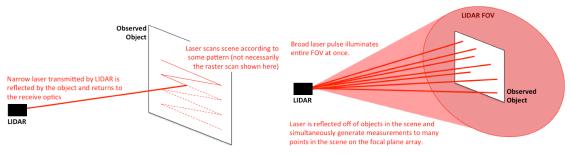

Depending on the illumination and sensing technology, two different types of LiDAR system can be distinguished. These types will be described more in detail in the following Section.

#### Scanning LiDARs

Scanning LiDARS have a narrow laser beam that is swept over the field of view in order to scan the scene. This approach is illustrated in Figure 2.2a. Either a single detector or an array of detectors is used to receive the reflected light. A system of mirrors, lenses or similar devices enables this system to sweep the narrow laser beam. By knowing the direction of the laser beam and the measured time-of-flight, a 3D point cloud can be obtained.

An advantage of scanning LiDAR systems is that they provide a high resolution at high precision. A typical application field is tracking of objects. While the system of

#### 2.2. LIDAR SYSTEMS - STATE-OF-THE-ART

(a) Example for a scanning LiDAR system.

(b) Example for a detector array LiDAR system.

Figure 2.2: Two different illumination/sensing technologies for LiDAR systems [CC13].

mirrors provides a high precision of the direction of the laser beam on the one side, these moving parts can wear out or lead to hardware problems on the other side. [SKKK]

#### Flash LiDARs

Flash LiDARs illuminate the entire scene at once, as it is illustrated in Figure 2.2b. The receiving unit is formed by a more-dimensional array of detectors. This means, that each pixel measures the time-of-flight of the reflected light it senses. With this method, a 3D image is obtained by combining the 2D pixel information with the measured time-of-flights. An advantage of detector array LiDARs over scanning LiDARs is that they are less failure-prone since they do not have any moving parts. However, since several detectors are used for the receiving unit, the complexity of calibration is increasing. [SKKK]

#### 2.2.4 Receiver

For detection of the light pulses, APDs are used. APDs are fast photo diodes that produce electrons via photo-electric effect and use the avalanche breakdown for internal amplification. These APDs can be driven in Geiger mode or linear mode. In this Section, these two different types for receiving are explained and their advantages and disadvantages are discussed.

#### Linear Mode

When an APD is used in linear mode, the via photoelectric effect produced current is proportional to the incoming photons. Most systems working with APDs in linear mode use a single laser and a single receiver that are swept over the field-of-view by reflecting and refracting elements [UPa]. These specifications yield in the fact that data is acquired sequentially.

Usually, ADCs are used to convert the output of the APDs into a stream of samples. In the first step, this stream is analyzed by separating noise and signal in order to detect the received echo signals, hence the targets. Therefore, a threshold is used that distinguishes between noise and a target. In the next step, the temporal position of these detected targets is determined and subsequently the distances to these targets can be derived. Additionally, information such as signal strength and reflectance of the target are estimated. A characteristic of LiDARs using linear APDs is a high distance resolution.

#### Geiger Mode

LiDARs in Geiger mode use APDs that are biased above their breakdown voltage. This means, that already a single photons triggers the APD. A comparison between linear and Geiger mode APDs can be seen in Figure 2.3. Another difference to linear mode is that a pixel can be triggered just once per laser pulse. As a result, the distance resolution depends on the recovery time of the APD. If the first target reflects enough photons, this target will be detected and targets near behind the first are ignored, since the APD already broke through. Another characteristic resulting from the effect of being triggered by a single photon is that no information like signal strength can be extracted. However, an advantage of Geiger mode LiDARs is that they can be used for very high range applications thanks to their high sensitivity, resulting from single photon triggering. [UPa] This high sensitivity

Figure 2.3: Comparison of ordinary photo diode, linear mode and Geiger mode APDs [Lab].

also leads to issues regarding solar background. It is an important point to minimize this solar background as far as possible. Therefore, different considerations play a role. First of all, the wavelength used for the system has a high impact and has to be taken into consideration. Further methods for reduction of solar background are listed from Stoker et al. [SANW16]:

- minimization of the system aperture

- implementation of a bandpass filter in the receive path

- reduction of the instantaneous field of view of the detector

- minimization of the range gate duration

- operation at night

#### 2.2.5 Signal Processing

In this Section, different aspects and technologies regarding signal processing for feature extraction and classification are introduced. The processing steps can happen in real-time, but also be applied on offline data after the measurements. The possible signal processing steps are highly dependent on the type of data available through one measurement.

#### Analog Discrete vs Full-Waveform Return LiDARs

Mainly two different kinds of LiDARs exist regarding the waveform of the return signal, analog discrete return and full waveform LiDARs. These are illustrated in Figure 2.4. With analog discrete return, each reflection is represented by a discrete peak at a certain time. Usually, TDCs are used for these kinds of LiDARs. The electric signal generated by photo-electric effect of the APDs triggers a TDC. By knowing the time when a peak returns, the range to the detected object can be calculated. The only information that can be obtained from the peak, is that there was a reflection. But no information about the signal strength of the return peak or its pulse width is gained.

Contrary, full-waveform LiDARs receive a continuous waveform of the return signal instead of discrete peaks. Usually, this is achieved by the usage of APDs in linear mode and fast ADCs for digitization. Full-waveform return signals provide additional information beside the distance, such as signal strength or pulse width. With these signal properties, features like reflectance, classification of targets' surface or object classification - just to mention a few of them - can be extracted. [UPa]

Figure 2.4: Illustration of analog discrete return and full-waveform return LiDARs [HGF13].

#### Feature Extraction with Full-Waveform Return LiDARs

As assumed by Ullrich and Pfennigbauer [UP11], the system response  $s_E(t)$  of a received signal is a convolution of the emitted laser pulse  $s_R(t)$  with the target signature T(t)[PWWU14]:

$$s_E(t) = s_R(t) * T(t)$$

(2.2)

This is also illustrated in Figure 2.5. The red line represents the shape of the laser pulse  $s_R(t)$ , the black line the target signature T(t) and the green line the system response

$s_E(t)$ . However, if it is possible to extract the target signature by a reverse convolution, properties about the detected target could be derived. This deconvolution is the current aim of full-waveform analysis. In general, there exist two kinds of approaches for this reverse convolution. The first one is a rigorous deconvolution. A disadvantage of this approach is that it is prone to noise. Another idea for the extraction of the backscattering properties is the attempt to reconstruct the received signal by the combination of basic functions. The most popular approach for this is Gaussian decomposition.

Figure 2.5: The system response (green line) of a received signal can be described as convolution of emitted laser pulse (red line) and target signature (black line) [UP11].

### 2.3 State-of-the-Art

For this Section, five different papers are presented that cover current research topics regarding LiDAR technology. These cover different techniques of feature extraction and their use. Since this work implements a histogram and analyzes the data of a discrete LiDAR system, the main focus on the presented papers is on signal processing. Full waveform LiDARs are more and more used in the research field since these provide the most feature-rich signals. But the underlying physical properties of these signals are also valid for discrete LiDAR systems.

#### 2.3.1 Calibration for Reflectance

In this Section, the work of Hartzell et al. [HGF13] is presented. The authors aim to develop templates for system response waveforms empirically. These templates should cover the dynamic range of terrestrial laser scanners when Gaussian fitting appears inapplicable. As a result, it should be possible to estimate the reflectance of an object by fitting the measured system response to a matching beforehand derived template.

#### **Experimental Setup**

The used hardware consists of a VZ-400. This is a tripod laser scanner from Riegl. In order to be capable of recording full waveform of the backscattered laser beam, a firmware upgrade was accomplished by the manufacturer. The most important specifications of the VZ-400 are summarized in Table 2.1.

|                                      | Longe Range Mode | High Speed Mode |

|--------------------------------------|------------------|-----------------|

| Effective Pulse Rate $(Hz)$          | 42000            | 122000          |

| Max. Range (reflectivity $90\%$ )(m) | 600              | 800             |

| Max. Range (reflectivity $29\%)(m)$  | 280              | 160             |

| Beam Divergence (mrad)               | 0.3              | 0.3             |

| Angular Resolution (°)               | 0.0005           | 0.0005          |

| Laser Wavelength $(nm)$              | 1550             | 1550            |

Table 2.1: Specifications of the VZ-400

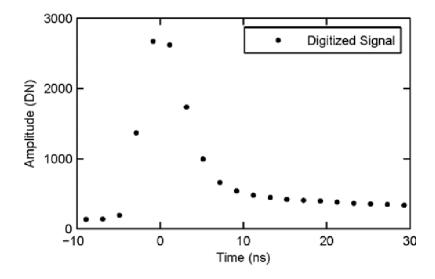

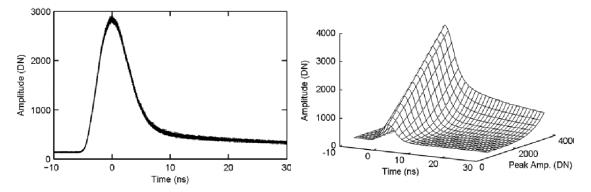

Along with the VZ-400, the authors encountered two main issues. The first one is that very few points are captured of the response pulse. This effect results from the short pulse width of the outgoing signal on the one hand, and the low digitization rate on the other hand. A typical waveform of such a response pulse is illustrated in Figure 2.6. The second problem arises from the fact that the response pulse does not describe a Gaussian distribution. Hence, Gaussian fitting is not very applicable for this laser scanner. Further, the user receives hardly any information about the internal properties of the scanner. Therefore, three 12"x 12" reflectance targets out of spectralon are used in order to measure with known reflectance and geometric configurations. At a wavelength of 1550 nm, these three targets have a reflectance of 99%, 62%, and 30%.

#### **Measurement Performance**

Several thousand measurements are performed at different distances (2m - 260m) in order to cover the dynamic range of the VZ-400 comprehensively. Then, the authors use cubic spline fit to align the waveforms. Thus, a 3D representation of the system response is achieved for each return pulse amplitude. This can be seen in Figure 2.7b, while Figure 2.7a illustrates a sample of a splined response pulse. All aligned waveforms for a certain distance are combined to obtain an averaged waveform that is representative for this

Figure 2.6: A typical waveform of a response of the VZ-400 [HGF13].

distance. All averaged waveforms over the different distances are then combined and form a template for a certain reflectance.

(a) Sample system response at certain distance (b) Alignment of several waveforms to obtain 3D and reflectance. representation.

Figure 2.7: The collected measured waveforms are aligned using a cubic spline fit in order to receive a 3D representation for each response pulse [HGF13].

Additionally, not only the distance was varied, but also the incident angle. The measurements were performed at incident angles of  $0^{\circ}$ ,  $20^{\circ}$ ,  $40^{\circ}$ , and  $60^{\circ}$ . This topic is covered more in detail in the next section.

#### 2.3. STATE-OF-THE-ART

#### **Incident Angle**

Hartzell et al. [HGF13] observed interesting effects regarding the incident angle. When observing the response waveform at the same distance with different incident angles, they expected the amplitude to decrease along with an increasing angle. This expectation was only met for distances above 160 m, but not for shorter distances.

Figure 2.8: Waveforms of backscattered signals with different incident angles (on the left side with a distance of 32 m, on the right side with 160 m). The amplitude does not change as much, regarding to the changing incident angle, as expected [HGF13].