Michael Kalcher, Dipl.-Ing., BSc

## Fully Integrated Mixed-Signal RF-Domain Transmitter-Induced Self-Interference Cancellation for Advanced Wireless Cellular Mobile Transceivers

## **DOCTORAL THESIS**

to achieve the university degree of Doktor der technischen Wissenschaften

submitted to

## **Graz University of Technology**

Supervisor

Univ.-Prof. Dipl.-Ing. Dr.techn. Bernd Deutschmann

Institute of Electronics

## AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present doctoral thesis.

Date

Signature

## Acknowledgments

This work has been done at the Institute of Electronics at Graz University of Technology in cooperation with Intel Austria, Villach. The completion of this thesis would not have been possible without the help of many.

First and foremost, I want to thank my supervisor Professor Bernd Deutschmann from Graz University of Technology. He provided the necessary academic and scientific feedback and input, and helped me navigate through all organizational matters. Furthermore, I express my gratitude to Professor Catherine Dehollain from École Polytechnique Fédérale de Lausanne, who agreed to be the external reviewer of this thesis.

Members of Intel's Villach site always made me feel welcome and continuously provided their help and guidance. Specifically, I want to acknowledge and thank my supervisor and mentor Daniel Gruber, for his patient guidance, his stamina, and his tenacity regarding matters concerning this thesis. He is not only an exceptional engineer, but also a humorous and straight forward co-worker. I have further relied numerous times on the help, knowledge, and insights provided by Alan Paussa, Davide Ponton, and Edwin Thaller, who also greatly helped conducting this thesis.

Moreover, I thank Francesco Conzatti, Thomas Hartig, Simon Grünberger, Werner Schelmbauer, and Claus Stöger for their help on various engineering issues and topics related to this work. Having essentially had only little experience with physical design of integrated circuits, I could rely on the help of Villach's strong layout team. Especially, I want to thank Markus Burian, Gerald Rauter, Christoph Duller, and Martina Rumpelnig for sharing their expertise. As all integrated circuitry are designed using computer aided tools, I want to express my gratitude to Patrik Osgnach and Gernot Babin, who fixed any such computer and tool related issues, of which I had many. For the manufacturing of the developed test chip, I give special thanks to Bernhard Stein and Zdravko Boos, who assisted me on organizational topics and helped making the tapeout finally happen. Furthermore, I thank Allan Borja for handling the assembly and related issues. Ultimately, I thank Ulrich Gaier and Thomas Lusin for their support in the final phase of the project.

I also want to thank my fellow students at Graz University of Technology, Lukas Zöscher, Markus Hänsler, and Patrick Schrey, and additionally Stefan Trampitsch, for numerous discussions of technical and administrative matters and whatever else would worry a PhD student. Further, I express my gratitude towards my dear colleagues at Intel Villach, Marco Bresciani, Patrizia Greco, Sanne-Maria Kobin, Gerald Spitz, Matteo Camponeschi, and Gerhard Knoblinger and to whomever else helped in one way or another.

Finally, I thank my parents, my sister, and my friends who, against all odds, managed to keep me sane during the time of working on this project.

Michael Kalcher

## Abstract

Mobile cellular data traffic has continuously grown exponentially for the past decade with no end in sight, mainly driven by users' increasing demand for video streaming. This fuels technological advances, e.g. certain aspects of the upcoming 5G standard, since the available RF spectrum for data transmission is restricted by regulations and physical limits.

A key 5G candidate technology to significantly increase spectral efficiency is in-band full duplex, where transmission and reception of signals simultaneously occur on an overlapping band of frequency; the known transmit signal completely blocks the receive unit without any further measures. The technology to enable in-band full duplex is self-interference cancellation (SIC). Furthermore, data throughput in existing 4G cellular systems with multiple aggregated carriers benefits from SIC: The fixed frequency separation of upand downlink channels and fragmented spectrum allocation for cellular operators creates challenging transmitter-induced self-interference scenarios.

Analysis of the state-of-the-art reveals that most existing SIC systems are either fully digital or analog/RF systems, incapable of simultaneously exploiting the benefits of RF-domain cancellation and digital signal processing. Fundamental investigations led to a novel hybrid SIC solution, a fully integrated RF-domain mixed-signal approach, presented in this work. The cancellation signal is generated digitally, benefiting from the flexibility of digital signal processing. A radio-frequency digital-to-analog converter (RF-DAC), specially designed for this application, is used to directly convert the digital signal into the RF-domain, where it is directly injected into the receiver, canceling the transmitter-induced self-interference and restoring receive performance.

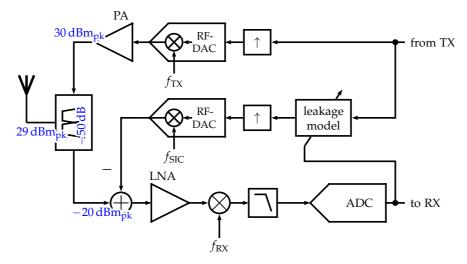

Based on this new SIC topology, an integrated CMOS demonstrator is developed and scientifically investigated. To demonstrate the feasibility of the approach, the mixed-signal RF-domain SIC system operates from 1.4 to 2.7 GHz covering the mid and high frequency 4G and 5G new radio frequency bands.

Furthermore, a novel quadrature and multiphase local oscillator (LO) generator circuit architecture is introduced, saving power in LO distribution. It is intended to be used as the quadrature LO source for the developed cancellation RF-DAC, but can also be directly employed in other applications. Based on the new topology, two prototype circuits are designed, a differential quadrature and a differential 120° three phase generator. The circuit architecture is scientifically investigated with simulations and measurements.

The proposed SIC method is scientifically evaluated and its feasibility, by means of the developed prototype, is demonstrated with comprehensive postlayout circuit level simulations. The SIC system achieves a cancellation performance better than 25 dB over a variety of analyzed self-interference scenarios, targeting high transmit and receive bandwidths exceeding 100 MHz. Furthermore, the proposed system allows the receiver to recover from saturation up to peak interference powers of -20 dBm. The achieved performance, which can be further enhanced with more sophisticated cancellation signal processing, demonstrates the feasibility of the proposed mixed-signal RF-domain approach.

The developed system and its demonstrated performance, besides being a key component for in-band full duplex, can enhance data throughput in existing 4G. Carrier aggregation scenarios which are limited by transmitterinduced self-interference, can be enabled with the proposed, scientifically analyzed, and implemented approach. The enhancements are especially beneficial where high transmit powers are required, i.e. at enclosed locations or far away from base stations.

# Contents

| Ał | Abstract                                           |                                                                                                      |          |  |  |

|----|----------------------------------------------------|------------------------------------------------------------------------------------------------------|----------|--|--|

| 1  | Introduction                                       |                                                                                                      |          |  |  |

|    | 1.1                                                | Thesis Organization                                                                                  | 3        |  |  |

| 2  | Transmitter-Induced Self-Interference              |                                                                                                      |          |  |  |

|    | 2.1                                                | Frequency Division Duplex Systems                                                                    | 7        |  |  |

|    | 2.2                                                | In-Band Full Duplex Systems                                                                          | 13       |  |  |

| 3  | A Review of Self-Interference Cancellation Systems |                                                                                                      |          |  |  |

|    | 3.1                                                | Self-Interference Cancellation for Frequency Division Duplex                                         |          |  |  |

|    |                                                    | Systems                                                                                              | 18       |  |  |

|    |                                                    | 3.1.1 Analog and RF Domain Self-Interference Cancellation                                            |          |  |  |

|    |                                                    | SystemsSystems3.1.2Digital-Only Self-Interference Cancellation Systems                               | 19       |  |  |

|    |                                                    |                                                                                                      | 32       |  |  |

|    |                                                    | <ul><li>3.1.3 Mixed-Signal Self-Interference Cancellation Systems</li><li>3.1.4 Conclusion</li></ul> | 37       |  |  |

|    | 3.2                                                | Selected Systems with Self-Interference Cancellation for In-Band                                     | 44       |  |  |

|    | 3.2                                                | Full Duplex                                                                                          | 45       |  |  |

| 4  | Mix                                                | ed-Signal RF-Domain Self-Interference Cancellation System                                            | 55       |  |  |

| -  | 4.1                                                | Transceiver Circuit Blocks                                                                           | 57       |  |  |

|    | 4.1                                                | 4.1.1 Transmitter                                                                                    | 57<br>58 |  |  |

|    |                                                    | 4.1.2 Receiver                                                                                       | 58       |  |  |

|    | 4.2                                                | Mixed-Signal RF-Domain Self-Interference Cancellation                                                | 59       |  |  |

|    | <b>-</b>                                           | 4.2.1 Maximum Leakage Power                                                                          | 60       |  |  |

|    |                                                    | 4.2.2 Canceler Noise in RX-Band                                                                      | 61       |  |  |

|    |                                                    | 4.2.3 Canceler Linearity                                                                             | 62       |  |  |

|    |                                                    | 4.2.4 Canceler Resolution                                                                            | 63       |  |  |

|    |                                                    |                                                                                                      | -        |  |  |

## Contents

|   |                                                                   | 4.2.5                                                  | Cancellation RF-DAC Local Oscillator and Sampling Fre- |          |  |  |  |  |  |  |

|---|-------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|----------|--|--|--|--|--|--|

|   |                                                                   |                                                        | quency                                                 | 64       |  |  |  |  |  |  |

|   | 4.3                                                               | rated Mixed-Signal RF Domain Self-Interference Cancel- |                                                        |          |  |  |  |  |  |  |

|   |                                                                   | lation                                                 | Prototype                                              | 68       |  |  |  |  |  |  |

|   |                                                                   | 4.3.1                                                  | Prototype Architecture                                 | 68       |  |  |  |  |  |  |

|   |                                                                   | 4.3.2                                                  | Self-Interference Cancellation Specification           | 69       |  |  |  |  |  |  |

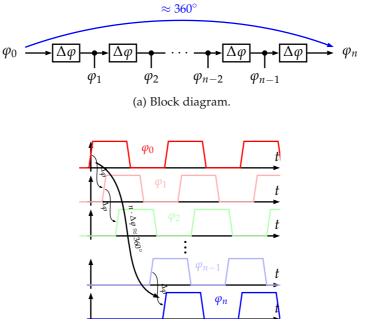

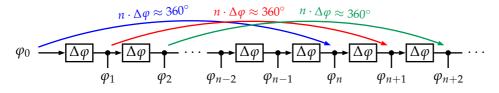

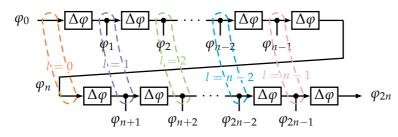

| 5 | Quadrature and Multiphase Local Oscillator Generation             |                                                        |                                                        |          |  |  |  |  |  |  |

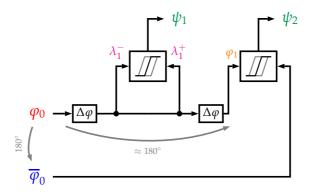

|   | 5.1                                                               | Quad                                                   | rature Generation                                      | 73       |  |  |  |  |  |  |

|   |                                                                   | 5.1.1                                                  | Operating Principle                                    | 73       |  |  |  |  |  |  |

|   |                                                                   | 5.1.2                                                  | Non-50% Duty Cycle of the Input Phases                 | 77       |  |  |  |  |  |  |

|   |                                                                   | 5.1.3                                                  | Circuit Implementation                                 | 81       |  |  |  |  |  |  |

|   |                                                                   | 5.1.4                                                  | Measurement Results                                    | 86       |  |  |  |  |  |  |

|   |                                                                   | 5.1.5                                                  | Comparison to the State-of-the-Art                     | 91       |  |  |  |  |  |  |

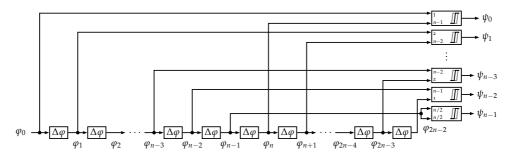

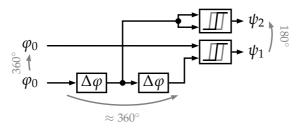

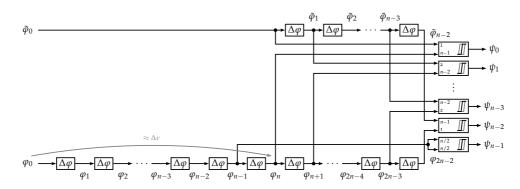

|   | 5.2                                                               | Gener                                                  | ralization and Multiphase Generation                   | 93       |  |  |  |  |  |  |

|   |                                                                   | 5.2.1                                                  | Operating Principle                                    | 94       |  |  |  |  |  |  |

|   |                                                                   | 5.2.2                                                  | Comparison to the Quadrature Phase Generator           | 98       |  |  |  |  |  |  |

|   |                                                                   | 5.2.3                                                  | Arbitrary Multiphase Interpolation                     | 100      |  |  |  |  |  |  |

|   |                                                                   | 5.2.4                                                  | Circuit Implementation                                 | 101      |  |  |  |  |  |  |

|   |                                                                   | 5.2.5                                                  | Simulation Results                                     | 105      |  |  |  |  |  |  |

|   | 5.3                                                               | Concl                                                  | usion                                                  | 108      |  |  |  |  |  |  |

| 6 | Mixed-Signal RF-Domain Self-Interference Cancellation Circuit De- |                                                        |                                                        |          |  |  |  |  |  |  |

|   | sign                                                              | _                                                      |                                                        | 111      |  |  |  |  |  |  |

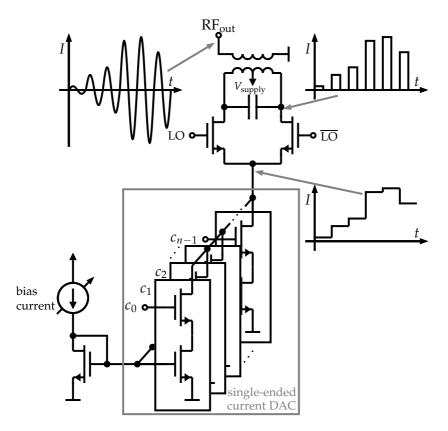

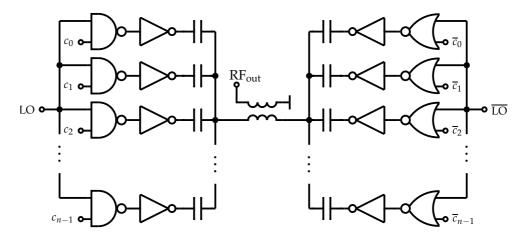

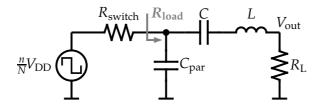

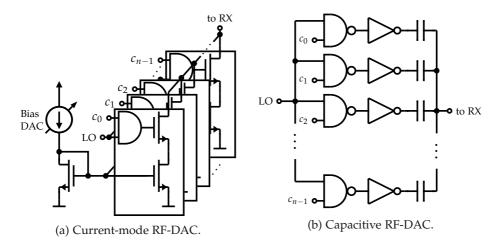

|   | 6.1                                                               |                                                        | ef Survey of RF-DACs                                   | 112      |  |  |  |  |  |  |

|   |                                                                   | 6.1.1                                                  | Current-Mode RF-DACs                                   | 112      |  |  |  |  |  |  |

|   |                                                                   | 6.1.2                                                  | Capacitive RF-DACs                                     |          |  |  |  |  |  |  |

|   |                                                                   | 6.1.3                                                  | Conclusion                                             | 116      |  |  |  |  |  |  |

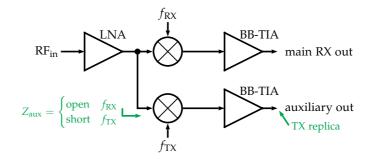

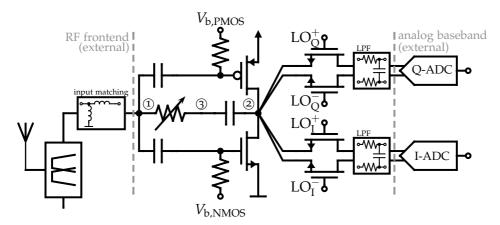

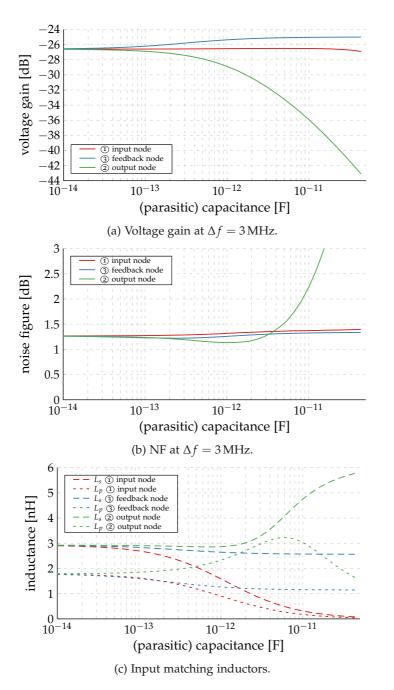

|   | 6.2                                                               | 0                                                      | ion-Augmented Receiver Design                          | 117      |  |  |  |  |  |  |

|   |                                                                   | 6.2.1                                                  | Adopted Receiver Design                                | ,<br>117 |  |  |  |  |  |  |

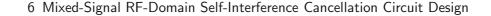

|   |                                                                   | 6.2.2                                                  | Cancellation Signal Injection                          |          |  |  |  |  |  |  |

|   | 6.3                                                               | Cance                                                  | ellation RF-DAC Design                                 | 124      |  |  |  |  |  |  |

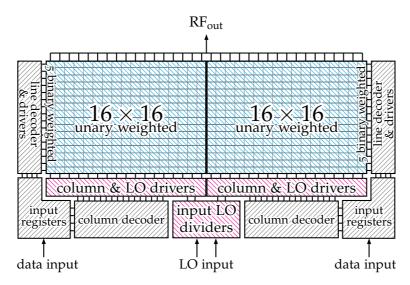

|   | 0                                                                 | 6.3.1                                                  | Cancellation RF-DAC Architecture                       |          |  |  |  |  |  |  |

|   |                                                                   | 6.3.2                                                  | Noise Contributors and Budget                          |          |  |  |  |  |  |  |

|   |                                                                   | 6.3.3                                                  | Circuit Implementation                                 |          |  |  |  |  |  |  |

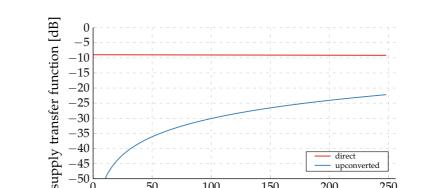

|   |                                                                   | 6.3.4                                                  | Supply Concept and Domains                             |          |  |  |  |  |  |  |

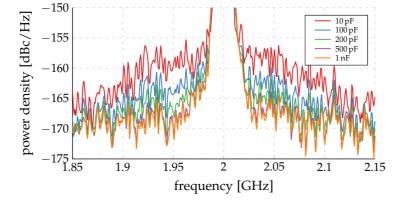

|   |                                                                   | 6.3.5                                                  | Supply Quality and Regulation                          |          |  |  |  |  |  |  |

|   |                                                                   |                                                        |                                                        | -        |  |  |  |  |  |  |

## Contents

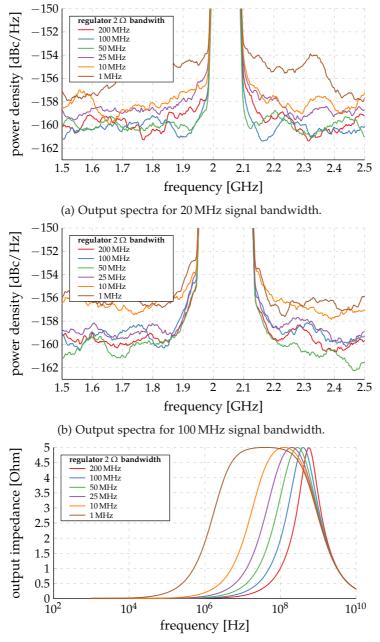

|    | 6.4           | Ultra-High Bandwidth Low-Dropout Regulator            |                                                   |     |  |  |  |

|----|---------------|-------------------------------------------------------|---------------------------------------------------|-----|--|--|--|

|    |               | 6.4.1                                                 | Flipped Voltage Follower                          | 162 |  |  |  |

|    |               | 6.4.2                                                 | Frequency Compensation Schemes                    | 165 |  |  |  |

|    |               | 6.4.3                                                 | Circuit Implementation                            | 172 |  |  |  |

|    |               | 6.4.4                                                 | Conclusion                                        | 178 |  |  |  |

|    | 6.5           | Cancellation System                                   |                                                   |     |  |  |  |

|    | 6.6           | Simula                                                | Simulation Results                                |     |  |  |  |

|    |               | 6.6.1                                                 | Cancellation RF-DAC Performance                   | 183 |  |  |  |

|    |               | 6.6.2                                                 | Cancellation of Single Tone Complex Exponentials  | 185 |  |  |  |

|    |               | 6.6.3                                                 | Cancellation of Multi Tone High Bandwidth Signals | -   |  |  |  |

|    |               | 6.6.4                                                 | Restoring Receiver Performance with SIC           | 201 |  |  |  |

|    | 6.7           | Conclu                                                | usion                                             | 204 |  |  |  |

| 7  | Con           | clusion                                               | and Outlook                                       | 207 |  |  |  |

|    | 7.1           | Mixed                                                 | I-Signal RF Domain Self-Interference Cancellation | 207 |  |  |  |

|    | 7.2           | Quadrature and Multiphase Local Oscillator Generation |                                                   |     |  |  |  |

|    | 7.3           | List of                                               | Publications                                      | 209 |  |  |  |

|    | 7.4           | Outlo                                                 | ok                                                | 211 |  |  |  |

| At | Abbreviations |                                                       |                                                   |     |  |  |  |

| Bi | Bibliography  |                                                       |                                                   |     |  |  |  |

## **1** Introduction

In recent years, the total global data traffic experienced exponential growth. According to Cisco [1], the total global traffic exceeded 150 EB per month in 2018, where approximately 20 EB per month are attributed to mobile (cellular) traffic. Similarly, Ericsson [2] claims exponential growth for mobile data traffic, reaching 20 EB per month in 2018 and exceeding 100 EB per month by 2022. Cisco, while predicting more conservative 77 EB per month in 2022, also forecasts exponential growth for mobile data traffic. Compound annual growth rates (CAGRs) exceeded 50 % in the past and are expected to further grow.

Increasing (wireless) data traffic is caused mainly by two technologically driven developments: First, cellular communication providers create new business models, e.g. by offering broadband fixed wireless access (FWA) or connectivity for internet of things (IoT) [3], [4]. Second, customers' demand for video streams significantly drives wireless and cellular data traffic. Technology-wise, this growth in data traffic fuels all further development, since all wireless radio communications operate on the limited resource of usable radio-frequency (RF) spectrum.

A key fifth generation (5G) candidate technology to significantly increase spectral efficiency is in-band full duplex (FD), where transmission and reception of signals simultaneously occurs on the same or an overlapping band of frequency [5], [6]. While there are many challenges to be solved to allow practical commercialization of in-band FD, existing cellular systems face spectral inefficiencies: The relatively inflexible frequency separation of transmitted and received signals and fragmented spectra allocated to the individual operators [7] further complicate or completely render efficient spectrum usage impossible. The crucial effect is transmitter (TX) induced self-interference (SI), which desensitizes reception or, in the case of in-band FD, (completely)

#### 1 Introduction

masks the received signals. A detailed problem description is provided in Chapter 2.

The key technology to counter these issues, as well as to enable in-band FD, is self-interference cancellation (SIC) [6]. Several SIC systems have been published so far, mostly either being fully digital or entirely analog systems. Fully digital approaches perform calculation of the cancellation signal as well as the cancellation itself in the digital domain, being unable to restore receiver (RX) performance in case of nonlinear operation, e.g. saturation or clipping. Analog/RF domain solutions perform cancellation and generate the required signals in an analog fashion, which makes it impossible to exploit the benefits of digital signal processing (DSP), amidst other drawbacks. Chapter 3 focuses on published and state-of-the-art SIC approaches with an emphasis on integrated circuit design.

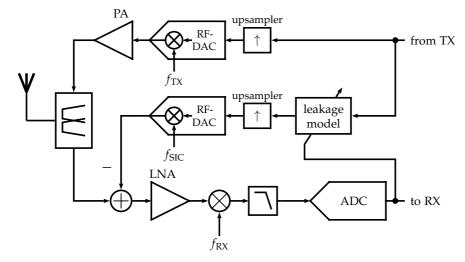

A hybrid solution, generating the cancellation signal digitally, converting it to analog and performing the cancellation in the RF domain was presented by Schacherbauer *et al.* in 2000 [8]. Using a discrete prototype composed from off-the-shelve components, Schacherbauer *et al.* demonstrated the principal operation of such a system. Due to the high overhead and some non-optimal design choices, the attractiveness of this system suffered, as well as being a discrete prototype.

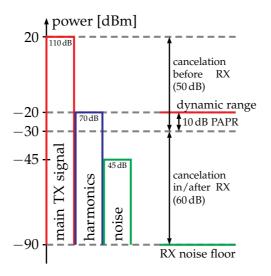

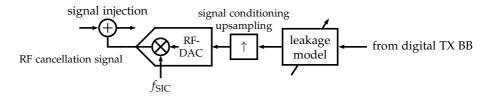

This work presents and investigates a novel hybrid SIC solution, a fully integrated RF-domain mixed-signal approach, greatly extending the previous approach. The cancellation signal is generated digitally, exploiting all the benefits of DSP. A specialized radio-frequency digital-to-analog converter (RF-DAC) is used to directly convert the digital signal into the RF domain, where it is directly injected into the RX, canceling the SI and restoring RX performance. Scientific analyses and further considerations on system level of the developed approach are summarized in Chapter 4.

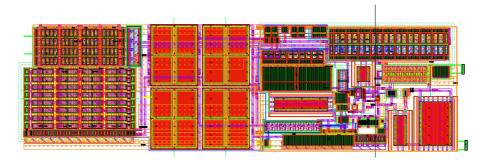

Within this work, to show the presented approach's feasibility, an integrated complementary metal-oxide-semiconductor (CMOS) demonstrator is developed. The system implements the proposed mixed-signal RF domain SIC approach, operating from 1.4 GHz to 2.7 GHz covering the mid and high Long-Term Evolution (LTE) and 5G new radio (5G-NR) frequency bands. Chapter 6 details the integrated circuit design of the dedicated cancellation RF-DAC and the SIC augmented RX.

Furthermore, a novel quadrature and multiphase local oscillator (LO) and/or clock generator circuit architecture is developed. It is intended to be used as the LO source for the developed cancellation RF-DAC, but can also be directly adopted for use in other applications. The circuit architecture is thoroughly detailed and investigated in Chapter 5. Two prototypes are developed, implementing a differential quadrature and a differential 120° three phase generator.

### 1.1 Thesis Organization

This thesis is structured as follows: Chapter 2 further details the effect and workings of TX induced SI. Chapter 3 provides a comprehensive review of published (circuit design oriented) SIC solutions. System-level considerations and aspects of the developed SIC approach are detailed in Chapter 4. The quadrature and multiphase LO circuit architecture and implementations are covered in Chapter 5. Circuit design and simulation results of the cancellation augmented RX and the cancellation RF-DAC and necessary auxiliary circuitry are detailed in Chapter 6. Finally, Chapter 7 concludes this work and provides an outlook on future research activities.

# 2 Transmitter-Induced Self-Interference

The phenomenon of transmitter-induced SI or alternatively TX-leakage has drawn the attention of RF engineers mainly due to two rather recent developments in mobile handsets.

First, the demand for cheaper, smaller and more flexible hand-held devices resulted in TX and RX architectures featuring less passive components with each generation. This trend is additionally accelerated by the digitization of as much RF functionality as possible, and the increased spectral flexibility required to support all the latest wireless communication standards [9].

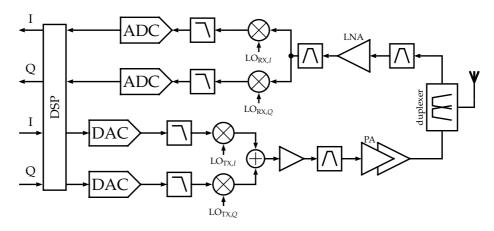

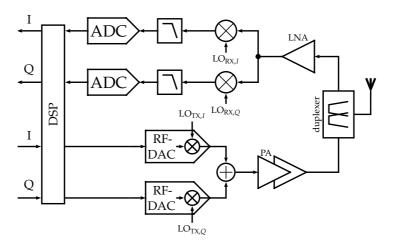

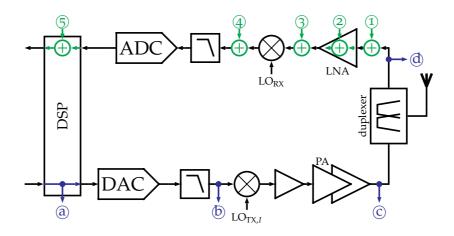

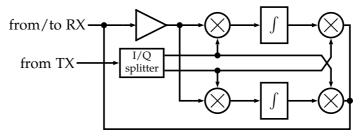

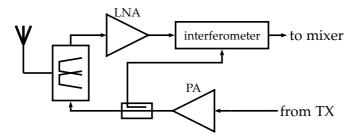

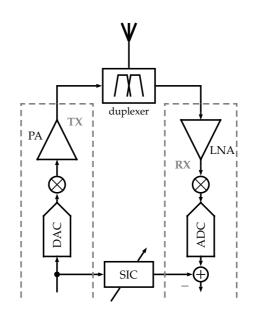

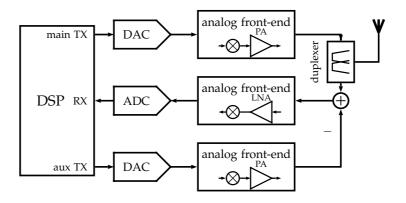

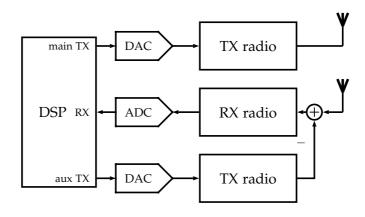

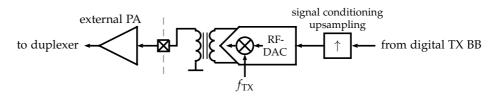

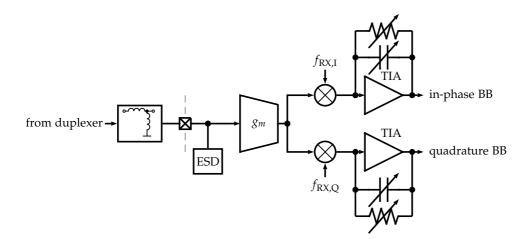

Figure 2.1 shows a conventional direct-conversion transceiver (TRX) setup, providing filtering in the RF domain and in baseband [10]. Modern direct modulation (cf. Figure 2.2) TRXs try to avoid as many passive components as possible, exploiting technology scaling and digital signal processing, and employing filters only when absolutely necessary.

The remaining distinct passive component in a TX-RX shared antenna system, commonly used in modern cellular phones, is the so called duplexer [11]. It decouples the RX from the TX. Such devices function similarly to circulators, but utilize the frequency separation of frequency division duplex (FDD) operation, achieving improved TX-to-RX isolation. Unfortunately, these components are generally fixed in operating frequencies, usually several of them are required for multi-band operation. They account for a big portion of a phone's RF system's cost, while providing only limited TX-to-RX isolation. These factors make manufacturers want to eliminate duplexers from their designs or replace them with cheaper components providing even less isolation. Similarly, systems having no duplexer but dedicated RX and

#### 2 Transmitter-Induced Self-Interference

Figure 2.1: Conventional direct-conversion TRX architecture.

Figure 2.2: Modern digital-intensive direct-modulation TRX architecture.

TX antennas equally suffer from limited TX-to-RX isolation, on top of the space and component overhead of two distinct antennas.

The reduced spectral selectivity in the RX caused by the omission of passive filtering increases the susceptibility to any interfering signals. The TRX's own transmitted signal leaking via the non-ideal isolation of the duplexers is especially critical due to the high transmit power required. This potentially strong interfering signal can drive the RX into non-linear operation regimes, 2.1 Frequency Division Duplex Systems

such as saturation or even clipping, therefore severely degrading the RX's performance.

Second, several technologies and techniques [12], [13] have been proposed to achieve the targets [4], [14], [15] of the upcoming 5G wireless communication standards. One of the candidate technologies is FD [16]–[18], where transmission and reception simultaneously occur in the same or an overlapping band of frequency. Advances in CMOS technology and signal processing enabled researchers to break the general consensus that FD communication is impossible [19, Chapter 14]. This technique potentially allows for doubled spectral performance of wireless communication systems and eases frequency planning.

Obviously, as the TX and RX are operating simultaneously on equal bands of frequency, due to non-ideal isolation, the transmitted signal directly masks the received signal. This is also true for low transmit powers, as there is no frequency separation compared to FDD systems.

Relaxing the requirements on isolation between the TX and RX paths in FDD TRX without adding additional filtering, as well as enabling FD communications, are made possible by utilizing knowledge of the TRX's own transmit signal. The harmful self-interference is canceled and eliminated in the RX.

## 2.1 Frequency Division Duplex Systems

Modern multi-mode hand held phones support a variety of (legacy) wireless cellular standards and bands, ranging from Global System for Mobile Communications (GSM) to LTE. Many of these bands are operated in FDD, where transmission and reception is occurring simultaneously but on different bands of frequency [20, Chapter 19].

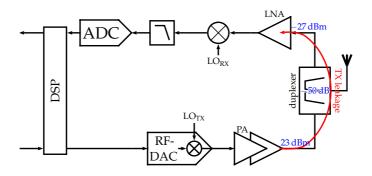

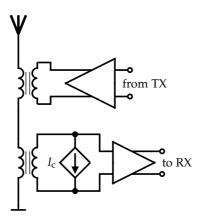

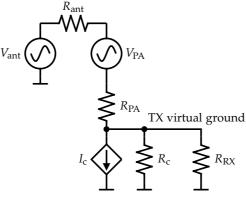

Due to nonideal components a portion of the transmitted signal is leaking into a simultaneously active RX: Either the dedicated RX antenna receives the (attenuated) TX signal, or in the shared antenna case the duplexer, which decouples the RX from the TX, provides only limited isolation, as sketched in Figure 2.3.

#### 2 Transmitter-Induced Self-Interference

Figure 2.3: Transmitter leakage in modern digital-intensive direct-modulation TRX (simplified architecture).

Even though the TX and RX operate in distinct bands of frequencies, the residual leaked signal can be substantial and heavily impair the RX performance. Also, the duplex spacing, i.e. the frequency separation between the uplink (UL) and downlink (DL) channels, is rather small, generally only  $4 \sim 5\%$  of the mean UL and DL frequencies, and as low as 10 MHz in the worst case. This phenomenon is further aggravated by the omission of frequency selective components in the RX and TX paths.

Practical high-performance duplexers are usually limited to approximately 50 dB TX-to-RX isolation subject to dynamic variations caused by changes in temperature and especially antenna impedance [21]. To put this figure into context, consider the maximum transmit power of handsets defined by the LTE standard of 23 dBm at the antenna [20], [22]. Assuming 50 dB of attenuation, the resulting leakage signal has a power of -27 dBm (2  $\mu$ W) at the RX's input. The RX's sensitivity level<sup>1</sup>, which varies with band and signal bandwidth, is always below -90 dBm (1 pW) [22]. Comparing this value to leaked signal power reveals a difference greater than six orders of magnitude, which can easily cause non-linear operation of the receiver, e.g. saturation or even clipping effects.

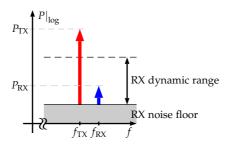

Such a scenario is sketched in Figure 2.4. The RX input signal is the sum of the weak desired signal at frequency  $f_{RX}$  and the self-interference portion

<sup>&</sup>lt;sup>1</sup>The sensitivity level defines minimum signal power level the receiver must be able to correctly receive, essentially specifying the required noise performance.

#### 2.1 Frequency Division Duplex Systems

Figure 2.4: RX signal powers in the self-interference case.

at frequency  $f_{TX}$ . If the signal power exceeds the RX's dynamic range (DR), non-linear clipping occurs rendering correct signal reception impossible.

In case the TX is operated in back-off, alas below its maximum power, and the received signal power is well above the sensitivity limit, the leaked signal (even when within the RX's DR, cf. Figure 2.4) can still cause performance degradations in the RX due to the low duplex distances and non-idealities in the RX, e.g. non-linearities, spurious tones on the LO etc.

A prominent example is the second-order intermodulation distortion (IMD2) caused by the non-linearities of the RX components [23]. A portion of the leakage is converted to undesired signal components around 0 Hz, i.e. falling into the baseband (BB) of direct conversion RXs. Hence, the received signal is corrupted with these second-order components.

Furthermore, the leaked signal, although centered around the TX frequency, can be directly downconverted into baseband corrupting the actual DL signal [24] by spurious and intermodulation tones on the LO.

This aforementioned effect is further aggravated by carrier aggregation (CA) introduced in LTE. In order to increase data rates, signal bandwidths need to be increased. In the LTE standard, the maximum signal bandwidth per RF carrier is limited to 20 MHz [20], [22]. To increase the effective bandwidth, several such carriers are aggregated to form a virtual signal band that exceeds this 20 MHz limit achieving peak data rates exceeding 1 Gb/s [25]–[27].

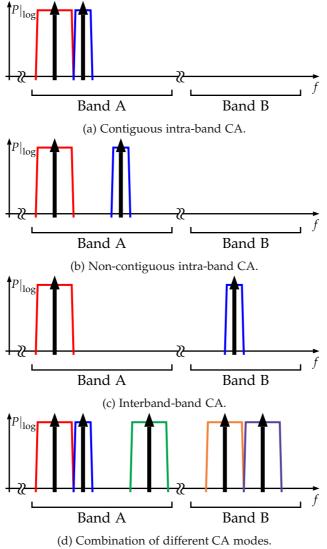

The LTE defines three possible CA scenarios [25]–[27] to accommodate the fragmented spectrum of wireless cellular operators [7]:

- 2 Transmitter-Induced Self-Interference

- Intra-band CA: Two or more RF carriers of potentially different bandwidths are combined in the same frequency band, forming either a contiguous signal band as sketched in Figure 2.5a, or a non-contiguous frequency band of virtual higher bandwidth sketched in Figure 2.5b.

- **Inter-band CA**: Two or more carriers are combined in different frequency bands, forming a virtual band as sketched in Figure 2.5c.

- Any combination: Currently, the LTE standards allows for combining up to five RF carriers. This can include inter- as well as intra-band and contiguous and non-contiguous CA. Figure 2.5d shows an example.

Any of these CA combinations increase the available signal bandwidth ultimately increasing data throughput. From an RF perspective, the intra-band contiguous case is potentially the easiest to handle: If the total continuous bandwidth does not exceed the RX's or TX's analog and signal processing bandwidths, virtually no or little modifications in RF circuitry are required, e.g. progressing from a maximum bandwidth of 20 MHz towards 40 MHz in the case of  $2\times$  contiguous CA.

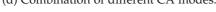

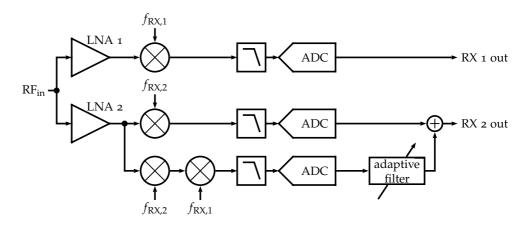

For the non-contiguous and inter-band CA cases most probably several TXs and RXs are required featuring their own LOs as sketched in Figure 2.6 for a  $2 \times$  DL-CA scenario. Due to non-ideal isolation and crosstalk between these simultaneously active LOs, additional spurious and intermodulation tones are present, some of them falling close to the transmit frequency (or frequencies) [24], [28]–[30]. This phenomenon aggravates the previously mentioned effect of downconverting the leakage signal from the TX into the received baseband.

Due to the coupling between the different LO signals, intermodulation spurious tones are generated from the harmonics of the LOs with frequencies

$$f_{\text{spur},mn} = m \cdot f_{\text{RX},1} + n \cdot f_{\text{RX},2} \tag{2.1}$$

where  $m, n \in \mathbb{Z}$  for the case of two simultaneously active RX paths. As an example assume the combination of LTE bands 5 and 7, where the band 5 UL frequency is  $f_{\text{TX}} = 832 \text{ MHz}$  and the aggregated DL bands are located at  $f_{\text{RX},1} = 877 \text{ MHz}$  and  $f_{\text{RX},2} = 2675 \text{ MHz}$  for band 5 and 7 respectively. Due to this coupling mechanism of the RX-LOs, several intermodulation tones are generated: The combination of m = 4 and n = -1 results in  $f_{\text{spur}} = 833 \text{ MHz}$ , which is only 1 MHz away from the TX frequency  $f_{\text{TX}}$ . If this spur

#### 2.1 Frequency Division Duplex Systems

Figure 2.5: Exemplary LTE CA scenarios.

#### 2 Transmitter-Induced Self-Interference

Figure 2.6: Transmitter leakage in LTE CA TRX with two dedicated receive paths for  $2 \times$  CA in DL (simplified architecture).

is prominent, a substantial portion of the leaked TX signal, centered around  $f_{\text{TX}}$ , is downconverted into the first RX baseband due to this intermodulation tone, impairing the received signal as sketched in Figure 2.6.

There are yet other transmitter-induced SI effects present in conjunction with CA. First, with several CA combinations a harmonic (e.g. second or third) of the UL signal directly falls into a paired DL band [31]. E.g. the third UL harmonic of band 17 (ranging from 704 MHz to 716 MHz, i.e. the harmonic potentially lies between 2112 MHz and 2148 MHz) directly falls into the associated DL of band 4 ranging from 2110 MHz to 2155 MHz, potentially degrading signal reception.

Second, in non-contiguous CA modes additional intermodulation effects can cause undesired signal components again falling into the RX band [32]. Assuming inter-band CA of bands 1 and 3 with TX frequencies of  $f_{TX,1}$  = 1950 MHz and  $f_{TX,2}$  = 1750 MHz respectively, several intermodulation products will appear. One such undesired distortion is the third-order intermodulation (IM3) component at  $f_{IM3} = 2 \cdot f_{TX,1} - f_{TX,2} = 2150$  MHz. This component directly falls into the RX frequency region from 2110 MHz to 2170 MHz of band 1.

A possibility to overcome these self-interference issues is increasing the effective isolation of the TX to the RX. The readily available TX (baseband) data, which defines the transmitted and therefore interfering signal, can be utilized to recreate the interference. This copy can then be used to cancel out the actual interference seen in the RX effectively increasing the TX-to-RX isolation. A review of published SIC systems for FDD applications is provided in Section 3.1.

### 2.2 In-Band Full Duplex Systems

In in-band FD systems transmission and reception of signals simultaneously occurs on the same or an overlapping band of frequency [5], [6]. Obviously the strongest interferer is the TRX's own TX without any frequency separation and directly impairing the received signal quality.

Assuming practical transmission powers in the ballpark of 20 dBm and sensitivity levels well below -90 dBm, which is true for Wi-Fi and LTE, the isolation requirement easily exceeds 110 dB [33]. Without sophisticated means of interference cancellation such isolation values are impossible to achieve.

An overview of published SIC approaches and solutions is provided in Section 3.2. The challenge not only lies in the tremendous power difference between RX and TX signals, but also in the composition of the SI signal. There are generally three categories these contributions can be classified into [33]:

- Linear components: Linearly weighted attenuated and delayed signal components e.g. from echoes and reflections. These should make up for the most part of the SI.

- Nonlinear components: Contrary to the linear SI portions, nonlinearities introduce signal components at frequencies different from the undistorted signal. A prominent example usually is the power amplifier in the TX path, which is a source of harmonics and spectral regrowth, e.g. in the adjacent channel leakage ratio (ACLR) region.

- **TX noise**: Noise from the TX becomes non-negligible due to the high power difference and must also be taken care of.

2 Transmitter-Induced Self-Interference

Obviously all these components must be canceled in a FD system, since all of them potentially fall into the RX bandwidth of interest. Bharadia, McMilin, and Katti [33] provide an overview of the cancellation requirements of FD for Wi-Fi-type systems.

Cancellation of the SI signal is required down to the RX's (thermal) noise floor, in order to achieve the same signal-to-noise ratio (SNR) compared to the non-FD operation. Cancellation of the interference below the noise floor obviously cannot further improve the SNR of the received signal.

As argued above, an isolation and/or cancellation of the linear main component of the TX signal of 110 dB is required. For cellular LTE-systems these numbers are even more stringent with lower sensitivity levels and higher output powers.

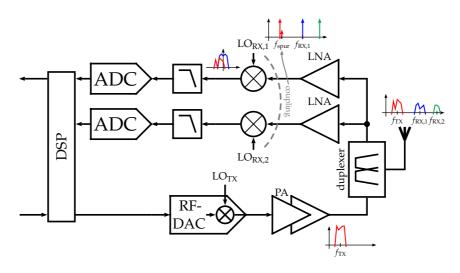

Second, the experimentally observed harmonics and spectral regrowth is more than 40 dB below the main linear component [34] for high performance TXs (i.e. 70 dB above the RX noise floor), dominating emissions in the adjacent channels. Similarly, the (thermal) TX noise is at least  $60 \sim 70 \text{ dB}$  below the main linear TX component, requiring roughly  $40 \sim 50 \text{ dB}$  of cancellation. In contrast to the linear and non-linear interference components, the noise portion obviously cannot be recreated by any algorithm from the baseband data. In order to cancel it a copy must be obtained where it is generated, e.g. at the TX output.

Figure 2.7 sketches these relations. An additional constraint again is the DR of the RX. Any (leakage) signal exceeding this limit results in clipping and other undesired saturation effects in the RX. Assuming a 70 dB dynamic range [35], already 50 dB of isolation and/or cancellation, also accounting for 10 dB peak-to-average power ratio (PAPR) of the TX and SI signal, must be present in front of the RX to avoid saturation.

Although challenging, in-band FD systems offer several benefits, complementing and sustaining the evolution of 5G networks, not exhibited in their non-FD counterparts [6]:

• **Increased link capacity**: Under ideal conditions true FD communication doubles the link capacity, because the available bandwidth can be utilized in both time and frequency.

#### 2.2 In-Band Full Duplex Systems

Figure 2.7: SI signal component powers in the FD case.

- **Spectrum virtualization**: True FD is the (extreme) case where both TX and RX bands are completely overlapping. Theoretically, the mechanisms employed in FD systems can isolate any TX and RX frequencies, e.g. partially and non overlapping bands of frequency. Such systems potentially act as software-defined duplexers.

- Eased CA scenarios: FD capable systems can isolate any TRX's own TX from any own RX, heavily easing CA configurations. With the reconfigurability of FD systems, various CA can be handled adaptively.

- Novel relay solutions: With FD systems employed in base stations and relays, the simultaneous reuse of spectrum is possible for backhaul and access channels.

- **Physical layer network security** [36]: Instead of using the FD communication for enhanced throughput, the received signal can also be masked or jammed with a strong (meaningless) signal. Only the RX with knowledge of that jamming signal can cancel it and recover the desired signal.

Essentially several benefits justify research and development of SIC, although this obviously is a challenging task. Section 3.2 provides an overview over published SIC systems for FD applications.

# 3 A Review of Self-Interference Cancellation Systems

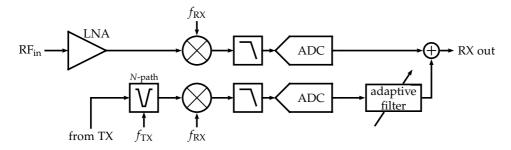

This chapter provides an overview of published SIC systems, both for FDD and FD applications. SIC systems can be distinguished not only by their targeted tasks. Further differentiation concerns the point(s) of cancellation in the RX and the generation and/or acquisition of the reference and cancellation signals.

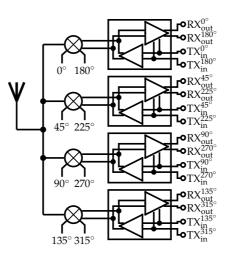

Figure 3.1 sketches possible points of cancellation signal injection into an RX lineup:

- ① at the very RX input

- ② in the input low-noise amplifier (LNA), e.g. in a specially designed LNA to support signal injection

- ③ after the input LNA, still in the RF domain

- ④ in the analog BB or intermediate frequency (IF) domain

- (5) digitally in the digital BB

Additionally, Figure 3.1 highlights potential points to obtain a TX reference signal to generate a cancellation signal:

- (a) digitally in the digital BB

- (b) in the analog BB or IF domain

- ⓒ at the TX's output

- d) at the RX's input

There are essentially three popular choices for SIC systems published:

First, fully digital systems, where the reference signal is obtained in the digital TX BB, additional signal processing is performed and the cancellation happens in the digital RX BB, e.g. a combination of (a) and (5) in Figure 3.1.

#### 3 A Review of Self-Interference Cancellation Systems

Figure 3.1: Cancellation signal injection possibilities (green) and potential taps to obtain the reference signal (blue) in modern wireless TRX (simplified direct conversion architecture).

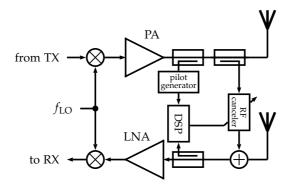

- Second, a full RF domain approach, where the reference signal is obtained at the very TX output and canceled in the RX's RF portion, e.g. from © to ①, ②, or ③.

- And third, a combination of the two approaches, almost always employed in in-band FD systems.

## 3.1 Self-Interference Cancellation for Frequency Division Duplex Systems

This section reviews published SIC systems for FDD applications, e.g. for (existing) third generation (3G) and fourth generation (4G) TRXs. Solutions battling issues introduced with CA, described in Chapter 2, are also covered in this section.

#### 3.1 Self-Interference Cancellation for Frequency Division Duplex Systems

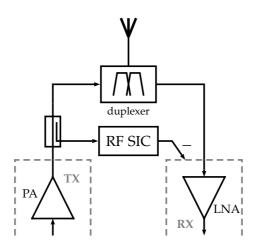

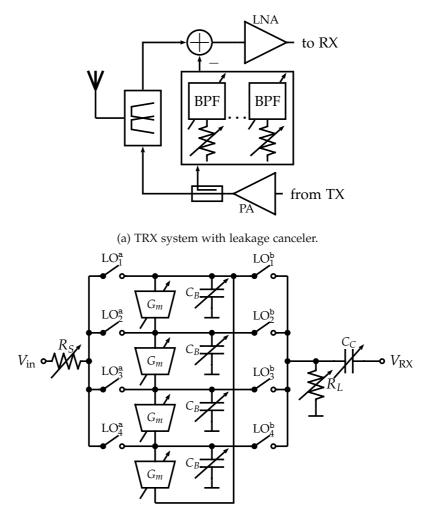

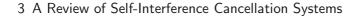

Figure 3.2: Conceptual sketch of TRX systems employing RF domain leakage cancelers.

#### 3.1.1 Analog and RF Domain Self-Interference Cancellation Systems

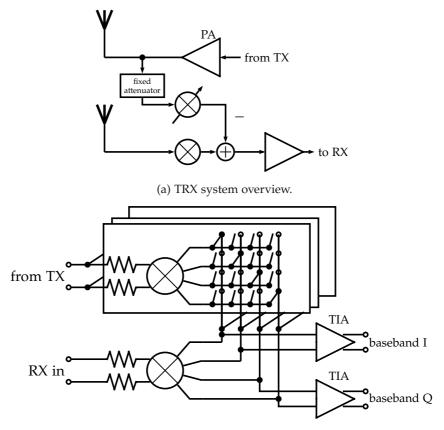

As briefly mentioned in the introduction of this chapter, and sketched in Figure 3.2, most RF domain SIC systems obtain a copy of the TX signal at the very output, just before the antenna or duplexer/coupler. This reference signal then is used by the SIC circuitry to generate a replica interference signal. The reference signal is accordingly modified, e.g. delayed and frequency shaped, to match the undesired signal at the RX as closely as possible in the frequency region(s) of interest. This interference replica is then subtracted in the RX in the RF domain.

It shall be noted, that RX interference tolerance enhancing methods, e.g. multiple paths or enhanced filtering (e.g. [37]–[39]), are not covered in this section. The reason is that these schemes mainly improve the out-of-band rejection by additional filtering and frequency selective multipath approaches, contrary to "traditional" cancellation scenarios. Similarly, electrical balance duplexers (e.g. [40]–[43]) are not covered in this survey, as they aim at directly providing the duplexing functionality on CMOS.

Research in TX related SIC essentially started in the late '90s with the prospect of extensions to GSM, such as General Packet Radio Service (GPRS) and En-

3 A Review of Self-Interference Cancellation Systems

Figure 3.3: Adaptive duplexer structure employing a double loop cancellation structure introduced by Kannangara and Faulkner [44]. The transfer functions  $h_1$  and  $h_2$  are implemented as (programmable) time delays and attenuators.

hanced Data Rates for GSM Evolution (EDGE), as well as Universal Mobile Telecommunications System (UMTS). First, RF domain SIC was seen as a flexible and cost-effective alternative to the poor and insufficient performance of discrete passive duplexers.

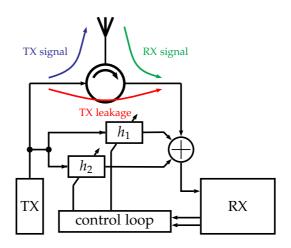

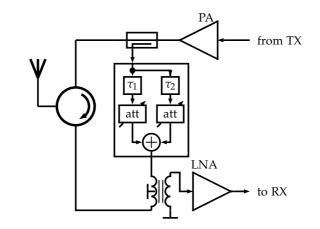

Kannangara and Faulkner proposed an adaptive wideband duplexer architecture [44], [45] for code division multiple access (CDMA) and wideband code division multiple access (WCDMA). They employ a wideband circulator with low isolation to couple the antenna and decouple TX from RX. The residual leaked TX signal is canceled with two delayed and attenuated replicas effectively generating two nulls: one at the main TX frequency, to avoid RX overloading and saturation, and another one at the main RX frequency, to remedy the TX-in-RX band noise. The setup is sketched in Figure 3.3.

With their discrete prototype, Kannangara and Faulkner achieve a cancellation of 46 dB (where an additional 20 dB of isolation are attributed to the wideband circulator) for an unspecified signal bandwidth.

This approach was advanced by O'Sullivan *et al.* [46] to improve the isolation of a surface acoustic wave (SAW) duplexer. The authors report an increase of

#### 3.1 Self-Interference Cancellation for Frequency Division Duplex Systems

isolation (i.e. cancellation) of more than 20 dB for 2 MHz wide CDMA signals for their discrete prototype and a single cancellation loop. Furthermore, for two loops, a 20 dB cancellation is reported for more than 4.5 MHz bandwidth. The power consumption is 9.75 mW and 22.4 mW for the single and double loops respectively. The authors report an insertion loss (IL) of 0.24 dB in the RX band.

The original structure was further extended with extensive means of DSP by Eslampanah *et al.* to support CA applications [47]. With their approach, they achieve a cancellation of 30 dB over a 20 MHz bandwidth with LTE signals in simulations.

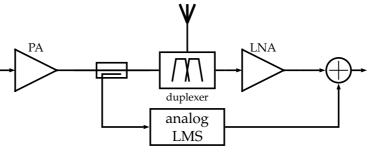

Also for CDMA RXs, Aparin *et al.* introduced a fully integrated leakage canceler featuring an analog least mean squares (LMS) algorithm to dynamically estimate the duplexer's or isolator's leakage transfer function [48]. The implemented system is sketched in Figure 3.4. The system essentially estimates complex coefficients with the analog LMS algorithm by trying to null the signal portion that is correlated with the TX signal.

With this approach, Aparin *et al.* achieve more than 40 dB of cancellation of a single tone at 835 MHz. For a 1.23 MHz bandwidth CDMA signal, employing a SAW duplexer, the cancellation degrades to 14.3 dB, compared to the case of 20.7 dB of leakage suppression, when a linear attenuator is used. Obviously the employed LMS cannot fully cover the complicated TX-to-RX transfer function, which essentially limits the cancellation performance for TX signals with wider bandwidths.

As further disadvantages of this solution the authors list reduced LNA gain and an increased noise figure (NF) from 1.4 dB to 2.7 dB. The maximum power consumption is reported as 16 mA from a 2.7 V supply and varies with operating frequency and TX output power.

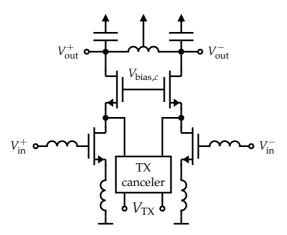

A more recent approach was introduced by Kim *et al.* for a WCDMA receiver [49]. A cascoded inductively degenerated differential common source (CS) LNA is extended with leakage cancellation as sketched in Figure 3.5a. The canceler, shown in Figure 3.5b, comprises a quadrature splitter, two variable gain amplifiers (VGAs), and an output summation and buffer circuit.

The quadrature splitter is implemented as a single passive polyphase filter (PPF) stage, since a precise  $90^{\circ}$  phase shift is not required. The VGAs in the

#### 3 A Review of Self-Interference Cancellation Systems

(a) Overall system employing the adaptive leakage canceler.

(b) Analog LMS algorithm to dynamically cancel the TX leakage.

Figure 3.4: Adaptive leakage canceler introduced by Aparin et al. [48].

quadrature paths are based on a modified folded Gilbert cell, whose gain can be changed from -1 to +1 respectively. The summation is done in the current domain simply by adding the output currents of the VGAs. By varying the gain accordingly, a full 360° phase rotation and amplitude variation can be achieved.

Finally, the buffer of the canceler is a differential pair, whose output drain terminals are directly connected to the LNA's low impedance nodes at the source terminals of the cascode devices. The required phase rotation and amplitude of the cancellation signal are determined by an adaptive LMS algorithm operating in the RX's baseband.

Using an external SAW duplexer for UMTS with 25 dB of passive isolation, Kim *et al.* report a minimum TX leakage rejection of 22.5 dB throughout the whole WCDMA band for 5 MHz signal bandwidths. The NF of their LNA increases from 2.4 dB to 2.84 dB when the cancellation unit is active. The full

#### 3.1 Self-Interference Cancellation for Frequency Division Duplex Systems

(a) Inductively degenerated LNA with leakage cancellation.

(b) Block diagram of the employed leakage canceler.

Figure 3.5: TX leakage cancellation system by Kim et al. for WCDMA applications [49].

RX RF system consumes 19.6 mA from an 1.8 V supply, where 10.5 mA are attributed to the leakage canceler.

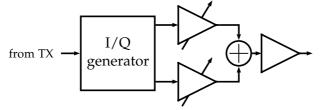

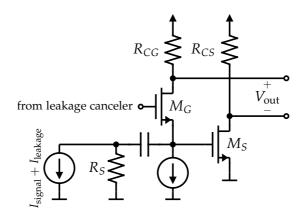

A principally similar solution of RF domain SIC was published by Zhou *et al.* [50], [51], employing a cancellation signal injection-augmented common gate (CG) LNA. The LNA is based on thermal noise canceling [52], [53], sketched in Figure 3.6.

Transistor  $M_G$  is a wideband CG amplifier matched to the 50  $\Omega$  input, the matching stage. Transistor  $M_S$  is an inverting CS amplifier, sensing the input signal and the noise generated by  $M_G$ , the noise canceling stage. If the outputs of the two stages are subtracted, e.g. by differential signaling, the noise cancels and only the input signal remains.

#### 3 A Review of Self-Interference Cancellation Systems

Figure 3.6: Thermal noise canceling LNA [52], [53] augmented with SIC capabilities by Zhou *et al.* [50], [51]. Biasing not fully shown.

For TX leakage cancellation, the canceler's signal is injected onto the CG amplifier's gate, canceling the interfering signal at the input. Additionally, a second point of injection is added at the output of the CS path to further cancel the TX-in-RX-band noise.

The canceler has two paths, one for the CG and CS paths respectively. Each path is composed from programmable gain amplifiers, operating on quadrature split inputs, similarly to the previous approach by Kim *et al.* as sketched in Figure 3.5b.

Zhou *et al.* built a wideband SIC-RX operating from 0.3 GHz to 1.7 GHz achieving a NF of 4.2 dB without leakage cancellation active. The worst case NF degradation due to leakage cancellation is reported to be 0.8 dB when canceling SI with 2 dBm power (3 dB PAPR). Cancellation of roughly 30 dB or more is achieved with an antenna pair or an attenuator used as TX-to-RX isolating devices.

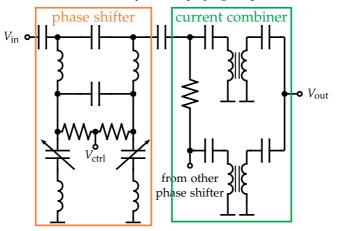

A passive leakage cancellation method based on the interferometer principle was demonstrated by Li *et al.* for frequencies above 10 GHz [54]. As sketched in Figure 3.7a, the suppression of the undesired leakage signal is achieved in the passive interferometer inserted after the RX-LNA. It consists of two lumped reflective type phase shifters and a transformer based current combiner. The current combiner additionally offers impedance transformation

(a) Cancellation enhanced TRX-system employing the passive interferometer.

(b) Schematic of the passive interferometer.

for on-chip loads different from  $50 \Omega$ . The full interferometer is sketched in Figure 3.7b.

Their prototype, fabricated in a 65 nm CMOS technology, occupies an area of  $0.95 \times 1.05 \text{ mm}^2$  and contains only the passive interferometer. Li *et al.* achieve a cancellation better than 40 dB in the frequency region of  $9.5 \sim 11.5 \text{ GHz}$  with optimal manual tuning, although neither signal bandwidth nor type is specified. Furthermore, the measured insertion loss of the interferometer prototype is 15 dB, which requires a high gain LNA in the RX lineup.

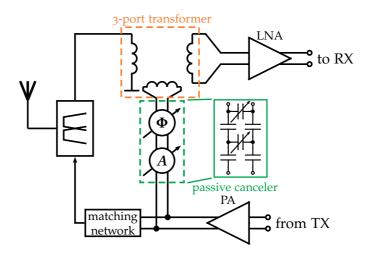

Zhang *et al.* presented another passive SI canceler based on a three-input transformer [55]. The transformer based matching network at the RX LNA's

Figure 3.7: Passive interferometer based TX leakage cancellation system by Li et al. [54].

Figure 3.8: Passive leakage canceler based on a three port transformer [55].

input is extended with another port to inject the cancellation signal. The block diagram of the implemented system is shown in Figure 3.8. The canceler itself is a passive circuit providing programmable attenuation and phase shift.

Their prototype, manufactured in a 40 nm CMOS process, occupies a silicon area of  $1.6 \times 1.3 \text{ mm}^2$ , including a matching network for the power amplifier (PA) (but not the PA itself), the leakage canceler, LNA and testing buffers. The transformer of the SIC system occupies an area of roughly  $400 \times 400 \,\mu\text{m}^2$ .

The peak measured LNA conversion gain is reported as 20.6 dB, including the IL of the employed WCDMA duplexer. The NF is approximately 5 dB over the entire 60 MHz RX band, including ILs of the duplexer ( $1.5 \sim 2 \text{ dB}$ ) and the transformer based leakage canceler and matching network ( $1 \sim 1.5 \text{ dB}$ ). The LNA's in-band third order input referred intercept point (IIP<sub>3</sub>) is +3 dBm.

Zhang *et al.* report an achievable cancellation of 23 dB for continuous wave (CW) signals across the entire TX band of  $1.92 \sim 1.98$  GHz when manually optimizing the canceler's settings. For modulated WCDMA signals with 3.84 MHz bandwidth a cancellation better than 20 dB is achieved.

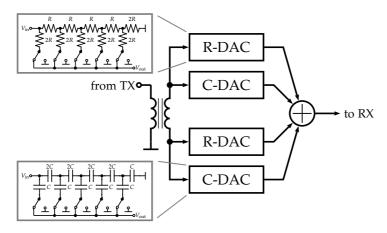

Another passive approach for RF-cancellation is presented by Montanari *et al.* [56], [57]. The proposed method is further combined with a mixed-signal TX-cancellation system, discussed in Section 3.1.3. The proposed RF leakage

Figure 3.9: Passive leakage canceler presented by Montanari *et al.* [56], [57]. The C- and R-DACs are programmable capacitive and resistive voltage dividers.

canceler gets the differential TX signal, either directly from the TX if available, otherwise by means of a balun. To minimize losses in the canceler, parallel programmable attenuators, one resistive and one capacitive, are placed on both differential phases. The output currents are summed and directly injected at the RX input, as shown in Figure 3.9. The attenuators are implemented as *R*-2*R* and *C*-2*C* networks respectively.

The prototype was manufactured in a 28 nm CMOS technology. The entire RX occupies an area of 0.51 mm<sup>2</sup>. The measured NF with the canceler disabled is 4.6 dB at 2 GHz, varying from 4 dB to 5.2 dB versus operating frequency. Activating the RF canceler degrades the NF by  $0.4 \sim 0.8$  dB, depending on its programming. For correct canceler settings, the authors report 20 dB cancellation for 15 MHz bandwidth signals. The RX IIP<sub>3</sub> is improved by 16 dB reaching 25 dBm until the canceler nonlinearity limits performance.

A different approach to replicate the TX-to-RX leakage signal path was chosen by Zhou *et al.*, where parallel band pass filters (BPFs) are employed to generate the desired transfer function in the leakage canceler [58], [59]. Figure 3.10a shows the overall system with the employed canceler consisting of parallel BPFs.

The cancellation signal is injected capacitively into the RX. The thermal noise canceling CG LNA is similar to their previous SIC implementation [50] pre-

(b) Implementation of an *N*-path  $G_m C$  second order filter.

Figure 3.10: Leakage canceler based on parallel BPFs by Zhou et al. [58], [59]

sented earlier in this section. The reconfigurable BPFs are implemented as high quality-factor *N*-path  $G_mC$  filters [60]–[62] with embedded programmable phase shifting and amplitude control. In Figure 3.10b the second order BPF's implementation is sketched. The filter bandwidth is controlled by changing the value of capacitors  $C_B$ , the center frequency by  $G_m$ , the attenu-

ation with  $R_S$ , and the overall phase shift by the skew of the 25%-duty cycle LO phases (denoted as a and b in Figure 3.10b) that is driving the filter's switches.

The prototype, manufactured in a 65 nm CMOS technology, occupies an active area of  $4.8 \text{ mm}^2$ . The measured RX NF ranges from  $4.8 \sim 5.8 \text{ dB}$  over the operating frequency range of  $0.8 \sim 1.4 \text{ GHz}$ .

For FDD operation, 20 dB cancellation bandwidths of 17 MHz and 24 MHz are achieved, when using one and two parallel BPFs respectively. An LTE-like *LC*-based duplexer, providing 30 dB of isolation, is used for this measurement. The increase in NF is measured as 0.5 dB and 0.6 dB respectively. In this case the *N*-path filters are driven with the TX LO, the frequency offsets of the filters are achieved by varying their respective  $G_m$ .

A single canceler's BPF's power consumption is reported as maximally 47 mW for the  $G_m$ -cells and additionally 44 mW for the LO at 1.35 GHz.

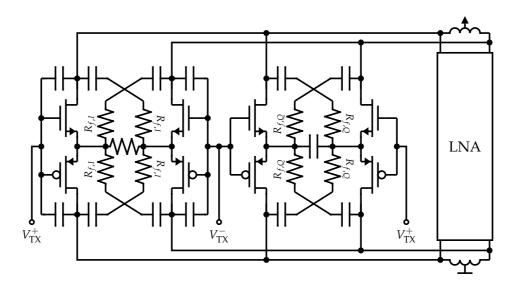

Another active RF domain cancellation scheme is presented by Tijani and Manstretta [63]. The required phase shift and attenuation of the TX signal is achieved by two parallel programmable transconductance amplifiers. The two amplifiers incorporate the functionality of an *RC-CR* quadrature splitter, as previously discussed. Furthermore, they are designed as slices, that can independently be turned on and off, providing for the required programmability. The system and the SI canceler are shown in Figure 3.11. To further linearize the canceling amplifiers, feedback resistors  $R_{f,I}$  and  $R_{f,Q}$  are added to feed back a portion of the RX and canceler's output signal.

The system is designed in a 40 nm CMOS technology with a 1.8 V supply. The maximum simulated power consumption of the active canceler is reported as 16.2 mW. In simulations, a 30 dB cancellation bandwidth is achieved when there is no TX-to-RX delay. For a more realistic scenario with 2 ns delay, the 30 dB bandwidth decreases to 10 MHz. The simulated NF degradation is 0.8 dB. For in-band scenarios, the 1 dB-compression point is improved from -25 dBm to 4 dBm with the cancellation active. Similar to out-of-band scenarios, it is improved from 1.7 dBm to 5 dBm in simulations.

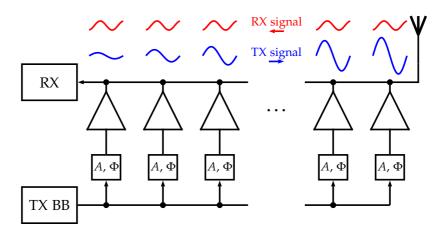

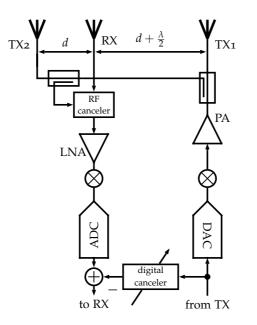

A different approach was adopted by Yüksel *et al.* [64], [65], where the interfering TX signal is canceled by destructive interference from the RX. Figure 3.12 essentially depicts the operating principle of the distributed TX,

Figure 3.11: Active RF-domain leakage canceler by Tijani and Manstretta [63].

Figure 3.12: Transmission line based duplexing scheme by Yüksel et al. [64], [65].

whose output signals add constructively towards the antenna output and cancel destructively to the RX input.

The individual sub-TXs have individual BB signal processing, effectively providing complex weighting factors. This allows for constructive TX signal combination at the antenna output while simultaneously nulling the signal at the RX input.

The artificial transmission line is implemented with lumped elements: inductors and capacitors, which provide an electrical delay. The design of the distributed TX, including the artificial transmission line, heavily influences the operating frequency region, output power and eventually TX efficiency. The number of TX stages  $N_{st}$  effectively determines the practicable frequency range  $f_{\text{max}}/f_{\text{min}} \approx N_{st}$ , while the interstage delay  $\tau_{st}$  sets the upper frequency limit  $f_{\text{max}} \leq 1/(2 \cdot \tau_{st})$ .

Furthermore, the practical limit of  $N_{st}$  is set by the maximum tolerable IL of the transmission line, since the RX signal needs to traverse through it, effectively degrading the RX NF. Also, the area occupied by the transmission line is non-negligible, as each interstage inductor has a value of 2 nH.

Yüksel *et al.* chose  $N_{st} = 6$ , although the three sub-TX closest to the antenna feature a special high-swing high-power design with increased supply voltage. In order to combat the uncorrelated noise of the sub-TX in the RX frequency band, an adaptive source degeneration of the PAs is included. A passive mixer is used to provide a narrowband degeneration at the RX frequency, effectively suppressing the TX-in-RX band noise.

Their prototype, manufactured in a 65 nm CMOS technology, occupies an area of  $2.4 \times 3.0 \text{ mm}^2$ . The operating frequency region is reported as  $0.3 \sim 1.6 \text{ GHz}$ . The TRX system consumes 2.2 W from a 2.5 V supply, while transmitting 16 dBm at 900 MHz and receiving at 785 MHz. The RX NF is measured as  $8 \sim 12 \text{ dB}$ , although a flaw in physical design prevented the prototype to achieve the expected performance.

The prototype achieves a TX-to-RX isolation better than 25 dB over the entire operating frequency range. A change in the voltage standing wave ratio (VSWR) (from 1 : 1 to 1 : 3) results in a drop of isolation by 20 dB and of 5.4 dB in output power. By recalculating the weights of the individual sub-TX, the TX-to-RX isolation can be restored.

Figure 3.13: Conceptual sketch of TRX systems employing digital-only leakage cancelers.

#### 3.1.2 Digital-Only Self-Interference Cancellation Systems

As introduced in the beginning of this chapter, digital-only SIC operates fully in the digital domain. This includes obtaining the reference signal, which is the data stream provided to the TX. The cancellation of the undesired leakage signal is also done entirely in the digital domain, after the analog-to-digital conversion of the RX as conceptually sketched in Figure 3.13.

This obviously implies that the SI must not degrade the RX's operation, e.g. drive it into saturation or clipping, since digital-only SIC only impacts the signal after all RF and analog signal processing. Therefore, digital-only SIC can only improve reception if, for example, nonlinear artifacts of the leaked TX signal have sufficiently low power and are well covered by the analog linearity the RX offers. These products may directly impair the desired RX signal, e.g. by folding or falling into the RX baseband, where they then may be removed with means of digital SIC.

Advantageous to digital-only SIC is that it fully exploits the benefits of digital signal processing, including adaptive filters [66], which are able to not only

learn the leakage transfer characteristics but can also track changes thereof over time. Furthermore, existing RX designs can be easily augmented with digital-only SIC. No changes to the analog and RF RX hardware are necessary, and no additional analog circuits, e.g. auxiliary LNAs, mixers, or analog-todigital converters (ADCs), are needed.

Therefore, research into digital-only SIC emerged with feasible and affordable integrated digital signal processing capabilities, which are directly linked to advances in CMOS technology.

First approaches in 2008 to digital-only SIC tackled second order nonlinear effects of TX leakage. Frotzscher and Fettweis published a LMS algorithm [67], [68] to cancel second-order intermodulation (IM2) products of the leaked SI signal in a zero-IF WCDMA RX. In such a system, these nonlinear TX-induced components directly fall onto the desired RX signal. Without any further means (e.g. improved TX-to-RX isolation or cancellation) the reception is heavily impaired by the TX leakage.

In simulations, with a linear SI model for their algorithm, Frotzscher and Fettweis achieve a 2 dB gain in SNR for a  $10^{-2}$  bit error rate (BER).

Similarly, Kahrizi *et al.* also mitigate the TX-induced IM2 distortion products in a WCDMA RX [69]. In addition to a LMS algorithm, an adaptive delay is added to align the TX IM2 products and their digital recreation. In simulations, the authors report that "cancellation" of the IM2 products is achieved.

Yet another LMS-based IM2 cancellation was published by Lederer and Huemer [70]. In addition to the LMS algorithm, an adaptive fractional delay filter [71] is added to improve cancellation. The authors report a measured improvement of the susceptibility of 5 dB of the RX to TX induced IM2 products for equal noise levels when comparing the cancellation algorithm switched on and off.

Similarly, Kiayani *et al.* introduced a digital-only IM2 cancellation system [72], based on a second order Volterra kernel [73]. The parameters of the model are estimated adaptively with a linear least squares (LS) algorithm. The authors specify that correct time alignment of the reference signal and the baseband output of the RX is crucial for correct operation.

The proposed IM<sub>2</sub> cancellation system introduces higher complexity and effort compared to the previously presented IM<sub>2</sub> cancellation schemes. But the authors report that for 10 MHz LTE signals their system outperforms the others, canceling the TX-induced IM<sub>2</sub> products below the RX noise floor.

In 2017 Gebhard *et al.* proposed a nonlinear low-complexity LMS-type algorithm for adaptive TX-induced IM2 cancellation [23], [74]. For 10 MHz LTE signals the authors report cancellation of the IM2 products down to the RX noise floor up to 23 dBm TX signal power with a high performance duplexer in place.

A different approach to IM2 (and other nonlinearities) cancellation is published by Gerzaguet *et al.* [75], [76]. The (nonlinearly distorted) reference signal is passed through an adaptive fractional delay and an adaptive single tap complex gain to recreate the leakage signal. The gain and delay are adapted with a joint LMS-based estimation algorithm. The authors report a signal-tointerference ratio after cancellation of more than 35 dB for their approach for 1.4 MHz bandwidth LTE signals.

Increasing data rates require higher bandwidths in the uplink TX signals required by modern wireless communication standards. All nonlinear components in the TX chain, especially the PA, contribute to spectral regrowth [77]. With increased signal bandwidths, inevitably the frequency range polluted by this intermodulation distortion (IMD) is also vastly increased. With low duplex spacings and high bandwidths, as specified and employed in UMTS and LTE, this TX out-of-band (OOB) emission can directly overlay with the simultaneously active RX band. This undesired IMD products can now also leak through the duplexer into the RX, degrading its performance.

While this effect can be countered by digital pre-distortion (DPD) of the TX [78], [79], effectively linearizing the TX, Omer *et al.* counter this effect with OOB emission SIC [80]. Several IMD products, potentially falling into the RX band, of the reference signal are generated. They are then passed through adaptive linear filters resembling the duplexer and other signal processing components in the leakage path. This closely resembles a bank of Hammerstein filters [81], [82] to recreate the leakage signal.

With recursive least squares (RLS) adaptation, the authors report a 18 dB cancellation of the leaked TX OOB emissions leaving a residual approximately

2 dB above the noise floor in measurements for a 10 MHz High Speed Uplink Packet Access (HSUPA) signal.

A similar approach is chosen by Kiayani *et al.*: They again recreate IMD products falling into the RX band [83]. These distortion components are again weighted and passed through a set of LS adaptive filters. In simulations, they achieve cancellation of the TX OOB emissions below the noise floor for a 5 MHz LTE signal. They also note that for acceptable performance, all necessary polynomial orders in the recreation of the reference IMD products are required.

Another issue related to TX-induced SI is the so called modulated spur problem. In this case, the RX LO exhibits a spurious tone close to the TX frequency. This spur, although with low power compared to the main tone at the RX frequency, downconverts the high power TX leakage directly into the RX baseband, corrupting reception. Spurs can be a result of nonlinearities, e.g. in the frequency synthesizers, or cross-coupling with other simultaneously active clocks or LOs.

First in 2012, Omer *et al.* tackle this modulated spur issue [84]. The approach requires knowledge of the RX, TX, and the spur frequencies. An iterative RLS-based approach is used to estimate the leakage transfer function and the spur downconversion characteristics.

For a 2MHz bandwidth Evolution-Data Optimized (EVDO) signal the authors report that their approach can restore the RX signal-to-interference-andnoise ratio (SINR) to the original SNR within 1.6 dB for low RX powers. For higher RX powers, starting at 15 dB of SNR, the restored SINR falls short by more than 3 dB compared to the original SNR. The higher power RX signal obviously disturbs the performance of the adaptive algorithms to estimate the TX leakage channel.

Kanumalli *et al.* propose a similar approach for LTE CA RXs [21], [23], [24]. In these systems two or more RX LOs are active. Combinations of these LOs or their harmonics can easily lead to such undesired spurs close to the TX frequency.

With an LMS-based estimation approach, where again all involved frequencies are known, the authors report more than 11.6 dB of cancellation for a 10 MHz LTE signal. For increasing RX signal strengths, again the restored

SINR drops compared to the original RX SNR, although the degradation is confined to 1.1 dB at 24.7 dB RX SNR.

Another challenge tackled by digital-only SIC is related to non-contiguous uplink CA (see Section 2.2). Dabag *et al.* developed a multiple-input single-output cancellation algorithm to battle intermodulation products of multiple TX falling into RX bands [85]–[87]. This algorithm considers only crossmodulation terms of two or more TX signals, as they potentially fall onto RX frequencies. For the different transmitters usually dedicated passive front-end components are used, resulting in different group delays of the individual TX signals before the antenna. The authors account for these different time delays in their cancellation system.

In simulations, perfect cancellation is achieved when correctly estimating the different delays of the TX signals for 5 MHz LTE signals. In measurements, for RLS-based adaptation and  $2 \times$  uplink CA with 5 MHz TX signals, a cancellation of more than 19 dB is reported for weak RX powers.

Kiayani *et al.* proposed a similar algorithm that also considers I/Q imbalance of the TXs [88]. In simulations, they achieve cancellation of the interfering intermodulation products below the RX noise floor for sufficiently high modeling orders, achieving  $15 \sim 20 \text{ dB}$  of suppression in presence of a weak RX signal. In measurements, for two 5MHz wide quadrature phase shift keying (QPSK) signals, cancellation of roughly 20 dB is achieved without an RX signal present. With a weak LTE downlink signal present, the leakage suppression is reduced to approximately 18 dB.

Yet another similar approach is introduced by Yu and Zhu [89], [90]: Contrary to the previous approaches, only a single crossmodulation term is computed from the two TX baseband signals falling into the RX band. Further nonlinear components are added by introducing the composite envelope of the total TX signal. This approach heavily reduces computation complexity and sampling rate requirements. Moreover, this approach can be generalized to incorporate multiple TX signals [89]. In measurements, for two 5MHz LTE signals, the authors report up to 25 dB of cancellation without any RX signal present.

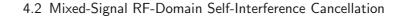

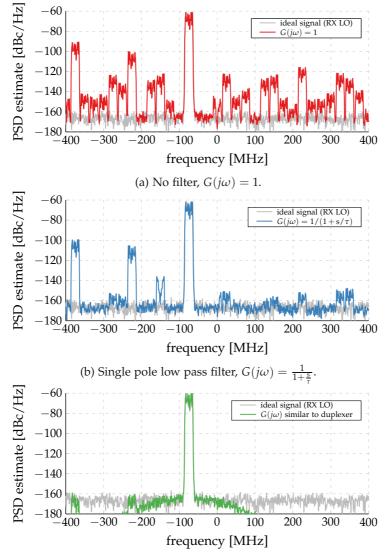

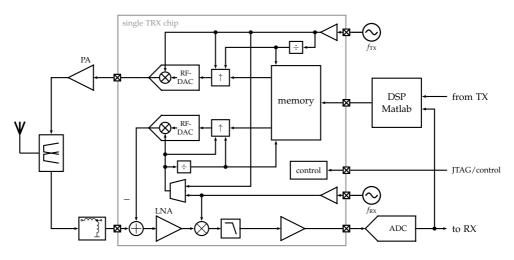

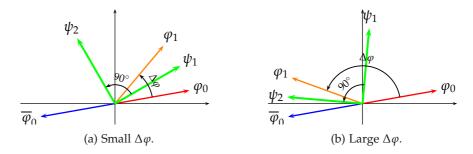

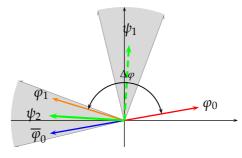

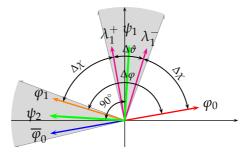

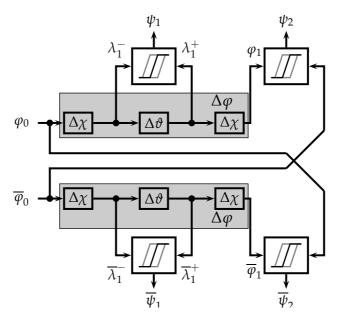

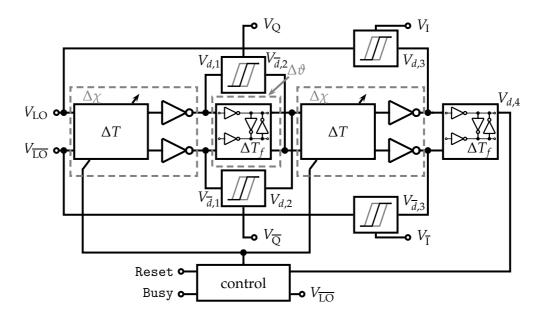

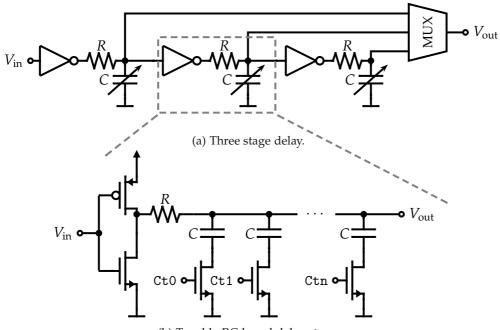

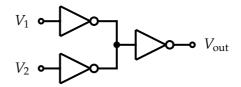

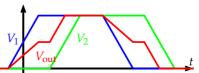

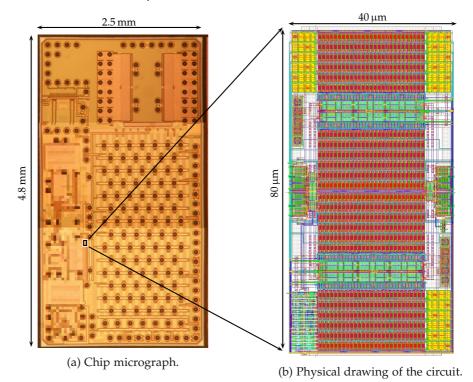

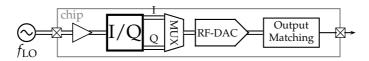

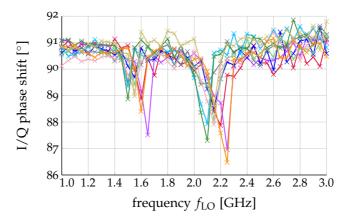

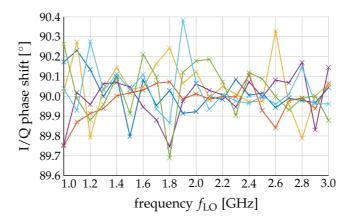

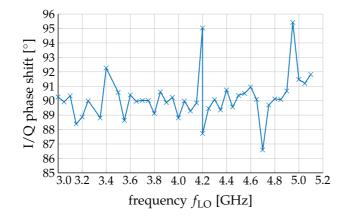

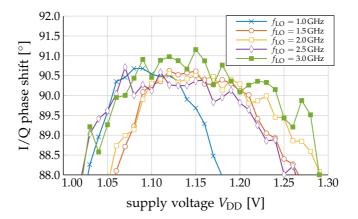

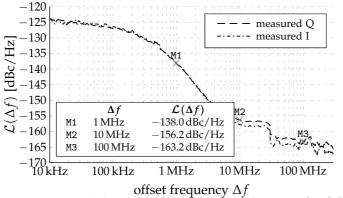

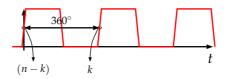

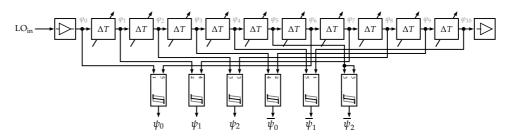

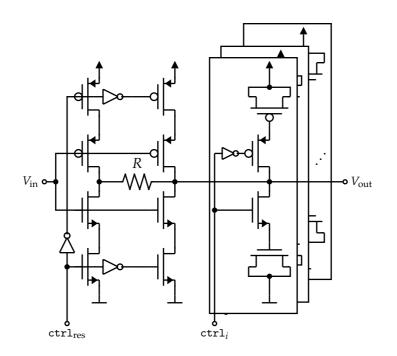

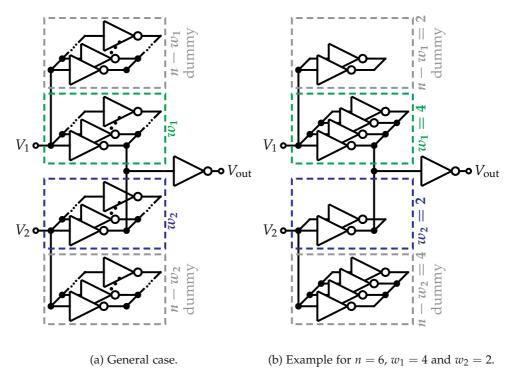

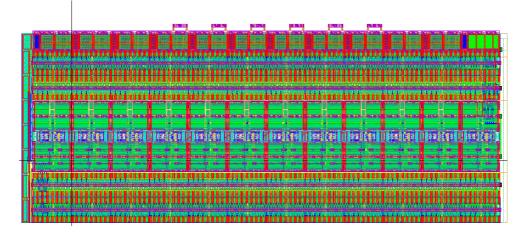

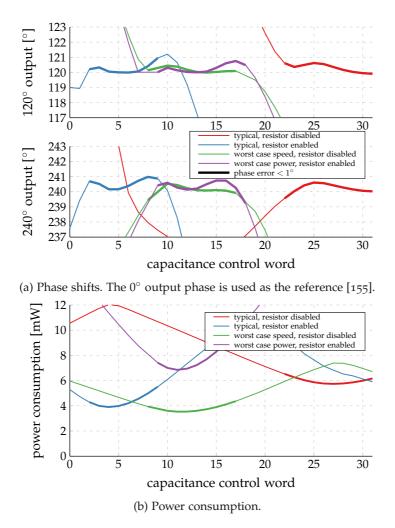

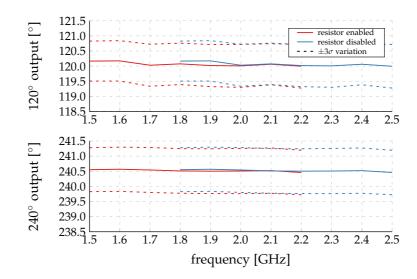

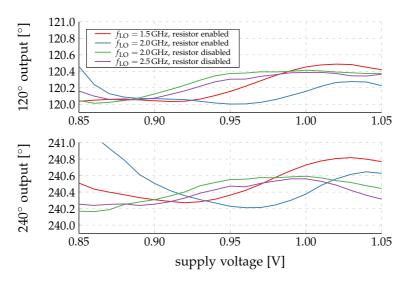

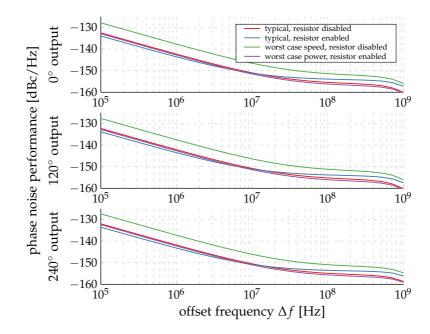

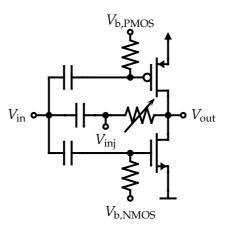

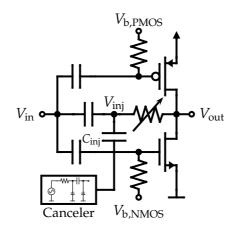

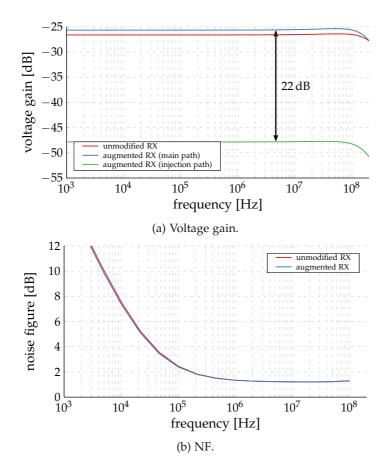

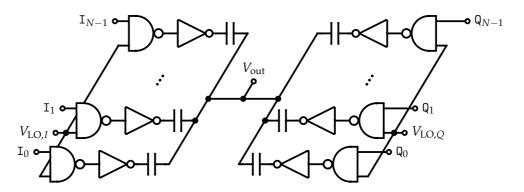

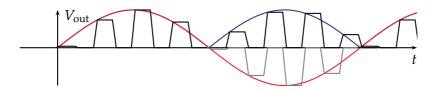

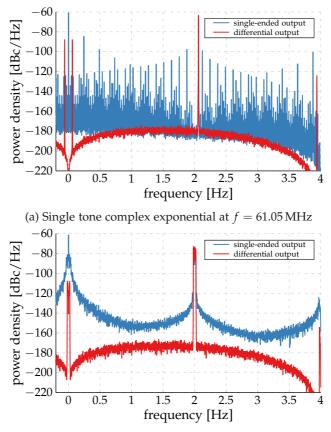

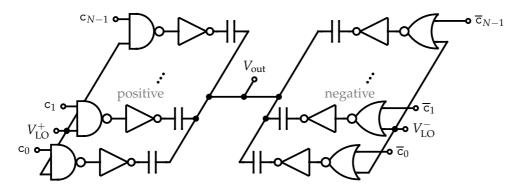

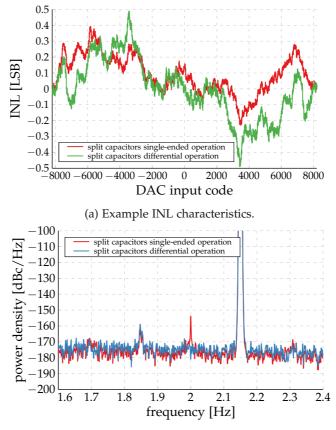

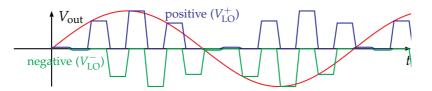

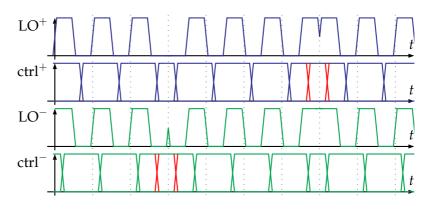

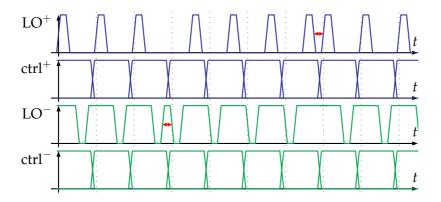

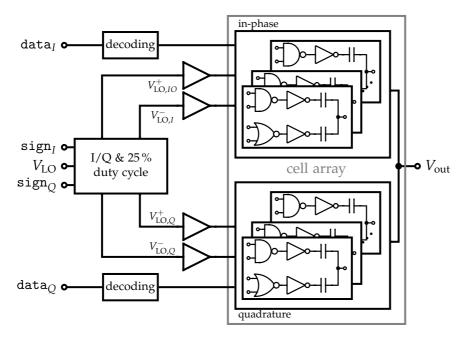

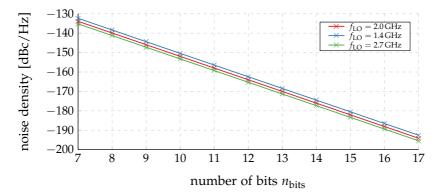

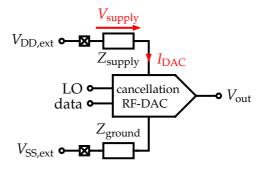

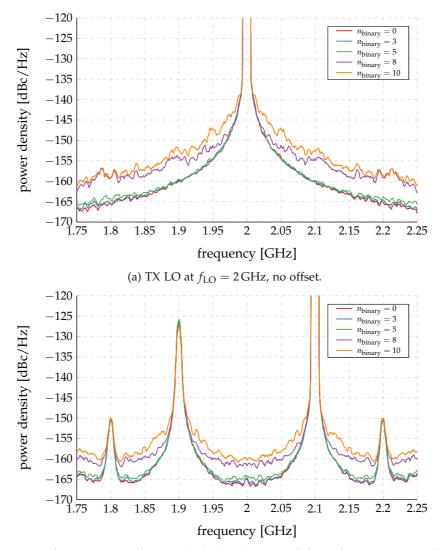

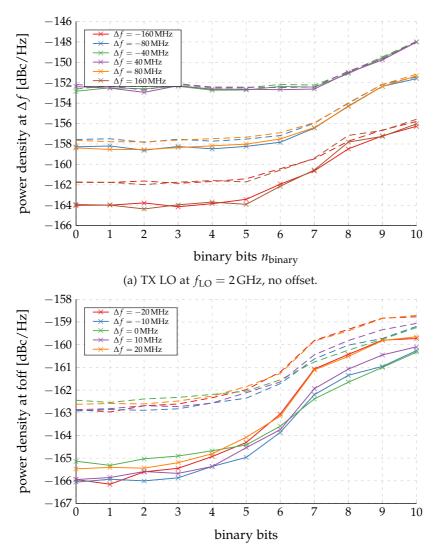

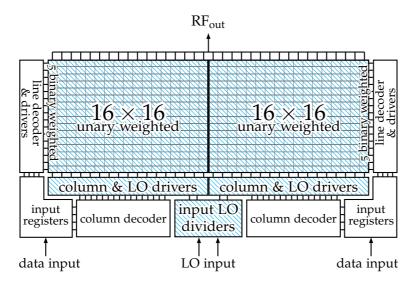

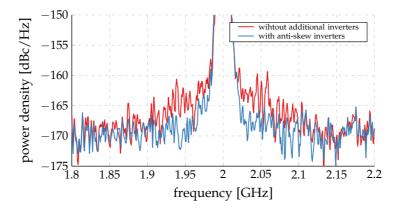

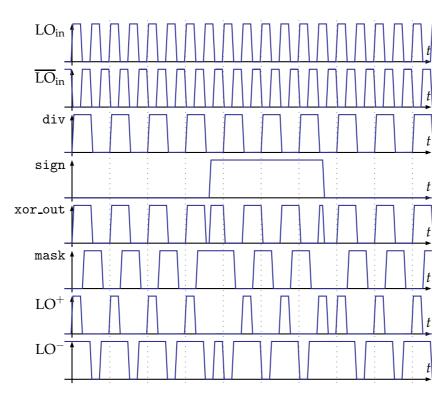

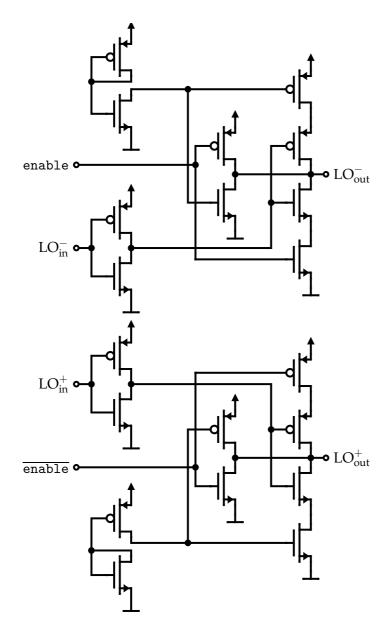

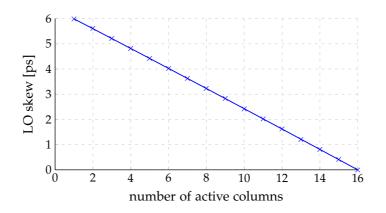

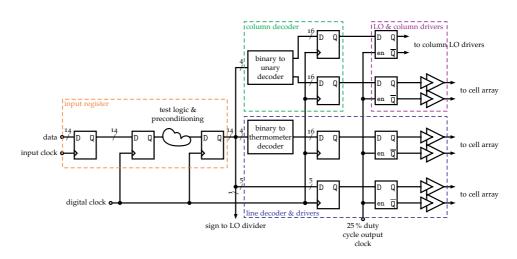

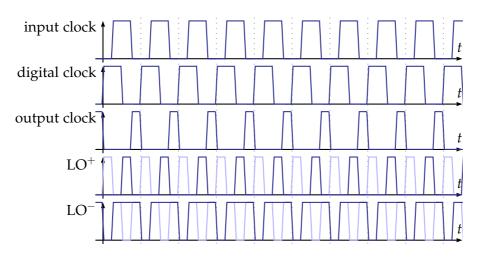

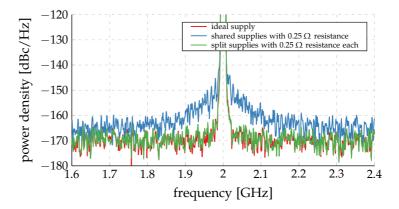

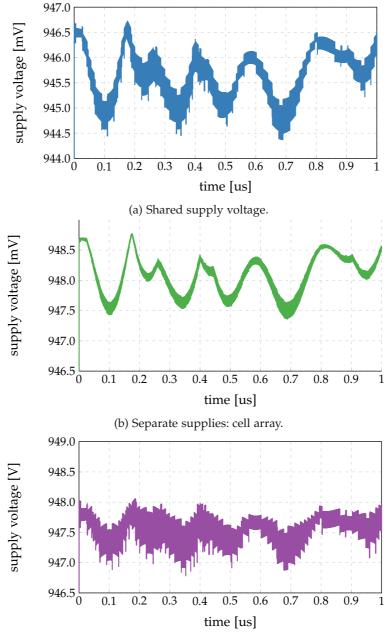

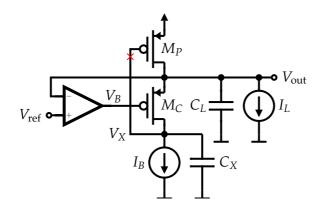

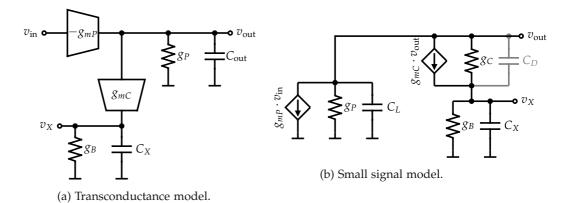

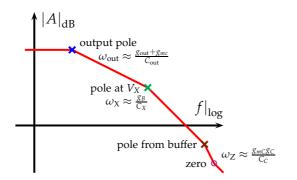

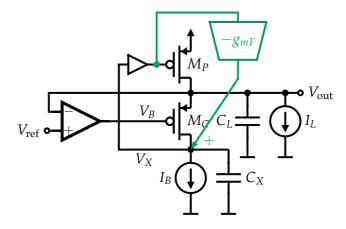

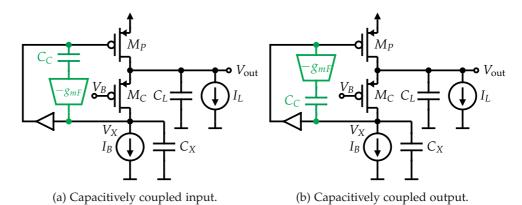

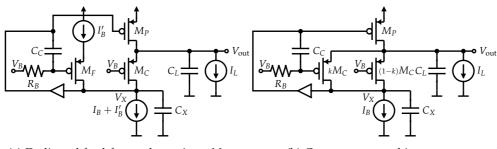

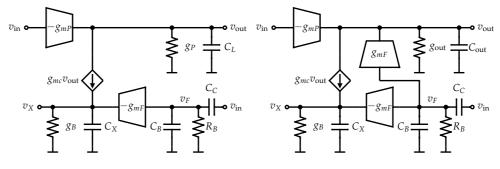

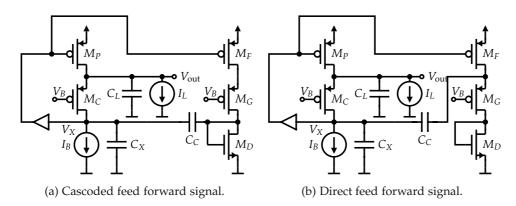

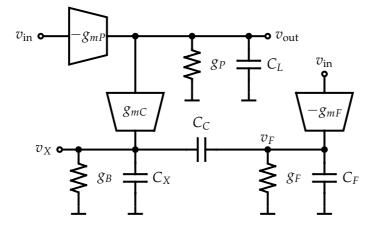

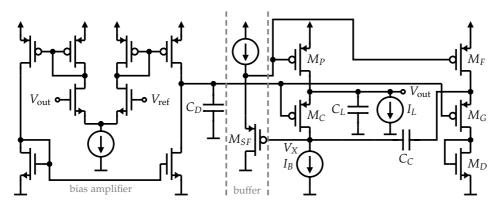

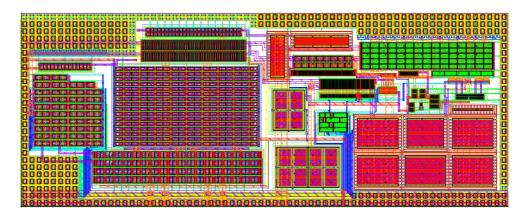

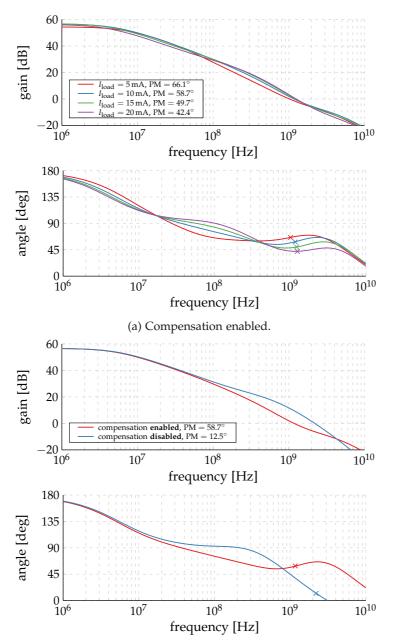

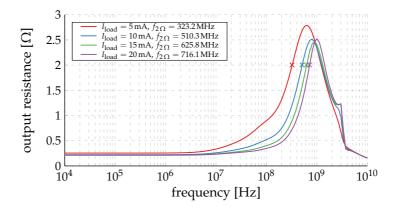

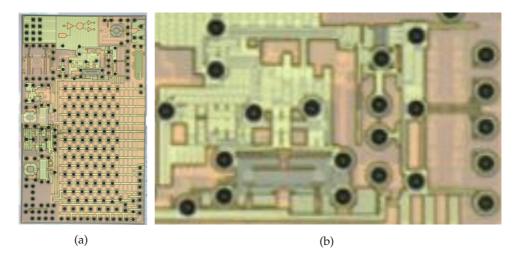

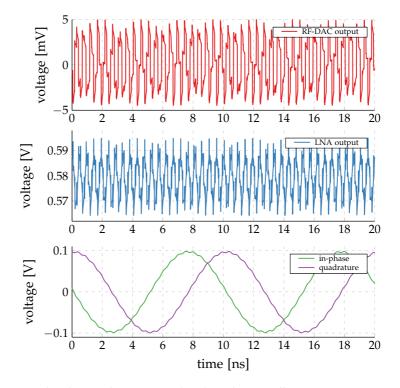

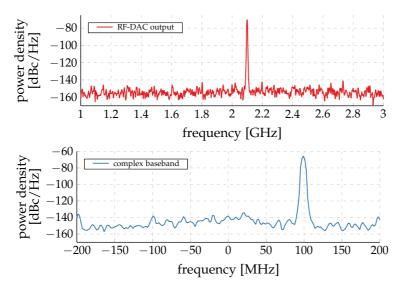

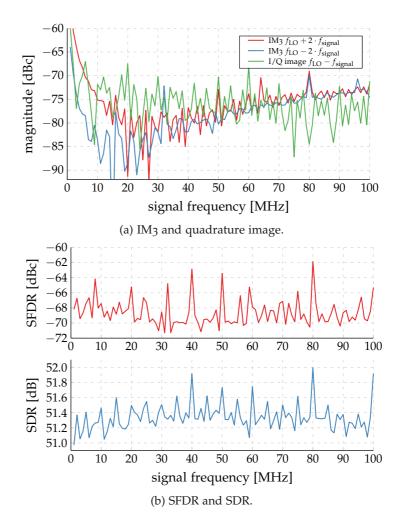

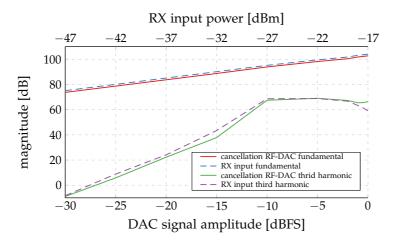

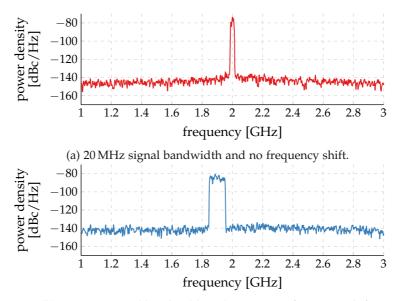

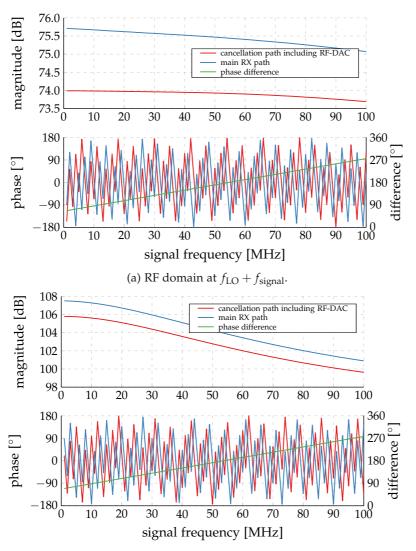

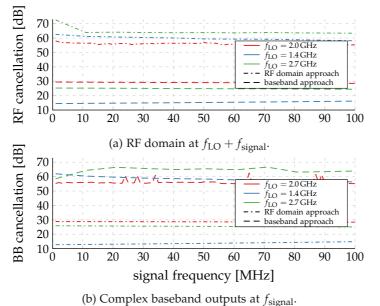

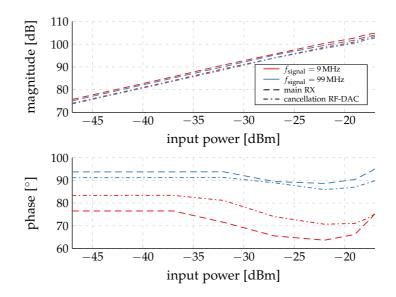

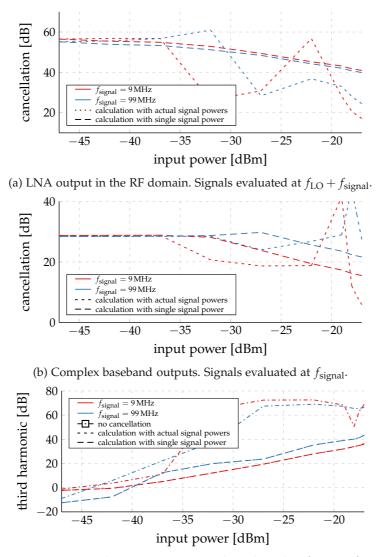

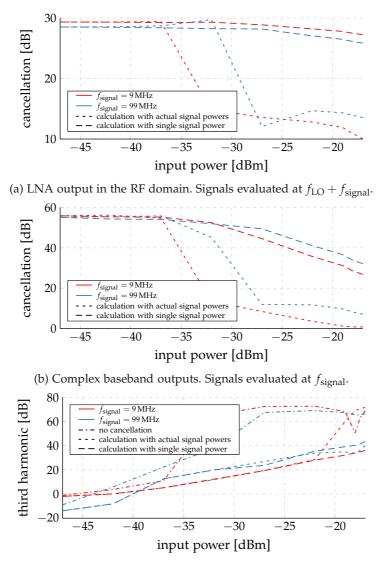

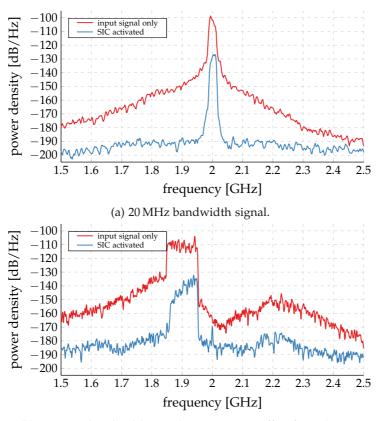

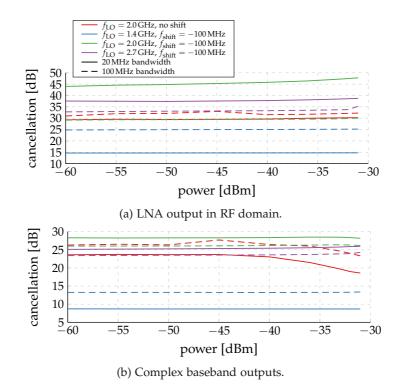

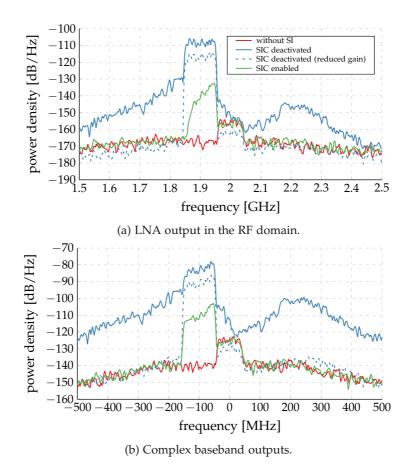

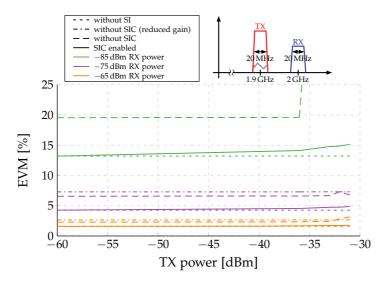

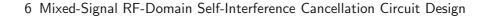

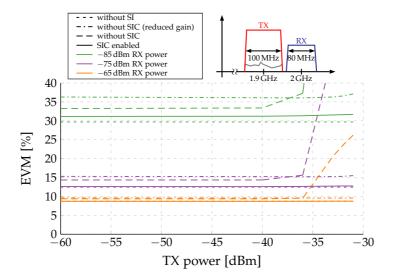

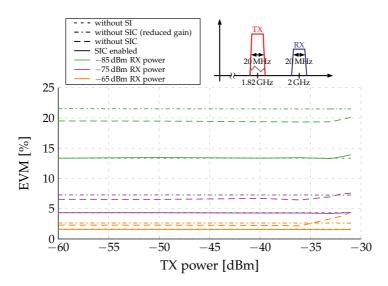

Waheed *et al.* approach this issue for the case in which both TX signals have their own PAs additionally introducing different nonlinearities on the two uplink signals [32]. In simulations, for a frequency-flat duplexer, the authors