DI Varvara Bezhenova

### X-Ray Radiation Effects on CMOS Integrated Circuits and Radiation Hradening

#### **DOCTORAL THESIS**

to achieve the university degree of

Doktorin der technischen Wissenschaften

submitted to

#### **Graz University of Technology**

Supervisor

Uni.-Prof. Dipl.-Ing. Dr. techn. Bernd Deutschmann

Institute of Electronics

Co-Supervisor: Dr. Alicja Michalowska-Forsyth

#### AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present doctoral thesis.

02.07.19

Date

16 Ares Signature

"... Getting an education was a bit like a communicable sexual disease. It made you unsuitable for a lot of jobs and then you had the urge to pass it on. ..."

—Terry Pratchett, "Hogfather"

#### GRAZ UNIVERSITY OF TECHNOLOGY

Faculty of Electrical and Information Engineering Institute of Electronics

> Doctor of Science by Varvara Bezhenova

This thesis summarizes my work in the frame of a research project, intending development of radiation hard integrated circuit design guidelines for next generation computed tomography. Under the influence of ionizing radiation integrated circuits degrade their parameters. To ensure reliable operation, the effects of ionizing radiation on electronics must be understood, and mitigation techniques and testing methods developed.

Within this work I investigate effects of X-ray radiation, typically used in computed tomography imaging, on susceptible semiconductor devices: diodes and MOS transistors. For this investigation I have designed two test chips, including standard and custom layout devices and circuit blocks, covering variety of parameters. The studied parameters included in particular different size, doping, layout and gate oxide thickness of different types of MOS transistors as well as area and perimeter of different types of diodes. The effects of X-ray radiation were studied in dependence on these parameters, leading to development of radiation hardening methodology.

One of the important steps in radiation hardened circuit design is circuit simulation. In this thesis my novel model for radiation hardened transistor simulation is presented and evaluated. Also, methodology for circuit radiation effects simulation is presented. This methodology allows not only to anticipate effect radiation will have on the circuit behaviour, but to track origins of radiation effects on the circuit level to the device level.

Although many standard guidelines for radiation effects testing exist, all of them require many engineering decisions for best testing procedure for a particular application. Within this work methodology for radiation effects testing at the circuit development stage is proposed, including electrical characterization and parameters extraction methodology, together with X-ray irradiation procedure. Finally, comparison of test results from different X-ray sources and facilities, according to the proposed results unification methodology, is presented.

Altogether, this work provides comprehensive study on X-ray effects on integrated circuits, methods for their mitigation, and procedures for radiation effects testing in research and development stage.

### Acknowledgements

It is always difficult to express the gratitude one feels for all the support on the long and sometimes difficult path towards PhD. On this way, there are many people contributing to the final success, one way or another - inspiring, guiding, setting an example, or just being there for you. So I can only try to mention all the people who have made me the researcher I am now.

First of all, I would like to mention my supervisor Prof. Bernd Deutschmann, whose guidance was indispensable. I would also like to express my gratitude to my project leader and scientific advisor Dr. Alicja Michalowska-Forsyth, for the expertise she has shared with me, and for setting an inspiring example of a driven scientist. My special thanks go also to my mentor Prof. Wolfgang Boesch: although we were not constantly in touch, I have always felt I have a shoulder to lean on in the academia routine.

I am appreciative towards my colleagues from the Institute of Electronics, for fruitful scientific (and not only) discussions and technical support, when it was needed. In this context I am also indebted to Patrick Schrey, for all the LaTex and Matlab help, but also for sharing the burdens of PhD life together.

I'd like to mention students and workshop colleagues, who have been a helping hand during my experiments - I wouldn't manage to gather so much data without help of Tim Reisenhofer, Stephan Fink, Eduard Dorner, Daniel Eisenkoelbl, Nikolaus Czepl, Birgit Schlager and Dominic Zupan.

For sharing their network, infrastructure and expertise, I am also much obliged to the Institute of Solid-State Physics, Institute of Biomedical Engineering and Institute of Electronic Sensor Systems. At this point I would also like to acknowledge MedAustron Non-Clinical Department Research, for providing access to the research facilities and equipment, and to thank Seibersdorf Laboratories for (sometimes heated) discussions on radiation effects and dosimetry.

I am grateful to Graz University of Technology, for excellent in-house training opportunities. My acknowledgement goes also to the PhD Union and Doctoral School of Information and Communication Engineering, for continuous effort in improvement of doctoral studies.

I cannot but mention my industry collaborators from ams AG: Thomas Mueller, Kund Mollnar, Walter Pflanzl, Jerzy Kudlaty and especially Massimiliano De Gaspari. They have motivated me in my research, gave valuable insights into industry work flow and praxis relevant approach to scientific questions, for which I am thankful. I want to thank my network from Karriereprogramm 2017, some of whom have become dear friends, for support and understanding, lightning the weight of little and not so little troubles of academic life from my heart.

For the last motivational boost I owe Robert Anderson: his teaching has brightened up my (at that point already very long) waiting for this manuscript review, and inspired to carry on even when you feel down. He taught me to listen. And listening makes your life a whole lot easier, especially when you have to deal with feedback.

Last but not least, I want to express my gratitude to my family and friends: to my parents Elena and Sergey, for inspiring me to go into science and for their unconditional love; to all my friends, especially to Sonia, who has never doubted me, even when I have doubted myself; to my boyfriend and partner Michael, for putting up with me through good and bad times, giving me the strength to come where I stand now.

With this I apologize to all of those I have failed to mention by name. I could continue this list much longer, but I need to give the reader a chance to actually find out what these years of research, you all have supported me through, were about.

### Contents

| Ał           | stract                                                                                               | vii  |

|--------------|------------------------------------------------------------------------------------------------------|------|

| Ac           | knowledgements                                                                                       | ix   |

| Co           | ntents                                                                                               | xi   |

| Lis          | t of Figures                                                                                         | xiii |

| Lis          | t of Tables                                                                                          | xix  |

| Ał           | breviations                                                                                          | xxi  |

| $\mathbf{M}$ | otivation and Scope                                                                                  | 1    |

|              | 1 Basics:                                                                                            |      |

|              | Ionizing radiation and its effects on electronic devices                                             | 1    |

|              | New generation of computed tomography                                                                | 4    |

|              | 3 Scope of the thesis                                                                                | 5    |

|              | 4 Structure of the thesis                                                                            | 7    |

| Ι            | X-Ray Effects and their Mitigation                                                                   | 9    |

|              | Introduction                                                                                         | 9    |

|              | 1 Transient effects                                                                                  | 10   |

|              | 2 Total Ionizing Dose Effects                                                                        | 12   |

|              | 2.1 Diodes $\ldots$ | 15   |

|              | 2.2 MOS Transistors                                                                                  | 19   |

|              | 2.2.1 DC parameters                                                                                  | 20   |

|              | Size Dependence                                                                                      | 20   |

|              | Doping Dependence                                                                                    | 23   |

|              | Layout Dependence                                                                                    | 26   |

|              | Standard and Enclosed Layouts                                                                        |      |

|              | Gate Extension Area Dependence                                                                       | 27   |

|              | 2.2.2 Flicker noise                                                                                  | 30   |

|              | 3 Radiation Hardening by Design                                                                      | 33   |

|              | Conclusion                                                                                           | 39   |

| II           | Radiation Hardening Implementation Methodology                                                       | 41   |

|              | Intro | oduction . |                                                     | •   | • |     |   |     |   |   |     | 41 |

|--------------|-------|------------|-----------------------------------------------------|-----|---|-----|---|-----|---|---|-----|----|

|              | 1     | Modellin   | g of Enclosed Layout Transistor                     | •   | • |     |   |     |   |   |     | 42 |

|              |       | 1.1 R      | linged source models                                | •   | • |     |   |     |   |   |     | 42 |

|              |       | 1.2 A      | nnular gate models                                  | •   |   |     |   |     |   |   |     | 45 |

|              | 2     | Modellin   | g of Circuit Radiation Effects                      | •   | • |     |   |     |   |   |     | 54 |

|              |       | 2.1 In     | nverter case study                                  | •   | • |     |   |     |   |   |     | 56 |

|              |       | 2.2 E      | andgap voltage reference case study                 | •   |   |     |   |     |   |   |     | 60 |

|              | Cone  | clusion .  |                                                     | •   | • |     | • |     | • | • | •   | 64 |

| II           |       |            | ond Standards                                       |     |   |     |   |     |   |   |     | 65 |

|              | Intro |            |                                                     |     |   |     |   |     |   |   |     | 67 |

|              | 1     | Paramet    | ers Measurement and Extraction                      | • • | • |     | • |     |   | • | •   | 67 |

|              |       |            | est-structures development                          |     |   |     |   |     |   |   |     | 67 |

|              |       | 1.2 P      | arameters extraction techniques                     | •   | • |     | • |     | • | • | •   | 70 |

|              |       |            | The constant current method                         | • • | • |     | • |     |   | • | •   | 71 |

|              |       |            | The transconductance derivative method .            | • • | • |     | • |     |   | • | •   | 73 |

|              |       |            | The linear extrapolation method $\ldots$ .          | •   | • |     | • |     |   | • | •   | 74 |

|              |       |            |                                                     |     |   |     |   |     |   |   |     | 76 |

|              | 2     | e          | sting and Dosimetry                                 | • • | • |     | • |     |   | • | •   | 80 |

|              |       | 2.1 II     | rradiation source and irradiation facility choice . | • • | • |     | • |     |   | • | •   | 81 |

|              |       | 2.2 D      | Dosimetry                                           | •   | • |     | • |     |   | • | •   | 82 |

|              |       | 2.3 II     | radiation facilities comparison                     | •   | • |     | • |     | • | • | •   | 83 |

|              | Cone  | clusion .  |                                                     | •   | • |     | • |     |   | • | •   | 85 |

| Co           |       |            | d Outlook                                           |     |   |     |   |     |   |   |     | 87 |

|              |       |            | lings and Contributions                             |     |   |     |   |     |   |   |     | 87 |

|              | Outl  | ook: indu  | is<br>trial implementation and further research     | •   | • | · • | • | • • | • | • | •   | 90 |

| $\mathbf{A}$ | Exp   | eriment    | al details                                          |     |   |     |   |     |   |   | ļ   | 91 |

|              | 1     | Experim    | ental structures                                    |     | • |     |   |     |   |   |     | 91 |

|              | 2     | Electrica  | l characterization                                  |     | • |     |   |     |   |   |     | 97 |

|              | 3     | Irradiati  | on experiments                                      | ••• | • |     | • | • • |   | • | . 1 | 01 |

| в            | Nois  | se Meası   | irements                                            |     |   |     |   |     |   |   | 1   | 07 |

|              |       |            |                                                     |     |   |     |   |     |   |   |     |    |

Bibliography

109

# List of Figures

| 1    | Different types of ionizing radiation and their placement within energy                                                                                                                                                                                                                                                                                      |          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | spectrum.                                                                                                                                                                                                                                                                                                                                                    | 2        |

| 2    | Illustration of single energetic charged particle striking an NMOS transistor leading to single event effect (SEE)                                                                                                                                                                                                                                           | 2        |

| 3    | Illustration of charge trapping in gate oxide of a Silicon-based NMOS transistor under constant exposure to X-rays, leading to total ionizing dose (TID) effect.                                                                                                                                                                                             | 3        |

| 4    | Illustration of incident particle hitting crystal lattice of semiconductor material leading to displacement damage (DD).                                                                                                                                                                                                                                     | 3        |

| 5    | Illustration of commercial p-substrate CMOS process. Cross-section of an NMOS and a PMOS transistors                                                                                                                                                                                                                                                         | 5        |

| I.1  | Average (points), and minimal and maximal (bars) $10 \times 10 \mu$ m diode pho-                                                                                                                                                                                                                                                                             |          |

|      | to<br>current as a function of X-ray tube current (A) and voltage<br>(B)                                                                                                                                                                                                                                                                                     | 11       |

| I.2  | Qualitative sketch of the energy spectrum of Tungsten target X-ray source                                                                                                                                                                                                                                                                                    |          |

| I.3  | (Logarithmic Y-scale)                                                                                                                                                                                                                                                                                                                                        | 11       |

| 1.0  | tocurrent as a function of X-ray tube current (A) and voltage (B) before irradiation (blue) and after TID of 1 Mrad (magenta). $\dots \dots \dots \dots$                                                                                                                                                                                                     | 13       |

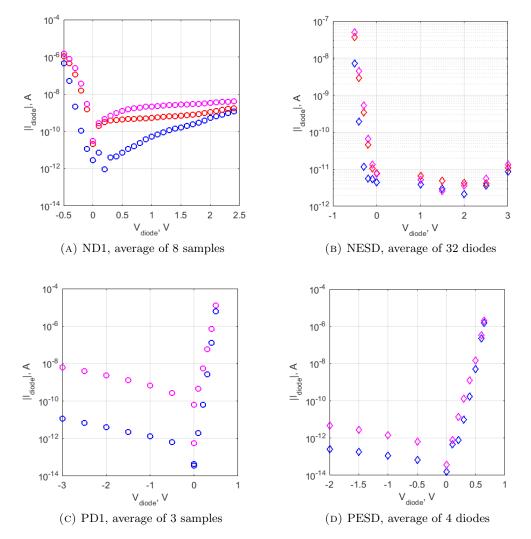

| I.4  | Average measured I-V characteristics of the $N+$ in Substrate (a, b) and $P+$ in N-Well (c, d) diode arrays (a, c) and ESD diodes (b, d) before                                                                                                                                                                                                              | 10       |

|      | irradiation and after 300 krad (a, b, c, d) and 1 Mrad (a, b) TID                                                                                                                                                                                                                                                                                            | 16       |

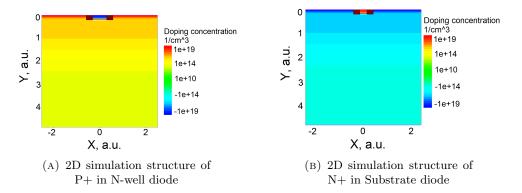

| I.5  | TCAD Sentaurus 2D simulation structures of P+ in N-well and N+ in                                                                                                                                                                                                                                                                                            |          |

| IC   | Substrate diodes                                                                                                                                                                                                                                                                                                                                             | 17       |

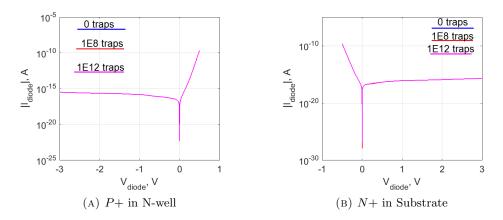

| I.6  | Simulated diode I-V characteristics before and after introduction of dif-<br>ferent number of oxide traps                                                                                                                                                                                                                                                    | 18       |

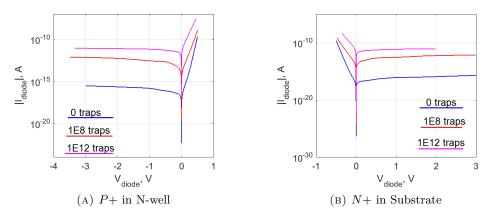

| I.7  | Simulated diode I-V characteristics before and after introduction of dif-                                                                                                                                                                                                                                                                                    | 18       |

| I.8  | *                                                                                                                                                                                                                                                                                                                                                            | 10       |

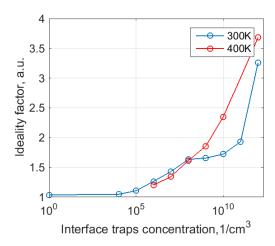

| -    | face traps concentration at 300 K (blue) and 400 K (red)                                                                                                                                                                                                                                                                                                     | 19       |

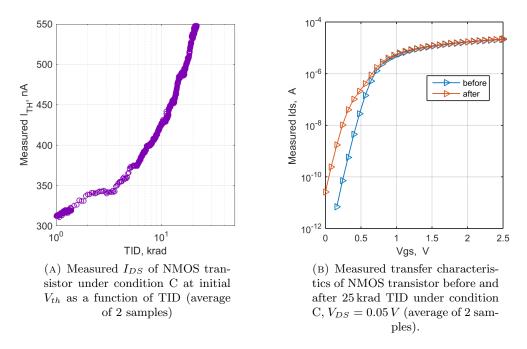

| I.9  | NMOS transistor characteristics change with increasing TID. $\ldots$ .                                                                                                                                                                                                                                                                                       | 20       |

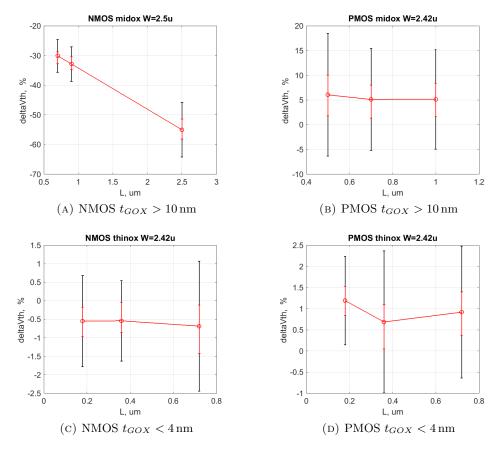

| I.10 | Relative threshold voltage shift $\Delta V_{th}$ of the medium oxide (A-B) and<br>thin oxide (C-D) NMOS (A, C) and PMOS (B, D) transistors after<br>TID=300 krad as a function of channel length: average (red line), min-<br>max bar (red bar) and $3\sigma$ bar (black bar) data of 20 samples irradiated                                                  |          |

|      | under worst case condition.                                                                                                                                                                                                                                                                                                                                  | 21       |

|      | NMOS transistor characteristics change with increasing TID Relative threshold voltage shift $\Delta V_{th}$ of the medium oxide (A-B) and thin oxide (C-D) NMOS (A, C) and PMOS (B, D) transistors after TID=300 krad as a function of channel length: average (red line), min-max bar (red bar) and $3\sigma$ bar (black bar) data of 20 samples irradiated | 19<br>20 |

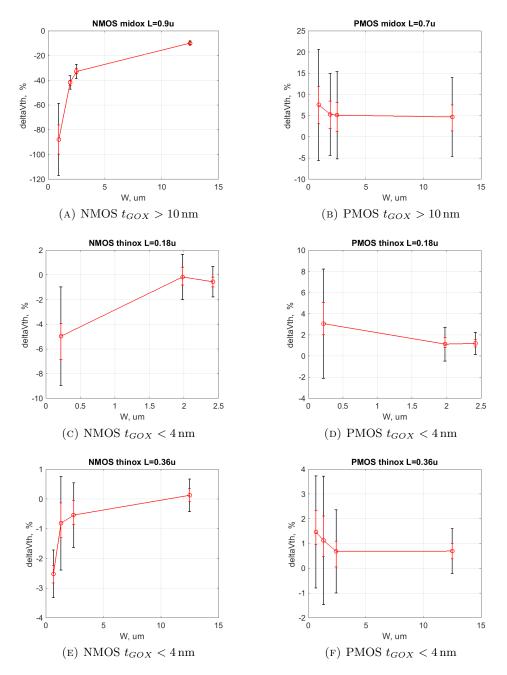

| I.11         | Relative threshold voltage shift $\delta V_{th}$ of the medium oxide (A-B) and thin<br>oxide (C-F) NMOS (A, C, E) and PMOS (B, D, F) transistors after<br>TID=300 krad as a function of channel width: average (red line), min-<br>max bar (red bar) and $3\sigma$ bar (black bar) data of 20 samples irradiated | 20           |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| I.12         | under worst case condition                                                                                                                                                                                                                                                                                       | . 22<br>. 23 |

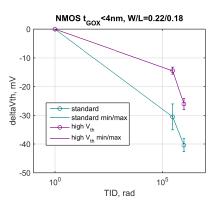

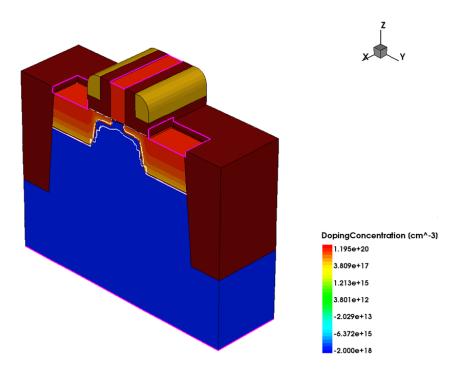

| I.13         | Relative threshold voltage shift as a function of TID of NMOS (A, B) and PMOS (C, D) transistors with $t_{GOX} < 4 \text{ nm}$ with standard (A, C)                                                                                                                                                              |              |

|              | and high (B, D) threshold voltage                                                                                                                                                                                                                                                                                | . 24         |

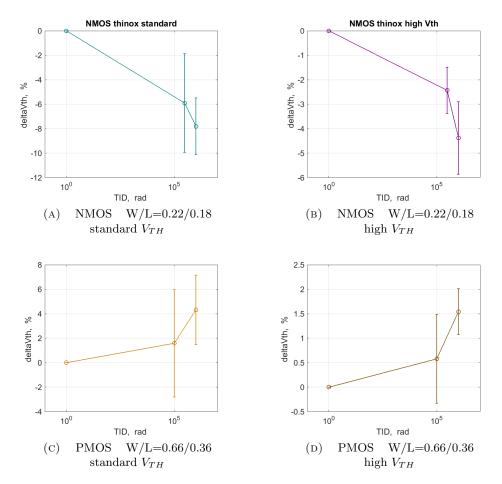

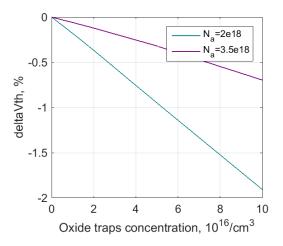

| I.14<br>I.15 | 3D model of an NMOS transistor in TCAD simulation                                                                                                                                                                                                                                                                | . 25         |

| I.16         | tration                                                                                                                                                                                                                                                                                                          | . 25         |

| I.17         |                                                                                                                                                                                                                                                                                                                  | . 26         |

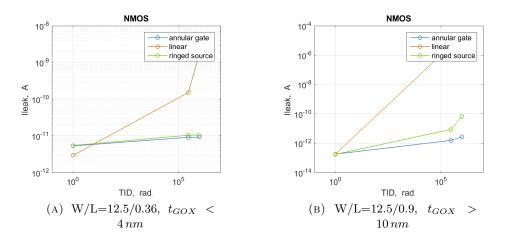

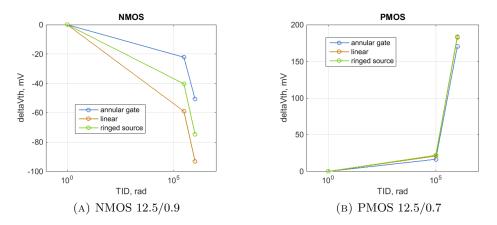

|              | in standard linear (brown), ringed source (green) and annular gate (blue) layout as a function of TID                                                                                                                                                                                                            | . 27         |

| I.18         | Threshold voltage shift of linear layout and ELT NMOS (A) and PMOS (B) transistors with $t_{GOX} > 10 \text{ nm}$ . Average of 8 samples.                                                                                                                                                                        | . 27         |

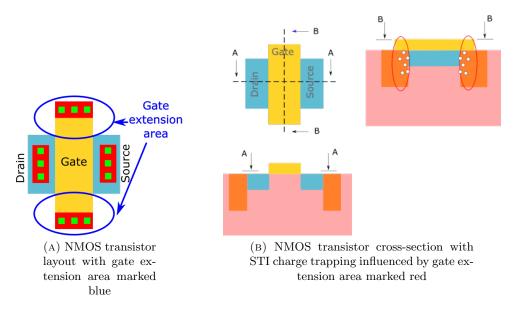

| I.19         | Illustration of gate extension area and its effect on charge trapping in                                                                                                                                                                                                                                         | . 21         |

|              | the underlying STI as layout (A) and as a simplified cross-section of an NMOS transistor in a commercial CMOS process.                                                                                                                                                                                           | . 28         |

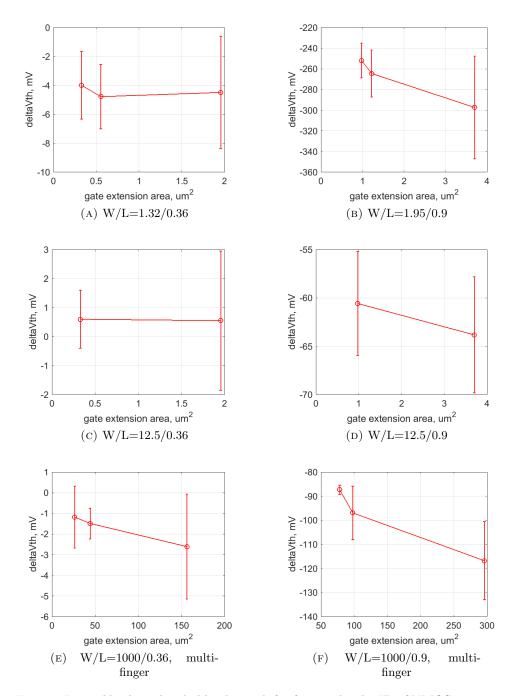

| I.20         | Absolute threshold voltage shift after 300 krad TID of NMOS transistors with $t_{GOX} < 4 \text{ nm}$ (A, C, E) and $t_{GOX} > 10 \text{ nm}$ (B, D, F). Average (lines),                                                                                                                                        | 20           |

| I.21         | and minimal and maximal (bars) of 8 samples                                                                                                                                                                                                                                                                      | . 29         |

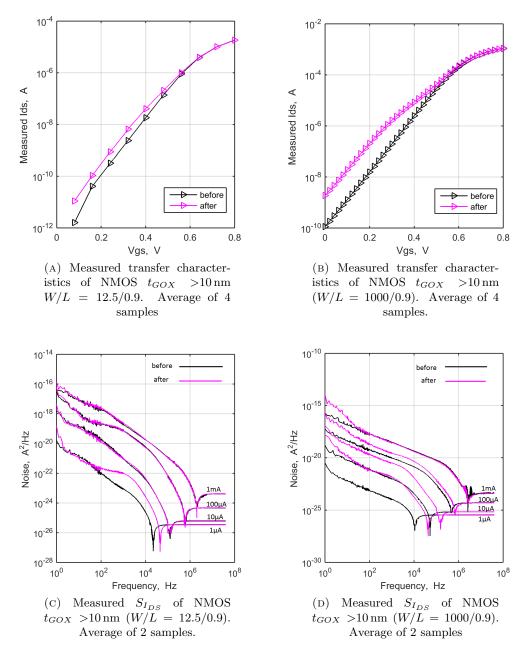

|              | case irradiation bias (condition B, average of 2 samples). $\ldots$                                                                                                                                                                                                                                              | . 31         |

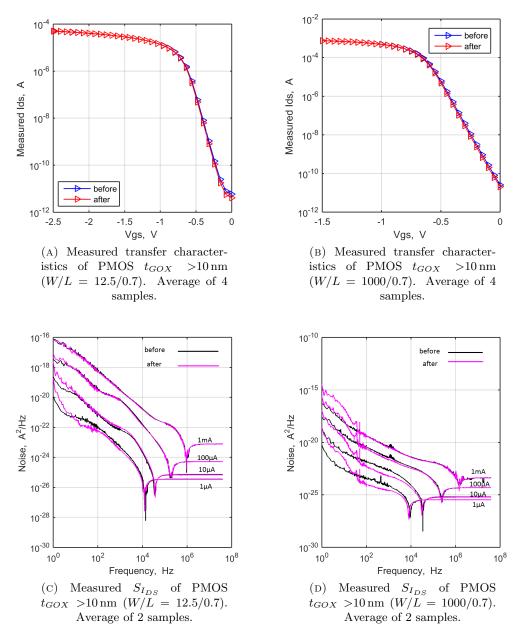

| I.22         | Measured transfer characteristics (A, B) and noise $S_{I_{DS}}$ (C, D) of PMOS transistors before and after 15 krad TID                                                                                                                                                                                          |              |

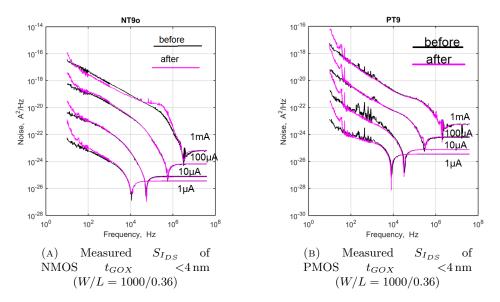

| I.23         | Measured noise $S_{I_{DS}}$ of $t_{GOX} < 4 \text{ nm}$ ( $W/L = 1000/0.36$ ) NMOS (A) and PMOS (B) before (black) and after (magenta) 15 krad TID. Average of 2                                                                                                                                                 |              |

|              | samples                                                                                                                                                                                                                                                                                                          | . 33         |

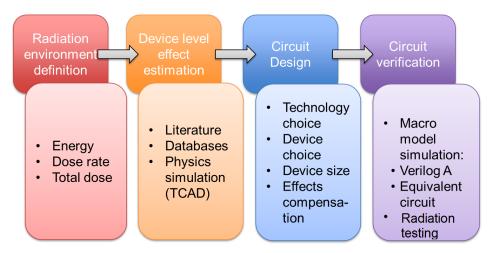

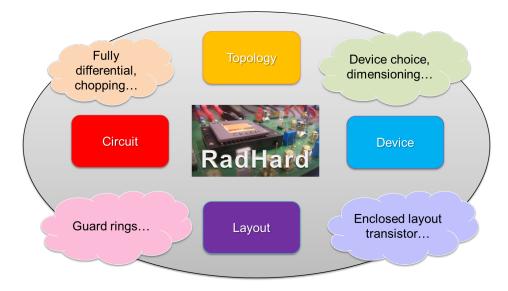

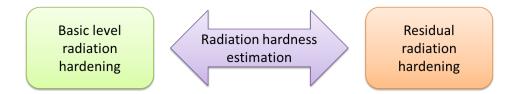

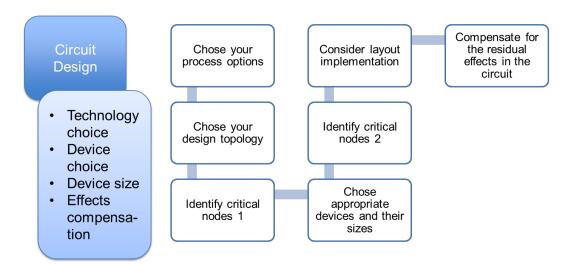

| I.24         | Radiation aware IC development flow.                                                                                                                                                                                                                                                                             | . 34         |

| I.25         | Possible approaches to radiation hardening                                                                                                                                                                                                                                                                       |              |

| I.26         | Three phases of radiation hardened design                                                                                                                                                                                                                                                                        |              |

| I.27         | Radiation aware circuit design flow                                                                                                                                                                                                                                                                              | . 36         |

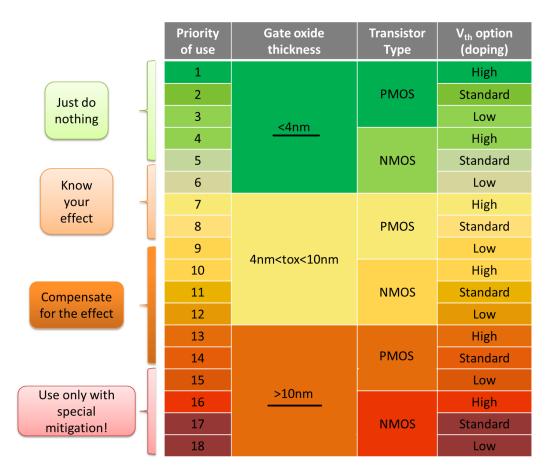

| I.28         | Priority of devices and device options use for radiation hard design valid<br>up to 1 Mrad TID                                                                                                                                                                                                                   | . 37         |

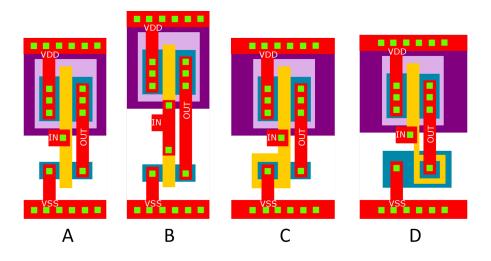

| I.29         | Illustration of CMOS inverter layout: standard (A), with decreased gate                                                                                                                                                                                                                                          | . 37         |

|              | extension area (B), with ringed source NMOS (C), and with annular gate NMOS (D)                                                                                                                                                                                                                                  | . 39         |

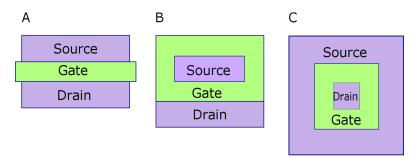

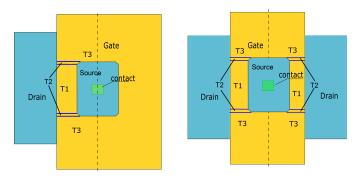

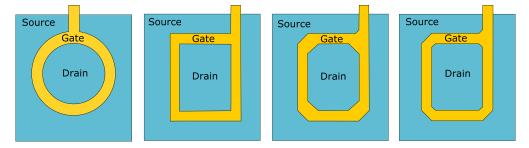

| II.1         | Possible realizations of ringed source layout                                                                                                                                                                                                                                                                    | . 43         |

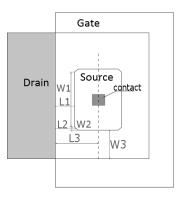

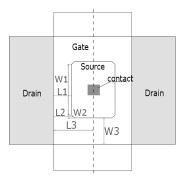

| II.2         | Geometrical model of single drain ringed source transistor                                                                                                                                                                                                                                                       |              |

| II.3         | Geometrical model of double-drain ringed source transistor                                                                                                                                                                                                                                                       | . 44         |

| II.4  | Different realizations of annular gate layout                                                                                                                                                                                                    | 45         |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

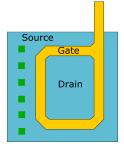

| II.5  | Area optimized annular gate transistor.                                                                                                                                                                                                          | 46         |

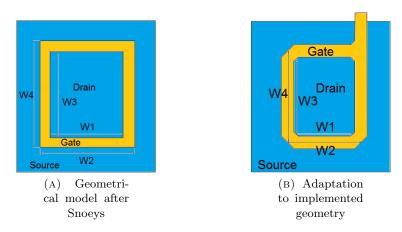

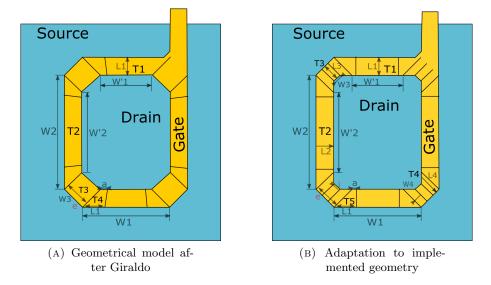

| II.6  | Geometrical model of annular gate transistor after Snoeys (A) and its adaptation to cut-corner geometry (B)                                                                                                                                      | 46         |

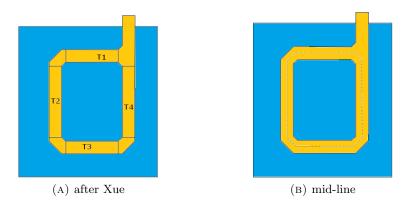

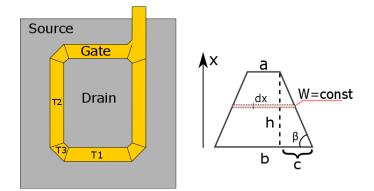

| II.7  | Geometrical model of annular gate transistor after Giraldo (A) and its<br>adaptation to realization with different inner and outer cut-corner di-                                                                                                |            |

| II.8  | mensions (B)                                                                                                                                                                                                                                     | 47<br>48   |

| II.9  | Isosceles trapezoid approximation for equivalent aspect ratio calculation<br>of an annular gate transistor.                                                                                                                                      | 49         |

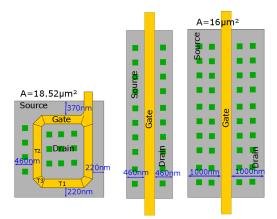

| TT 10 | Implemented test structures                                                                                                                                                                                                                      | 4 <i>5</i> |

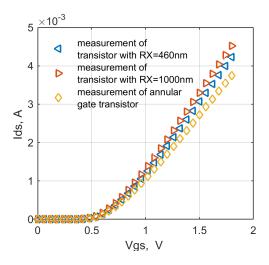

|       | Measured transfer characteristics of the two standard NMOS transistors                                                                                                                                                                           | 91         |

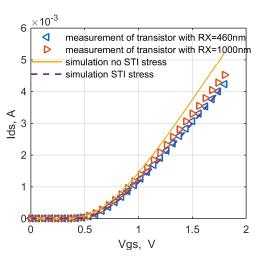

|       | with different RX and an annular gate transistor at $V_{ds} = 1.8 V \dots$                                                                                                                                                                       | 52         |

|       | 2 Measured transfer characteristics of the two standard NMOS transistors<br>with different RX and simulation with and without STI stress at $V_{ds} = 1.8 V$                                                                                     | 52         |

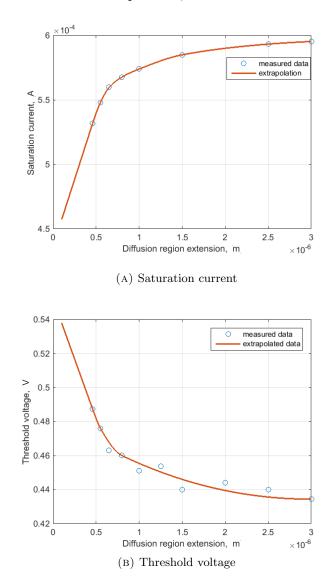

|       | Extrapolation of saturation current (A) and threshold voltage $V_{th}$ (B) as<br>a function of diffusion region extension RX                                                                                                                     | 53         |

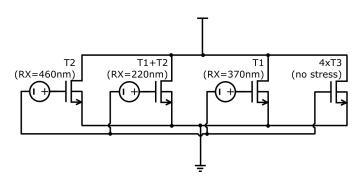

|       | Equivalent sub-circuit simulation model for STI stress simulation in an asymmetrical annular gate transistor                                                                                                                                     | 53         |

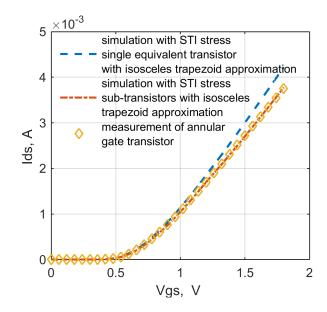

| II.15 | 6 Measured transfer characteristics of the annular gate transistor and sim-<br>ulation of the single equivalent standard transistor with STI stress and of<br>the sub circuit model with corresponding STI stress at $V_{\rm e} = 1.8 V_{\odot}$ | 54         |

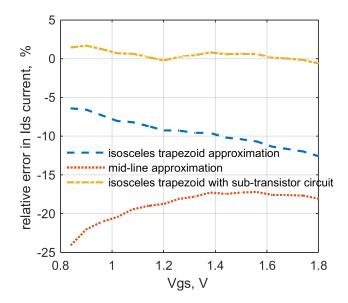

| II.16 | the sub-circuit model with corresponding STI stress at $V_{ds} = 1.8 V \dots$<br>Relative error of approximation models between simulated and measured                                                                                           |            |

| II.17 | transfer characteristics                                                                                                                                                                                                                         | 55         |

| TT 10 | PMOS (B) transistors                                                                                                                                                                                                                             | 55<br>56   |

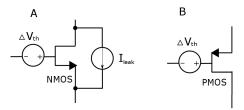

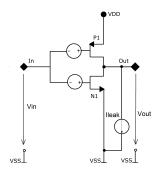

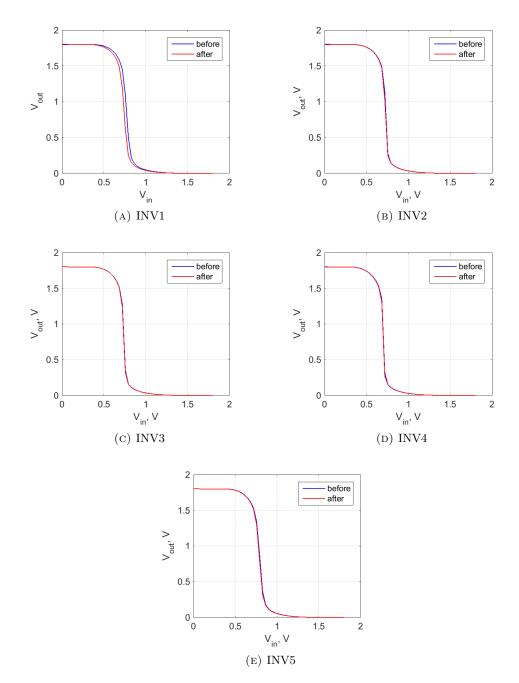

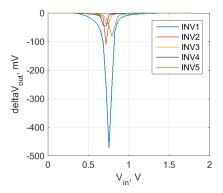

|       | Schematics of inverter macro-model incorporating TID effects                                                                                                                                                                                     | 56<br>57   |

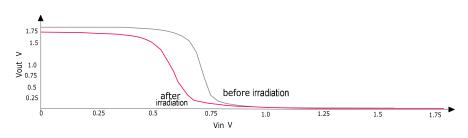

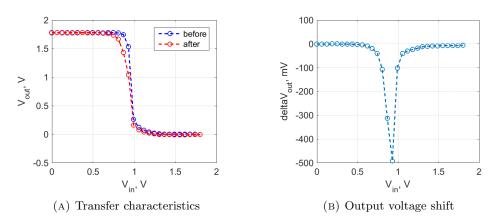

|       | TID effects on inverter transfer characteristics.                                                                                                                                                                                                | 57         |

| II.21 | fore and after irradiation according to the model depicted in Fig. II.18<br>Simulated inverter output voltage shift after irradiation for different di-                                                                                          | 58         |

| II.22 | mensions of inverters                                                                                                                                                                                                                            | 59         |

|       | output voltage shift after 300 krad TID of a standard inverter with PMOS $W/L=400/180$ and NMOS $W/L=350/180$ . Average of 8 samples                                                                                                             | 59         |

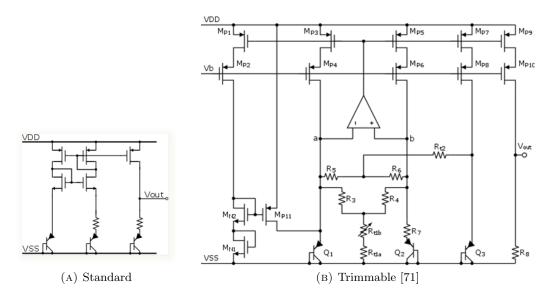

| II.23 | B Simplified schematics of standard (A) and radiation hardened trimmable (B) bandgap voltage references                                                                                                                                          | 60         |

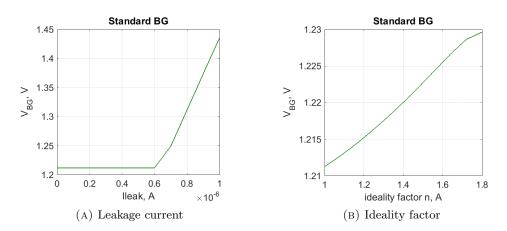

| II.24 | Simulated output voltage of the standard bandgap voltage reference as a function of TID dependent parameter: leakage current of NMOS transis-                                                                                                    |            |

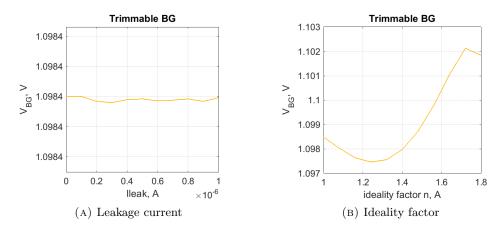

| II.25 | tors (A and ideality factor of diodes (B)                                                                                                                                                                                                        | 61         |

|       | as a function of TID dependent parameters: leakage current of NMOS transistors (A) and ideality factor of diodes (B).                                                                                                                            | 61         |

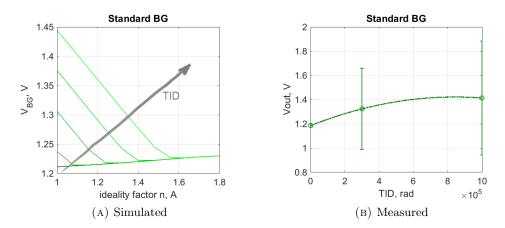

| II.26 | Output voltage of the standard bandgap voltage reference simulated with TID induced ideality factor and leakage current shifts (A) and measured                                                                                                  |            |

|       | average of 7 samples, with $3\sigma$ bars (B).                                                                                                                                                                                                   | 62         |

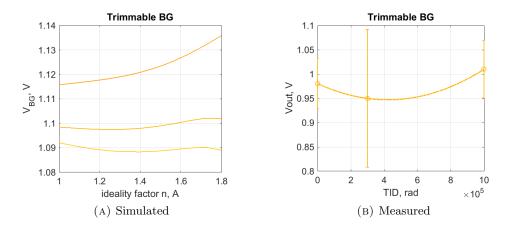

| II.27 Output voltage of the trimmable bandgap voltage reference simulated<br>with TID induced ideality factor and leakage current shifts at process<br>corners (A) and measured average of 7 samples (B)                                                                                                       | 3 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

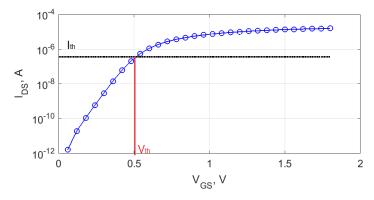

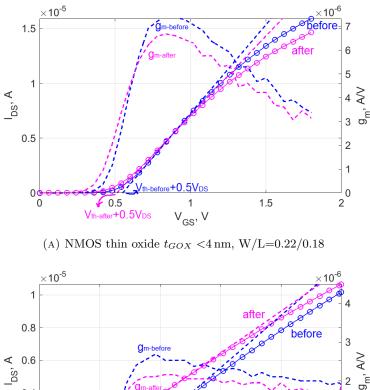

| III.1 Threshold voltage extraction methods on example of measured NMOS $(t_{GOX} < 4 \text{ nm} \text{ and } W/L=0.22/0.18)$ transfer characteristics in linear region $(V_{DS}=0.05 \text{ V})$ before irradiation                                                                                            | 1 |

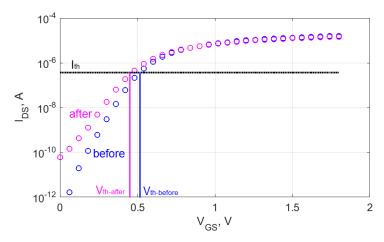

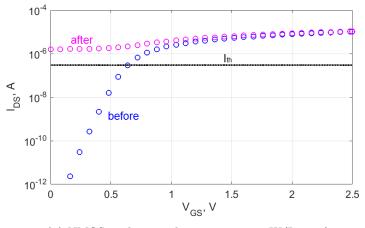

| III.2 Constant current method threshold voltage $(V_{th})$ extraction from measured transfer characteristics of thin $t_{GOX} < 4 \text{ nm}$ (A) and medium $t_{GOX} > 10 \text{ nm}$                                                                                                                         | n |

| (B) oxide NMOS transistors before (blue) and after (magenta) TID of $1 \operatorname{Mrad} V_{DS} = 50 \operatorname{mV}$ .                                                                                                                                                                                    | 2 |

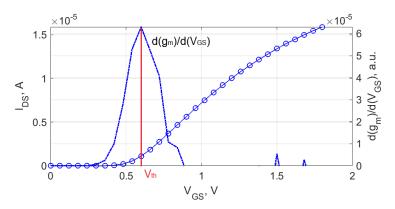

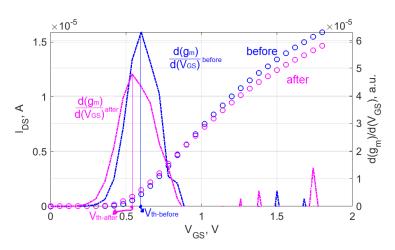

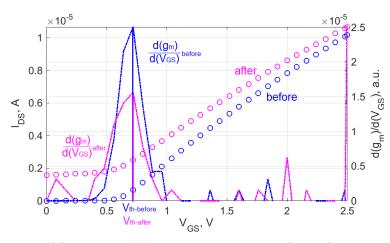

| III.3 Transconductance derivative method threshold voltage $(V_{th})$ extraction<br>from measured transfer characteristics of thin $t_{GOX} < 4 \text{ nm}$ (A) and medium<br>$t_{GOX} > 10 \text{ nm}$ (B) oxide NMOS transistors before (blue) and after (ma-<br>genta) TID of 1 Mrad $V_{DS}=50 \text{ mV}$ | 2 |

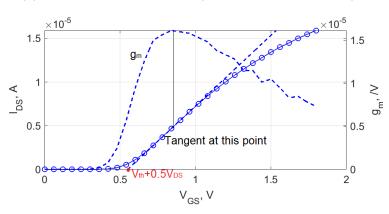

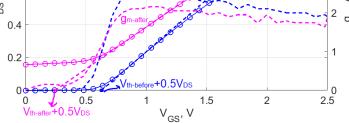

| III.4 Linear extrapolation method threshold voltage $(V_{th})$ extraction from measured transfer characteristics of thin $t_{GOX} < 4 \text{ nm}$ (A) and medium $t_{GOX} > 10 \text{ nm}$ (B) oxide NMOS transistors before (blue) and after (magenta) TID of                                                 |   |

| 1 Mrad $V_{DS}$ =50 mV                                                                                                                                                                                                                                                                                         | 1 |

| fer characteristics of NMOS transistor with $t_{GOX} > 10 \text{ nm}$ and W/L=2.5/2.5 before (blue) and after TID of 1 Mrad (magenta), $V_{DS} = 50 \text{ mV}$                                                                                                                                                | 5 |

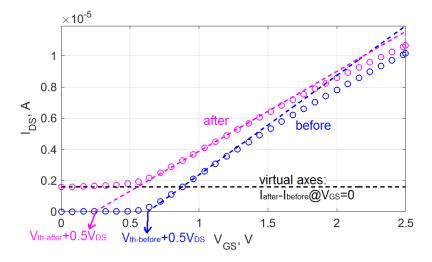

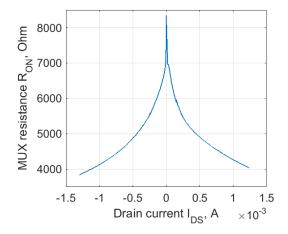

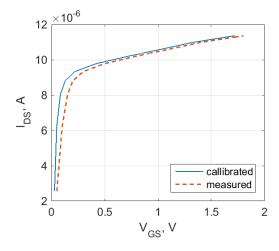

| III.6 $R_{ON}$ of MAX328CPE multiplexer as a function of drain current 77<br>III.7 Output characteristics of PMOS transistor with $t_{GOX} < 4 \text{ nm}$ (see Appendix A) measured with MAX328CPE multiplexer (in red) and cali-                                                                             | 7 |

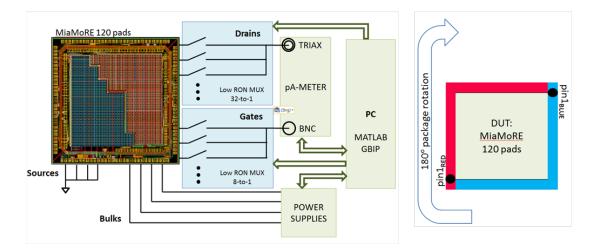

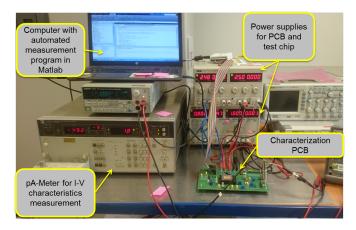

| brated with recalculation of $V_{DS}$ value by taking corresponding $R_{ON}$ value. 78<br>III.8 Block diagram of semi-automated electrical characterization system for                                                                                                                                         |   |

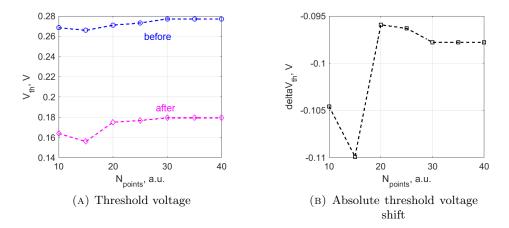

| MiAMoRE test chip (picture credit: Alicja Michalowska-Forsyth)                                                                                                                                                                                                                                                 | 3 |

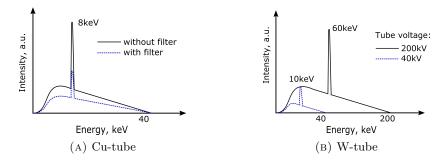

| measurement points $N_{points}$ by means of linear extrapolation at $V_{DS}=50$ mV. 79<br>III.10Scetch of Cu- (A) and W-tube (B) photon energy spectra with different                                                                                                                                          | 9 |

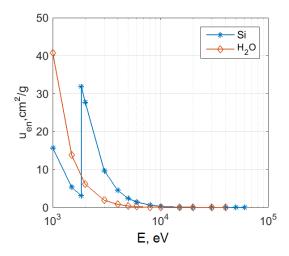

| experimental settings (marked in black solid and blue dashed lines) 80<br>III.11Mass-energy absorption coefficients of silicon and water                                                                                                                                                                       |   |

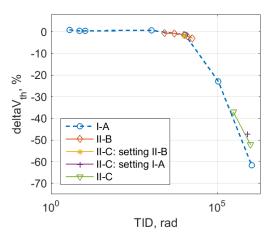

| with $t_{GOX} > 10 \text{ nm}$ and W/L=1.95/0.9 as a function of TID after irradi-<br>ation at different facilities and X-ray source settings                                                                                                                                                                  | 4 |

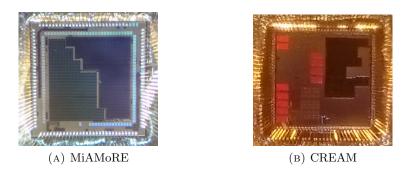

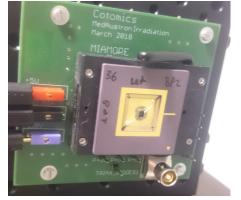

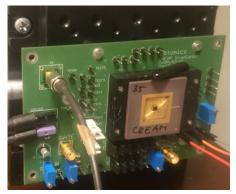

| A.1 Photographs of MiAMoRE (A) and CREAM (B) test chips                                                                                                                                                                                                                                                        |   |

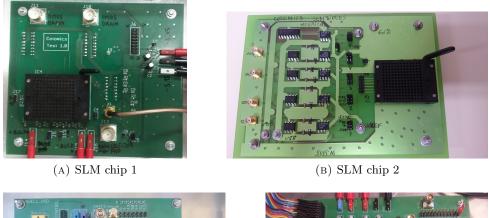

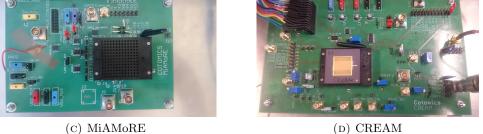

| <ul> <li>A.2 Measurement set-up for electrical characterization of DC parameters 98</li> <li>A.3 PCB for electrical characterization of test chips SLM chip 1(A), SLM chip 2(B), MiAMoRE (C) and CREAM (C)</li></ul>                                                                                           |   |

| A.4 Illustration of experimental setup and measured signal during the hospital experiment                                                                                                                                                                                                                      |   |

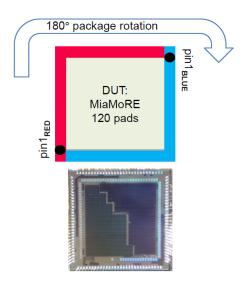

| A.5 Diagram of MiAMoRE chip rotation for test                                                                                                                                                                                                                                                                  |   |

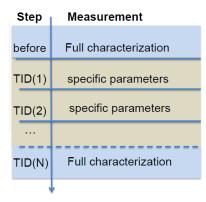

| A.6 Principal diagram of irradiation experiments flow                                                                                                                                                                                                                                                          |   |

| A.7 PCBs for electrical bias during irradiation                                                                                                                                                                                                                                                                |   |

|                                                                                                                                                                                                                                                                                                                |   |

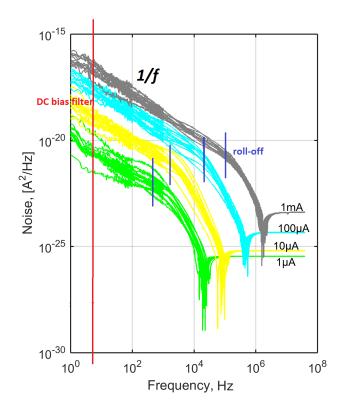

B.1 Measured drain current noise density  $S_{I_{DS}}$  of NMOS with  $t_{GOX} > 10 \text{ nm}$ over 13 dies (not irradiated). Blue markers indicate average roll-off frequency of the measurement system for the particular current setting  $\ldots$  108

# List of Tables

| 2     | Effects of ionizing radiation on semiconductor devices - summary                                | 4         |

|-------|-------------------------------------------------------------------------------------------------|-----------|

| I.1   | Experimental Structures                                                                         | 15        |

| I.2   | Measurement Results: saturation current                                                         | 16        |

| I.3   | Measurement results: ideality factor                                                            | 17        |

| I.4   | MOS transistor dimensioning for radiation hardness                                              | 38        |

| II.1  | Equivalent aspect ratio of ringed source transistors                                            | 45        |

| II.2  | Equivalent aspect ratio of annular gate transistors                                             | 49        |

| II.3  | Error of equivalent aspect ratio of annular gate transistors related to extracted $W/L$         | 49        |

| II.4  | Dimensions of simulated inverters                                                               | -13<br>57 |

| 11.4  |                                                                                                 | 51        |

| III.1 | Test structures implemented on the first custom-designed test chip with                         |           |

|       | corresponding parameter variations.                                                             | 68        |

|       | MOS transistor parameters variation matrix                                                      | 69        |

| III.3 | Threshold voltage shift of NMOS transistors with $t_{GOX} > 10 \text{ nm}$ and                  |           |

|       | W/L=12.5/0.9 after 1 Mrad TID extracted by means of conventional lin-                           |           |

|       | ear extrapolation $\Delta V_{th}$ and with the help of virtual X-axes $\Delta V_{th-virtual}$ . | =0        |

| TTT 4 | ·····                                                                                           | 76        |

|       | Threshold voltage extraction methods: results comparison                                        | 76        |

|       | Irradiation facility choice                                                                     | 81        |

|       | Dosimetry tools and methods                                                                     | 82        |

| 111.7 | Irradiation test plan for facilities comparison                                                 | 84        |

| A.1   | Test material - MiAMoRE                                                                         | 92        |

| A.2   | Test material - CREAM                                                                           | 96        |

| A.3   | Test material - SLM chips provided by foundry                                                   | 97        |

| A.4   | Irradiation experiments                                                                         | 102       |

| A.5   | Bias conditions during Experiment 1 - MiAMoRE test chip                                         | 103       |

| A.6   | Bias conditions during Experiment 2 - MiAMoRE test chip                                         | 104       |

| A.7   | Bias conditions during Experiment 3 - MiAMoRE test chip                                         | 104       |

| A.8   | Bias conditions during Experiment 4 - MiAMoRE test chip                                         | 104       |

| A.9   | Bias conditions during Experiment 4 - CREAM test chip                                           | 104       |

| A.10  | Beam settings and dose rates during Experiment 1 - MiAMoRE test chip                            | 105       |

| A.11  | Beam settings and dose rates during Experiment 2 - MiAMoRE test chip                            | 105       |

| A.12  | Beam settings and dose rates during Experiment 3 - MiAMoRE test chip                            | 105       |

| A.13  | Beam settings and dose rates during Experiment 4 - MiAMoRE test chip                            | 105       |

| A.14  | Beam settings and dose rates during Experiment 4 - CREAM test chip                              | 105       |

## Abbreviations

| BP                                             | Bonding Plan                                                                                                                                                          |  |  |  |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CMOS                                           | $\mathbf{C} omplementary\text{-}\mathbf{M} etal\text{-}\mathbf{O} xide\text{-}\mathbf{S} emiconductor$                                                                |  |  |  |

| CREAM                                          | Circuit Radiation Effects Analysis and Mitigation                                                                                                                     |  |  |  |

| СТ                                             | Computed Tomography                                                                                                                                                   |  |  |  |

| DC                                             | Direct Current                                                                                                                                                        |  |  |  |

| DD                                             | $\mathbf{D}$ isplacement $\mathbf{D}$ amage                                                                                                                           |  |  |  |

| ELT                                            | Enclosed Layout Transistor                                                                                                                                            |  |  |  |

| EMI                                            | $\mathbf{E}$ lectro- $\mathbf{M}$ agnetic Interference                                                                                                                |  |  |  |

| ESD                                            | Electro-Static Discharge                                                                                                                                              |  |  |  |

| FOXFET                                         | $\mathbf{F}$ ield $\mathbf{O}$ xide $\mathbf{F}$ ield $\mathbf{E}$ ffect $\mathbf{T}$ ransistor                                                                       |  |  |  |

| IC                                             | Integrated Circuit                                                                                                                                                    |  |  |  |

| LEO                                            | Lower Earth Orbit                                                                                                                                                     |  |  |  |

| MiAMoRE                                        | ${\bf Mi} tigation \ {\bf A} nalysis and \ {\bf Mo} delling \ of \ {\bf R} adiation \ {\bf E} ffects$                                                                 |  |  |  |

| $\mathbf{MOSFET} \ \mathrm{or} \ \mathbf{MOS}$ | $\mathbf{M} \mathrm{etal}~\mathbf{O} \mathrm{xode}~\mathbf{S} \mathrm{emiconductor}~\mathbf{F} \mathrm{ield}~\mathbf{E} \mathrm{ffect}~\mathbf{T} \mathrm{ransistor}$ |  |  |  |

| PCB                                            | Printed Circuit Board                                                                                                                                                 |  |  |  |

| RINCE                                          | $ {\bf R} {\rm adiation} \ {\bf Induced} \ {\bf N} {\rm arrow} \ {\bf Channel} \ {\bf E} {\rm ffect} $                                                                |  |  |  |

| RISCE                                          | $ {\bf R} {\rm adiation} \ {\bf Induced} \ {\bf S} {\rm hort} \ {\bf C} {\rm hannel} \ {\bf E} {\rm ffect} $                                                          |  |  |  |

| SEE                                            | Single Event Effect                                                                                                                                                   |  |  |  |

| SLM                                            | Scribe Line Monitor                                                                                                                                                   |  |  |  |

| STI                                            | $\mathbf{S}$ hallow $\mathbf{T}$ rench $\mathbf{I}$ solution                                                                                                          |  |  |  |

| TID                                            | Total Ionizing Dose                                                                                                                                                   |  |  |  |

### Motivation and Scope

"...It is well known that a vital ingredient of success is not knowing that what you're attempting can't be done..."

-Terry Pratchett

Ionizing radiation can be encountered in a vast amount of environments and applications: starting with relatively intuitive ones, like nuclear power plants or outer space, through less obvious and more everyday, like medical imaging, and to least expected, like commercial applications used in our surroundings, with background radiation. Under the influence of ionizing radiation electronic devices and circuits can change their properties and behaviour. This was first reported by Hughes and Giroux in [1], and since then remains a topical issue. These changes in electronic devices and circuits may lead to an operational error or a malfunction of the final application. One of the challenges today is to ensure correct operation of the electronic devices and systems in the environment of ionizing radiation.

#### 1 Basics:

#### Ionizing radiation and its effects on electronic devices

Ionizing radiation is kind of radiation possessing enough energy to ionize material. Fig. 1 illustrates different types of ionizing radiation. Here, simplified classification of radiation is given.

Ionizing radiation can be wave (like X- and gamma-rays) or particle (like alpha, beta or neutron radiation). It can also be directly and indirectly ionizing. The directly ionizing radiation is the charged particle flux radiation, such as high energetic protons and electrons (e.g. alpha and beta radiation). As the charged particle interacts with

FIGURE 1: Different types of ionizing radiation and their placement within energy spectrum.

matter, its energy together with charge ionizes this matter. The indirectly ionizing radiation is kind of radiation with no charged particles involved (e.g. gamma, X-ray or neutron radiation). In this case radiation influences charged particles in the matter which in turn interact within matter, ionizing it. In case of wave radiation, photons transfer their energy to secondary electrons and they deposit kinetic energy to the matter leading to dose accumulation. Neutrons on the other hand can physically knock out atoms out of their place in the crystal lattice, changing physical properties of material.

Depending on type of radiation and interaction mechanism, different effects can occur in a semiconductor device. Generally, effects of ionizing radiation on semiconductor devices can be sub-divided into two categories: single event effects and cumulative effects [2].

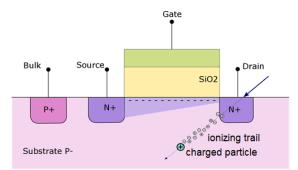

FIGURE 2: Illustration of single energetic charged particle striking an NMOS transistor leading to single event effect (SEE).

Single event effects (SEE), as the name suggests, occur when a single particle strikes the device. They are caused by charged particles, such as protons or heavy ions. When such particle strikes the device, it leaves ionization trail within the semiconductor material. The charge is then collected by the neighbouring nodes, leading to voltage or current spikes in the circuit. SEE is illustrated by Fig. 2. SEE can be destructive (such as latch-up or burn-in), or non-destructive (such as single event bit-flip or single event transient). Type of SEE is often defined by the effect it has on the particular circuit [3], [4].

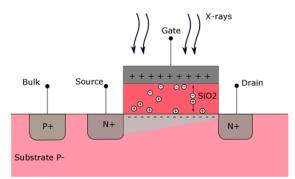

FIGURE 3: Illustration of charge trapping in gate oxide of a Silicon-based NMOS transistor under constant exposure to X-rays, leading to total ionizing dose (TID) effect.

Cumulative effects occur when the semiconductor device is exposed to ionizing radiation over a longer period of time. There are two kinds of cumulative effects: total ionizing dose (TID) effects and total displacement damage (DD).

TID effect takes place in the insulating layers of a semiconductor device or circuit. Under this effect excessive charge is trapped in  $SiO_2$  and on its interface (Fig. 3). This charge creates a parasitic electric field, leading to device parameter shifts [5], [6].

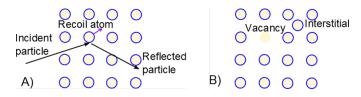

DD in turn is a change in the crystal structure of the semiconductor. It occurs when an energetic particle has enough mass to knock atoms out of their place in crystal lattice, creating a vacancy-interstitial pair (Fig. 4), changing the physical properties of the material [7], [8].

FIGURE 4: Illustration of incident particle hitting crystal lattice of semiconductor material leading to displacement damage (DD).

Table 2 summarizes the effects of ionizing radiation on semiconductor devices and circuits, including origin of the effect, place of its occurrence and the consequences on device and circuit level.

|             | SEE              | TID                        | DD                        |

|-------------|------------------|----------------------------|---------------------------|

| Origin      | single energetic | exposure                   | over time                 |

|             | charged particle | all kinds of radiation     | particles with mass       |

| Occurrence  | Si               | $SiO_2$                    | Si                        |

| Effect      | Ionization trail | Trapped charge             | Vacancy-Interstitial      |

|             | latch-up,        | $V_{th}$ shift,            | breakdown voltage change, |

| Consequence | transient,       | increased leakage current, | increased noise,          |

|             | bit flip         | increased noise            | gain decrease             |

TABLE 2: Effects of ionizing radiation on semiconductor devices - summary.

#### 2 Motivation:

#### New generation of computed tomography

Computed tomography (CT) is one of the key diagnostic tools of the modern medicine [9]. However, this powerful tool is connected with a certain risk for the patient exposed to ionizing radiation. For example, the typical dose equivalent (total dose absorbed by a living tissue) of a chest CT is 7 mSv [10]. This corresponds to 7 years of the annual dose limit of civilian population in European Union [11]. The major objectives of the modern CT developments are patient exposure reduction together with improvement of image quality. This requires high speed high precision read-out electronics. In 2010 ams AG has launched a new revolutionary CT sensor solution developed in close cooperation with Siemens AG, the worldwide market leader for CT-scanners [12]. This sensor integrated circuit (IC) is based on a 3D integration of die stacking technology with photo sensor and read-out circuit connected realizing the shortest interconnects [13]. This new CT solution yielded dramatic improvements in linearity, noise reduction, speed and power consumption. To provide even better image resolution maintaining chip area, single channel read-out circuit acquiring X-ray image must be shrank in size even further.

The new much tighter spacing of photo detector and readout ICs raises new challenges for X-ray radiation hardness of the IC design. The circuits must provide precision measurement and maintain their accuracy over the possibly long lifetime under the influence of ionizing radiation. That is why a comprehensive study of the effects of Xrays on ICs and their mitigation is needed to facilitate radiation hard IC development for the next generation CT, enabling in the next 5-10 years new solutions with improved medical imaging resolution at lowered x-ray exposure for the patients

#### 3 Scope of the thesis

The focus of this thesis lies on the effects of X-ray radiation on integrated circuits, for two reasons. First of all, this is the kind of radiation relevant for the CT, and next generation CT is the main driver for this work. Additionally, X-ray effects are relevant for other application fields with other types of radiation. The major effect caused by X-rays is TID effect. Study of X-ray effects allows to isolate TID from other effects occurring under other types of radiation. So this study can be also used as a stepping-stone to further radiation hardness investigations involving other effects.

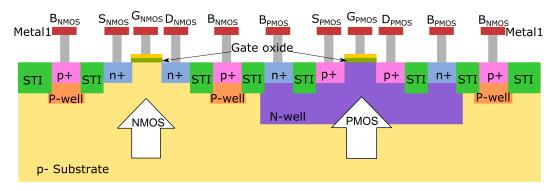

The potential industrial utilization of the scientific findings of my work is one of the major concerns in its implementation, so a commercial Complementary Metal-Oxide Semiconductor (CMOS) IC manufacturing process was chosen. Focusing on economic aspects, a 180 nm CMOS technology with shallow trench insulation (STI) was selected, offering a good trade-off between performance and costs. Fig. 5 illustrates a cross-section of the CMOS process.

FIGURE 5: Illustration of commercial p-substrate CMOS process. Cross-section of an NMOS and a PMOS transistors.

Within this thesis I address three main subjects: X-ray effects and their mitigation, modelling and testing. In this way I cover major steps in the IC development flow in order to enable industrial radiation aware IC design in the future. The scope of my work is defined as follows:

- **Vision** of this work is to enable next generation CT: with reduced patient dose, improved image quality and increased reliability better diagnostics for better health.

- **Mission** of this work is to provide scientific and industrial community with comprehensive study on X-ray effects on integrated circuits, methods for their mitigation, and procedures for radiation effects testing in research and development stage.

- **Subject** of this work is X-ray effects on semiconductor devices and circuits in a commercial CMOS process with STI.

- Methods used in this work include device and circuit design and layout, modelling, variety of electrical measurements, irradiation tests and analytical device and circuit parameters extraction.

- Novelty of this work lies in its generalist approach to a specific topic of X-ray effects on semiconductor devices and circuits. In my work all aspects relevant to IC development for X-ray environment are addressed: from single device effects, through modelling of devices and circuits, and to X-ray effects testing. The main contributions to the state of science and state of the art are:

- Comprehensive study of X-ray effects on integrated devices and circuits, in particular substrate doping and gate extension area influence on TID effects.

- New data on low TID (<25 krad) effects on DC and noise performance of MOS transistors.

- Approach to radiation aware IC design: device choice, dimensioning and layout.

- Novel isosceles trapezoid model for annular gate transistor equivalent aspect ratio estimation.

- Circuit-level radiation effects analysis by means of macro-modelling, applied in circuit simulator.

- Methodology for X-ray effects characterization. The highlights are test structure development and parameter extraction methodology, including novel threshold voltage extraction technique adaptation for gate and STI components separation.

- Methodical approach to X-ray testing beyond standards and X-ray test results unification between different irradiation sources and facilities.

#### 4 Structure of the thesis

This work is sub-divided into three main parts; together with this Motivation and the Conclusions it covers 4 years of intensive scientific work on the X-ray effects on ICs and methodology for radiation hardening, done in the frame of funded Austrian Funding Agency (FFG) project Cotomics (number 5082678). Every chapter is supported by a short introduction highlighting the state of science and a short conclusion summarizing main scientific findings presented within the chapter.

Chapter I deals with effects of X-rays on the integrated devices and approaches to their mitigation on device and circuit level. The main focus lies on integrated diode structures and MOS transistors, as those constitute the majority of devices in an integrated circuit. This chapter is sub-divided into three sections: transient X-ray effects, TID effects, and radiation hardening by design. Here the devices behaviour and parameters before, during and after irradiation is studied and analysed. It is concluded with circuit radiation hardening methodology.

In Chapter II the methodology of radiation hardening implementation is discussed. This chapter deals primarily with modelling, as a key step to reliable circuit design. It is subdivided into two sections: modelling of radiation hardened enclosed layout transistors (ELTs), and modeling of circuit radiation effects.

Chapter III of my thesis summarizes the testing methodology beyond standards necessary to be able to ensure robustness of ICs against X-rays. This chapter consists of two sections: dealing with test structures, their parameters and extraction of these parameters, and X-ray test development and dosimetry.

I finish this thesis with Conclusions and Outlook, highlighting my scientific contribution to the state of the art, and with an outlook on the future scientific opportunities, triggered with my research.

I provide details, vital for reproducibility of my research results in two Appendixes. In Appendix A one can find experimental details on how the results presented in this thesis were obtained, and Appendix B gives an inside on noise measurements.

### Chapter I

# X-Ray Effects and their Mitigation

"...Learnin' how not to do things is as hard as learning how to do them..." —Terry Pratchett, "A Hat Full of Sky"

#### Introduction

X-rays possess enough energy to ionize semiconductor materials, silicon and silicon dioxide in particular. Effects of such ionizing radiation have been studied for the past few decades [14], [15]. Unlike effects of particle and heavy ion radiation, dealing usually with instantaneous single event effects (SEE) [16], [17], in the context of X-ray the focus lies on cumulative effects and TID [2]. Still, there exists an SEE equivalent in this context - X-ray pulse induced transient [18].

The basic mechanism behind TID - the charge trapping - has been topical for few decades [19], [20], [6]. Still, not all phenomena are understood, triggering further research activities [21], [22]. Also the known mitigation techniques have to be adapted to the emerging technologies, as the transistor features scale down [23], [24].

In this chapter I deal with the particularities of the X-ray effects on basic building blocks of an integrated circuit - diodes and transistors. I analyse the basic mechanisms behind the qualitative and quantitative effects and their dependence on the various device parameters. This comprehensive study advances the state of scientific knowledge

10

about X-ray effects, covering transient effects and TID effects and dependence of the TID effects on device size, doping and layout.

I conclude with a summary on the mitigation techniques and radiation hard by design methodology as a set of design guidelines for analog and mixed signal ICs operating under exposure to X-rays. The innovative design methodology in its simplicity can be easily integrated in the standard industrial design flow, facilitating research and development in the field of radiation hard integrated circuits. Unique in their completeness the design guidelines allow ensuring of radiation hardness with close to no complex mitigation techniques - by simple dimensioning and smart device choice. Only the residual effect has to be mitigated with specific circuit and layout techniques.

The data presented in this chapter and used for the analysis has been obtained in the experiments described in Appendix A.

#### **1** Transient effects

Traditionally, transient radiation effects on electronics are analysed in context of high dose rate upsets [25]. However even at lower dose rates and moderate ionizing radiation energies transient effects can take place. Under the influence of photons of certain energy semiconductors undergo photoelectric effect [26], [27]. The generation of electron-hole pairs due to the photoelectric effect depends on the intensity of the photon beam and the wavelength (influencing penetration depth). In the case of X-rays, the energy the photon deposited in the silicon can be enough to generate two to fifty thousand electronhole pairs. This phenomenon is widely used in photon counting detectors, but can lead to undesired noise, current and voltage spikes when an X-ray pulse hits the circuit under operation. Alexander in his work [18] gives a comprehensive overview of the few decades of research in the area of transient radiation effects. The particular interest in this research area lies on transient effects modelling for very high dose rate radiation, whereas only little is reported about medium and low dose rate radiation of moderate energy, like X-rays.

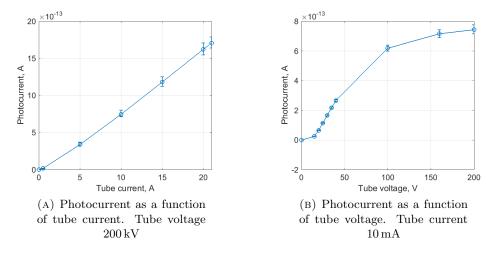

In the frame of my thesis I consider transient effects of X-ray radiation in the context of radiation hard IC design. The current density generated by an X-ray pulse is particularly important in this context. In this section my experimental results on transient effects on integrated diodes fabricated in a commercial CMOS process with STI are presented. The photocurrent of integrated diodes generated by a 60 keV X-ray source is shown in Fig. I.1 as a function of tube current (A) and of tube voltage (B).

FIGURE I.1: Average (points), and minimal and maximal (bars)  $10 \times 10 \,\mu$ m diode photocurrent as a function of X-ray tube current (A) and voltage (B)

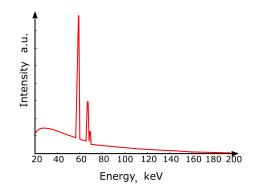

The linear dependence observed in the Fig. I.1A corresponds to the intensity linearity of the X-ray source. The non-linear dependence of the photocurrent on the tube voltage as seen in Fig. I.1B illustrates difference in depth of collection region for the different energy of X-rays. A sketch of the energy spectrum of the X-ray source, reflecting the spectral distribution of X-ray intensity in arbitrary units (a.u.), is shown in Fig. I.2. The dominant spike corresponds to K-shell characteristic energy of the X-ray target (in the discussed case Tungsten). It is superimposed on the Bremsstrahlung emitted as the tube is bombarded with a beam of electrons. The intensity of the generated X-rays is defined by tube current and the energy spectrum of the X-rays by the tube voltage.

FIGURE I.2: Qualitative sketch of the energy spectrum of Tungsten target X-ray source (Logarithmic Y-scale)

The photocurrent is proportional to the area of the diode, dose rate and thus intensity of the X-ray beam, and depth of the collection region [25]. The non-linearity of the photocurrent dependent on the tube voltage (and thus mean energy of the beam) is related to the different penetration depth and absorption coefficient of different energies of X-ray in silicon. This means on the one hand variation in dose rate and on the other hand variation in charge collection depth. These quantities changing with different speed along the tube voltage lead to a non-linearity in the photocurrent response. In contraty the tube current changes only the intensity and thus the dose rate, leading to linear dependence of the photocurrent on the tube current at constant voltage.

The quantitative behaviour of the photocurrent depends on the afore mentioned factors as well as on the fabrication process of the device. The higher the doping of the silicon in the exposure region, the less effect the produced photocurrent will have. The results shown in Fig. I.1 show general robustness of the analysed devices. The order of magnitude of the photocurrent at maximal tube voltage (Fig. I.1A) varies between 1 and  $10 \text{ fA}/\mu m^2$ . Such photocurrent can be considered insignificant for most circuits. The results presented here are obtained from a 180 nm CMOS technology. This allows to assume that with scaling down of the technology nodes incorporating higher doping levels, higher photocurrent values would be required to cause behaviour changes in a circuit. However, capacitances in smaller technology nodes are also getting smaller, thus the photocurrent values have to be carefully taken into account in radiation tolerant design, as will be discussed later in Section 3 of this chapter.

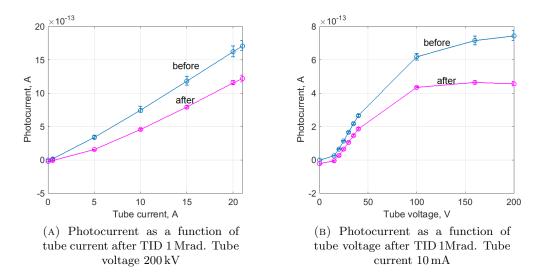

Finally, I report the difference in photocurrent between virgin and pre-irradiated samples. Fig. I.3 illustrates photocurrent of the same  $10 \times 10 \,\mu\text{m}$  N+ in substrate diode before irradiation and after TID of 1 Mrad. In this figure the induced photocurrent is significantly lower after irradiation. Thus, TID has influence on the charge collection efficiency at given energy or on material absorption properties. This hints on the change DC performance of the diodes. This change is discussed in the next subsection.

#### 2 Total Ionizing Dose Effects