Christoph Ehrenhöfer BSc

## Design and Implementation of an FPGA-based Time-of-Flight Processing System

## MASTER'S THESIS

to achieve the university degree of

Diplom-Ingenieur

Master's degree programme: Telematics

submitted to

## Graz University of Technology

Supervisor

Ass.Prof. Dipl.-Ing. Dr.techn. Christian Steger

Institute for Technical Informatics

Advisor: Ass.Prof. Dipl.-Ing. Dr.techn. Christian Steger Dipl.-Ing. Dr.techn. Norbert Druml (Infineon Technologies Austria AG)

## Affidavit

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present masters thesis dissertation.

.....

.....

Signature

Date

## Kurzfassung

Der Einsatz von dreidimensionalen Bildverarbeitungstechnologien in Unterhaltungs- und Industrieelektronik wurde in den letzten Jahren sehr populär, wobei die Time-of-Flight-Technologie insbesondere das Interesse auf sich gezogen hat. Aufgrund der kompakten Baugröße von Time-of-Flight-Kameras, können solche Systeme leicht in verschiedene eingebettete Systeme, z.B. Smartphones, integriert werden. Daher können die Anforderungen an implementierte Anwendungsfälle sehr unterschiedlich sein. Deshalb ist es nicht so einfach ein Time-of-Flight-System zu entwerfen, welches einen guten Kompromiss zwischen Hardwarebeschleunigung und Flexibilität erzielt.

Diese Masterarbeit stellt eine neuartige Plattform zur Verarbeitung von Time-of-Flight-Daten auf einem flexiblen und schnellen Hardware-/Software-System dar. Das wird unter Verwendung der Xilinx Zynq-Plattform erreicht, die bereits erfolgreich für die zweidimensionale Bildverarbeitung in verschiedenen Anwendungsfällen, z.B. Falldetektion, eingesetzt wurde. Der Zynq-System-on-Chip ermöglicht die hardwarebeschleunigte Berechnung von Time-of-Flight-Daten auf einem FPGA. Zusätzlich können die hardwareintegrierten Komponenten in Software, auf einem ARM-Prozessor, gesteuert werden. Dieses leistungsstarke Hardware-/Software-System bietet hohe Flexibilität und eine wesentliche Beschleunigung in Hardware.

Darüber hinaus wird die Durchführbarkeit des vorgestellten Systems demonstriert. Das komplette System besteht aus der Automobilplattform AURIX von Infineon Technologies, einer Time-of-Flight-Kamera, entwickelt von Infineon Technologies in Kooperation mit PMDTechnologies, und einem Zynq-Entwicklungsboard. Zwei Time-of-Flight-Algorithmen für die Vorverarbeitung der Tiefeninformation für typische Anwendungsfälle (z.B. Gestenerkennung, Indoor-Navigation) werden implementiert. Diese Tiefen- und 3D-Daten werden dann dem AURIX zur Verfügung gestellt. Die erhaltenen Ergebnisse zeigen, dass nahezu 100 FPS bei einem durchschnittlichen Rechenfehler von 0.08 mm erreicht werden können.

Außerdem wird ein praktischer Ansatz von Rapid-Prototyping für Algorithmen vorgestellt. High-Level-Synthesis wird für die Erstellung von Hardwarekomponenten für zwei Testfälle verwendet, welche dann mit dem FPGA-basierten Time-of-Flight-Koprozessor verglichen werden. Die Ergebnisse zeigen, dass die implementierten Hardwaremodule die gleiche Größenordnung in Bezug auf Leistung und Größe haben. Dies zeigt, dass die entwickelte Time-of-Flight-Plattform hinsichtlich verschiedener Anwendungsfälle und deren Anforderungen sehr flexibel ist.

## Abstract

Three-dimensional imaging technologies have become very popular during the last years in consumer and industrial electronics. The Time-of-Flight (ToF) technology has especially attracted lots of interest. Due to the small form factor of Time-of-Flight cameras, such systems can be easily integrated in a variety of different embedded devices, for example, in smart phones. The requirements of implemented use-case applications can therefore differ widely. Thus, it is not easy to create a Time-of-Flight framework that can achieve a good trade-off between hardware-acceleration and flexibility.

This thesis presents a novel platform to process Time-of-Flight data on a flexible and fast hardware/software system. This is accomplished by using the Xilinx Zynq platform, which is already successfully used in evaluating two-dimensional image processing in various kinds of applications, for example, fall detection. The Zynq System-on-Chip (SoC) allows the hardware-accelerated computation of Time-of-Flight data on an FPGA. In addition, the hardware-integrated components are controlled in software on an ARM CPU. This powerful hardware/software system provides high flexibility while achieving an essential speed-up in hardware.

The work also demonstrates the feasibility of the proposed system. The complete system consists of the automotive platform AURIX from Infineon Technologies and a Time-Flight camera system, developed from Infineon Technologies in cooperation with PMDTechnologies, and the Zynq development board. Two Time-of-Flight pre-processing algorithms for typical use-case applications (e.g., gesture recognition, indoor navigation) are implemented to provide distance and 3D data to the AURIX. The results show that almost 100 FPS are possible with an average calculation error of 0.08 mm.

Furthermore, a practical approach of rapid algorithm prototyping is introduced. High Level Synthesis is used to create hardware components for two test cases, which are compared to the FPGA-based Time-of-Flight co-processor. The results show that the implemented hardware modules have the same dimension regarding performance and utilization. This shows that the developed Time-of-Flight processing platform is highly flexible regarding different use-case applications and requirements.

## Acknowledgments

This master's thesis was carried out at the Institute for Technical Informatics at the Technical University Graz. The practical part of this work was developed at Infineon Technologies in Graz. First of all, I want to express my thanks to all people who were involved in the creation process of this thesis.

I would like to appreciate the efforts and assistance of my thesis advisor Ass.Prof. Dipl.-Ing. Dr.techn. Christian Steger. With his participation and valuable comments, the quality of this work was considerably improved. In addition, it gives me great pleasure in acknowledging the support of my advisor Dipl.-Ing. Dr. techn. Norbert Druml at Infineon Technologies Austria AG. He attracted me to the interesting topic of this thesis and steered me in the right direction to successfully complete my work.

I also would like to acknowledge my fellow students throughout my years of study in Graz. In particular I consider it an honor to work with Josef and Lukas on a vast number of projects during my bachelor and master studies. Furthermore, I would like to underscore the harmonic and effective teamwork before deadlines and exams with them.

Finally, I would like to extend my thanks to my whole family, especially my parents, for their emotional and financial support during my academic studies. Without their unfailing help, the accomplishment of my master's degree would have been significantly more difficult. Thank you.

Graz, May 2016

Christoph Ehrenhöfer

# Contents

| 1        | Intr | oducti         | on                                             | 19              |

|----------|------|----------------|------------------------------------------------|-----------------|

|          | 1.1  | Motiva         | ation                                          | 20              |

|          | 1.2  | Object         | tives                                          | 20              |

|          | 1.3  | Outlin         | e                                              | 21              |

| <b>2</b> | Rel  | ated W         | Vork                                           | 23              |

| -        | 2.1  |                | of-Flight Principle                            | 23              |

|          |      | 2.1.1          | Modulation Signals                             | $\frac{20}{24}$ |

|          |      | 2.1.2          | Other 3D Measurement Systems                   | 25              |

|          |      | 2.1.2<br>2.1.3 | Photonic Mixer Device                          | 26              |

|          |      | 2.1.0<br>2.1.4 | 4-Phases Measurement                           | $\frac{20}{27}$ |

|          |      | 2.1.1<br>2.1.5 | Unambiguous Range Extension                    | $\frac{21}{28}$ |

|          |      | 2.1.0<br>2.1.6 | Systematic Measurement Errors and Compensation | 20<br>29        |

|          | 2.2  |                | of-the-Art                                     | $\frac{20}{32}$ |

|          | 2.2  | 2.2.1          | FPGA-based Time-of-Flight Processing           | 32              |

|          |      | 2.2.1<br>2.2.2 | Image Processing on the Xilinx Zynq Platform   | 36              |

|          | 2.3  |                | ng Framework                                   | 40              |

|          | 2.0  | 2.3.1          | System                                         | 40              |

|          |      | 2.3.2          | Image Processing                               | 41              |

|          |      | 2.3.3          | Results                                        | 43              |

|          |      | 2.3.4          | Limitations                                    | 44              |

|          |      |                |                                                |                 |

| 3        | Des  | •              |                                                | 45              |

|          | 3.1  | -              | rements                                        | 45              |

|          | 3.2  | 0              | n Architecture                                 | 46              |

|          |      | 3.2.1          | Concept                                        | 46              |

|          |      | 3.2.2          | Selection of the FPGA Platform                 | 47              |

|          |      | 3.2.3          | Interaction                                    | 47              |

|          | 3.3  |                | ecture on the Zynq Platform                    | 49              |

|          |      | 3.3.1          | Concept                                        | 49              |

|          |      | 3.3.2          | Interaction                                    | 51              |

|          | 3.4  | Interfa        |                                                | 52              |

|          |      | 3.4.1          | Parallel Interface                             | 52              |

|          |      | 3.4.2          | Control Interface                              | 53              |

|          | 3.5  | Time-o         | of-Flight Processing Pipeline                  | 54              |

#### CONTENTS

|              |                  | 3.5.1 4-Phases Algorithm                | 54        |  |  |

|--------------|------------------|-----------------------------------------|-----------|--|--|

|              |                  | 3.5.2 8-Phases Algorithm                | 57        |  |  |

|              |                  | 3.5.3 Calibration Data                  | 59        |  |  |

|              | 3.6              | High Level Synthesis                    | 59        |  |  |

| 4            | Imp              | blementation 6                          | <b>51</b> |  |  |

|              | 4.1              | Development                             | 51        |  |  |

|              |                  | 4.1.1 Workflow                          | 51        |  |  |

|              |                  | 4.1.2 Environment                       | 52        |  |  |

|              | 4.2              | Time-of-Flight Processing Platform      | 64        |  |  |

|              |                  | 4.2.1 System                            | 55        |  |  |

|              |                  | 4.2.2 Hardware Specifics                | 67        |  |  |

|              |                  | 4.2.3 Time-of-Flight Processing Library | 71        |  |  |

|              | 4.3              | Time-of-Flight Processing Algorithm     | 73        |  |  |

|              |                  | 4.3.1 Workflow                          | 74        |  |  |

|              |                  | 4.3.2 Implementation                    | 74        |  |  |

|              | 4.4              | High Level Synthesis                    | 77        |  |  |

|              |                  | 4.4.1 Workflow                          | 78        |  |  |

|              |                  | 4.4.2 Implementation                    | 78        |  |  |

|              | 4.5              | Verification                            | 30        |  |  |

| <b>5</b>     | $\mathbf{Res}$   | ults                                    | <b>31</b> |  |  |

|              | 5.1              | Implementation                          | 31        |  |  |

|              |                  | *                                       | 31        |  |  |

|              |                  | 5.1.2 Throughput                        | 34        |  |  |

|              | 5.2              |                                         | 35        |  |  |

|              |                  |                                         | 36        |  |  |

|              |                  | 5.2.2 8-Phases Measurement              | 90        |  |  |

|              | 5.3              |                                         | 94        |  |  |

|              | 5.4              | High Level Synthesis                    | 98        |  |  |

| 6            | Con              | nclusion and Future Work 10             | )1        |  |  |

|              | 6.1              | Conclusion                              | )1        |  |  |

|              | 6.2              | Future Work                             |           |  |  |

| $\mathbf{A}$ | Har              | rdware System 10                        | )5        |  |  |

| Bi           | Bibliography 107 |                                         |           |  |  |

|              |                  |                                         | •         |  |  |

# List of Abbreviations

| $\mathbf{ARM}$ | Advanced RISC Machine                    |

|----------------|------------------------------------------|

| AXI            | Advanced eXtensible Interface            |

| BRAM           | Block Random Access Memory               |

| $\mathbf{CPU}$ | Central Processing Unit                  |

| DDR            | Double Data Rate                         |

| DMA            | Direct Memory Access                     |

| DRAM           | Dynamic Random Access Memory             |

| DSP            | Digital Signal Processor                 |

| $\mathbf{FF}$  | Flip-Flop                                |

| FPGA           | Field Programmable Gate Array            |

| FPN            | Fixed Pattern Noise                      |

| FPPN           | Fixed Pattern Phase Noise                |

| FPS            | Frames per second                        |

| HLS            | High Level Synthesis                     |

| I2C            | Inter-Integrated Circuit                 |

| IDE            | Integrated Development Environment       |

| ΙΟ             | Input/Output                             |

| IP             | Intellectual Property                    |

| $\mathbf{LUT}$ | Look-up Table                            |

| PCB            | Printed Circuit Board                    |

| $\mathbf{PIF}$ | Parallel Interface                       |

| PMD            | Photonic Mixer Device                    |

| $_{\rm PL}$    | Programmable Logic                       |

| $\mathbf{PS}$  | Processing System                        |

| SDK            | Software Development Kit                 |

| SDRAM          | Synchronous Dynamic Random Access Memory |

| SoC            | System-on-Chip                           |

| ToF            | Time-of-Flight                           |

| $\mathbf{TPG}$ | Test Pattern Generator                   |

| UDP            | User Datagram Protocol                   |

| URE            | Unambiguous Range Extension              |

| VDMA           | Video Direct Memory Access               |

| VTC            | Video Timing Controller                  |

|                |                                          |

# List of Figures

| 1.1  | Basic Time-of-Flight working principle $[DFH^+15]$ (with changes)           | 19 |

|------|-----------------------------------------------------------------------------|----|

| 2.1  | Basic principle of a Time-of-Flight ranging system [Lan00]                  | 23 |

| 2.2  | Indirect Time-of-Flight principle [HLCH12].                                 | 24 |

| 2.3  | Contactless 3D measurement systems [SHB <sup>+</sup> 99]                    | 25 |

| 2.4  | Schematic structure of a PMD pixel [Alb07].                                 | 27 |

| 2.5  | Example of a 4-Phases measurement [HLCH12]                                  | 28 |

| 2.6  | Example of a measurement combining two modulation frequencies $[JBP^+10]$ . | 29 |

| 2.7  | Wiggling effect at multiple integration times [FAT11]                       | 30 |

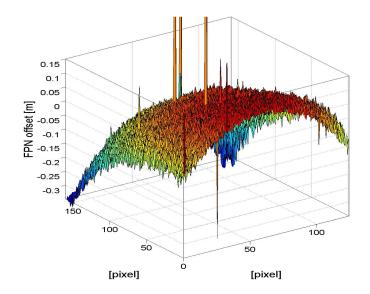

| 2.8  | Fixed pattern noise offset per pixel [KIR06]                                | 31 |

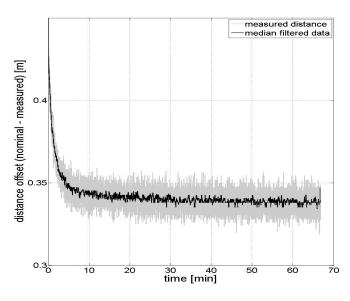

| 2.9  | Temperature-related error over an observed time [KIR06]                     | 31 |

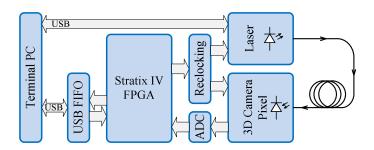

| 2.10 | Block diagram of the measurement setup [SHDZ13]                             | 33 |

|      | Interaction between the different sub-components. Obtained from [CCJD11].   | 33 |

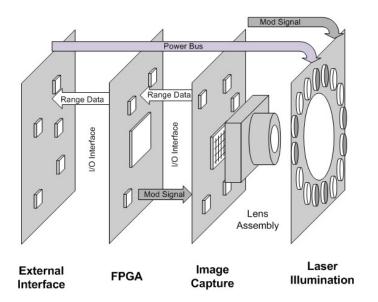

|      | System architecture of mobile image ranger system [CCJD11]                  | 34 |

|      | Development board and interconnections [JCDP08]                             | 35 |

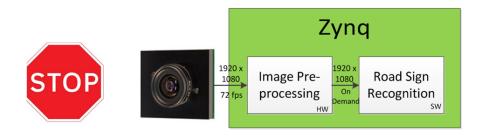

|      | Basic system architecture for road sign recognition [RF13].                 | 36 |

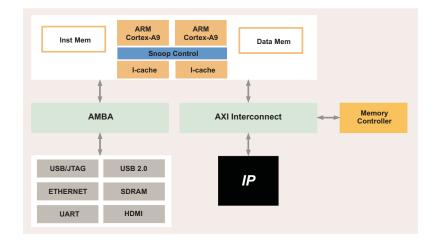

|      | Hardware architecture including HLS-generated IP [SCH <sup>+</sup> 14]      | 38 |

|      | System prototyping flow of the fall detection system [SCH <sup>+</sup> 14]  | 39 |

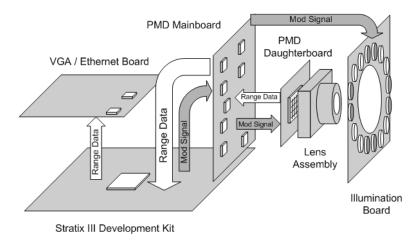

|      | Architecture of the ToF 3D imaging system [DFH <sup>+</sup> 15]             | 40 |

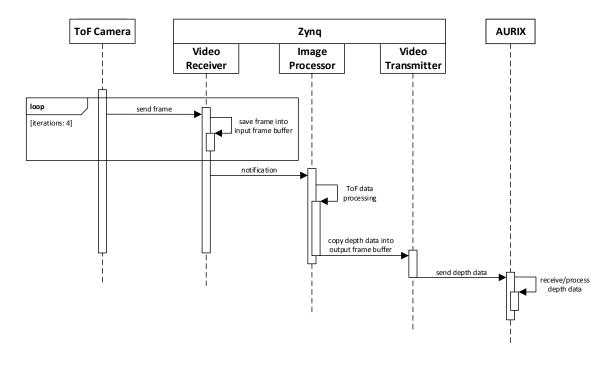

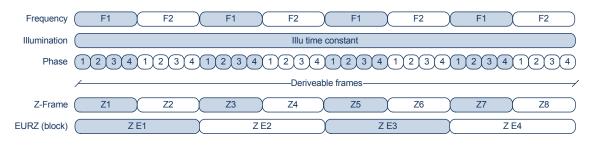

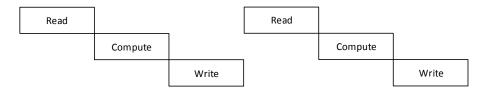

| 2.18 | Sequence diagram of the current system $[DFH^+15]$ (with changes)           | 42 |

| 3.1  | Basic system architecture of the proposed platform.                         | 47 |

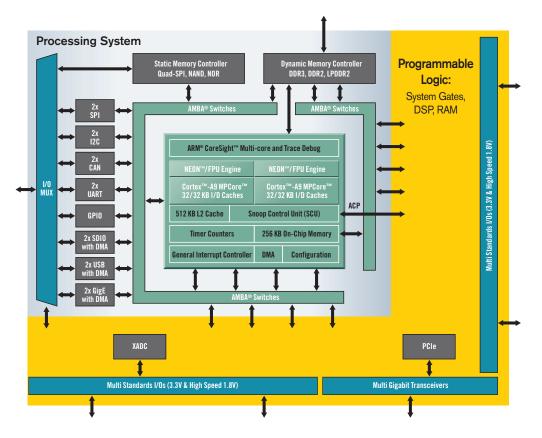

| 3.2  | Basic architecture of the Xilinx Zynq platform [Xil11a]                     | 48 |

| 3.3  | Sequence diagram of the new system                                          | 49 |

| 3.4  | Architecture on the FPGA of the new system                                  | 50 |

| 3.5  | Sequence diagram of the architecture on the Zynq                            | 52 |

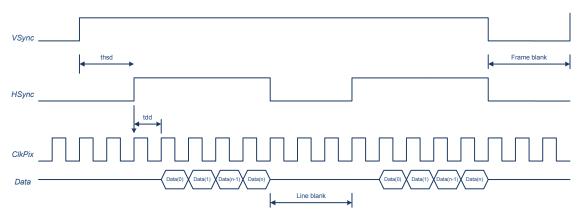

| 3.6  | Parallel interface timing [Inf15b]                                          | 53 |

| 3.7  | Structure of one frame [Inf15b]                                             | 53 |

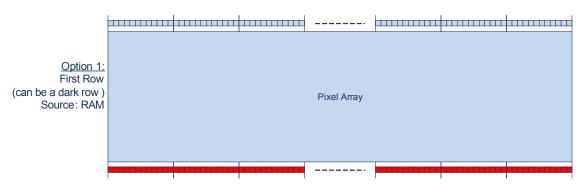

| 3.8  | Frame sequence of the 4-Phases algorithm [Inf15b]                           | 54 |

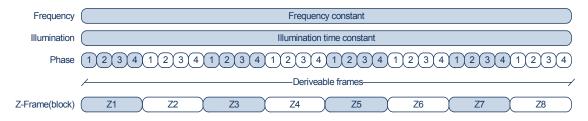

| 3.9  | Calculation steps of the 4-Phases algorithm [PMD13a]                        | 55 |

| 3.10 | Frame sequence of the 8-Phases algorithm [Inf15b]                           | 58 |

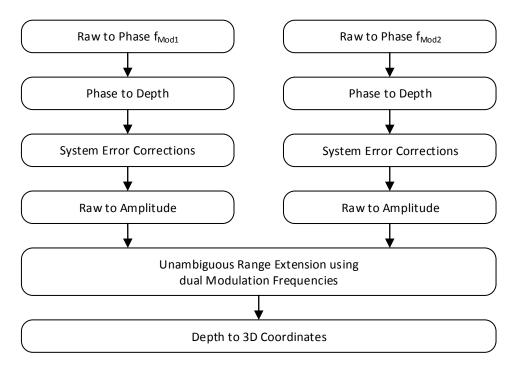

| 3.11 | Calculation steps of the 8-Phases algorithm [PMD13a]                        | 58 |

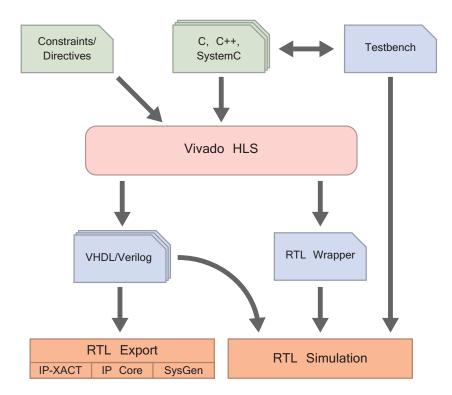

| 3.12 | Basic concept of High Level Synthesis [Cad13].                              | 60 |

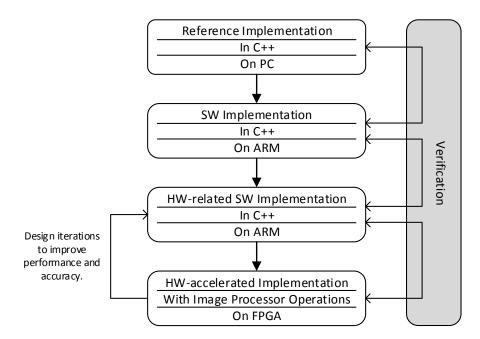

| 4.1  | Development flow based on the Xilinx Zynq platform [Cig15] (with changes).  | 62 |

| 4.2  | The used hardware from Trenz Electronics.                                   | 65 |

#### LIST OF FIGURES

| 4.3  | Implementation of the new system                                            | 66  |

|------|-----------------------------------------------------------------------------|-----|

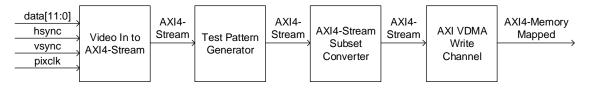

| 4.4  | Basic architecture of the video input stage.                                | 68  |

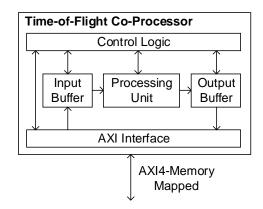

| 4.5  | Baisc architecture of the image processor [Enc14]                           | 69  |

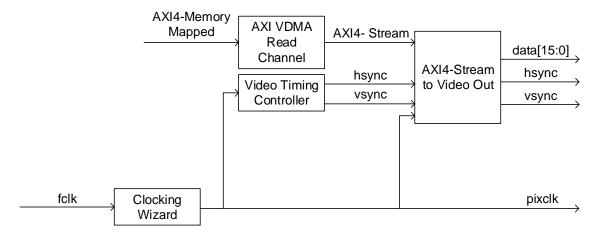

| 4.6  | Basic architecture of the video output stage                                | 70  |

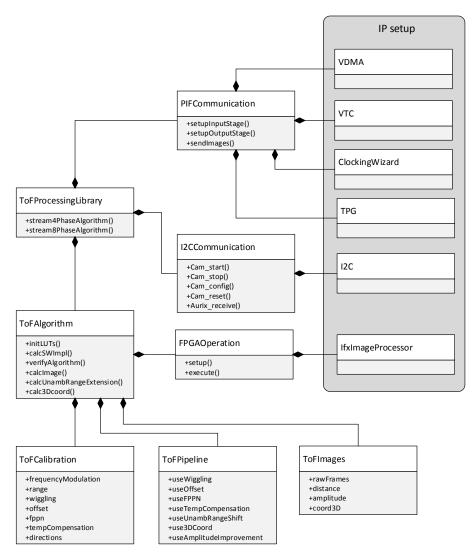

| 4.7  | Class diagram of the ToF processing library.                                | 72  |

| 4.8  | Development flow for the implemented ToF algorithm.                         | 74  |

| 4.9  | Basic concept of High Level Synthesis [CEES14] (based on [Xil11b])          | 78  |

| 4.10 | Architecture of the multi-burst approach.                                   | 79  |

| 4.11 | Architecture of the pipeline approach.                                      | 80  |

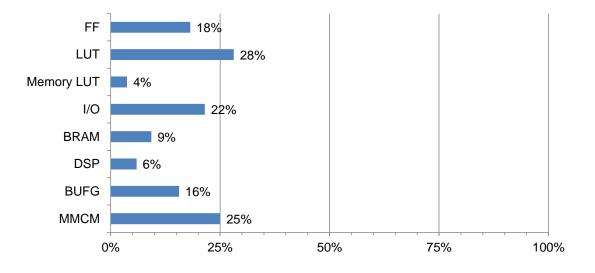

| 5.1  | Percentage utilization of the resources.                                    | 82  |

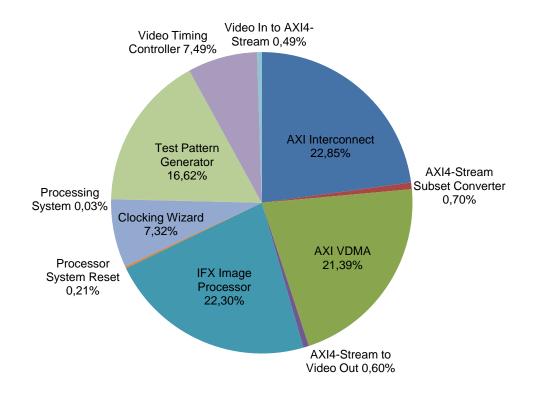

| 5.2  | Percentage distribution of the used look-up tables.                         | 84  |

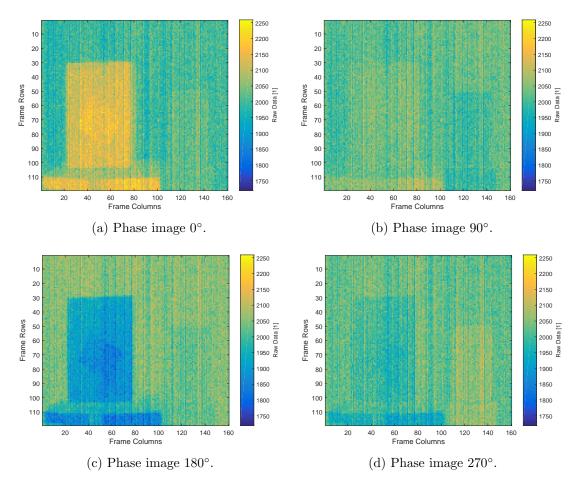

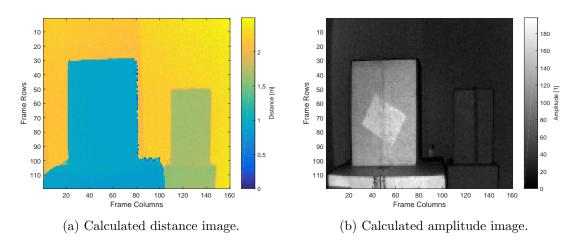

| 5.3  | Raw frames of 4-Phases measurement $(f_{Mod}: 60 \text{ MHz})$              | 86  |

| 5.4  | Calculated depth data of 4-Phases measurement $(f_{Mod}: 60 \text{ MHz})$   | 87  |

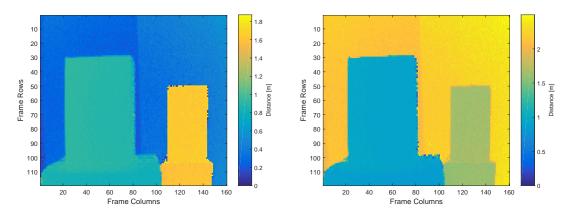

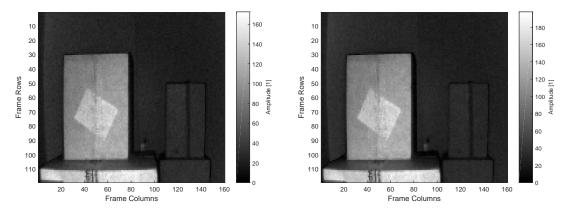

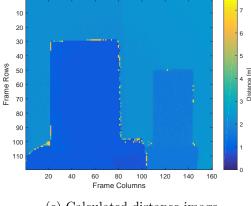

| 5.5  | Unambiguous range extension using dual modulation frequencies               | 91  |

| 5.6  | Developed demonstrator of the overall system.                               | 95  |

| 5.7  | Transmission errors at the video input stage using a 10 cm long flat cable. | 96  |

| 5.8  | Adapter PCB [Inf15a]                                                        | 97  |

| 5.9  | Transmission errors at the adapter PCB using a 2 cm long flat cable         | 98  |

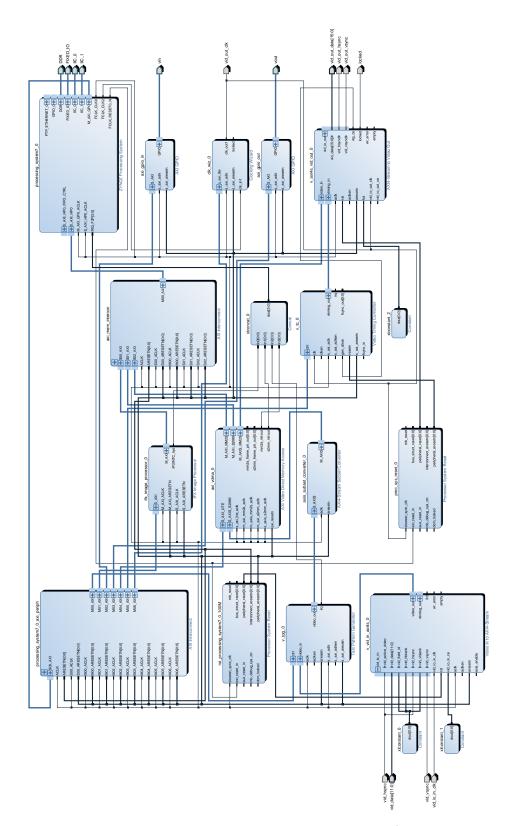

| A.1  | Block diagram of the hardware system on the FPGA.                           | 106 |

# List of Tables

| $2.1 \\ 2.2$        | Timing results of the ToF framework [DFH <sup>+</sup> 15]                                                                                                                                                                                              |     |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1                 | Configured clock frequencies of the system.                                                                                                                                                                                                            | 67  |

| $5.1 \\ 5.2 \\ 5.3$ | FPFA utilization of used resources.       FPFA utilization of all components.         FPFA utilization of all components.       FPFA utilization of all components.         Theoretical bandwidths of the memory interfaces, which are calculated from |     |

|                     | the configured hardware parameters.                                                                                                                                                                                                                    | 85  |

| 5.4                 | Timing results of the 4-Phases algorithm.                                                                                                                                                                                                              | 88  |

| 5.5                 | Mean/max errors of the 4-Phases algorithm                                                                                                                                                                                                              | 88  |

| 5.6                 | Mean/max errors after each image processor operation of the 4-Phases al-                                                                                                                                                                               |     |

|                     | gorithm                                                                                                                                                                                                                                                | 89  |

| 5.7                 | Timing results of the 8-Phases algorithm.                                                                                                                                                                                                              | 92  |

| 5.8                 | Mean/max errors of the 8-Phases algorithm                                                                                                                                                                                                              | 93  |

| 5.9                 | Mean/max error after each image processor operation of the 8-Phases algo-                                                                                                                                                                              |     |

|                     | rithm                                                                                                                                                                                                                                                  | 94  |

| 5.10                | HLS results: addition of two images.                                                                                                                                                                                                                   | 99  |

| 5.11                | HLS results: ToF amplitude calculation.                                                                                                                                                                                                                | 100 |

## Chapter 1

# Introduction

In application domains such as consumer electronics, machine vision and automotive technology, three-dimensional imaging has grown in popularity in the last years due to improvements in such systems. In a 3D image, each pixel corresponds to the range of scenery. Thus, scanning the environment with an additional dimension in comparison to 2D is possible.

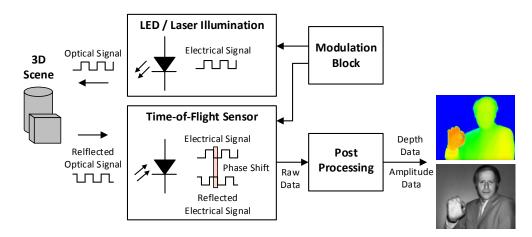

The Time-of-Flight range imaging technology has especially raised the interest. The principle is 3D imaging technology that measures the travel time of emitted light and provides distance information, by sending a laser pulse from an emitter. The reflection of the signal at the object is then detected and processed to a range image. The time consumed in-between corresponds to the distance. One implemented approach of this concept is shown in Figure 1.1. With photonic mixer devices (PMD), the phase difference of the transmitted and received modulated optical signal is measured. This phase shift is converted into a voltage that is proportional to the distance. After post-processing, typically done in software, the results are a depth image and an amplitude image.

Figure 1.1: Basic Time-of-Flight working principle [DFH<sup>+</sup>15] (with changes).

ToF-based cameras can gather a whole scene with one shot. Thus, such systems can achieve very high frame rates up to 100 FPS, which is perfect for real-time applications. Compared to other 3D imaging technologies, no moving parts are necessary, allowing cost-efficiency cameras with very small form factors to be built. The resulting distance images can be efficiently computed by a post-processing algorithm. Therefore, such robust systems are perfectly suitable to be integrated into consumer electronic or safety-critical applications.

With the growing distribution of this technology in lots of domains, various kinds of different use-cases occur. The requirements of applications vary a lot regarding the use-case. For instance, for gesture recognition high frame rates and a short measurement range is required, whereas for indoor navigation a long measurement range is needed and lower frame rates are sufficient. By keeping these characteristics in mind, it is difficult to design a cost-efficient ToF-based framework for completely different and yet, unknown use-case applications. In addition, the processing algorithm has to be fast, accurate and flexible.

## 1.1 Motivation

Today Time-of-Flight cameras can be embedded in all sorts of smart devices such as, smart phones and tablets, based on the small form factor of indirect ToF cameras, and the compact design of integrated circuits in the semiconductor industry. Due to the large range of devices, a variety of use-case applications with particular requirements, such as gesture recognition and indoor navigation, are needed. Parameters include the image resolution, frame rate, range and computation specific details. Therefore, commercial ToF solutions are normally focused on one specific use-case only.

Furthermore, some use-cases, such as gesture recognition, require high frame rates of around 40 frames per second (FPS). For a depth image, several raw images provided by the ToF camera are required. It is challenging to deliver a high number of images in a short time if the processing system performs time-consuming computation in software. In addition, the interface needs to transmit large loads of data, which also takes up time and resources.

This raises interest in showing the feasibility of a hardware/software platform that tackles these issues. This work will focus on a hardware-accelerated and flexible ToF co-processing framework. This system should efficiently implement a basic ToF post-processing flow on a Field-Programmable Gate Array (FPGA). Additionally, it will feature a flexible realization for different use-case applications. A demonstrator should be developed using the FPGA-based system as an interface between a ToF camera and an automotive processing platform.

### 1.2 Objectives

The goal of this thesis is to design and implement a hardware-accelerated ToF imaging processing system, which is highly flexible in terms of different use-case applications. The

#### 1.3. OUTLINE

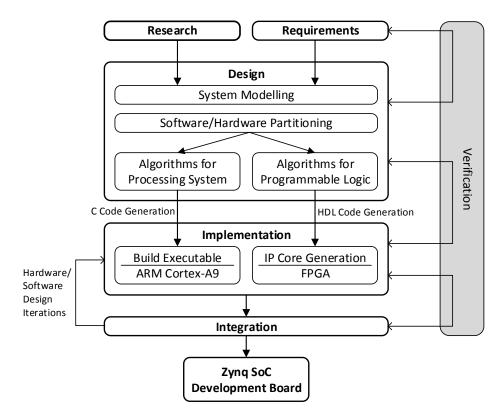

hardware/software platform enables the possibility to have a framework which is highly customizable regarding unknown applications in future. Two different use-cases should be efficiently implemented on an FPGA and evaluated regarding their performance. To reach this goal, the structure of the work represents the process of the performed activities:

- Research of basic principles and related state-of-the-art publications

- Design of a flexible hardware-accelerated ToF imaging framework

- Implementation of the FPGA-based ToF processing system

- Realization of the concept in terms of a demonstrator

- Evaluation of the implementation results regarding different performance parameters

## 1.3 Outline

The work is organized as follows: in Chapter 2, an overview of the literature research in the areas of Time-of-Flight and hardware-accelerated 2D and 3D image processing systems is given. The important topics of this work are discussed and the state-of-the-art work regarding related solutions is presented. In addition, the current system and its limitations are described. Then in Chapter 3, the requirements of the new system are summarized. Furthermore, the design of the FPGA-based Time-of-Flight processing system is shown in detail. This is followed by Chapter 4, which presents the implementation of the hardware/software system. Details about the development environment and the workflow are explained. Chapter 5 contains the results of the implementation regarding area, performance and other parameters of the processing system. Further on, details about the final demonstrator of the implemented system are shown. Finally, in Chapter 6, the work is concluded and an outlook of possible future prospects is given.

## Chapter 2

## **Related Work**

The goal of this chapter is to provide a good overview of the literature research. At first, the basic Time-of-Flight principle and its applications, as well as the common systematic errors are outlined. Next, state-of-the-art projects regarding related solutions are represented. An outline therefore about current hardware-accelerated 2D and 3D image processing systems is provided. Finally, the publication of the existing framework is described in detail.

## 2.1 Time-of-Flight Principle

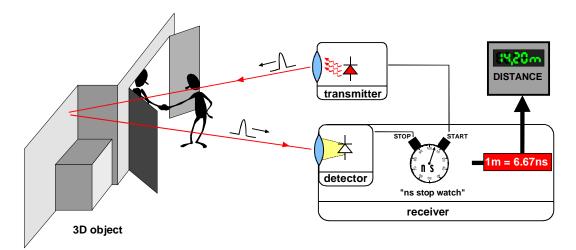

By knowing the precise value of the speed of light, it is possible to determine distances. This is calculated by measuring the time that light travels from a transmitter to a target and back to a receiver [Lan00].

Figure 2.1: Basic principle of a Time-of-Flight ranging system [Lan00].

The basic principle of a Time-of-Flight ranging system, as outlined in [Lan00], is depicted in Figure 2.1. A light pulse is emitted by an active light source and the measurement system is simultaneously initiated. The light pulse is then reflected back by the target and received by a detector, which stops the measurement system. By considering that the light travels to and from the reference point, a distance of 1 m corresponds to a measured time of 6.67 ns. This relation is illustrated in Equation 2.1 where  $\tau$  is the echo time and crepresents the speed of light. In order to avoid shadowing effects due to different camera angles, the emitter and detector are closely located. Another important property of the system is the synchronous operation of the active light source and the detector.

$$d = \frac{c \cdot \tau}{2} \tag{2.1}$$

#### 2.1.1 Modulation Signals

In order to implement this approach, different modulation types of the emitted signal exist, as described in [Lan00]. In general, pulsed modulation or continuous wave (CW) modulation is used. The most obvious technique is the pulsed light operation. By directly measuring the turn-round time of an emitted light pulse, the distance can be determined. The basic problem of such a system is the high accuracy that is required for the measurement mechanism.

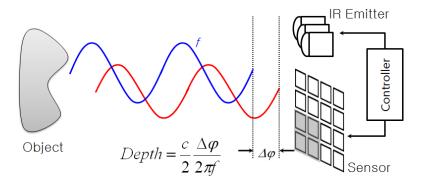

Figure 2.2: Indirect Time-of-Flight principle [HLCH12].

With the use of continuous wave modulation [Lan00], it is possible to indirectly measure the echo time by determining the phase difference between the modulated emitted and detected signal, as depicted in Figure 2.2. For such systems, lots of different light sources are available and the shape of the signal can be chosen, for example, sine wave, square wave. With the knowledge of the modulation frequency  $f_M$  and the measured phase  $\varphi$ , the echo time  $\tau$  can be calculated, as shown in Equation 2.2. With the help of this formula, the final distance d can then be computed, as represented in Equation 2.3. Because of the periodicity of the measured phase, the unambiguous range is restricted to  $c/(2f_M)$ .

$$\tau = \frac{\varphi}{2\pi f_M} \tag{2.2}$$

$$d = \frac{c \cdot \varphi}{4\pi f_M} \tag{2.3}$$

#### 2.1.2 Other 3D Measurement Systems

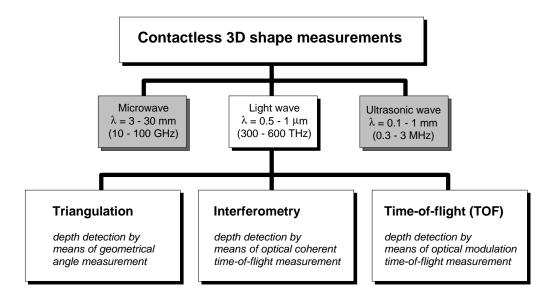

A hierarchical characterization of contactless 3D measurement techniques is given in Figure 2.3, as summarized from the author in [Lan00]. Such systems use microwave, light wave or ultrasonic wave techniques to measure the range to a target. Microwave- and ultrasonic wave-based systems are typically used in GPS or radar use-case applications. However, these two methods are not further discussed because they are not suitable for 3D measurements with high angular resolution, due to diffraction limitations. In this work, the focus is to provide an overview of optical range measurements techniques with a wave length between 0.5 - 1  $\mu$ m. The most important optical 3D measurements techniques are triangulation, interferometry and Time-of-Flight.

Figure 2.3: Contactless 3D measurement systems [SHB<sup>+</sup>99].

#### Triangulation

The triangulation measurement method, as outlined in [Lan00], is based on geometrical analysis of a triangle. The distance of a reference point is one unknown point of the triangle, whereas the other two known points belong to the system. By measuring the angles or the base line of the triangle, the unknown distance can be determined. Two different techniques exist: passive and active triangulation.

For passive triangulation [Lan00], two cameras are placed apart with a known distance and observe the same point. By measuring the viewing angles, the distance can then be determined. One common realization of this principle is **stereo vision**. 2D-correlation is used to find typical object features in both images. Due to this identification of the same point, high contrast images are necessary. This method works quite well for rich contrast scenes that need no active light source. The disadvantages however are the shadowing effect, the high computation effort and the system's size. In the active triangulation approach [Lan00], a positive sensitive detector observers a point on the scene projected from a light source. There is no need of measuring the viewing angles. Instead, the distance can be determined by knowing the focal length of the system and the point projection on the detector. In order to measure the whole scene, the laser point needs to scan the whole object surface. Using **laser scanning** on a complete line provides a faster measurement. Drawbacks are the time-consuming scanning and the need of mechanical parts in the system. An advanced technique that does not require moving parts, is based on two-dimensional **structured light**. This system projects a 2D striped pattern on the whole surface, a 2D camera then captures the scene. The range can then be determined by analyzing the displacement of the stripes.

#### Interferometry

This technique [Lua01] is based on the superposition of two monochromatic waves with the same frequency. A beam splitter is used to split a laser beam. One beam is projected to a mirror and the other to the target. An integrated detector captures both rays as they are reflected back. After integration, an interferogram provides phase information, related to the distance. Interferometry is suited for applications where high accuracy over small distances is required. The main disadvantages are that only relative distances can be measured and that the unambiguous range is very low.

#### Time-of-Flight

The basic principle of Time-of-Flight has already been described in the beginning of this chapter. An advantage of indirect ToF cameras is the small form factor because no moving parts are used and the sensor can be built in CMOS technology [Lan00]. Therefore, the camera system is robust and inexpensive. High frame rates are possible because information for all pixels is gathered in parallel whereby the phase information can be determined without much computation effort. The main drawbacks are the low resolution, the maximum unambiguous range and measurement errors, which need to be compensated by calibration.

#### 2.1.3 Photonic Mixer Device

This work will focus on Time-of-Flight imaging based on continuous wave modulation. The main feature of this method is the realization of the sensor with the photonic mixer device (PMD) technology, which implements the process of mixing and correlation of the detected optical signal and the reference signal in one semiconductor circuit, as shown in [Lua01]. The correlation between the received signal and the original signal is known as cross-correlation. Such an independent PMD pixel can be easily integrated into a matrix in 3D, which provides parallel determination of the phase.

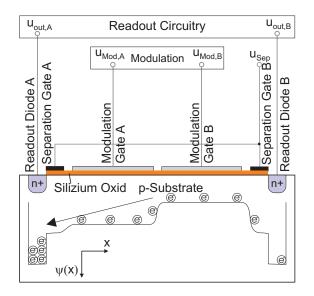

The schematic structure of a PMD pixel, as depicted in Figure 2.4, is described in detail in [Alb07]. Because of the inner photoelectric effect, incoming photons in the poly-siliconlayer are split-up into electron-hole pairs. The electrons are then separated into bucket A

#### 2.1. TIME-OF-FLIGHT PRINCIPLE

or B. This depends on the modulation of the reference signal, which generates an electrical field. After a certain integration time, the buckets are read out. The difference between the voltages of both buckets corresponds to the overlapping of the emitted and detected signal. With a longer integration time, the signal-to-noise ratio can be improved. An issue of this approach is that one measurement cannot unambiguously determine the phase delay. Hence, a further measurement is performed with the phase-shifted emitted signal. With the results of these two measurements, the phase delay can then be unambiguously calculated. Therefore, at least two illuminations are necessary to determine the phase delay.

Figure 2.4: Schematic structure of a PMD pixel [Alb07].

### 2.1.4 4-Phases Measurement

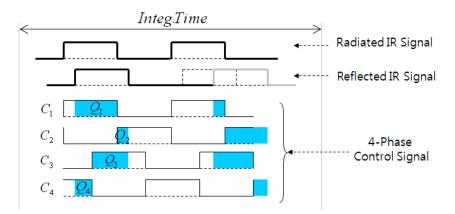

The indirect TOF measurement method using the PMD technology is within the focus of this thesis. Therefore, at least two measurements with different phase-shifts are necessary, as mentioned in the previous paragraph. Most of the state-of-the-art solutions, which use the same method and technology, perform four measurements with different shifted phases, as presented in [LS01]. Advantages of this approach include a simplified formula in calculating the final phase delay and the reduced impact of some systematic errors. In general, an equivalent phase-shift of  $90^{\circ}$  is used, which results in measurements with the following phase-shifts:  $0^{\circ}$ ,  $90^{\circ}$ ,  $180^{\circ}$  and  $270^{\circ}$ .

An example measurement [HLCH12] is depicted in Figure 2.5. The amount of electric charge for the measurements  $C_1$  to  $C_4$  is respectively represented with the quantities  $Q_1$  to  $Q_4$ . The PMD pixel efficiency determines the overlapping in one semiconductor based circuit.

Figure 2.5: Example of a 4-Phases measurement [HLCH12].

The phase and the amplitude can be unambiguously computed [HLCH12]. The phase  $\varphi$  can be calculated with the arcus tangent function, as illustrated in Equation 2.4. The values from the four measurements  $(Q_{0^{\circ}}, Q_{90^{\circ}}, Q_{180^{\circ}}, Q_{270^{\circ}})$  provided from the PMD pixel array, are used to calculate two intermediate differences, which are divided. With the same differences the amplitude A can be computed, as shown in Equation 2.5. The amplitude, which represents the strength of the received signal [FAT11], is used for prediction of the measurement quality.

$$\varphi = \arctan\left(\frac{Q_{270^{\circ}} - Q_{90^{\circ}}}{Q_{0^{\circ}} - Q_{180^{\circ}}}\right)$$

(2.4)

$$A = \frac{\sqrt{(Q_{270^{\circ}} - Q_{90^{\circ}})^2 + (Q_{0^{\circ}} - Q_{180^{\circ}})^2}}{2}$$

(2.5)

#### 2.1.5 Unambiguous Range Extension

As already mentioned, the measured phase exhibits a 2pi-periodicity. Hence, the distance is restricted to an unambiguous range of  $c/(2f_M)$ . In this section, a method is presented to extend the unambiguous range. The most obvious approach is to decrease the modulation frequency [JCPD10]. The drawback of this technique is that the measurement precision is also decreased. Another method is presented in [DCP<sup>+</sup>07]. By performing two measurements with different modulation frequencies of the scene, it is possible to extend the unambiguous range, as shown in Equation 2.6. The precision of the measurement does not significantly worsened.

$$d_u = \frac{c}{2\left|f_{M1} - f_{M2}\right|} \tag{2.6}$$

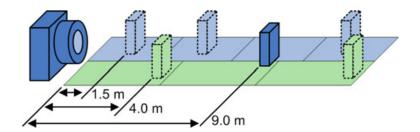

The basic idea behind dual frequency modulation is depicted in Figure 2.6. The result of each measurement is a possible set of object locations. The true location of the object is where both measurements are most in agreement. Algorithms that perform this selection step using two modulation frequencies are presented in [JCPD10] and [JBP<sup>+</sup>10].

Figure 2.6: Example of a measurement combining two modulation frequencies [JBP+10]. The correct location of the object is at 9 m.

#### 2.1.6 Systematic Measurement Errors and Compensation

Like almost all sensing devices, Time-of-Flight cameras also show different measurement error sources. Lots of research is done in this field to identify and minimize the common errors. A good overview of literature regarding systematic errors is given in [FAT11]. In general, the ToF measurement exhibits systematic, which are compensated using calibration, and non-systematic errors, which are reduced using filters. This section will focus on the main system-errors and their countermeasures.

#### Wiggling Error

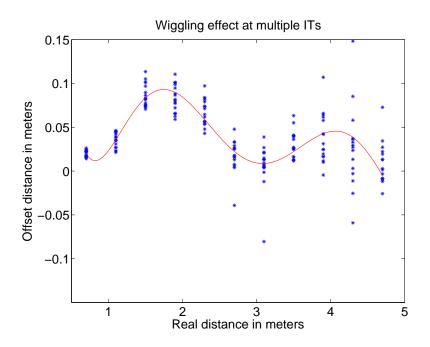

The wiggling error, also referred to as circular distance error, is based on imperfect sinusoidal waves used as emitted and reference signal, as shown in [FAT11]. It is difficult to generate in practice a plain sinusoidal signal. Therefore, an offset, which is distancedepended, is added to every pixel. The shape of the error, which can look like a sine wave, is depicted in Figure 2.7.

The error can be compensated, by measuring the distance with the camera to a known reference point [FAT11]. This is repeated for every distance value within the unambiguous range. Measured and reference distances are then compared. The result is an offset for every distance value over the complete unambiguous range. This method comes with the drawback that a high accuracy sensor is needed to determine the reference distance, e.g., track line, color camera. Another approach is to generate a model of the error by evaluating multiple relative measurements, but has the disadvantage that the processed compensation values are only suited for a limited range.

With the processed offsets, calibration data is generated to compensate the wiggling error [FAT11]. Several solutions exist to encode the data. It can be stored in a look-up table (LUT), which represents the offset, depending on the distance. It is also possible, to express the depth error by a mathematical function. A B-spline or a polynomial function higher degree can be used to store the values in a compact form.

Figure 2.7: Wiggling effect, approximated with a 6-degree polynomial, at multiple integration times [FAT11].

#### **Pixel-Related Error**

Pixel-related errors vary for every pixel and are independent of the modulation frequency, as outlined in [FAT11]. One error source is diversity of produced pixels regarding manufacturing tolerances and different material characteristics. Neighboring pixels determine different results for the same distance. Another reason for occurrence of this error is the location of the pixel on the sensor. Because of different signal path lengths, a latency-related offset is generated.

Literature distinguishes between following pixel-related errors: fixed-pattern noise (FPN) and fixed-pattern phase noise (FPPN). In [Alb07], pixel-characteristic-related errors are referred to as FPN, whereas FPPN is known as pixel-location-related errors. In general, the calibration is performed by measuring the distance to a reference plain, and determining the offsets between both results, as depicted in Figure 2.8. The compensation results are then saved in a LUT. In [LSKK10], an approach to compensate FPN is described by averaging a high amount of images that are taken with shut optics (black images).

#### **Temperature-Related Error**

Like almost all electronic devises, the temperature of the ToF camera has an impact on the measurement, as illustrated in [FAT11]. The measured distances of the whole image drift with the temperature. Internal and external temperature changes can cause this error because the sensor shows a temperature-dependent behavior. Until the working temperature is reached, the internal temperature rises and causes an offset error, as depicted in Figure 2.9.

Figure 2.8: Fixed pattern noise offset per pixel [KIR06].

The calibration, as described in [PMD13b], can be performed by measuring the distance to a known reference point, as well as the temperature of the camera while changing the internal/external temperature over a certain range. By comparing the offset error and the temperature, a thermal correction coefficient can be determined.

If a temperature sensor is directly positioned in the camera, it is possible to compensate the error with the processed calibration data [PMD13b]. If this not the case, the typically strategy is to wait until the camera reaches working temperature. After that, the compensation coefficient for the typical temperature occurring in the intended use-case is used.

Figure 2.9: Temperature-related error over an observed time [KIR06].

### 2.2 State-of-the-Art

The goal of this section is to provide an overview of similar solutions. First of all, FPGAbased Time-of-Flight imaging systems are presented. Hence the architecture and the processing algorithm of the implementations are described. Finally, the image processing projects for different use-case applications, which use the Xilinx Zyng platform, are shown.

#### 2.2.1 FPGA-based Time-of-Flight Processing

In the last years 3D imaging raised the interest in several domains, some examples include automotive technology and consumer electronics. Real-time processing is required for lots of use-case applications. For instance, a typical gesture recognition use-case requires around 40 FPS to work properly. Hence, the following paragraphs list the projects that investigate this challenge with the help of an FPGA.

#### FPGA-based Time-of-Flight Characterization System

The authors of [SHDZ13] presented an FPGA-based characterization system for a ToF sensor. The proposed framework allows the flexible generation of all control signals that are needed for a ToF distance measurement, for example, the shape of the control signal. After a measurement the captured data is pre-processed on an FPGA and sent to the host PC, which decreases the amount of data that needs to be transferred over the USB interface.

A simplified block diagram is depicted in Figure 2.10. A new measurement starts by activating the FPGA (i.e., Altera Stratix IV) over the USB interface of the host PC. The control signals are generated from the FPGA and sent to the illumination unit, as well as the 3D sensor. A laser is used as an illumination source because of the large signal bandwidth. Therefore, the illuminated light is coupled into the ToF chip through an optical fiber to remove possible error sources. The used pixels of the ToF chip, which are able to suppress very high intensities of background light, are described in [DSH<sup>+</sup>13]. The camera supports an image resolution of up to 128x128 pixels. After successful measurement the output voltages generated from the ToF chip are read from the FPGA via an ADC. The device performs the storage of a full correlation triangle into the SRAM. With a memory controller, the data can be read out to the USB interface and forwarded to the host PC. In addition, all control signals are generated in a signal generation block on the FPGA.

The author is highlighting the high flexibility of the system as compared to other publications, no commercial products are used in this work. The results show that the standard deviation of the measured distance is 0.15 mm. The FPGA can average a maximum of 256 correlation triangles to improve measurement precision. By performing the pre-processing on the FPGA, the integration time can be virtually increased. In addition, the load of data, which is transferred over the USB interface, is reduced. Hence, a highly flexible platform to characterize error sources was introduced.

Figure 2.10: Block diagram of the measurement setup [SHDZ13].

#### Easily Configurable Range Imaging System

Jongenelen et al. [JCP<sup>+</sup>09] developed a range imaging system that is easily configurable by means of modulation patterns. The platform is suited for further experiments regarding ToF-based applications. Commercial products are limited to a choice of fixed configurable parameters, whereas the proposed system can be more flexibly configured from the FPGA.

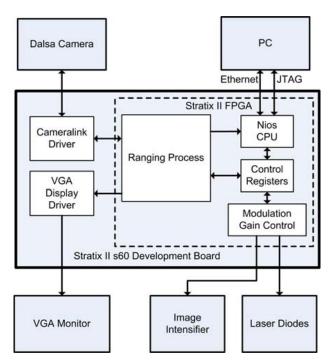

The system architecture of the hardware design, as shown in Figure 2.11, comprises several components. A ToF sensor from PMDTechnologies is connected via a mainboard to the Altera Stratix III FPGA. An illumination board provides the modulated light. The connection between the FPGA and the host PC is established with a VGA/Ethernet board. The FPGA drives the modulation signals and generates control signals for the PMD sensor. In addition, the device temporally stores the gathered raw data and computes distance images, which are then forward to a VGA monitor and a host PC. Over a JTAG interface, the PC can configure the operating parameters. The computation of the range images as well as the PMD and VGA interface are implemented in VHDL, whereas the Ethernet and JTAG interface are programmed in C on the Nios II processor.

Figure 2.11: Interaction between the different sub-components. Obtained from [CCJD11].

The experimental results showed the relation between modulation frequency and standard deviation of the phase and distance. Therefore, several measurements were obtained using different configured modulation frequencies. It was demonstrated that at a modulation frequency of 36 MHz, the best precision of the distance measurements, which is approximately 3.5 mm, can be achieved. The distance precision is related to the phase precision, which becomes worse at higher modulation frequencies due to the bandwidth limitation of electronics. The conclusion highlights the aspect of the ease of configuration of several operating parameters.

#### Image Ranger System for Mobile Robotic Platforms

In [CCJD11], the authors demonstrated an FPGA-based range imaging system that can be mounted on mobile robotic platforms. An unambiguous region of up to 15 m is required. The proposed system in [JCP<sup>+</sup>09], as mentioned in the previous paragraph, was redesigned to achieve a small form factor. The Stratic III FPGA from Altera was therefore replaced by the Altera's Cyclone III FPGA.

The basic architecture of the system is illustrated in Figure 2.12. The sub-components are designed to allow stacking on top of each other. This stacked setup provides a small form factor and upgradability of each unit. The image sensor from PMDTechnolgies allows a resolution of up to  $160 \times 120$  pixels. The FPGA implements a typical 4-Phases measurement algorithm.

Figure 2.12: System architecture of mobile image ranger system [CCJD11].

The results showed that the imaging system has the compact size of  $120 \times 200 \times 120$  mm, which corresponds to approximately 30% of the initial setup. In order to evaluate the imaging quality, a video was captured with the following configuration: 26 MHz modulation frequency, 16.7 FPS and 20 ms integration time per frame. The reference points were evaluated in the captured video sequence. Objects located in the mid-range of the image have a standard deviation of 3.8 mm, whereas objects placed further away have a standard deviation of 32.6 mm, which corresponds to 4.8% of the measured distance. By using calibration, the errors can be significantly decreased. In comparison to commercial systems

for instance, products from Canesta and Mesa Imaging, the result were reasonably good. The conclusion of this work highlighted the good performance for the cost, in comparison to equivalent commercial products.

#### Range Imaging in Real-time

In [JCDP08], the authors developed a ToF imaging system with the help of an FPGA. Laser diodes are used for illumination and the Dalsa Pantera 1M60 digital video camera captures the images. A constructed circuit board with Direct Digital Synthesizer ICs is used to control the emitted and reference signal. The architecture on the FPGA is depicted in Figure 2.13. Via the cameralink interface, the frames are transmitted to the FPGA. For computation of the phase, five raw frames are used. After one received frame, a new depth image is calculated. With a configured image resolution of 128 x 128 pixels a frame rate of up to 30 FPS can be achieved. Furthermore, the system is evaluated by capturing moving targets with modulation frequency of 40 MHz, which results in an error of around 4 cm.

Figure 2.13: Development board and interconnections [JCDP08].

#### **Time-of-Flight Range Imaging**

The authors of [JBP<sup>+</sup>10] implemented an FPGA-based system to efficiently compute the phase of captured raw data. The same hardware platform, as described in [JCP<sup>+</sup>09], was used. In particular, the trade-off between the accumulator's bit widths and the processing accuracy was evaluated. A 4-Phases algorithm was implemented using accumulators to

calculate the pixel intensities and the arcus tangent function. The results showed that for the proposed system, an accumulator width of 14 bits is necessary to provide a phase error below the system standard deviation. Furthermore, a novel algorithm was presented for extending the unambiguous range by using two different modulation frequencies.

#### 2.2.2 Image Processing on the Xilinx Zynq Platform

The Xilinx Zynq platform has attracted the interest in recent years for the realization of FPGA-based imaging systems. In this section, two-dimensional imaging projects are presented which implement this framework. The publications focus on a specific use-case application and outline the advantages of the Zynq platform.

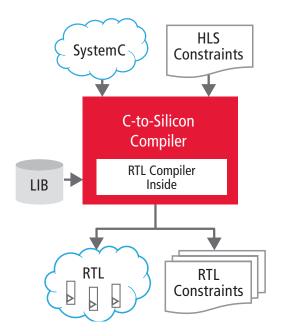

The Zynq platform consists of several ARM CPUs and an FPGA, which are integrated on one chip to provide high data bandwidth between both components, as described in [Xil15j]. The system is highly flexible as software can be executed on an ARM CPU while simultaneously using hardware-acceleration on the FPGA. In addition, Xilinx provides a practical approach of rapid prototyping for the platform, namely High Level Synthesis (HLS).

#### **Road Sign Recognition**

Russell et al. [RF13] has proposed a road sign recognition system using the Zynq platform. The detection of road signs is an essential component in autonomous driving, as well as automotive assistance systems and road sign maintenance. The system was implemented on the Zedboard, which is a development board with an integrated Xilinx Zynq chip.

In Figure 2.14 the basic architecture of the system is illustrated. The VITA-2000 image sensor from ON Semiconductor provides a stream with an image resolution of 1920 x 1080 at 72 frames per second. Image pre-processing is performed with hardware-integrated components on the FPGA. Predefined video hardware modules provided by Xilinx are used to correct the image, such as defective pixel correction. For the color based filtering, a manually developed hardware unit performs the color segmentation algorithm. The classification of the shapes and the identification of the signs from a database are implemented on the ARM CPU with the help of OpenCV.

Figure 2.14: Basic system architecture for road sign recognition [RF13].

#### 2.2. STATE-OF-THE-ART

The results showed that the system is able to detect all red and blue signs in one frame, in approximately 5 seconds. Compared to other designs that also use hardware-acceleration, the proposed system is slower. The authors considered that other implementations only process frames with an image resolution of VGA quality or below, while the proposed design processes Full HD images. Furthermore, more software computations could be hardware-integrated on the FPGA to achieve an essential speed-up. The work was concluded with an emphasis of the potential of the Zynq. This platform is well suited for embedded road sign recognition or other imaging systems. The design of the entire system took only six weeks due to the use of Xilinx tools and the standard memory interface.

#### Fall Detection

Several publications exist that implement a fall detection use-case application using the Xilinx Zynq platform, as shown in [SCH<sup>+</sup>14], [ASA<sup>+</sup>14] and [NBVT14]. All of these systems similarly investigated fast prototyping of fall detection in daily life. In order to achieve the real-time requirement, parts of the algorithms were hardware-accelerated using High Level Synthesis tools, which directly translate code in high-level language, such as C++, into a hardware description.

In [SCH<sup>+</sup>14], the authors developed a smart-camera based fall detection processing system. Based on the Zynq platform, a fast prototyping methodology was proposed which allows comparison between different real-time fall detection implementations. By using high-level algorithmic description, such as C++, and High Level Synthesis tools, this hard-ware/software system was used in the design space exploration phase for testing different architectures.

The implemented use-case has applications in the detection of falls of the elderly in daily life. Therefore, the automatic detection of falls in real-time is required. A fast response of the system is very important. The algorithm consists of image acquisition, low-level processing and fall detection. Most of the processing steps are performed on the ARM using OpenCV. The classification algorithm, which is described in C++, is used to generate a hardware component with the help of High Level Synthesis.

The basic hardware architecture is illustrated in Figure 2.15. The Intellectual Property (IP) description, which performs the hardware-accelerated computation, communicates with the two ARM CPUs and the extended memory through an AXI memory interface. This hardware module can be manually developed or generated using HLS. A pre-built Linux is used to provide a software adaption layer between hardware and use-case application.

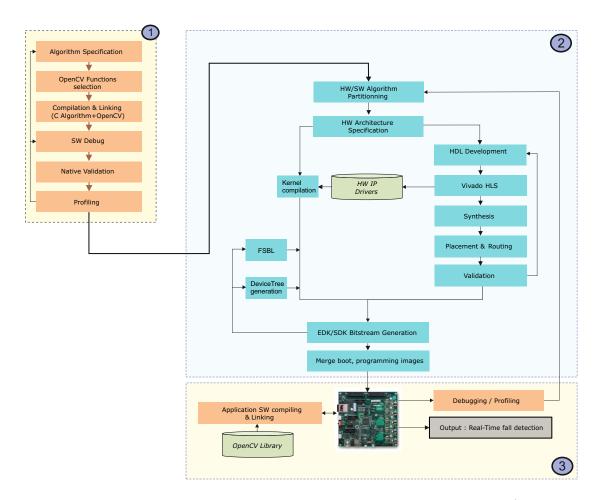

The authors especially outlined the benefits of the hardware/software integration. Therefore, the used prototyping flow of the system is depicted in Figure 2.16. The flow is proposed for the Zynq platform, but can be used also for similar hardware/software systems. It allows a fast validation and prototyping of the fall detection application. Firstly, part 1 illustrates the standard flow on a host computer. After the initial algorithm development, the computation steps are validated and optimized.

Figure 2.15: Hardware architecture including HLS-generated IP [SCH<sup>+</sup>14].

In part 2, the basic flow for creation of the hardware/software system is presented. Therefore, the initial algorithm is partitioned into hardware/software. The least regular part should be performed on the CPU to provide high flexibility. The most regular part is implemented on the FPGA. Compared to the algorithm on the host PC, additional computation performance is available because the regular parts are then hardware-accelerated. The hardware components can be manually developed or with High Level Synthesis.

Finally, in part 3 all sub-components are compiled and executed on the target platform. Implementation results can be used to start a further iteration of part 2 to improve the overall system.

The synthesis and timing results of the HLS-based hardware component were evaluated. Different versions were implemented using improved synthesis directives. The execution time of the full ARM-based software implementation (30  $\mu$ s) was almost the same as the generated hardware IP without any directives (29  $\mu$ s). By using synthesis directives the final execution time could be decreased to 2.5  $\mu$ s by using a pipeline architecture and parallelization of computation steps. The work was concluded with a description of the benefits that the Zynq platform offers for fast prototyping.

#### **Border Detection**

Sabouri et al. [SGC14] developed a border detection processing system for early diagnosis of melanoma using the Xilinx Zynq platform. By analyzing melanoma skin lesions images, skin cancer can be discovered. The goal of the study was the investigation of novel methods on an embedded system. High resolution and performance are important for portable imaging systems used in the medical domain.

Different edge detection methods, such as Sobel, Kirsch, Canny, LoG, were therefore implemented and analyzed regarding accuracy and performance. The hardware component used for border detection was generated with HLS software, which converted the C++ code to synthesizable FPGA code.

Figure 2.16: System prototyping flow of the fall detection system [SCH<sup>+</sup>14].

The results indicated that the extended 5x5 canny edge detection algorithm had the best performance compared to other presented methods. The authors showed that it is possible to achieve a frame rate of up to 60 FPS, which is well suited for real time applications. The work also outlined the rapid processing power, which is demonstrated by the Zynq platform.

#### Grayscale Conversion and Convolution

The authors of [AGBS15] implemented a real-time image processing system on the Zynq platform using hardware/software co-design. The Zedboard, a Zynq-based development kit from Xilinx, was used to explore different realizations of image algorithms. The following hardware-accelerated algorithms were investigated: grayscale conversion and convolution operations, such as edge detection, sharpening, blurring).

The overall system consists of a HDMI monitor, a standard USB camera and the Zedboard. A Linux operating system on the ARM processor is used to capture images from a video source. A manually developed image co-processor in Verilog HDL performs the algorithms on the gathered image data.

The experimental results showed that images with a resolution of  $256 \times 256$  could be processed with around 40 FPS. The hardware design utilized around 5% of the available flip-flops and look-up tables. For future work, a direct memory access (DMA) implementation was proposed, which would result in an essential speed-up of the system.

## 2.3 Existing Framework

The ToF 3D imaging system presented in [DFH<sup>+</sup>15] outlines the current system of this thesis. Therefore, this paper is described in detail in this section.

A ToF camera sensor provides raw data to an automotive computation platform. The distance is computed by performing an efficient implementation of a ToF processing dataflow. The works shows a robust solution for mixed-critical applications, in the automotive domain, on a safety-critical platform. This existing framework is already implemented and used as a starting point for the new proposed system.

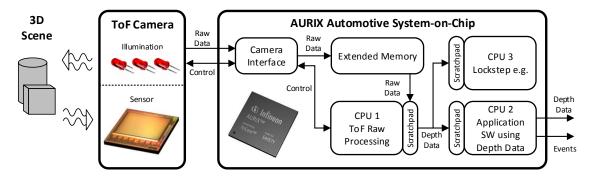

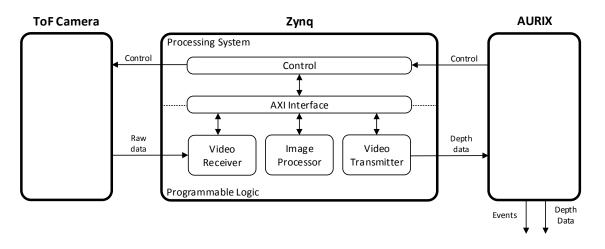

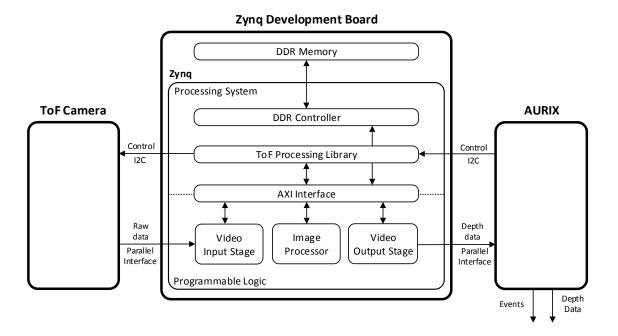

## 2.3.1 System

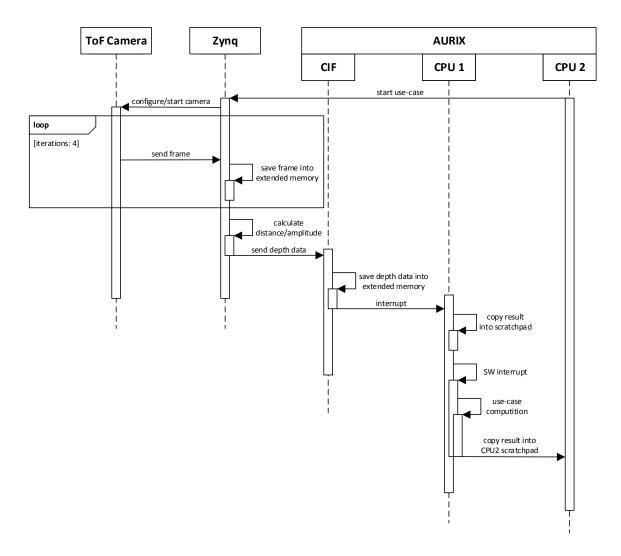

The architecture, as illustrated in Figure 2.17, consists of a ToF camera and an automotive microcontroller. Through a parallel interface which connects the two systems, raw image data provided by the camera is transmitted. The processing of the raw data is then implemented on the automotive microcontroller, which calculates depth data on one core and computes use-case specific data and events on the other, in a mixed-critical environment.

Figure 2.17: Architecture of the ToF 3D imaging system [DFH<sup>+</sup>15].

### Automotive System-on-Chip

The computation platform AURIX TC299 from Infineon Technologies is used, which targets performance and safety critical applications in the automotive industry, as outlined in [Inf14]. It is compliant to several standards including IEC 61508, ISO 26262 and ISO 25119. The multicore approach is based on three independent Tri-Core CPUs, where

#### 2.3. EXISTING FRAMEWORK

each core operates with a maximum clock frequency of 300 MHz. The Tri-Core architecture, implemented on one chip package, unifies the instruction sets of a microcontroller, a RISC processor and a DSP. Several concepts for safety critical systems including lockstep architecture and safe internal communication buses are well-integrated in the platform. These features express the perfect environment for secure, mixed-critical and real-time applications.

One issue concerning memory-intensive computations for use-cases, such as gesture recognition, is the limited memory capacity of the AURIX. There is in total 2728 kBytes static RAM (SRAM) available, which is divided into 2048 kBytes global extended memory and up to 240 kBytes scratchpad memory attached to each Tri-Core. Therefore, difficult image processing must be implemented in a highly optimized way. Due to this limitation, implementations of complex data processing algorithms are hardly feasible.

#### **Time-of-Flight** Camera

The camera evaluation kit used in the framework is an ongoing joint project of Infineon Technologies and PMDTechnologies. The camera system is Infineon's IRS10x0C Evaluation Kit that features the 3D image sensor IRS10x0C, as shown in [Inf13]. The ToF-based camera can be used in consumer electronics as well as in critical applications, such as automotive domain and robotics. It features a flexible setup which consists of a LED-based illumination unit and a sensor System-on-Chip (SoC). The evaluation board features different external interface, for example parallel interface and CSI-2, and allows access to important signals of the image sensor. Some characteristics are the resolution of up to 100k pixels, a maximum frame rate of up to 100 FPS and a modulation frequency of maximum 100 MHz. Furthermore, robustness during darkness and full sunlight is given by implementing suppression of background illumination on the sensor.

The camera is configured as followed: image resolution is set to  $160 \ge 120$  pixels, 12 Bits are transmitted per pixel and 4 phases are measured with an exposure time of 1 ms. The output, processed on the AURIX, consists of a 16-Bit depth and 8-Bit amplitude image.

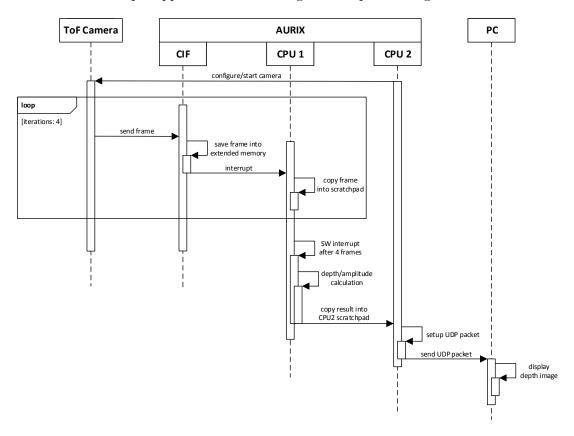

## 2.3.2 Image Processing

The framework computes the depth data from the raw data, transmitted from the camera sensor, by implementing several steps of a generic ToF processing pipeline. A use-case in the automotive domain can be implemented, for example, interior monitoring. Due to the memory and performance restrictions of the AURIX, only the necessary steps of the ToF processing algorithm are implemented. In detail, only one modulation frequency is used, post-processing, such as filter, analysis, Cartesian coordinate conversions, are omitted and only a minimum of systematic error removal is carried out.

In order to clearly illustrate the interaction of the different components, a simplified sequence diagram is depicted in Figure 2.18. The data processing steps of one full calculation of a depth/amplitude image, including the start of the system, are shown. An optional host PC is connected over Ethernet with the AURIX evaluation board. The

calculated data is transferred via User Datagram Protocol (UDP) to the PC to display a live-stream in a simple application or to debug the computed images.

Figure 2.18: Sequence diagram of the current system [DFH<sup>+</sup>15] (with changes).

On a reset of the AURIX, the processing platform is started. At first CPU 2 configures the ToF camera over the Inter Integrate Circuit (I2C) interface, and the camera interface (CIF) is activated. Therefore, a system reset of the camera evaluation board is done and the configuration stored on the AURIX is sent. After sending the start signal, the image transmission is started. The image stream is received on the AURIX via the parallel interface and pushed from the CIF module into the extended memory.

After the transmission of one raw frame, an interrupt is triggered. Upon this event, CPU 1 copies the frame from the extended memory in its scratchpad memory. These processing steps are repeated four times resulting in a software interrupt thrown by CPU 1 to start data computation. The calculation is efficiently implemented and results in a phase and amplitude image. The images are stored in its own scratchpad memory. After the execution of the ToF algorithm, the phase and amplitude image are copied to the scratchpad memory of CPU 2 by using DMA.

After finishing computation and copy operation, an interrupt is thrown by CPU 2, signaling that the results can be further processed. On this core, the transmission to the host PC for display purposes is carried out. A UDP stack is implemented in order to send the data via the network interface. Hence, multiple UDP packets of the phase image

#### 2.3. EXISTING FRAMEWORK

and amplitude image are created and transmitted. Because one single UDP packet is too small to transmit the complete result, the data has to be divided and provided with some metadata. With a simple application, the calculated data is viewed as a live-stream and analyzed.

The PC is used to simulate a real system that can react on the use-case events generated on the AURIX. For instance, a human detection system can be implemented on CPU 3. If a person sits on a seat without a fastened seat belt, an event will be thrown and the car will be notified to alert the passengers with an acoustic signal.

## 2.3.3 Results

The timing results of the work are presented in Table 2.1. Due to an exposure time of 1 ms, it requires 4 ms to gather the raw data of four measurements. It takes a further 3.4 ms to transfer the four images from the extended memory into the scratchpad. In addition, it takes 3.25 ms to perform the ToF processing and saving the data into the scratchpad of CPU 2. These results take up a total time of 12.5 ms, which includes some overhead timing to compute a depth and amplitude image. Therefore, the frame rate of the camera can be set to a maximum of 80 FPS. The depth (16 Bits/pixel) and amplitude (8 Bits/pixel) images take up 57,600 Bytes in total. The memory results are shown in detail in Table 2.2. For the computation of the depth and amplitude images the equations 2.7 and 2.8 are efficiently implemented. Thus, the results meet the predefined accuracy requirements for the use-case.

$$\varphi = \arctan\left(\frac{A_{270^{\circ}} - A_{90^{\circ}}}{A_{0^{\circ}} - A_{180^{\circ}}}\right)$$

(2.7)

$$A = \frac{\sqrt{(A_{270^{\circ}} - A_{90^{\circ}})^2 + (A_{0^{\circ}} + A_{180^{\circ}})^2}}{2}$$

(2.8)

The conclusion of this work is a robust multi-core ToF framework for mixed-critical applications in the automotive domain. The processing is efficiently performed to provide a frame rate of 80 FPS. Consideration of functional safety, such as the ISO 26262 standard, is also fulfilled. As future work, a hardware accelerator can be integrated into the framework to outsource performance-intensive calculations and to have more free resources available for use-case applications on the AURIX.

OperationTime[ms]Exposure Time and Raw Data Acquisition4Raw Data DMA Transfers3.4Phase and Amplitude Calculations3.25Total (including Overhead Timing)12.5

Table 2.1: Timing results of the ToF framework [DFH<sup>+</sup>15].

| Memory Description                        | # [Bytes] |

|-------------------------------------------|-----------|

| Raw Data in Extended Memory               | 153600    |

| CPU 1 Scratchpad Raw Data Memory          | 115200    |

| CPU 1 Scratchpad Phase and Amplitude Data | 0         |

| CPU 2 Scratchpad Phase and Amplitude Data | 57600     |

Table 2.2: Memory results of the ToF framework [DFH<sup>+</sup>15].

## 2.3.4 Limitations

One of the major challenges is the memory limitation of the AURIX. The complete amount of internal memory is 2728 kBytes of SRAM, which is divided into 2048 kBytes of extended memory and three times up to 240 kBytes of scratchpad memory allocated to each CPU. In order to compare this given condition with the memory used in practice, the configuration of the camera has to be considered.

The image resolution of the chosen configuration is  $160 \times 120$  pixels (16 Bits/pixel), and for a computed distance image four raw measurements are necessary. Due to this setup, the memory needed for one image calculation is shown in Equation 2.9. For four raw frames around 115 kBytes of memory is needed. As a result, the scratchpad memory will be almost half full if the complete raw data is saved for further computation. It is not possible to save four frames with the maximum image size of the camera system, which is approximately 100k pixels. Furthermore, pre-processing (e.g., averaging) that uses higher amount of images, is not feasible because only a small number of frames can be stored.

$$memory_{frames} = image_{rows} \cdot image_{columns} \cdot memory_{pixel} \cdot \#frames$$

= 120 \cdot 160 \cdot 12 bit \cdot 4

= 115200 Byte (2.9)

Another limitation is the computation power of the automotive SoC. The time needed for calculation of the phase and amplitude calculation is 3.25 ms. As the computation is in software, and not performed in parallel to the receive logic, it is completely added to the total time (raw data acquisition, DMA transfers and calculation). By keeping in mind that the implemented algorithm only calculates the phase and amplitude without any systematic error correction and further processing, like filters, the total time would be largely increased by adding an error correction consisting of many operations. It is possible to involve additional CPUs, but for the use of another core, the data has to be copied into its scratchpad memory. Thus, the performance in terms of latency will be decreased.

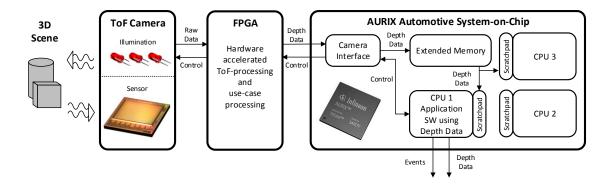

Finally, due to the mentioned memory and performance limitations, it is not possible to implement challenging use-cases, such as gesture recognition, on the AURIX. Thus, the interest in a new hardware-accelerated ToF processing platform, with a sufficient highspeed memory, is raised.

# Chapter 3

# Design

The focus of this chapter is to provide the design of the new system. The architectures and interactions are presented in a top-down approach. Therefore, the requirements are derived from the already described existing framework and its limitations. In addition, the ToF processing algorithm is introduced and the proposed High Level Synthesis design decisions are explained.

# 3.1 Requirements

The main aim of this master's thesis is the creation of a flexible and fast Time-of-Flight processing platform. Following requirements for the platform are as specified:

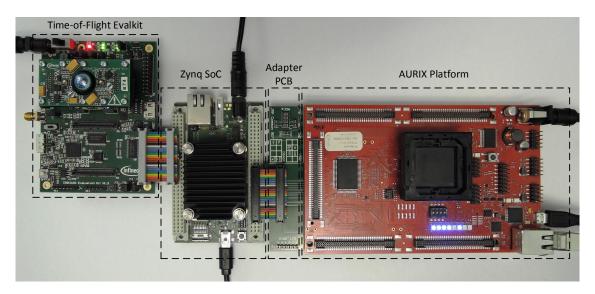

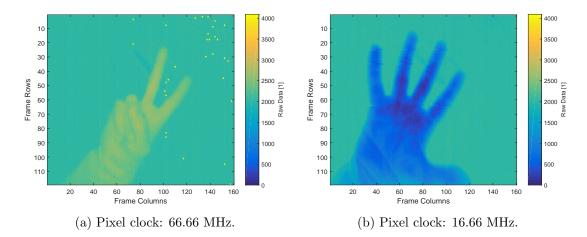

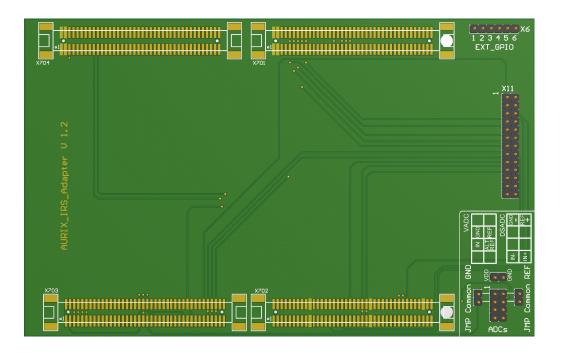

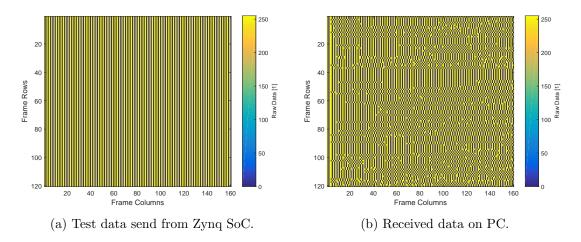

## • HW-accelerated Computation