Thomas Hinterkircher, BSc

# **Direct3D Shader Crosscompiler**

# MASTER'S THESIS

to achieve the university degree of

Diplom-Ingenieur

Master's degree programme: Computer Science

submitted to

# Graz University of Technology

Supervisor

Univ.-Prof. Dipl.-Ing. Dr.techn. Dieter Schmalstieg

Institute for Computer Graphics and Knowledge Visualization Head: Univ.-Prof. Dipl.-Ing. Dr.techn. Dieter Schmalstieg

> Co-Supervisor Dipl.-Ing. Michael Kenzel BSc

> > Graz, März 2018

# AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present master's thesis.

Date

Signature

# Abstract

In recent developments, GPGPU technologies have become flexible enough to make GPU-based software renderers feasible. Popular computer graphics libraries and increasing demands of developers and artists have originally driven the move towards programmable GPUs, but do still rely on dedicated hardware for some of the functionality, such as rasterization, depth testing or blending. However, unlike GPGPU frameworks, a specialized shading language is used for programmable stages (shaders) in the rendering pipeline. Providing a compatible graphics API with an underlying software implementation requires means of executing those shaders.

In this master's thesis, a program to compile Direct<sub>3</sub>D shaders to CUDA device code has been developed. The input language is not HLSL, a shading language designed for Direct<sub>3</sub>D, but a driver-independent low-level intermediate binary format produced by Microsoft's HLSL compiler. This same form is also used in the Direct<sub>3</sub>D API, making it a requirement for sufficient compatibility. For each shader, a CUDA unit containing C++ or PTX code is produced, which can later be linked statically or at runtime with a software renderer.

# Contents

| stract                            | iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.1. Shaders in Computer Graphics | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                   | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                   | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                   | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.3.4. Shader to GPGPU Compiler   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Related Work                      | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1. Shader Compilers             | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Direct3D Shader Format            | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1. Structure                    | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.3. Hull Shaders                 | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| System Design                     | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | 1.2. Shader Programming versus GPGPU Programming         1.3. Possible Implementations         1.3.1. Manual Translation         1.3.2. CUDA Graphics Interoperability         1.3.3. GPU-side Interpreter         1.3.4. Shader to GPGPU Compiler         1.3.4. Shader to GPGPU Compiler         2.1. Shader Compilers         2.2. Code generators         2.3. Debugging and Instrumentation Tools         2.4. Software Renderering on GPUs         2.5. Shader Models and Instruction Set         3.6. Hull Shaders         3.7. Hull Shaders         3.8. Hull Shaders         4.1. Program Structure         4.2. Phases         4.2.1. Front End and Shader Code Representation         4.2.3. Back End |

## Contents

|     | 4.4. Reconstructing Type Information                                                                           | 32                               |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|

| 5.  | Back-End Implementation5.1. Name mangling5.2. Code Generator5.3. Example: Translation of a complex instruction | 39                               |  |  |  |

| 6.  | Results         6.1.       Test Environment                                                                    | 50                               |  |  |  |

| 7.  | . Conclusion 5                                                                                                 |                                  |  |  |  |

| Α.  | List of Abbreviations                                                                                          | 65                               |  |  |  |

| B.  | Direct3D Shader Instruction SetB.1. Declarations                                                               | 67<br>68<br>68<br>69<br>69<br>69 |  |  |  |

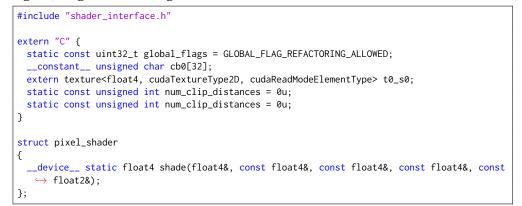

| С.  | Shader Translation Example                                                                                     | 71                               |  |  |  |

| Bil | bliography                                                                                                     | 77                               |  |  |  |

# **List of Figures**

| 1.1.         | Comparison of work flows for shader compilation               | 2        |

|--------------|---------------------------------------------------------------|----------|

| 3.1.<br>3.2. | Shader binary structure                                       | 17<br>19 |

| 3.2.         |                                                               | 19       |

| 4.1.         | Code tree example                                             | 24       |

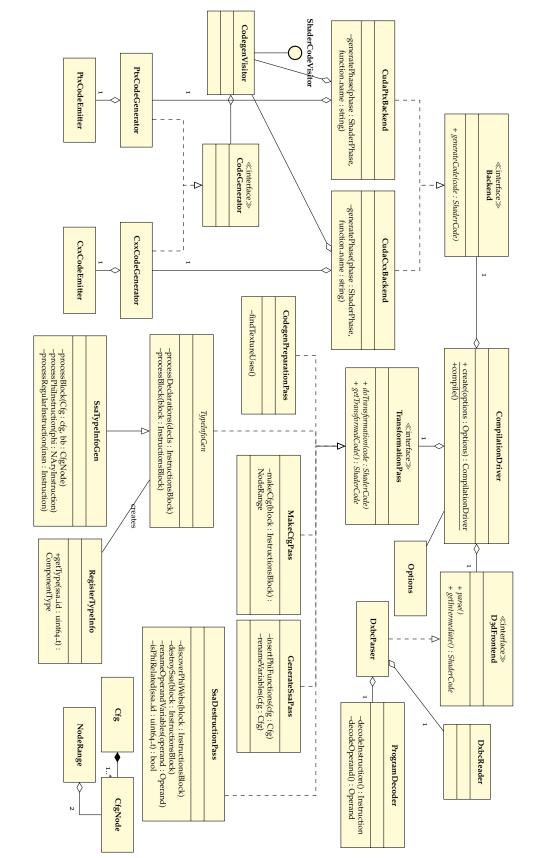

| 4.2.         | Class diagram                                                 | 28       |

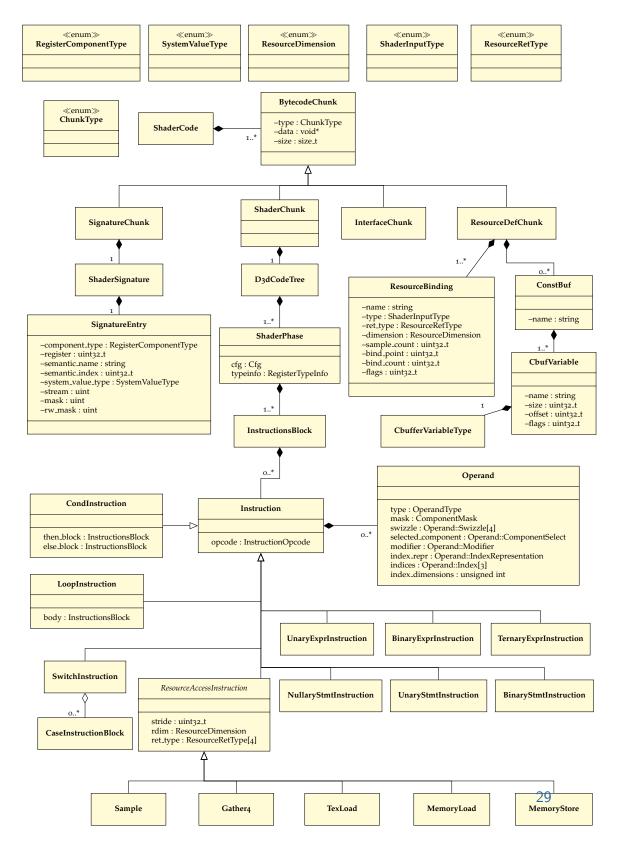

| 4.3.         | Class diagram of data structures representing the shader code | 29       |

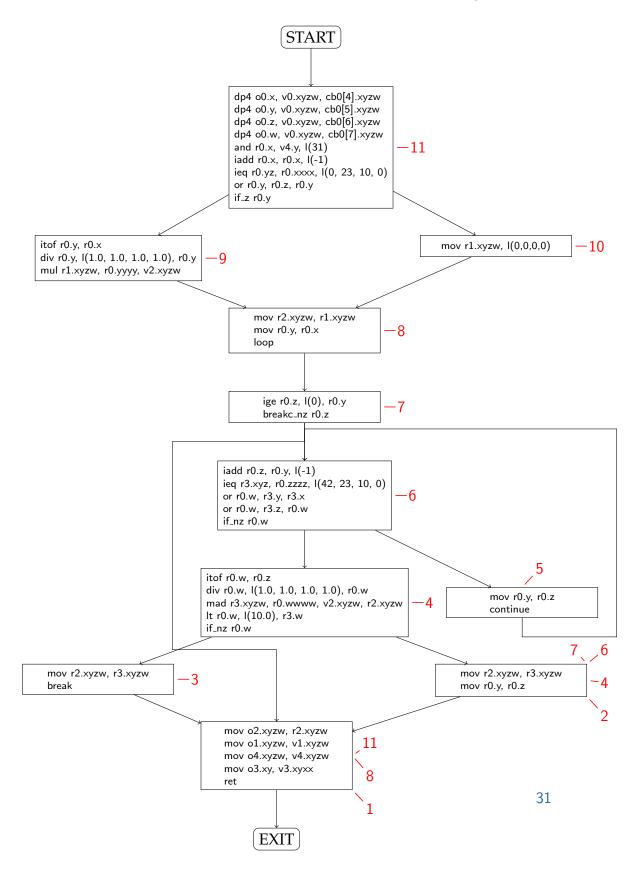

| 4.4.         | Example control-flow graph construction                       | 31       |

| 4.5.         | Shader assembly code in SSA form                              | 33       |

| 5.1.         | Name mangling example                                         | 38       |

|              | Translation of control-flow structures                        | 41       |

|              |                                                               |          |

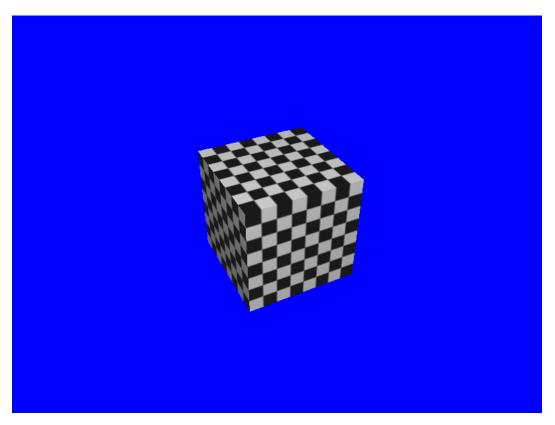

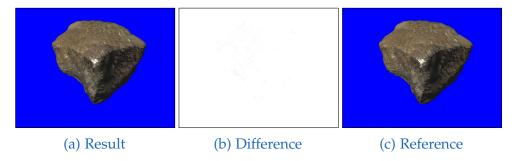

|              | Texturing example                                             | 53       |

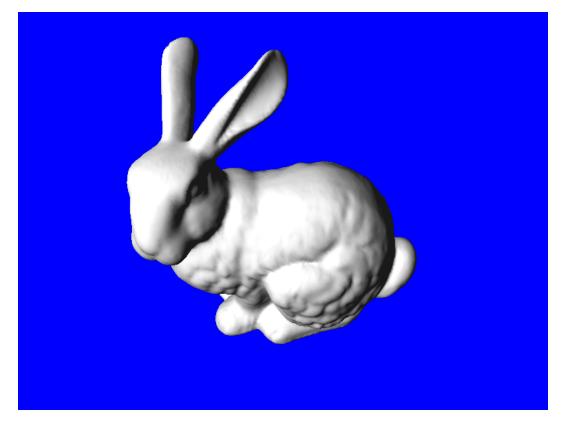

| 6.2.         | Diffuse lighting example                                      | 55       |

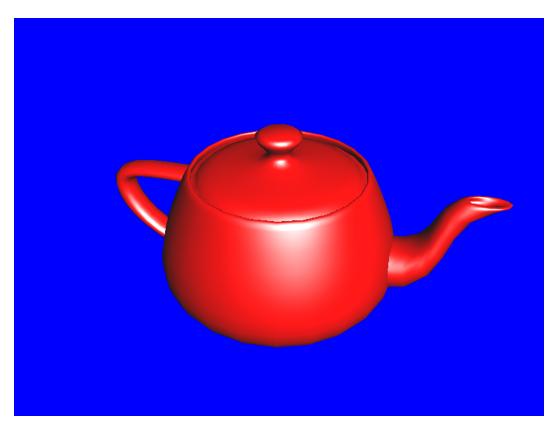

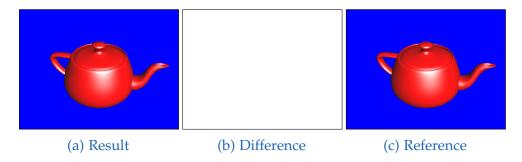

| 6.3.         | Specular lighting example                                     | 56       |

| 6.4.         | Specular lighting example                                     | 57       |

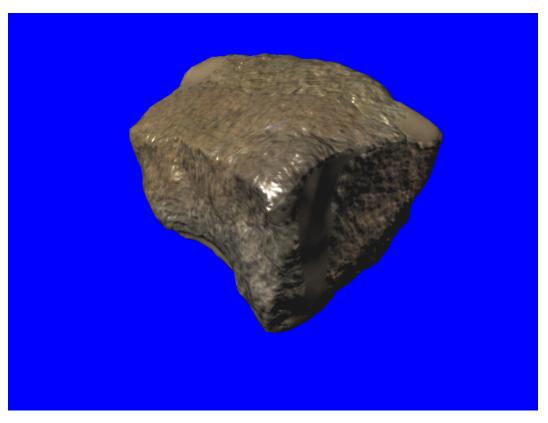

| 6.5.         |                                                               |          |

|              | plementation                                                  | 57       |

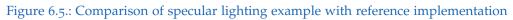

| 6.6.         | Comparison of diffuse lighting example with reference im-     |          |

|              | plementation                                                  | 58       |

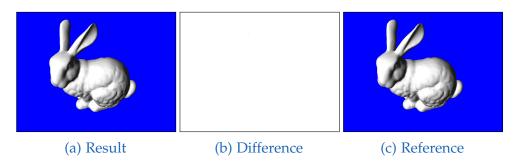

| 6.7.         | Comparison of texturing example with reference implemen-      |          |

|              | tation                                                        | 58       |

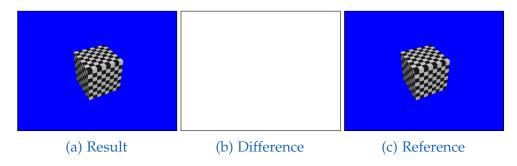

| 6.8.         | Comparison of texturing example with reference implemen-      |          |

|              | tation                                                        | 58       |

# 1. Introduction

Modern graphics application programming interfaces (APIs) provide means to implement some parts of their rendering pipeline with small custom programs to enhance flexibility and allow for a wide range of visual effects. Programs which execute a programmable section of a rendering pipeline are commonly referred to as *shaders* and are usually written in a specialized *shading language*. Graphics processing units (GPUs) are capable of running many shader instances in parallel to accelerate the rendering process. To utilize those computational capabilities in applications outside of computer graphics, general-purpose GPU (GPGPU) frameworks have been developed, such as OpenCL or NVidia CUDA.

Using these technologies, a GPGPU-based software rendering pipeline is being developed in an ongoing research project. The goal is to evaluate new rendering algorithms on real application data that was acquired by recording all calls to the Direct<sub>3</sub>D API. The graphics pipeline used by Direct<sub>3</sub>D comprises a combination of fixed-function and programmable stages (Blythe, 2006). GPUs often contain dedicated hardware to implement some of the fixed-function stages efficiently. Application programmers have limited control over those parts of the pipeline. Replacing the fixedfunction stages with GPU-side programs in CUDA is a major objective of the research. However, for the correct interpretation of input data, the evaluation of programmable stages has become essential for state-of-the-art real-time graphics. In order to make an implementation compatible, shaders of the same format as used by Direct<sub>3</sub>D need to be executed. Features for interoperability with graphics APIs exist for CUDA (NVIDIA Corporation, 2017a) and OpenCL (The Khronos Group, 2010; Houston and Cameron, 2010). However, such features are currently limited to sharing resources between graphics and GPGPU implementations, but no executable code in either source or compiled binary form. For these reasons, a program to

#### 1. Introduction

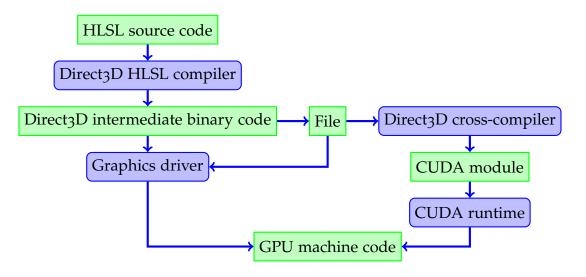

Figure 1.1.: Comparison of work flows for shader compilation

automatically compile Direct<sub>3</sub>D shaders to CUDA-compatible code has been developed in this master thesis. In the generated code, the functionality of a shader will be represented by a function performing the same task in CUDA<sup>1</sup>. As shown in figure 1.1, shaders are translated from an intermediate form instead of the original source code, which is not always included in applications using Direct<sub>3</sub>D.

# 1.1. Shaders in Computer Graphics

Frequently, controlling a rendering system through a set of configuration parameters is too restricting for a programmer or an artist. To overcome such limitations, the operation to be performed by the renderer may be specified using a programming language, instead of configuring fixed functionality. Depending on the context, different parts of the rendering process are feasible to be implemented using shaders. A very common application for shaders is to calculate the lighting or color of a point on a surface.

<sup>&</sup>lt;sup>1</sup>An exception is the hull shader stage, where parts of the same shader may run in parallel

#### 1.1. Shaders in Computer Graphics

Shading languages often supply domain-specific features integrated into a general-purpose language syntax. For example, special data types for vectors and matrices are usually part of the language instead of being implemented as user-defined types. Texture samplers, images or atomic types are also often provided as built-in types. Syntactic constructs designed for interaction with fixed-function pipeline stages are common as well, such as syntax to specify the binary interface of a shader, or attributes containing meta-information that are interpreted by the renderer.

In the real-time computer graphics library OpenGL (Segal and Kurt Akeley, 2016), extensions supported vertex and fragment shaders written in an assembly language (Beretta, 2013; K. Akeley, 2002), as well as earlier and more limited forms of programmability, before the OpenGL Shading Language (GLSL; Kessenich, Baldwin, and Rost, (2016)) was introduced. Similarly, in Microsoft Direct<sub>3</sub>D shaders are programmed using the High Level Shading Language (HLSL). Cg (Mark, Glanville, et al., 2003) is another shading language intended for real-time rendering, developed by NVidia and Microsoft, which is intended to be compatible with both Direct3D and OpenGL. The Vulkan graphics API (The Khronos Vulkan Working Group, 2017) uses a lower-level intermediate representation for shaders instead of a specific programming language; shading languages are not part of its specification. This intermediate form, called Standard Portable Intermediate Representation (SPIR; Kessenich, Ourial, and Krisch, (2017)), is intended as a format for both shaders and compute kernels (see also 1.2). Other shading languages for non-real-time rendering exist as well, such as the Open Shading Language (Gritz, 2016) or the RenderMan Shading Language (Hanrahan and Lawson, 1990).

As of now, multiple types of shaders are used by the prominent real-time graphics libraries OpenGL and Direct<sub>3</sub>D, making a significant portion of their graphics pipelines programmable. Vertex shaders generally implement a transformative step for vertex data before it is assembled into primitives. Typical transformations include, for example, the conversion between co-ordinate systems, or a procedure required for skeletal animation called *skinning*.

Pixel shaders control the color of a rasterized fragment. However, pixel shader output is treated in an abstract manner and may, especially in the

#### 1. Introduction

case of multi-pass rendering, represent arbitrary data other than colors. Since the appearance of those two shader types, more recent developments have introduced additional types of shaders.

Geometry shaders are an optional pipeline stage that support programmatic access to geometric primitives, such as triangles or points, and can output one or more primitives per input primitive. The generation of new primitives has in many cases been superseded by the use of tessellation shaders.

Tessellation is programmable using two types of shaders, one to control how finely a patch should be subdivided along each edge and on the inside, and one to compute attributes of the vertices generated by the tessellator. In OpenGL, those are called *Tessellation Control Shaders* and *Tessellation Evaluation Shaders*, while in Direct<sub>3</sub>D the terms *Hull Shader* and *Domain Shader* are used, respectively.

Compute shaders are a step towards general-purpose computing on the GPU within a graphics API while not requiring an external library. The same shading language as for other shader types is used. However, there are some language extensions currently specific to compute shaders, such as shared memory and new synchronization primitives.

Although real-time graphics APIs intend shaders to be compiled for execution on a GPU, other implementations are conceivable. Reasons to have a shader implementation target the CPU, either by a compiler or interpreter, would be to remove the dependency on dedicated graphics hardware or to enhance the debugging experience.

While the OpenGL specification only defines the source language for shaders, Direct<sub>3</sub>D also specifies the intermediate representation HLSL programs will be compiled to, which graphics drivers then translate into executable code during runtime. The intermediate representation of Direct<sub>3</sub>D shaders is the input format for this master thesis' shader cross-compiler and will be described in more detail in chapter <u>3</u>.

# 1.2. Shader Programming versus GPGPU Programming

By generalizing the programming model beyond the requirements of graphics programming, GPGPU libraries have introduced some differences to the conventional shader programming model, which will be investigated in this section. Terminology is different for GPGPU programming, since there is not necessarily a connection to computer graphics. Programs are consequently called *kernels* instead of *shaders*. Input and output data are accessed via arrays of arbitrary data types, residing in the main memory of a GPU. This stands in contrast to shaders that operate on data streams where elements represent vertices, control points, patches, primitives or fragments.

For shaders in a rendering pipeline, parallelism is implicit. Programmable stages are designed in a way that parallel execution is possible and graphics drivers will attempt to run multiple shaders instances in parallel, but the parallelization is not controlled by the programmer. Instead, drawing commands are issued by the user of a graphics API, and input data such as vertex attributes or interpolated fragment data is automatically assigned to shader instances. On the other hand, for compute kernels, a programmer explicitly invokes a number of instances (threads), which in case of CUDA or OpenCL kernels or compute shader instances are organized in a grid of up to 3 dimensions, that is, each thread has its own spatial index. Input and output data are passed from and to the kernels as an array containing all data, each thread then uses its coordinates within the grid to calculate the address for reading or writing data values.

Shading languages have been described in the previous sections. In case of OpenCL or CUDA, kernels are written in dialects of existing languages, such as C, C++ or FORTRAN. Compilation of kernels can occur ahead of time or at runtime when executing the host program (NVIDIA Corporation, 2017b; NVIDIA Corporation, 2017c). Additionally, CUDA makes use of a common intermediate language similar to assembly code, called "PTX" short for *parallel thread execution* (NVIDIA Corporation, 2017e). Both CUDA and OpenCL implementations provide a runtime library for compiling or loading kernels, managing memory and other objects. No dependency on

#### 1. Introduction

| Method                   | Impl. Effort | Scalability | Ease of Use | Performance |

|--------------------------|--------------|-------------|-------------|-------------|

| Manual<br>Translation    | None         | Bad         | Bad         | High        |

| Graphics In-<br>terop.   | Medium       | Good        | Medium      | Low         |

| GPU-based<br>Interpreter | High         | Good        | Good        | Low         |

| Compile to<br>CUDA       | High         | Good        | Good        | High        |

Table 1.1.: Overview of possible implementations

graphics libraries exist, although using both a graphics and a compute library in the same program is possible, with some interoperability features being provided by the compute API.

# **1.3.** Possible Implementations

Several approaches to the portability problem have been considered and will be described in this section. It should also be discussed if the problem can be solved using libraries or other existing infrastructure. Graphics applications, especially game engines, frequently use a large number of different shaders or select between a variety of shading techniques in the same shader ("Ubershaders"). Therefore, an important objective is that the solution scales with the number of shaders used, and also with increasing complexity of a single shader. Table 1.1 gives an overview of all considered approaches, as well as an assessment according to the applied selection criteria.

### 1.3.1. Manual Translation

For each Direct<sub>3</sub>D shader in use by the original application, a shading function is written by hand to reproduce the behavior of the shader. If

#### 1.3. Possible Implementations

the HLSL source is not available, the shader has to be translated from its disassembly.

- **Effort** Since no additional program or component has to be implemented, the up-front effort is low. However, it is proportional to the number of shaders required.

- **Advantages** If the rendered scene is not complex, this approach is the most straight-forward.

- **Disadvantages** The effort for rendering complex scenes is high. Additionally, the translation is prone to human errors.

- **Applicability** Scalability and inflexibility are major drawbacks to this method. Other approaches are preferable for a general purpose software renderer.

## 1.3.2. CUDA Graphics Interoperability

CUDA is able to share resources such as buffers or textures with the graphics libraries OpenGL and Direct<sub>3</sub>D. However, shaders can still only be launched from Direct<sub>3</sub>D and use a different programming model, as described in section 1.2. In order to run a shader, a rendering call has to be issued. Direct<sub>3</sub>D only provides access to the output of shader stages through an optional stream-output stage or texture render targets (Microsoft Corporation, 2018). Pass-through shaders are required to obtain the results of other stages in the pipeline for use in CUDA.

- **Effort** Routines to execute shader stages and obtain the results without other side-effects need to be created once. Pass-through shaders need to be written or automatically generated for every different shader signature (see also section 3.1).

- **Advantages** Since Direct<sub>3</sub>D is used to run the shaders, correctness of shader execution is ensured by the graphics driver.

- **Disadvantages** Some pipeline stages will be run with a pass-through configuration redundantly, possibly multiple times, to isolate the desired shader stage. Performance is likely to be negatively affected by this. Furthermore, a dependency on Direct<sub>3</sub>D is introduced by this method.

#### 1. Introduction

**Applicability** While the amount of manual work does not increase with complexity, the performance implications are a drawback. The Direct<sub>3</sub>D rendering pipeline is used in a way it is not intended for, leaving this approach to be considered more of a work-around than a solution.

#### **1.3.3. GPU-side Interpreter**

With the high degree of programming flexibility in modern GPUs, implementing an interpreter running as a compute kernel becomes possible. Some pre-processing might be required for the Direct<sub>3</sub>D intermediate binary format. Interpreting instructions introduces some additional data-dependent branching. However, threads in the same warp would interpret the same shader, making these conditional branches mostly uniform and not inherently introduce blocking times in addition to the interpreter overhead.

- **Effort** The effort for implementation and testing is estimated to be about the same as implementing a compiler for the shaders.

- **Advantages** With an interpreter, any shader can be used at runtime by the renderer. With a compiler, every shader that participates in producing a frame has to be identified and translated in preparation of the rendering process.

- **Disadvantages** Despite most branching being uniform, the interpreter would cause considerable slowdown of shader execution.

- **Applicability** This approach is feasible, but the practical advantages over using a compiler instead are unclear.

#### 1.3.4. Shader to GPGPU Compiler

Shaders are automatically translated to one or more shading functions in a programming language usable within CUDA. In order to make the generated code compatible with C++, the most suitable target languages are C, C++ and PTX. Additionally, it is possible to generate code in the internal representation of NVidia's CUDA compiler, NVVM, which is derived from the intermediate representation of the LLVM compiler infrastructure

#### 1.3. Possible Implementations

(NVIDIA Corporation, 2017d). A PTX back-end for NVVM code is available in the CUDA toolkit.

- **Effort** Implementation and testing cause a considerable amount of effort up front, but allows the use of any shader in a CUDA-based renderer in an automated way afterwards.

- **Advantages** The overhead compared to running the original shader is very low.

- **Disadvantages** It is necessary to work around a few limitations of the CUDA API. Those limitations are described in more detail in chapter 5 and section 6.2.

- **Applicability** Scalability and execution performance make this approach well suited for software rendering. Any of the mentioned target languages would suffice.

From the options presented, a compiler for automatic translation to CUDA has been chosen. Its strength lies in the run-time performance of ported shaders, since no inherent slow-down exists. This makes it possible to evaluate algorithms designed for interactive rendering speed. Taking the high scalability and simple workflow into account, it becomes the most viable option, despite the initial effort required for its implementation.

# 2. Related Work

Automatic code generation for shaders has been a subject of interest for some time, in order to make authoring of shaders easier and to make different shading languages or graphics libraries more interchangeable. This chapter will give an overview of other existing work on this subject. Furthermore, some related work has been done regarding the run-time analysis or emulation of shaders or compute kernels, with some similarities to this project.

# 2.1. Shader Compilers

In addition to the shading languages described in 1.1, several other GPU programming systems have been created to exploit the programmability of modern graphics processors. The Cg shading language (Mark, Glanville, et al., 2003) along with its host runtime library aims to unify GPU programming across different 3D graphics APIs and operating systems. Its implementation employs a compiler using assembly code as its target language, either off-line or during application runtime. While still targeting GPUs as a platform, the Cg compiler aims at different goals, and the generated code is similar to the Direct3D bytecode used as a source language here. Furthermore, Cg is no longer actively developed, and it is not possible for end users to extend the Cg compiler with new target languages.

In Mark and Proudfoot, (2001), a compiler for the Stanford Real-time Shading Language (Proudfoot et al., 2001), targeting low-level shader programming interfaces (the NV\_vertex\_program and NV\_register\_combiners OpenGL extensions) is described. Pipeline stages are not programmed directly, but instead vertex and fragment programs are derived from a single

#### 2. Related Work

shader that specifies the frequency at which values are computed. This master thesis, in comparison, intends to port shaders bound to a specific stage of the rendering pipeline to CUDA. Source and target languages are different as well.

Peercy et al., (2000) achieves programmable shading by translating shaders written in a newly developed shading language to a multi-pass rendering procedure in OpenGL, treating each pass as one or more primitive operations of the shader program. At the time of its publication, programmable shading was not widely available in real-time graphics APIs. While modern graphics processors offer a high degree of programming freedom that is exploited by HLSL and the Direct<sub>3</sub>D intermediate code, it is useful to keep in mind that shaders can also be mapped to other programming models, in case direct translation to GPU device code becomes difficult.

The PixelFlow system (Olano and Lastra, 1998) was one of the first programmable real-time renderers. Shaders are written in *pfman*, a programming language similar to the RenderMan shading language. It is implemented with an optimizing compiler generating code for a dedicated SIMD computer. The *pfman* compiler differs from this work in its specialization on the PixelFlow target platform and *pfman* shading language. Due to its publication time frame, rendering pipeline stages other than pixel shaders are not programmable.

An alternative shading language for the Direct<sub>3</sub>D API called Spark (Foley, 2012) aims at managing complex shaders through modularization. The per-stage programming model is abstracted so that effects involving multiple stages of the rendering pipeline can easily be added while keeping the implementation encapsulated and in one place. Spark source code is compiled to a set of HLSL shaders along with C++ classes for the client to configure the pipeline and initiate the rendering process.

As part of its Windows API compatibility layer, the WINE software package (Julliard, 2017) provides a compiler for Direct<sub>3</sub>D shaders that translates their binary form to GLSL. Some 3D graphics engines are capable of compiling shaders written in one shading language to another, in order to be compatible with many platforms. The Unreal Engine provides a library to translate HLSL shaders to GLSL (Epic Games, Inc., 2017). Unity can generate GLSL code from HLSL, Cg or Direct<sub>3</sub>D bytecode (Unity Technologies,

2017). While conceptually similar, those tools aim for compatibility with a different graphics API instead of porting shaders to a GPGPU platform. In Rhodin, 2010, a PTX back-end for an LLVM-based shader compiler for a custom shading language is developed. A shader compiler for functional programming was created by Elliott, (2004).

## 2.2. Code generators

Automatic generation of code for various shading languages has been employed frequently in tools that simplify the editing of shading functions. Various forms of visual shader editors exist already, commonly using different types of shade trees (Cook, 1984). For instance, Jensen et al., (2007) combines a shade tree editor with an optimizing Cg back-end. In McGuire et al., (2006), a program to create shade trees on a higher abstraction level is introduced. McCool et al. developed a C++ framework to perform algebraic operations on shaders, with the ability to generate shader code from recorded calls (M. McCool et al., 2004), based on the Sh shader metaprogramming language (M. D. McCool, Qin, and Popa, 2002). Similar to the program created for this master's thesis, those shader editing tools implement automatic generation of the shading code, but starting from a different shader representation. Before GPGPU frameworks were common, Brook for GPUs (Buck et al., 2004) provided a means to use a GPU for arbitrary parallel computations. It provides a compiler that translates kernels into shader programs and a runtime API to abstract the usage of a graphics library (Direct<sub>3</sub>D or OpenGL) to execute the shaders through a rendering call. An alternative CUDA module compiler targeting PTX assembly language was developed by Wu et al., (2016).

# 2.3. Debugging and Instrumentation Tools

For the purpose of debugging or software profiling, tools have been created which automatically manipulate shaders. Unlike this master's thesis, shaders are not translated to another target language, but the required parsing

#### 2. Related Work

and code generation poses some similarities. Strengert, Klein, and Ertl, (2007) developed a GLSL debugger that modifies shaders at source level, transparent to the user. The program "Total Recall" (Sharif and Lee, 2008) aids graphics debugging by instrumenting Direct<sub>3</sub>D shaders to record their behavior and subsequent emulation of specific shader execution instances on the CPU. In Duca et al., (2005), another debugger which uses automatic shader instrumentation has been created.

# 2.4. Software Renderering on GPUs

Existing software rendering pipelines are good examples of applications motivating the automatic translation of shaders. Implementing the entire renderer in software overcomes the limitations imposed on customizability by fixed-function parts of common real-time graphics libraries.

FreePipe (Liu et al., 2010) implements a fully programmable rendering pipeline in CUDA with a structure similar to OpenGL or Direct<sub>3</sub>D.

CUDARaster (Laine and Karras, 2011) implements a graphics pipeline in CUDA with emphasis on achieving high performance while following the same rules for rasterization and rendering order as fixed-function units of graphics processors.

Piko (Patney et al., 2015) is a framework to synthesize implementations of arbitrary graphics pipelines with programmable shading based on a description in a domain-specific programming language similar to C++. It uses LLVM to generate target code for CUDA GPUs or multi-core CPUs.

A complete implementation of a Direct<sub>3</sub>D driver needs to translate the shader binaries for its target architecture. This is true even if the API is implemented without a system-level component but entirely as a user-space library on top of CUDA. Such a system, intended to evaluate experimental rendering algorithms on frame data captured from real-world graphics applications, is the target platform of the translator developed in this master's thesis.

# 3. Direct3D Shader Format

Shaders for the Direct<sub>3</sub>D API are authored in HLSL and compiled to a hardware-abstracted low-level binary format by Microsoft's HLSL compiler. The result is a program in an assembly language for a virtual GPU, as described in section 3.2. In earlier versions of Direct<sub>3</sub>D, it was possible for programmers to write shaders in that assembly language, but that option has been removed for recent versions. Graphics drivers will perform the final translation step to machine code at application runtime. Since the binary format is hardware independent, and the behavior is defined explicitly, it is possible for applications to use only shader binaries during deployment, and not ship the HLSL source code. Consequently, it is necessary to use this binary format instead of HLSL as the input language for this work, in order to be compatible with all Direct<sub>3</sub>D shaders.

# 3.1. Structure

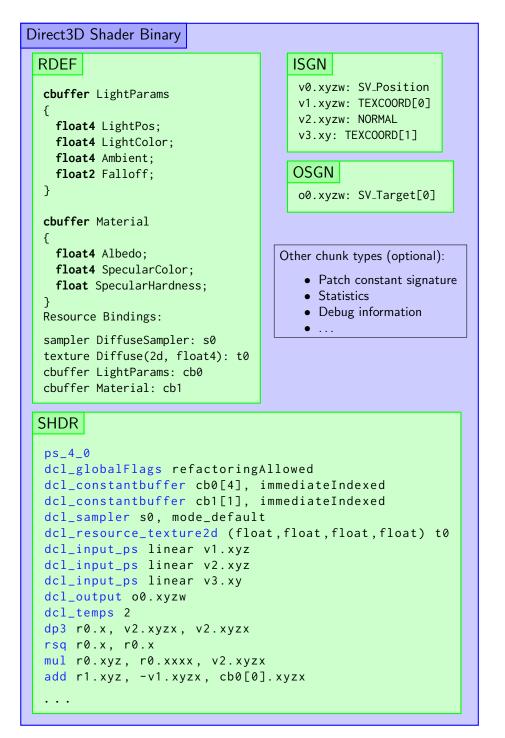

Direct<sub>3</sub>D shader binaries are organized into self-contained "chunks", each describing a set of information needed for loading the shader. One type of those chunks contains the encoded shader program, others are for example the signatures of the shader or debug information. Signatures tell a graphics driver how to link different shader stages together, and which input or output variables have *system value semantics*, that is they are generated or interpreted by fixed-function graphics pipeline stages. Another important chunk type describes the data layout and binding information for shader resources, such as constant buffers, textures, generic buffer types or unordered access views (UAVs). Figure 3.1 gives a schematic view of the structure of shader binaries, using a pixel shader as an example. The remainder of this section focuses mostly on the contents of the shader code chunk, since this

#### 3. Direct3D Shader Format

representation of the program serves as the compiler's source language. Information encoded by other chunks is used to derive the public interface to the generated code, for example the signature of the shading function.

## **3.2. Shader Models and Instruction Set**

Direct<sub>3</sub>D defines *shader models* as an abstraction of graphics hardware to define required features of a GPU. They are used as a basis for the instruction set of Direct<sub>3</sub>D's intermediate code, an assembly language for a virtual graphics processor (Microsoft Corporation, 2017). The instruction set architecture can be classified as a load-store architecture with non-destructive operands. In general, instructions are orthogonal, except if the instruction operates on specific operand types, such as texturing instructions. One exception to this classification are constant buffer operands, which can be used as a source operand to almost every instruction.

Shader models use numbered registers as an abstraction of memory areas of real graphics hardware. Different types of operands, such as shader input and output or local variables are modeled as sets of registers, with each set using a separate numbering starting from o. In most cases a register refers to a vector with 4 components, each 32 bits in size; however some specialpurpose operand types are of different size. A register may also refer to an opaque type, such as textures, samplers, UAVs or shared memory buffers. All registers for opaque types have their own numbering as well. How the physical memory is allocated is not specified. Layout of the address space as well as ordering of concurrent memory accesses by shaders to shared resources is defined by the implementation.

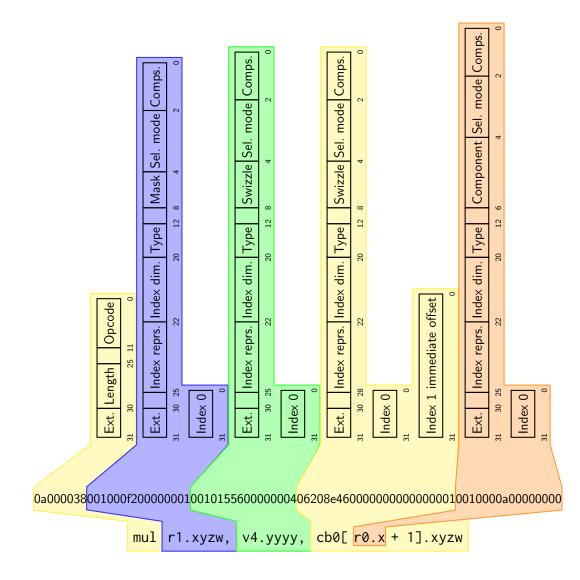

Instruction opcodes and operands are encoded using any number of 32-bit tokens, therefore the size of each whole instruction is always a multiple of 4 bytes; however their length varies widely. Every instruction generally consist of an opcode comprising one or more tokens, in some cases encoding additional instruction-specific information in the form of attributes or flags. Such additional data encoded in the opcode is present mostly for a group of instructions that serve as variable or attribute declarations. The opcode is followed by any number of operands. Since operands can encode 3.2. Shader Models and Instruction Set

Figure 3.1.: Shader binary structure. Note that the code makes up only part of the file contents. Chunk types are use the same abbreviated names as in the binary file. RDEF: Resource definitions, ISGN: Input signature, OSGN: Output signature, SHDR: Shader code 17

#### 3. Direct3D Shader Format

dynamic indexing of arrays, nested operands are possible. In that case, the encoded dynamic index will come after the array operand in the shader binary. Operands can take many different forms in Direct<sub>3</sub>D shader binaries. Vector components can be write-masked for destination operands while for source operands, component swizzle or selection of a single component as a scalar operand is possible. Additionally, different array indexing modes are supported using either constant or variable offsets or a combination of the two. An optional modifier may be applied to the operand that calculate the absolute numeric value or invert its sign. Instead of registers, operands may also contain immediate data in the form of one or four 32-bit values. A visualization of the instruction encoding is given by figure 3.2, showcasing a multiplication instruction with a temporary register as destination, an input register and a constant buffer operand as sources. The use of an additional operand for dynamic indexing is also shown.

Most instructions can be categorized as arithmetic, declarations, memory accesses or data copy, control flow or application specific instructions. Typical integer and floating-point arithmetic instructions are provided, with an optional modifier to clamp the result to the range [0,1] existing for many floating-point operations. Control flow is implemented as structured programming constructs, unlike most assembly or machine languages using conditional and unconditional jumps. For example, instructions to mark the beginning and end of conditional, loop or switch statements exist. All data objects used by the program require a declaration instruction to be present at the start of the program. These declarations abstract the details of memory allocation and therefore have no similarity to non-virtual computer architectures. Memory that is shared between shader instances is accessed using memory load and store or texturing instructions, or atomic operations. Other application-specific instructions include thread and memory barriers, geometry shader operations to emit vertices and finish primitives, screen-space derivative approximation instructions, or discarding pixels.

#### 3.2. Shader Models and Instruction Set

Figure 3.2.: Instruction encoding example. The instruction multiplies components of a dynamically indexed constant buffer vector with the y component of an input operand and stores the result in a temporary register.

#### 3. Direct3D Shader Format

# 3.3. Hull Shaders

Hull shaders are programmed as one pipeline stage, but independently compute output data for each control point as well as once per patch, called patch constant data. At minimum, the patch constant data contains all required tessellation factors for a patch. This computation of independent outputs allows for more parallelism than the amount exposed to shader programmers. Therefore, a hull shader contains multiple phases designed to possibly run with a different number of instances. A HLSL compiler can automatically generate the different phases from source code to maximize the amount of work that can be done in parallel (Ni et al., 2009, p. 24). Up to three different phases can exist in a single hull shader. The first phase is the control point phase, running once for each output control point. The other two phases are known as *fork phase* and *join phase*, and compute the patch constant data as well as tessellation factors along the edges and for the interior of a patch, respectively. All phases are contained in a single shader binary, with special instructions marking the start of each phase. In addition to phases, hull shaders have a declaration section for declarations common to phases, as well as setting up some configuration parameters for the tessellator.

# 4. System Design

Writing a compiler is generally a well understood task, for which many techniques have been thoroughly researched and are being applied in productive environments. In this case, the required source language and ensuing target languages somewhat reduce the implementation complexity. Most compilers are designed to accept a plain text source program written in a language described by a context-free or possibly even less restricted grammar. Working with a binary input format simplifies the parsing step, since no lexical analysis is required.

A three phase structure has been followed comprising a front end for parsing the shader binaries, back ends to generate PTX or C++ code or disassembly and a middle end operating on the internal representation of a shader. No optimization is performed when translating shaders, since the generated code will be subject to optimization done by the CUDA toolchain. In addition to translating the shader code, a C++ header declaring the interface to the shader is automatically derived for integrating the generated code in a CUDA application. Direct<sub>3</sub>D shader intermediate code does not carry explicit type information, but its instructions imply that their source and destination operands have a certain data type. Since both C++ and PTX as target language allow programming in a type-safe manner, type information is reconstructed based on the implied types of operands.

# 4.1. Program Structure

In the compiler's 3-phase implementation, the front-end is responsible for three related tasks. The chunks contained in a shader binary are parsed to obtain linkage and resource definition information, then the shader

#### 4. System Design

program embedded inside a program is decoded according to the instruction encoding described in chapter 3. In the third place, while decoding the shader, a tree structure is created that serves as the internal representation of the input program. This tree form simplifies PTX code generation and construction of a control flow graph. Other than the shader code itself, important chunks are the shader signatures and resource definitions. The former define the binary layout of input and output variables as well as the per-patch data for tessellation shaders, while resource definition chunks describe the contents of constant buffers and other shader resources. In order to allocate those resources in generated code and to provide an interface to the graphics pipeline implementation, the binary parser needs to recognize the resource definitions. Similarly, shader signatures determine the set of input and output parameters that need to be generated for a function implementing a shader stage or hull shader phase.

Operations performed in the middle phase typically have no control dependencies between each other. Therefore, the middle phase is implemented as a series of passes sharing a common interface. Each pass generally carries out a code transformation or computation of additional information about the shader. The passes are optional and are enabled based on requirements of the selected back-end and program invocation parameters. Most configurations require a control-flow graph to be created. The middle phase is also capable of converting the source program into static single assignment (SSA) form. Reconstructing type information for local variables operates on the SSA representation of shaders.

Code generation back-ends have been implemented for C++ and PTX as target languages. The program is also capable of disassembling the shader binary without code generation. For generating code, a visitor pattern operating on the code tree produced by the parser is used. A more detailed description of the back-end implementation is given in chapter 5.

# 4.2. Phases

Different translation targets, the disassembler functionality and other userspecified options lead to a variety of required behaviors for the compiler. The described structure of interchangeable modules is capable of adjusting to such variation. A driver class has been implemented that is responsible for instantiating a front-end and a back-end object and the required passes of the middle phase, and for guiding the compilation process.

## 4.2.1. Front End and Shader Code Representation

The frond-end for shader binaries has been separated into three components to break down the complexity of parsing the binary file format. First, lowlevel input methods are delegated to a separate class. Those input operations involve reading objects of primitive types, such as integers and character sequences, and following offsets for structures stored using pointer swizzling. The main parsing routines involve recognizing the different chunks of the program described earlier. Since the shader instruction encoding is essentially an additional binary format, a second class has been created for decoding the program. A hand-written recursive descent parser is used for both types of binary encodings found in shader files. Using a parser generator would be difficult with the use of pointer swizzling by the file format; furthermore, deriving the formal grammar of all chunk types and the instruction encoding would be a cumbersome task.

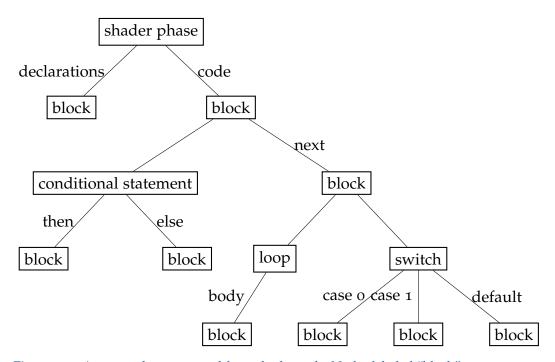

Both the instructions of a shader program and its tree structure are represented in the same class hierarchy. Most of those classes are an abstraction of a set of instructions which follow a common pattern, for example, a three operand instruction performing a binary operation or a texture or UAV memory access. Sequences of instructions without branching are contained by block objects, which share the same base class as the tree object hierarchy. The control flow instructions if\_z, if\_nz, loop and switch are implemented as subclasses that hold blocks of instructions the shader program may branch into, therefore forming a tree which resembles a syntax tree of a structured programming language. A visual example of such a tree can be found in figure 4.1. Since instruction operands have a complex structure, a self-contained operand class has been created instead of storing the encoding of operands directly within the instruction objects, therefore encapsulating the large number of possible operand forms and corresponding to the mostly orthogonal nature of the instruction set architecture.

## 4. System Design

Figure 4.1.: An example tree created from shader code. Nodes labeled "block" are sequences of instruction objects. Non-branching instructions that may be part of blocks have been omitted.

4.2. Phases

## 4.2.2. Middle End

Converting the programs to SSA form is a central responsibility of the middle phase. For one of the approaches implemented to derive type information, SSA form is a prerequisite. Three transformation pass subclasses are implemented to build the control flow graph (CFG), convert the shader code to SSA form and finally SSA destruction. The term "SSA destruction" commonly refers to the operation that removes the  $\Phi$ -functions and renames the arguments and return value of  $\Phi$ -functions to a common variable name, which is required for code generation. Deriving type information from the shader binary also uses the same interface. During that pass, a table is generated to associate each component of a temporary register with a basic type, such as integers or floating-point numbers.

Depending on the selected texturing mode, an additional renaming step for texture and sampler objects may be required. CUDA supports two different modes of accessing textures. In what is called *independent* texturing mode, texture objects are separated from various other controls, such as filtering and addressing modes, which are held in a sampler object. Textures and samplers may then be combined arbitrarily for sampling textures. Direct<sub>3</sub>D and HLSL always use textures this way. The other texturing mode, used by default in CUDA, is called *unified* mode and causes each texture object to contain a single sampler object to use in sampling instructions. In order to generate code in unified texturing mode, the transformation pass needs to detect all texture and sampler uses and rename the objects to a common texture object also containing the corresponding sampler state.

## 4.2.3. Back End

Both code generation back-ends are designed in an almost identical manner, since the main difference lies in what code needs to be generated for each instruction. Consequently, it is possible to share parts of the implementation between the back-ends. Per target, a subclass of the back-end interface is responsible for generating file-level declarations and boilerplate code, as well as orchestrating code generation for each shader function and the hull shader phases. A header file is generated for the externally visible names

#### 4. System Design

required to use the translated shader in a CUDA kernel. For generating code for a shader phase or function, both back-ends make use of a visitor class, which traverses the tree structure of the parsed code, and passes each instruction to a code generator class. A common base class is used for the code generators of both targets. An auxiliary class collects declaration instructions as they are visited, in order to simplify accessing the declaration object when referenced by an operand using its register number. The code generators each make use of another class that emits C++ statements or PTX assembly instructions, respectively. As a result, creating formatted textual output is separated from generating the declarations or statements.

# 4.3. Generating SSA Form

This section goes into detail about constructing a CFG for the shader and converting it to SSA. For the latter, a number of established algorithms exist that realize all necessary steps. Some considerations had to be made on how to integrate the changes from conversion to SSA into the existing shader code structures.

Some methods of generating the SSA form, including the chosen implementation, require a control flow graph to be created. The CFG is implemented as a class for storing per-node data, and another class to hold the set of node objects and implement the algorithms described in this section. A single CFG is generated per shader phase in hull shaders and for the main function otherwise. Since shader functions share registers with their caller and all call destinations can be statically determined, it is more sensible to insert edges to a function subgraph for calls than to create a different CFG for each function.

A rather simple algorithm to identify basic blocks and construct a CFG exists for code using only conditional and unconditional jump statements for control flow (Aho et al., 2007, pp. 525-516, 529). Such a format is common for intermediate code in compiler infrastructures. However, as mentioned previously, Direct<sub>3</sub>D shader code does not use jump instructions for control flow. To avoid creating a custom intermediate code format based on jumps, a different algorithm has been used to build the CFG.

The following control flow constructs are part of the shader intermediate code instruction set:

- Conditionals, using if\_z, if\_nz, else and endif

- Loops, using loop and endloop, as well as break and continue (all loops are terminated using break)

- Selection statements, using switch, case and default

- Function calls with late binding, using call and fcall (functions are denoted using a label instruction)

Constructing the CFG is essentially a depth-first search (DFS) on the code tree, with some additions to support the break and continue instructions present in some shaders. In order to set the correct nodes as successors, the

# Figure 4.2.: Class diagram

28

4. System Design

## 4.3. Generating SSA Form

Figure 4.3.: Class diagram of data structures representing the shader code

#### 4. System Design

current path of the DFS needs to be walked backwards to find the enclosing loop or switch block. The implementation uses a recursive function that generates the CFG for a branch of the program tree and, given as a block of instructions, returns a pair of references to the first and last node of the created CFG. After a recursive call for a branch, those nodes are required to correctly set successors of nodes depending on the control flow instruction that ends the given block. Figure 4.4 gives an example of this recursive construction leading up to the complete graph.

In the case of conditional statement instructions, the procedure is straightforward: the node created for the input block must have the first node of the *then* block as successor, and node for the block following the given one is set as successor of the *then* block's last node; the same is done for the *else* branch if it exists. For loop instructions, the first node of the loop body is a successor of the given block's node and also a successor of the loop body's last node. In a manner similar to conditionals, switch statement instructions add an edge from the current node to the first node for the block started by the case label, and another edge from its last block to the block after the given one. Loop bodies and case blocks may end early with a break instruction, creating another edge to the successor of the loop body's or case block's last node. Similarly, an edge to the loop body's first node must be inserted for blocks ending with continue instructions. Interface calls jump to a location only known at runtime. Since the caller and callee share the same set of temporary registers, each possible call target is added as a successor, and the return statements of those functions have the node of the caller's next block added as a successor. For the main routine, return instructions cause an exit node to be added as successor.

In the process of SSA generation, variables are given a unique name whenever appearing as a destination operand of an instruction. Moreover,  $\Phi$ functions are inserted for variables when a point is reached where multiple different definitions of that variable may have occurred based on the path taken at runtime. Unique variable names are usually created by adding a version number to each occurrence of a variable. For the operands of vectorized instructions, as used for shader binaries, each vector component of a register constitutes a variable name, operand objects containing one to four variable names as a result. A 64-bit integer is used to encode the register and component numbers with their version to form a unique name.

4.3. Generating SSA Form

Figure 4.4.: A CFG created from one of the test cases, which uses a do-while loop and conditionals. The basic blocks are numbered to illustrate the intermediate results of the recursive calls.

#### 4. System Design

Using a shader program from another test case, figure 4.5 illustrates the conversion to SSA form. A new instruction with an arbitrary number of operands is added to the shader instruction set to represent  $\Phi$ -functions. Those instructions only exist during the middle phase of translation until they are removed by SSA destruction.

Standard algorithms have been used to implement the  $\Phi$ -function insertion at the CFG's dominance frontiers and variable renaming, originally developed by Cytron et al., 1991, pp. 466,470,472. To compute the dominators of each CFG node, an efficient algorithm created by Cooper, Harvey, and Kennedy, 2001 is a common solution and was used in this work as well. As a somewhat special case, any dynamic array indices that may be present in an operand object need to be regarded as source operands as well during the renaming step. Since no optimizations were required, the conventional SSA form is retained throughout all phases. Therefore, the  $\Phi$ -functions can be removed directly during SSA destruction.

## 4.4. Reconstructing Type Information

The PTX assembly language is an abstraction of graphics hardware that gives its users the ability to write programs in a type-safe way by declaring registers with a data type. This feature is optional; PTX also supports the declaration of untyped registers. C++ is naturally type-safe, a reinterpretation of variable contents as a different type has to be enforced using CUDA C++ language extensions. An attempt has been made to generate type-safe code for both languages, using typed variables and only forcing a conversion when the shader binaries reinterpret binary register contents through instructions expecting a certain type. This case occurs for example when a shader author uses the HLSL intrinsic functions asfloat or asuint, but is also sometimes generated by the HLSL compiler, as observed from manual inspection of shader disassembly.

Other type reconstruction tools have previously been developed to reverse engineer machine code with decompilers. Mycroft, (1999) converts target code in register-transfer (RTL) form to SSA and expresses the assignment of types to renamed variables as a solution to a system of type constraints

## 4.4. Reconstructing Type Information

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $\begin{array}{c}\text{phi r1.y_1, r1.y_0, r1.y_2} \\\text{phi r1.x_1, r1.x_0, r1.x_2} \\\text{phi r0.x_0, r0.w_0, r0.x_0} \\ \text{uge r0.w_1, r1.y_1, r0.x_0} \\ \text{breakc_nz r0.w_1} \\ \text{iadd r1.x_2, r0.z_0, r1.x_1} \\ \text{iadd r1.y_2, r1.y_1, 1(1)} \\ \text{endloop} \\ \text{mov o4.y, r1.x_1} \\ \text{mov r1.xz_{1,1}, 1(0,0,0,0)} \\ \text{loop} \\\text{phi r0.x_2, r0.x_1, r0.x_3} \\\text{phi r0.x_2, r0.x_1, r0.x_3} \\ \text{uge r0.w_3, r0.z_2, r0.y_0} \\ \text{breakc_nz r0.x_3, r0.x_2, v4.w} \\ \end{array} $ |