Adam SCHNELLBACH, MSc

# Fail-operational automotive systems

**Doctoral Thesis**

Graz University of Technology

Institute of Automotive Engineering Head: Univ.-Prof. Dr. Peter FISCHER

Supervisor: Assoc.-Prof. Dr. Mario HIRZ

Graz, November 2016

# **Statutory Declaration**

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly marked all material, which has been quoted either literally or by content from the used sources.

Graz,

Date

Signature

# Eidesstattliche Erklärung<sup>1</sup>

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe.

Graz, am

Datum

Unterschrift

<sup>&</sup>lt;sup>1</sup>Beschluss der Curricula-Kommission für Bachelor-, Master- und Diplomstudien vom 10.11.2008; Genehmigung des Senates am 1.12.2008

# Acknowledgements

Foremost, I would like to express my gratitude to my supervisor, Assoc.-Prof. Dr. Mario Hirz. His profound knowledge, his critical view on my thesis and his continuous support were essential. His guidance helped me to stay focused and motivated, even in the toughest times in the past two years.

My sincere thanks goes to my superiors at Magna Powertrain, especially to Andreas Münzer. His support and encouragement was one of the triggers to start my PhD studies, and to keep on working on my thesis even if challenges at work were overwhelming.

Last but not least, I would like to thank my wife and children for supporting me throughout writing this thesis.

I don't believe in talent. I believe in passion and work.

GEORGE KOLLIAS

# Abstract

Due to historic and cost efficiency reasons E/E automotive systems rely on so called fail safe architectures. These systems are switching into an inactive safe state when detecting internal or external failure modes that require this reaction. Their safety mechanisms are designed to detect failures and to trigger a system shut down, to prevent a safety critical failure propagation. Advantages of these systems are their simple architecture and hence their low piece price, by providing the appropriate level of safety integrity. The disadvantage of these architectures is obviously their limited availability in case of internal or external failures. The expectations, behaviour and skills of today's drivers' are changing. The non-availability of systems leading to significant overall vehicle function degradation cannot be tolerated to the same extent as it was in the past. Due to these reasons the demand on fail operational systems is increasing. These are able to maintain the full or an acceptably limited function in case of internal or external failures, instead of just shutting down.

Since other domains (e.g. avionics) have gathered lots of experience with such topologies, the key challenge is to understand, carry over and tailor already existing technical solutions and design principles.

In this thesis, the current state of the art of automotive systems in various transport-related industrial domains is investigated, focusing on their related functional safety standards and technical solutions. Based on that, a detailed investigation of the ISO 26262:2011 is performed, from the perspective of fail-operational systems. The applicability of this standard is investigated, and improvement proposals are defined, wherever necessary. Besides that, typical fail-operational SW and HW architectures are investigated within the framework of the ISO 26262:2011 and an automotive application. The key finding of this investigation is that for automotive fail-operational systems, full redundancy is seldom required. The designers have to be capable of adding the right type of redundancy at the right spot in the architecture. To support the definition of these sufficiently independent redundant architectures, a generic, structured dependent failure analysis, fitting into the analysis framework of the ISO 26262:2011 is developed. Based on these findings, the redundancy allocation problem – a well-known problem in other industrial domains – is solved for an automotive application. In order to do so, a complex mathematical model is derived, to host failure-propagation modelling, and the calculation of the HW metrics of the ISO 26262:2011 as reliability metric. A straightforward genetic algorithm is developed to utilise this mathematical model. The verification of these models and algorithms is performed using realistic examples.

# Contents

| <ul> <li>1.2 Didactic structure of the thesis</li> <li>1.3 Typographic conventions</li> <li>2 Introduction to functional safety</li> <li>2.1 Basics of functional safety</li> <li>2.2 Basic terms of functional safety</li> <li>2.3 Introduction to safety standards</li> <li>2.4 Introduction to the [ISO11]</li> <li>2.4.1 Lifecycle model of the [ISO11]</li> <li>2.4.2 Hazard analysis and risk assessment (HARA)</li> <li>2.4.3 ASIL decomposition</li> <li>2.4.4 Quantitative metrics of the [ISO11]</li> <li>2.5 Introduction to safety standards</li> <li>2.5.3 FTA</li> <li>2.5.3 FTA</li> <li>2.5.3 FTA</li> <li>2.5.3 FTA</li> <li>3.1 Fail-operational behaviour and fault tolerance in general</li> <li>3.1.1 Fail-operational aspects in avionics standards and guidelines</li> <li>3.2.1 Fail-operational aspects in avionics standards and guidelines</li> <li>3.2.2 Fail-operational aspects in avionics standards and guidelines</li> <li>3.3.2 Fail-operational aspects in attee-of-the-art avionics systems</li> <li>3.3.2 Fail-operational aspects in railway standards</li> <li>3.4.1 Fail-operational aspects in railway standards</li> <li>3.4.2 Fail-operational aspects in automotive applications</li> <li>3.4.1 Fail-operational aspects in automotive applications</li> <li>3.4.2 Fail-operational aspects in automotive applications</li> <li>3.4.3 Fail-operational aspects in automotive applications</li> <li>3.4.4 Fail-operational aspects in automotive applications</li> <li>3.5.4 Fail-operational aspects in automotive applications</li> <li>3.5.5 Fail-operational aspects in automotive applications</li> <li>3.5.6 Summary of the literature research</li> <li>4 Aspects of fail-operational aspects in design in state-of-the-art automotive systems</li> <li>3.6 Summary of the literature research</li> <li>4 Aspects of fail-operational aspects in automotive applications</li> <li>3.5.1 Fail-operational aspects in automotive applications</li> <li>3.5.2 Fail-operational aspects in the [ISO11]</li> <li>4.3 Definition of the attributes of fail-operational behaviour [</li></ul> | Ab | strac | ct                                                                     | vii     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|------------------------------------------------------------------------|---------|

| <ul> <li>1.2 Didactic structure of the thesis</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1  | Intro | oduction                                                               | 1       |

| <ul> <li>1.2 Didactic structure of the thesis</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 1.1   | Introduction of the problem and motivation of this thesis              | 1       |

| <ul> <li>1.3 Typographic conventions</li> <li>2 Introduction to functional safety</li> <li>2.1 Basics of functional safety</li> <li>2.2 Basic terms of functional safety</li> <li>2.3 Introduction to safety standards</li> <li>2.4 Introduction to the [ISO11]</li> <li>2.4.1 Lifecycle model of the [ISO11]</li> <li>2.4.2 Hazard analysis and risk assessment (HARA)</li> <li>2.4.3 ASIL decomposition</li> <li>2.4.4 Quantitative metrics of the [ISO11]</li> <li>2.5 Introduction to safety analysis techniques</li> <li>2.5.1 FMEA</li> <li>2.5.2 FMEDA</li> <li>2.5.3 FTA</li> <li>3 Results of the literature research - the state of the art</li> <li>3.1 Fail-operational aspects in the [IEC10]</li> <li>3.1.2 Basics of fail-operational aspects in avionics</li> <li>3.2.3 Fail-operational aspects in railway standards and guidelines</li> <li>3.3.4 Fail-operational aspects in ariolway anglications</li> <li>3.4.2 Fail-operational aspects in the [AS114]</li> <li>3.3.4 Fail-operational aspects in the [AS114]</li> <li>3.4 Fail-operational aspects in the [AS114]</li> <li>3.5.1 Fail-operational aspects in railway standards.</li> <li>3.4.2 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational aspects in the [ISO11]</li> <li>3.5.3 Fail-operational aspects in avionice standards.</li> <li>3.4.2 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational aspects in the [AS114]</li> <li>3.5.3 Fail-operational aspects in the [AS114]</li> <li>3.5.4 Fail-operational aspects in the [ISO11]</li> <li>3.5.5 Fail-operational aspects in the atte-of-the-art arguicultural systems</li> <li>3.4 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational aspects in the [ISO11]</li> <li>3.5.3 Fail-operational aspects in the [ISO11]</li> <li>3.5.4 Fail-operational aspects in the [ISO11]</li> <li>3.5.5 Fail-operational aspects in the [ISO11]</li> <li>3.5.6 Summary of the literature research</li> <li>4 Aspects of fail-operational systems conforming to the [ISO11]</li> <li>4.1 Structure of this chapter</li> <li>4.2 Method to</li></ul> |    | 1.2   | Didactic structure of the thesis                                       | 1       |

| <ul> <li>2.1 Basics of functional safety</li> <li>2.2 Basic terms of functional safety</li> <li>2.3 Introduction to safety standards</li> <li>2.4 Introduction to the [ISO11]</li> <li>2.4.1 Lifecycle model of the [ISO11]</li> <li>2.4.2 Hazard analysis and risk assessment (HARA)</li> <li>2.4.3 ASIL decomposition</li> <li>2.4.4 Quantitative metrics of the [ISO11]</li> <li>2.5 Introduction to safety analysis techniques</li> <li>2.5.1 FMEA</li> <li>2.5.2 FMEDA</li> <li>2.5.3 FTA</li> </ul> 3 Results of the literature research - the state of the art <ul> <li>3.1 Fail-operational behaviour and fault tolerance in general</li> <li>3.1.1 Fail-operational aspects in the [IEC10]</li> <li>3.2.1 Fail-operational aspects in avionics</li> <li>3.2.2 Fail-operational aspects in avionics standards and guidelines</li> <li>3.2.2 Fail-operational design in state-of-the-art avionics systems</li> <li>3.3 Fail-operational aspects in railway applications</li> <li>3.4.1 Fail-operational aspects in railway standards</li> <li>3.4.2 Fail-operational aspects in the [ISO11]</li> <li>3.5.1 Fail-operational aspects in the ISO11]</li> <li>3.5.1 Fail-operational aspects in the ISO11]</li> <li>3.5.2 Fail-operational aspects in the ISO11]</li> <li>3.5.4 Fail-operational aspects in the ISO11]</li> <li>3.5.5 Fail-operational aspects in the ISO11]</li> <li>3.5.6 Summary of the literature research</li> <li>4 Aspects of fail-operational design in state-of-the-art automotive systems</li> <li>3.6 Summary of the literature research</li> <li>4.3 Evall-operational aspects in the ISO11]</li> <li>4.3.1 Fault tolerance argets</li> <li>4.3.4 Evaluational aspects in the ISO11]</li> <li>4.3.5 Fail-operational aspects in the ISO11]</li> <li>4.3.6 Summary of the literature research</li> <li>4.3.7 Fail-operational aspects</li> <li>4.3.8 The operational aspects</li> <li>4.3.4 Evaluational design in state-of-the-art automotive systems</li> <li>3.4 Fail-operational aspects in the ISO11]</li> <li>4.3 Definition of the attributes of fail-operational behaviour [Sch1</li></ul>        |    | 1.3   | Typographic conventions                                                | 1       |

| <ul> <li>2.1 Basics of functional safety</li> <li>2.2 Basic terms of functional safety</li> <li>2.3 Introduction to safety standards</li> <li>2.4 Introduction to the [ISO11]</li> <li>2.4.1 Lifecycle model of the [ISO11]</li> <li>2.4.2 Hazard analysis and risk assessment (HARA)</li> <li>2.4.3 ASIL decomposition</li> <li>2.4.4 Quantitative metrics of the [ISO11]</li> <li>2.5 Introduction to safety analysis techniques</li> <li>2.5.1 FMEA</li> <li>2.5.2 FMEDA</li> <li>2.5.3 FTA</li> </ul> 3 Results of the literature research - the state of the art <ul> <li>3.1 Fail-operational behaviour and fault tolerance in general</li> <li>3.1.1 Fail-operational aspects in the [IEC10]</li> <li>3.2.1 Fail-operational aspects in avionics</li> <li>3.2.2 Fail-operational aspects in avionics standards and guidelines</li> <li>3.2.2 Fail-operational design in state-of-the-art avionics systems</li> <li>3.3 Fail-operational aspects in railway applications</li> <li>3.4.1 Fail-operational aspects in railway standards</li> <li>3.4.2 Fail-operational aspects in the [ISO11]</li> <li>3.5.1 Fail-operational aspects in the ISO11]</li> <li>3.5.1 Fail-operational aspects in the ISO11]</li> <li>3.5.2 Fail-operational aspects in the ISO11]</li> <li>3.5.4 Fail-operational aspects in the ISO11]</li> <li>3.5.5 Fail-operational aspects in the ISO11]</li> <li>3.5.6 Summary of the literature research</li> <li>4 Aspects of fail-operational design in state-of-the-art automotive systems</li> <li>3.6 Summary of the literature research</li> <li>4.3 Evall-operational aspects in the ISO11]</li> <li>4.3.1 Fault tolerance argets</li> <li>4.3.4 Evaluational aspects in the ISO11]</li> <li>4.3.5 Fail-operational aspects in the ISO11]</li> <li>4.3.6 Summary of the literature research</li> <li>4.3.7 Fail-operational aspects</li> <li>4.3.8 The operational aspects</li> <li>4.3.4 Evaluational design in state-of-the-art automotive systems</li> <li>3.4 Fail-operational aspects in the ISO11]</li> <li>4.3 Definition of the attributes of fail-operational behaviour [Sch1</li></ul>        | 2  | Intr  | oduction to functional safety                                          | 3       |

| <ul> <li>2.2 Basic terms of functional safety</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -  |       | -                                                                      | 3       |

| <ul> <li>2.3 Introduction to safety standards</li> <li>2.4 Introduction to the [ISO11]</li> <li>2.4.1 Lifecycle model of the [ISO11]</li> <li>2.4.2 Hazard analysis and risk assessment (HARA)</li> <li>2.4.3 ASIL decomposition</li> <li>2.4.4 Quantitative metrics of the [ISO11]</li> <li>2.5 Introduction to safety analysis techniques</li> <li>2.5.1 FMEA</li> <li>2.5.2 FMEDA</li> <li>2.5.3 FTA</li> <li>3.1 Fail-operational behaviour and fault tolerance in general</li> <li>3.1.1 Fail-operational aspects in the [IEC10]</li> <li>3.2.1 Fail-operational aspects in avionics</li> <li>3.2.2 Fail-operational aspects in avionics standards and guidelines</li> <li>3.3.2 Fail-operational design in state-of-the-art avionic systems</li> <li>3.3 Fail-operational aspects in railway applications</li> <li>3.4.1 Fail-operational aspects in railway applications</li> <li>3.4.1 Fail-operational aspects in state-of-the-art arionic systems</li> <li>3.4.2 Fail-operational design in state-of-the-art agricultural systems</li> <li>3.4.1 Fail-operational aspects in railway applications</li> <li>3.5.2 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational aspects in the [ISO11]</li> <li>3.5.4 Fail-operational aspects in the [ISO11]</li> <li>3.5.5 Fail-operational design in state-of-the-art agricultural systems</li> <li>3.4 Fail-operational aspects in railway applications</li> <li>3.5.1 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational design in state-of-the-art automotive systems</li> <li>3.6 Summary of the literature research</li> <li>4 Aspects of fail-operational systems conforming to the [ISO11]</li> <li>4.1 Structure of this chapter</li> <li>4.2 Method to determine the necessity of fail-operational behaviour [Sch15]</li> <li>4.3 Definition of the attributes of fail-operational behaviour [Sch15]</li> <li>4.3 Line or emain operational after the first fault occurred</li> <li>4.3.3 Time to remain operational after the first fault occurred</li> </ul>                |    |       |                                                                        | 4       |

| <ul> <li>2.4 Introduction to the [ISO11]</li> <li>2.4.1 Lifecycle model of the [ISO11]</li> <li>2.4.2 Hazard analysis and risk assessment (HARA)</li> <li>2.4.3 ASIL decomposition</li> <li>2.4.4 Quantitative metrics of the [ISO11]</li> <li>2.5 Introduction to safety analysis techniques</li> <li>2.5.1 FMEA</li> <li>2.5.2 FMEDA</li> <li>2.5.3 FTA</li> <li>3 Results of the literature research - the state of the art</li> <li>3.1 Fail-operational behaviour and fault tolerance in general</li> <li>3.1.1 Fail-operational aspects in the [IEC10]</li> <li>3.1.2 Basics of fail-operational behaviour and fault tolerance in general</li> <li>3.2.1 Fail-operational aspects in avionics</li> <li>3.2.2 Fail-operational aspects in avionics standards and guidelines</li> <li>3.2.2 Fail-operational aspects in state-of-the-art avionics systems</li> <li>3.3.1 Fail-operational design in state-of-the-art agricultural systems</li> <li>3.3.1 Fail-operational design in state-of-the-art agricultural systems</li> <li>3.4.1 Fail-operational design in state-of-the-art argicultural systems</li> <li>3.4.1 Fail-operational design in state-of-the-art argicultural systems</li> <li>3.4.2 Fail-operational design in state-of-the-art argicultural systems</li> <li>3.4.2 Fail-operational design in state-of-the-art argicultural systems</li> <li>3.5.1 Fail-operational aspects in railway standards</li> <li>3.5.2 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational aspects in the [ISO11]</li> <li>3.5.3 Fail-operational aspects in the [ISO11]</li> <li>3.5.4 Fail-operational aspects in the [ISO11]</li> <li>3.5.5 Fail-operational systems conforming to the [ISO11]</li> <li>4.1 Structure of this chapter</li> <li>4.2 Method to determine the necessity of fail-operational behaviour [Sch15]</li> <li>4.3 Definition of the attributes of fail-operational behaviour [Sch15]</li> <li>4.3 Definition of the attributes of fail-operational behaviour [Sch15]</li> <li>4.3 Diffusion of the attributes of fail-operational behaviour [Sch15]</li> <li>4.3 Allowed funct</li></ul> |    |       |                                                                        | 4       |

| <ul> <li>2.4.1 Lifecycle model of the [ISO11]</li> <li>2.4.2 Hazard analysis and risk assessment (HARA)</li> <li>2.4.3 ASIL decomposition</li> <li>2.4.4 Quantitative metrics of the [ISO11]</li> <li>2.5 Introduction to safety analysis techniques</li> <li>2.5.1 FMEA</li> <li>2.5.2 FMEDA</li> <li>2.5.3 FTA</li> <li>2.5.3 FTA</li> <li>3.1 Fail-operational behaviour and fault tolerance in general</li> <li>3.1.1 Fail-operational aspects in the [IEC10]</li> <li>3.1.2 Basics of fail-operational behaviour and fault tolerance .</li> <li>3.2 Fail-operational aspects in avionics</li> <li>3.2.2 Fail-operational aspects in avionics standards and guidelines</li> <li>3.2.2 Fail-operational aspects in the [ASI14]</li> <li>3.3 Fail-operational aspects in the [ASI14]</li> <li>3.3.2 Fail-operational aspects in the [ASI14]</li> <li>3.3.2 Fail-operational aspects in railway applications</li> <li>3.4.1 Fail-operational design in state-of-the-art agricultural systems</li> <li>3.4 Fail-operational aspects in railway standards</li> <li>3.4.2 Fail-operational design in state-of-the-art railway systems</li> <li>3.5 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational design in state-of-the-art railway systems</li> <li>3.4 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational design in state-of-the-art agricultural systems</li> <li>3.4 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational design in state-of-the-art agricultural systems</li> <li>3.5.1 Fail-operational design in state-of-the-art automotive systems</li> <li>3.6 Summary of the literature research</li> <li>4 Aspects of fail-operational systems conforming to the [ISO11]</li> <li>4.1 Structure of this chapter</li> <li>4.2 Method to determine the necessity of fail-operational behaviour [Sch15]</li> <li>4.3 Definition of the attributes of fail-operational behaviour [Sch15]</li> <li>4.3 Time to remain operational after the first fault occurred</li> <li>4.3.3 Time to remain operational after the first fault occurred</li> </ul>              |    | 9     |                                                                        | 9       |

| <ul> <li>2.4.2 Hazard analysis and risk assessment (HARA)</li> <li>2.4.3 ASIL decomposition</li> <li>2.4.4 Quantitative metrics of the [ISO11]</li> <li>2.5 Introduction to safety analysis techniques</li> <li>2.5.1 FMEA</li> <li>2.5.2 FMEDA</li> <li>2.5.3 FTA</li> <li>2.5.3 FTA</li> <li>3.1 Fail-operational behaviour and fault tolerance in general</li> <li>3.1.2 Basics of fail-operational aspects in the [IEC10]</li> <li>3.2.2 Fail-operational aspects in avionics standards and guidelines</li> <li>3.2.2 Fail-operational aspects in aspects in the [ASI14]</li> <li>3.3 Fail-operational aspects in railway applications</li> <li>3.4 Fail-operational aspects in railway standards</li> <li>3.4.1 Fail-operational aspects in railway standards</li> <li>3.4.2 Fail-operational aspects in railway standards</li> <li>3.4.1 Fail-operational aspects in railway standards</li> <li>3.4.2 Fail-operational aspects in the [ISO11]</li> <li>3.5.1 Fail-operational aspects in atte-of-the-art automotive systems</li> <li>3.5 Fail-operational aspects in the [ISO11]</li> <li>4.1 Structure of the literature research</li> <li>4 Aspects of fail-operational systems conforming to the [ISO11]</li> <li>4.1 Structure of the literature research</li> <li>4.3 The operational aspects in the [ISO11]</li> <li>4.3 Chapter Aspects of fail-operational behaviour [Sch15]</li> <li>4.3 Definition of the attributes of fail-operational behaviour [Sch15]</li> <li>4.3 Time to remain operational after the first fault occurred</li> <li>4.3.3 Time to remain operational after the first fault occurred</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 2.4   |                                                                        |         |

| <ul> <li>2.4.3 ASIL decomposition</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       |                                                                        | 9<br>12 |

| <ul> <li>2.4.4 Quantitative metrics of the [ISO11]</li> <li>2.5 Introduction to safety analysis techniques</li> <li>2.5.1 FMEA</li> <li>2.5.2 FMEDA</li> <li>2.5.3 FTA</li> <li>2.5.3 FTA</li> <li>3.1 Fail-operational behaviour and fault tolerance in general</li> <li>3.1.1 Fail-operational aspects in the [IEC10]</li> <li>3.1.2 Basics of fail-operational behaviour and fault tolerance</li> <li>3.2 Fail-operational aspects in avionics</li> <li>3.2.1 Fail-operational aspects in avionics standards and guidelines</li> <li>3.2.2 Fail-operational aspects in agricultural applications</li> <li>3.3.1 Fail-operational aspects in the [ASI14]</li> <li>3.3.2 Fail-operational design in state-of-the-art agricultural systems</li> <li>3.4 Fail-operational aspects in railway applications</li> <li>3.4.1 Fail-operational aspects in atte-of-the-art railway systems</li> <li>3.4 Fail-operational aspects in the [ISO11]</li> <li>3.5.1 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational aspects in the [ISO11]</li> <li>4.1 Structure of this chapter</li> <li>4.2 Method to determine the necessity of fail-operational behaviour [Sch15]</li> <li>4.3 Definition of the attributes of fail-operational behaviour [Sch15]</li> <li>4.3.3 Time to remain operational after the first fault occurred</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |       |                                                                        |         |

| <ul> <li>2.5 Introduction to safety analysis techniques</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |       |                                                                        | 14      |

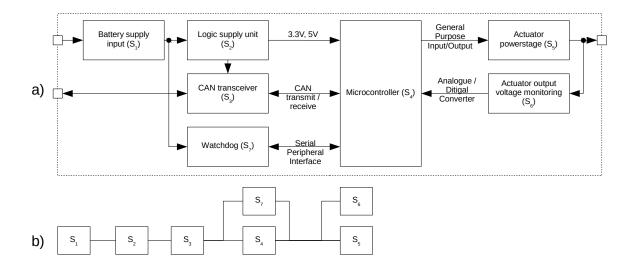

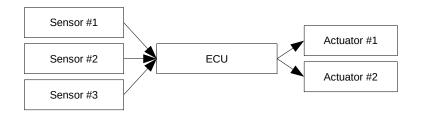

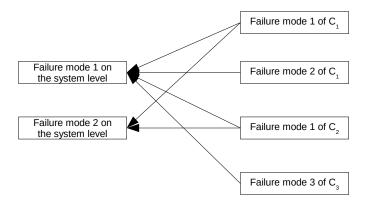

| <ul> <li>2.5.1 FMEA</li> <li>2.5.2 FMEDA</li> <li>2.5.3 FTA</li> <li>3.1 Fail-operational behaviour and fault tolerance in general</li> <li>3.1.1 Fail-operational aspects in the [IEC10]</li> <li>3.1.2 Basics of fail-operational behaviour and fault tolerance .</li> <li>3.2 Fail-operational aspects in avionics</li> <li>3.2.1 Fail-operational aspects in avionics standards and guidelines</li> <li>3.2.2 Fail-operational design in state-of-the-art avionics systems</li> <li>3.3 Fail-operational aspects in the [ASI14]</li> <li>3.3.2 Fail-operational design in state-of-the-art agricultural systems</li> <li>3.3 Fail-operational aspects in railway applications</li> <li>3.4.1 Fail-operational aspects in railway standards</li> <li>3.4.2 Fail-operational design in state-of-the-art railway systems</li> <li>3.4.4 Fail-operational aspects in automotive applications</li> <li>3.5.1 Fail-operational design in state-of-the-art railway systems</li> <li>3.5.2 Fail-operational design in state-of-the-art railway systems</li> <li>3.5.1 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational design in state-of-the-art automotive systems</li> <li>3.5.4 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational design in state-of-the-art automotive systems</li> <li>3.5.4 Fail-operational aspects in the [ISO11]</li> <li>3.5.2 Fail-operational design in state-of-the-art automotive systems</li> <li>3.6 Summary of the literature research</li> <li>4 Aspects of fail-operational systems conforming to the [ISO11]</li> <li>4.1 Structure of this chapter</li> <li>4.2 Method to determine the necessity of fail-operational behaviour [Sch15]</li> <li>4.3 Definition of the attributes of fail-operational behaviour [Sch15]</li> <li>4.3 Difficution of the attributes of fail-operational behaviour [Sch15]</li> <li>4.3 Difficution of the attributes of fail-operational behaviour [Sch15]</li> <li>4.3 Time to remain operational after the first fault occurred</li> </ul>                                                                               |    |       |                                                                        | 15      |

| <ul> <li>2.5.2 FMEDA</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 2.5   |                                                                        | 17      |

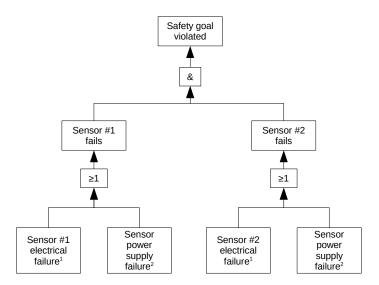

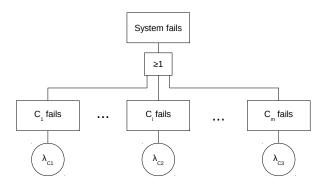

| <ul> <li>2.5.3 FTA</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       | 5                                                                      | 18      |

| <ul> <li>3 Results of the literature research - the state of the art</li> <li>3.1 Fail-operational behaviour and fault tolerance in general</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |       |                                                                        | 19      |

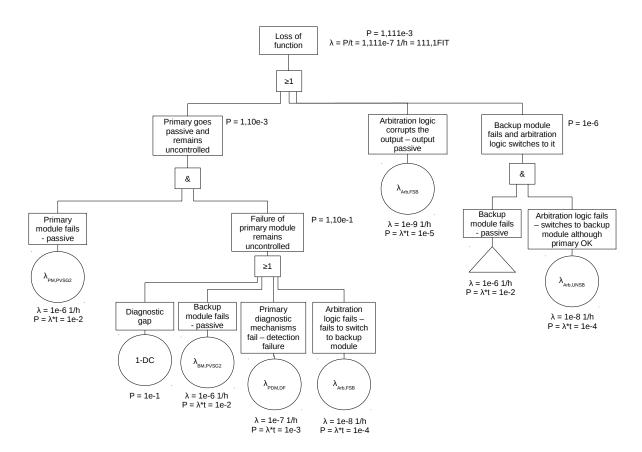

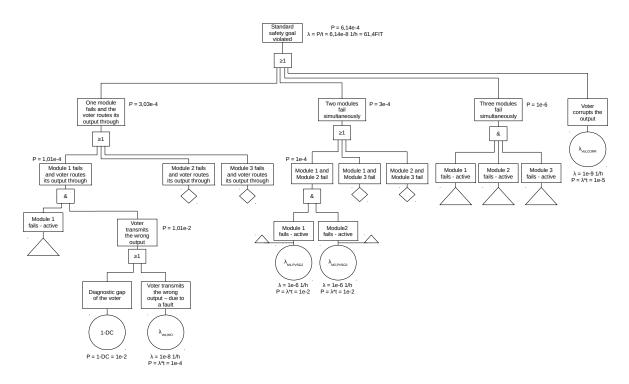

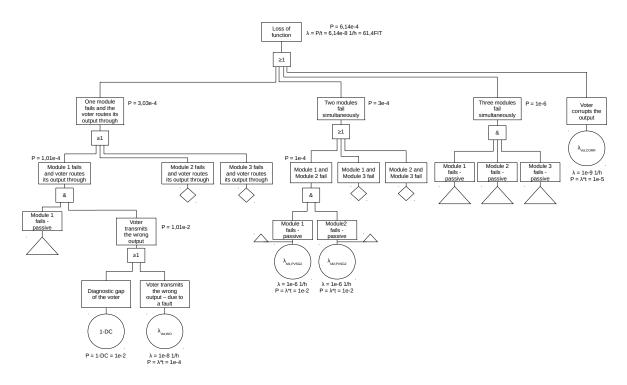

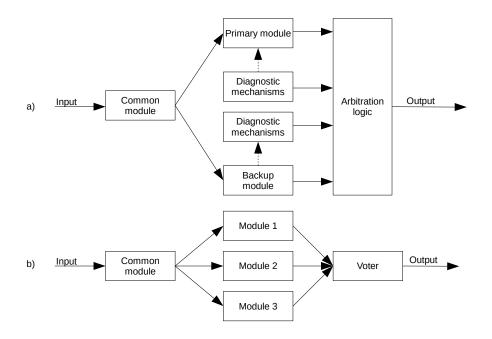

| <ul> <li>3.1 Fail-operational behaviour and fault tolerance in general</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       | 2.5.3 FIA                                                              | 21      |

| <ul> <li>3.1.1 Fail-operational aspects in the [IEC10]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3  | Res   |                                                                        | 23      |

| <ul> <li>3.1.2 Basics of fail-operational behaviour and fault tolerance</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 3.1   | Fail-operational behaviour and fault tolerance in general              | 23      |

| <ul> <li>3.2 Fail-operational aspects in avionics</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       |                                                                        | 23      |

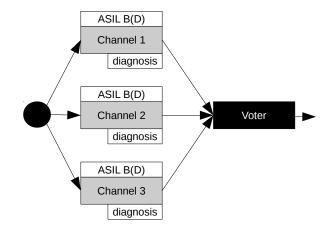

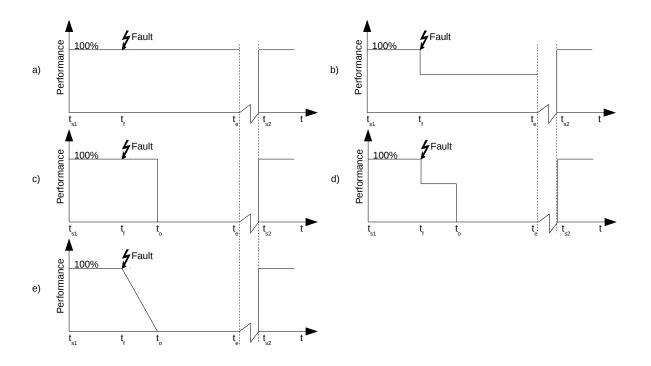

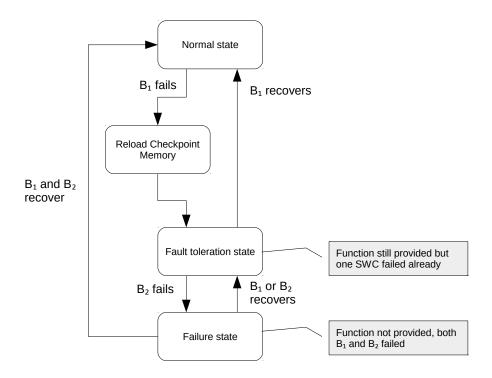

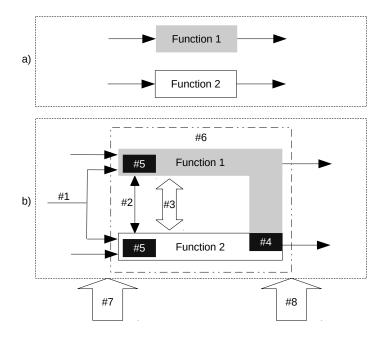

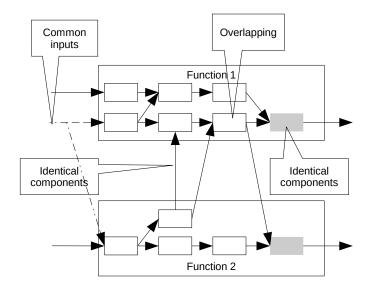

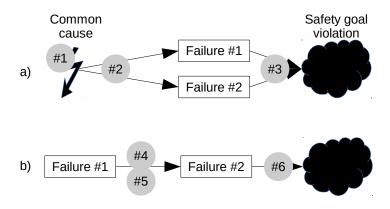

| <ul> <li>3.2.1 Fail-operational aspects in avionics standards and guidelines</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |       | 3.1.2 Basics of fail-operational behaviour and fault tolerance         | 24      |

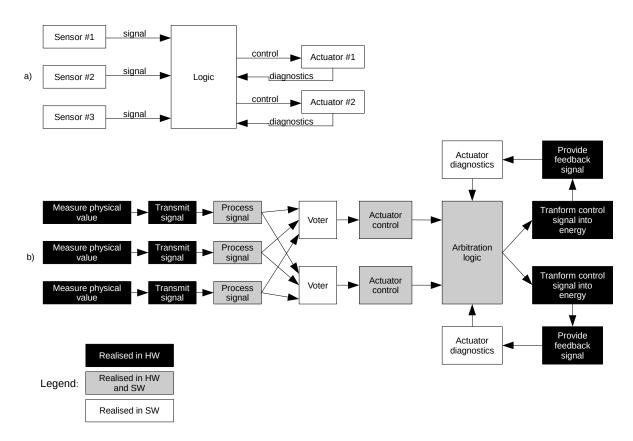

| <ul> <li>3.2.2 Fail-operational design in state-of-the-art avionics systems 3.3 Fail-operational aspects in agricultural applications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 3.2   | Fail-operational aspects in avionics                                   | 33      |

| <ul> <li>3.3 Fail-operational aspects in agricultural applications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |       | 3.2.1 Fail-operational aspects in avionics standards and guidelines    | 33      |

| <ul> <li>3.3.1 Fail-operational aspects in the [ASI14]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       | 3.2.2 Fail-operational design in state-of-the-art avionics systems     | 35      |

| <ul> <li>3.3.2 Fail-operational design in state-of-the-art agricultural systems .</li> <li>3.4 Fail-operational aspects in railway applications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 3.3   | Fail-operational aspects in agricultural applications                  | 41      |

| <ul> <li>3.3.2 Fail-operational design in state-of-the-art agricultural systems .</li> <li>3.4 Fail-operational aspects in railway applications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |                                                                        | 41      |

| <ul> <li>3.4 Fail-operational aspects in railway applications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |       |                                                                        | 42      |

| <ul> <li>3.4.1 Fail-operational aspects in railway standards</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 3.4   | Fail-operational aspects in railway applications                       | 43      |

| <ul> <li>3.4.2 Fail-operational design in state-of-the-art railway systems</li> <li>3.5 Fail-operational aspects in automotive applications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 51    |                                                                        | 43      |

| <ul> <li>3.5 Fail-operational aspects in automotive applications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |       | 3.4.2 Fail-operational design in state-of-the-art railway systems      | 43      |

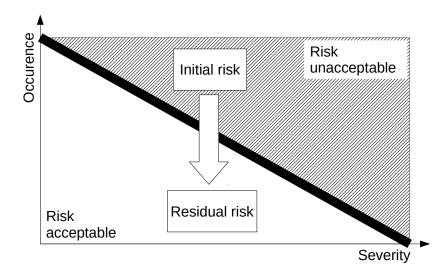

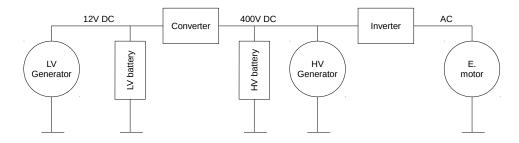

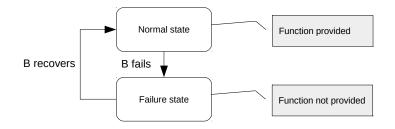

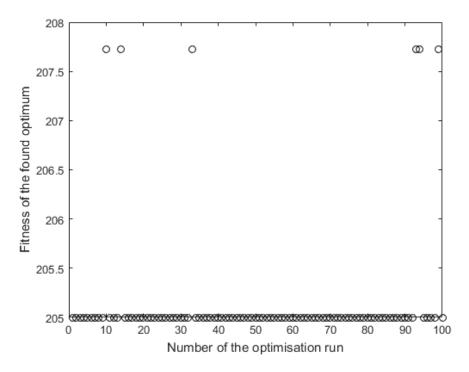

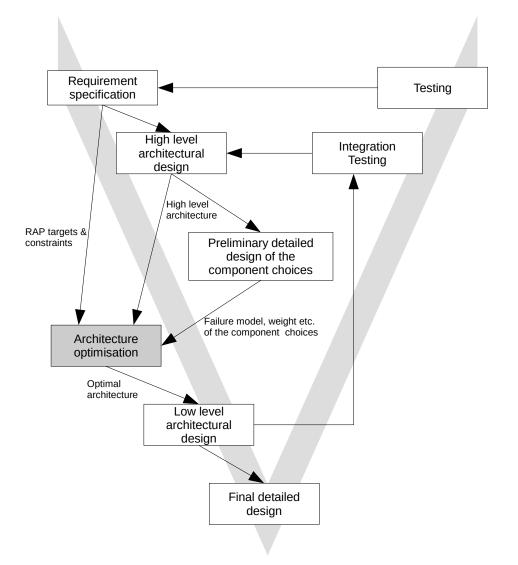

| <ul> <li>3.5.1 Fail-operational aspects in the [ISO11]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 3.5   | Fail-operational aspects in automotive applications                    | 44      |