Martin Schachner, BSc

# Design and Implementation of a Co-Simulation Environment based on Virtual Platforms

# **MASTER'S THESIS**

to achieve the university degree of

Diplom-Ingenieur

Master's degree programme: Computer Science

submitted to

# Graz University of Technology

Supervisor

Ass.Prof. Dipl.-Ing. Dr.techn. Christian Steger Institute for Technical Informatics

Advisor

Ass.Prof. Dipl.Ing. Dr.techn. Christian Steger Dipl.-Ing. Dr.techn. Ralph Weissnegger, BSc (CISC Semiconductor GmbH)

Graz, August 2017

# AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present master's thesis dissertation.

Date

Signature

### Abstract

As many different stakeholders with different technical background have to work together for the realization of cyber-physical systems, the complexity of such projects increases continuously. Furthermore, developments, such as those of the automotive industry, are strongly driven by the demand for cost-reduction. But not only costs play a decisive role, nowadays compliance with standards to provide functional safety become more and more important. This leads to the need for a paradigm shift in the design and development of cyber-physical systems. The main focus must be on closer cooperation between developers, such that shorter time to market can be achieved.

This work presents a way how common methodologies from software development and those from classical engineering disciplines such as mechanical or electrical engineering can be combined. The idea is grounded on graphic, model-based solutions. An existing development framework was extended by the integration of virtual hardware prototypes. This approach makes it possible to execute and simulate appropriate application code even in early design phases.

The practical part describes the way of how to extend the existing modeling framework by means of graphic description for virtual hardware prototypes. Furthermore, a possible embedding of the created platforms in the physical environment is discussed and simulated. This interaction is shown by a simplified electrical vehicle model. In particular temperature data of a lithium-ion battery is monitored by an integrated hardware platform.

**keywords**: cyber-physical system development, model driven engineering, model based design, UML/MARTE, virtual hardware prototyping, co-simulation

# Kurzfassung

Die Entwicklung von cyber-physischen Systemen gestaltet sich zunehmend schwieriger, da viele Interessensvertreter mit unterschiedlichem technischen Hintergrund an einem heterogenen Gesamtsystem arbeiten müssen. Weiters werden Entwicklungen, wie zum Beispiel jene der Automobilindustrie, stark durch die Kostenfrage getrieben. Doch nicht nur Kosten spielen eine entscheidende Rolle, auch die Einhaltung von Standards zur Gewährung von funktionaler Sicherheit werden immer wichtiger. Dadurch ergibt sich für die Hersteller von cyber-physischen Systemen die Notwendigkeit für einen Paradigmenwechsel in der Entwicklung. Hauptaugenmerk muss dabei auf eine engere Zusammenarbeit zwischen Entwicklern gelegt werden, um eine kürzere Time-to-Market realisieren zu können.

Mit dieser Arbeit wird eine Möglichkeit vorgestellt, wie gebräuchliche Methoden aus der Softwareentwicklung und jener von klassischen Ingenieursdisziplinen, wie dem Maschinenbau oder der Elektrotechnik verbunden werden können. Im Zentrum stehen dabei graphische, modellbasierte Lösungen. Dabei wurde ein bestehendes Entwicklungsframework um die Integration von virtuellen Hardwareprototypen erweitert, sodass schon in frühen Designphasen eine Simulation mit konkretem Applikationscode möglich wird.

Die praktische Arbeit beschreibt dabei die Möglichkeiten das bestehende Modellierungsframework um die graphische Beschreibung von Hardwareprototypen zu erweitern. Weiters wird gezeigt wie die erstellten Plattformen in die physikalische Umgebung eingebettet und simuliert werden können. Diese Interaktion wird anhand eines vereinfachten Elektrofahrzeugmodells gezeigt. Dabei werden Temperaturdaten einer Lithium-Ionen-Batterie mit Hilfe einer virtuellen Hardwareplatform überwacht.

**Stichwörter**: cyber-physical system development, model driven engineering, model based design, UML/MARTE, virtual hardware prototyping, co-simulation

# Acknowledgment

Without the help of several people, this work and my time at Graz University of Technology would not have been possible. So I would like to take the opportunity and say thank you at this point.

First I would like to thank the Institute for Technical Informatics. Especially I would like to thank my supervisors Dr. Christian Steger and Dr. Ralph Weissnegger for their great support and excellent guidance through the project duration. It would not have been possible to do my researches, without the help of my colleague Markus Schuss, whom I want to thank as well.

I am also grateful to the company CISC Semiconductor and Dr. Markus Pistauer for the cooperation during the work on this thesis.

Last but not least, I want to thank my family and friends for giving me love, guidance and courage in all life situations.

Graz, August 2017

Martin Schachner

# Contents

| 1        | Intr           | oducti       | on 1                                                           |  |  |  |  |  |  |  |

|----------|----------------|--------------|----------------------------------------------------------------|--|--|--|--|--|--|--|

|          | 1.1            | Motiva       | ation                                                          |  |  |  |  |  |  |  |

|          | 1.2            | Object       | tive $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $3$ |  |  |  |  |  |  |  |

|          | 1.3            | -            | e                                                              |  |  |  |  |  |  |  |

| <b>2</b> | Bac            | Background 6 |                                                                |  |  |  |  |  |  |  |

|          | 2.1            | Cyber        | -physical systems                                              |  |  |  |  |  |  |  |

|          |                | 2.1.1        | Definition                                                     |  |  |  |  |  |  |  |

|          |                | 2.1.2        | The evolution of CPS                                           |  |  |  |  |  |  |  |

|          |                | 2.1.3        | Challenges for the design of CPS                               |  |  |  |  |  |  |  |

|          |                | 2.1.4        | Automotive: Example for the usage of CPS                       |  |  |  |  |  |  |  |

|          | 2.2            | Develo       | opment aspects of CPS                                          |  |  |  |  |  |  |  |

|          | 2.3            | Model        | s                                                              |  |  |  |  |  |  |  |

|          |                | 2.3.1        | Model-driven engineering/development                           |  |  |  |  |  |  |  |

|          |                | 2.3.2        | Model-based design                                             |  |  |  |  |  |  |  |

|          |                | 2.3.3        | Virtual electronic/hardware prototypes                         |  |  |  |  |  |  |  |

|          | 2.4            | Model        | ing of digital systems                                         |  |  |  |  |  |  |  |

|          |                | 2.4.1        | Abstraction layers                                             |  |  |  |  |  |  |  |

|          |                | 2.4.2        | Execution performance                                          |  |  |  |  |  |  |  |

|          |                | 2.4.3        | Components of virtual hardware platforms                       |  |  |  |  |  |  |  |

| 3        | $\mathbf{Rel}$ | ated w       | ork 23                                                         |  |  |  |  |  |  |  |

|          | 3.1            | Model        | ing electronics in compliance with the ISO 26262               |  |  |  |  |  |  |  |

|          | 3.2            | State-       | of-the-art approaches for virtual prototyping                  |  |  |  |  |  |  |  |

|          |                | 3.2.1        | Open models                                                    |  |  |  |  |  |  |  |

|          |                | 3.2.2        | Graphic modeling                                               |  |  |  |  |  |  |  |

|          | 3.3            | Co-sin       | nulation CPS and SoC models                                    |  |  |  |  |  |  |  |

|          |                | 3.3.1        | Industrial example - Mathworks and Cadence                     |  |  |  |  |  |  |  |

|          |                | 3.3.2        | Conclusion                                                     |  |  |  |  |  |  |  |

|          | 3.4            | SHAR         | C IDE                                                          |  |  |  |  |  |  |  |

|          |     | 3.4.1   | Modeling with UML                                                 | 28 |

|----------|-----|---------|-------------------------------------------------------------------|----|

|          |     | 3.4.2   | The SysCore simulation framework                                  | 29 |

|          |     | 3.4.3   | System verification                                               | 30 |

|          | D   | •       |                                                                   |    |

| 4        | Des | 0       |                                                                   | 33 |

|          | 4.1 |         | vstem-level modeling language SystemC                             | 33 |

|          |     | 4.1.1   | SystemC's core components                                         | 34 |

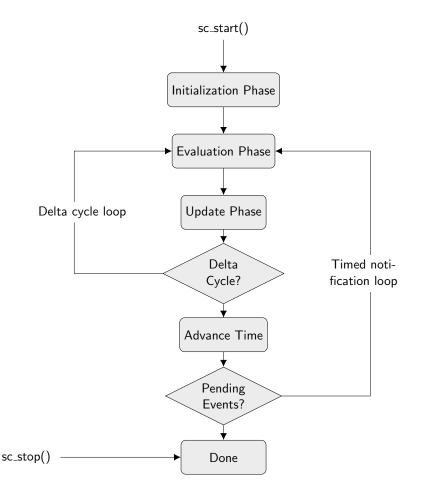

|          |     | 4.1.2   | SystemC's simulation core                                         | 36 |

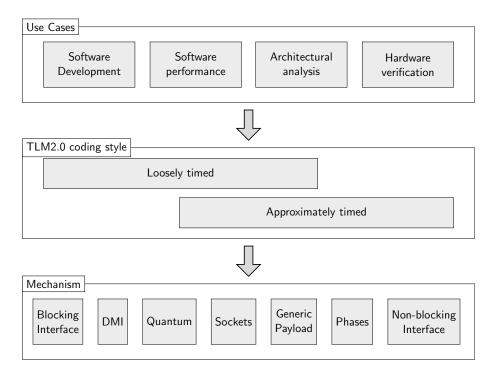

|          |     | 4.1.3   | SystemC TLM-2.0                                                   | 37 |

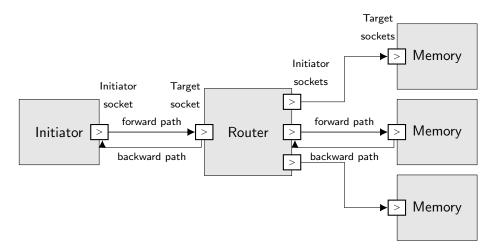

|          |     | 4.1.4   | System design with SystemC TLM-2.0                                | 40 |

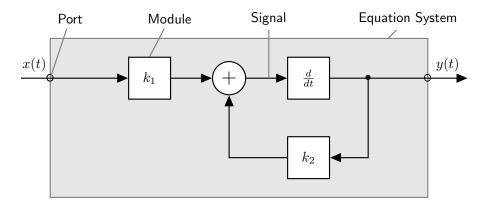

|          |     | 4.1.5   | SystemC AMS                                                       | 42 |

|          |     | 4.1.6   | The use of SystemC AMS in SysCore                                 | 45 |

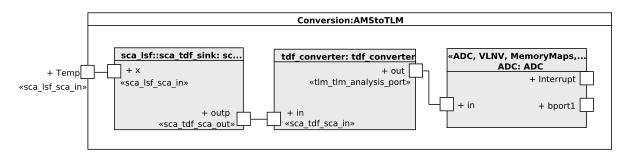

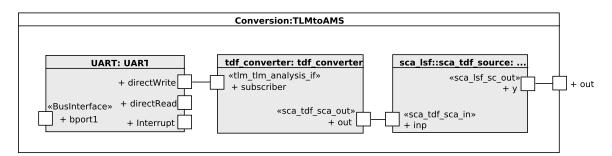

|          |     | 4.1.7   | Connecting SystemC TLM-2.0 with SystemC AMS models                | 47 |

|          | 4.2 | -       | Virtual Platforms                                                 | 49 |

|          |     | 4.2.1   | OVP's core technologies                                           | 50 |

|          |     | 4.2.2   | OVP models in SystemC TLM-2.0 platforms                           | 52 |

|          |     | 4.2.3   | iGen - tool control language                                      | 53 |

|          | 4.3 |         | ical modeling languages                                           | 55 |

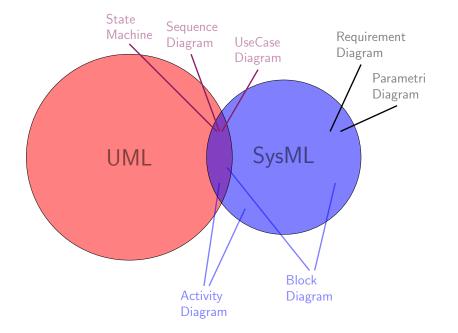

|          |     | 4.3.1   | UML                                                               | 55 |

|          |     | 4.3.2   | SysML                                                             | 56 |

|          |     | 4.3.3   | MARTE                                                             | 57 |

|          | 4.4 | Integra | ated development environment                                      | 58 |

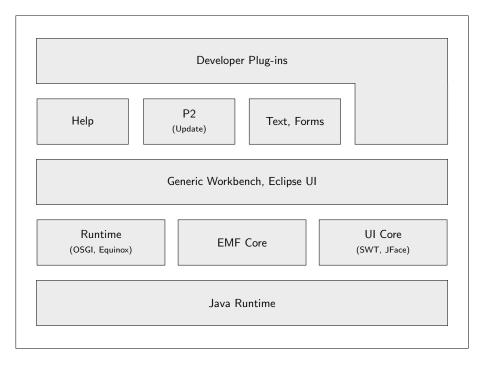

|          |     | 4.4.1   | Eclipse IDE                                                       | 58 |

|          |     | 4.4.2   | Papyrus UML editor                                                | 60 |

| <b>5</b> | Imp | lemen   | tation                                                            | 61 |

|          | 5.1 | Toolch  | ain for virtual hardware prototyping in SHARC                     | 61 |

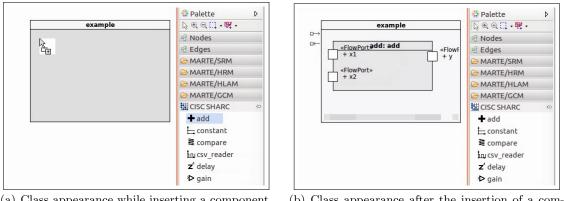

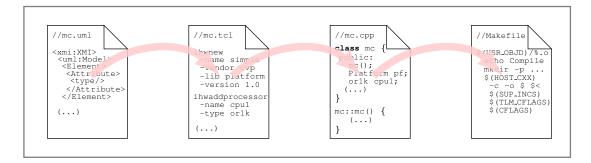

|          |     | 5.1.1   | Graphical representation of virtual hardware prototypes           | 62 |

|          |     | 5.1.2   | Integrating an OVP platform into the SysCore simulation framework | 69 |

|          |     | 5.1.3   | Use of OVP library models                                         | 72 |

|          | 5.2 | Exam    | ble platform for a battery management system                      | 74 |

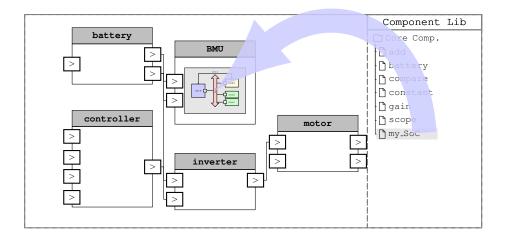

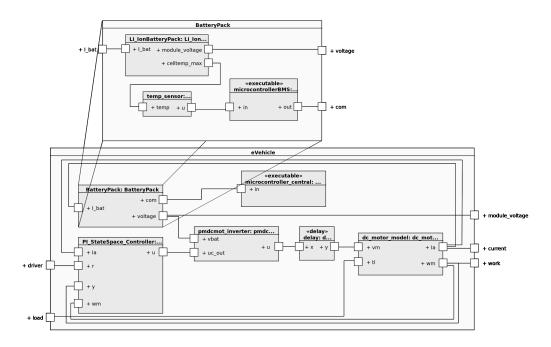

|          |     | 5.2.1   | Enhancing the eVehicle example by using temperature observation . | 75 |

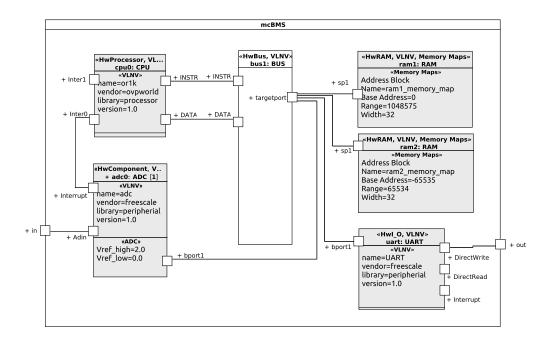

|          |     | 5.2.2   | Definition of the hardware platform used in the BMS               | 75 |

|          |     | 5.2.3   | Software running on the defined platform                          | 76 |

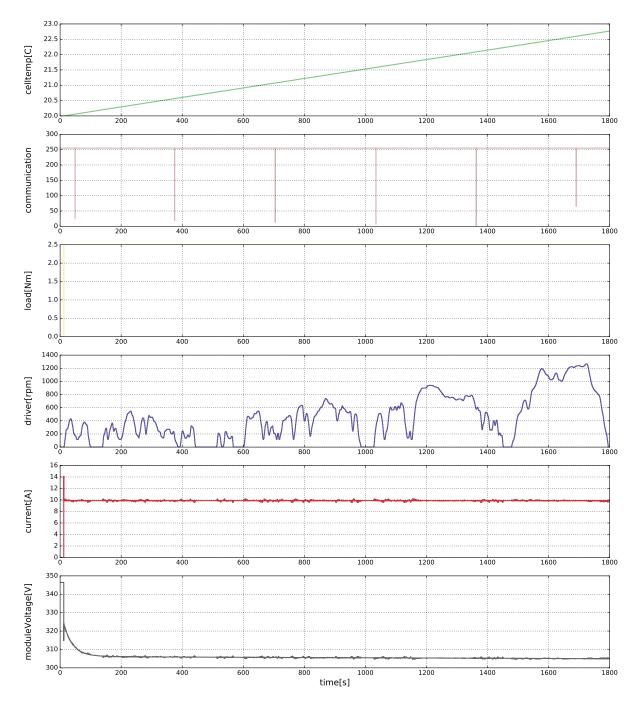

|          |     | 5.2.4   | Simulation with standardized input                                | 77 |

| 6        | Con | clusio  | n                                                                 | 80 |

# Bibliography

VI

$\mathbf{82}$

# List of Figures

| 1.1                                                              | Conceptual mockup for the integration of virtual hardware platforms                                                                                                                                                                                                                                    | 4                            |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| $2.1 \\ 2.2 \\ 2.3$                                              | Market penetration of different electric components in vehicles                                                                                                                                                                                                                                        | 11<br>14<br>19               |

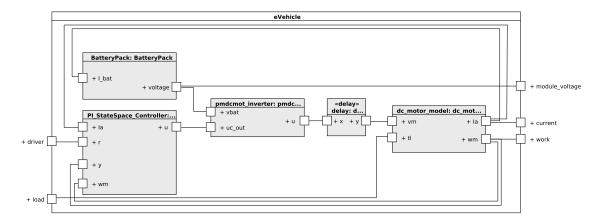

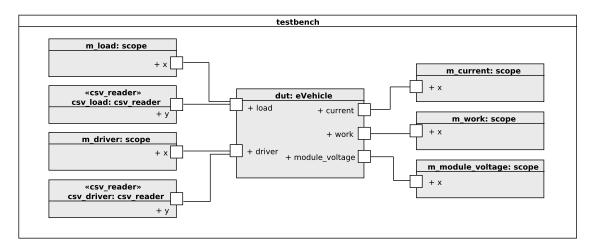

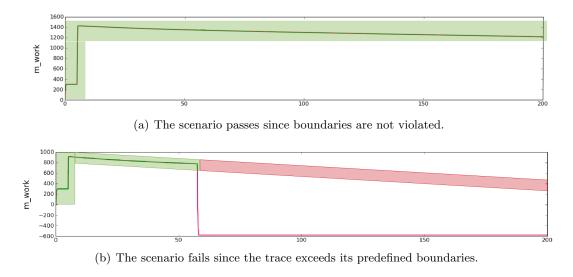

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                  | Different views on an ISO 26262 item, defined with EAST-ADL [19] Graphical model of an electric vehicle, which was modeled in SHARC Instantiating a SysCore component from the palette Automatically generated testbench, containing DUT, drivers and monitors. Examples for the observation of traces | 24<br>29<br>30<br>31<br>32   |

| $ \begin{array}{r} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \end{array} $ | Architecture of SystemC's core components, as described in [9] State chart of the SystemC scheduler [9]                                                                                                                                                                                                | 34<br>38<br>40<br>41         |

| $4.6 \\ 4.7 \\ 4.8 \\ 4.9$                                       | lation [8].Example of a LSF cluster as described in [8]Graphical equivalent to the TCL description in listing 4.4.Distinction between SysML and UML [7]Structure of the Eclipse IDE [50]                                                                                                               | $43 \\ 45 \\ 54 \\ 57 \\ 59$ |

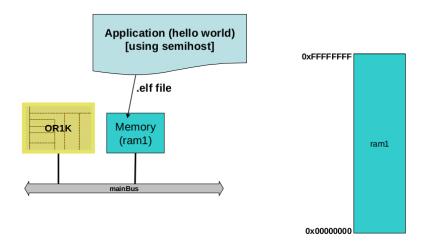

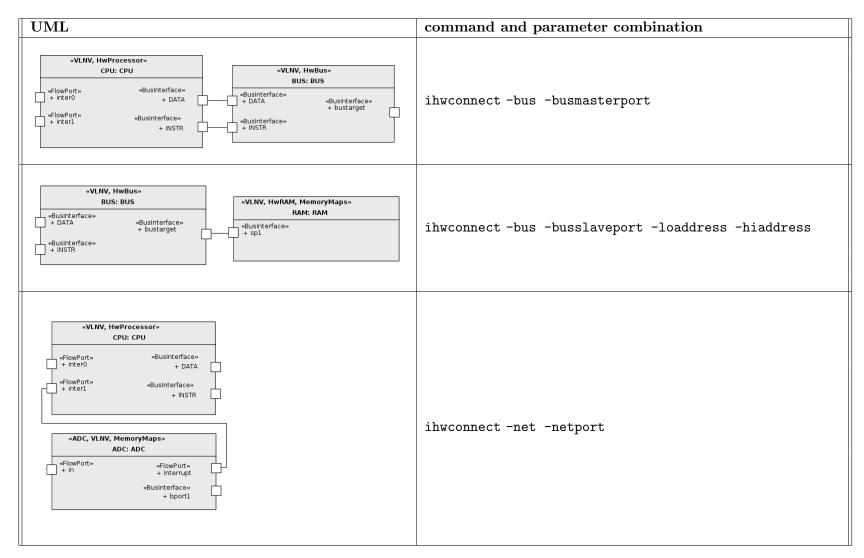

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4 \\ 5.5$                                | Toolchain to integrate a platform description in SysCore                                                                                                                                                                                                                                               | 62<br>68<br>71<br>76<br>77   |

| 5.6                                                              | Simulation result with the WLTP driving maneuver                                                                                                                                                                                                                                                       | 79                           |

# List of Tables

| 2.1 | Implementation examples of window lifters in a vehicle              | 10 |

|-----|---------------------------------------------------------------------|----|

| 5.1 | Defined stereotypes to establish TCL compliance                     | 64 |

| 5.2 | Defined enumerations, used in table 5.1                             | 64 |

| 5.3 | Defined hardware types, used for the graphical platform description | 65 |

| 5.4 | TCL commands to instantiate components.                             | 66 |

| 5.5 | TCL commands to connect components                                  | 67 |

| 5.6 | TCL commands to parameterize instantiated components                | 68 |

| 5.7 | Most important registers of the UART model                          | 73 |

| 5.8 | Most important registers of the ADC model.                          | 74 |

# Listings

| 4.1 | Typical structure of a TDF module.                                | 44 |

|-----|-------------------------------------------------------------------|----|

| 4.2 | Interface implementation to use SystemC AMS components in SysCore | 46 |

| 4.3 | Example how to embed TDF in LSF modules                           | 48 |

| 4.4 | Example of a TCL file to describe an OVP platform                 | 54 |

|     |                                                                   |    |

# Chapter 1

# Introduction

This thesis describes an approach to enhance cyber-physical system (CPS) development. The work was launched in the context of the SHARC project [55], which has the aim to allow system modeling in one single Integrated Development Environment (IDE). SHARC stands for *Simulation and Verification of Hierarchical Embedded Microelectronic Systems*; it uses graphical descriptions to represent a system and enables the simulation in a very early design phase. The SHARC IDE is based on a mapping between graphical Unified Modeling Language (UML) blocks and executables, which implement their functionality in SystemC Analog Mixed Signal (AMS). Previous works on this project have shown that the connection of the individual UML blocks contains enough information to generate an executable system [53]. The work in hand describes a way of how to extend the existing SHARC IDE by using virtual hardware prototyping. This approach enables more accurate descriptions and increases, therefore, the granularity of the developed system. Simulating such systems gains additional information, which has an impact on the overall design process.

The introduction provides a short overview about the underlying motivation and necessity for the written master thesis. Further on the reader can find the description of a predefined goal for this work and finally an outline in different chapters.

### 1.1 Motivation

Since the performance of electronic components is continuously improved and their size decreases at the same time, the application area has changed considerably in recent years. Microelectronics are widely used in all technical disciplines and enable the realization of novel functionality. One area that is particularly affected by this development is the automotive industry. A few decades ago, a vehicle consisted of mechanical components only. As the desire for more comfort became greater and meant also a market advantage, new approaches were achieved in the early 1980s and electrical/electronic systems were installed in cars more often. Due to technical advances, this approach became more important over the past years, resulting in a shift to an interdisciplinary development. In the meantime almost any innovation is implemented by means of computer-aided systems and the development towards electric vehicles and self-driving cars will lead to a further demand for interdisciplinary cooperation. The interaction of the physical environment with electronics is often referred as cyber-physical. The development of such systems requires, therefore, the interdisciplinary cooperation between mechanical/electrical engineers and computer scientists. These requirements present new challenges and problems for the development process. Therefore, efforts are being made to define functional specifications at a high level of abstraction to allow descriptions with many views on a single item. Those descriptions may be used by domain experts to further increase the granularity of the developed system. The original approach of so-called model-driven engineering arose in software development, but now it is also entering the system design.

No matter what engineering discipline, modern development happens in a virtual environment. An important concept is the simulation of the developed design, as it gives a first insight. Problems arise in this context mainly through stand-alone development, without taking the application environment into account. Conceptually, this requires the use of simulations at a high abstraction level, such that faulty designs can be found and respective countermeasures can be set in early design phases.

SystemC, a C++ library with different extensions was designed to cover these issues and allows to increase the granularity of systems continuously through the whole development process, without changing simulation nor development environments. Refinements on hardware/software systems are generally done in different steps, beginning from models that are synchronized via communication down to cycle-accurate descriptions. However, the original SystemC simulation kernel was not designed to simulate analog/continuous-time signals. Therefore SystemC AMS [8] was developed upon the needs to define models of physical systems. Due to the same underlying simulation principles, SystemC provides possibilities for the co-simulation of hardware/software system models and their physical environments, designed with SystemC AMS.

As already mentioned, the requirements for the development of cyber-physical systems must be seen differently. A system model has to cover the physical as well as the digital world. The developed SHARC framework is based upon an existing simulation environment for analog mixed signal models defined in SystemC AMS. This leads to the necessity for the integration of virtual hardware prototypes into the existing simulator to cover full system design and allow further software development on target platforms in early design phases.

### 1.2 Objective

The outlined goal of the work in hand is the integration of virtual hardware prototypes into the given SystemC simulation environment, on which application software/firmware can be tested. Relying on the previous projects, similar approaches should be used to create those virtual hardware platforms. Meaning that graphical description should be sufficient to describe a so-called system on chip (SoC), which can be embedded in the simulation environment.

In contrast to the current approach, an existing library should be used which provides a large number of hardware models from different manufacturers. A further criterion is the possibility of the elegant co-simulation of digital and analog/mixed signal models. The Open Virtual Platforms (OVP) framework was chosen since it meets both criteria and provides additional tools which facilitate the platform development.

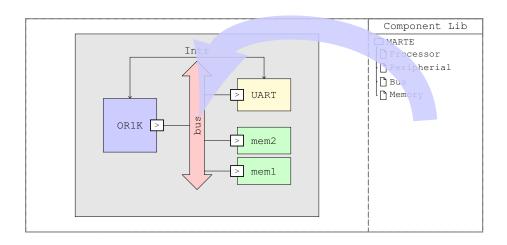

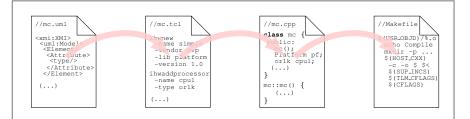

Thus the concepts to extend the used IDE, which is an Eclipse Rich Client Platform, should be developed and described in this thesis. Previous works on this project have shown how to extend the IDE, by Eclipse's plug-in mechanism. In a similar way, a toolchain should be implemented which derives necessary information of the graphical platform representations, such that it can be translated to compilable SystemC Code. For the integration of the generated platform description, the implementation of the software interface will be required. All these steps should be done automatically and lead to a representative UML block of the OVP platform, which can be integrated into the simulation platform, together with other components. A conceptional mockup of the toolchain can be seen in figure 1.1. One main challenge within this project is, however, the definition of interfaces between SystemC AMS and the OVP platform with an underlying SystemC TLM-2.0 (Transaction Level Modeling in its second version) description.

The main use case of the SHARC platform is a simplified electric vehicle (eVehicle), where the driving speed and the road load influence the system behavior. The commercial success of electric cars in the next few years depends primarily on the deployed batteries; in this context particularly the range and the durability are important. In addition, also reliability and safety have to be ensured since failures might have harmful effects on traffic occupants. The eVehicle model uses, therefore, a detailed lithium-ion battery pack, which computes internally the new state of charge, the temperature, and the module voltage. In order to guarantee safety, so-called battery management systems (BMS) are assembled, which control and monitor the behavior of the battery. A BMS is a typical application for a cyber-physical system and is, therefore, used as a use case to demonstrate and test the introduced approach.

Figure 1.1: Schematic representation for the necessary steps to integrate virtual hardware platforms into the existing simulation and modeling framework.

### 1.3 Outline

Chapter 2 provides an insight into the most important concepts used in the context of this thesis. The term cyber-physical system is introduced first. Challenges arising in this area are shown by means of development standards in the automotive sector. Another important topic is the explanation of modeling approaches on which system simulations are carried out. Finally, this chapter concludes with the concept of hardware design for the creation of virtual hardware prototypes.

The third chapter deals with state-of-the-art methods for the development of cyber-physical systems and the need for stronger cooperations between different development groups and simulation tools. Furthermore, the previous work on this project will be examined. This includes modeling in SystemC and UML, as well as the possibilities of cloud-based verification.

Chapter 4 presents the corresponding design of the work. First, the reader will find an introduction to the system description language SystemC with the distinction in SystemC AMS and SystemC TLM-2.0. Further on, Open Virtual Platforms, the library, and simulation framework for the creation of the virtual hardware prototypes in this work is discussed. UML and its extension MARTE (Modeling and Analysis of Real Time and Embedded systems) offer possibilities for graphical modeling of the used hardware components, thus both modeling languages will be explained briefly. Finally, this chapter gives a short overview of Eclipse and its UML editor Papyrus, which was enhanced in this project via plug-ins.

Chapter 5 provides an overview of the implementation concepts of this work. One component is the mapping between graphical UML descriptions and components that can be used to describe hardware platforms. Furthermore, the reader will find a description of how those created models can be embedded in the existing simulation framework, which allows the simulation of an entire cyber-physical system model. Furthermore, a concrete example is sketched in which the granularity of an existing system is increased by the integration of communicating hardware platforms.

The sixth and final chapter provides a summary of the achievements and a comprehensive outlook on future projects that can be realized in this context.

# Chapter 2

# Background

This chapter opens with a discussion of the context in which the present work has been written. Thus it provides a scientific definition of the term cyber-physical system, the developmental history, as well as the staidly growing challenges in this area. These challenges are highlighted by the means of the ISO 26262, a standard for the development of electronic driving assistance systems in the automotive sector, which is becoming of greater importance. Thereafter, some development methods are shown which have proved themselves over the years in the various fields and are used in the realization of cyber-physical systems and in compliance with standards such as the ISO 26262. Due to the outlined goal, which is to integrate virtual hardware prototypes into the existing simulation framework, the terms virtual models respectively prototypes have to be explained in more detail. The chapter is concluded with an introduction to hardware descriptions on different levels of abstraction and an overview of basic components for a simple computing platform, such as processors, memories or a bus system.

# 2.1 Cyber-physical systems

This thesis was written as part of a project with the aim to develop a framework to enhance cyber-physical system design. Therefore definition and evolution of CPS should introduce the domain and further on illustrate the problems which arise within this field of work.

#### 2.1.1 Definition

Through the last decades, a clear trend in the evolution of computation could be seen. In the mainframe era, people worked together with one computer, later on, this changed to the usage of workstation computers for each person in the nineties. But even during the early nineties researchers like Mark D. Weiser, chief scientist at Xerox PARC, saw a further evolution of computing, such that it will become a ubiquitous part of our everyday life. In [52] he predicted the evolution of future computing, similar to the technical development of small and efficient electric motors at the beginning of the twentieth century. In that time it got possible to give machines their own motive force, which was in contrast to the approach of using a system of shafts and pulleys which were connected to one central engine. Analog to this technical evolution he predicted:

Specialized elements of hardware and software, connected by wires, radio waves and infrared, will be so ubiquitous that no one will notice their presence.

From today's perspective, his prediction should be right; and although a big media focus is set on customer devices such as smart phones, from an engineering perspective the steadily increasing amount of microelectronics, assembled in nano-world to large-scale wide-area systems are of bigger interest. Shrinking processor sizes and less power consumption give the impression of disappearance for users and this trend is crucial for the ubiquity of computer aided systems.

Due to this fact, the last years of computer engineering were characterized by different trends and key words. The term embedded system, for instance, characterizes a computer system with a dedicated application, assembled in a larger electrical or mechanical system. The range of embedded systems reaches from simple portable devices, with a single microcontroller to large complex systems, consisting of a variety of peripherals and networks, e.g. vehicles and avionics.

Another key word which arose in the last few years is the terminology of so-called cyberphysical systems, which is the combination of physical devices, known as the plant, with computers. In that sense, feedback loops, which monitor the environment affect the computations and vice versa [56, 25]. In that manner, CPS are a certain kind of embedded systems with the requirement to be real-time capable. Applications of CPS can often be found in distributed environments and its components have to fulfill requirements with respect to performance, availability, safety, and security. These properties should also hold for the communication with CPSs, which can be wire-bound or wireless [46]. A very accurate description can be found in [36], the authors boil the nature of CPS down to an essence. The way of computing in CPS is in somehow different since it has to cope mainly with the uncertainty and the noise in the dynamic physical environment. Further on failures in both domains have to be compensated. This is aggravated by the fact that CPS vary in scale and complexity. The development requires structured methods and powerful tools, such that accidents and failures can be canceled out and robust systems emerge.

A closer look at the properties of CPS shows that they cannot be associated with a certain field of research. Sztipanovits [48] claims for instance that the research on CPS has to be

done at the intersection of physical, biological, engineering and information sciences. This approach implies that system designers have to cope with a large heterogeneity of different components and combine the requirements of different stakeholders.

#### 2.1.2 The evolution of CPS

Cyber-physical systems are not an invention of the current century. Right after the development of the Z3 by Conrad Zuse, he invented a system with the purpose to survey aircraft wings. Within this computing system, measured sensor values got processed by a computing unit. In this case, data became the variables in the application program. The first CPS was born [46].

Especially aviation has played a pioneering role in the development of embedded computing. In the 60s of the past century, the so-called space race between Russia and the United States of America has set new standards. In comparison to general purpose mainframes used in business, space missions required highly reliable computing systems, designed to fulfill certain functionality, whilst minimizing weight and size. Those demands led to the design of redundant systems, as well as the formal verification [49]. Other areas which affected the development of CPS were the development of robotics and factory automation in the late 70s and 80s. Through modern communication techniques, today's focus lies on the so-called Internet of Things, with the aim to share environmental information among other CPS. This leads in general to new possibilities, since synergy effects might be useable to build systems with totally different properties such as swarm intelligence. The enormous capabilities of this area can be seen in [44], it predicts that the IoT retail market will be almost 5 times bigger in 2025 than it was 10 years before. From this short timeline perspective, one can see that we have gained lots of know-how in the field of real-time and embedded systems engineering, but this trend does not seem to stop. In fact, quite the opposite is the case, the European Union, for instance, investigates substantial funds in the development of smart factories, which relies on the idea to handle complex dynamic manufacturing networks by connecting embedded electronics. Similar funding exist also in the USA, where the US National Science Foundation (NSF) supports projects on sensorbased autonomous systems, distributed robotics, autonomous vehicles and ambient assisted living since 2006. Also the German Federal Ministry of Education and Research has made some attempts to cope with the ongoing research by setting up a cooperative study project with the German industry to develop an Integrated research agenda Cyber-Physical Systems [46].

As Weiser predicted [52], the development of computing goes towards ubiquity and will transform how humans interact with the surrounding environment in the future.

#### 2.1.3 Challenges for the design of CPS

One of the most important development aspects of CPS is the field of its application. Naturally the design of CPS depends on the criticality of its application. In order to ensure the safety of CPS, standards were introduced, which must be followed by system developers. Standards have different advantages, on the one hand, they guarantee the transparency for costumers, on the other, they make errors detectable. In the case of failures, it protects companies which have provable followed the standard within their development process. One of the first safety standards was the domain-independent standard for functional safety of electrical/electronic/programmable electronic safety related systems (IEC 61508) [42]. This standard has been adapted by different domains such as railway, medical or nuclear power. One of the most important safety standards is specified by the ISO 26262, it contains the procedure for system development in the automotive field [20].

CPS are highly heterogeneous systems including mechanics as well as electronic components and corresponding software. Due to the properties of CPS, the design requires a interdisciplinary engineering approach, which makes it necessary that domain experts with different fields of expertise work together to realize a certain function. In contrast to the needs of general purpose computing, the control of dynamic systems such as physical processes requires different approaches, since they are sensitive to the feedback loop, and disturbance. Ignoring such aspects in early design phases might lead to failures and redesigns later on [31].

The research area of CPS focuses therefore on modeling approaches, which should lead to coherent designs, reusing existing components and models, as well as their analysis and verification. To cope with the mentioned issue of redesigns, the design on system level should already provide enough information to obtain the affection of the computation on the physical process and vice versa. Indispensable in this sense is the use of simulation tools and test benches, which are on the one hand capable to satisfy the needs of different stakeholders [46] and provide enough possibilities to model both environments, the physics as well as the electronics. A fundamental scientific and technological basis can lead to the final break through in the work on CPS. From an economical point of view especially time to market is crucial and has to be minimized. In addition, the development has to be in accordance with the given safety standards of the respective domain. According to [31], the central issue is to find methods, which guarantee that different project groups can work on different tasks in parallel and share their results.

#### 2.1.4 Automotive: Example for the usage of CPS

The application of CPS is of general purpose and can be seen in the context of simple systems such as robotic lawn mowers up to systems of high complexity like power plants.

However, especially the current trend in the automotive area, like the evolution towards electric vehicles and the development of self-driving cars justifies the emphasize in this industry on good design strategies, which include all aspects discussed in in the previous section.

#### Evolution and trends in the automotive industry

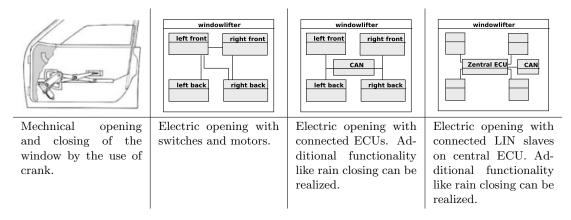

Through the last years, one could see a clear trend in the automotive area; most of the new innovative functions were caused by electronic systems. But not only new systems follow this trend, also pure mechanical systems got replaced by interconnected mechatronic systems. One illustrative example is therefore shown in table 2.1. It highlights the evolution of a window lifter, from mechanical to a fully connected solution of electronic control units (ECUs). In this case, the ECUs can retrieve further information of other ECUs. This makes it possible to implement further features, like automatically closing windows in case of rain [45].

Table 2.1: Examples for the implementation of a window lifter which is realized mechanically, electrically and electronically.

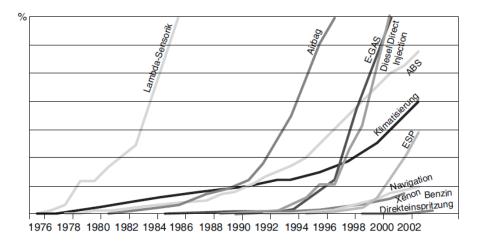

Besides the trend to mechatronic systems, almost all innovations, which make driving more convenient, rely on electronic control systems. Figure 2.1 shows that some of those additional features went through an exponential market penetration and are assembled in any car nowadays [45].

The increasing number of functions in vehicles implies the necessity to interconnect these electronics. Today's cars contain almost 100 ECUs, which build a complex computing network with various properties. But it is not only the variety of ECUs, it is also the increasing amount of transferred data, which let the industry be faced with huge challenges. From single bit transfers, used to switch gadgets on or off, communication goes towards

Figure 2.1: Time line for the market penetration of different electric components, which are assembled in modern vehicles [45].

streaming audio or video data, from multimedia sources or cameras. A view years ago the electronics of a car has been an encapsulated system. Especially now, in the days of IoT, intercommunication seems to be the next milestone for automotive systems. IoT requires to open systems and integrate multiple interfaces for the communication to the environment or traffic participants [45].

Through the communication to the internet, cars have also become targets for hackers. In their work on automotive security, the authors of [23] have identified and exploited potential security risks of the CAN bus. In this case, they were able to gain control over the motor controller and the braking system. Since this time, there has been an increasing number of publications in this area, which also led to many recalls by automobile manufacturers to close security gaps.

#### The aim of the functional safety standard ISO 26262 for road vehicles

As already mentioned, the ISO 26262 provides the essential guide for the development of electronic driving assistance systems in cars. The main goal is to define a so-called safety life cycle, which involves structured approaches that must be carried out during development, production, operation, maintenance, and disposal. The standardization is therefore divided into different parts, where 3 to 7 address the product life cycle. Part 4 is development on system level, part 5 describes approaches for development on hardware level and 6 the software development. Any development has to start with the definition of an item, which describes a tangible function of the vehicle. Having a constructive view on the item, it consists of an array of systems and their respective elements. In the case of the outlined electric window lifter, the item description would only contain the definition of the function itself. Namely, the centralized opening and closing of any window in any driving situation performed by the driver and on the other hand the automatic closing of the windows in case of rain. Furthermore, a functional concept, which contains the actuators, controllers, and sensors is designed for this purpose. Developers should also think about other interfaces, in this case, messages from a rain sensor to make decisions whether the window should be automatically closed.

In the next step, the so-called hazard analysis and risk assessment is performed. It is used to identify potential risks, arising from the defined item. In this case, scenarios are examined in which a malfunction would have serious consequences for involved parties. The hazardous event is classified by 3 different metrics: Firstly severity describes the potential damage for involved people. Secondly, the exposure of the event if it occurs and finally controllability of the hazardous event. The combination of those three assessments results in a so-called automotive safety integrity level (ASIL) for the considered event. A so-called Safety Goal is defined for the highest obtained ASIL, which refers to the function of the item itself. In the case of the window lifter, the window should not close when body parts of a person are in the opened window. There are many different constructive approaches to realize functional safety in this context.

#### Issues for the development of vehicle electronics

One should not forget that any development of the automotive industry is primarily driven by the price of the product and its time to market. One can imagine that the malfunction of an electronic power steering system has other consequences than a broken light in the sun visor. The development of components with a higher ASIL is always associated with a significant design overhead since such systems have to prove their full function at all times. For this reason, it is important to find design strategies, which shorten the development times and comply with the safety standard at the same time.

To guarantee comprehension, a further discussion of the development methodologies for digital systems in the automotive field is given in the following sections.

### 2.2 Development aspects of CPS

Especially the development of bigger systems led to the demand for structured development methods, which incorporates all sub-development steps, leading to an overall system.

Due to the fact that software has to cover very complex procedures, involving also knowledge from other domain experts, its development requires special treatment. Therefore research had been done on how to define good workflows, which bring the involved parties on one table. Nowadays it can be seen as some pioneering work, which is also adapted to other areas of system design that have to deal with similar issues. A big focus has always been on reuse and adoption of existing components, as well as defining requirements. In this sense, it is necessary to split up the overall system in sub-systems and find appropriate ways to define interfaces on which different developers, parts, and phases can rely on. Development strategies basically allocate human resources to certain activities and define the time interval in which the work should be done. Furthermore, they try to find concepts of how to define intermediate goals and how to ensure the quality of sub deliverables. For the development process, it is crucial that such methods guarantee the current status representation of the entire system.

It's quite common that the first development phase is considered to deal with the definition of system requirements. In contrast to that, the last state might have a wide range, varying from finalizing the development to the best way of disposal. Most system development methodologies rely on the principles of the waterfall model, described by Royce in the 70s of the previous century [38]. His approach shows a hierarchical structure of so-called implementation steps. Each step is finished by the definition of certain documents, which determine the starting point for the next phase. This concept includes the definition of requirements and goes towards design, coding, testing and the final delivery to customers. Another commonly used method is the so-called rapid application development, which was introduced by James Martin [29]. Martin breaks with the waterfall model and claims that almost any knowledge is gained during the implementation itself, which should be fed back to the initial requirements and the overall design. The execution/simulation of prototypes with limited functionality should indicate whether a design works or not.

#### V-Model

Putting an eye on the ISO 26262, the development methodology of electronic driving assistance systems is based on the V-model, which should be highlighted throughout this section. Its main idea relies on the waterfall model, but additionally, it integrates the idea of quality management, within the development phases. The bottom up approach reflects redundancy, which is a core concept of how to design safety-critical systems. Testing and verification can be seen as a way of monitoring the implementation.

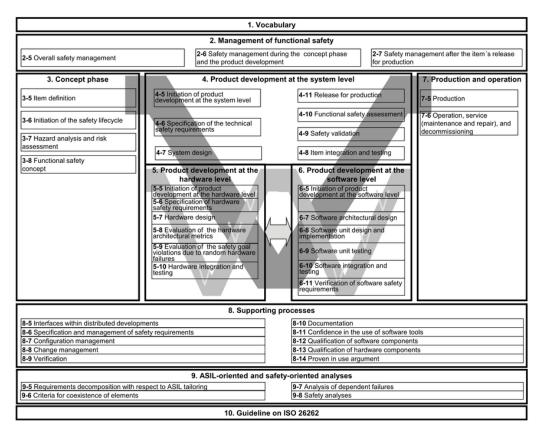

The V-model is often adopted to cope with the needs of certain domains. Thus it is used in the ISO 26262 standard [20] for the system development, as well as for hardware and software development. Figure 2.2 highlights the importance of the V-model for the standard. Similar to the waterfall model the granularity becomes more accurate in the

#### CHAPTER 2. BACKGROUND

development. Even if a V-model was designed to fulfill certain properties, the central aspect of the V-model is testing. Depending on the granularity of a system, one has to consider different test types. On the lowest level of abstraction testing is done on single components, thereafter tests concern the integration of components. Further on system tests, and finally, the validation with the initially defined system requirements/specification.

Figure 2.2: Representation of the v-model, which plays a central role throughout the realization of systems in compliance with the ISO 26262 [20].

## 2.3 Models

Table 2.1 shows the schematic representation of a window lifting system, which might be assembled in modern vehicles. Although these representations vary in their working principles, they have in common that they represent an abstract view of a real system. Models play a central role in the system development, but depending on the context of the working group, they are often seen in different ways. Therefore the terminology following Stachowiak [43] is provided:

- **Mapping**: The model is always an abstraction of an original, which might have to be constructed or remains completely imaginary.

- **Reduction**: A model specifies the necessary properties of its subject. In the model representation always some reduction of reality.

- **Pragmatic**: Models fulfill a replacement functionality which means that a model can be used instead of the original with respect to a certain purpose.

A model is a simplified representation of the reality. It allows scientists and engineers to make predictions. The main challenge for a designer is however to find a good trade-off between complexity and sufficiency, which always depends on the requirements for a certain design. Models are not only used to create designs and documentations. A common trend can be seen in their capabilities to make model-based analysis and diagnostics. In general, models are used to define dependencies and information in a real or virtual context. If relations emerge from reality, they have to be put together in the virtual environment and with an appropriate semantically interpretation [19].

Depending on the field of work, people have different understandings of the terminology and therefore two different views have to be introduced. The first term is the so-called model-driven engineering (MDE) respectively model-driven development (MDD), which is introduced as software development methodology. In contradiction to this, the terminology model-based design (MBD) describes a commonly used methodology to design control, signal processing or communication systems and has a certain importance for mechanical respectively electrical engineers. Due to the fact that the design of CPS requires an interdisciplinary cooperation, there is ongoing research on how to combine both approaches. One attempt to bring those approaches together has been presented in [53].

#### 2.3.1 Model-driven engineering/development

Model-driven engineering is a software development methodology, with the aim to create models focusing on design perspectives. It should basically help to enhance the communication between different teams, working on the realization of a common goal. From a very abstract view, one can declare a modeling paradigm for MDE as effective, if it provides all information for developers who are in charge of the implementation [22]. Model-driven development in comparison goes even a step further, in that case, the models become essential artifacts and provide more than just an abstract design representation. Detailed model descriptions allow system/software development through model transformation techniques, such that models on a higher level of abstraction can be transformed to low-level models. The goal is to reach a description, which contains enough information to execute the model either through an interpreter or code generation [22]. Through the representation of a model on different levels of abstraction, MDE increases the automation in the program development process. In many cases, so-called graphical modeling languages, like UML, its extension MARTE or SysML (Systems Modeling Language) are used. Graphical modeling languages are extensively covered in section 4.3. The main concept of modeling languages is however the use of abstract and concrete syntax descriptions, a mapping between those and a semantic description. A description can however also be textual, this concept was used for the instantiation of the hardware platform. The respective description can be found in 4.2.3.

#### 2.3.2 Model-based design

MBD is used in a different context than MDE/MDD and those terminologies should not get mixed. The meaning of MBD follows Aarenstrup [37].

The difference lies mainly in the context of the model itself. MBDs concern physical models which are designed for simulation purpose only, where MDE/MDD is used to describe software architectures and control flows. MBD places the model as the central component for the development of control units, signal processing, communication and other dynamic parts of the system. Therefore their working principles have to be seen differently. Models created by MBD consist mainly of basic mathematical functions, which allow the calculation of system properties at a certain time. The first challenge is, therefore, how to define the system in an abstract/algorithmic way. The second challenge is the question of how to realize the developed control units and integrate them in the real physical process. In the best case, the whole design flow can be done within one environment.

Aarenstrup provides an illustrative example of how the development of a motor controller might look like when using model-based design. Typically the overall system is split up in the plant/environment, which is a model of the engine on one hand and on the other an algorithmic description of the controller. The next step is determined by testing the high-level system with different input scenarios and verify the outputs. Furthermore, if the team is sure that the model is working correctly, more details would be added to the system and again tested continuously by simulation. This term is known as model elaboration, which should guarantee testing over the entire development process. One of the most critical parts is, however, the switch from the continuous to discrete-time, meaning the transformation from an algorithmic controller description into a hardware/software system. Increasing granularity should lead to the definition of accurate embedded software which can later be integrated into rapid prototypes and HiL (hardware in the loop) testing. Accurate models should even be able to develop production code. Casting an eve on the ISO 26262, the transformation is very difficult and can hardly be automated, especially since designed systems have to meet safety-critical requirements, which require a lot of engineering sensitivity.

#### 2.3.3 Virtual electronic/hardware prototypes

As already mentioned in the previous section, prototyping plays a central role for MBD, which leads to the necessity of clarification. It describes the methodology to build preliminary models, in an early design phase. Those models allow first predictions of faulty designs, which would cause higher costs through redesigns. In literature often the terminologies rapid and virtual prototyping arise, which are different in their meaning. The term rapid prototyping is commonly used in production engineering since it basically describes the approach of a fast fabrication of a physical model, which is usually represented by a three-dimensional computer aided design (CAD). Due to new technology approaches, like 3D printing, it has gained a lot of attention and is mainly used in this context. Within MBD the term rapid prototyping describes mainly code generation from a virtual system description, which should be executed on real hardware [51] and tested within the real physical environment. Virtual prototypes, on the other hand, try to define pure virtual models of a system, which can be executed on a host. From its simulation, designers can draw conclusions of the current development stage. Both techniques affect almost any modern engineering approach, but since the focus of the thesis in hand was mainly set on the integration of virtual hardware prototypes into an existing simulation framework, main aspects of their development are addressed in the following section.

## 2.4 Modeling of digital systems

The term integrated electronic systems denotes a system which consists of two parts. These are, on the one hand, the microelectronic hardware and on the other hand the corresponding software. The hardware components are known as integrated circuits (ICs). A commonly used term in the field of CPS is the so-called System on Chip (SoC). It is an integration of different sub-components like microprocessors, memories and different kind of peripherals on a single chip. The communication of those components is typically achieved by a bus system. SoCs are commonly designed to monitor and control the plant of a CPS, a core component is, therefore, the Analog Digital Converter (ADC).

As already mentioned, besides the microelectronic hardware, the requirements for the software components increase continuously. A certain application is commonly executed on a real-time operating system, which provides necessary drivers for the communication to integrated peripherals. Because of the necessity to implement safety mechanisms, application software is getting more complex and therefore its design might exceed the hardware design significantly. Due to that fact, there is a high demand for the software development to start in early phases. As already mentioned, the common approach to cope with this issue is the use of virtual hardware prototypes.

Before we dive into details about how to model hardware platforms, the concept of abstraction in digital systems should be explained first since it is crucial for the comprehension of digital system designs.

#### 2.4.1 Abstraction layers

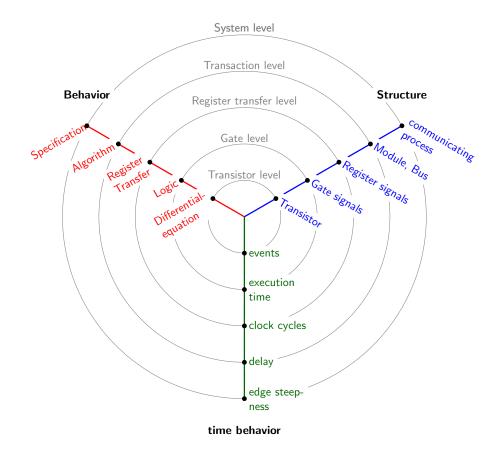

One term, that is of central interest, when talking about digital hardware systems, is the term of abstraction. In the 1960s and 1970s, the development of digital systems was mainly established by the usage of functional tables with boolean equations, from which circuits could be deduced. This approach changed with the invention of so-called hardware description languages (HDLs), like VHDL and Verilog in the 80s. Instead of connecting gates, the structural behavior of the hardware is described on the so-called register transfer level (RTL). The development of electronics on the RTL is still of common interest. Through the last 10 years, new approaches emerged, however, with the aim to define layers with a higher grade of abstraction, such as electronic system level design and transaction level modeling (TLM). A common representation of those different abstraction layers is given by the Gajski-Kuhn chart shown in figure 2.3. It visualizes the properties of 3 different domains, namely structural, behavioral and timing on the different layers.

#### Register Transfer Level (RTL)

An RTL model describes the micro architecture of the hardware, which is the structure of clocked registers and flip-flops, as well as the unclocked combinatoric logic. In comparison to the abstraction on gate level, the time delay is not modeled, but instead only the moment when the clock changes is used. Therefore RTL models are clock cycle-accurate, meaning that a real chip would need the same amount of cycles for the execution of a certain task as the developed model. The success of RTL is mainly caused by the fact that such models can be synthesized to gate level, which can then be realized on an application-specific integrated circuit (ASIC) or field-programmable gate array (FPGA). However, Such an approach can be compared with compiling source code to a dedicated platform. Therefore it can be seen as the standard approach for hardware development.

#### Transaction Level Modeling (TLM)

TLM is in general not subject to such a strict timing behavior as RTL. The term 'level' might be misleading in this context and should, therefore, be seen more like a modeling

Figure 2.3: Modified Gajski-Kuhn Y-Diagramm [21].

technique [21]. TLM focuses on communication, meaning the bus connection, of dataprocessing units like processors, memories, and peripherals. The crucial point is the decoupling of data transaction and data processing. On RTL a bus model includes all signals in a cycle-accurate manner, TLM, on the other hand, does not have cycles. The communication is established through so-called channels, which implement callback functions. The main advantage of bus abstraction and clock decoupling can be seen in the fact that TLM systems can be simulated more efficiently than RTL systems. Modeling of user registers in peripherals is still done on TLM, this is in general accurate enough to develop application software for the platform. The rest of the functionality is still not written in the way of an RTL micro-architecture, it is more an algorithmic model which is implemented like a software function.

#### System Level Design

The system level is part of the design phase, where hardware and software functionality are not fully split up. More or less the main aim is to translate the specification in a model which can be independent from any time behavior [21]. This approach is called hardware/software co-design, and tries to focus on the requirements of the digital system itself. System Level Design can be seen as the transition from system to the hardware development, which is also shown in figure 2.2.

#### 2.4.2 Execution performance

The performance of a simulation model can be verified and compared by measuring the execution time on a computer. One of the big problems in the simulation is that the program tools run on an operating system with concurrent programs. Furthermore, the simulation time depends mainly on the abstraction level of the model, resulting in larger simulation times for precise ones. The simulation time of an RTL model can differ from the execution time on real hardware by a factor of 100.000. RTL models are mostly not convenient for the development of system architectures and software, thus it is required to detach them from strict timing behavior, towards a more abstract way provided by TLM [21].

#### 2.4.3 Components of virtual hardware platforms

The outlined goal of this thesis is the enhancement of the existing modeling framework by providing the capability to integrate computing platform into existing CPS models. As described in the previous section the simulation performance depends on the accuracy of the given model. Since we want to gain further details about the overall system and use them for a software development process, those platforms should be defined as TL-models. In compliance with Wolf [56] necessary components of a computing platform are defined as follows :

• **Processors:** Central processing units (CPUs) are defined by their instruction sets, which implement hardware functions. The software is nothing else than a sequence of instructions that can implement any kind of algorithm on a computing platform. The algorithm which established those capabilities is the so-called fetch-execute algorithm. As the name indicates, instructions are first decoded and then executed. This is the main idea and power behind modern computing, changing the instructions leads to a different behavior, without reimplementing hardware functionality. Basic computing platforms, such as the von Neumann or Harvard Architecture, consist of a CPU and one or two memories. Memories generally hold data and instructions, where

the CPU itself has several internal registers, which store values, necessary for the computation. A register that is of certain interest is the program counter (PC). It is an address pointer to the instruction that should be executed next. High-performance simulations can only be achieved, when all components of a platform are modeled on a high level of abstraction. A common approach for CPU models is the usage of so-called instruction set simulators (ISS) which have the capabilities to execute the compiled binary code.

- Bus system: To establish a communication between CPU, memories and other peripherals a so-called bus system and respective protocols are needed. The communication between two devices is established by the so-called four-cycle handshake, which ensures that both parties are ready to transmit and receive data. In the common case, the CPU would be in the middle of any transaction, thinking of loading data from a fast I/O device into the memory, involvement of the CPU is not necessary. Direct memory access (DMA) addresses this issue and allows direct reads and writes to memory regions. Hardware components such as CPUs and DMAs can initiate bus communications and therefore they are known as bus masters. Components that can be addressed are so-called slaves. As already mentioned in the previous section, the main bottle neck, when simulating virtual hardware platforms on RTL, is the cycle-accurate communication between all components. Exactly this problem of device communication is addressed by TLM, with a higher level of abstraction.

- Memory: Memories are commonly organized as two-dimensional arrays, where a row and column address one bit. In computing systems especially random-access memories (RAM) are of certain interest because they can be read and written. Modern systems mainly use dynamic RAM, which exists in various types. They have the property to be fast, but decay over time, such that they have to be refreshed every few microseconds. Another commonly used memory type in the field of embedded systems is flash memory, which is a so-called read-only memory (ROM). ROMs are commonly used to store binaries and data, which are not changed by an application.

- Input/Output Devices: Components which are of certain interest are input and output devices (I/Os). They are necessary to interact with the environment and consist mainly of some analog parts. To establish a communication interface between I/Os and CPUs, registers are used that can be accessed by the CPU. The most common way to establish the communication between an I/O device and a processor is memory-mapped I/O. The approach of memory-mapped I/O is the usage of addresses, with which the registers of a device can be accessed. In this case the CPU can use normal reads and writes to access data. From a programmers view there are mainly two approaches of how data from I/Os can be retrieved:

- Busy wait is a very naive approach for the communication between I/Os and CPUs. In this case the CPU is continuously checking the status register of the

device. This is also well-known as polling. Generally this approach is extremely inefficient and consumes lots of computing resources.

- Interrupts are more elegant in comparison to busy waits. Interrupts inform the CPU about the occurrence of a certain event, and forces it to execute the so-called interrupt service routine (ISR). If an interrupt occurs it has to be guaranteed that the execution of the foreground program can be continued. This is done by saving the PC and return to it after the execution of the ISR.

# Chapter 3

# **Related work**

First of all this chapter provides an overview of state-of-the-art methods for the development of CPS. The first part introduces a tool, which makes use of the MDE paradigm. The next part addresses state-of-the-art approaches for virtual prototyping, the role of SystemC, and respective solutions of leading EDA (electronic design automation) companies. Another part which has to be discussed is the term co-simulation, its importance and how it is applied to certain problems. An example of an industrial cooperation shows the need of leading simulation tools to work closer together.

Secondly, the previous work on the SHARC IDE and its simulation framework SysCore is highlighted. It combines MDE with MBD by using UML and SystemC AMS. This part should give a basic introduction to the working principles, which are used in chapter 4 and 5. The capabilities for modeling, simulation and verification are summarized.

### 3.1 Modeling electronics in compliance with the ISO 26262

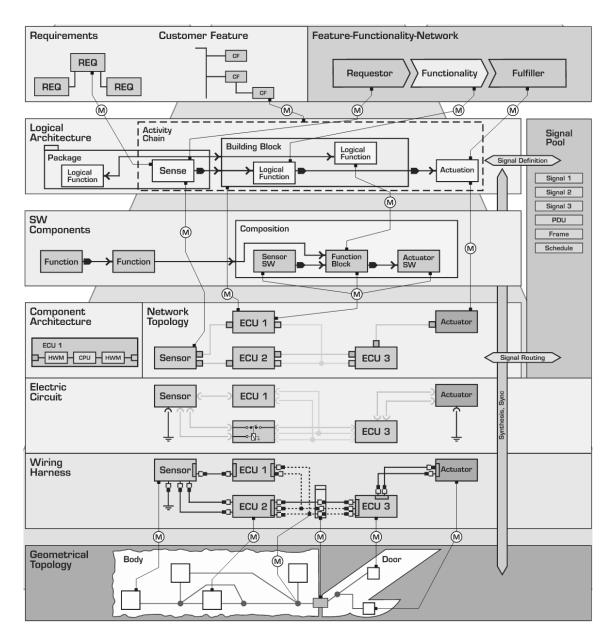

As already mentioned, the ISO 26262 strongly restricts the methods for the design of CPS in the automotive industry and places the safety goal in the center of any development. Individual steps, which are defined in the system design, should be accessible by all project groups and define guidelines for the constructive design. Hillenbrand [19] introduces the tool PREEvision, developed by the Daimler AG and obeying the presented paradigm of MDE. Therefore a defined item is represented at different abstraction levels, the description language is EAST-ADL (Architecture Description Language), an extension of UML, developed to model electronic components in the automotive industry [11]. Figure 3.1 illustrates the schematic structure of the modeling language, which can be used to refine the system.

Figure 3.1: Different views on an item, defined with the modeling language EAST-ADL, which was designed to be compliant with the development requirements of ISO 26262 [19].

The different abstraction layers are described as follows:

• The requirements layer defines the requirements of the developed item in text

form. Additionally, those descriptions can be set in relationships, which further leads to the representation of an entire network.

- Logical Architecture is used to create the concept of an item. In this case individual components and their connections are represented. This illustration, however, does not reveal anything about the use of hardware and software.

- With the **software components**, a concept for application software can be created. It is used for the representation of functions, communication interfaces, as well as logical and functional dependencies which arise during the implementation of the application. Communication is established via ports, which define interfaces and the corresponding communicated signals. Furthermore, this guarantees hierarchical compositions for structuring.

- The illustrated **component diagrams** refer to different layers of abstraction. Basically, there is a distinction in diagrams. Component diagrams represent the inner life of the used hardware such as CPUs, memories or peripherals. In contrast, the network topology is used to represent their logical connection. Further presentations, which are less important for the work in hand, illustrate the electric circuits, which contain the power supply and the mass concept of the electronics, as well as the realization of the wiring harness.

- The **Geometrical Topology** finally concentrates on the structural limitations, which arise when the electronics are wired in a car.

PREEvision focuses mainly on the usage of the MDE paradigm and therefore it does not include the simulation of given designs within the development environment. Although they provide some additional capabilities to combine it with simulation tools such as Mat-lab/Simulink, the issue to close the gap between different development environments remains.

## 3.2 State-of-the-art approaches for virtual prototyping

This section gives an insight into the development styles of the leading companies in the area of EDA, where especially time to market plays an important role to stay competitive.

Regardless which manufacturer, the main focus is therefore to develop a design flow that closes the gaps between the simulation of virtual prototypes, FPGA-based prototypes, and the corresponding test instances. Usually, there are corresponding stand-alone tools, which allow only fragments in the development. As a result, it might happen that in the elaboration of the development phase, the produced models can hardly be reused or integrated. Cadence [4] claims that the use of virtual prototypes, which have little to do with the actual hardware implementation, are responsible for poor design flows.

Today, SystemC has become de facto the standard for describing virtual TL platforms. Thus it is widely used by leading electronic manufacturers. Nevertheless, as already discussed in 2.4.1, there are some limitations for the creation of virtual prototypes since TLM descriptions are usually not synthesizable. In most cases, migration from one development stage to another has to be done by hand. Another point complicating the integration is the use of proprietary models, which can usually not be further configured by the user. This makes the step from TLM to RTL in general very difficult. To cope with this issue, the industry tries to develop open, connected and scalable solutions [4].

#### 3.2.1 Open models

EDA manufacturers have indeed an interest in delivering open comprehensive and functional models, as they make it easier to place their products on the market. Thus it is not surprising, that libraries such as OVP gained attraction over the years and have tight cooperations with leading EDA developers. Cadence's *Virtual System Platform* tool offers, for instance, the use of OVP models, which are of certain interest for the thesis in hand. The use of standards guarantees models which have been appropriately reinforced by different manufacturers. Furthermore, vendors guarantee that the corresponding hardware realization exists.

#### 3.2.2 Graphic modeling

The tool Vista Virtual Prototyping from Mentor [30] allows the creation of a virtual hardware prototype by deriving it from a graphical description. Therefore a library of standard TLM models is used, whose description can further be modified, if necessary. The created platform can be used for the development of application software. Using a visual description offers the possibility for an intuitive creation by combining function blocks.

Similar to the approach of integrating entire OVP platforms in Cadence's Virtual System Platform tool, Mentor provides finished TLM platforms which can be executed off-the-shelf.

## 3.3 Co-simulation CPS and SoC models

Co-simulation is one of the most important concepts for the development of CPS and attempts to simulate an entire system by simulating its subsystems. The main issue for modeling is the fact that is most likely done without taking the surrounding environment into account. In the actual co-simulation, communication between two systems takes place via data exchange. In this context, the use of different, often also proprietary simulation mechanisms, makes the connection of subsystems difficult [16]. Especially so-called hybrid co-simulation is of certain interest since it has to couple the simulation of discrete events (DE) with continuous-time (CT). To combine both, it is always essential to translate the respective signal into the other modeling approach. As described in [14] mainly appropriate scheduling of the co-simulation engine is responsible for the progress in time and the respective data exchange between discrete and physical world.

One interesting standard, which is worth mentioning, is the Functional Mockup Interface (FMI) [3]. It implements an additional layer that enables data exchange between simulation tools. But at the same time it protects the intellectual property (IP) of the model itself. FMI exist for different programming languages such as Java or Python as well as for dynamic modeling tools such as *Simulink* or *Matlab*.

#### 3.3.1 Industrial example - Mathworks and Cadence

The importance of co-simulation is also highlighted with the announcement for a stronger cooperation between Matworks and Cadence in November 2016 [47]. Together they worked on an integration of the Cadence *PSPICE* (Personal Simulation Program with Integrated Circuit Emphasis) simulator with *Matlab* and *Simulink*, which enhances the PCB (printed circuit board) design. *Simulink* is the state-of-the-art tool to simulate physical and dynamic systems using the described MBD approach, whereas *PSPICE* is used to develop mixed signal electrical and electronic circuits.

Simulating both parts together in an integrated environment has the advantage to obtain results faster with fewer errors since input and output affect the other subsystem in the simulation. In general, the integration works on both sides, such that one can either use co-simulation within *Simulink* by integrating *PSPICE* models or by exporting behavioral models from Simulink through code generation and integrate them in *PSPICE*. This approach enhances also the verification methodology since stimuli comply with the conditions under which the system is working.

#### 3.3.2 Conclusion

Gomes et.al. [16] showed that co-simulation depends very much on the context in which it is used. *PSPICE*, for instance, is based on SPICE (Simulation Program with Integrated Circuit Emphasis), which is the most popular analog circuit simulator. Whereas especially Verilog and VHDL are used for development of digital circuits. The cooperation of such companies highlights the demand for integrated solutions to develop CPS. Nevertheless, this proprietary tool cooperation is only important for the final realization of a certain part, namely the interaction between the plant and an analog circuit.

From this example, it can be seen that the gap between individual development approaches diverges. Therefore, especially in terms of simulation on a high level of abstraction, one has to find a way to model the environment, digital and analog circuits as well as corresponding software in a sufficient manner. SystemC and its extension SystemC AMS were designed to cover this demand. Because of its capabilities to simulate physical as well as analog and digital designs especially on a higher level of abstraction it has been used for the realization of this thesis. Further descriptions can be found in chapter 4.

### 3.4 SHARC IDE

One of the declared objectives of this project was the combination of the two paradigms, model-driven engineering, and model-based design as described in section 2.3. This section shows how systems with the developed SHARC IDE can be designed in a graphical way. Furthermore, the basic concepts of the simulation are introduced. These approaches provide the possibilities for simulation-based verification in the cloud [39].