# Spezifikation und Design einer integrierten Ausgangsstufe für den Ladungsausgleich einer Lithium-Ionen Batterien Serienschaltung für automobile Applikationen

Diplomarbeit DA666

## Clemens Kain

Technische Universität Graz Institut für Elektronik

Leiter: Univ.-Prof. Dipl.-Ing. Dr.techn. Wolfgang Pribyl Betreuer: Ass.-Prof. Dipl.-Ing. Dr.techn. Peter Söser Telefon: +43(0)316-873-7521 FAX: +43(0)316-873-8020

E-Mail: sek.ife@tugraz.at

Graz, Jänner 2010

# EIDESSTATTLICHE ERKLÄRUNG

| Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt und die den benutzen Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Graz,Unterschrift:                                                                                                                                                                                                                                           |

| STATUTORY DECLARATION                                                                                                                                                                                                                                        |

| I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources and that I have explicitly marked all material which has been quoted either literally or by contend from the used sources.          |

| Graz,Signature:                                                                                                                                                                                                                                              |

# Inhaltsverzeichnis

| 1. | Einle | eitung    |                        | 1      |

|----|-------|-----------|------------------------|--------|

|    | 1.1.  | Motiva    | vation                 | <br>1  |

|    | 1.2.  | Zielset   | $\operatorname{tzung}$ | <br>2  |

|    | 1.3.  | Gliede    | erung                  | <br>2  |

| 2. | Grur  | ndlagen   | n                      | 4      |

|    | 2.1.  | Batter    | rien                   | <br>4  |

|    |       | 2.1.1.    | Batterieeigenschaften  | <br>4  |

|    |       | 2.1.2.    | Batterietypen          | <br>7  |

|    | 2.2.  | Balanc    | ncing                  | <br>9  |

|    | 2.3.  | Fertigu   | gungsprozess SPT6      | <br>18 |

|    |       | 2.3.1.    | Bipolar-Transistoren   | <br>19 |

|    |       | 2.3.2.    | CMOS-Transistoren      | <br>20 |

|    |       | 2.3.3.    | DMOS-Transistor        | <br>20 |

| 3. | Spez  | zifikatio | on                     | 21     |

| -  | 3.1.  |           | m                      | <br>21 |

|    | 3.2.  |           |                        |        |

|    | 3.3.  | _         | angsstufe              |        |

| 4. | Scha  | altungs   | sentwurf               | 37     |

|    |       | _         | Balancing Schaltung    | <br>37 |

|    |       | 4.1.1.    |                        |        |

|    |       | 4.1.2.    | •                      |        |

|    |       | 4.1.3.    |                        |        |

|    | 4.2.  | Passiv    | v Balancing Schaltung  |        |

|    |       | 4.2.1.    |                        |        |

|    |       | 4.2.2.    | 9                      |        |

|    |       | 4.2.3.    |                        |        |

|    |       | 4.2.4.    |                        |        |

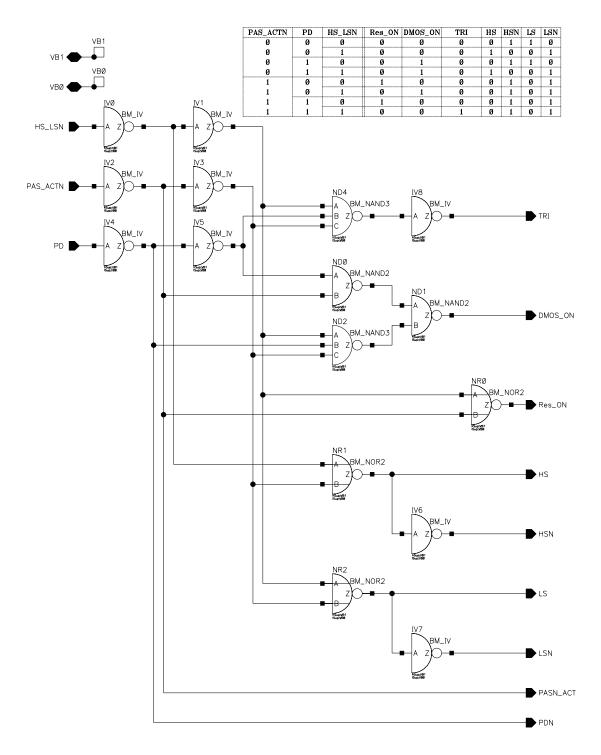

|    | 4.3.  | Kontro    | rollblock              | <br>50 |

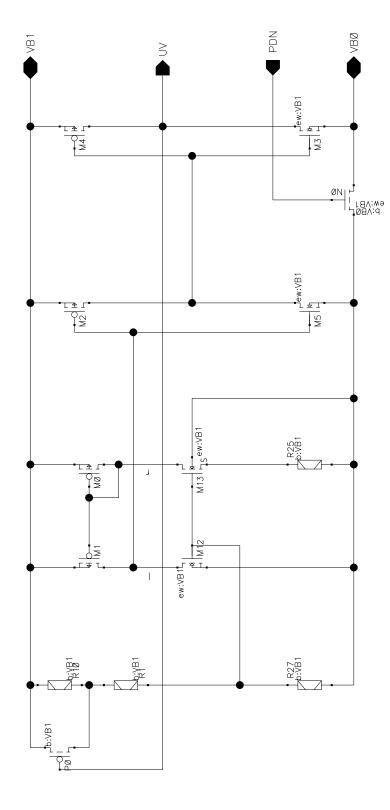

|    |       | 4.3.1.    | Power-Down Schaltung   | <br>50 |

|    |       | 4.3.2.    | 9                      |        |

|    |       | 4.3.3.    |                        |        |

|    |       | 4.3.4.    |                        |        |

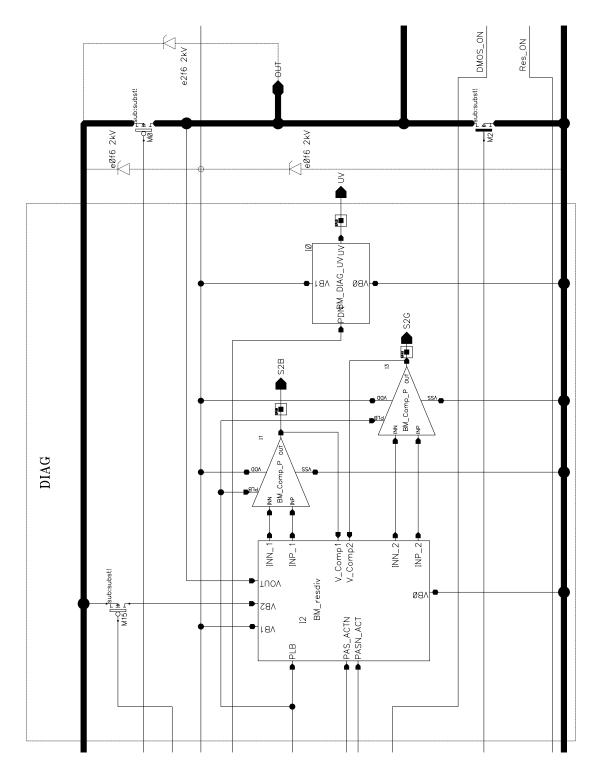

|    | 4.4.  | Diagno    | nose                   |        |

|                       |      | 4.4.1.   | Ausgangsspannungsüberwachung aktiv  | 55 |  |  |  |  |

|-----------------------|------|----------|-------------------------------------|----|--|--|--|--|

|                       |      | 4.4.2.   | Ausgangsspannungsüberwachung passiv | 58 |  |  |  |  |

|                       |      | 4.4.3.   | Unterspannungserkennung             | 60 |  |  |  |  |

|                       |      | 4.4.4.   | Simulation                          | 63 |  |  |  |  |

|                       |      | 4.4.5.   | Layout                              | 66 |  |  |  |  |

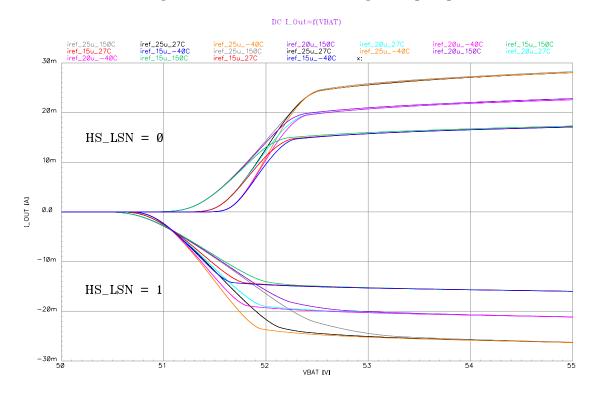

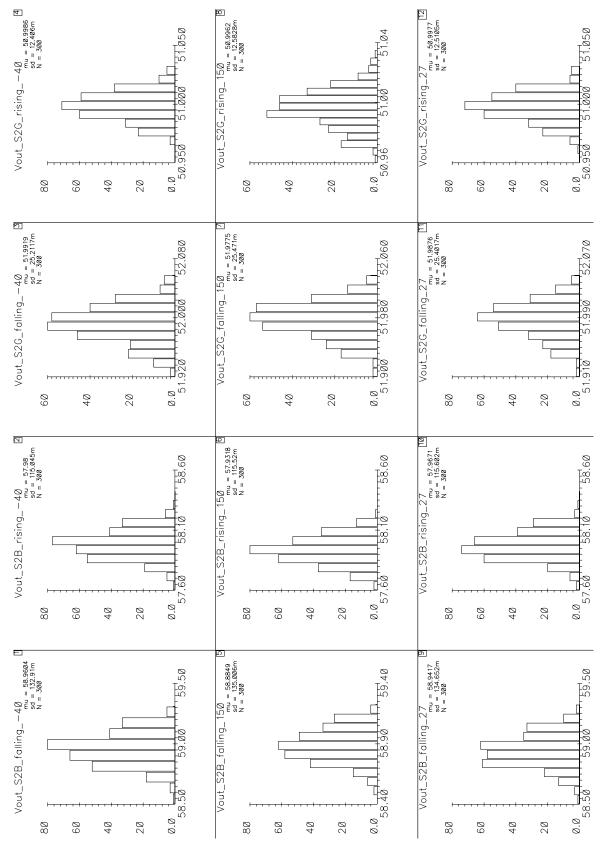

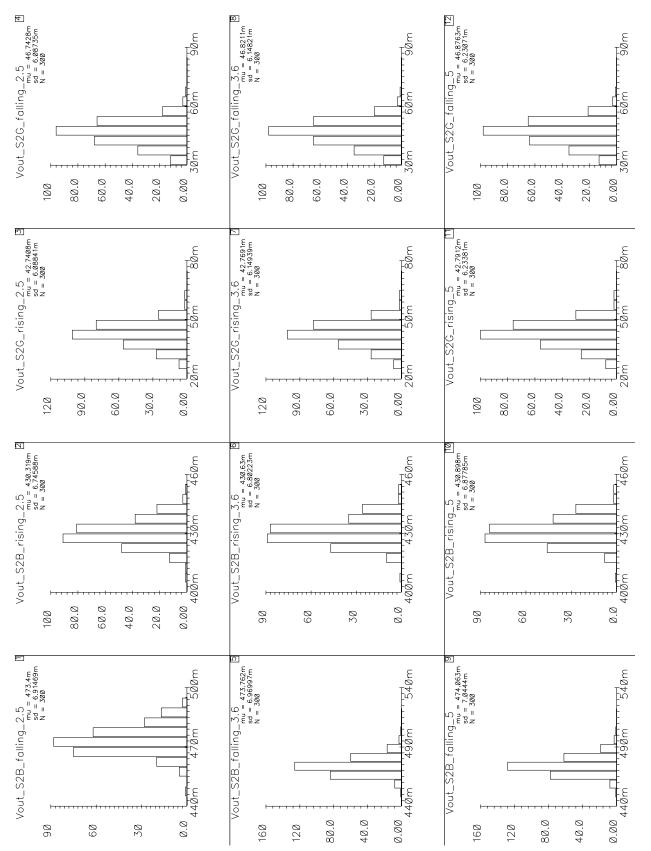

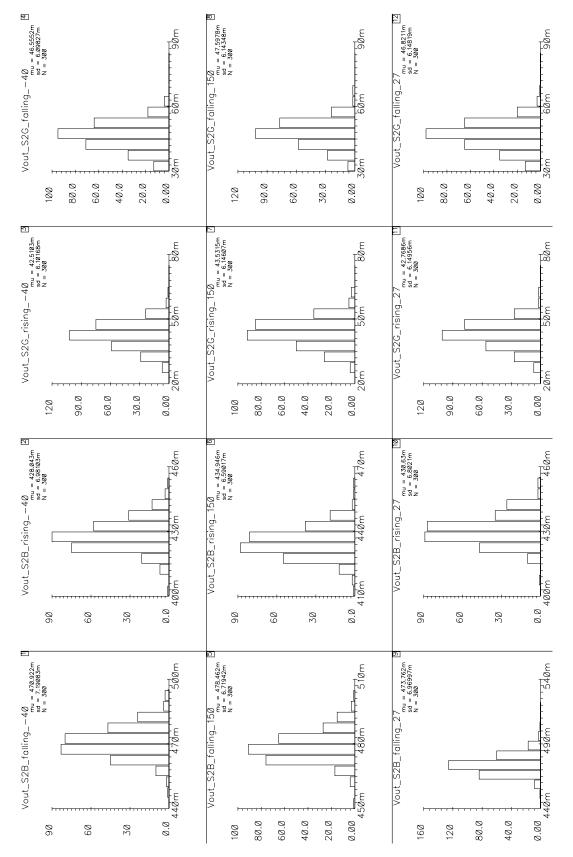

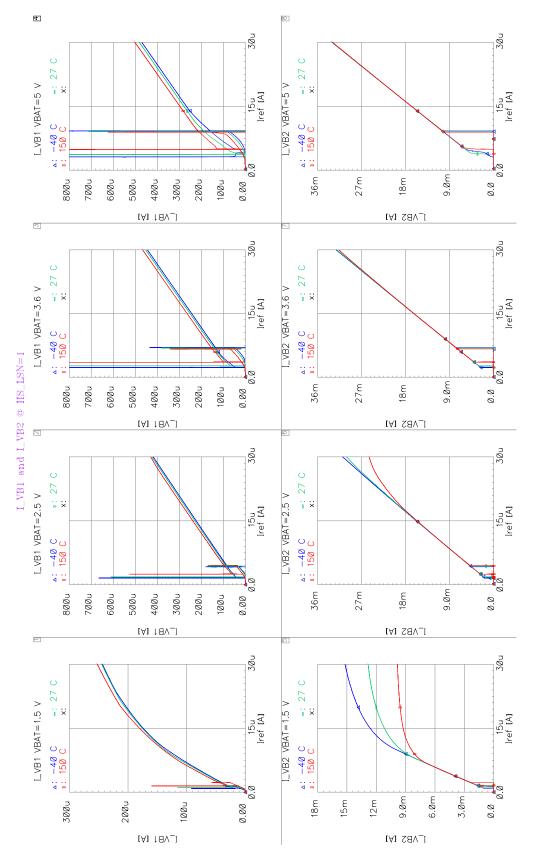

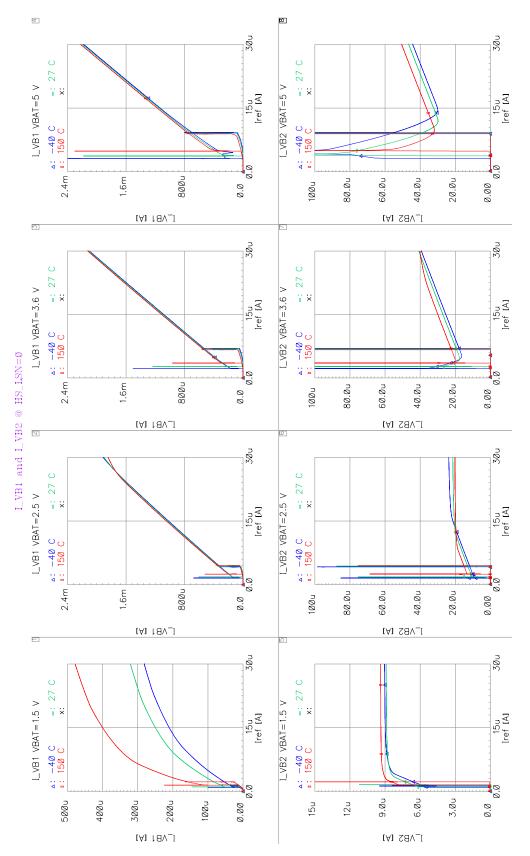

|                       | 4.5. | Simula   | ation Ausgangsstufe                 | 67 |  |  |  |  |

|                       |      | 4.5.1.   | Aktiver Balancing modus             | 67 |  |  |  |  |

|                       |      | 4.5.2.   | Passiver Balancing modus            | 68 |  |  |  |  |

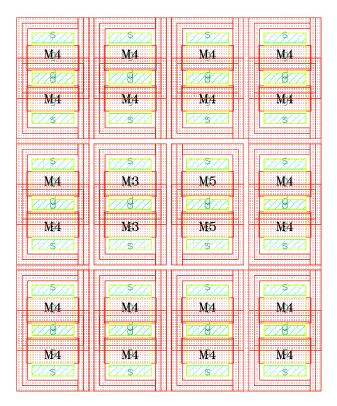

|                       | 4.6. | Layout   | t Ausgangsstufe                     | 69 |  |  |  |  |

| 5.                    | 5.1. | Zusam    | fassung und Ausblick menfassung     |    |  |  |  |  |

| Literaturverzeichnis  |      |          |                                     |    |  |  |  |  |

| Abbildungsverzeichnis |      |          |                                     |    |  |  |  |  |

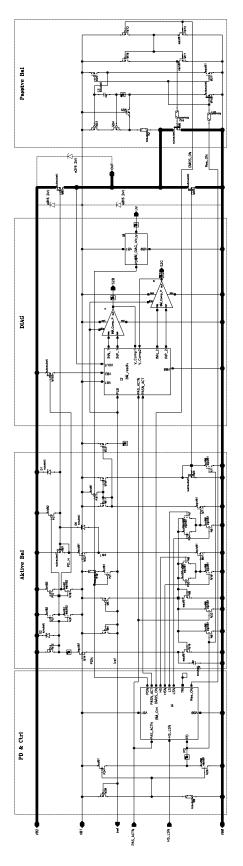

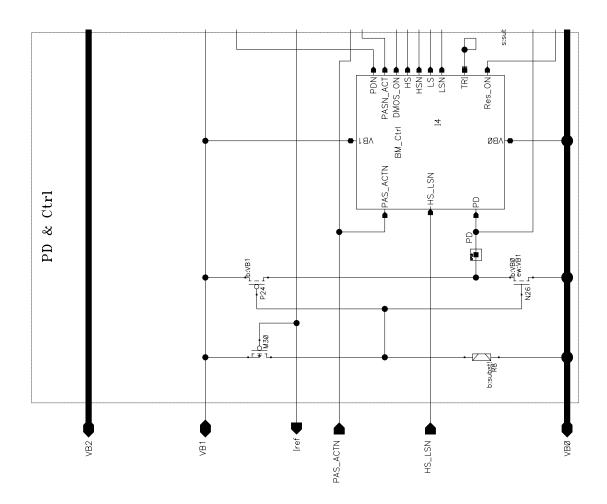

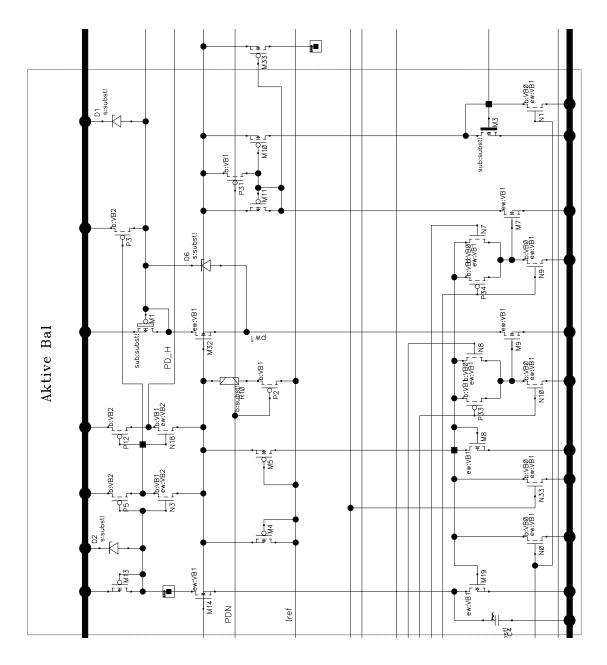

| A. Schematics         |      |          |                                     |    |  |  |  |  |

| В.                    | Sim  | ulatione | en en                               | 87 |  |  |  |  |

# Abkürzungsverzeichnis

ADC ... Analog Digital Converter, Analog-Digital Umsetzer

ASIC ... Application Specific Integrated Circuit,

Speziell für eine Anwendung entwickelte integrierte Schaltung

BCD ... Bipolar CMOS DMOS

BMS ... Batterie-Management-System

CeFu ... Central-Functions EV ... Electric Vehicle

FET ... Field Effect Transistor, Feldeffekttransistor

HS ... High Side LS ... Low Side

MOS ... Metal Oxide Semiconductor, Metall-Oxid-Halbleiter

MV ... Mittelvolt

NTC ... Negative Temperature Coefficient, Negativer Temperaturkoeffizient

NV ... Niedervolt OL ... Open Load

OPV ... Operationsverstärker

PD ... Power Down S2B ... Short to Battery S2G ... Short to Ground

S&H ... Sample and Hold, Abtasten und Halten

SC ... Switched Capacitor

SOC ... State of Charge, Ladezustand

SPI ... Serial Peripheral Interface, Serieller Datenbus

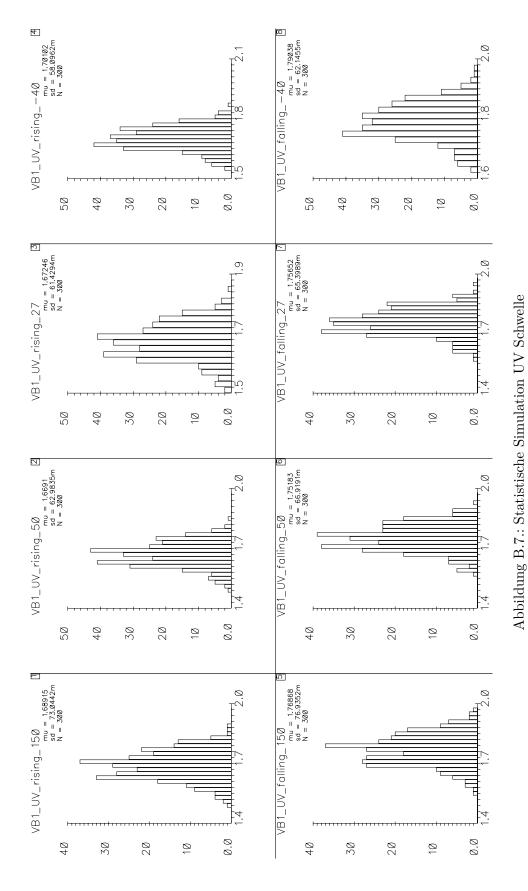

SPT ... Smart Power Technologie UV ... Undervoltage, Unterspannung

$\mu C$  ... Mikrocontroller

## **Vorwort**

Seit 2003 bin ich bei der Firma Infineon in der Automotive-Abteilung Graz als Chip-Layouter tätig. Es lag nahe, dass ich meine Diplomarbeit in Zusammenarbeit mit der Firma Infineon mache. Das Diplomarbeitsthema ergab sich durch ein neues Forschungsprojekt unter der Leitung von Herrn Dipl.-Ing. Viktor Kahr. Aufgrund der Aktualität des Themas E-Mobility war die Begeisterung für die Diplomarbeit schnell geweckt. Die vorliegende Arbeit entstand im Zeitraum vom April 2009 bis Dezember 2009.

Die Diplomarbeit wurde von Herrn Ass.-Prof. Dipl.-Ing. Dr.techn. Peter Söser, vom Institut für Elektronik, betreut, bei ihm möchte ich mich an dieser Stelle recht herzlich bedanken. Während der Erstellung der Diplomarbeit wurde ich auch von Herrn Dipl.-Ing. Michael Hausmann, Firma Infineon, betreut, ihm darf ich für sein persönliches Engagement besonders danken. Für die Einführung in das bestehende System danke ich Herrn Dipl.-Ing. Werner Rössler. Weiters möchte ich mich bei Herrn Dr.Dipl.-Ing. Günter Gross für seine Unterstützung bei schaltungstechnischen Fragen bedanken.

Allen Mitarbeitern der Abteilung sei mein Dank für die gute Zusammenarbeit in der Firma ausgesprochen. Ebenso danke ich meinen Studienkollegen, für ihre Unterstützung in organisatorischer, fachlicher sowie privater Hinsicht. Vor allem möchte ich mich jedoch bei meiner Familie und meinen Freunden für die Unterstützung in all den Jahren hindurch bedanken.

## Kurzfassung

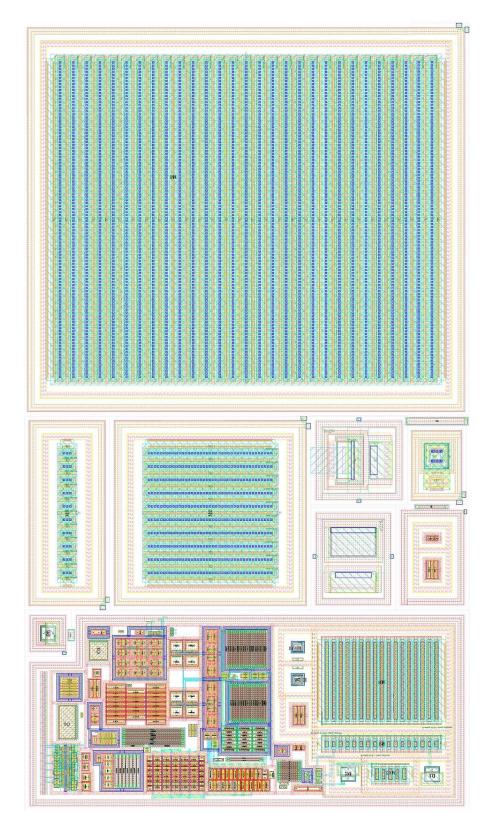

Elektrisch betriebene Automobile stellen an die darin verwendeten Energiespeicher hohe Ansprüche. Der Energiespeicher besteht aus mehreren Batterien, welche in Serie geschalten werden (Batteriestack). Um diesen Batteriestack möglichst effizient und über viele Zyklen laden und entladen zu können, ist es notwendig einen Ladungsausgleich zwischen den Batterien durchzuführen (Balancing). Man unterscheidet dabei zwischen dem aktiven und dem passiven Balancingverfahren. Im Rahmen der Diplomarbeit soll an der Entwicklung eines Batterie-Management-Systems (BMS) mit den Firmen Infineon Technologies, Magna und AIT mitgearbeitet werden. Ziel dieses Forschungsprojekts ist es einen ASIC zu entwickeln, welcher einerseits jede Einzelspannung und Zelltemperatur in einem Batteriestack misst, und andererseits mittels eigens dafür konstruierten Ausgangsstufen externe Bauteile ansteuert um aktives oder passives Balancing zu unterstützen. Ziel der Diplomarbeit ist die Spezifizierung der Ausgangsstufe sowie deren integrierter Schaltungsentwurf samt Layout in der Smart Power Technologie SPT6. Im theoretischen Teil der Arbeit werden Batterien sowie verschiedene Ladungsausgleichsverfahren beschrieben. Im praktischen Teil wird auf die Spezifikation des Chips sowie die Entwicklung der Ausgangsstufe eingegangen. Um die Schaltung zu verifizieren sind transiente, DC sowie statistische Simulationen, welche die Einhaltung der Spezifikationsgrenzen belegen, durchzuführen und die Ergebnisse zu dokumentieren. Da die Schaltung 12 mal am Chip eingesetzt werden soll, ist sowohl auf ein flächenoptimales Design als auch auf ein kompaktes Layout besonderes Augenmerk zu legen.

#### **Abstract**

Energy Storage for Electric Vehicles (EV) has to meet many requirements. It usually consists of several batteries connected in series (battery stack). To efficiently charge and discharge the battery stack over a lot of cycles it is necessary to balance the charge among the batteries (balancing). A distinction has to be made between active and passive balancing. The topic of this diploma thesis arose in the course of the joint development of a battery management system (BMS) between Infineon Technologies, Magna and AIT. The aim of this research is to develop an ASIC to measure all battery voltages and temperatures and to support active and passive balancing by means of an integrated output stage driving external components. The aim of this thesis is the specification, design and layout of the integrated output stage using Infineon's SPT6 technology. The theoretical part of this thesis discusses various battery technologies and charge equalisation methods. The second part covers the specification of the ASIC and the development of the output stage. To verify the design transient, DC and statistical simulations are done to prove compliance with the specification limits. Since this output stage will be placed on the chip twelve times, compact design and layout are of importance.

# 1. Einleitung

## 1.1. Motivation

Elektrisch angetriebene Automobile sind nicht erst eine Option der letzten Jahre. Der Bleiakkumulator, welcher um 1859 erfunden wurde, konnte bis 1881 für das Elektrofahrzeug zur Praxisreife gebracht werden. Unter anderem wurden vor 1900 sogar Geschwindigkeitsrekorde mit den damals zur Verfügung stehenden Elektroautos aufgestellt. Bis 1940 konnte das Elektroauto mit seinen Konkurrenten, welche mit Dampf oder fossilen Brennstoffen betrieben wurden, in deren Verbreitung durchaus mithalten. Ein großer Nachteil der batteriebetrieben Automobile ergab sich schon damals durch die geringe Energiedichte des Energiespeichers. Bei gleichen baulichen Voraussetzungen, wie maximalem Volumen bzw. maximales Gewicht, kann durch fossile Brennstoffe mehr Energie mit dem Fahrzeug mitgeführt werden, als mit Batterien. Mit dem Ausbau der Straßen und zunehmenden Individualverkehr auch über die Stadtgrenze hinaus, stellte die Reichweite des Automobils eine immer wichtiger werdende Anforderung dar. [12]

Die Forschung und Entwicklung fokussierte sich damit auf die Verbrennungsmaschinen, welche kontinuierlich verbessert wurden, während für die Akkumulatoren die Zeit still zu stehen schien. Ausgelöst durch Ölkrisen und steigendes Umweltbewusstsein der Gesellschaft wurde erst um 1990 mit Nachdruck nach Alternativen zum Verbrennungsmotor gesucht. Neben dem Akkumulator wurde auch die Brennstoffzelle als Energiespeicher in Betracht gezogen. Während E-Autos mit Brennstoffzellen über einzelne Prototypen hinaus noch nicht hergestellt werden, kann der Akkumulator schon auf einige Kleinserien in der Vergangenheit zurückblicken.

Unterstützt durch das Aufkommen mobiler elektrischer Geräte wie Laptop, PDA und dem Handy in großen Stückzahlen, wurden NiCd und NiMH Akkumulatoren als Energiespeicher verwendet. Aktuell werden der Lithium Batterie die besten Erfolgsaussichten im Elektroauto vorausgesagt.

Um einen geringeren Strom sowie dünnere Leitungen bei gegebener Leistung zu ermöglichen werden viele dieser Zellen in Serie zueinander angeordnet um Spannungen von mehreren hundert Volt zu erreichen. Durch Produktionsunterschiede der Zellen sowie verschiedenen Alterserscheinungen nach vielen Ladezyklen können diese Zellen verschiedene Ladungszustände aufweisen, was ein Batterie-Management-System notwendig

macht. Dieses Batterie-Management-System überwacht zum einen alle Zellspannungen auf deren regulären Betrieb innerhalb der vorgesehenen Spannungsgrenzen, und steuert zum anderen die Ladungsbalancierung, damit alle Zellen gleich weit geladen bzw. entladen werden können. [1]

Die Entwicklung dieses Systems erfolgt in einer Kooperation der Firmen Magna, AIT und Infineon. Infineon Technologies entwickelt dazu einen IC, welcher die Schnittstelle zwischen den Batterien und dem Mikrocontroller ( $\mu$ C) darstellt. Diese Diplomarbeit umfasst dabei die Beschreibung verschiedener Balancing Verfahren sowie das Konzipieren und Realisieren eines Gatetreibers auf diesem IC, welcher ein von der Firma Infineon verwendetes aktiv Balancing Verfahren sowie das passiv Balancing unterstützt.

## 1.2. Zielsetzung

Im Laufe der Diplomarbeit soll an einer ersten Spezifikation des geplanten Chips (ASIC) mitgearbeitet werden. Äußere Beschaltung und Funktionen des Chips sollen nach Absprache mit den Projektpartnern festgelegt werden. Die Ausgangsstufe des Chips soll anschließend näher spezifiziert und in der Technologie SPT6 entworfen werden. Die statistischen Simulationen sollen die Einhaltung der Spezifikation bestätigen. Abschließend soll die Ausgangsstufe gelayoutet werden, damit die Schaltung auf einem Testchip produziert werden kann.

# 1.3. Gliederung

Die Diplomarbeit wurde in drei große Kapitel geteilt. Im ersten Kapitel werden die Grundlagen erläutert. Aktuell eingesetzte Batterien werden angeführt und deren Vorund Nachteile erläutert. In diesem Teil werden auch Veröffentlichungen zum Thema verkürzt angeführt und ein Überblick der zur Zeit verwendeten Balancing Verfahren gegeben. Den Abschluss dieses Kapitels bildet eine Einführung in die Technologie SPT6, welche die Rahmenbedingungen für den Schaltungsentwurf darstellt.

Im zweiten Kapitel wird die Spezifikation des Chips beschrieben. Nach der Beschreibung des gesamten Systems werden Anforderungen und Vorgaben der Systementwickler angeführt. Eine Simulation an einem diskret aufgebauten System schafft einen Überblick und lässt eine Beschreibung sowie die nähere Spezifikation der Ausgangsstufe zu.

Im dritten Kapitel werden verschiedene Schaltungsentwürfe miteinander verglichen und auf deren sinnvolle Einsetzbarkeit für die Applikation überprüft. Die finale Schaltung wird detailiert auf Transistorebene beschrieben. Simulationen der einzelnen Schaltungs-

blöcke sowie der gesamten Ausgangsstufe sollen die Einhaltung der Spezifikation bezeugen.

Weiters werden die Herausforderungen des physikalischen Entwurfs angeführt und das finale Layout der Ausgangsstufe gezeigt.

Im abschließenden Kapitel Zusammenfassung und Ausblick werden die Erkenntnisse aus dieser Diplomarbeit zusammengefasst und auf die Erreichung der Zielsetzung eingegangen. Den Fortgang der Chipentwicklung und eine Abschätzung der benötigten Fläche des Chips bilden den Ausblick dieser Arbeit.

Im Anhang der Arbeit werden zunächst die Detail-Schematics der Ausgangsstufe und weitere Simulationsergebnisse angeführt.

# 2. Grundlagen

## 2.1. Batterien

Batterien sind galvanische Zellen und dienen der Speicherung elektrischer Energie. Wichtige Bestandteile der galvanischen Zelle sind die beiden Elektroden aus unterschiedlichen Materialien, welche die Zellspannung bestimmen, und der Elektrolyt. Trotz einiger Versuche in der Vergangenheit konnte sich die Batterie als Energiespeicher für Autos noch nicht gegen fossile Treibstoffe durchsetzten. Ein Hauptproblem ist die geringe Energiedichte, die Batterien gegenüber Benzin oder Diesel aufweisen.

Grundsätzlich teilt man Batterien in 2 Gruppen ein, den Primär- und den Sekundärzellen. Als Traktionsbatterien, also Batterien die ein Auto vollständig mit Energie versorgen, kommen nur Sekundärzellen in Frage. Im Gegensatz zu den Primärzellen können diese Zellen wieder aufgeladen werden und kommen dem konventionellen Treibstofftank des Autos wesentlich näher.

#### 2.1.1. Batterieeigenschaften

Im Folgenden sollen die wichtigsten Eigenschaften der Traktionsbatterien erklärt werden.

Die spezifische Energiedichte einer Batterie beschreibt die speicherbare Energie in Wh pro Kilogramm. Dieser Wert ist essentiell für die Reichweite des Automobils. Je höher die spezifische Energiedichte umso leichter kann das Auto bei gleichem Energievorrat gebaut werden. Das senkt die benötigte Energie für eine Wegstrecke. Die volumetrische Energiedichte gibt einen Wh pro Liter Wert an, welcher für die Platzierung der Batterie und dessen benötigte Abmessungen berücksichtigt werden muss. Beide Werte sollten für ein rein elektrisch betriebenes Auto (EV) möglichst hoch sein.

Die Leistungsdichte in W pro kg gibt die Leistung, welche aus der Batterie entnommen werden kann, in Bezug auf das Gewicht an. Je höher dieser Wert ist, umso höhere Beschleunigungen können mit dem Auto erreicht werden. Weiters gibt die Leistungsdichte indirekt an, mit welcher Stromstärke die Batterie geladen werden kann. Für Batterien in Hybrid-Autos ist dieser Wert sehr wichtig, da zum Beispiel während einer Beschleunigungsphase für kurze Zeit eine hohe Leistung abrufbar sein soll.

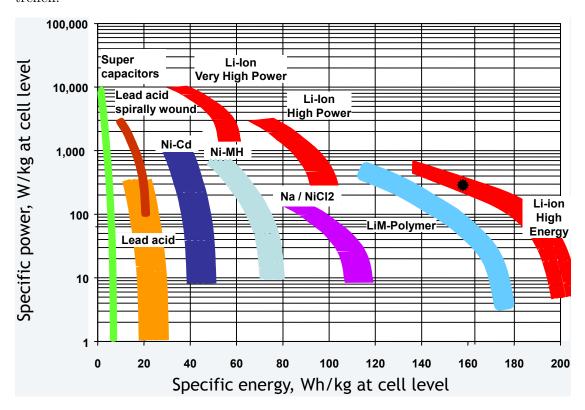

In Abbildung 2.1 ist das Ragone-Diagramm für verschiedene Batterien abgebildet. Das Ragone-Diagramm zeigt die Leistungsdichte in Bezug auf die spezifische Energiedichte. Je nach Anwendung ist oft eine Auswahl zwischen Energie- oder Leistungsbatterien zu treffen.

Abbildung 2.1.: Ragone Diagramm [Quelle: Firma SAFT]

Die Zellspannung einer Batterie ist abhängig vom Batterietyp beziehungsweise den Bestandteilen der Zelle, wie den Elektrodenmaterialien.

Wichtige Spannungsangaben einer Batterie sind:

- Leerlaufspannung: Spannung der Zelle ohne Belastung

- Ladeschlussspannung: Maximale Spannung, bis zu der die Batterie geladen werden darf

- Entladeschlussspannung: Minimale Spannung der Batterie, welche nicht unterschritten werden darf

Die Kapazität einer Batterie definiert die speicherbare Energie einer Zelle. Sie wird in Ah angegeben. Die Änderung der Zellspannung mit dem Ladezustand der Batterie ist in

der Entladecharakteristik zu sehen. Oft ist die Kapazität zusätzlich vom Entladestrom abhängig, da der Innenwiderstand der Zelle bei höheren Strömen stärker erhitzt wird. Auch die Umgebungstemperatur ändert den Kurvenverlauf der Entladecharakteristik. Die Kapazität kann also je nach Temperatur oder Stromentnahme variieren. [6]

Der State-of-Charge (SOC) Wert entspricht dem Ladezustand eines Energiespeichers und nimmt Werte zwischen 0 und 100 Prozent an. Der SOC-Wert ermöglicht somit eine Abschätzung, der verbleibenden Reichweite des Autos. Mittels Messung der Spannung, des Stromes und der Temperatur einer Zelle kann der SOC-Wert berechnet werden. [15]

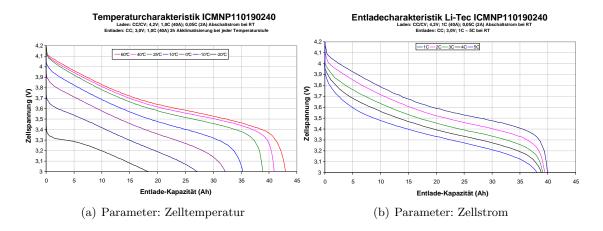

Grundlage dieser Berechnung ist die Entladecharakteristik einer Zelle. Abbildung 2.2 zeigt die Entladecharakteristik einer Lithium-Ionen Zelle. Lade- oder Entladeströme werden bei Akkumulatoren oft in C-Werten angegeben. Der 1C-Strom entspricht jenem Strom, der die Zelle in einer Stunde, von dessen Nennkapazität ausgehend, vollständig entlädt. Spricht man von einer 40 Ah Zelle so ist der 1C-Strom 40 Ampere. [12]

Abbildung 2.2.: Entladecharakteristik einer Lithium-Ionen Zelle [Quelle: Firma Li-Tec]

Der Ladefaktor ist der Kehrwert des Ladewirkungsgrads und beschreibt die Relation zwischen der Energie, mit der die Zelle geladen wird, und der Energie, die später aus der Zelle entnommen werden kann. Ein Ladewirkungsgrad von 1 ist demnach optimal. [6]

Die Lebensdauer der Batterie wird meist in Vollzyklen angegeben. Die Zelle wird dabei zu 80% pro Zyklus entladen. Die Batterie gilt für automotive Anwendungen als kaputt wenn sie nach den Lade-/Entladezyklen nur mehr 80% ihrer Nennkapazität aufweist. Manche Batterien besitzen eine Lebensdauerangabe in Jahren, welche auch die Lagerung der Batterien begrenzt. [16]

#### 2.1.2. Batterietypen

Die wichtigsten Vertreter von Traktionsbatterien in der Vergangenheit und Gegenwart sind der Bleiakkumulator sowie die NiMH und die Lithium-Ionen Zelle. Die Eigenschaften dieser Akkumulatoren werden folglich etwas näher beschrieben.

#### **Bleiakkumulator**

Der Bleiakkumulator wurde um 1859 erfunden. Die Zelle besteht an der positiven Elektrode aus Bleidioxid und an der negativen Elektrode aus Blei. Als Elektrolyt wird bei der Blei-Säure-Batterie 38-prozentige Schwefelsäure verwendet. Die Eigenschaften der Batterie wie Hochstromfestigkeit und Zyklenfestigkeit können durch die Platten-Oberfläche, deren Abstände sowie der Isolation beeinflusst werden und für bestimmte Applikationen optimiert werden. [12]

Bei einem Blei-Gel-Akkumulator ist der Elektrolyt als Gel vorhanden. Die Vorteile gegenüber der Blei-Säure-Zelle ist die Wartungsfreiheit, eine höhere Lebensdauer und Energieeffizienz sowie die Lageunabhängigkeit der Batterie. Beim Laden muss darauf geachtet werden, dass der Akkumulator nicht durch Überladen mehr Knallgas erzeugt als an den Polen rekombiniert werden kann. Die Folge wäre ein erhöhter Druck in der Zelle sowie das Ausgasen bzw. das Entweichen des Elektrolyts über das Sicherheitsventil des Gehäuses, was irreparable Schäden verursachen kann.

Eine weitere Bauform ist der Blei-Flies-Akkumulator, deren Schwefelsäure mit einem Flies gebunden wird. Dieser Akkumulator zeichnet sich durch verbesserte Lebensdauer, bessere Eigenschaften bei niedrigen Temperaturen und der Tiefentladefähigkeit aus. [12]

Die Nennspannung einer Zelle beträgt 2 Volt obwohl je nach Lade- bzw. Entladezustand eine Leerlaufspannung zwischen 1,75 und 2,4 Volt gemessen werden kann.

Applikationen für Bleiakkumulatoren:

- Startbatterie in Verbrennungsfahrzeugen

- Energiespeicher in unterbrechungsfreien Stromversorgungen

- Traktionsbatterien kleiner Elektrofahrzeuge

- Batterien für Solaranlagen

#### **NiMH Akkumulator**

Die Nickel Metall-Hydrid Zelle ist seit 1992 auf dem Markt und folgt der in Europa bereits wegen dem giftigen Cadmium verbotenen NiCd Akkumulator. Die positiven Elektrode besteht meist aus Nickelhydroxid und die negative Elektrode wird meist aus Kobalt-Mangan-Legierungen geformt. Der Elektrolyt ist Kalilauge. Der erlaubte Temperaturbereich der Zelle liegt zwischen -40 und 50 °C. Die theoretisch erreichbare Energiedichte von 215 Wh/kg wird in der Praxis (70-90 Wh/kg) bei weitem nicht erreicht. [6][16]

Die Nennspannung des NiMH Akkumulators liegt bei 1,2 V. Die Ruhespannung liegt zwischen der Entladeschlussspannung von 1 V und der Ladeschlussspannung von 1,45 V. Die Entladeeigenschaft ist vom Entladestrom sowie der Außentemperatur abhängig. Als Vorteil dieser Zelle ist das gute Hochstromverhalten, bedingt durch das negative Temperaturverhalten, zu nennen. [16]

Die Zyklenfestigkeit liegt bei ca. 2500 Zyklen (80 % Entladetiefe) bzw. 160000 Zyklen (5 % Entladetiefe). Überladen und Tiefentladen sind zu vermeiden, da es durch Kristallbildungen zu permanenten Schäden an der Zelle führen kann.

Ein großer Nachteil dieser Zelle ist die hohe Selbstentladungsrate von 4-5 % pro Tag bzw. 20-25 % pro Monat. [16] NiMH Akkumulatoren werden oft als Ersatz von Primärzellen in tragbaren Geräten wie MP3-Player, Digitalkamera usw. verwendet. Auch aktuell erhältliche Hybrid-Autos (Prius) verwenden diese Zellen.

#### Li-Ionen Akkumulator

Der Lithium-Ionen Akkumulator verdrängt seit Markteinführung 2004 die NiCd und auch NiMH Zelle. An den Elektroden-Materialien der Lithium-Ionen Zellen wird nach wie vor mit Nachdruck geforscht. Die meisten erhältlichen Lithium-Ionen Akkumulatoren besitzen eine positive  $LiCoO_2$  Elektrode sowie eine negative Elektrode aus Kohlenstoff. Der Elektrolyt ist eine organische Flüssigkeit. Besonders an der positiven Elektrode befinden sich verschiedene Materialien, welche unterschiedliche Einflüsse auf die Eigenschaften der Zelle haben. In der Tabelle 2.1 sollen Zellen mit verschiedenen Legierungen der positiven Elektrode gegenübergestellt werden.

Lithium-Ionen Zellen mit  $LiCoO_2$  Elektroden neigen bei hoher Spannung ab 4,4 V oder bei hohen Temperaturen zu einer starken exothermen Reaktion weshalb die Zellen elektronisch überwacht werden müssen. Viele Batterie-Hersteller integrieren auch schon mechanische Stromabschalteinrichtungen um gefährliche Temperaturen, hohe Ströme oder einen zu hohen Druck der Zellen zu vermeiden. Die mechanische Abschaltung der Zelle selbst ist jedoch irreversibel.

| System       | Zellspannung | Temperatur           | spez. Energiedichte |         | Zyklen   | Leistung |

|--------------|--------------|----------------------|---------------------|---------|----------|----------|

|              | V            | $^{\circ}\mathrm{C}$ | Wh/kg               | Wh/l    |          |          |

| $LiCoO_2$    | 3,6          | -20/60               | 140-190             | 360-500 | 800-1200 | N-M      |

| NCA          | 3,5          | -20/60               | 220-240             | 500-630 | 800-1200 | N-M      |

| NCM          | 3,7          | -20/60               | 100-150             | 230-400 | 500-700  | M-H      |

| Mn spinel    | 3,7          | -20/60               | 130-150             | 300-320 | 500-700  | Н        |

| Fe phosphate | 3,3          | -30/70               | 100-140             | 250-380 | >1000    | SH       |

| Nexelion     | 3,5          | -20/60               | 160                 | 480     | 1000     | M-H      |

Tabelle 2.1.: Übersicht Li-Ionen Systeme [12] [16]

N ... NiedrigM ... MittelH ... HochSH ... Sehr Hoch

Die Ladeschlussspannung des Lithium-Ionen Akkumulator liegt bei 4,2 V und sollte aus Sicherheitsgründen genau eingehalten werden. Die Entladeschlussspannung schwankt je nach Elektrodenmaterial zwischen 2,3 bis 3 V. Die Abhängigkeit der Zellspannung gegenüber dem Strom und der Temperatur muss für SOC-Berechnungen berücksichtigt werden. Bei Temperaturen unter 0 °C nimmt die Kapazität stärker ab als bei höheren Temperaturen. Bei diesen niedrigen Temperaturen sollte die Zelle mit kleineren Strömen geladen werden um einen vollständigen Ladevorgang zu ermöglichen. [16]

Die Selbstentladung von Lithium-Ionen Akkumulatoren liegt bei 1-5~% im Monat was relativ gering ist. Bei Zelltemperaturen höher  $30~^{\circ}$ C steigt die Selbstenladung weshalb die Lagerung von Lithium-Ionen Batterien bei Raumtemperatur und 60~% SOC erfolgen sollte. [16] Lithium-Ionen Akkumulatoren werden vor allem in tragbaren Geräten wie Handy, Laptop usw. verwendet. Auch neue Hybrid- und reine Elektroautos werden mit Lithium-Ionen Zellen geplant und aller Voraussicht nach die bestehenden NiMH Systeme ersetzen.

# 2.2. Balancing

Eine Serienschaltung von Batterien (Batteriestack) bringt mehrere Probleme mit sich. Speziell wiederaufladbare Batterien mit flacher Entladecharakteristik und unbedingt einzuhaltenden Spannungsgrenzen stellen hohe Anforderungen an das Batterie-Management-System (BMS).

Man unterscheidet in der Literatur zwischen internen und externen Gründen für Zellen in einem Batteriestack mit unterschiedlichen Ladungszuständen (unbalancierter Batte-

riestack). [3] Interne Gründe sind zum Beispiel unterschiedliche Parameter wie Kapazität, Selbstentladungsrate oder Serienwiderstand. Diese unterschiedlichen Parameter können massiv durch verschieden alte Zellen bzw. Zellen verschiedener Hersteller auftreten. Optimal ist deshalb ein Batteriestack mit Zellen einer Produktionstranche. Durch die Prozessstreuung, welche je nach Werk und verwendeter Technologie unterschiedlich ausfallen kann, kommt man jedoch an der Tatsache nicht vorbei, dass die Zellparameter zumindest leicht verschieden sind.

Externe Gründe können unterschiedliche Belastungen der Zellen durch die äußere Beschaltung (Spannungsüberwachung) oder auch verschiedene Zelltemperaturen sein. Da sich die maximale Entladekapazität, die Selbstentladungsrate und der Serienwiderstand einer Zelle mit deren Temperatur verändert, sind Temperaturunterschiede der einzelnen Zellen möglichst zu vermeiden.

Zur Veranschaulichung der Problematik eines unbalancierten Batteriestacks ist auf [1] zu verweisen. Vergleichbar mit einem Wassermodell, indem die Batterien durch Gefäße dargestellt werden, kann ein Batteriestack nur solange geladen werden bis die vollste Zelle ihre maximal erlaubte Spannung erreicht hat. Umgekehrt begrenzt die leerste Zelle den Entladevorgang durch die minimal erlaubte Zellspannung. Der Ladungsunterschied zwischen der vollsten und der leersten Zelle gleicher Kapazität eines Stacks reduziert die theoretisch zur Verfügung stehende Ladung des gesamten Stacks. Im Extremfall befindet sich eine volle und eine leere Batterie in einem Stack was bewirkt, dass der Stack weder geladen noch entladen werden kann.

Bei Einhaltung aller Empfehlungen kann ein Batteriestack gefertigt werden, dessen einzelne Zellparameter nur wenig voneinander abweichen. Während den ersten Lade-/Entladezyklen spielen diese Abweichungen keine große Rolle. Bei längerer Lagerung oder höherer Zyklenanzahl summiert sich die Unausgewogenheit der einzelnen Zellen zusehends, sodass die zu erwartende Lebensdauer des Stacks doch deutlich geringer ausfällt, als die einer Einzelzelle. [10]

Da die gespeicherte Energie in den Batterien immer höher wird um größere Reichweiten zu ermöglichen, werden auch die Ladungsunterschiede der einzelnen Zellen absolut gesehen immer höher. Ungleiche Innenwiderstände der Batterien verursachen bei Spannungsmessungen während dem Betrieb (durch laden oder entladen) unterschiedliche Zellspannungen, und führen ohne einer zusätzlichen Referenzmessung der Ruhespannung zu verfälschten SOC-Berechnungen der Zellen.

In der Literatur existieren verschiedene Auffassungen bezüglich der Aufteilung der Balancingmethoden in aktives und passives Balancing. Bei Blei-Säure- oder NiCd-Batterien kann durch die zelltypbedingte Überladungsresistenz der gesamte Stack solange geladen werden, bis die letzte Zelle voll ist. Die überschüssige Leistung wird in Form von Wärmenergie oder durch Ausgasen der Zelle (Elektrolyse) an die Umgebung abgegeben. Diese Art des Balancings wird als passives Balancing bezeichnet. Wird eine externe Schaltung

ungeachtet der verwendeten Bauteile oder der Methode für das Balancing verwendet, so spricht der Autor von aktivem Balancing. [3]

Speziell beim Balancing von Lithium-Ionen Batterien, wie sie in dieser Arbeit vorgestellt werden soll, spricht man jedoch von passivem Balancing, wenn die überschüssige Energie einer bereits vollen Zelle durch die äußere Beschaltung in Wärme umgewandelt wird, und von aktivem Balancing, wenn überschüssige Energie den anderen Zellen zugeführt wird. [1]

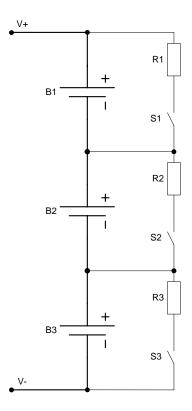

#### **Passives Balancing**

Das passive Balancing ist ein weit verbreitetes Balancingverfahren für Lithium-Ionen Batterien mit niedriger bis mittlerer Zellkapazität. Die Grundidee dahinter ist, Zellen mittels eines Widerstandes zu belasten und somit ein weiteres Aufladen der Zelle, je nach Dimensionierung des Balancingstromes, einzubremsen oder zu verhindern. Die Schaltung in Abbildung 2.3 zeigt eine Schaltung für passives Balancing. [3] Durch ermitteln des SOC-Wertes aller Zellen kann eine Entscheidung getroffen werden, welche Zellen langsamer geladen werden sollen. Den betroffenen Zellen wird ein Widerstand parallel geschaltet wodurch je nach Widerstandswert ein Teil des Ladestroms an der Zelle vorbei geführt wird. Die Verlustleistung des Widerstandes berechnet sich aus der Spannung der Zelle  $V_{B1}$  sowie aus dem Balancingwiderstand R.

$$P_{R1} = \frac{V_{B1}^2}{R1} [W] \tag{2.1}$$

Bei der Dimensionierung des Widerstandes ist auf die Verlustleistung zu achten und die Wärmeabfuhr aus dem System sicherzustellen, wenn alle Widerstände zugeschalten wurden. Durch den geringeren Ladestrom der volleren Zellen gleichen sich alle Zellen an. Nachdem alle Zellen den gleichen SOC-Wert aufweisen, können die Widerstände wieder abgeschaltet werden.

Die Vorteile dieser Methode sind der prinzipiell einfache Aufbau der Schaltung sowie geringe Anforderungen an die Schalteransteuerung. Pro Zelle wird ein Schalter und ein Widerstand benötigt. Für n Zellen ergibt dies n Schalter und n Widerstände, was die Kosten der Schaltung gering hält. Der Balancingstrom wird durch den Widerstandswert einfach definiert und kann somit für die verschiedenen Applikationen angepasst werden.

$$I_{R1} = \frac{V_{B1}}{R1}[A] \tag{2.2}$$

Abbildung 2.3.: Passives Balancing mit Widerstand

Ein großer Nachteil dieser Methode ergibt sich durch die geringe Energieeffizienz des Systems, da überschüssige Energie in Wärme umgewandelt wird und für die Applikation verloren geht. Aus diesem Grund ist ein Ladungsausgleich mit dieser Methode nur während einem Aufladevorgang der Batterie sinnvoll einsetzbar. Je nach thermischem Management kann die maximale Verlustleistung des Systems den Balancingstrom begrenzen, weshalb diese Methode oft nur für kleine Balancingströme (ca. 100 mA) angewandt wird.

Integrierte Schaltungen, welche passives Balancing für mehrere Zellen in Serie unterstützen sind zum Beispiel LTC6802 (Linear Technologies), AD7280 (Analog Devices) sowie BQ77PL900 (Texas Instruments).

#### **Aktives Balancing**

Beim aktiven Balancing wird die Energie voller Zellen an leere Zellen abgegeben. Für diesen Vorgang muss wegen der Serienschaltung der Zellen Energie temporär gespeichert werden, was entweder kapazitiv oder induktiv erfolgen kann. Kapazitiver Ladungsausgleich beruht meist auf SC (Switched Capacitor) Schaltungen.

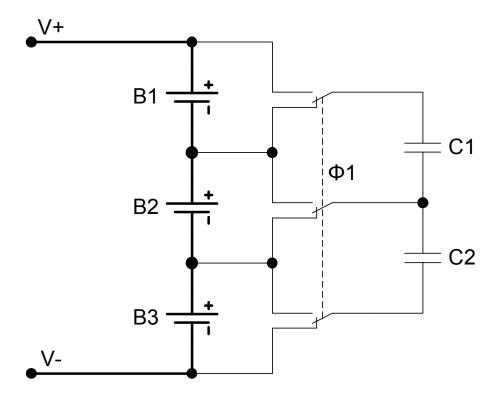

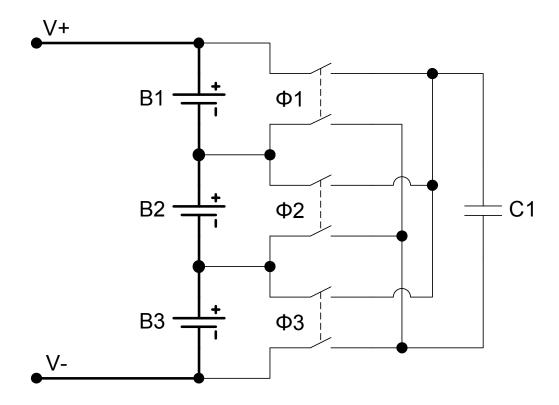

In Abbildung 2.4 ist eine SC Schaltung nach [3] dargestellt, die 2n Schalter, (n-1) Kondensatoren und ein Ansteuersignal benötigt. Das Ansteuersignal kann durch ein einfaches Taktsignal erzeugt werden. Jeder Kondensator stellt einen Spannungsausgleich zwischen 2 benachbarten Zellen her, was in Summe zu einem Angleichen aller Zellspannungen führt. Die Geschwindigkeit des Ladungsausgleichs definiert sich durch die Größe der Kapazitäten sowie der Taktfrequenz des Ansteuersignals und der Anzahl der Zellen.

Abbildung 2.4.: Aktiv Balancing mit SC

Eine Abwandlung der Schaltung ist in Abbildung 2.5 dargestellt. Diese Single SC-Schaltung benötigt 2n Schalter, einen Kondensator und n Ansteuersignale. [3] Mit dieser Schaltung kann durch eine intelligente Ansteuerung gezielt zwischen zwei beliebigen Zellen im Stack balanciert werden. Die Vorteile dieser Schaltung ergeben sich durch die verminderte Kondensatoranzahl, sowie einer höheren Geschwindigkeit bei komplexerer Erzeugung der Ansteuersignale. Bei der Ausführung der Schalter mit Halbleiterbauelementen ist auf die höhere Schaltspannung gegenüber der SC-Schaltung hinzuweisen.

Abbildung 2.5.: Aktiv Balancing mit Single SC

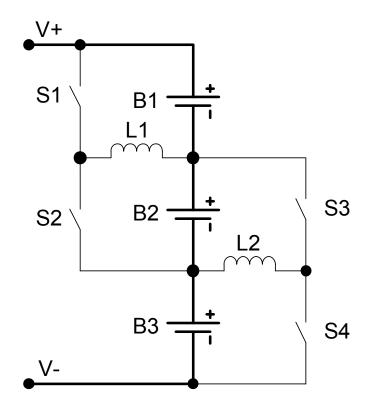

Eine induktive Balancingschaltung wird in Abbildung 2.6 gezeigt. [3] Diese Schaltung wird von Texas Instruments unter der Bezeichnung BQ78PL114 PowerPump verwendet. Die Schaltung benötigt 2(n-1) Schalter sowie (n-1) Induktivitäten und 2(n-1) Ansteuersignale. Im Ruhezustand sind alle Schalter geöffnet. Will man Energie von der Batterie 1 zur Batterie 2 transferieren so wird zunächst S1 geschlossen. Der Strom in der Spule L1 steigt linear an. Nach Erreichen des maximalen Stromes wird S1 geöffnet und S2 geschlossen, womit die Spule die magnetische Energie über die Batterie 2 abbaut und dieser somit Energie zuführt. Wenn der Strom den Nulldurchgang erreicht wird S2 wieder geöffnet womit sich die Schaltung wieder im Ausgangszustand befindet.

Sind den Schaltern parallel Dioden angeordnet, wie es bei MOSFET-Schaltern der Fall ist, kann die Ansteuerung von S2 für diesen Zyklus entfallen. Soll Energie von der Batterie 2 zur Batterie 1 transferiert werden wechseln die Schaltzustände von S1 und S2. Ähnlich wie bei der SC-Schaltung ist es in einem Schaltzyklus nur möglich Energie zwischen benachbarten Zellen zu wechseln. Durch gezieltes Weiterschieben der Teilladungen kann Energie zwischen beliebigen Zellen ausgetauscht werden. Die Ansteuerung dieser Schaltung ist Aufgrund der vielen unterschiedlichen Ansteuersignale als komplex zu bezeichnen.

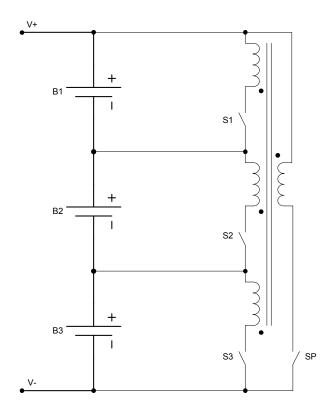

Abbildung 2.6.: Aktiv Balancing mit Spulen

Eine weitere induktive Balancingschaltung wie sie bei Infineon verwendet wird ist in Abbildung 2.7 zu sehen. Es werden ein Transformator mit einer Primärwicklung und n Sekundärwicklungen sowie (n+1) Schalter und (n+1) Ansteuersignale für die Schaltung benötigt. [1] Das Funktionsprinzip entspricht dem eines bidirektionalen Flybackconverters. [7] Der Energieaustausch kann auf 2 Arten erfolgen. Wird einer Zelle Energie entzogen und der gesamte Stack damit geladen spricht man von Topbalancing. Entzieht man dem gesamten Stack Energie und ladet damit eine Zelle, so spricht man von Bottombalancing. Es kann jede Zelle im Stack gezielt entladen oder aufgeladen werden. Eine genauere Beschreibung der Funktionsweise befindet sich in [1].

Abbildung 2.7.: Aktiv Balancing mit Transformator

Kapazitive und induktive Balancingschaltungen unterscheiden sich in deren Eigenschaften grundsätzlich. Beim kapazitiven Balancing kann mit relativ geringem Ansteuerungsaufwand ein Spannungsausgleich zwischen den Zellen hergestellt werden. Der Balancingstrom weist, wie für Kapazitäten typisch, hohe Stromspitzen auf, welche abhängig vom Spannungsunterschied der beiden Zellen und den Zuleitungswiderständen samt Schaltwiderstand sind. Haben alle Zellen die selbe Spannung ist kein Ladungsaustausch möglich.

Folgende Berechnungen sollen eine Hilfe bei der Dimensionierung der Schaltung geben und die Verfahren bezüglich Verlustleistung vergleichbar machen. Die Berechnungen erfolgen unter Annahme idealer Bedingungen, also ohne Verlustleistungen an Leitungs-, Einschalt- oder Innenwiderständen.

Die Energie, welche mit einem Kondensator der Kapazität C zwischen 2 Zellen in einem Zyklus ausgetauscht werden kann, ist bei  $VB_1 > VB_2$  definiert durch:

$$W_C = \frac{C \cdot (V_{B1}^2 - V_{B2}^2)}{2} [J] \tag{2.3}$$

Für eine Zyklenfrequenz f, bei der sichergestellt ist, dass der Kondensator vollständig geladen bzw. entladen ist, ergibt sich ein maximaler Leistungsausgleich der Zellen von:

$$P_C = W_C \cdot f[W] \tag{2.4}$$

Das ergibt für die Batterie B1 eine Belastung von:

$$I_{B1+} = \frac{P_C}{V_{B1}}[A] \tag{2.5}$$

Während die Batterie B2 geladen wird mit:

$$I_{B2-} = \frac{P_C}{V_{B2}}[A] \tag{2.6}$$

Mit einer Spule der Induktivität L wird eine Energie von

$$W_L = \frac{L \cdot \hat{i_L}^2}{2} [J] \tag{2.7}$$

zwischen zwei Batterien transferiert. Das ergibt eine Leistung von

$$P_L = W_L \cdot f[W] \tag{2.8}$$

für die Zyklenfrequenz f, die jedoch der Beziehung

$$\frac{1}{f} > t_{ein} + t_{aus} = \hat{i}_L \frac{L}{V_{B1}} + \hat{i}_L \frac{L}{V_{B2}} [s]$$

(2.9)

folgen muss, wenn sichergestellt ist, dass sich die Spule beim maximalen Strom noch nicht in Sättigung befindet. Demnach gilt für den Entladestrom in B1

$$I_{B1+} = \frac{P_L}{V_{B1}}[A] \tag{2.10}$$

während die Batterie B2 geladen wird mit

$$I_{B2-} = \frac{P_L}{V_{B2}}[A] \tag{2.11}$$

Ein Vorteil der induktiven Schaltung liegt in der Unabhängigkeit gegenüber der Batteriespannung. So könnte auch Energie von einer Batterie mit geringerer Zellspannung zu einer mit höherer Zellspannung transferiert werden. Ein solches Balancing wäre denkbar um zum Beispiel statische Temperaturunterschiede oder definierte Kapazitätsunterschiede der Batterien vor einem Entladevorgang auszugleichen.

Weitere Vorteile sind der gemächliche Stromverlauf durch die Spule und die Skalierbarkeit des Balancingstromes mit der Frequenz und den Spulenabmessungen (Sättigung,  $\hat{i}_L$ ). Nachteile ergeben sich durch das Gewicht (Eisenkern), die komplexere Ansteuerung und die höheren Bauteilkosten (Spule, Transformator) der Schaltung.

# 2.3. Fertigungsprozess SPT6

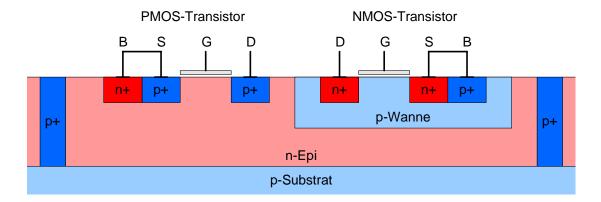

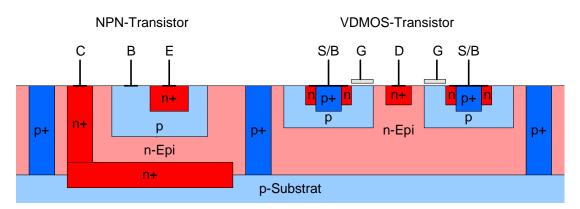

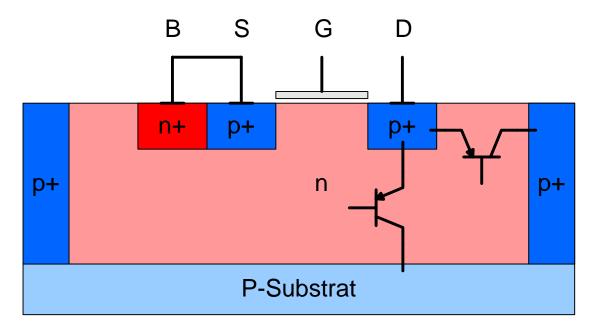

In diesem Kapitel wird die verwendete Technologie sowie deren Bauelemente beschrieben. Abbildung 2.8 zeigt ein Schnittbild des Prozesses. SPT6 steht für Smart Power Technologie und ist ein 800 nm BCD Prozess. Das bedeutet, dass sowohl Bipolar als auch CMOS und DMOS Transistoren in dieser Technologie verfügbar sind.

Auf die p-dotierte Siliziumscheibe wird in einem Epitaxie-Prozessschritt n-dotiertes Silizium aufwachsen gelassen. Durch tiefe p-Dotierungen rund um geplante Epi-Wannen entsteht eine Verbindung zwischen Substrat und Chipoberfäche. Somit kann das Substrat an der Chipoberfläche kontaktiert werden. Im Gegensatz zu konventionellen CMOS Prozessen ist SPT6 ein Zweiwannenprozess was bedeutet, dass im p-Substrat keine Devices platziert werden. Vielmehr wird durch eine flache p-Dotierung in der Epi-Wanne eine p-Wanne erzeugt, in der Bauelemente platziert werden können.

Die Epi-Wannen werden untereinander über eine Junction-Isolierung getrennt. Voraussetzung dafür ist, dass der Substratanschluss am niedrigsten Potential des Chips liegt und das Potential jeder Epi-Wanne über den p-Wannen liegt. Somit sperren alle pn-Übergänge und die einzelnen Wannen stören einander nicht. Die maximale Spannungsfestigkeit der Epi-Wannen zueinander beträgt 60 V womit diese Technologie vor allem für automotive Anwendungen verwendet wird.

Um die Bauelemente untereinander verbinden zu können stehen drei fein strukturierbare Aluminium-Metallebenen sowie eine Kupfer-Metallebene für hohe Ströme zur Verfügung. Des Weiteren können mit 2 Polysiliziumebenen Widerstände mit verschiedenen Schichtwiderstandswerten und spannungsunabhängige Poly-Poly Kapazitäten implementiert werden.

Abbildung 2.8.: Schnittbild SPT6

#### 2.3.1. Bipolar-Transistoren

In SPT6 können vertikale NPN-Transistoren und laterale PNP-Transistoren verwendet werden. Da die Epi-Wanne immer einen Anschluss des Bauelements darstellt ist es oft nicht möglich mehrere Transistoren in einer Epi-Wanne zusammen einzubauen. Das ist jedoch ungünstig, da durch die Junction-Isolation zwischen den Epi-Wannen relativ große Abstände eingehalten werden müssen. Besonders als Einzelbauelement benötigen Bipolar Transistoren viel Chipfläche, weshalb sie, wenn möglich, vermieden werden sollten.

Oft werden die NPN-Transistoren als Z-Dioden eingesetzt indem die Basis-Emitter Diode in Sperrrichtung betrieben wird. Diese Z-Dioden werden zum Beispiel eingesetzt um Niederspannungs (NV) CMOS Schaltungen vor Überspannungen zu schützen. Der Kollektor (= Epi-Wanne) kann dabei entweder mit dem Emitter kurzgeschlossen oder an ein unempfindliches Potential (Versorgungsspannung) angeschlossen werden. Unter gewissen Bedingungen können somit Z-Dioden in eine bestehende Epi-Wanne integriert und der zusätzliche Flächenbedarf minimiert werden.

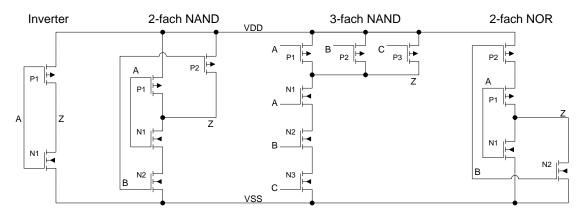

#### 2.3.2. CMOS-Transistoren

In CMOS Schaltungen werden sowohl NMOS- als auch PMOS-Transistoren verwendet. Die PMOS-Transistoren werden in der Epi-Wanne, welche daher den Bulk-Anschluss darstellt, platziert. NMOS-Transistoren werden in einer flacheren p-Wanne innerhalb der Epi-Wanne platziert. Da in einer Epi-Wanne auch mehrere p-Wannen integriert werden können, sind NMOS-Transistoren mit verschiedenen Bulks flächensparender integrierbar als PMOS-Transistoren mit unterschiedlichen Bulk-Anschlüssen.

Es gibt 3 Spannungsklassen bei den PMOS- und NMOS-Transistoren wobei die maximale Drain-Source Spannung zwischen 5 V (NV), 20 V (MV) und 60 V (HV) gewählt werden kann. Je höher die Spannungsklasse, desto größer werden die Transistoren durch die längeren ldd (lightly doped drain)-Abmessungen. Die maximale Gate-Source Spannung ist unabhängig von der Spannungsklasse mit +- 5 V spezifiziert.

#### 2.3.3. DMOS-Transistor

Speziell für das Schalten hoher Ströme wird in SPT6 der DMOS-Transistor (Doppelt Diffundierter MOS) eingesetzt. Dieses Bauelement entspricht den Eigenschaften nach einem optimierten NMOS-Transistor, welcher einen geringen Einschaltwiderstand pro Fläche aufweist und deshalb oft als Highside (HS) oder Lowside (LS) Schalter Verwendung findet. Die maximale Drain-Source Spannung beträgt 60 V mit einer maximalen Gate-Source Spannung von 5 V.

Die Epi-Wanne stellt den Drainkontakt des DMOS-Transistors dar, weshalb eine gemeinsam genutzte Epi-Wanne oft nicht möglich ist. Ein weiterer Nachteil kann die Epi-Substrat Kapazität am Drainanschluss für das dynamische Verhalten bei geringen Signalströmen darstellen. Da ein DMOS-Transistor oft sehr groß ist (bis einige  $mm^2$ ) um hohe Ströme zu schalten, kann der Flächenbedarf der Junction-Isolierung an den Rändern des Bauelements vernachlässigt werden.

# 3. Spezifikation

# 3.1. System

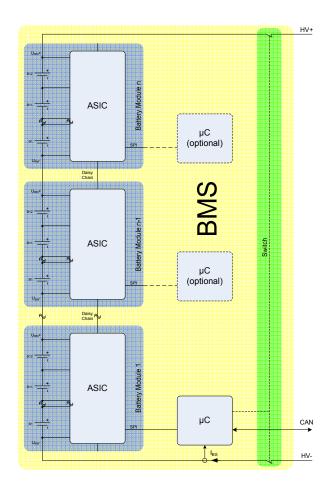

Die Abbildung 3.1 zeigt die wichtigsten Bestandteile des BMS. Um Spannungen von mehreren hundert Volt zur Verfügung zu stellen werden die Batterien in Serie geschalten. Dieser Batteriestack wird in mehrere Module zu je maximal 12 Zellen aufgeteilt. Die Aufteilung in mehrere Module ermöglicht das Auswechseln von fehlerhaften Teilen des Stacks ohne den gesamten Stack austauschen zu müssen. Damit beim Hantieren mit dem Modul keine gefährliche Spannung für den Menschen auftreten kann, sollte die Modulspannung auf jeden Fall unter der Kleinspannungsgrenze von 60 VDC liegen. Mit einer Begrenzung der Zellenanzahl auf 12, bei einer maximalen Zellspannung von bis zu 5 V, wird außerdem die gewohnte Automotive-Spannungsgrenze von 60 V nicht überschritten. Ein ASIC, in der Technologie SPT6 gefertigt, sollte somit die Spannungs- und Temperaturmessung jeder einzelnen Zelle innerhalb des Moduls sicher stellen können.

Ein  $\mu$ C kommuniziert mittels SPI mit dem ersten ASIC im Stack. Alle weiteren ASICs sind mittels Daisy Chain mit dem ersten IC verbunden womit sichergestellt ist, dass der  $\mu$ C mit jedem ASIC kommunizieren kann. Eine Strommessung liefert dem  $\mu$ C den aktuellen Strom des Batteriestacks und ermöglicht zusammen mit den Spannungs- und Temperaturwerten der ASICs die Berechnung der SOC Werte sowie der Innenwiderstände jeder einzelnen Zelle. Erkennt der  $\mu$ C einen Fehler, kann er den Stromkreis mittels eines Schalters jederzeit unterbrechen und somit die Zellen wieder in einen sicheren Betriebszustand bringen. Der  $\mu$ C übernimmt auch die Kommunikation mit der Umgebung z.B. mittels CAN-Bus und liefert damit die Daten für die Ladezustandsanzeige und die Temperatur der Batterie, sowie der verbleibenden Reichweite des Automobils.

Nach der Ermittlung des SOC-Wertes jeder Zelle kann der  $\mu$ C im Bedarfsfall Balancing-Anweisungen an die ASICs zurücksenden und somit einen ausbalancierten Batteriestack sicherstellen.

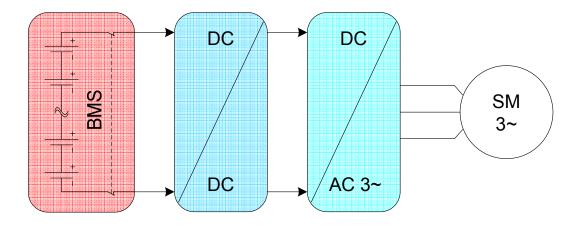

Wie in der Abbildung 3.2 gezeigt kann durch mehrere Module in Serie angeordnet eine Gesamtspannung von mehreren hundert Volt erreicht werden. Da der Elektromotor auf eine maximale Spannung berechnet und optimiert wird, kann die Spannungsänderung der Batterie, bedingt durch die Entladecharakteristik, über einen DC-DC Konverter ausgeglichen werden, während der DC-AC Konverter die Drehzahl der Maschine steuert.

Abbildung 3.1.: Blockschaltbild BMS

Pro Modul wird ein ASIC auf einer Platine in das Modulgehäuse zusammen mit den Batterien verbaut. Der ASIC versorgt sich direkt von den Batterien, die er überwachen soll. Dies setzt einen möglichst geringen Stromverbrauch voraus. Auf der Platine befinden sich je nach verwendeter Balancing Methode auch die benötigten externen Bauteile wie Widerstände, Transformator, Kapazitäten usw.

Das BMS kommuniziert nach außen über die CAN-Schnittstelle des  $\mu$ C. Die berechneten SOC- und Innenwiderstands-Werte der Batterie liefern dem Fahrer Informationen darüber, wie voll die Batterie ist und wie weit das Auto noch fahren kann bzw. wann die Batterie zu tauschen ist. Ein Fehlerfall kann auch direkt in das Motormanagement des Autos eingreifen.

Innerhalb des BMS stellt die Kommunikation zwischen den ASICs und dem  $\mu$ C auf Grund der großen Spannungsunterschiede eine besondere Herausforderung an die Kommunikationsschnittstelle des ASICs dar. Jeder ASIC soll über ein Daisy Chain Interface

Abbildung 3.2.: Blockschaltbild Elektrischer Antrieb

und ein SPI Interface verfügen. Prinzipiell funktioniert die Kommunikation innerhalb des BMS nach dem Master-Slave Prinzip. Der  $\mu C$  als Master fordert Daten von den ASICs an, welche diese dann an den  $\mu C$  zurück schicken. Der Master veranlasst, nach dem Auswerten der Messdaten, einen bestimmten ASIC einen Balancingvorgang für bestimmte Zellen durchzuführen. Lediglich ein Fehler innerhalb des Moduls veranlasst den ASIC von sich aus mit dem  $\mu C$  zu kommunizieren.

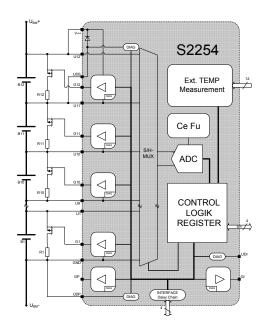

# 3.2. Chip

Die Entwicklung eines ASICs für diese Applikation stellt für Infineon eine neue Herausforderung dar. In der ersten Entwicklungsstufe soll ein ASIC entworfen werden, mit dessen Hilfe man ein möglichst breites Spectrum an Balancing Schaltungen abdecken kann. Ziel ist es einen funktional überdimensionierten Chip zu entwickeln, der die verwendeten Schaltungsblöcke implementiert und zum Aufbau von Prototypen herangezogen werden kann. Das entspricht nicht den üblichen Anforderungen an einen IC, nur die nötigsten Funktionen zu implementieren um kostenoptimierte ICs in hoher Stückzahl produziert werden können. Durch diesen Zwischenschritt kann Know How in diesem neuen Anwendungsgebiet aufgebaut werden, welches in der zweiten Entwicklungsphase zu einem optimierten und kommerziell erfolgreichen Produkt führen soll.

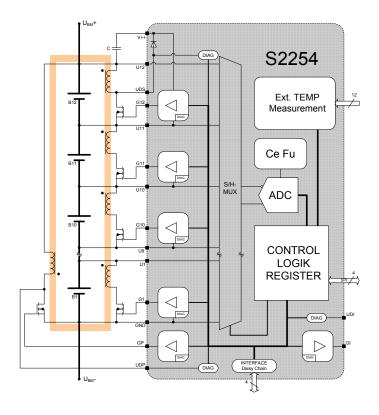

Der Chip soll grundsätzlich für passives Balancing (Abbildung 3.4) oder aktives Balancing (Abbildung 3.3) verwendet werden können. In welchem Betriebsmodus der IC arbeitet wird durch die äußere Beschaltung des ICs festgelegt.

Die wichtigsten Funktionen des ICs sind:

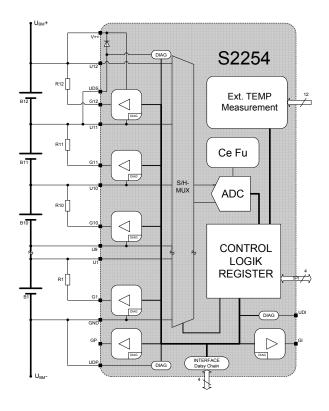

Abbildung 3.3.: Blockschaltbild IC aktiv Balancing

- Überwachen aller Zellspannungen und Zelltemperaturen

- Kommunikation über Daisy Chain und SPI

- Balancing der Batteriezellen nach Vorgabe des μCs

Abbildung 3.3 und 3.4 zeigen die einzelnen Blöcke des ICs.

Die Kommunikation unter den ASICs verläuft über eine Daisy-Chain welche aus zwei Leitungen besteht. Die Information soll über ein differentielles Stromsignal zwischen den Interfaces von einem Modul-Spannungslevel zum nächsten weitergegeben werden. Die SPI-Schnittstelle dient vor allem als Verbindung zwischen den ASICs und dem Master (μC), welche nur vom untersten ASIC im Stack aus betrieben wird. Eine besondere Herausforderung an das Daisy-Chain Interface ist ein hoher Spannungsunterschied (bis zur gesamten Stackspannung) bei Unterbrechung der Batterieverbindung zwischen den Modulen. Die kann Beispielsweise vorkommen, wenn ein Sicherungsschalter für Wartungszwecke in der Mitte des Stacks angeordnet wird. Da die Batteriemodule auch örtlich verteilt im Fahrzeug untergebracht werden können sind die Leitungswiderstänzwischen den Batteriemodulen unbedingt zu berücksichtigen. Diese Leitungswiderstän-

Abbildung 3.4.: Blockschaltbild IC passiv Balancing

de können je nach Betriebsart (Laden oder Entladen) bei entsprechenden Strömen nicht zu vernachlässigende Spannungsunterschiede zwischen den Interfaces hervorrufen.

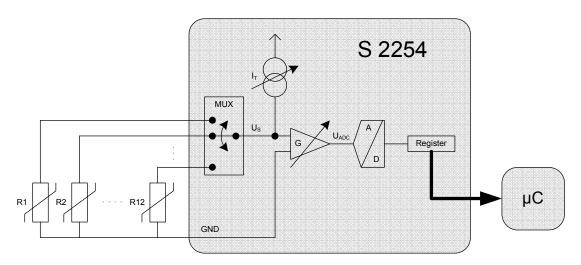

Die Messung der Zellspannungen erfolgt über ein S&H Glied kombiniert mit einem Multiplexer und einem ADC. Diese Anordnung kann gewählt werden da die Spannungsüberwachung mit einer Messung aller Batterien in einer Sekunde gegeben ist. Die Spannungen sollen jedoch möglichst gleichzeitig zu einem bestimmten Zeitpunkt gemessen werden. Nach einem Messbefehl werden mittels dem S&H Glied alle Zellspannungen gleichzeitig abgegriffen und auf das niedrigste Potential des Batterieblocks (GND) bezogen. Der Digitalteil kann später mittels dem Multiplexer und dem ADC eine Zellspannung nach der anderen konvertieren und in den dafür vorgesehenen Registern speichern. Der Vorteil dieser Topologie ist, dass nur ein ADC samt Referenzspannungsquelle benötigt wird.

Eine große Herausforderung stellt jedoch der S&H-Multiplexer dar, welcher für Commonmode Spannungen bis zu 60 V ausgelegt werden muss.

Die benötigte Auflösung des ADCs ergibt sich aus der Entladecharakteristik der verwendeten Zelle. Je flacher die Entladekurve verläuft, umso genauer muss der ADC die Spannung auflösen um dennoch eine genaue SOC-Berechnung zu ermöglichen. Da die

Entladecharakteristik unter den verschiedenen Zelltypen stark variiert empfiehlt es sich für die Berechnung der benötigten Auflösung des ADCs die ungünstigste Zelle zu verwenden. Die Auflösung soll innerhalb eines einstellbaren Spannungsbereichs, der nicht größer als 1 V ist, 1 mV betragen, was einen 10-bit ADC voraussetzt.

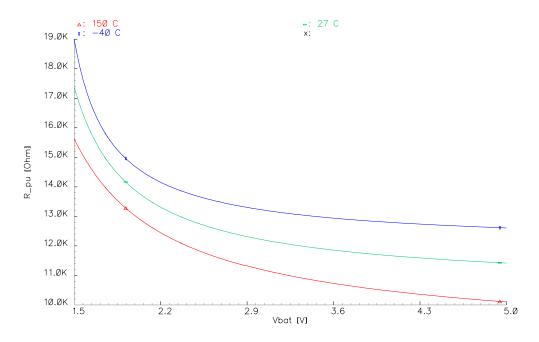

Wie in Abbildung 3.5 gezeigt soll die Temperaturmessung über einen Multiplexer und einen eigenen ADC, welcher alle Spannungen mit einer Frequenz von 0,1 bis 10 Hz messen soll, erfolgen. Ein Referenzstrom erzeugt durch den NTC-Widerstand eine temperaturabhängige Spannung, welche mit dem ADC gemessen wird. Der  $\mu$ C rechnet anschließend aus dem digitalen Wert die Temperatur des Widerstandes aus. Der eingezeichnete programmierbare Verstärker wird benötigt um die Messspannung an den Eingangsspannungsbereich des ADCs anzupassen. Die Nominalwerte der verwendeten NTC-Widerstände soll zwischen 5 und 50 k $\Omega$ , bei einem Temperaturkoeffizient zwischen 2,3 und 7,4 %/°C, betragen. Die geforderte Auflösung beträgt 1 °C, was bei einem Temperaturbereich von -40 °C bis 150 °C mindestens einen 8-bit ADC erfordert. Neben einer Übertemperaturabschaltung des Chips soll außerdem ein am Chip integrierter Temperatursensor über diesen ADC ausgelesen werden.

Abbildung 3.5.: Blockschaltbild Zell-Temperaturmessung

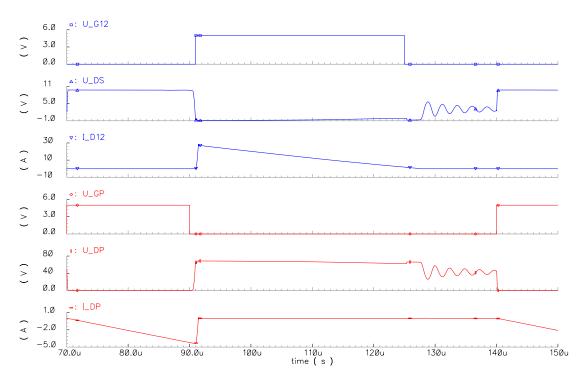

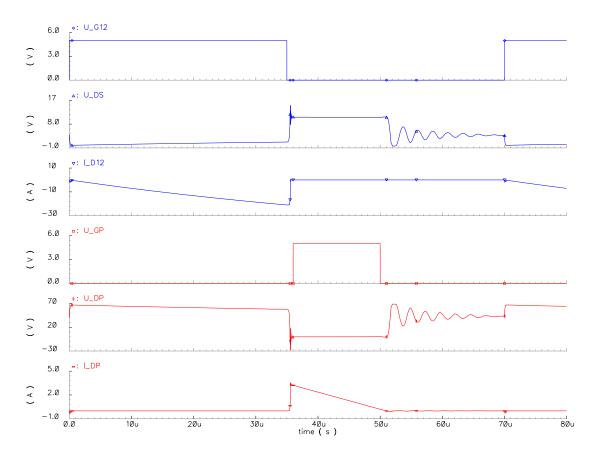

Um Fehler der externen Bauteile zu detektieren und darauf reagieren zu können, soll der IC über eine Funktionskontrollschaltung verfügen. Es kann beim aktiv Balancing in Abbildung 3.3, durch Überwachen der Drainspannungen des Primärtransistors sowie der Drainspannung eines Sekundärtransistors, eine Funktionskontrolle implementiert werden. Wird zuerst der Primärtransistor eingeschaltet, wie es beim Bottom-Balancing (Abbildung 3.6) der Fall ist, kann man an den Sekundärtransistoren eine Spannungsüberhöhung gegenüber der Zellspannung feststellen die proportional dem Wicklungsverhältnis des Transformator ist. Durch eine Spannungsüberwachung am Pin UDS (Abbildung

3.3) kann somit festgestellt werden, ob der Primärtansistor funktioniert bzw. ob die magnetische Kopplung zwischen den Wicklungen des Transformators gegeben ist.

Abbildung 3.6.: Bottom Balancing

Beim Top-Balancing der Schaltung in Abbildung 3.3 wird zunächst ein Sekundärtransistor eingeschaltet was analog zum vorigen Fall eine Spannungsüberhöhung am Primärtransistor bewirkt (siehe Abbildung 3.7) . Mittels dem Pin UDP kann somit die Funktion der Sekundärtransistoren sowie des Transformators ebenfalls festgestellt werden.

Abbildung 3.7.: Top Balancing

Im Central-Funktions Block (CeFu) vereinen sich Standardblöcke, wie sie in vielen Chips zu finden sind. In diesem IC sind dies Bandgap, Oszillator, Power On Reset, Undervoltage Detection, Spannungsregler usw. Auf diese Schaltungsblöcke soll in dieser Arbeit nicht näher eingegangen werden.

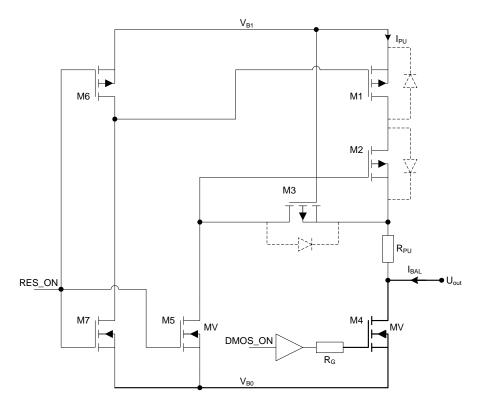

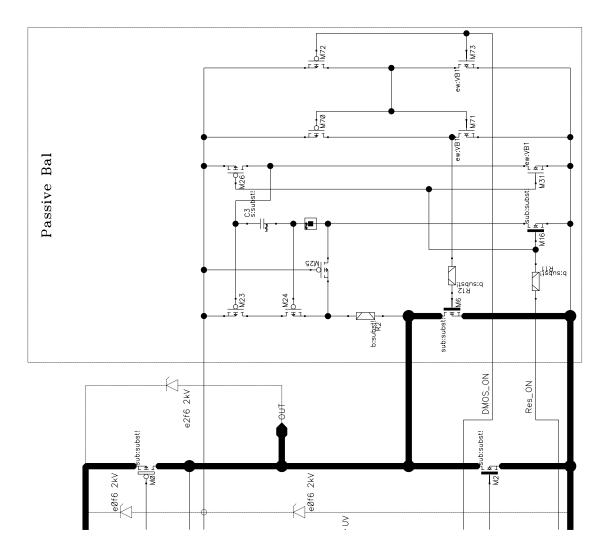

# 3.3. Ausgangsstufe

Die Ausgangsstufe des Chips besteht aus dem Gatedriver (HS und LS Stromquelle), einem LS-Schalter mit einem abschaltbaren Pullup-Widerstand sowie den Diagnoseschaltungen. Im aktiv Balancing Betriebsmodus steuert die Ausgangsstufe einen externen NMOS-Transistor mit einer Freuquenz zwischen 10 und 50 kHz als Schalter an. Aus Sicht der EMV ist ein Laden des Gates mit einem konstanten Strom, gegenüber einer Variante mit Highside- und Lowsideschalter, zu bevorzugen. Für das passive Balancing hingegen kann der DMOS einfach mittels HS- und LS-Schalter angesteuert werden, da

dieser nur selten (während Ladevorgängen) und für längere Zeit (bis zum Ende des Ladevorgangs) eingeschaltet wird.

Für die Bemessung des Lade- und Entladestroms des Gates wurde aus dem Datenblatt des IPD70N03S4L (NMOS 30 V 70 A) der Firma Infineon aus der Gateladungskurve bei einer Gatespannung von 5 V und einer Drain-Source Spannung kleiner 6 V eine Ladung von 18 nC ermittelt. Soll der Transistor in 1 µs vollständig geladen sein benötigt man einen Gateladestrom von  $I=\frac{Q}{t}=18~mA$ . In Absprache mit den Projektpartnern wurde vereinbart, dass der Lade- und Entladestrom auf 15, 20 oder 25 mA per SPI eingestellt werden können soll.

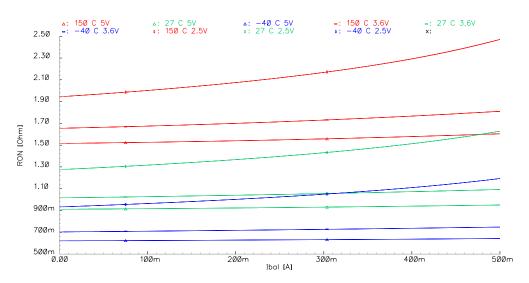

Beim passiven Balancing wird der Balancestrom über den integrierten DMOS-Schalter geführt. Geht man von einer maximalen Umgebungstemperatur  $T_{U_{max}}$  an der Unterseite des Packages aus sowie von einer unteren Abschalttemperaturschwelle  $T_{ab_{min}}$  des internen Temperatursensors aus, so kann über den thermischen Widerstand des Packages  $R_{thJC}$  die maximale Verlustleistung des Chips berechnet werden.

$$P_{tot_{max}} = \frac{T_{down_{min}} - T_{U_{max}}}{R_{thJC}} \tag{3.1}$$

Die Gesamtverlustleistung setzt sich zum Großteil aus der Verlustleistung des Spannungsreglers und den Verlustleistungen der LS-Schalter in den Ausgangsstufen zusammen. Die Verlustleistung des DMOS-Transistors ist abhängig vom Balancestrom sowie vom  $R_{on}$  des DMOS-Transistors.

$$R_{on_{max}} = \frac{P_{DMOS_{max}}}{I_{bal}^2} \tag{3.2}$$

Der minimal garantierte passive Balancestrom durch den DMOS-Transistor wurde mit 200 mA definiert. Daraus ergab sich ein maximaler  $R_{on}$  des DMOS-Transistors von ca. 2  $\Omega$ . Dieser  $R_{on}$ -Wert soll für Zellspannungen größer 2,5 V garantiert werden, da bei kleineren Zellspannungen eine weitere Entladung der Zelle nicht sinnvoll erscheint.

Die Versorgungsspannung der Ausgangsstufe variiert mit der erlaubten Zellspannung, welche sich zwischen 2 und 5 V befinden kann, wobei die typische Zellspannung heute verwendeter hochenergie Zelltypen ca. 3,6 V beträgt. Die Unterspannungserkennung besitzt einen Auslösebereich zwischen 1,5 und 2 V bei steigender Versorgungsspannung. Bei Unterschreiten dieser Zellspannung wird die Ausgangsstufe durch den Digitalteil in den Power-Down (PD) Betriebszustand versetzt. Insgesamt darf die Ausgangsstufe also von 1,5-5 V Zellspannung keine Fehler verursachen. In diesem Bereich müssen auch alle Diagnosefunktionen erfüllt werden. Da die Balancingfunktionen erst ab erhöhten Zellspannungen benötigt werden und ein einfacheres Design zu erwarten ist, wurde dessen Spezifikationsbereich auf Zellspannungen zwischen 2,5-4,5 V begrenzt. Außerhalb dieser Spezifikationsgrenze werden die Balancing-Funktionen grundsätzlich noch richtig ausgeführt, wobei aber Werte wie  $R_{on}$ , Lade- und Entladestrom deren spezifizierten Bereich verlassen.

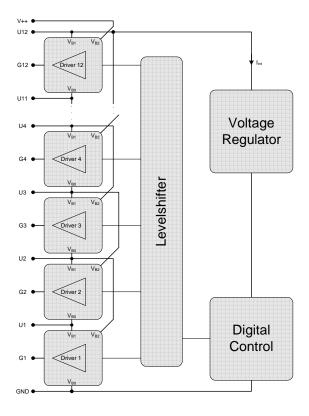

Abbildung 3.8.: Versorgung Ausgangsstufe

Ein Problem der Ausgangsstufe im aktiv Balancing ist deren Versorgungsspannung. Bei einem Logic Level MOSFET benötigt man eine 5 V Spannungsversorgung um den Transistor vollständig einzuschalten. Da die Spannung einer Lithium Ionen Zelle zu gering ist, versorgen jeweils 2 Batterien einen Gatedriver. Somit wird der Transistor für alle Zellspannungen größer 2,5 V sicher eingeschaltet. In Abbildung 3.8 erkennt man die Beschaltung der Ausgangsstufen-Versorgungen sowie den Levelshifter und den Digitalteil samt Spannungsregler. Der Levelshifter wird benötigt um die Kommunikation zwischen den verschiedenen Spannungsebenen zu ermöglichen. Für die maximal erlaubte Zellspannung von 5 V wird das Gate bis auf 10 V aufgeladen, was für viele MOS-Transistoren jedoch kein Problem darstellt. Da dem letzten Gatedriver keine zweite Batterie zur Verfügung steht, muss eine Hilfsspannung erzeugt werden. Bedingt durch das aktive Balancing entsteht am Pin UDS (Abbildung 3.3) bei jedem Balancing-Zyklus eine Spannungsüberhöhung gegenüber  $U_{12}$ , welche über eine Diode in einer externen Kapazität gespeichert werden kann. Bei ausreichender Dimensionierung der Kapazität kann das Gate mit der Spannung  $V_{++}$  geladen werden.

Die Spannung  $V_{++}$  lässt sich in Abhängigkeit von der Zellspannung und der Wicklungsverhältnisse wie folgt berechnen:

$$V_{++} = \hat{U_{DS}} - U_{D_f} = U_{12} \left( 1 + \frac{N_S}{N_P} \right) - U_{D_f}$$

(3.3)

$U_{D_f}$  ... Diodenspannung

$N_P$  ... Windungszahl Primärwicklung  $N_S$  ... Windungszahl Sekundärwicklung

Um bei verschieden Zelltypen und verschiedenen Wicklungszahlen des Transformators immer die selbe Spannung zur Verfügung zu haben empfiehlt es sich eventuell einen Spannungsregler zwischen dem Pin V++ und  $V_{B2}$  der letzten Ausgangsstufe vorzusehen. Bei der Schaltungsentwicklung ist zu berücksichtigen, dass bei passivem Balancing die Spannung  $V_{++}$  nicht erzeugt werden kann bzw. somit die Ausgangsstufe mit Ausnahme der Highside-Stromquelle von nur einer Zellspannung betrieben werden muss.

Da der Chip Sicherheitsanforderungen (nach IEC 61508) erfüllen muss sind verschiedene Diagnosefunktionen in die Ausgangsstufe zu integrieren, um Fehler erkennen und dementsprechend reagieren zu können.

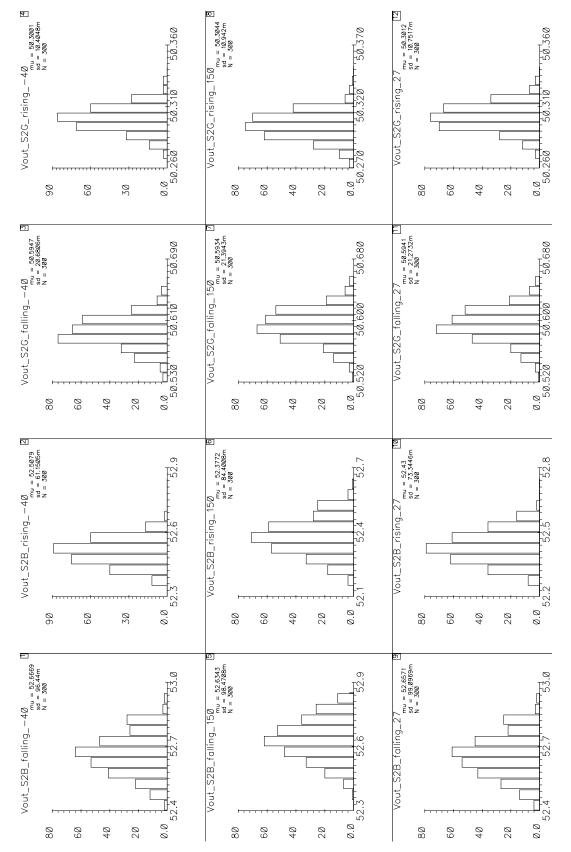

Beim aktiven Balancing wird die Ausgangsstufe durch das Gate kapazitiv belastet. Um zu erkennen, ob der Ausgang mit  $V_{B0}$  oder  $V_{B1}$  kurzgeschlossen wurde, wird die Ausgangsspannung im Betrieb mit den Referenzspannungen  $U_{S2G}$  und  $U_{S2B}$  verglichen. Es gilt für die Wahl der Referenzspannungen  $V_{B0} < U_{S2G} < V_{B1} < U_{S2B} < V_{B2}$  wobei jede Referenzspannung eine Hysterese aufweist um ein Toggeln des Ausgangs zu verhindern.

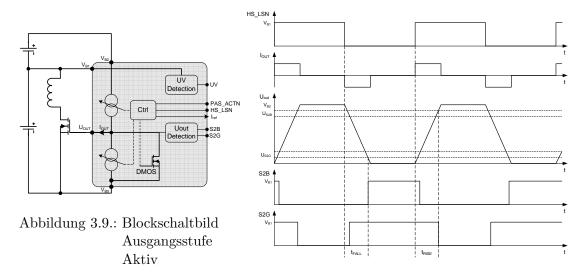

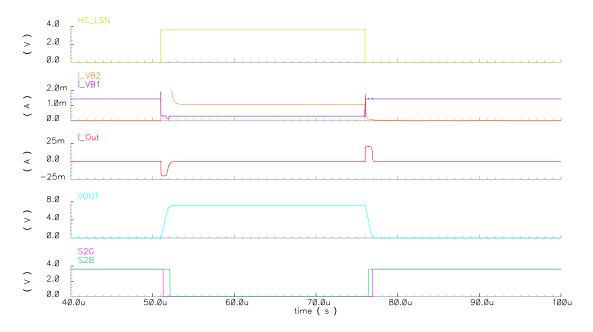

Abbildung 3.10 zeigt das Ansteuersignal HS\_LSN, Ausgangsspannung und Ausgangsstrom sowie die Diagnosesignale S2B und S2G bei einer Belastung des Ausganges mit einer Kapazität. Nach Aufwachen der Ausgangsstufe ist HS\_LSN=0 und die Ausgangsspannung  $U_{out} = V_{B0}$ , weshalb die Signale S2B und S2G auf logisch 1 liegen werden. Will man nun den MOSFET einschalten wird HS\_LSN=1 und der Treiber ladet das externe Gate. Die Ausgangsspannung erreicht zunächst die Schwelle  $U_{S2G_H} = 0.9 \cdot V_{B2}$  worauf S2G=0 wird. Nach Überschreiten der Spannung  $U_{S2B_H} = 0.9 \cdot V_{B2}$  wird auch S2B=0 und der Transistor ist somit eingeschaltet.

Wird nun wieder HS\_LSN=0 so fällt die Ausgangsspannung zunächst auf  $U_{S2B_L}=0.8\cdot V_{B2}$  womit S2B=1 wird. Fällt die Spannung unter  $U_{S2G_L}=0.1\cdot V_{B2}$  so ist S2G=1 und der Initialzustand ist wieder hergestellt. Der Digitalteil erwartet nach jedem Umschalten des Signals HS\_LSN innerhalb der Zeit  $t_{RISE_{max}}=t_{FALL_{max}}$ , dass beide Ausgänge von 1 auf 0 bzw. von 0 auf 1 wechseln. Trifft das nicht ein wird dem  $\mu$ C ein Fehler an dieser Ausgangsstufe gemeldet.

Abbildung 3.10.: Diagnose Aktiv Balancing

#### Detektierbare Fehler sind:

- niederohmige Verbindung zwischen den Pin Out und  $V_{B0}$  (S2B=1 S2G=1)

- niederohmige Verbindung zwischen den Pin Out und  $V_{B1}$  (S2B=0 S2G=1)

- niederohmige Verbindung zwischen den Pin Out und  $V_{B2}$  (S2B=0 S2G=0)

- HS oder LS Stromquelle funktionieren nicht mehr

- Externe Kapazität  $C_{Load} > \frac{t_{RISE} \cdot I_{OUT}}{0.9 \cdot V_{B2}}$

Wird die Verbindung zwischen Ausgangsstufe und MOSFET unterbrochen (Openload) entspricht dies beim aktiven Balancing einer zu kleinen Ausgangskapazität und ist nur mit hohen Aufwand zu detektieren. Da dieser Fall jedoch auch mittels der am Chip geplanten Funktionskontrollschaltung erkannt wird, kann eine separate Detektionsschaltung in der Ausgangsstufe entfallen.

Wird die Ausgangsstufe beim aktiven Balancing in den Power-Down Betriebszustand versetzt, so werden beide Stromquellen deaktiviert und der DMOS-Transistor wird eingeschaltet. Damit ist  $U_{out} = V_{B0}$  bzw. der externe NMOS ist sicher ausgeschaltet und der Stromverbrauch der Schaltung kann auf ein Minimum reduziert werden.

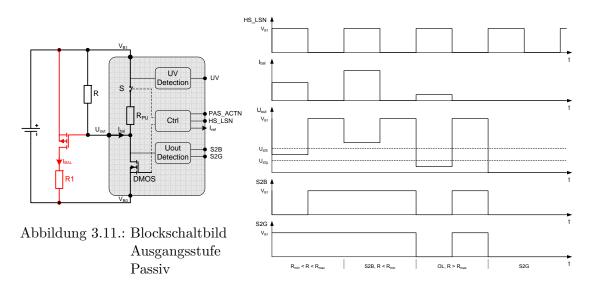

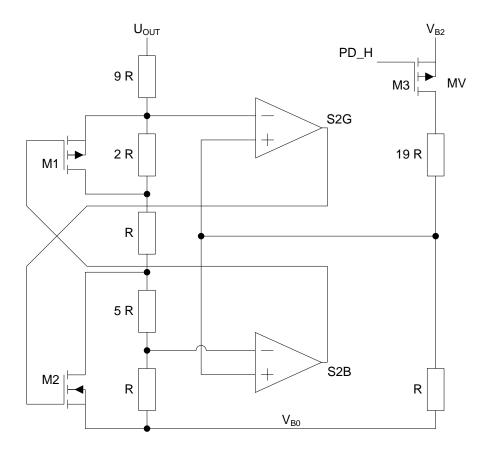

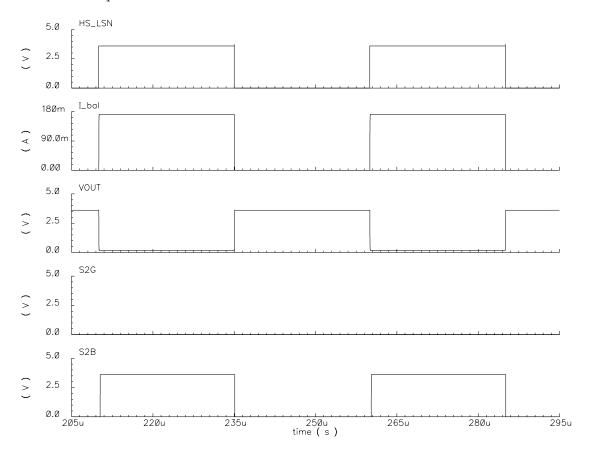

Beim passiven Balancing ist der Ausgang mittels eines Widerstandes R mit  $V_{B1}$  verbunden. Der Widerstand verhindert, dass ein zu hoher Strom den DMOS-Transistor thermisch beschädigt. Betrachtet man den DMOS-Transistor im eingeschalteten Zustand so stellt dieser einen spannungs- und temperaturabhängigen Widerstand dar. Mittels ei-

ner Spannungsüberwachung am Drainpotential sollen Kurzschluss- und Openload-Fehler erkannt werden. Dazu wird die Drainspannung des DMOS-Transistors mit den Referenzspannungen  $U_{s2q}$  und  $U_{s2b}$  verglichen. Ist der DMOS-Transistor eingeschaltet, so muss  $U_{s2b} < U_{out} < U_{s2b}$  sein, wenn der externe Widerstand richtig dimensioniert ist. Spricht S2G oder S2B nach dem Einschalten des DMOS-Transistors länger als  $t_{delay}$  an, so wird der Fehler an den µC weitergegeben. In Abbildung 3.12 werden die zu erwarteten Kombinationen der Diagnosesignale bei verschiedenen externen Widerständen gezeigt.

Abbildung 3.12.: Diagnose Passiv Balancing

Die Diagnose soll für einen Balancestrom  $I_{bal}$  im Bereich zwischen 50 und 200 mA bei einem typischen  $R_{ON}$  von  $1\Omega$  keinen Fehler ausgeben.

Somit berechnen sich die Schranken zu:

$$U_{s2b} > I_{bal_{max}} \cdot R_{ON_{max}} \tag{3.4}$$

$$U_{s2g} < I_{bal_{min}} \cdot R_{ON_{min}} \tag{3.5}$$

Für die Dimensionierung von R gilt allgemein:

$$I_{bal} = \frac{U_{out}}{R_{ON}} \tag{3.6}$$

$$I_{bal} = \frac{U_{out}}{R_{ON}}$$

$$R_{max} = \frac{R_{ON_{max}}}{U_{s2g}} \cdot (V_{B1_{max}} - U_{s2g})$$

$$R_{min} = \frac{R_{ON_{min}}}{U_{s2b}} \cdot (V_{B1_{max}} - U_{s2b})$$

(3.6)

$$(3.7)$$

$$R_{min} = \frac{R_{ON_{min}}}{U_{s2b}} \cdot (V_{B1_{max}} - U_{s2b}) \tag{3.8}$$

$R_{ON}$  ... Einschaltwiderstand des DMOS-Transistor

$U_{s2b}$  ... obere Spannungsgrenze für  $U_{out}$   $U_{s2g}$  ... untere Spannungsgrenze für  $U_{out}$   $V_{B1_{max}}$  ... maximal erlaubte Zellspannung

Mit der rot eingezeichneten Zusatzbeschaltung in Abbildung 3.11 kann ein höherer Balancestrom erreicht werden.

Wird der DMOS-Transistor ausgeschaltet (HS\_LSN=0) oder ist die Ausgangsstufe im Power-Down Betriebszustand, so wird der Pin OUT mittels eines Pullup-Widerstandes  $R_{PU}$  auf  $V_{B1}$  geschaltet. Damit wird bei einem Openload bzw. bei kapazitiver Belastung des Ausganges (Gate eines PMOS-FET) die Ausgangsspannung  $V_{out} = V_{B1}$  im ausgeschalteten Zustand definiert. Außerdem wird somit eine Unterscheidung der Fehler S2G und Openload ermöglicht.

Abbildung 3.13.: Passiv Balancing mit externen PMOS

Mit der äußeren Beschaltung in Abbildung 3.13 ist es prinzipiell möglich mittels eines zusätzlichen PMOS-FETs oder eines PNP-Transistors auch mit höheren Balanceströmen passiv Ladungsunterschiede auszugleichen. Da der Drainstrom des DMOS-Transistors jedoch nur mehr einen Bruchteil des spezifizierten Balancestromes ausmacht, wird S2G ständig einen Fehler auslösen und müsste dementsprechend ausmaskiert werden. Eine Openload- bzw. eine Kurzschlussdetektion (OUT mit  $V_{B0}$ ) kann mit dieser Schaltung nicht mehr gewährleistet werden.

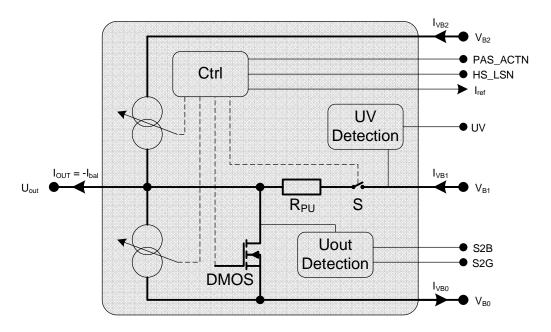

In Abbildung 3.14 wird das Blockschaltbild der Ausgangsstufe gezeigt.

Abbildung 3.14.: Blockschaltbild Ausgangsstufe

Die folgende Tabelle 3.1 zeigt die bereits oben diskutierte Spezifikation der Ausgangsstufe in kompakter Form.

| Parameter                      | Symbol min     | mim | typ                | max | Einheit | max   Einheit   Kommentar                         |

|--------------------------------|----------------|-----|--------------------|-----|---------|---------------------------------------------------|

| Nominale Versorgungsspannung   | $V_{B2}$       | 5   | 7,2                | 6   | Λ       | $V_{B2} = 2 \cdot V_{B1}$                         |

| Erweiterte Versorgungsspannung | $V_{B2_{ext}}$ | 3   | 7,2                | 10  | Λ       | keine Fehlfunktionen der Schaltung                |

| Unterspannung Detektionsgrenze | $U_{UV}$       | 1,5 | 1,75               | 2   | Λ       | wenn $V_{B1} < U_{UV}$ wird $UV = V_{B1}$         |

| Gateladestrom                  | $I_{OUT}$      | 15  | 20                 | 25  | mA      | einstellbarer Ladestrom bei $U_{OUT} = V_{B1}$    |

| Gateentladestrom               | $I_{OUT}$      | -15 | -20                | -25 | mA      | einstellbarer Entladestrom bei $U_{OUT} = V_{B1}$ |

| Aktiv S2G Referenz             | $U_{S2G_L}$    |     | $0.1 \cdot V_{B2}$ |     | ^       | Referenz bei fallendem $U_{OUT}$                  |

| Aktiv S2G Referenz             | $U_{S2G_H}$    |     | $0.2 \cdot V_{B2}$ |     | Λ       | Referenz bei steigendem $U_{OUT}$                 |

| Aktiv S2B Referenz             | $U_{S2B_L}$    |     | $0.8 \cdot V_{B2}$ |     | Λ       | Referenz bei fallendem $U_{OUT}$                  |

| Aktiv S2B Referenz             | $U_{S2B_H}$    |     | $0.9 \cdot V_{B2}$ |     | ^       | Referenz bei steigendem $U_{OUT}$                 |

| Einschaltzeit                  | $t_{RISE}$     |     | 1                  | ಒ   | hs      | bei $C_{iss} = 2.5 \ nF$ und typ. $V_{B2}$        |

| Ausschaltzeit                  | $t_{FALL}$     |     | 1                  | ಒ   | hs      | bei $C_{iss} = 2.5 \ nF$ und typ. $V_{B2}$        |

| Balancingfrequenz              | $f_{BAL}$      | 10  | 25                 | 20  | kHz     | aktive Balancing                                  |

| Balancingstrom                 | $I_{bal}$      | 20  |                    | 200 | mA      | passiv Balancing $I_{bal} = -I_{OUT}$             |

| DMOS Einschaltwiderstand       | $R_{ON}$       |     | 1                  | 2   | $\Im$   | max. Wert bei 120 °C und $V_{B1} = 2.5V$          |

| Pullup-Widerstand              | $R_{PU}$       | 10  |                    |     | kΩ      | integrierter Pullup-Widerstand                    |

| Passiv S2G Referenz            | $U_{s2g}$      |     |                    | 40  | mV      | $U_{s2g} < I_{bal_{min}} \cdot R_{ON_{min}}$      |

| Passiv S2B Referenz            | $U_{s2b}$      | 400 |                    |     | mV      | $U_{s2b} > I_{bal_{max}} \cdot R_{ON_{max}}$      |

| Delayzeit                      | $t_{delay}$    |     | 5                  |     | srl     | Zeit bis Fehler gemeldet wird                     |

Tabelle 3.1.: Spezifikation der Ausgangsstufe

# 4. Schaltungsentwurf

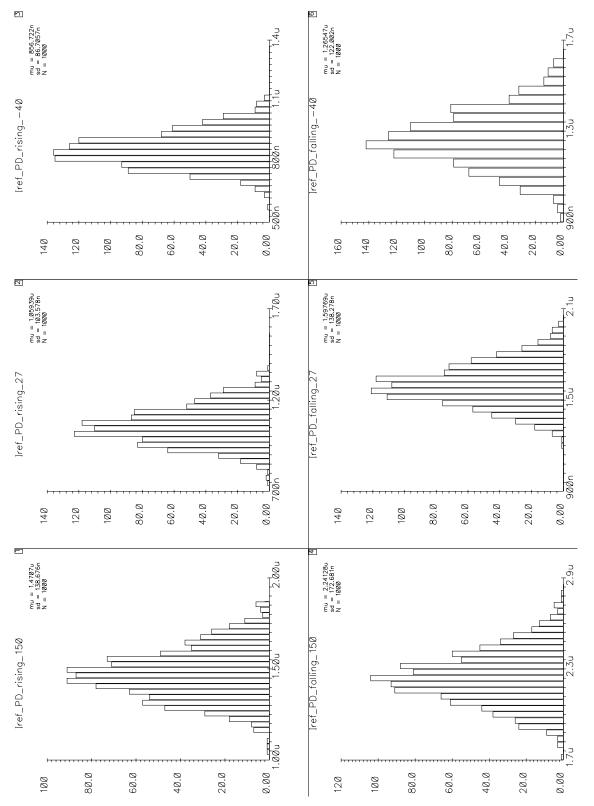

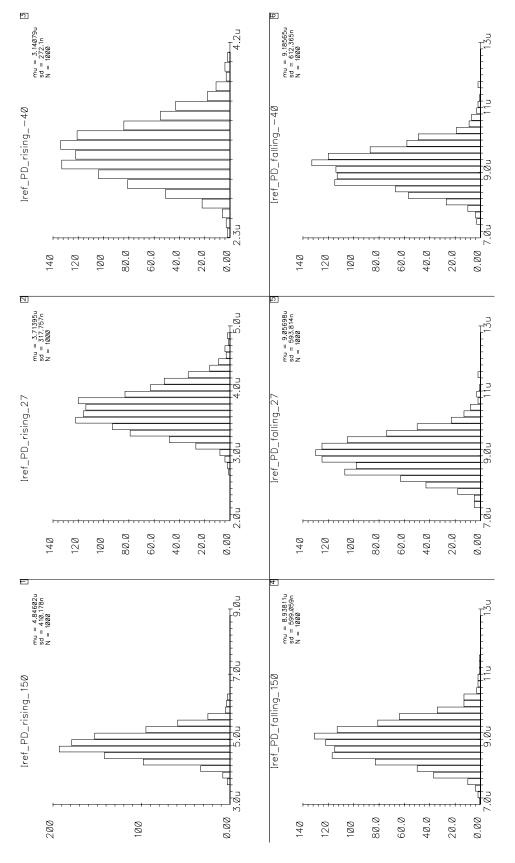

# 4.1. Aktiv Balancing Schaltung

Die Ansteuerung des externen MOSFETs erfolgt über zwei Stromquellen. Die einstellbaren HS- und LS-Stromquellen sollen das Gate mit einem Strom zwischen 15 und 25 mA laden oder entladen können. Die Ausgangsstufe verfügt über einen Referenzstrom, welcher von der Bandgap Spannungsreferenz und einem Polywiderstand abgeleitet wird. Um die Schwankungen des Absolutwertes bedingt durch die Prozessstreuung des Polywiderstandes zu kompensieren wird der Strom getrimmt. Grundsätzlich soll der Referenzstrom der Ausgangsstufe im Betrieb zwischen 15 und 25  $\mu A$  variiert werden können. Dieser Referenzstrom, 1000-fach verstärkt, soll den Lade- und Entladestrom der Ausgangsstufe bestimmen.

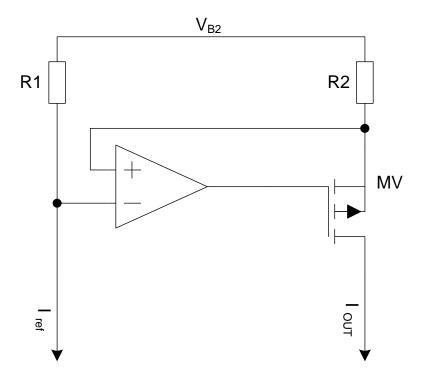

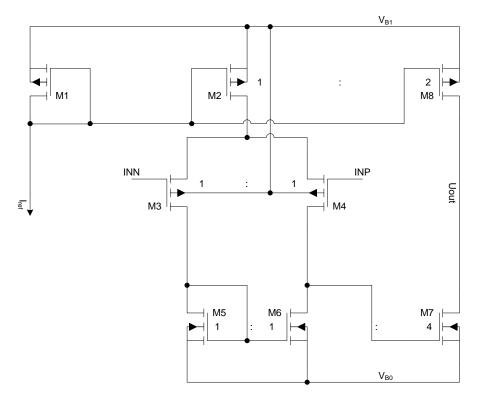

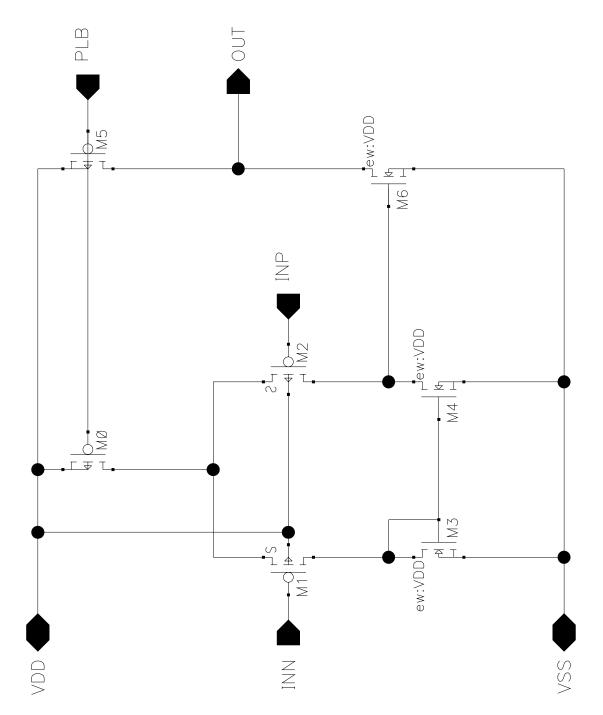

## 4.1.1. Stromquelle

Die schaltungstechnische Implementierung einer Stromquelle kann auf verschiedene Arten erfolgen. Im Wesentlichen reduziert sich die Auswahl der Schaltungstopologie auf zwei Varianten. Eine Operationsverstärker (OPV) Schaltung für die HS-Stromquelle, wie sie in Abbildung 4.1 gezeigt wird, erlaubt bei integrierten Schaltungen einen Stromspiegel mit hoher Stromverstärkung. Ein weiterer OPV würde für die äquivalente LS-Schaltung benötigt werden. Der Ausgangsstrom berechnet sich aus dem Verhältnis der beiden Widerstände und dem Referenzstrom. Werden die Widerstände aus den gleichen Teilwiderständen gebaut, kann ein gutes Matching zwischen den Widerständen erreicht und der Einfluss der Widerstands-Prozessstreuung sowie des Widerstands-Temperaturgangs minimiert werden.

$$I_{OUT} = I_{ref} \cdot \frac{R_1}{R_2} \tag{4.1}$$

Ein Vorteil dieser OPV Schaltung ist zum einen die geringe Stromaufnahme, bestimmt durch den Referenzstrom, sowie dem OPV. Als Nachteil ist die Source-Degeneration des Mittelvolt-PMOS zu nennen, welche sich in der Größe des Bauelements negativ auswirkt. Des weiteren müsste ein eigener Referenzstrom für die OPV in die Ausgangsstufe geführt werden, welcher auch bei verschiedenen Ausgangsströmen konstant bleibt. Die Common-Mode Spannung des OPVs wird durch die Dimensionierung der Widerstände bestimmt.

Abbildung 4.1.: OPV Stromquelle

Ein weiterer Nachteil ergibt sich durch die Versorgungsspannung des OPVs, welcher einen eigenen Spannungsregler benötigt um den OPV mit NV-MOSFETs aufbauen zu können.

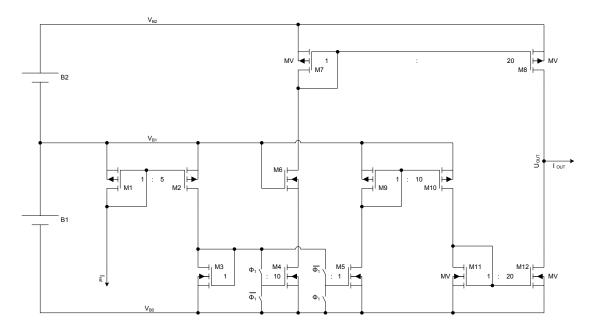

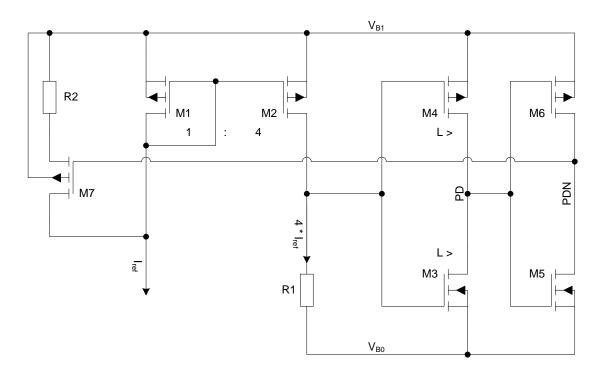

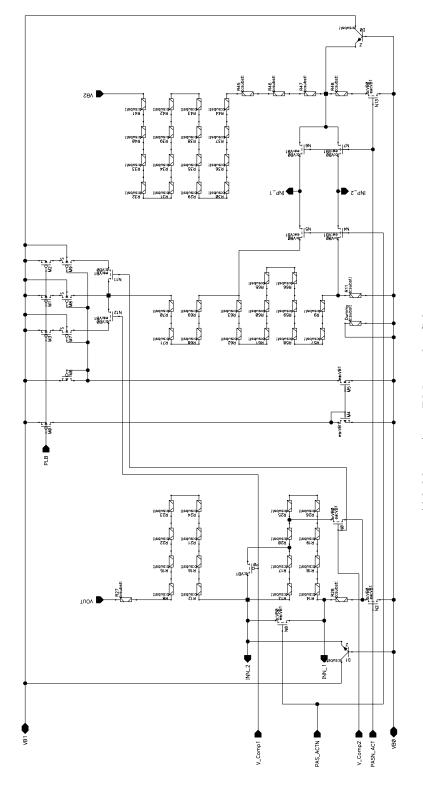

Eine weitere Schaltung zur Vergrößerung des Referenzstroms ergibt sich durch mehrere einfache Stromspiegel. Konventionelle integrierte Stromspiegel sollten aufgrund guter Matching-Eigenschaften nur bis zu einem Stromverhältnis von 1:20 gebaut werden. Um eine Vergrößerung des Referenzstroms von 1000 zu realisieren, muss der Strom also mindestens 3 mal gespiegelt werden. Abbildung 4.2 zeigt ein Prinzipschaltbild.

Der Referenzstrom wird beim ersten Stromspiegel mittels M1 und M2 um den Faktor 5 vergrößert. Die Transistoren M3, M4 und M5 bilden einen umschaltbaren Stromspiegel. Entweder wird der Strom durch die MOS-Diode M3 um den Faktor 10 vergrößert durch M4 oder unverstärkt durch M5 fließen. Für den LS Pfad existiert ein zusätzlicher Stromspiegel, welcher den Strom um den Faktor 10 vergrößert. Je nach Schalterstellung kann somit die HS Stromquelle oder die LS Stromquelle aktiviert und damit das externe Gate geladen bzw. entladen werden.

Da die Ausgangsspannung von 0 bis zu 10 V betragen kann, müssen die Ausgangstransistoren mindestens aus Mittelvolttransistoren ausgeführt werden. Aus diesem Grund wurde jeweils für den HS- und den LS-Pfad ein Mittelvolt-Stromspiegel verwendet. Das

Abbildung 4.2.: Prinzip Stromspiegelschaltung

Verhältnis der Stromspiegel ist jeweils 1:20, womit in jedem Pfad der Referenzstrom mal Faktor 1000 vergrößert am Ausgang auftritt. Vorteil dieses Schaltungsentwurfs ist, dass keine Spannungsregler benötigt werden und der Flächenbedarf der Schaltung geringer ausfällt. Negativ ist der erhöhte Strombedarf im Vergleich mit der OPV Schaltung, da besonders durch die MOS-Dioden der Ausgangsstromspiegel ein relativ hoher Strom fließt.

Die Genauigkeit der Verstärkung definiert sich vor allem durch die unterschiedlichen Drain-Source Spannungen bei unterschiedlichen Zellspannungen. Sie ist geringer einzustufen als die Genauigkeit der OPV-Schaltung.

Da die Genauigkeit des Ausgangsstroms die Funktion nur unwesentlich beeinflusst und mittels Power-Down-Schaltung die Stomaufnahme im PD-Modus minimiert werden kann, wurde das Stromspiegelkonzept weiterverfolgt.

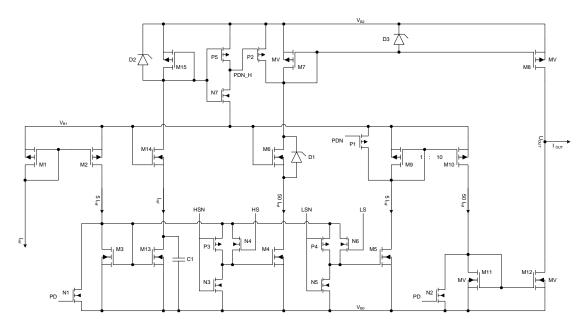

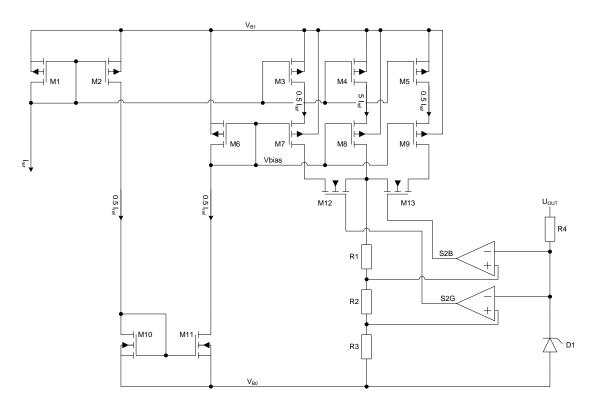

Abbildung 4.3 zeigt die finale Schaltung der Stromquellen. Die eingezeichneten Ströme beziehen sich auf den eingeschaltenen Betriebszustand des jeweiligen Strompfades. Im Gegensatz zum Prinzipschaltbild ist die Schaltung etwas aufwändiger geworden, um im PD-Betriebszustand auch wirklich alle Ströme und Transistoren abzuschalten. Die Signale PD, PDN, HSN, HS, LSN und LS werden im Kontrollblock der Ausgangsstufe erzeugt. Mittels der NMOS Transistoren N1 und N2 werden die NMOS-Stromspiegel im PD-Modus abgeschaltet. Das selbe gilt für die PMOS-Transistoren P1, P2 und die PMOS-Stromspiegel.

Abbildung 4.3.: Stromspiegelschaltung

Da sich alle Ansteuersignale zwischen  $V_{B0}$  und  $V_{B1}$  bewegen, muss für P2 ein PDN\_H Signal erzeugt werden, welches gleich mit PDN, jedoch um eine Zellspannung höher (zwischen  $V_{B1}$  und  $V_{B2}$ ), verläuft. Dieses Signal wird über die zusätzlich eingefügten Transistoren M13, M14 und M15 erzeugt. Ist die Ausgangsstufe aktiv (PD= $V_{B0}$ , PDN= $V_{B1}$ ) so fließt durch M13, bedingt durch das Größenverhältnis zu M3, der Strom  $I_{ref}$ . M14 wird benötigt um die Drain-Source Spannung von M13 auf maximal eine Zellspannung (<5 V) zu begrenzen. Die Abmessungen von M15, welcher eine MOS-Diode bildet, wurde so gewählt, dass bei einem minimalen Referenzstrom von 15 μA eine Spannung von 5 V anliegt.

Für den PMOS-Transistor gilt laut [18] die Beziehung:

$$U_{SG} = \sqrt{\frac{2 \cdot I_{ref} \cdot L}{K_P' \cdot W}} + U_{th_P} \tag{4.2}$$

Daraus wird ersichtlich, dass durch eine höhere Länge L bei kleinerer Weite W des Transistors, die Source-Gate Spannung bei einem konstanten Strom erhöht werden kann.

Damit ist sichergestellt, dass nach dem Inverter (P5, N7) das Signal PDN\_H= $V_{B2}$  ist und der Stromspiegel M7-M8 nicht abgeschaltet wird. Die Z-Diode D2 begrenzt die Gate-Source Spannung von M15 auf maximal -5,2 V, wenn ein Referenzstrom größer 15  $\mu$ A fliesen sollte. Wenn das PD-Signal high ist (PD= $V_{B1}$ ), so wird der Transistor M13 durch N1 ausgeschaltet und es fließt kein Strom durch M14 bzw. M15. Die Source-Drain

Spannung von M15 fällt unter die Thresholdspannung und der Inverter schaltet PDN\_H auf  $V_{B1}$ , womit der Stromspiegel abgeschaltet wird.

Um die richtige Stromvergrößerung der Stromspiegel für Zellspannungen bis 2,5 V zu gewährleisten, muss garantiert werden, dass alle Stromquellen-Transistoren in Sättigung betrieben werden. Das heißt, für jeden Transistor muss die Bedingung

$$U_{DS} > U_{DS_{sat}} = U_{GS} - U_{th} \tag{4.3}$$

erfüllt werden. Für den Übergang zwischen den PMOS- und NMOS Stromspiegel ergibt sich folgende Bedingung.

$$2.5 V > U_{SD_{sat_{M2}}} + U_{GS_{M3}} \tag{4.4}$$

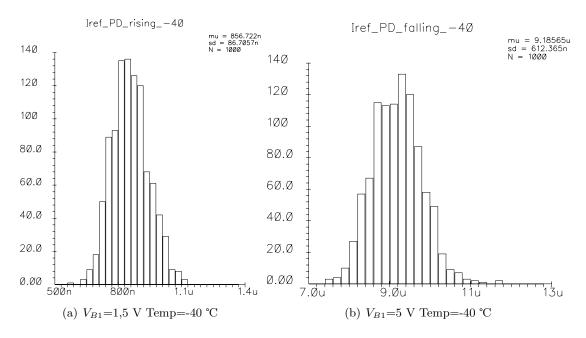

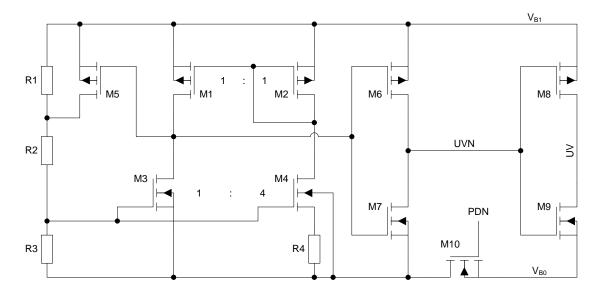

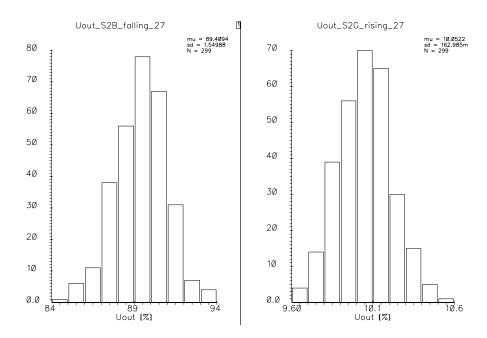

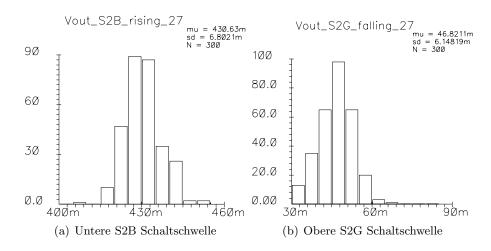

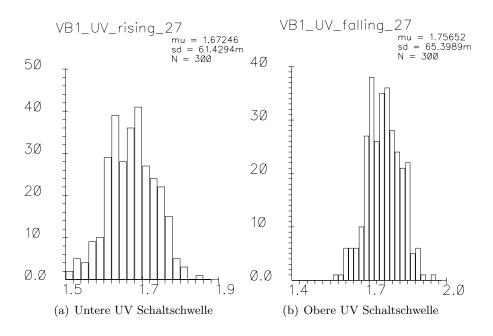

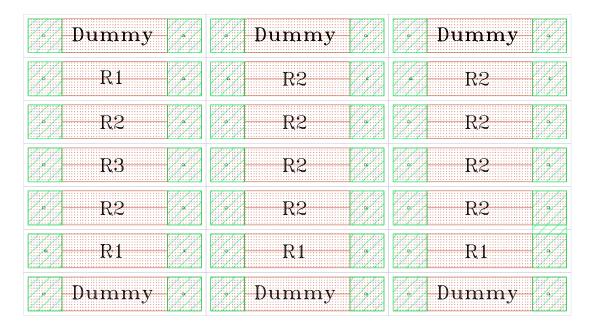

Die Berechnung der Spannungen erfolgt mit dem maximalen Referenzstrom.