Study and Implementation of an Integrated CMOS High Resolution Time-to-Digital Converter for High Energy Physics Applications

Lukas Perktold Institute of Electronics Graz University of Technology

A thesis submitted for the degree of Doctor of Engineering Sciences (Dr. techn.) 2013 July

ii

Chairperson: Ao.Univ.-Prof. Dr. Werner RENHART

1. Examiner: Univ.-Prof. Dr. Wolfgang PRIBYL

2. Examiner: Prof. dr. ir. Edoardo CHARBON

Day of the defense: 13 August 2013

Signature from head of committee:

$\mathrm{iv}$

## EIDESSTATTLICHE ERKLÄRUNG

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe.

Graz, am .....

.....(Unterschrift)

Englische Fassung:

## STATUTORY DECLARATION

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

date

(signature)

vi

#### Abstract

In high energy physics (HEP), time measurements represent an efficient way to perform particle identification and tracking. Such applications often require to implement hundreds or thousands of measurement channels. For future upgrades of the LHC experiments at CERN, time resolutions in the sub 10 ps-rms range have become necessary. Thereby, the time-to-digital converter constitutes a fundamental crucial building block within the complete measurement chain.

In the scope of this thesis a novel multichannel time-to-digital converter (TDC), featuring fine-time resolutions has been developed. Based on a two stage interpolation mechanism, employing a Delay-Locked-Loop (DLL) in the first stage and a resistive voltage division circuit in the second stage, least significant bit (LSB) sizes of 5 ps are achieved. The interpolator structure is implemented only once per application specific integrated circuit (ASIC), shared among all the channels. A novel calibration approach to efficiently calibrate out device mismatches is proposed. Time offsets due to process-voltage-temperature (PVT) variations are compensated by the feedback mechanism of the DLL. At the same time, the interpolator has been designed to be operated at lower time resolutions, offering less demanding applications to profit from improved power consumption.

A demonstrator ASIC with a total of 8 channels has been implemented in a 130 nm technology. After calibration has been applied, time-resolutions of better than 3 ps-rms have been demonstrated. Differential-non-linearity (DNL) and integral-non-linearity (INL) have been evaluated to be below +/-0.9 LSB and +/- 1.3 LSB respectively. Depending on the mode of operation, the full prototype consumes between 34 mW/channel to 42 mW/channel. Less power is consumed for lower resolution settings. The demonstrator exhibits a time shift in presence of voltage variations of -0.19 ps/mV and a temperature dependence of 0.44 ps/deg. With the measurement precision of the test setup, inter-channel crosstalk between two neighboring channels has been evaluated to be below +/- 1 LSB.

viii

#### Kurzfassung

In der Hochenergiephysik stellen Zeit-Messungen eine effiziente Möglichkeit dar, Teilchen zu identifizieren und deren Flugbahn aufzuzeichnen. Derartige Anwendungen erfordern eine Integration von oft hunderten oder tausenden Messkanälen. Für zukünftige Nachrüstungen der LHC-Experimente am CERN werden zeitliche Auflösungen von unter 10 ps-rms benötigt. Innerhalb der Messkette stellt dabei der Zeit-zu-Digital-Umsetzer einen fundamental kritischen Baustein dar.

Im Zuge dieser Dissertation wurde ein neuartiger, mehrkanaliger Zeit-zu-Digital-Umsetzer, der das Erreichen hoher zeitlicher Auflösungen ermöglicht, entwickelt. Basierend auf einem zweistufigen Interpolationsmechanismus, unter der Verwendung eines Verzögerungsregelkreises in der ersten Stufe und eines Spannungsteilers auf Widerstandsbasis in der zweiten Stufe, werden kleinste zeitliche Auflösungen von 5 ps erzielt. Eine Implementierung der Interpolationsschaltung ist nur einmal pro Microchip notwendig und wird von den am Chip integrierten Kanälen gemeinsam genutzt. Um Bauteilvariationen ausgleichen zu können, wird ein neuartiger Kalibrierungsmechanismus vorgeschlagen. Zeitliche Verzögerungen aufgrund von Prozess-, Spannungs- sowie Temperaturschwankungen werden durch die Regelschleife des Verzögerungsregelkreises ausgeglichen. Die Interpolationsschaltung wurde zugleich für den Einsatz für niedrigere zeitliche Auflösungen ausgelegt, um weniger anspruchsvollen Anwendungen einen geringeren Leistungsbedarf zu ermöglichen.

Für Demonstrationszwecke wurde ein Microchip mit insgesamt 8 Kanälen in einer 130nm-Technologie realisiert. Nach Kalibrierung der Schaltung konnten zeitliche Auflösungen von besser als 3 ps-rms erreicht werden. Der differentielle sowie der integrale Fehler der Nichtlinearitäten der Schaltung wurde zahlenmäßig auf unter +/- 0.9 LSB bzw. auf unter +/- 1.3 LSB bestimmt. Abhängig vom Betrieb der Schaltung weist der gesamte Chip einen Leistungsverbrauch zwischen 34 mW/Kanal bis 42 mW/Kanal auf. Für niedrigere zeitliche Auflösungen stellt sich ein geringerer Leistungsbedarf ein. Die aufgebaute Schaltung weist zeitliche Verschiebungen bei Spannungsschwankungen von -0.19 ps/mV und eine Temperaturabhängigkeit von 0.44 ps/deg auf. Mit der Messgenauigkeit des Versuchsaufbaus wurde die gegenseitige zeitliche Beeinflussung zweier benachbarter Kanäle auf unter +/-1 LSB bestimmt.

## Acknowledgements

I would like to thank Jorgen Christanesen for his continuous support and countless technical discussions during the design and evaluation period of this work. With his high level of expertise in the design of TDCs he has significantly contributed to the origin and quality of this work. A great thanks is also contributed to my supervisors, Wolfgang Pribyl and Kostas Kloukinas, for their continuous technical support and more noteworthy directive advice during the entire progress of this work. I would also like to thank Alexander Kluge and the design team of the NA62 Gigatracker ASIC for refining my technical skills and their encouragement during difficult periods of this work.

My gratefulness also goes to Matthew Noy as a virtuous engineer who shaped this work over endless inspiring teas and coffees. I got to know him not only as a gifted mind but also as a great friend.

Thank you!

ii

# Contents

| Li            | st of                | Figure  | es                                                      | vii  |

|---------------|----------------------|---------|---------------------------------------------------------|------|

| $\mathbf{Li}$ | st of                | Table   | S                                                       | xiii |

| 1             | Intr                 | oducti  | ion                                                     | 1    |

|               | 1.1                  | Struct  | sure of Work                                            | . 2  |

|               | 1.2                  | Summ    | nary of Contributions                                   | . 3  |

|               | 1.3                  | List of | f Publications                                          | . 4  |

| <b>2</b>      | $\operatorname{Tim}$ | ie Mea  | asurements in High-Energy-Physics and Related Fields    | 7    |

|               | 2.1                  | Field o | of applications                                         | . 8  |

|               |                      | 2.1.1   | Time Measurement Chain                                  | . 9  |

|               | 2.2                  | System  | n Level Implementation                                  | . 11 |

|               |                      | 2.2.1   | In-Pixel Architecture                                   | . 11 |

|               |                      | 2.2.2   | End-Of-Column Architecture                              | . 13 |

|               |                      | 2.2.3   | Multi-ASIC Approach                                     | . 15 |

|               |                      | 2.2.4   | Architecture Comparison                                 | . 17 |

|               | 2.3                  | Develo  | opment Trends                                           | . 19 |

|               |                      | 2.3.1   | Novel Sensors and Experiments                           | . 21 |

| 3             | The                  | e Essen | nce of Time-to-Digital Converter Design                 | 27   |

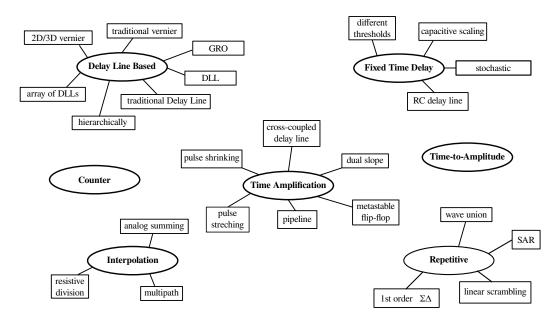

|               | 3.1                  | Time-   | to-Digital Converter Principles and their Architectures | . 27 |

|               |                      | 3.1.1   | Time Measurement Principle                              | . 28 |

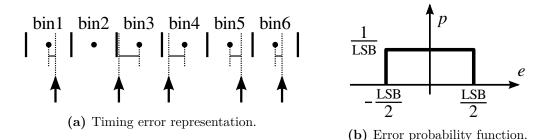

|               |                      | 3.1.2   | Quantization Noise                                      | . 29 |

|               |                      | 3.1.3   | Counter Principle                                       | . 30 |

|               |                      | 3.1.4   | Delay-Line Principle                                    | . 31 |

$\mathbf{4}$

| 3.1.5                   | Time Amplification Principle33                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1.6                   | Fixed Time Delay Principle                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1.7                   | Interpolation Principle                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.1.8                   | Time-to-Amplitude Principle    36                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.1.9                   | Repetitive Measurement Principle                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1.10                  | Event-Capture vs Clock-Capture                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.1.11                  | Multistage Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1.12                  | Event Sampling                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.1.13                  | Delay Control                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Challe                  | nges in Fine-Time Resolution TDC Design                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.2.1                   | Error Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.2.2                   | Quantization Noise                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.2.3                   | Device Mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.2.4                   | PVT Variations                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.2.5                   | Power Supply Noise                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.2.6                   | Inter-Channel Crosstalk                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.2.7                   | RC-Delays                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.2.8                   | Time Reference Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| h Dogo                  | lution, Multi-Channel Time-to-Digital Converter: A Pro-                                                                                                                                                                                                                                                                                                                                                                                                        |

| II-nesu                 | iution, Multi-Channel Inne-to-Digital Converter: A Fio-                                                                                                                                                                                                                                                                                                                                                                                                        |

| al                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| al<br>Needs             | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                         | 55 in the High-Energy Physics Community                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Needs                   | 55in the High-Energy Physics Community56Time-to-Digital Converter Requirements56                                                                                                                                                                                                                                                                                                                                                                               |

| Needs<br>4.1.1          | 55in the High-Energy Physics Community56Time-to-Digital Converter Requirements56Fine-Time Resolution Aspects58                                                                                                                                                                                                                                                                                                                                                 |

| Needs<br>4.1.1          | 55in the High-Energy Physics Community56Time-to-Digital Converter Requirements56Fine-Time Resolution Aspects584.1.2.1Quantization Noise58                                                                                                                                                                                                                                                                                                                      |

| Needs<br>4.1.1          | 55in the High-Energy Physics Community56Time-to-Digital Converter Requirements56Fine-Time Resolution Aspects584.1.2.1Quantization Noise584.1.2.2Device Mismatch58                                                                                                                                                                                                                                                                                              |

| Needs<br>4.1.1          | 55in the High-Energy Physics Community56Time-to-Digital Converter Requirements56Fine-Time Resolution Aspects584.1.2.1Quantization Noise584.1.2.2Device Mismatch584.1.2.3PVT Variations59                                                                                                                                                                                                                                                                       |

| Needs<br>4.1.1          | 55in the High-Energy Physics Community56Time-to-Digital Converter Requirements56Fine-Time Resolution Aspects584.1.2.1Quantization Noise584.1.2.2Device Mismatch584.1.2.3PVT Variations59                                                                                                                                                                                                                                                                       |

| Needs<br>4.1.1          | 55in the High-Energy Physics Community56Time-to-Digital Converter Requirements56Fine-Time Resolution Aspects584.1.2.1Quantization Noise584.1.2.2Device Mismatch584.1.2.3PVT Variations594.1.2.4Power Supply Noise604.1.2.5Inter-Channel Crosstalk61                                                                                                                                                                                                            |

| Needs<br>4.1.1          | 55in the High-Energy Physics Community56Time-to-Digital Converter Requirements56Fine-Time Resolution Aspects584.1.2.1Quantization Noise584.1.2.2Device Mismatch584.1.2.3PVT Variations594.1.2.4Power Supply Noise604.1.2.5Inter-Channel Crosstalk61                                                                                                                                                                                                            |

| Needs<br>4.1.1<br>4.1.2 | 55         in the High-Energy Physics Community       56         Time-to-Digital Converter Requirements       56         Fine-Time Resolution Aspects       58         4.1.2.1       Quantization Noise       58         4.1.2.2       Device Mismatch       58         4.1.2.3       PVT Variations       59         4.1.2.4       Power Supply Noise       60         4.1.2.5       Inter-Channel Crosstalk       61         4.1.2.6       RC-Delay       61 |

|                         | 3.1.7<br>3.1.8<br>3.1.9<br>3.1.10<br>3.1.11<br>3.1.12<br>3.1.13<br>Challe<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8                                                                                                                                                                                                                                                                                                              |

#### CONTENTS

|          |                |        | 4.1.4.1    | LSB Auto-Adjustment                                                                                                        | 65          |

|----------|----------------|--------|------------|----------------------------------------------------------------------------------------------------------------------------|-------------|

|          |                |        | 4.1.4.2    | Event Signal Characteristics                                                                                               | 66          |

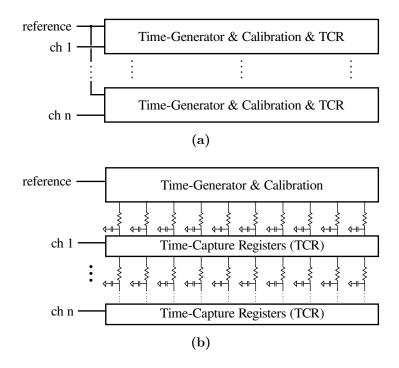

|          | 4.2            | Propo  | sed Archit | $ecture \dots \dots$ | 66          |

|          |                | 4.2.1  | Sub-Gate   | e Delay Resolutions - Concept Choice                                                                                       | 67          |

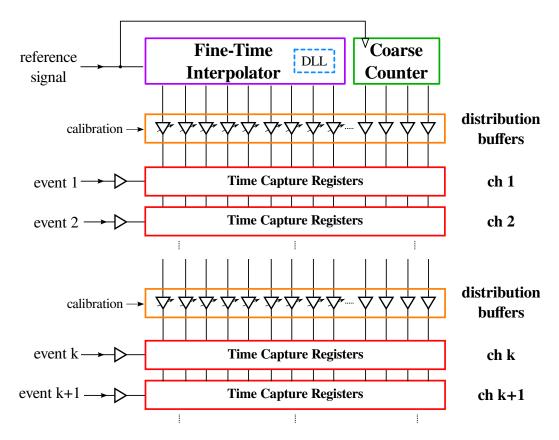

|          |                | 4.2.2  | Fine-Tin   | ne Interpolator Structure                                                                                                  | <u> 5</u> 9 |

|          | 4.3            | Archit | ectural Fe | eatures Summary                                                                                                            | 70          |

|          |                | 4.3.1  | Key Desi   | gn Aspects                                                                                                                 | 73          |

|          |                |        | 4.3.1.1    | Adjustment Feature                                                                                                         | 73          |

|          |                |        | 4.3.1.2    | Fast Delay Cell                                                                                                            | 73          |

|          |                |        | 4.3.1.3    | Fast Time-Capture Registers                                                                                                | 74          |

| <b>5</b> | Der            | nonstr | ator ASI   | С 7                                                                                                                        | 75          |

|          | 5.1            | Demo   | nstrator A | rchitecture                                                                                                                | 75          |

|          | 5.2            | Centra | al Fine-Ti | me Interpolation                                                                                                           | 76          |

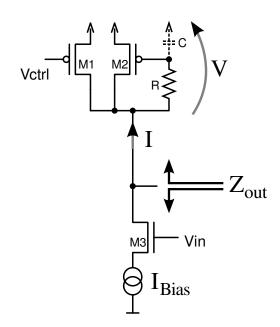

|          |                | 5.2.1  | Fast Dela  | ay Buffer                                                                                                                  | 78          |

|          |                | 5.2.2  | Resistive  | Time Interpolation                                                                                                         | 84          |

|          |                | 5.2.3  | Delay Lo   | cked Loop                                                                                                                  | 88          |

|          |                |        | 5.2.3.1    | Loop Dynamics                                                                                                              | 90          |

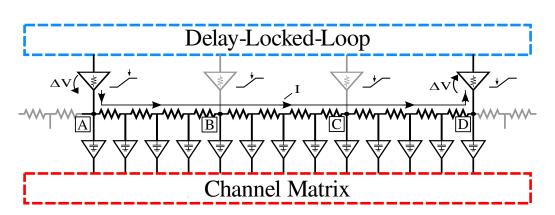

|          | 5.3            | Chanr  | nel Matrix |                                                                                                                            | 92          |

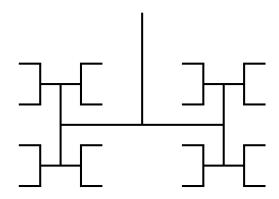

|          |                | 5.3.1  | Fine-Tin   | ne Code Buffers - Distribution Buffers                                                                                     | 93          |

|          |                | 5.3.2  | Event Ca   | apture Based Channel                                                                                                       | 95          |

|          |                |        | 5.3.2.1    | Event Capture Register                                                                                                     | 97          |

|          |                | 5.3.3  | Clock Ca   | apture Based Channel                                                                                                       | )0          |

|          |                |        | 5.3.3.1    | Clock Capture Register                                                                                                     | )1          |

|          |                | 5.3.4  | Event Di   | stribution $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $10$                                    | )4          |

|          | 5.4            | Expec  | ted Perfor | mance $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $10$                                                  | )5          |

|          |                | 5.4.1  | Timing I   | Precision $\ldots \ldots 10$    | )5          |

|          |                | 5.4.2  | Power Co   | onsumption $\ldots \ldots 10$                 | )7          |

| 6        | $\mathbf{Exp}$ | erime  | ntal Resu  | ilts 11                                                                                                                    | 1           |

|          | 6.1            | Measu  | rement Se  | tup                                                                                                                        | 11          |

|          | 6.2            | TDC    | Characteri | zation $\ldots \ldots 11$              | 12          |

|          |                | 6.2.1  | Function   | al Test                                                                                                                    | 14          |

|          |                | 6.2.2  | DLL Loc    | king Range                                                                                                                 | 17          |

|               |       | 6.2.3   | TDC Tra    | ansfer Function              | . 118 |

|---------------|-------|---------|------------|------------------------------|-------|

|               |       |         | 6.2.3.1    | Calibration                  | . 126 |

|               |       |         | 6.2.3.2    | Frequency Range              | . 128 |

|               |       |         | 6.2.3.3    | Expected RMS-Time Resolution | . 129 |

|               |       | 6.2.4   | RMS-Ti     | me Resolution                | . 130 |

|               |       | 6.2.5   | Power C    | onsumption                   | . 134 |

|               |       | 6.2.6   | Inter-Ch   | annel Crosstalk              | . 136 |

|               |       | 6.2.7   | Voltage-   | Temperature Variations       | . 137 |

| 7             | Con   | clusior | 1          |                              | 141   |

|               | 7.1   | Short . | Architect  | ure Description              | . 141 |

|               | 7.2   | Demor   | nstrator F | Performance                  | . 142 |

|               | 7.3   | Relate  | d Work .   |                              | . 144 |

|               | 7.4   | Scienti | fic Contr  | ibutions                     | . 145 |

|               | 7.5   | Future  | Develop    | ments                        | . 145 |

| Acronyms      |       |         | 148        |                              |       |

| Te            | ermin | ology   |            |                              | 151   |

| $\mathbf{Li}$ | st of | Symbo   | ols        |                              | 153   |

# List of Figures

| 2.1 | Sectional view of the CMS and ALICE detector. Available. [Online].                   |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | $eq:http://cms.web.cern.ch/ and http://aliceinfo.cern.ch/ \ $                        | 8  |

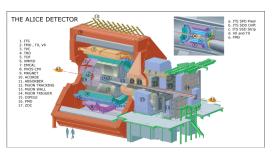

| 2.2 | Fluorescence-lifetime-imaging-microscopy (FLIM) principle                            | 9  |

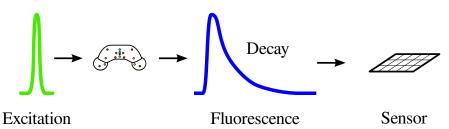

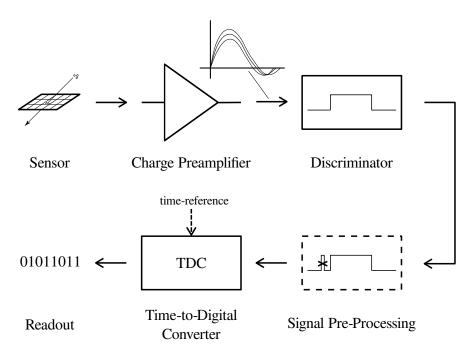

| 2.3 | Block diagram of a typical time measurement chain in HEP and related                 |    |

|     | fields.                                                                              | 10 |

| 2.4 | Timing uncertainties introduced by the different blocks of the time mea-             |    |

|     | surement chain.                                                                      | 11 |

| 2.5 | Popular implementation approaches to implement the complete time                     |    |

|     | measurement chain.                                                                   | 12 |

| 2.6 | Exemplary <i>in-pixel</i> architectures: (a) Timepix [4] (b) Delft-SPIS [5] $\ldots$ | 13 |

| 2.7 | Exemplary <i>end-of-column</i> architectures: (a) TDCpix [6] (b) EPFL-SPIS           |    |

|     | [7]                                                                                  | 14 |

| 2.8 | Exemplary <i>multi-ASIC</i> architectures: (a) and (b) muon drift tube (CMS)         |    |

|     | [8, 9] (c) time-of-flight (ALICE) [10]                                               | 16 |

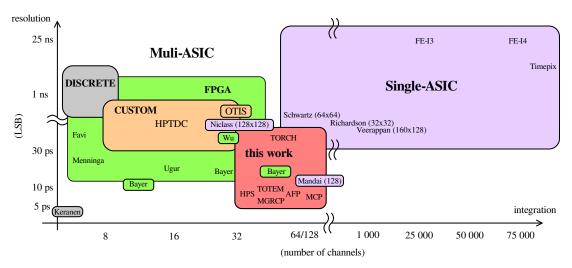

| 2.9 | Time-measurement trends observed in the HEP community                                | 19 |

| 3.1 | Classification of TDC architectures according to their underlying oper-              |    |

|     | ating principle                                                                      | 28 |

| 3.2 | Basic principle of time measurements                                                 | 29 |

| 3.3 | Illustration of the quantization noise                                               | 30 |

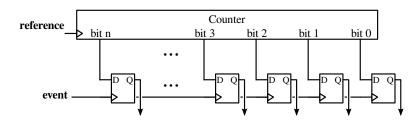

| 3.4 | Counter principle.                                                                   | 31 |

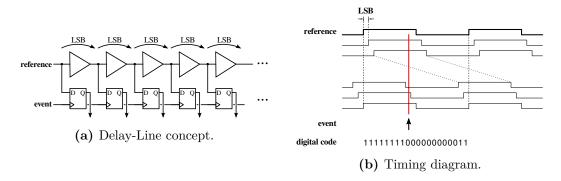

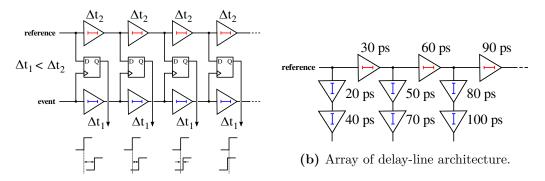

| 3.5 | Illustration of the delay-line principle                                             | 32 |

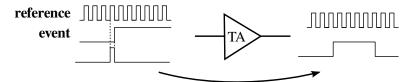

| 3.6 | Delay-line principle variants                                                        | 32 |

| 3.7 | Time-amplification principle.                                                        | 33 |

| 3.8 | Cross-coupled time-amplifier (TA)                                                    | 34 |

|     |                                                                                      |    |

## LIST OF FIGURES

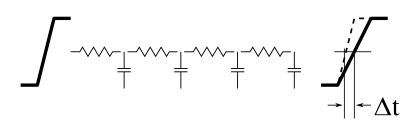

| 3.9  | Fixed time-delay principle and a capacitive scaling example              | 35 |

|------|--------------------------------------------------------------------------|----|

| 3.10 | Interpolation Principle.                                                 | 36 |

| 3.11 | Resistive voltage division example                                       | 36 |

| 3.12 | Time-to-amplitude principle.                                             | 37 |

| 3.13 | Illustration of the Wave-Union TDC approach.                             | 38 |

| 3.14 | Time-to-Digital converter based on successive-approximation              | 38 |

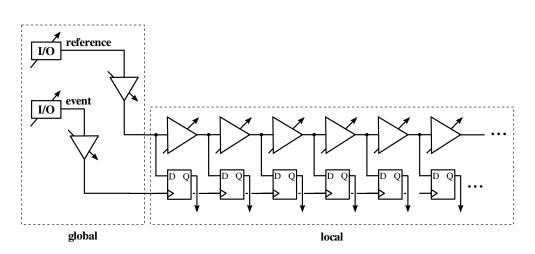

| 3.15 | Different time capturing principles                                      | 39 |

| 3.16 | Different time capturing principles based on a delay-line architecture.  | 40 |

| 3.17 | Illustration of a multistage TDC architecture                            | 41 |

| 3.18 | Illustration of a sampling TDC architecture                              | 42 |

| 3.19 | Control principles                                                       | 42 |

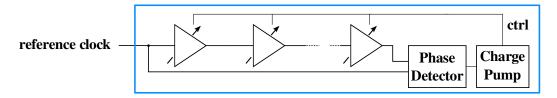

| 3.20 | A DLL block diagram.                                                     | 43 |

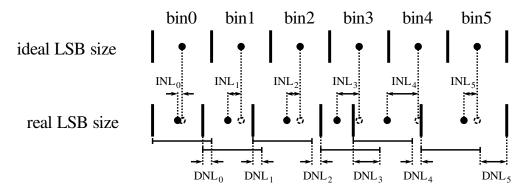

| 3.21 | Illustration of the INL and DNL error respectively                       | 45 |

| 3.22 | Illustration of local and global delay variations respectively           | 47 |

| 3.23 | Power supply noise sources                                               | 47 |

| 3.24 | Illustration of timing error introduced by power supply noise            | 48 |

| 3.25 | LSB variation for synchronous and asynchronous power supply noise        | 48 |

| 3.26 | Crosstalk induced timing variations.                                     | 49 |

| 3.27 | Time shifts introduced on a victim line due to capacitive coupling       | 50 |

| 3.28 | Delay offset shifts due to the RC-delay of a wire                        | 51 |

| 4.1  | Transition times and signal slopes using different driving configuration |    |

|      | to drive a large capacitive load                                         | 60 |

| 4.2  | Distribution of time critical signals                                    | 62 |

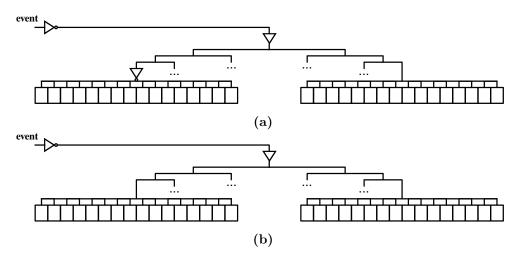

| 4.3  | Illustration of a) a local implementation approach b) a global implemen- |    |

|      | tation approach.                                                         | 63 |

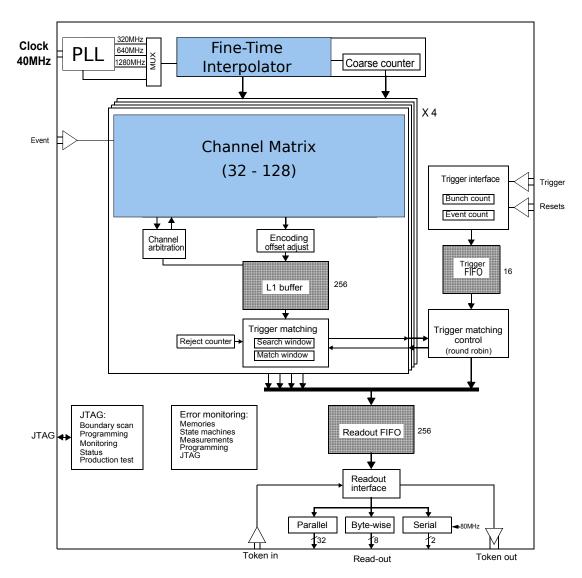

| 4.4  | Proposed multi-channel TDC architecture. [67]                            | 67 |

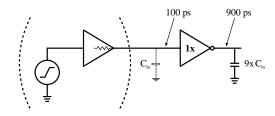

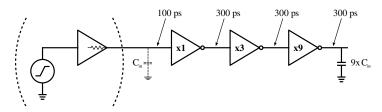

| 4.5  | A multi-stage Fine-Time Interpolator. [68]                               | 70 |

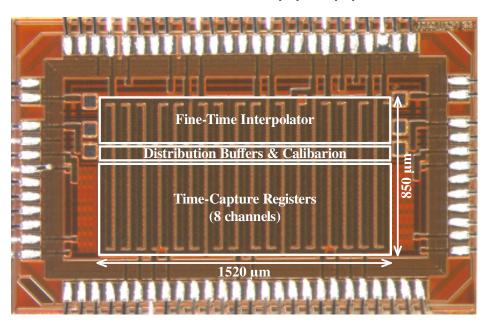

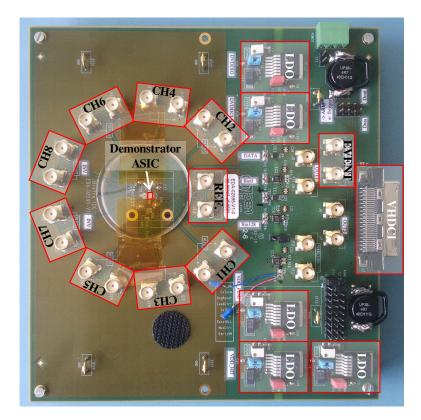

| 5.1  | Microphotograph of the demonstrator ASIC. [69]                           | 76 |

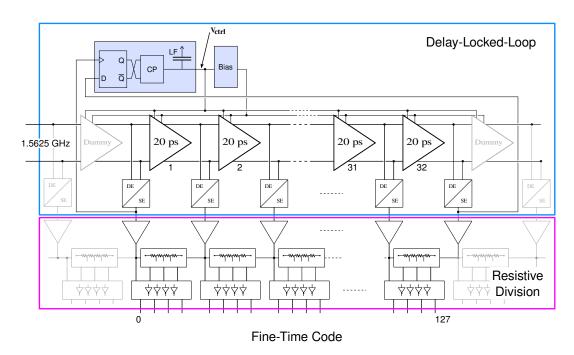

| 5.2  | Block level diagram of the fine-time generator implementation            | 77 |

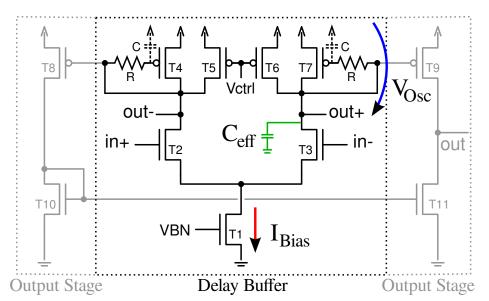

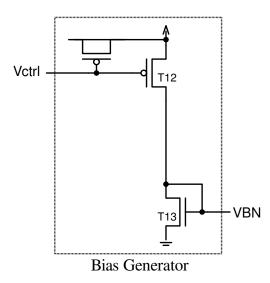

| 5.3  | High speed delay buffer implementing an additional zero in the signal    |    |

|      | path. [70]                                                               | 78 |

| 5.4  | Bias generator of the delay buffer cell. [69]                            | 79 |

## LIST OF FIGURES

| 5.5  | Half circuit equivalent of the delay buffer cell                                                     | 81  |

|------|------------------------------------------------------------------------------------------------------|-----|

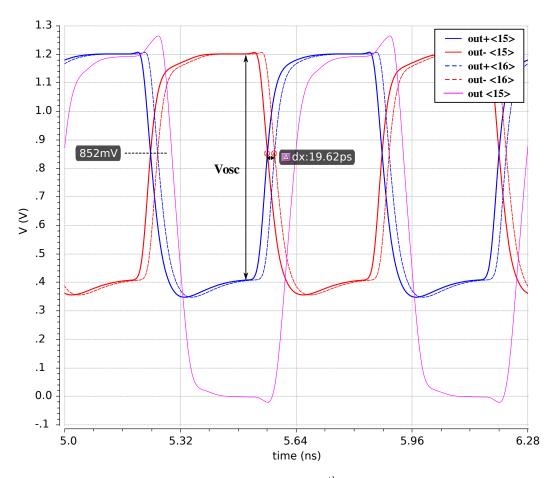

| 5.6  | Selected simulated waveforms of the delay line                                                       | 82  |

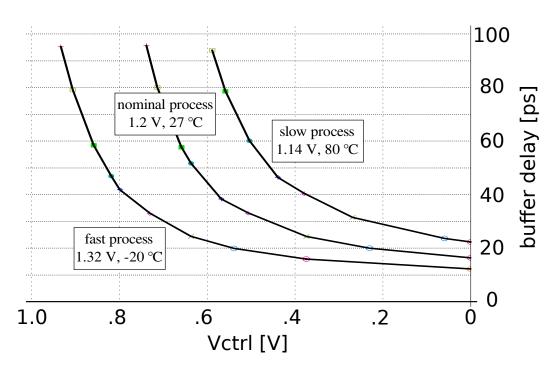

| 5.7  | Simulated buffer delay for different control voltages and operating con-                             |     |

|      | ditions. [69]                                                                                        | 83  |

| 5.8  | Resistive voltage division principle                                                                 | 84  |

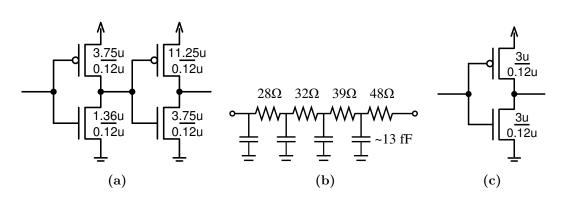

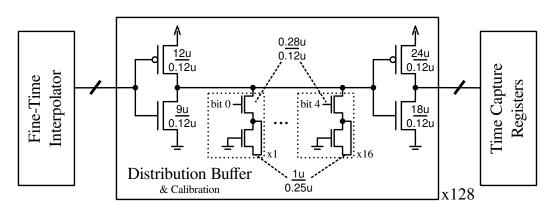

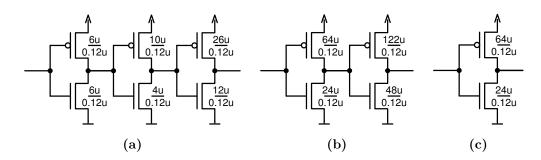

| 5.9  | Schematic diagrams and dimensions of the resistive interpolation circuit.                            | 86  |

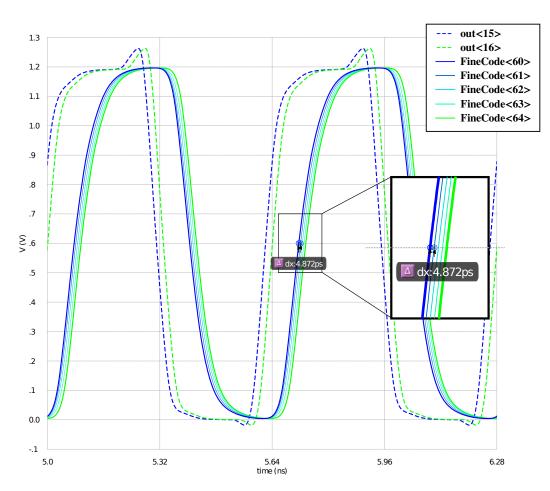

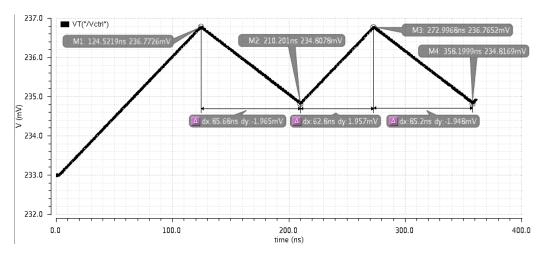

| 5.10 | Selected simulated waveforms of the interpolated fine-time code. $\ . \ . \ .$                       | 87  |

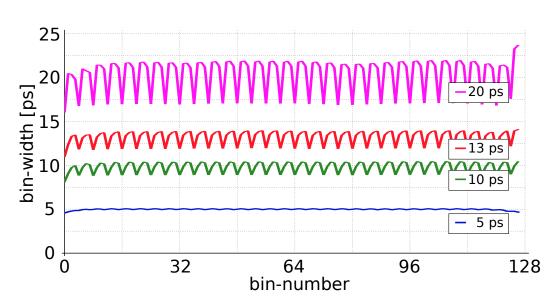

| 5.11 | Simulated LSB size for all 128 bins of the interpolator for different DLL                            |     |

|      | buffer delay settings. [69] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                    | 88  |

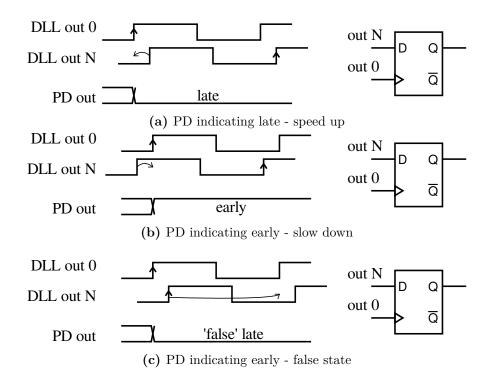

| 5.12 | Output states of a bang-bang phase detector (PD) implementation                                      | 89  |

| 5.13 | Simulated DLL control voltage for a 1562.5 MHz reference signal                                      | 91  |

| 5.14 | Schematic diagram of the distribution buffers to distribute the fine-time                            |     |

|      | code. [69]                                                                                           | 94  |

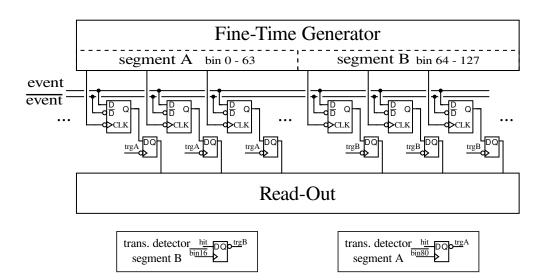

| 5.15 | Illustration of the <i>event-capture</i> implementation                                              | 95  |

| 5.16 | Schematic diagram of the time-capture registers (TCRs) for the <i>event</i>                          |     |

|      | capture based channel implementation                                                                 | 97  |

| 5.17 | Simulated waveform diagrams of the proposed $\mathit{event}\ \mathit{capture}\ \mathrm{register.}$ . | 98  |

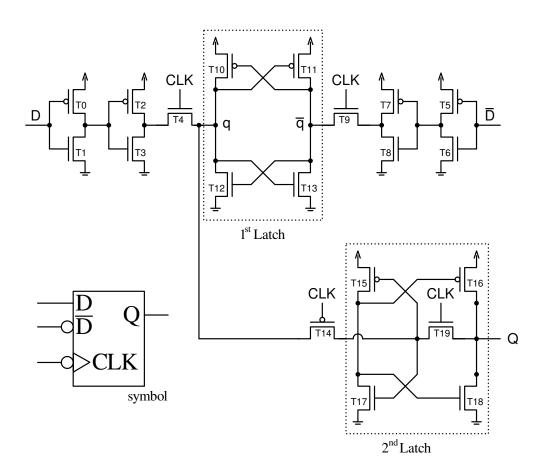

| 5.18 | Illustration of the <i>clock-capture</i> implementation. The time-of-arrival of                      |     |

|      | an event is captured by sampling the state of the fine-time interpolator.                            | 100 |

| 5.19 | Schematic diagram of the TCRs for the <i>clock capture</i> based channel                             |     |

|      | implementation. [69] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$         | 101 |

| 5.20 | Simulated waveform diagrams of the proposed $\mathit{clock}\ \mathit{capture}\ \mathrm{register.}$   | 102 |

| 5.21 | Block diagram of the event signal distribution network. $\hdots$                                     | 104 |

| 5.22 | Schematic diagrams and dimensions of the event distribution buffers                                  | 105 |

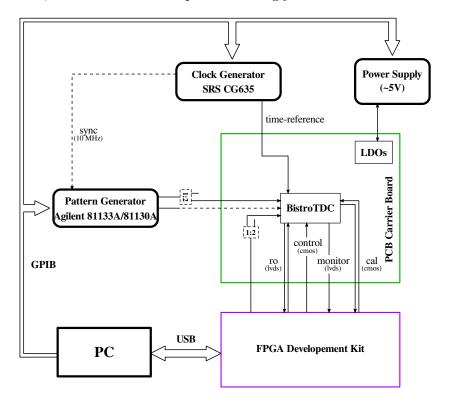

| 6.1  | Block level diagram of the test setup used to characterize the TDC                                   | 119 |

| 6.2  | Photograph of the carrier printed circuit board (PCB)                                                |     |

| 6.3  | Measured output of the PD signal in locked condition.                                                |     |

|      |                                                                                                      | 114 |

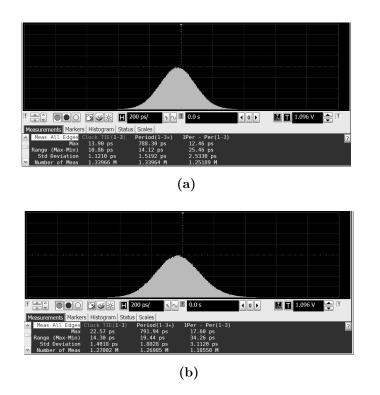

| 6.4  | Measured jitter characteristics of: (a) the input signal of the DLL (b)                              | 115 |

| 6 5  | the output signal of the DLL                                                                         | 119 |

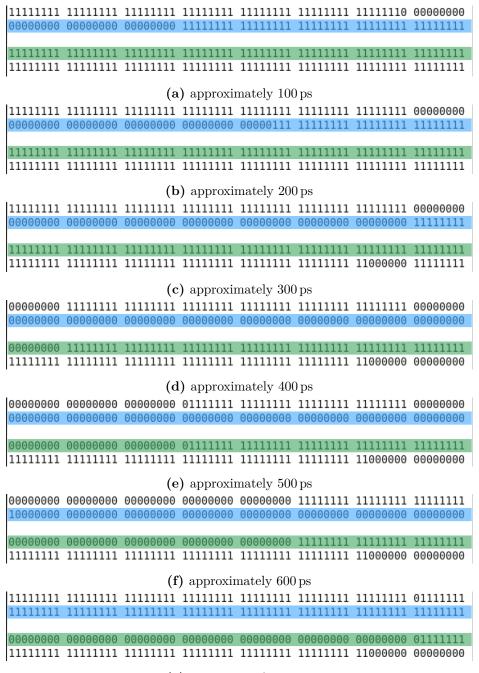

| 6.5  | <i>Event capture</i> scheme: Data patterns for different phases of the event signal                  | 116 |

|      | ыднан                                                                                                | 110 |

## LIST OF FIGURES

| 6.6  | $Clock \ capture \ scheme:$ Data patterns for different phases of the event                                    |     |

|------|----------------------------------------------------------------------------------------------------------------|-----|

|      | signal                                                                                                         | 117 |

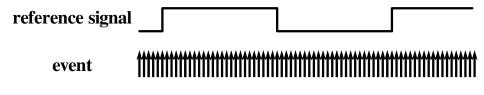

| 6.7  | Functional diagram of a code-density-test.                                                                     | 118 |

| 6.8  | Histogram of the event phase with respect to the reference signal's phase                                      |     |

|      | for a 1.28 GHz reference signal.                                                                               | 119 |

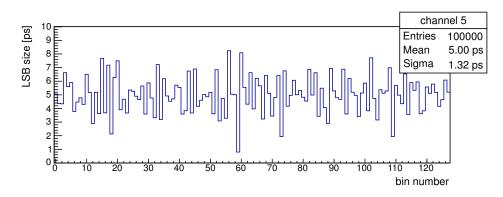

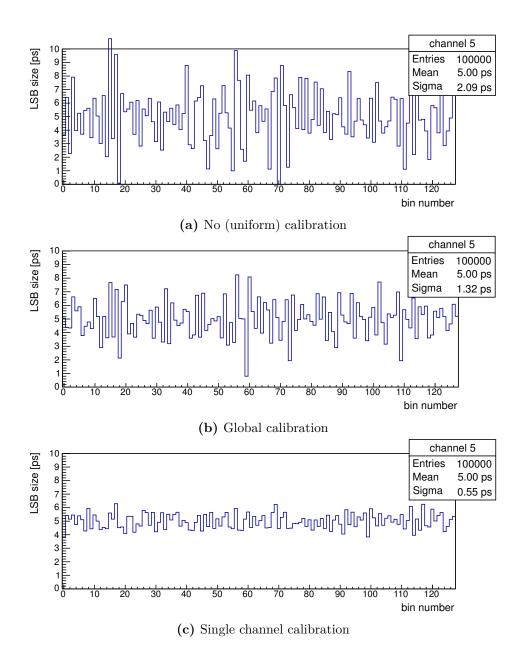

| 6.9  | Measured LSB size of channel 5 for all 128 bins after global calibration.                                      | 119 |

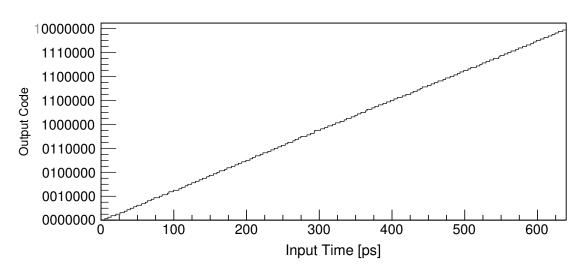

| 6.10 | Reconstructed input output transfer-function of channel 5                                                      | 120 |

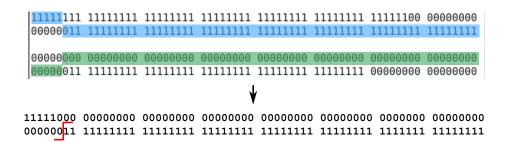

| 6.11 | Reconstruction of the data word of channel pair 1 & 2 with a virtual                                           |     |

|      | shift of 5 bins, to correct for timing offset shifts.                                                          | 121 |

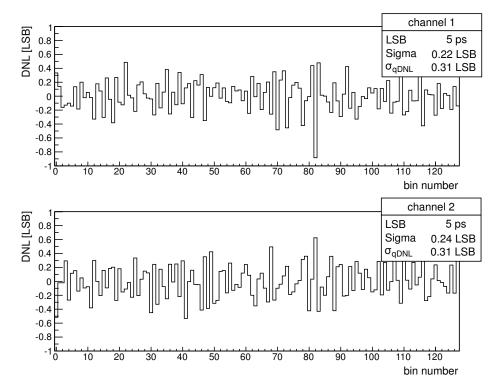

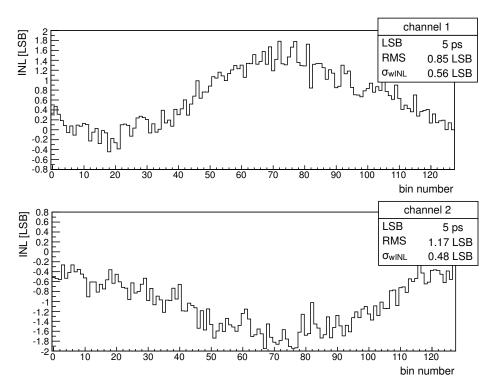

| 6.12 | Channel 1 and 2: Measured DNL of all 128 bins after global calibration                                         |     |

|      | for 5 ps LSB sizes.                                                                                            | 121 |

| 6.13 | Channel 1 and 2: Measured INL of all 128 bins after global calibration                                         |     |

|      | for 5 ps LSB sizes.                                                                                            | 122 |

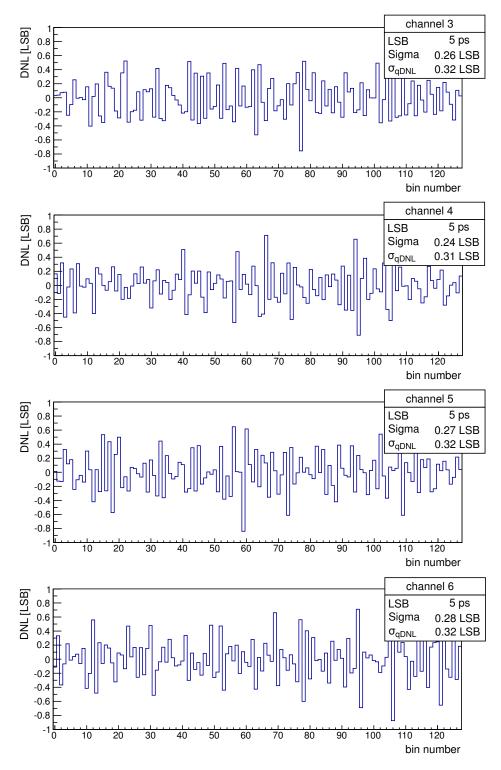

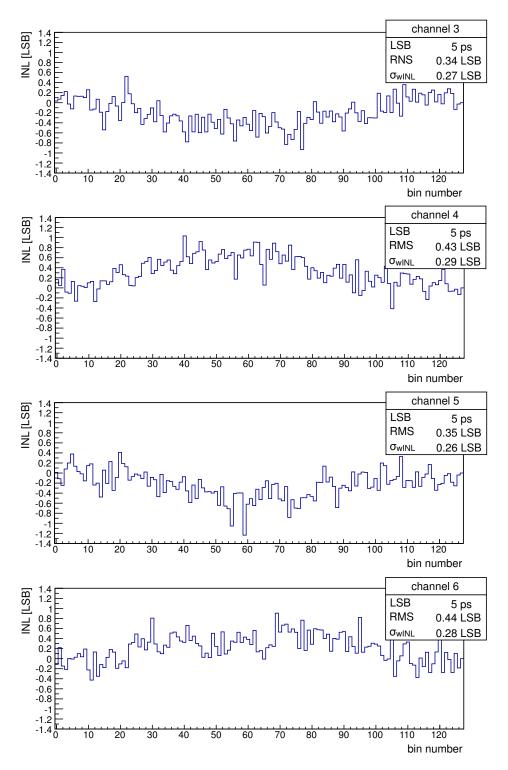

| 6.14 | Channel 3 - 6: Measured DNL of all 128 bins after global calibration for                                       |     |

|      | 5 ps LSB sizes. [76] $\ldots$                                                                                  | 123 |

| 6.15 | Channel 3 - 6: Measured INL of all 128 bins after global calibration for                                       |     |

|      | 5 ps LSB sizes. [76] $\ldots$                                                                                  | 124 |

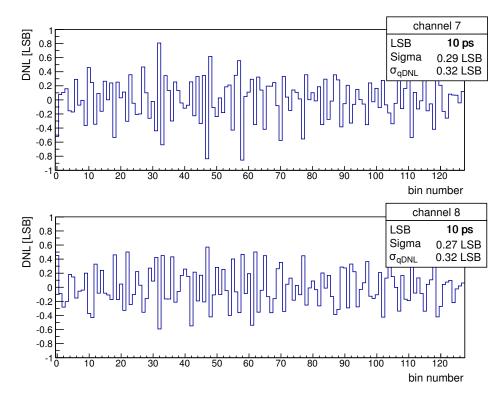

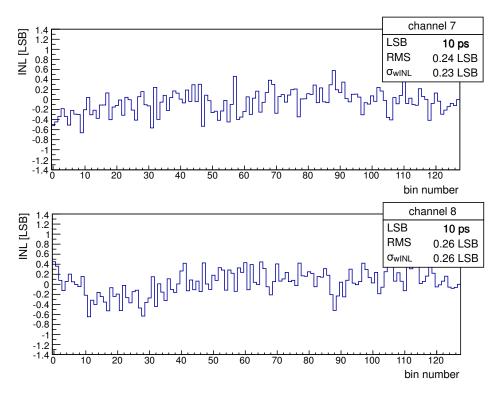

| 6.16 | Channel 7 and 8: Measured DNL of all 128 bins after global calibration                                         |     |

|      | for 10 ps LSB sizes. $\ldots$ | 125 |

| 6.17 | Channel 7 and 8: Measured INL of all 128 bins after global calibration                                         |     |

|      | for 10 ps LSB sizes. $\ldots$ | 126 |

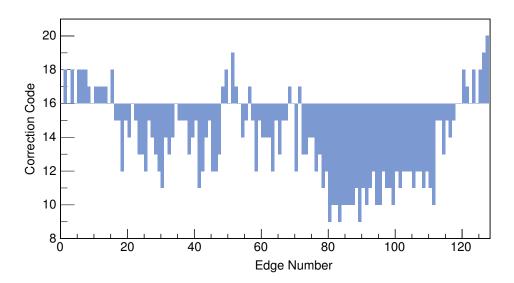

| 6.18 | Calibration vector derived from the cumulative INL error of channel 3 to $6.2$                                 | 127 |

| 6.19 | Measured LSB size of channel 5 for different calibration settings $\mathbbm{R}$                                | 128 |

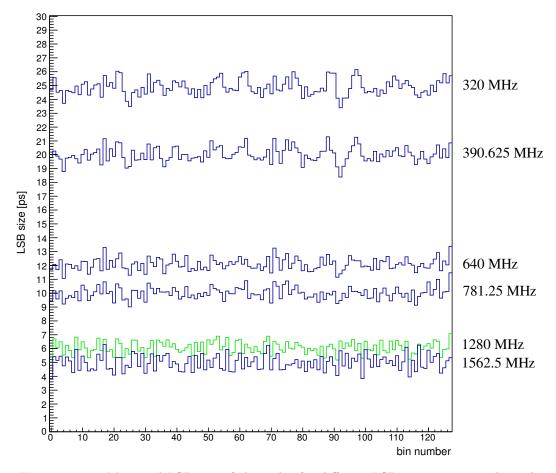

| 6.20 | Measured LSB size of channel 5 for different LSB size settings                                                 | 129 |

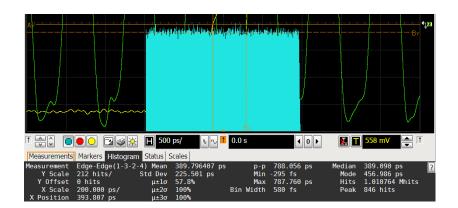

| 6.21 | Functional diagram to measure the rms-time resolution of the TDC                                               | 131 |

| 6.22 | Measured time difference of a 4 inch wire delay applied between channel                                        |     |

|      | 5 and 6                                                                                                        | 132 |

| 6.23 | Measured wire delay difference of channel pair 5 $\&$ 6 for different wire                                     |     |

|      | delays. [76]                                                                                                   | 132 |

| 6.24 | Measured power consumption of the demonstrator chip for different ref-                                         |     |

|      | erence clock frequencies when supplied with $1.3 \mathrm{V}.$                                                  | 135 |

| 6.25 | Functional diagram to measure inter-channel crosstalk between two ad-                                          |     |

|      | jacent channels                                                                                                | 136 |

| 6.26 | Measured inter-channel crosstalk of channel pair 5 and 6. $\ldots$    | 137 |

|------|-----------------------------------------------------------------------|-----|

| 6.27 | Functional diagram to measure voltage and temperature sensitivity of  |     |

|      | the TDC                                                               | 137 |

| 6.28 | Measured delay variations of channel pair 5 $\&$ 6 due to voltage and |     |

|      | temperature shifts. [76]                                              | 138 |

| 7.1  | Architectural view of a prospective full TDC ASIC. [81]               | 146 |

# List of Tables

| 2.1  | Summary of representative implementations of <i>in-pixel</i> , <i>end-of-column</i>          |     |

|------|----------------------------------------------------------------------------------------------|-----|

|      | and <i>multi-ASIC</i> architectures                                                          | 17  |

| 2.2  | Tendency of the number of TDC channels, the LSB size and the power                           |     |

|      | efficiency of different implementation approaches                                            | 18  |

| 2.3  | Timing performance of state of the art sensor designs                                        | 21  |

| 2.4  | Requirements of future experiments set on the TDC                                            | 22  |

| 3.1  | Common error sources in TDC design                                                           | 44  |

| 4.1  | Summary of <i>fine-time interpolator</i> concepts                                            | 68  |

| 5.1  | Device dimensions of the circuit shown in figure 5.3 and 5.4 respectively.                   | 80  |

| 5.2  | Charge-pump (CP) current for different CP current settings                                   | 90  |

| 5.3  | Nominal DLL parameters with the DLL operated at 1562.5 MHz                                   | 91  |

| 5.4  | Different channel configurations implemented by the demonstrator                             | 92  |

| 5.5  | Summary of the estimated input capacitances for the different time cap-                      |     |

|      | turing register (TCR) types                                                                  | 93  |

| 5.6  | Device dimensions of the <i>event capture</i> TCR                                            | 99  |

| 5.7  | Current consumption of the proposed <i>event capture</i> register                            | 99  |

| 5.8  | Parasitic input capacitance of the proposed <i>event capture</i> register                    | 99  |

| 5.9  | Device dimensions of a conventional flip-flop used as a <i>clock capture</i>                 |     |

|      | register                                                                                     | 102 |

| 5.10 | Current consumption of a conventional flip-flop used as a $\mathit{clock}\ \mathit{capture}$ |     |

|      | register                                                                                     | 103 |

| 5.11 | Parasitic input capacitance of the conventional flip-flop used as a $\mathit{clock}$         |     |

|      | capture register                                                                             | 103 |

## LIST OF TABLES

| 5.12 | Estimated parasitic capacitance of the TCRs to which the event signal                                                  |

|------|------------------------------------------------------------------------------------------------------------------------|

|      | needs to connected                                                                                                     |

| 5.13 | Estimated timing performance of the different channel configurations. $% \left( {{{\bf{n}}_{{\rm{m}}}}} \right)$ . 106 |

| 5.14 | Power consumption estimates of the respective blocks of the demonstrator.107                                           |

| 5.15 | Estimated parasitic load and power contribution of each channel config-                                                |

|      | uration                                                                                                                |

| 6.1  | Expected rms-time resolution of the demonstrator                                                                       |

| 6.2  | Measured rms-time resolution of channel pair 5 & 6 for different wire                                                  |

|      | delay settings                                                                                                         |

| 6.3  | Measured rms-time resolution of different channels and LSB size settings. $133$                                        |

| 6.4  | Measured power consumption of respective blocks of the demonstrator                                                    |

|      | supplied with $1.3 \text{ V}$                                                                                          |

| 7.1  | Performance summary of the demonstrator                                                                                |

| 7.2  | Performance comparison of different channel configurations                                                             |

| 7.3  | Comparison with related TDC designs reported in literature 144                                                         |

# 1

# Introduction

Very fine time resolution measurements are getting an ever increasing attention in the high energy physics (HEP) community. Many physical quantities like crossing time or energy of a particle can be conducted based on time measurements. Only, recently novel sensor designs have demonstrated to achieve time resolutions in the sub-10 ps-rms domain. Thereby, the quality of the measurement depends to a great extend on the timing precision of the time-to-digital converter (TDC). To allow novel experiments to profit form the improved detector capabilities, a new time-to-digital converter reaching far into the sub-10 ps-rms domain is required.

Time measurements in this resolution domain are challenging and rely on very high performance electronics. A new multichannel, fine-time resolution time-to-digital converter targeted to full-fill the requirements of upcoming HEP detectors like the ATLAS AFP, CMS HPS or LHCb TORCH and many other HEP R&D programs is demanded. For such a development, resources from different experiments need to be combined, requiring a high degree of flexibility of the design. In the HEP community, often, large systems with hundreds or thousands of channels distributed over a large area are needed, putting special requirements on the design and architecture of the TDC. In this work a TDC implementation targeted to full-fill the stringent requirements of novel HEP experiments is developed.

#### 1. INTRODUCTION

#### 1.1 Structure of Work

This work will discuss the specialties in TDC design in the HEP community and will develop a TDC architecture capable of achieving sub 10 ps-rms timing precisions for highly integrated designs.

In the first part of the work (Chapter 2), after a short introduction to the field of application, a complete picture of the time measurement chain in the HEP community is presented and different implementation approaches are discussed. The chapter will close with a study of the development trends observed in the field and outline the major requirements set by upcoming developments.

An extensive literature study is presented in Chapter 3. Different concepts to implement time-to-digital converters are presented and described. Later, in the same chapter, challenges and difficulties needed to be faced in the development of a fine-time resolution TDC are discussed and formally formulated.

In Chapter 4 the requirements of a novel multichannel TDC with fine time resolutions are described and illuminated. The difficulties and challenges identified in the previous chapter as well as important system level characteristics, found in the HEP community, are analyzed. Based on the foregoing discussed, a TDC architecture targeted to full-fill the requirements of the next generation physics experiments is presented. The chapter closes with a short summary of the important features of the proposed architecture.

To demonstrate the feasibility and performance of the proposed architecture, a demonstrator application specific integrated circuit (ASIC) has been designed and constructed. In Chapter 5 its transistor level implementation is developed. The central fine-time interpolator together with a total of 8 channels have been implemented. Based on simulation results, the expected performance of the demonstrator is analyzed.

Measurement results of the demonstrator are presented in Chapter 6. Testing procedures are detailed as well as the obtained results reported and compared to simulation. Most importantly, the linearity, the single-shot time resolution as well as the TDCs power consumption have been extracted. Inter-channel crosstalk as well as voltage and temperature variations of the design have also been investigated.

Chapter 7 concludes the work presented in this thesis. After a short summary of the implemented architecture, the achieved results of the demonstrator are summarized and discussed. Next, a comparison to similar work is presented and worth mentioning contributions made to the scientific community are listed. The chapter closes with a short outlook of a prospective full TDC development.

## **1.2 Summary of Contributions**

In the course of the implementation of a fine-time resolution TDC, following worthmentioning contributions have been made:

- Silicon implementation of a high-time resolution ASIC to demonstrate timeresolutions of better than 5 ps-rms. The prototype implements a total of 8 channels with different configurations.

- Study and implementation of a fast delay-cell. The cell is based on a Maneatis delay cell employing a higher current density load together with a additional zero in its signal path.

- Study and implementation of a resistive division interpolation concept. The interpolator has been designed and evaluated to be operated with different reference signal frequencies. An on-chip regulation circuit is implemented to auto-adjust the least-significant bit (LSB) size of the interpolator in presence of process-voltage-temperature (PVT) variations.

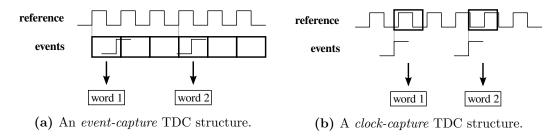

- Study and implementation of a so called *clock capture* and *event capture* based TDC architecture. The performance of both concepts has empirically been evaluated and compared to each other.

- Study and implementation of two different flip-flop types to investigate and compare effects on device mismatch and power consumption.

In the course of the implementation of the TDCpix readout ASIC for the Gigatracker station of the NA62 experiment, currently under development at CERN, following worth-mentioning contributions have been made:

• Study and evaluation of an existing 100 ps LSB size TDC to identify the shortcomings of the TDCpix prototype.

#### 1. INTRODUCTION

- Study and implementation of a revised delay-locked-loop (DLL) to be used in a DLL based TDC with 100 ps LSB size.

- Support of the integration of a DLL based TDC in the final version of the TDCpix ASIC.

## **1.3** List of Publications

This sections lists the publications made in the coarse of the presented work and details my personal contribution to them. Newest on top.

[1] To be published in the proceedings of International Instrumentation and Measurement Technology Conference, 2013 (I2MTC)

**Title:** A high time-resolution (< 3 ps-rms) Time-to-Digital Converter for Highly Integrated Designs

Authors: L. Perktold and J. Christiansen

**Contribution:** The proposed architecture, the designed circuits as well as measurement results of demonstrator are reported in this publication. This represents a selection of the work presented in Chapter 4, 5 and 6. The work reported in this paper has been designed and evaluated all by myself in the scope of my PhD thesis. The co-author contributed with valuable discussions to the work.

[2] Proceedings of Ph.D. Research in Microelectronics and Electronics, 2012 (PRIME).Title: A Flexible 5 ps Bin-Width Timing Core for Next Generation High-Energy-Physics Time-to-Digital Converter Applications

Authors: <u>L. Perktold</u> and J. Christiansen

**Contribution**: The fine-time interpolator structure, its transistor level implementation as well as simulation results are presented. This represents a fraction of the work, mainly presented in Chapter 5. The work reported in this paper has been designed and evaluated by myself in the scope of this thesis. The co-author contributed with valuable discussions to the work.

[3] Journal of Instrumentation, Volume 7, January 2012. Proceedings of Topical Workshop on Electronics for Particle Physics, 2011 (TWEPP).

**Title**: A 9-Channel, 100 ps LSB Time-to-Digital Converter for the NA62 Gigatracker Readout ASIC (TDCpix)

Authors: <u>L. Perktold</u>, G. Aglieri Rinella, E. Martin, M. Noy, A. Kluge, K. Kloukinas, J. Kaplon, P. Jarron, M. Morel and M. Fiorini

**Contributions**: The implementation of a DLL based TDC for the Gigatracker station readout chip, named TDCpix, of the NA62 experiment is presented. My responsibilities included the design and integration of a DLL for the fine-time resolution block. The implementation of this design is a good example of a monolithic end-of-column architecture as detailed in Chapter 2. The co-authors contributed with technical discussions to the work and have given valuable input on the schematic design and layout of the DLL.

#### **References Chapter 1**

- L. Perktold and J. Christiansen, "A high time-resolution (< 3 ps-rms) time-todigital converter for highly integrated designs," in *Instrumentation and Measurement Technology Conference (I2MTC), 2013 IEEE International,* 2013.

- [2] <u>L. Perktold</u> and J. Christiansen, "A flexible 5 ps bin-width timing core for next generation high-energy-physics time-to-digital converter applications," in *Ph.D. Re*search in Microelectronics and Electronics (PRIME), 2012 8th Conference on, 2012, pp. 1–4.

- [3] <u>L. Perktold</u>, G. A. Rinella, E. Martin, M. Noy, A. Kluge, K. Kloukinas, J. Kaplon, P. Jarron, M. Morel, and M. Fiorini, "A 9-channel, 100 ps lsb time-to-digital converter for the NA62 gigatracker readout ASIC (TDCpix)," *Journal of Instrumentation*, vol. 7, no. 01, p. C01065, 2012. [Online]. Available: http://stacks.iop.org/1748-0221/7/i=01/a=C01065

## 1. INTRODUCTION

# $\mathbf{2}$

# Time Measurements in High-Energy-Physics and Related Fields

In high energy physics (HEP) experiments and other closely related fields, e.g. positron emission tomography (PET) or fluorescence lifetime imaging microscopy (FLIM) to mention just a few, it is crucial to measure characteristics of physical particles crossing a detector. Quantities like position, crossing time or energy of a particle need to be measured, sometimes with very high precision. Whereas the position of the crossing point can be resolved by segmenting the sensor into smaller areas, crossing time as well as energy are most often directly derived by time measurements. This makes time measurements crucially important in the HEP community as well as in many other fields.

In this chapter the focus is set on time measurements in the HEP community and related fields. First, a short overview of the fields of application and the basic concepts to perform time measurements is given. Later on, different implementation approaches are presented, discussed and compared to each other. At the end, the trends observed in the community are illuminated and the need of a fine-time resolution time-to-digital converter (TDC) development is identified. The subsequent chapter then describes the difficulties experienced in fine time-resolution measurements and discusses potential solutions.

#### 2.1 Field of applications

Applications like HEP experiments, PET or FILM use the interaction of a particle like a photon to deduct its characteristics or timing information. Often such applications require several hundreds or thousands of channels to cover the physical area of interest. Depending on the systems level needs, the requirements set on the TDC can vary significantly with respect to power consumption, area, dynamic range or time resolution. Subsequently, exemplary, the requirements on the TDC set by FLIM and HEP experiments are very briefly illuminated.

(a) CMS detector: The CMS muon chamber spans across the whole experiment and implements approximately 200.000 channels. Due to the relatively low time resolution of the gas based drift time detector, time resolutions in the ns range are sufficient.

(b) ALICE detector: The time-of-flight detector of the ALICE experiment covers  $160 \text{ m}^2$  of area and has a diameter of 8 m. In total more than 150.000 channels are provided with time resolutions as low as 100 ps.

#### Figure 2.1

In HEP experiments most often large scale systems are constructed requiring to spread its electronics over a large area. Often in such experiments correlations between measurements across multiple measurement channels are necessary. For this purpose all the electronics are synchronized to one common time reference which is distributed to all the TDC channels to allow relate all measurements to the same time base. Time resolutions can vary widely across different detector architectures. The dynamic range of the system needs to cover at least one clock cycle of the system's time base which usually is in the range of several nanoseconds (e.g. 25 ns). In gas based tracking detectors, like the CMS muon detector as depicted in figure 2.1a, require moderate resolutions in the range of a few ns whereas in time-of-flight detectors, like in the ALICE experiment as depicted in figure 2.1b, time resolutions well below 100 ps are required.

**Figure 2.2:** FLIM principle. With a exponentially decaying function, the fluorescence dye emits a light pulse after excitation.

In FILM applications for example, as schematically shown in figure 2.2, the exponential decay of a fluorescence dye is recoded by repetitive excitation through a pulsed light source (e.g. laser). In this case large pixel arrays with fine granularity on a small physical area are implemented. For such applications, the TDC itself is often directly integrated into the pixel itself. This makes power consumption as well as the physical area consumed by the TDC crucial important on a system level for such applications. The dynamic range requirement is set by the pulse interval of the light source and can extend to several ns. Time resolutions in the order of 50 ps and less are required to reconstruct the exponential decay of the fluorescence dye with fine time granularity. To some limited extend such applications can improve time resolutions on a system level by repetitive measurements.

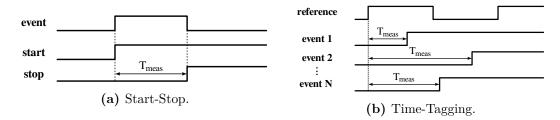

#### 2.1.1 Time Measurement Chain

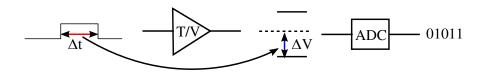

A typical time measurement chain of a single channel usually employed in HEP detector designs and related fields is shown in figure 2.3. At first, a sensor uses the physical interaction between the particle and the sensor material to generate an electrical signal. The physical quantity to be measured is the charge induced by the crossing particle in the sensor. The charge gets collected and pre-amplified to generate an analog signal. In some cases the sensor itself produces a strong enough signal avoiding the need of a pre-amplifier circuit. The shape of the induced analog signal discloses important physical characteristics of the particle. Some of the information contained in the analog waveform can be extracted by discriminating the signal in amplitude. This generates

# 2. TIME MEASUREMENTS IN HIGH-ENERGY-PHYSICS AND RELATED FIELDS

Figure 2.3: Block diagram of a typical time measurement chain in HEP and related fields.

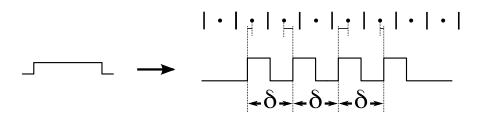

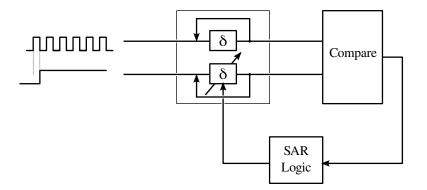

a pulse signal, still continuous in time, that can then be digitized using a TDC. The discrimination in amplitude represents a reduction of information greatly simplifying the complexity of the measurement chain. By measuring both the rising as well as the falling edge of the pulse, the energy of the particle as well as its time-of-arrival can be measured. As the signal induced in the sensor is not of perfect nature a signal preprocessing stage might be added to suppress glitches and/or provide a minimum pulse duration width and gap. To be complete, at the end of the processing chain a readout circuit responsible to provide a suitable way to access and retrieve the generated data is required.

At a system level the timing uncertainties are introduced at each level of the measurement chain as visualized in figure 2.4. This is, the timing uncertainty of the sensor itself denoted as  $\sigma_{sensor}$ , the noise introduced by the charge amplifier and the discriminator denoted as  $\sigma_{pre-amp}$  and  $\sigma_{distriminator}$  respectively as well as the timing uncertainty introduced by the TDC circuit itself, denoted as  $\sigma_{TDC}$ . Also the timing uncertainty introduced by the distribution of the reference signal through the timing, trigger and control (TTC) system of the detector, denoted as  $\sigma_{TTC}$ , need to be taken into account. If all the different error sources are assumed to be uncorrelated, the

Figure 2.4: Timing uncertainties introduced by the different blocks of the time measurement chain.

system's timing performance can be written as

$$\sigma_{sys} = \sqrt{\sigma_{sensor}^2 + \sigma_{pre-amp}^2 + \sigma_{discriminator}^2 + \sigma_{TDC}^2 + \sigma_{TTC}^2}$$

#### 2.2 System Level Implementation

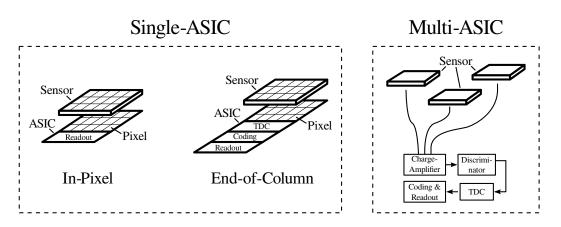

Depending on the physical construction of the sensor different implementation approaches to implement the complete measurement chain exit. They can be further grouped into *single-ASIC* and *multi-ASIC* designs. Fig. 2.5 shows the three different approaches. A *single-ASIC* approach is frequently used if high integration levels are essential as commonly the case for pixel detectors. For such an approach usually the different blocks, are directly integrated, as the name suggests, into a single ASIC only the sensor itself is often implemented as a separate module. A *single-ASIC* approach can be further divided into *in-pixel* and *end-of-column* architectures. If a high integration factor is not required a more modular approach, using multiple dedicated ASICs, can be pursued.

#### 2.2.1 In-Pixel Architecture

*In-pixel* architectures are commonly used to implement a very high number of pixels on a single chip. The electronics are either integrated in very close proximity in the sensor material itself or are integrated as a separate module which is pump bonded to the sensor's back-side. Usually, all measurement functions, including the TDC, are integrated directly into the pixel area. Only the readout block that groups all the channels into one single interface is implemented on a global scale. The sensor usually

# 2. TIME MEASUREMENTS IN HIGH-ENERGY-PHYSICS AND RELATED FIELDS

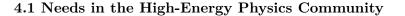

Figure 2.5: Popular implementation approaches to implement the complete time measurement chain.

is designed to provide very good spatial resolution with pixel sizes as small as a few tens or hundreds of  $\mu m^2$ . With such an approach, the area available to integrate the various electronic components is determined by the pixel size itself. Due to the limited space in each pixel, performance trade-offs need to be made.

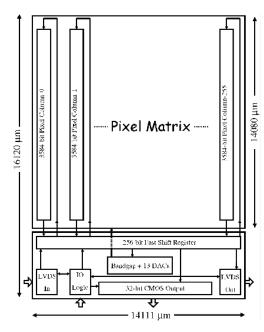

Exemplary, a block diagram of the Timepix readout chip developed at CERN [4] as well as a single photon image sensor developed at Delft university (here referred to as Delft-SPIS) [5] is shown in figure 2.6a and figure 2.6b respectively. Both implementations represent well suited examples of an *in-pixel* architecture. In the case of the Timepix chip, the sensor is to be bump-bonded to the readout chip whereas the Delt-SPIS chip employs a technology to allow to fully integrate the sensor directly into the pixel. As indicated by the dimension, only little area is occupied by the circuitry placed outside of the pixel matrix. The Timepix chip integrates a total of 65 536 pixels employing a pixel size of  $55\,\mu\mathrm{m\,x}\,55\,\mu\mathrm{m}$  whereas the Delft-SPIS integrates a total of 20 480 pixels using  $50 \,\mu \text{m} \ge 50 \,\mu \text{m}$  sized pixels. Different pixel functionality as well as different time resolution requirements exits for both solutions. For the Timepix implementation a binary counter is employed to perform the function of the TDC. In that case, the reported minimum least significant bit (LSB) achieved is 25 ns per LSB. The Delft-SPIS uses a more sophisticated approach employing a gated ring oscillator in the pixel to perform the fine interpolation. This approach allows to achieve LSB sizes as small as 55 ps. A global phase-locked-loop (PLL) is employed to overcome the intrinsic dynamic range limitation of the pixel. The power consumption of the full chip in case

of the Timepix chip is reported to be equivalent to  $13.6 \,\mu\text{W/pixel}$  whereas half of the power is devoted to the analog portion of the chip. In the case of the Delft-SPIS chip the equivalent power consumption is reported to equate to  $26.9 \,\mu\text{W/pixel}$ .

(a) Timepix floorplan: on the top square there is the 256 x 256 pixel matrix, on the bottom square there is the Timepix IO periphery and DACs.

(b) Photo micrograph of the sensor chip with pixel and microlens array details in the insets. The circuit, has an area of  $11.0 \times 12.3 \text{ mm}^2$ . The pixel pitch is  $50 \,\mu\text{m}$ .

Figure 2.6: Exemplary *in-pixel* architectures: (a) Timepix [4] (b) Delft-SPIS [5]

#### 2.2.2 End-Of-Column Architecture

To overcome the performance issues experienced in *in-pixel* architectures, in *end-of-column* architectures some parts of the measurement chain are moved to the end of the pixel matrix. Analog functions up to the discriminator are normally retained in the pixel area. The TDC, the coding as well as the common readout interface can be implemented on a global scale. Through the gained space, by moving some of the functions to the end-of-column region, performance improvements can be achieved. Such an approach also gives rise to share one TDC among several pixel to increase integration ratio. Anyway, in *end-of-column* architectures the analog signals need to

### 2. TIME MEASUREMENTS IN HIGH-ENERGY-PHYSICS AND RELATED FIELDS

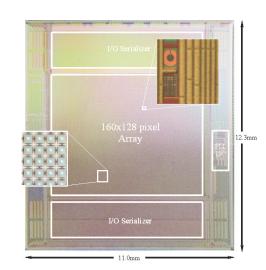

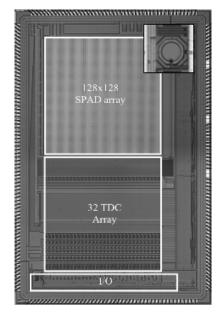

(a) TDCpix top level block arrangement. The ASIC implements 1800 pixels and consumes a total area of approximately  $12 \times 20 \text{ mm}^2$

(b) Photomicrograph of the timecorrelated single-photon counting (TC-SPC) image sensor with a pixel detail in the inset. The integrated circuit, fabricated in a 0.35  $\mu$ m CMOS technology, has a surface of 8 x 5 mm<sup>2</sup>.

Figure 2.7: Exemplary end-of-column architectures: (a) TDCpix [6] (b) EPFL-SPIS [7]

travel from the pixel all the way down to the end-of-column area. In the end-ofcolumn area a single TDC channel can be shared among several pixels. With such an architecture the integration of many channels is still feasible but the integration level is usually smaller compared to *in-pixel* architecture based designs.

An end-of-column approach for example is adopted by the TDCpix [6], a pixel readout chip currently under development at CERN, or a single photon image sensor chip developed at EPFL [7] here referred to as the EPFL-SPIS. A representative image of both implementations is shown in figure 2.7a and figure 2.7b respectively. In both cases, components placed outside the pixel matrix occupy a substantial portion of the full chip. Whereas the EPFL-SPIS implementation is supposed to be used as a single device, the TDCpix arranges all the connections on one side to allow several chips to be abutted to cover a larger area.

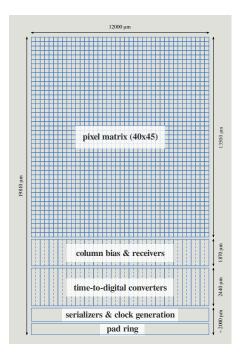

The TDCpix ASIC implements a 40 x 45 pixel matrix with  $200 \times 200 \ \mu m^2$  sized pixels.

As in the case of the Timepix chip, also for the TDCpix chip, the sensor is to be implemented by separate module. One TDC with a total of 36 channels, is implemented per double-column, 40 TDCs per chip. One TDC channel is shared among 5 pixels residing in the same column. The rising as well as the falling edge of the signals are measured by two distinct channels. To avoid signal quality degradation, on chip differential signaling is used to bring the timing critical signals to the end-of-column region. A delay-locked-loop (DLL) in conjunction with a binary counter is used to achieve LSB sizes of 97.7 ps. The power consumption of the TDC is 1.8 mW/channel.

The EPFL-SPIS chip integrates a  $128 \times 128$  large pixel array using  $25 \,\mu$ m squared pixels. The sensor in this case is integrated in the pixel itself. A total of 32 TDCs are implemented, each of the TDCs providing one channel. All TDCs share a global DLL whose time codes are distributed to the respective channels. The finest interpolation step is accomplished locally, active only on the arrival of an event. The TDC itself employs digitally calibrated delay line generating 97 ps sized LSBs. Each TDC serves four columns of the array. The power of the full chip is reported to equate to  $5.9 \,\mathrm{mW/channel}$ .

#### 2.2.3 Multi-ASIC Approach

In a *multi-ASIC* approach, the measurement functions are handled as separate blocks and are implemented at a time. A relatively small number of channels is grouped together and processed by a dedicated ASIC. Such an approach is especially attractive for detector designs that have their sensors physically far apart or for which a custom ASIC design is not feasible. Anyhow, as the critical timing signals in such an approach need to be send off chip and travel over relatively large distances, additional power needs to be invested to avoid signal integrity issues.

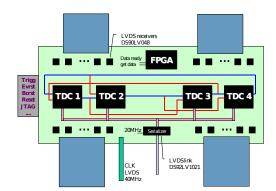

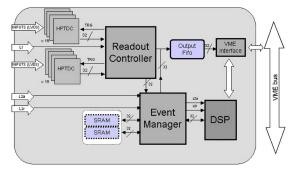

A popular implementation of such a *multi-ASIC* approach has been adopted by many different applications and experiments. To illustrate this approach the muon drift tube detector of the CMS experiment [8, 9] as well as the time-of-flight detector of the ALICE experiment [10] are to be discussed. The architecture of the module implementing the TDC function is depicted in figure 2.8a and 2.8b and figure 2.8c respectively.

In both cases the functionality of the discriminator as well as the sensor are implemented by separate modules sitting close to the sensor. Timing critical signals are

### 2. TIME MEASUREMENTS IN HIGH-ENERGY-PHYSICS AND RELATED FIELDS

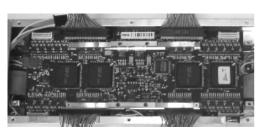

(b) Picture of a 128 channels Read-Out Board assembled on a Minicrate.

(a) Read-Out Board diagram.

(c) TDC Readout Module (TRM) conceptual design.

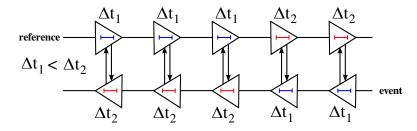

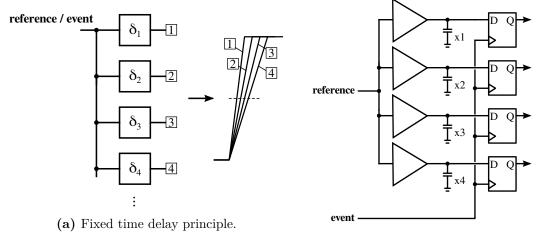

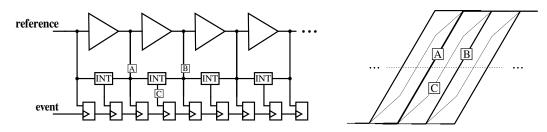

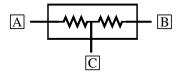

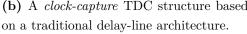

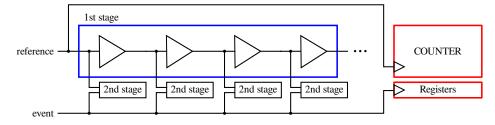

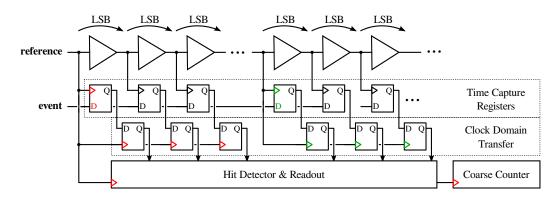

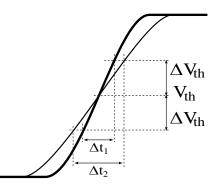

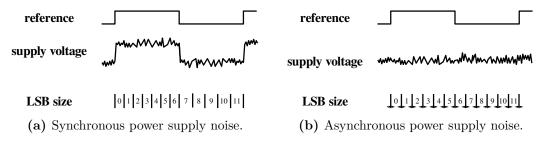

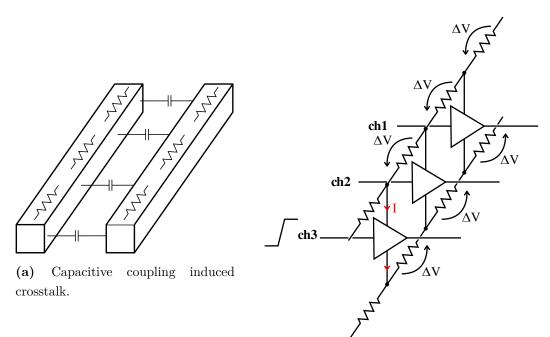

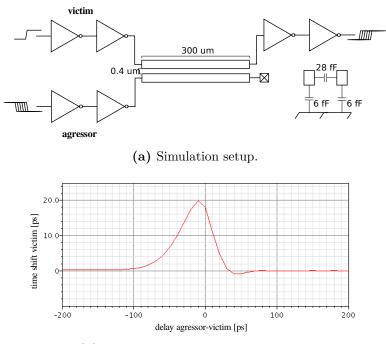

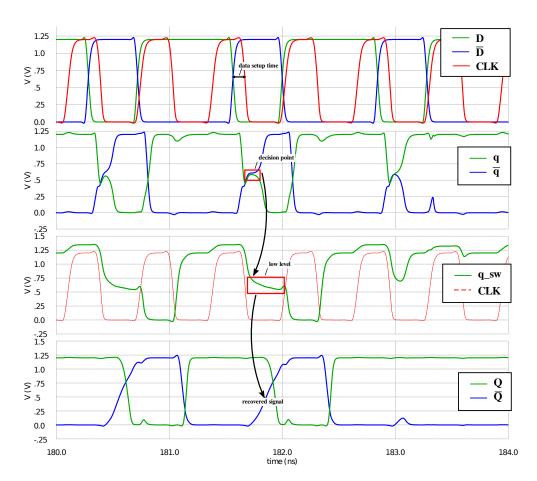

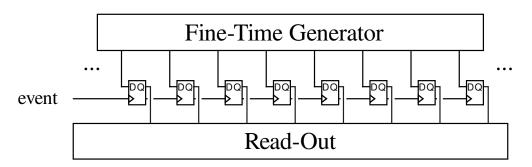

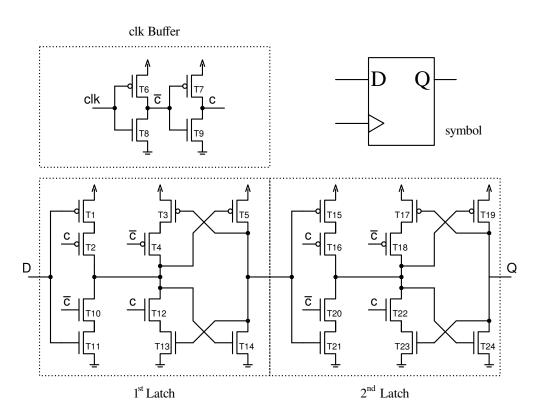

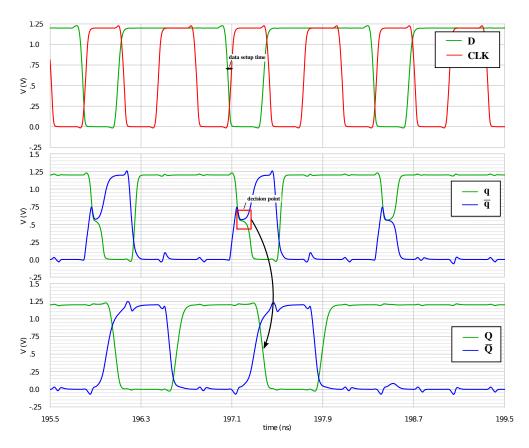

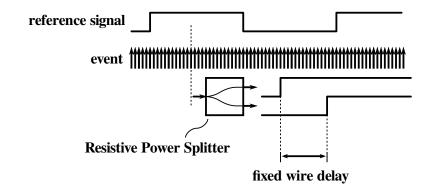

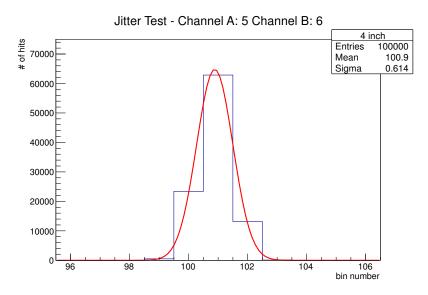

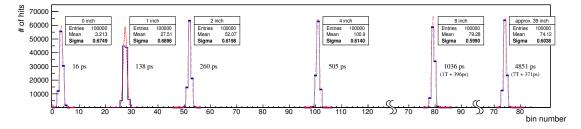

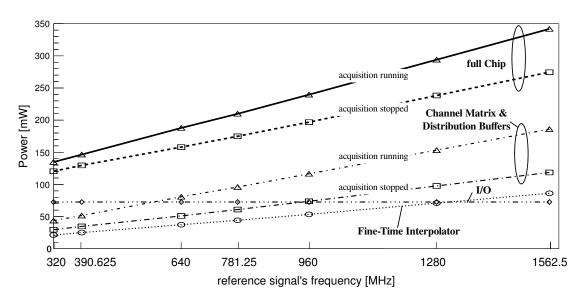

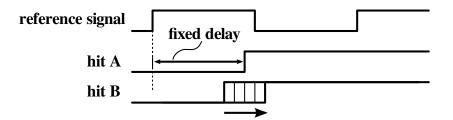

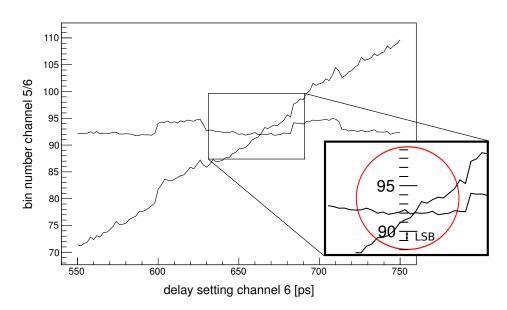

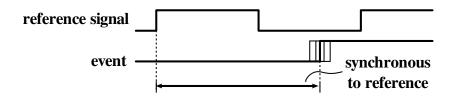

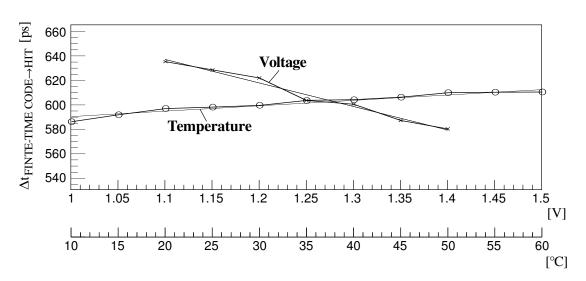

**Figure 2.8:** Exemplary *multi-ASIC* architectures: (a) and (b) muon drift tube (CMS) [8, 9] (c) time-of-flight (ALICE) [10]