Dipl.-Ing. Michael Lackner, BSc

### Hardware/Software Codesign for Secure Java Cards

### DISSERTATION

zur Erlangung des akademischen Grades

Doktor der technischen Wissenschaften

eingereicht an der

### Technischen Universität Graz

Betreuer

Em.Univ.-Prof. Dipl.-Ing. Dr.techn. Reinhold Weiß

Institut für Technische Informatik

### EIDESSTATTLICHE ERKLÄRUNG AFFIDAVIT

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe. Das in TUGRAZonline hochgeladene Textdokument ist mit der vorliegenden Dissertation identisch.

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present doctoral dissertation.

Datum / Date

Unterschrift / Signature

### Kurzfassung

Java Karten sind kleine elektronische Geräte mit stark eingeschränkten Ressourcen. Ihre Hauptaufgabe ist es sicherheitskritische Daten zu verarbeiten und zu speichern. Heutzutage werden diese Karten in verschiedenen Kontexten eingesetzt wie elektronisches Geld, Zugangskontrollen oder elektronische Reisepässe. Die Anzahl dieser Karten wird sich in naher Zukunft, wegen der wachsenden Zahl von Smartphones und mobilen drahtlos verbundenen Geräten, immer weiter erhöhen. Java Karten werden in verschiedenen sicherheitskritischen Systemen eingesetzt wie bei Nahfeldkommunikation (Near Field Communication, Abkürzung NFC) und bei Fingerabdrucksensoren. Java Karten unterstützen verschiedene kryptographische Funktionen wie Checksummenberechnung, Entschlüsselung und Verschlüsselung von Daten mithilfe von geheimen Schlüsseln. Diese Schlüssel werden sicher in der Karte gespeichert und verwaltet. Die Sicherheit der Java Karten Anwendungen werden durch das Java Karten Sandbox Modell gewährleistet. Dieses Modell gewährleistet, dass keine Java Karten Anwendung, die auf der Karte ausgeführt wird, in der Lage ist illegale Operationen auszuführen. Das Modell basiert auf der Tatsache, dass vor der Anwendungsinstallation ein einmaliger Verifikationsprozess ausgeführt wird. Diese Verifikation stellt sicher, dass die Anwendung die Java Karten Spezifikation erfüllt und keine illegalen Operationen oder Speicherzugriffe enthält. Unglücklicherweise ist es mithilfe einer Laufzeitattacke möglich das Sandbox Modell zu umgehen. Eine Laufzeitattacke ist zum Beispiel ein Beschuss mit einem Laser oder ein kurzzeitiger Spannungsabfall in der Stromversorgung.

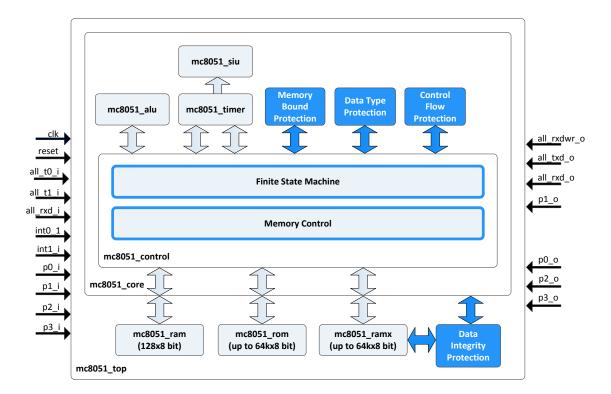

In dieser Arbeit werden neuartige Gegenmaßnahmen gegen verschiedene Attacken vorgestellt um eine zukünftig sichere Java Karte zu ermöglichen. Diese Gegenmaßnahmen werden entweder rein in Software oder mit Hardwareunterstützung ausgeführt. Neuartige digitale Schutzeinheiten werden in die Karte integriert um Speichergrenzen, Java Datentypen, Kontrollfluss und Datenintegrität während der Laufzeit zu überprüfen. Die Schutzeinheiten werden durch das Einfügen von neuen sicherheitsrelevanten Instruktionen in den Befehlssatz von zwei Java Karten Modellen angesprochen. Das erste Modell ist ein schnell ausführbares und leicht modifizierbares Systemmodell in der Hardwarebeschreibungssprache SystemC. Das zweite Modell ist ein taktgenaues Modell von Oregano Systems welches in VHDL programmiert ist. Der Prozessor der beiden Modelle ist ein 8-Bit 8051 kompatibler Prozessor. Beide Modelle werden während dieser Arbeit zur Erforschung von verschiedenen Software und Hardware Gegenmaßnahmen von Attacken eingesetzt. Die Verschiebung der Sicherheitsfunktionen von Software zur Hardware erhöht die Ausführungsgeschwindigkeit von Anwendungen auf der Karte. Die zusätzlich erforderliche digitale Logik für die neuen digitalen Schutzeinheiten bleibt relativ gering. Solch eine erhöhte Sicherheit für Java Karten wird benötigt, um zum Beispiel die sichere Installation und Ausführung von Anwendungen zu ermöglichen die durch den Kartenbenutzer installiert werden. Eine solche, vom Kartenbesitzer kontrollierte Karte, könnte ein nächstes profitables Geschäfts- und Anwendungsfeld für Java Karten sein.

### Abstract

Java Cards are small resource constrained electronic devices which are able to process and store security-critical data. Nowadays, these cards are used in various contexts such as electronic banking, access control or electronic passports. The quantity of these cards will even increase in the near future because of the growing number of smart phones and mobile wireless connected devices. These devices have various built-in security-critical chips like subscriber identification module (SIM) cards, near field communication (NFC) chips, and fingerprint sensors. The Java Cards provide different functionality like hashing, decryption and encryption of data by secret keys. These keys are securely stored on the card. The security of the Java Card applets is ensured by the Java Card sandbox model. This model guarantees that no Java Card applet, which is executed on the card, is able to perform illegal code or data accesses. The model relies on the fact that a static applet verification process is performed. This process ensures that the applet fulfills the Java Card specification and contains no illegal operations or memory accesses. Unfortunately, a fault attack is able to change the Java Virtual Machine code and data which results in a circumvention of the sandbox model.

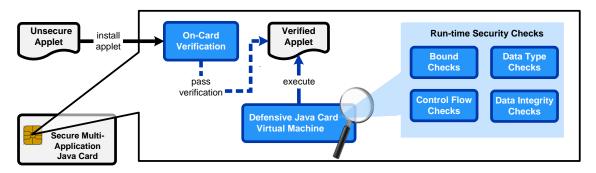

In this work novel attack countermeasures are explored to enable a secure future Java Card. To increase the overall Java Card security an on-card verified applet is protected by run-time security checks. These checks are either performed purely in software or with hardware support. Novel run-time protection units are integrated into the card to perform memory bound checks, Java data type checks, control flow checks, and data integrity checks. The protection units are addressed by inserting new security-sensitive instructions into the instruction set of two prototype smart card models. The first model is a fast executing and quickly modifiable system level model programmed in the hardware description language SystemC. The second one is a highly accurate register transfer level model from Oregano Systems programmed in the hardware description language VHDL. The processor of both models is an 8-bit 8051 processor. Both models are used for the design space exploration of various software and hardware security hardening techniques for a prototype Java Card. Moving the run-time security checks from software to hardware significantly increases the execution performance of the prototype. The additional digital logic required for the hardware protection units remains relatively small. Such increased security for Java Cards is needed, for example, to enable the secure installation and execution of any applet by the card user. Such a so called user centric ownership model could enable new profitable business fields and applications for Java Cards.

### Acknowledgements

This thesis has been pursued as part of the CoCoon research project, which is a successful cooperation between NXP Semiconductors Austria GmbH and the Institute for Technical Informatics of Graz University of Technology. Considering all these organizations and their employees that supported me during the accomplishment of my thesis, I would like to thank them all, but of course I am only able to mention a few.

First of all, I would like to thank Prof. Reinhold Weiss for providing this possibility to work in the hardware/software codesign research group at the Institute for Technical Informatics. Especially, I would thank for the helpful comments and advice given during the review phases of this work. Furthermore, I would like to express my gratitude to Christian Steger for his thoughtful supervision of the project and support concerning the academic publishing process. Our industry partners provided us with continuing insight into state-of-the-art products and industrial design environments. In this regard I would like to thank Johannes Loinig for sharing his knowledge concerning Java Cards and his valuable comments.

Also, I would like to give my thanks to Ernst Haselsteiner for his real interest in the topics of this thesis and his supportive comments especially at the beginning of the project. Special thanks go to my PhD colleagues Massimiliano Zilli and Wolfgang Raschke for their in-depth review of this work and their helpful comments on various publications. Also, I would like to thank Christian Kreiner for his various advices that were a tremendous help during my PhD. Furthermore, my thanks are due to Stefan Orehovec and Erik Gera-Fornvald for their help to improve various papers. In this regard I would also like to give my thanks to my project partner Reinhard Berlach for the great cooperation during the accomplishment of the CoCoon project. I would also like to thank all students contributing to this project: Michael Hraschan, Michael Irauschek, Stephan Oberauer, Mario Wagner, and Christian Zajc.

Graz, July 2014

Michael Lackner

### **Extended Abstract**

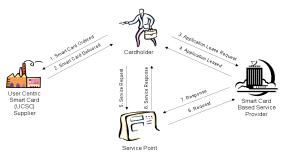

A Java Card is a standardized virtual machine running on a resource constrained smart card. The cards are used in a wide range of applications such as banking, transport, access control, and passports. All these applications rely on the security and reliability provided by these cards. To ensure Java Card security, today's card users are not allowed to install their own applets on the card. In future, it is expected that users will be allowed to perform post-issuance installation of their own applets. This post-issuance installation of user applets will enable new business fields and use cases like, for example, an applet store for Java Cards. On the other hand, new security issues and threats will emerge. Therefore, the next major challenge for Java Card platform design is to cover security concerns related to post-issuance installation of user applets on the card.

Current Java Card security is provided by a sandbox security model. This sandbox separates applets from each other and protects their security-critical code and data. Therefore, the sandbox thwarts all illegal access to fields and objects which are not part of the current applet context. The whole sandbox concept relies on the fact that the applet and its corresponding bytecodes are well formed and do not violate the Java Card specification. An applet which does not fulfill the specification is called a malicious applet and is able to perform logical attacks against the virtual machine. Logical attacks are, for example, an overflow of different memory buffers to illegally overwrite the current Java method return address. Such threats of logical attacks are currently thwarted by performing a static off-card applet verification in a secure environment. After a successful verification a signature is calculated over the applet by a secret key. This secret key is only known by authorized companies and authorities.

Unfortunately, attackers are able to mutate a successfully verified and installed applet into a malicious one. This mutation is done by performing a run-time fault attack (e.g., laser beam, clock/power supply glitch) to change the standard control and data flow of an applet to the advantage of an attacker. Such fault attacks can be counteracted by dynamic checks during the run-time of an applet.

Therefore, to enable the next generation of Java Cards with their high security requirements, new static and dynamic security features are needed. The CoCoon project<sup>1</sup>, which included and financed this work, aims at enabling the post-issuance installation of applets by the card user. This so called user-centric ownership model has to counteract two main security threats.

1. Logical attacks are performed by an attacker who manipulated a Java Card applet

<sup>&</sup>lt;sup>1</sup> CoCoon: Codesign for Countermeasures against Malicious Applications on Java Cards, collaborative research project of the Graz University of Technology, NXP Semiconductors Austria GmbH. Funded by the Austrian Federal Ministry for Transport, Innovation, and Technology under the FIT-IT contract FFG 830601.

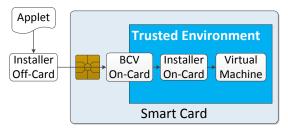

before its installation. Such a manipulated applet can be thwarted by an *on-card* verification during the install process.

2. Fault attacks can change the data and control flow of an applet during run-time. Such fault attacks are thwarted by new *run-time security checks* which enable a defensive virtual machine.

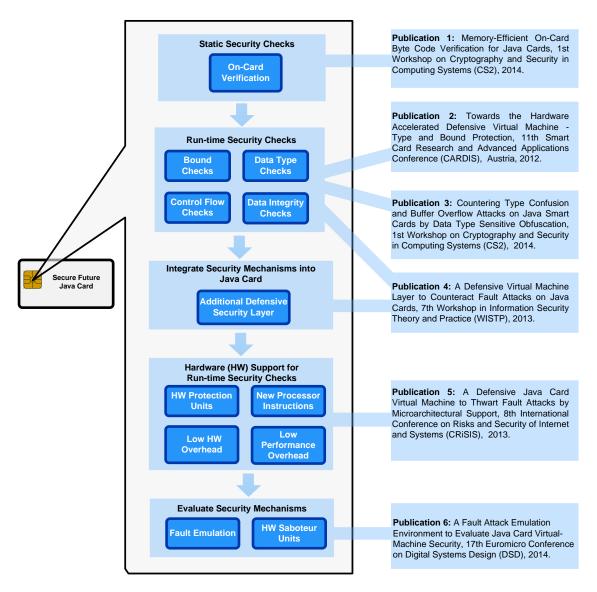

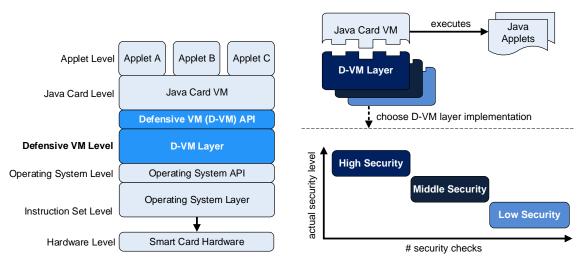

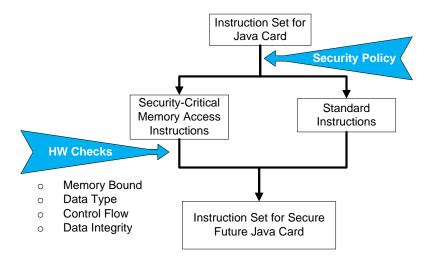

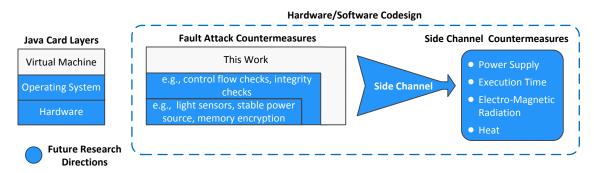

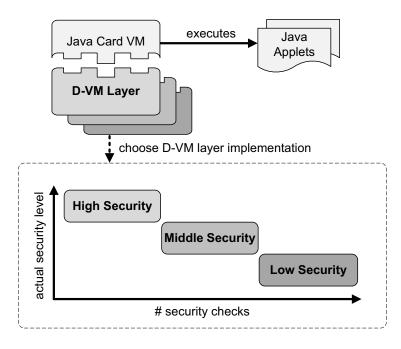

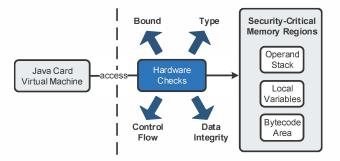

Both security concepts, on-card verification and run-time security checks, are illustrated in Figure 1. The on-card verification and the run-time security checks must be designed in respect to the constrained available resources on a Java Card. In particular for the run-time security checks, a tradeoff must be found between the performance/memory consumption and the required level of security. By moving security checks from software to hardware it is possible to improve the execution speed of the run-time checks. This security-related hardware/software codesign approach enables a significant performance improve against an approach where all checks are only performed in software.

**Figure 1:** To enable the user-centric ownership model each applet must be verified during the install process. A successfully verified applet is protected by a defensive Java Card virtual machine. This defensive virtual machine performs run-time checks to counteract fault attacks.

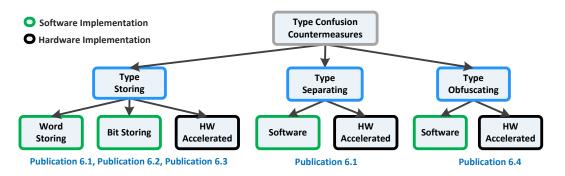

This thesis presents security mechanisms to enable the user-centric ownership model for future Java Cards. Based on a hardware/software codesign process, selected security mechanisms are accelerated by dedicated microarchitectural hardware support. The starting point of this work is the research on current state of the art attacks and security threats in the context of Java Cards and the user centric ownership model. The next step is the creation of countermeasure concepts and the assignment of the counteracted threats. Logical attacks are counteracted by an on-card applet verifier<sup>2</sup>. Fault attacks are counteracted by additional run-time checks. The most promising countermeasures are selected and evaluated in a countermeasure exploration phase. The countermeasures are evaluated in terms of their performance impact, memory consumption, detection rate and detection latency. For example, to counteract type confusion attacks three different countermeasure concepts were found: storing<sup>3</sup> the type information for each value during run-time, separating<sup>3</sup> the values to different memory areas depending on the data type,

<sup>&</sup>lt;sup>2</sup>Memory-Efficient On-Card Byte Code Verification for Java Cards, 1st Workshop on Cryptography and Security in Computing Systems (CS2'14), Vienna, Austria, 2014

<sup>&</sup>lt;sup>3</sup>Towards the Hardware Accelerated Defensive Virtual Machine - Type and Bound Protection, 11th Smart Card Research and Advanced Applications (CARDIS'12), Graz, Austria, 2012

and obfuscating<sup>4</sup> the values with different keys depending on the data type.

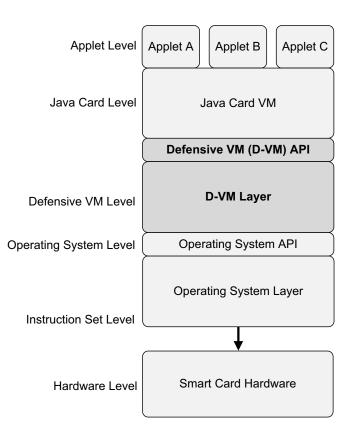

The next research topic is the effective integration of the selected countermeasures into the virtual machine. For the integration, an additional security layer<sup>5</sup> is added into the virtual machine. This security layer handles all accesses to security-critical memory regions of the virtual machine. The security layer provides a defined security application programming interface.

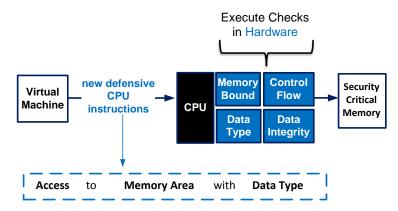

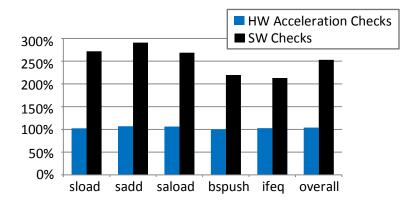

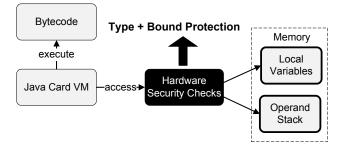

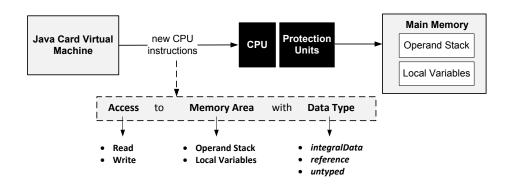

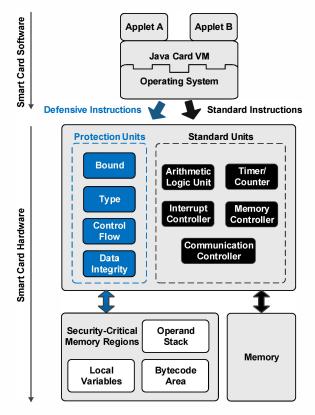

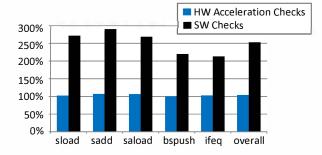

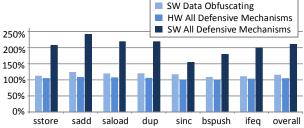

On the resource constrained Java Cards the impact of run-time countermeasures on the performance is very critical. Executing a lot of software countermeasures slows down the execution performance too much. Such a slow down could make the card useless for industrial use cases which have very strict execution time requirements. Therefore, this work shifts the above described run-time countermeasures from software to hardware during a hardware/software codesign phase. This is done by adding new defensive hardware protection units<sup>6</sup> into the smart card. These protection units are responsible for protecting memory bounds, data types, control flow, and data integrity of the virtual machine. This hardware acceleration shows an impressive increase in speed to the execution time for different Java bytecodes. Also the additional logic area needed on an FPGA development board is quite low.

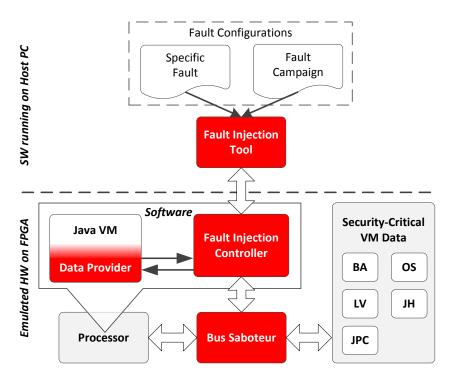

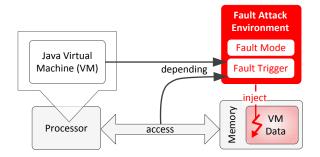

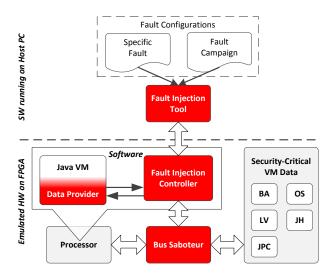

For a fast evaluation of future software and hardware countermeasures against fault attacks a fault emulation environment<sup>7</sup> is needed. This environment is especially designed to test the security of Java Virtual Machines against run-time attacks on the securitycritical memory regions of the virtual machine. During a case study a simplified Java wallet applet has been attacked to gain access to money transfer functionality without knowing the valid PIN.

To summarize, this dissertation presents selected countermeasures against current state of the art security threats and attacks against the Java Card virtual machine. These threats are counteracted by countermeasures during a hardware/software codesign process. Selected countermeasures are accelerated by microarchitectural support of the Java Card. Furthermore, a fault emulation environment is proposed to evaluate the Java Card security against fault attacks. The additionally integrated countermeasures are needed to enable the user-centric ownership model for future Java Cards.

<sup>&</sup>lt;sup>4</sup>Countering Type Confusion and Buffer Overflow Attacks on Java Smart Cards by Data Type Sensitive Obfuscation, 1st Workshop on Cryptography and Security in Computing Systems (CS2'14), Vienna, Austria, 2014

<sup>&</sup>lt;sup>5</sup>A Defensive Virtual Machine Layer to Counteract Fault Attacks on Java Cards, 7th Workshop in Information Security Theory and Practice (WISTP'13), Heraklion, Greece, 2013

<sup>&</sup>lt;sup>6</sup>A Defensive Java Card Virtual Machine to Thwart Fault Attacks by Microarchitectural Support, 8th International Conference on Risks and Security of Internet and Systems (CRiSIS'13), La Rochelle, France, 2013

<sup>&</sup>lt;sup>7</sup>A Fault Attack Emulation Environment to Evaluate Java Card Virtual-Machine Security, 17th Euromicro Conference on Digital Systems Design (DSD'14), Verona, Italy, 2014)

## Contents

| 1        | Intr           | Introduction 1                                                     |  |  |  |

|----------|----------------|--------------------------------------------------------------------|--|--|--|

|          | 1.1            | Motivation                                                         |  |  |  |

|          | 1.2            | Security Threats on Java Cards                                     |  |  |  |

|          |                | 1.2.1 Java Card Virtual Machine Security Concept                   |  |  |  |

|          | 1.3            | Hardware/Software Codesign for a Secure Future Java Card           |  |  |  |

|          |                | 1.3.1 The CoCoon Project                                           |  |  |  |

|          |                | 1.3.2 Problem Statements                                           |  |  |  |

|          |                | 1.3.3 Contributions of this Thesis                                 |  |  |  |

|          |                | 1.3.4         Thesis Structure         7                           |  |  |  |

| <b>2</b> | $\mathbf{Rel}$ | ated Work 8                                                        |  |  |  |

|          | 2.1            | Java Card Security Overview                                        |  |  |  |

|          | 2.2            | Java Card Attack Overview                                          |  |  |  |

|          |                | 2.2.1 Attacks on the Java Card Sandbox                             |  |  |  |

|          | 2.3            | Overview of Java Card Countermeasures                              |  |  |  |

|          |                | 2.3.1 Countermeasures to Harden the Java Card Sandbox              |  |  |  |

|          |                | 2.3.2 Drawbacks of Current Countermeasures and Discussion          |  |  |  |

|          | 2.4            | Summary and Difference to State-of-the-Art Countermeasures         |  |  |  |

| 3        | Des            | ign Evaluation for a Secure Future Java Card 14                    |  |  |  |

|          | 3.1            | Overview                                                           |  |  |  |

|          | 3.2            | Run-time Checks                                                    |  |  |  |

|          |                | 3.2.1 Run-time Security Policy 16                                  |  |  |  |

|          |                | 3.2.2 Type Confusion Countermeasure Designs 17                     |  |  |  |

|          |                | 3.2.3 Memory Overflow Countermeasure Designs                       |  |  |  |

|          | 3.3            | Countermeasure Integration into Java Card Architecture             |  |  |  |

|          | 3.4            | Static On-Card Applet Verification                                 |  |  |  |

|          | 3.5            | Hardware Support for Run-time Security Checks                      |  |  |  |

|          | 3.6            | Evaluate Java Card Security by Fault Emulation                     |  |  |  |

| 4        | $\mathbf{Res}$ | ults and Case Studies 23                                           |  |  |  |

|          | 4.1            | Evaluation Platforms                                               |  |  |  |

|          |                | 4.1.1 Tool Chain                                                   |  |  |  |

|          |                | 4.1.2 System Level Model                                           |  |  |  |

|          |                | 4.1.3 Register Transfer Level Model                                |  |  |  |

|          | 4.2            | Case Study on Type Confusion Countermeasures                       |  |  |  |

|          |                | 4.2.1 Type Storing                                                 |  |  |  |

|          |                | 4.2.2 Type Separating                                              |  |  |  |

|          |                | 4.2.3 Type Obfuscating                                             |  |  |  |

|          |                |                                                                    |  |  |  |

|          |                | 4.2.4 Hardware Support for Run-time Security Checks on 8051 CPU 29 |  |  |  |

|          | $4.3 \\ 4.4$ | 4.2.5       Hardware and Performance Overhead                                   | 31<br>32<br>34 |  |  |

|----------|--------------|---------------------------------------------------------------------------------|----------------|--|--|

| <b>5</b> | Con          | clusions and Future Work                                                        | 36             |  |  |

|          | 5.1          |                                                                                 |                |  |  |

|          | 5.2          | Directions for Future Work                                                      | 37             |  |  |

|          |              | 5.2.1 Fault Attack Countermeasures on Lower Java Card Layers                    | 37             |  |  |

|          |              | 5.2.2 Side Channel Leakage Countermeasures                                      | 38             |  |  |

| 6        | Pub          | lications                                                                       | 39             |  |  |

|          | 6.1          | Towards the Hardware Accelerated Defensive Virtual Machine - Type and Bound     |                |  |  |

|          |              | Protection                                                                      | 41             |  |  |

|          | 6.2          | A Defensive Virtual Machine Layer to Counteract Fault Attacks on Java Cards     | 56             |  |  |

|          | 6.3          | A Defensive Java Card Virtual Machine to Thwart Fault Attacks by Microarchitec- |                |  |  |

|          |              | tural Support                                                                   | 72             |  |  |

|          | 6.4          | Countering Type Confusion and Buffer Overflow Attacks on Java Smart Cards by    |                |  |  |

|          |              | Data Type Sensitive Obfuscation                                                 | 80             |  |  |

|          | 6.5          | Memory-Efficient On-Card Byte Code Verification for Java Cards                  | 86             |  |  |

|          | 6.6          | A Fault Attack Emulation Environment to Evaluate Java Card Virtual-Machine      |                |  |  |

|          |              | Security                                                                        | 90             |  |  |

| Re       | efere        | nces                                                                            | 98             |  |  |

# List of Figures

| 1                   | Overview of the secure future Java Card concept                            | v                                          |

|---------------------|----------------------------------------------------------------------------|--------------------------------------------|

| $1.1 \\ 1.2 \\ 1.3$ | Number of worldwide mobile subscriptions                                   | $\begin{array}{c} 1 \\ 2 \\ 3 \end{array}$ |

|                     | Security threats and attack scenarios on Java Cards                        |                                            |

| 1.4                 | Future multi-application Java Card                                         | 4                                          |

| 1.5                 | Security topics inside the CoCoon research project                         | 5                                          |

| 2.1                 | Overview of various Java Card attack points                                | 9                                          |

| 2.2                 | Memory overflow and underflow attacks on a Java Card                       | 10                                         |

| 2.3                 | Run-time control flow change by a fault attack                             | 11                                         |

| 3.1                 | Publication overview for a secure future Java Card                         | 15                                         |

| 3.2                 | Run-time security policy of a secure future Java Card                      | 17                                         |

| 3.3                 | Type confusion countermeasure designs                                      | 18                                         |

| 3.4                 | Data integrity and type policy                                             | 20                                         |

| 3.5                 | Statically performed applet verification process.                          | 21                                         |

| 3.6                 | Additional processor instructions are inserted into the Java Card          | 21                                         |

| 3.7                 | Shift run-time security checks to hardware                                 | 22                                         |

| 3.8                 | Overview of the fault emulation environment to evaluate Java Card security | 22                                         |

| 4.1                 | Java Card tool-chain for the evaluation of this work.                      | 24                                         |

| 4.2                 | High level SystemC model of the 8051 processor                             | 25                                         |

| 4.3                 | Low level VHDL model of the 8051 processor                                 | $\frac{-6}{26}$                            |

| 4.4                 | Overview of type confusion countermeasure publications                     | $\frac{-0}{26}$                            |

| 4.5                 | Implementation variants to store the type information during run-time.     | $\overline{27}$                            |

| 4.6                 | Type separating pre-processing step and typed bytecodes overview           | 29                                         |

| 4.7                 | Counteract type confusion by type obfuscating countermeasure               | 30                                         |

| 4.8                 | Run-time security checks integration with hardware support                 | 31                                         |

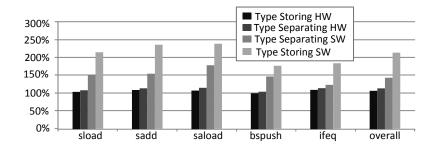

| 4.9                 | Performance overhead overview of the HW accelerated run-time checks        | 33                                         |

| 4.10                |                                                                            | 33                                         |

| 4.11                | - •                                                                        | 34                                         |

| 5.1                 | Directions for future work on Java Card security                           | 37                                         |

| 6.1                 | Publications overview for a secure future Java Card                        | 40                                         |

## List of Tables

| 3.1 | Comparison between type storing, type obfuscating, and type separating        | 19 |

|-----|-------------------------------------------------------------------------------|----|

| 4.1 | Performance overhead of the type storing countermeasures                      | 28 |

| 4.2 | Additional digital hardware resources to enable the hardware protection units | 32 |

| 4.3 | Performance overhead overview of the hardware accelerated run-time checks     | 32 |

| 4.4 | Fault emulation speedup                                                       | 35 |

| 4.5 | Fault emulation hardware overhead                                             | 35 |

## List of Abbreviations

| AHB<br>AMBA<br>API<br>BA<br>BB | AMBA High-Performance Bus<br>Advanced Microcontroller Bus Architecture<br>Application Programming Interface<br>Bytecode Area<br>Basic Block |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| BPU                            | Bound Protection Unit                                                                                                                       |

| FPU                            | Control Flow Protection Unit                                                                                                                |

| CPU                            | Central Processing Unit                                                                                                                     |

| DUT                            | Device Under Test                                                                                                                           |

| D-VM                           | Defensive Virtual Machine                                                                                                                   |

| EEPROM                         | Electrically Erasable Programmable Read-Only Memory                                                                                         |

| FIFO                           | First-In-First-Out                                                                                                                          |

| FPGA                           | Field Programmable Gate Array                                                                                                               |

| GUI                            | Graphical User Interface                                                                                                                    |

| HW                             | Hardware                                                                                                                                    |

| IPU                            | Data Integrity Protection Unit                                                                                                              |

| JH                             | Java Heap                                                                                                                                   |

| JPC                            | Java Program Counter                                                                                                                        |

| JVM                            | Java Virtual Machine                                                                                                                        |

| LA                             | Logical Attack                                                                                                                              |

| LVs                            | Local Variables                                                                                                                             |

| NFC                            | Near Field Communication                                                                                                                    |

| OS                             | Operand Stack                                                                                                                               |

| $\mathbf{PC}$                  | Personal Computer                                                                                                                           |

| RAM                            | Random-Access Memory                                                                                                                        |

| ROM                            | Read-Only Memory                                                                                                                            |

| SW                             | Software                                                                                                                                    |

| SoC                            | System on Chip                                                                                                                              |

| TPU                            | Type Protection Unit                                                                                                                        |

| VHDL                           | Very High Speed Integrated Circuit Hardware Description Language                                                                            |

| VM                             | Virtual Machine                                                                                                                             |

|                                |                                                                                                                                             |

## Glossary

### Hardware/Software Codesign

"Hardware/software codesign investigates the concurrent design of hardware and software components of complex electronic systems. It tries to exploit the synergy of hardware and software with the goal to optimize and/or satisfy design constraints such as cost, performance, and power of the final product. At the same time, it targets to reduce the time-to- market frame considerably."[1]

### Security

"The term security especially addresses system properties that need to be attained in the presence of malicious threats. Usually, security is either defined in terms of these threats and the objectives to achieve or as a composite of other characteristics. The latter is often called the CIA approach, because security is considered as being composed of the attributes confidentiality, integrity, and availability."[2]

#### Fault Attack

A *fault attack* is performed during run-time when the system performs security-critical operations. As described in [3] there are several ways to induce a fault like a glitch attack, temperature attack, light attack, and magnetic attack. The aim of a fault attack is to change the normal execution of the system to gain access to security-critical information.

### Integrity

"Integrity means that assets can be modified only by authorized parties. In this context, modification includes writing, changing, changing status, deleting, and creating." [4]

### Defensive Java Card Virtual Machine

Currently each applet is verified by an off-card verification process. Therefore, no additional run-time security checks are needed to ensure that the applet contains no illegal operations. Unfortunately, the data and program flow of such a verified applet can be manipulated by a fault attack. Therefore, to increase the overall security of a Java Card against fault attacks a so called *defensive Java Card Virtual Machine* is needed. This *defensive Java Card Virtual Machine* performs additional security checks during the run-time of a Java Card applet.

# Chapter 1 Introduction

### 1.1 Motivation

By around the end of 2014, the number of mobile phones on the planet will exceed the number of people (currently 7.1 billion). Every mobile phone has a subscriber identity module (SIM) or universal SIM (USIM) that is authenticated by the mobile service provider. These cards perform different cryptographic operations to enable this authentication. The high demand of specialized secure devices will most probably continue in the near future. Their high levels of security will be needed for different use cases such as automotive (e.g., connected/self-driving vehicles), government (e.g., electronic health record) or military (e.g., drones, autonomous robotic vehicles).

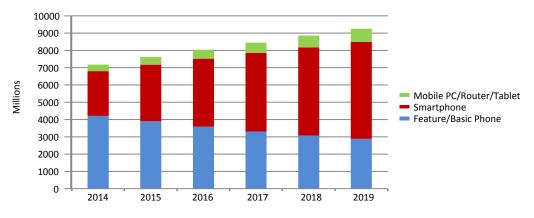

The number of mobile subscriptions, shown in Figure 1.1, is due to increase continuously from the year 2014 and will be over 9,000 million in the year 2019. In this time period the number of smart phones will have doubled. The increase in smart phone ownership is an important fact as specialized secure devices are used much more often in smart phones (e.g., fingerprint sensor, near field communication (NFC) chip) than in cheap basic phones. This means that one smart phone can contain several secure chips.

Figure 1.1: Number of worldwide mobile subscriptions for different devices like mobile personal computer, smart phone, and basic phone (obtained with modifications from [5]).

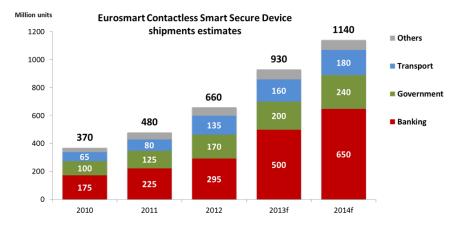

A very successful variant of these secure devices are the so called Java Cards. On these cards runs a Java Card Virtual Machine (VM) which executes different applications. These applications are, for example, deployed in the context of electronic passports, credit cards, customer loyalty cards, transport, and access control. A famous use case of the Java Cards is in the field of contactless communication. The exponential growth of this business market is shown in Figure 1.2 with quantities of around 650 million units.

Figure 1.2: Forecasts for the shipment number of contactless smart secure devices (obtained with modifications from [6]).

### **1.2** Security Threats on Java Cards

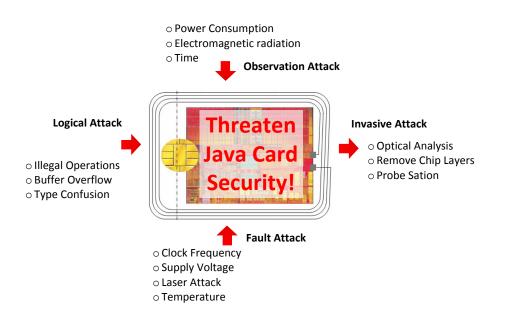

The Java Card consists of the software VM which is executed on a smart card. This smart card consists of different digital parts (e.g., processor, volatile/non-volatile memory, bus). During the execution of the Java Card VM various data is transmitted between these digital parts. Data is represented on the electronic circuits by electrical charges. By firing a high-energy optical pulse (laser attack) onto the digital parts it is possible to change the electrical charges and therefore the data which is processed by the VM. This means that it is possible to change the behavior of the VM during run-time using such a laser attack. Besides a laser attack, other security threats for Java Cards also exist which are shown in Figure 1.3.

- **Observation Attack:** By an observation of the power consumption, electromagnetic radiation, or execution time it is possible to draw conclusions on the internal behaviour of the chip.

- **Invasive Attack:** The chip is reverse engineered by optical analysis and a removal of the chip layer.

- Fault Attack: The normal chip execution is disturbed by abnormal high/low clock frequency, supply voltage, temperature, or a laser attack. By using a fault attack an adversary is, for example, able to overjump instructions or change data in memories.

- Logical Attack: An attacker uploads and installs a malicious applet. This malicious applet performs illegal operations like buffer overflows or type confusion attacks to illegally receive or manipulate security-critical data.

Figure 1.3: The security of the data and code stored on Java Cards is threatened by different security threats and attack scenarios (obtained with modifications from [7] [8]).

All these different security threats must be considered during the design and implementation phases of a secure future Java Card. This work shows countermeasures that can be used against the threat of run-time fault attacks and logical attacks.

The Java VM runs on a resource constrained smart card. These cards have to withstand logical attacks and physical attacks. To counteract these attacks it is necessary to integrate countermeasures into the hardware (HW) and software (SW). Unfortunately these countermeasures, particularly in SW, decrease the execution performance of the card or need a lot of memory for intermediate calculations. These cards are used in mass production which means that millions or billions of such cards are produced. Even a small amount of money saved per device results in a large overall saving. Therefore, this work shows various run-time countermeasures which have a low impact on the execution performance and HW overhead and are able counteract different proposed attack scenarios.

### 1.2.1 Java Card Virtual Machine Security Concept

The Java Card security is ensured by a sandbox concept. This sandbox ensures that each applet is somehow trapped in its own memory regions. Therefore, applets are not able to illegally access code or data of other applets installed on the card. This sandbox concept relies on the fact that each applet fulfills the Java Card VM specification [9, 10]. This specification defines, for example, that bytecodes are not allowed to access data outside of reserved memory regions by a buffer overflow attack. The compliance of an applet with the specification is currently checked by an off-card verification step in a secure environment. This means that, for example, such buffer overflows are currently checked by the static byte code verification process but not during run-time.

These run-time attacks are performed by firing a laser onto the card, dropping the supply voltage, applying an illegally high or low clock frequency or a strong electro magnetic field. With such attacks it is possible to overjump or change the execution behaviour of Java bytecodes. Therefore, an adversary is able to change the control and data flow of a Java applet to his will. By such a manipulation it is possible to bypass security checks during run-time. Such checks protect, for example, money transfer functions from users who do not know the secret personal identification number (PIN) of a credit card. An adversary which removes the PIN check functionality is able to withdraw or transfer money to the bank account of an adversary.

### 1.3 Hardware/Software Codesign for a Secure Future Java Card

This chapter provides an overview of the research project in which this thesis is established. Furthermore, this chapter explains the problem statements and the contributions and significance of this work.

### 1.3.1 The CoCoon Project

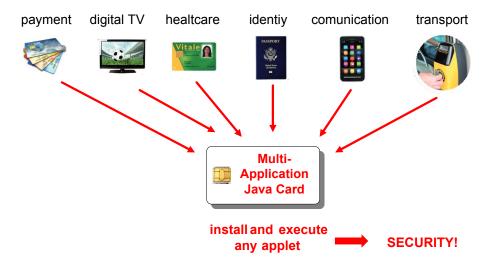

This thesis is part of the "Codesign for Countermeasures against Malicious Applications on Java Cards" (CoCoon) collaborative research project, shared between the Institute for Technical Informatics at the Graz University of Technology and NXP Semiconductors Austria GmbH. This combined effort targets the HW/SW codesign of a secure future Java Card. These future cards should support the user centric ownership model (UCOM). With the UCOM every user is able to upload any applet onto the card without any security problems. Therefore, with the help of the UCOM only one card is needed for different applications as shown in Figure 1.4.

Figure 1.4: In the UCOM every user is able to upload applications for different contexts. Therefore, the overall security of such future multi-application cards must be increased to counteract different security threats (obtained with modifications from [11]).

The main goal of the project is to increase the security of Java Cards as much as possible with the least amount of expense possible. A great benefit of the CoCoon project is the fact that NXP Semiconductors Austria GmbH is the developer of the Java Card SW and the smart card HW. Other Java Card manufacturers only produce the SW but without the HW and vice versa. This holistic view of the Java Card in the CoCoon project enables a HW/SW codesign process which particularly focuses on security.

An overview of the complex field of HW/SW codesign is presented in [12]. Another overview is given in the lecture notes from the ETH Zürich [13]. In general, as described in [13], the HW/SW codesign process can be seen as the integrated design of HW and SW components. During this process different alternative designs are planned, compared and evaluated during a design space exploration phase.

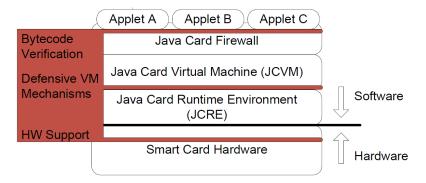

An overview of the different security topics inside the CoCoon project is shown in Figure 1.5. The CoCoon approach covers security checks at the Java layer, the Java Card firewall mechanism, run-time (defensive) VM mechanisms, static bytecode verification, and HW support of these security features. This work will concentrate on the last three topics. This thesis performs HW/SW codesign to enable a secure future Java Card for the UCOM.

Figure 1.5: Overview of the different security topics inside the CoCoon project (obtained with modifications from [14]).

### 1.3.2 Problem Statements

A Java VM runs on a Java Card which can be seen as a SW processor running on the real smart card processor. This abstraction adds an additional execution time overhead. This overhead is very critical especially for Java Cards which are used as a mass product. Therefore, appropriate run-time countermeasures must be designed to consume as few additional resources (computational power and memory) as possible. Furthermore, these countermeasures should counteract as many attacks as possible. State-of-the-art countermeasures on Java Cards are only implemented in SW and not accelerated by special HW mechanisms as proposed in this work. This means that we shift functionality from SW into HW during a HW/SW codesign phase shown in this work. Compared to currently proposed SW countermeasures against fault attacks, the following deficiencies can be identified:

- Currently proposed countermeasures are executed in SW which slows down the execution performance.

- Synergy effects from designing HW and SW in parallel for Java Cards is less researched especially from a security point of view.

- Countermeasure designs are quite well known by industrial Java Card manufacturers but not published in the scientific community.

- Lack of knowledge of how and which countermeasures are needed during run-time leads to a long countermeasure design space exploration phase or inefficient countermeasures.

- Missing knowledge about appropriate countermeasure designs creates insecure systems which can lead to economic, material, and human losses.

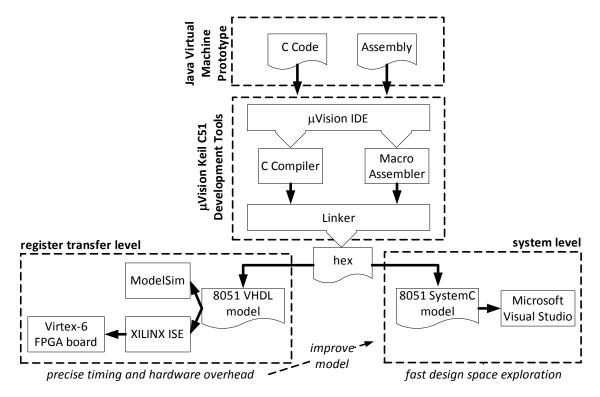

These limitations have been addressed by the creation and evaluation of different countermeasure proposals. Early evaluations are based on memory consumption, run-time overhead, detection latency, and the general security increase. To reduce the computational overhead the countermeasures are accelerated by HW support. The HW acceleration mechanisms are developed during a HW/SW codesign process. For this acceleration a smart card prototype was used which is implemented at different abstraction levels. For a fast design space exploration a high-abstracted transaction level model is used. For a finer computational and HW overhead analysis a low-abstracted register transfer level model is used. The countermeasures are seamlessly integrated into the VM by adding a new security related SW layer into the Java Card architecture.

#### **1.3.3** Contributions of this Thesis

In summary, this thesis provides contributions to the following fields:

- 1. Identify Security Threats on Future Java Cards and Create New Concepts of Countermeasures: Logical attacks are counteracted in this work by a statically performed bytecode verification process during the install time of an applet. During run-time additional checks were added to counteract fault attacks. Different security holes were identified and thwarted by additional checks. Only selected checks are performed during run-time to counteract as many attacks as possible with as little memory and performance overhead as needed. The new run-time checks are based on memory bound checks, data type checks, control flow checks, and data integrity checks. Different countermeasure designs are explored based on a design space exploration phase. For example to counteract type confusion attacks we proposed three general ideas: type storing, type separating, and type obfuscating.

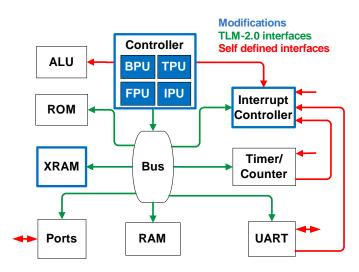

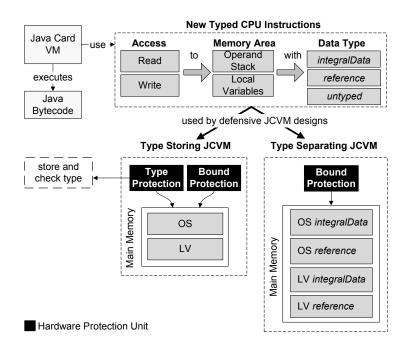

- 2. Hardware Support for Countermeasures: SW checks add an additional memory and performance overhead. Therefore, in this work we shifted different run-time checks from SW to specially designed HW units. The units are namely the memory bound protection, data type protection, control flow protection, and data integrity protection units. An execution speedup is reached by performing the checks of the HW units in parallel to the normal processor operations. To communicate with the HW units new specially designed processor instructions were added. These new instructions are used to access the security-critical memory regions of the VM. This novel approach enables a significant improvement in the execution speed of the runtime checks compared to a full SW implementation. The performance and HW overhead of the additional protection units were evaluated on a Java Card prototype implementation running on an FPGA board.

3. Seamless Integration of Countermeasures into Java Card: A novel security abstraction layer was added into the Java Card. This layer is used to access the security-critical memory regions of the VM. All run-time security checks of this work are added into this layer and can be easily enabled, disabled, or modified. The main benefits of the new layer are: high flexibility by partitioning security features from SW to HW or from one SW implementation to another; increased maintainability of security checks; accelerating further development of new security features for the VM.

### 1.3.4 Thesis Structure

Section 2 describes the related work in the field of Java Card security. Various attack scenarios against the Java Card sandbox model are presented such as memory overflow or Java data type confusion. Furthermore, an overview of state-of-the-art countermeasures and the drawbacks of these countermeasures are discussed. This section finishes with a summary of the main improvements to the countermeasures that have been developed in this thesis compared to state-of-the-art countermeasures.

Section 3 presents an evaluation of the design of a secure future Java Card. The run-time security policy of such a future card is discussed. Furthermore, various general countermeasure designs are introduced which fulfill the proposed run-time security policy. Also the integration of the countermeasures into the Java Card architecture and static on-card applet verification is discussed. Furthermore, the fault emulation environment of this work is presented.

Section 4 shows the results of HW, performance, and memory measurements on two evaluation platforms. The evaluation platforms are first described with their changes for the new run-time security checks. Followed by a case study on different type confusion countermeasure implementation variants. The acceleration of the run-time security checks by newly added HW protection units which are integrated into an 8051 processor is described. Followed by a discussion and presentation of the static on-card applet verification algorithm. Furthermore, the fault emulation environment is discussed in more detail followed by a case study of an attacked Java wallet applet.

Section 5 draws conclusions and future works from this thesis. Directions for future work are presented which could focus in the direction of HW/SW codesigned countermeasures against side channel attacks. Furthermore, the integration of countermeasures into deeper Java Card layers like the operating system or directly into the HW are suggested.

Section 6 presents the collection of publications which were published during this thesis.

# Chapter 2 Related Work

This section first presents an overview of the Java Card technology with a particular focus on security. Furthermore, an overview of attacks on Java Cards is given followed by countermeasures against these attacks. Finally, a summary of this section is shown with the main differences of this thesis compared to related work.

### 2.1 Java Card Security Overview

Security requirements of embedded systems like Java Card are continuously increasing. These security requirements also have to be considered during the design phase of a Java Card [15]. Java Cards have to withstand various attacks (e.g., microprobing, SW attacks, eavesdropping, fault generation) to protect the security-critical data stored on them [16].

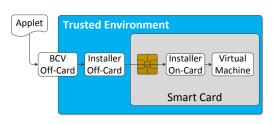

The current Java Card security concept relies on the fact that every Java Card applet is verified. This verification counteracts logical attacks against the Java Card sand-box model. Nowadays, this verification is performed off-card in a secure environment. On commercially available Java Cards like banking cards, the card user is not able to install new applets. To install new applets the card user would need to know a secret key which is only known by authorized companies and authorities. With this secret key it is possible to create a valid signature which is checked during the install process of an applet on the card.

The next big shift in the Java Card market will be the user centric ownership model. In this model the card user is able to install any applet he wants onto the card. Such a shift also increases the security requirements for Java Cards to counteract logical attacks by an on-card verification process. Furthermore, the Java Card must persist in an environment where attackers perform different attacks on the card. These attacks are, for example, side channel analysis, glitch attacks, and laser attacks.

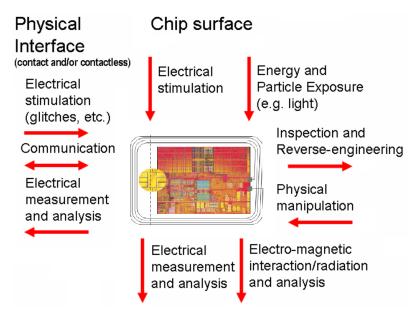

### 2.2 Java Card Attack Overview

The Java Card has various contact or contactless physical interfaces to communicate with other electronic devices. Furthermore, over the chip surface physical quantities can be measured or the internal processing of the chip can be disturbed by fault attacks shown in Figure 2.1. By the *electrical measurement and analysis* of the power consumption of the chip an attacker can gain knowledge of internal processes [17]. Over the communication interface SW viruses can be uploaded onto the Java Card [18]. By electrical stimulation (e.g., digital clock or power supply glitch) an adversary is able to change the data which is read out or written into volatile and non-volatile memories [19]. Over electrical stimulation or energy and particle exposure an attacker can manipulate internal calculations. Such manipulations during cryptographic operations can lead to the loss of secret cryptographic keys [17]. Furthermore, there is a threat of reverse-engineering and physical manipulation of the silicon chip [8]. Also so called side channel attacks, performed by electro-magnetic radiation analysis [20, 21, 22], are a serious security threat and a very active field of research.

Figure 2.1: A Java Card has several attack points such as physical interfaces or the measurement or manipulation by physical quantities (obtained with modifications from [7]).

### 2.2.1 Attacks on the Java Card Sandbox

An attacker is able to break the sandbox model of the Java VM using a malicious applet which does not fulfill the Java Card specification [9, 10]. Such a malicious applet can be created by an applet manipulation before the upload onto the card [23] or by a fault attack during run-time. In literature four general sorts of attack are described which are memory overflow attacks, control flow attacks, type confusion attacks, and data integrity attacks.

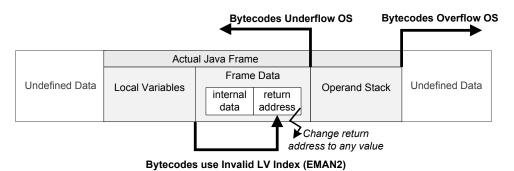

### Memory Overflow Attacks

For every invoked Java method a new so called Java Frame is created. When a Java method returns then the execution flow returns to the previous frame. This frame data generally consists of three fixed sized memory regions:

- Operand Stack (OS): The OS is used by the VM for most logical and arithmetic operations. Values are pushed and popped onto the top element of the OS.

- Local Variables (LVs): The LVs are freely accessible like standard registers in a processor.

- Frame Data: The frame data consists of internal data of the VM like the return address to the previous frame. Note that the specific internal frame data is implementation dependent and not specified inside the VM specification.

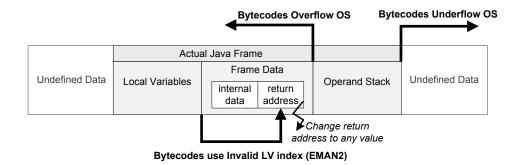

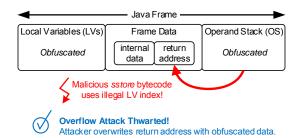

An attacker is able to provoke an overflow of the OS or LVs in order to illegally access data outside the reserved memory regions. An overview of such overflow attacks is shown in Figure 2.2. The authors in [24] show an attack, which is called EMAN2, where they provoke an overflow of the LVs and illegally gain access to the frame data to overwrite the return address. Therefore, they are able to change the control flow of an applet. In 2013 an OS underflow attack was proposed in [25]. By the help of illegal *swap* bytecodes they were able to illegally access the return address of a Java Frame.

Figure 2.2: On the Java Frame different attacks are proposed like an OS underflow attack [25] or an overflow attack on the LVs [24] memory (obtained with modifications from [26]).

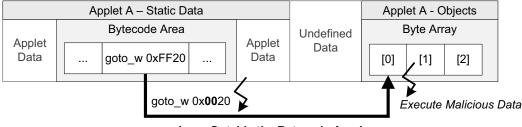

### **Control Flow Attack**

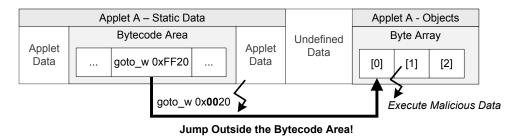

During the execution of an applet the VM fetches the bytecodes from the fixed sized bytecode area (BA). In 2011 a run-time attack, called EMAN4, was found by the authors in [24] which is shown in Figure 2.3. By a laser attack during run-time they were able to change the control flow of an applet to illegally jump outside the BA by a manipulated *goto* bytecode. The jump destination can then be, for example, a data array filled with malicious code. This leads to the security threat of executing data instead of code. Such a manipulation of the control flow can lead to serious security attacks like the memory dump of security-critical code and data on the card as described by the authors in [27].

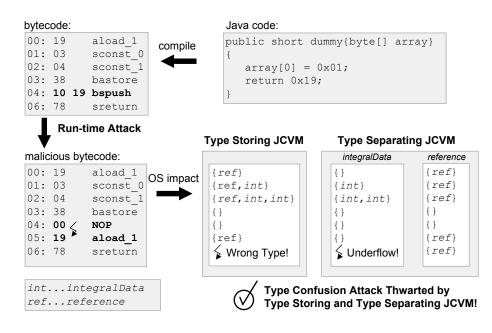

### Data Type Confusion Attack

By the Java Card specification [9, 10] it is exactly specified which data types are expected on the OS or LVs and which data types are written back. The data types can be divided into two main data types *integralData* (boolean, byte, short) and *reference* (object references). Type confusion between these two data types is often performed and mentioned

**Figure 2.3:** An attacker is able to change the bytecode operands to 0x00 or 0xff by a fault attack. By applying a fault attack on the *goto\_w* bytecode Barbu [24] was able to illegally change the control flow of an applet to execute malicious data (obtained with modifications from [28]).

in related works [29, 30, 31, 32, 33, 27, 24, 34] and is therefore a serious security threat. Such type confusion attacks are often the starting point for more advanced attacks like executing a data array instead of code as shown in [33, 24], the access to forbidden objects [34], and to characterize the Java Card API [30]. This thesis shows in Section 3.2.2 three different countermeasure designs which counteract type confusion attacks on the OS and LVs. Furthermore, these type checks have been shifted from SW into HW which is explained in more detail in Section 6.3.

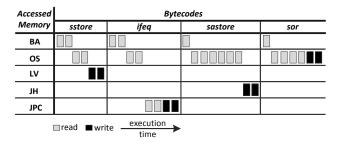

### Data Integrity Attack

The Java Card VM security and the Java Card sandbox model relies on the integrity of the data in the memory. This is especially true for the integrity of the OS and LVs because almost every bytecode reads or writes data into these memory regions. In 2011 the authors in [35] proposed a run-time data integrity attack on the OS using a laser beam. They abuse the fact that most conditional jump bytecodes (e.g., *ifeq, ifne, iflt, ifge*) rely their jump conditions on data on the OS. Therefore, by manipulating the OS data they were able to change the jump destination to their will. Therefore, this integrity attack enables the bypass of security checks (e.g., pin checks, control flow checks).

### 2.3 Overview of Java Card Countermeasures

Today various countermeasures are used to counteract attacks on Java Cards. These countermeasures start from additional physical sensors (e.g., light, high/low clock frequency or supply voltage), bus scrambling, additional protection layer in silicon or glue logic [8]. Various researcher proposed countermeasures against optical fault attacks [36], power analysis attacks [37, 38], and electromagnetic analysis attacks [20].

### 2.3.1 Countermeasures to Harden the Java Card Sandbox

In 2010 Barbu [29] showed the first practical attack where the Java sandbox model was skipped by a fault attack. Theoretical works on such attacks were earlier described [32, 31]. After Barbu's attack, researchers worked on the question of how to harden the sandbox against fault attacks on resource constrained Java Cards. Countermeasures in Java Cards should consume as little additional performance, memory and power as possible. To

reach these requirements various techniques are proposed which can be split into countermeasures where a Java Card applet is pre-processed and enriched with security relevant information and countermeasures which work on every Java Card applet without a preprocessing step.

Sere proposes in [39] that the value of the nop (no operation) bytecode be changed from 0x00 to another value. Such a modification prevents from the threat of skipping bytecodes by injecting 0x00 during a fetch operation of the VM. To protect against such skipping attacks Sere also proposes [39, 40] the calculation of a bit field over the bytecode. In this bit field is stored whether the actual fetched data is an opcode or an operand. Therefore, a confusion between opcodes and operands can be detected during run-time. Another countermeasure to detect skipped bytecodes is the off-card calculation of checksums over basic blocks (BBs) of the bytecode [41]. This is done by checking the pre-calculated checksum against the checksum calculated during run-time. Furthermore, by pre-calculating the control flow between BBs anomalies in the run-time control flow are detected. Such anomalies are illegal jumps from a BB to another BB which is not reachable. All of Seres countermeasures increase the size of the applet by additional security related data to store bit fields, checksums, and control flows. A more memory friendly countermeasure is proposed in [42] which is based on an off-card encryption of the bytecode. During run-time the bytecodes are then encrypted with a secret key. Such a bytecode encryption prevents from the threat of jumping outside the BA and executing attacker defined data. An attacker has to know the secret key to fill an array with valid code. Another countermeasure proposed in [43, 44] prevents the threat of type confusion between the two main data types integralData and reference on the OS. The countermeasure is based on splitting the OS into two memory regions. Depending on the expected main data type (integralData, reference) data is read or written into one of these memory regions. This countermeasure requires an off-card step to remove incompatible bytecodes (e.g., swap, pop, dup). In [45] a so called fingerprint is calculated off-card over the bytecodes of an applet. During run-time it is checked whether the actual applet execution is compliant with the fingerprint. In [46] an automation array is calculated during the linking time for every method. Based on this automation information the control flow of the applet is checked during run-time. In 2011 Barbu [35] proposed three countermeasure types against data integrity attacks on the OS. The first approach is based on an additional memory read and comparison operation after every read or write operation in the OS. Barbus second approach is performing a data integrity evaluation when the Java Card firewall checks are performed. By this approach the number of checks is reduced and therefore the overall execution performance of an applet increases. The third approach is based on calculating checksums for every written or read element into the OS. These checksums are evaluated at security-critical points in time during the execution of a Java applet.

### 2.3.2 Drawbacks of Current Countermeasures and Discussion

The currently proposed countermeasures against run-time attacks are implemented in SW and have two main drawbacks which are additional execution time overhead and memory consumption. The additional memory consumption comes from the fact that various countermeasures rely on a pre-processing step where checksums and control flow graphs are additionally added into the Java Card applet [39, 40, 45]. During run-time the

calculation and comparison of the checksums and control flow graphs requires additional execution time. Another drawback is that these SW checks can be skipped by a double fault injection [47]. Such a double fault injection gets easier when the time between the two faults is relatively long. To skip our new proposed HW checks in Section 6.3 an attacker has to inject faults very quickly which increases the difficulty of a successfully performed double fault injection [48]. Furthermore, the overall success rate of the attack decreases if more than one fault injection is needed. For example if one fault injection has a success rate of 10% than the overall success of an attack decreases to 10% \* 10% = 1% if two attacks are needed [49]. Therefore, the required number of attack runs for one successfully performed attack increases from 10 to 100. For an attacker this means that the card will most probably be unusable because the attack trigger will in all likelihood reach its maximum tolerable number which results in a card lock.

### 2.4 Summary and Difference to State-of-the-Art Countermeasures

This thesis aims at introducing the following main improvements to the state-of-the-art, with respect to the goals defined in Section 1.3.3:

- Run-time attacks are used by attackers to break out of the Java sandbox model to access security-critical data. In related work all proposed countermeasures which harden the VM against run-time attacks are performed in SW. In this work countermeasures to counteract, for example, type confusion attacks are accelerated by HW mechanisms during a HW/SW codesign process. This shift of functionality from SW to HW decreases the execution time overhead of the countermeasures.

- This thesis shows countermeasures which do not rely on an off-card pre-processing step to harden the Java Card sandbox. In related works pre-processing is needed to calculate, for example, checksums over the bytecode to counteract integrity attacks. Such integrity attacks are counteracted in this thesis by double checking the values which are read from or written into the memory.

- Related work does not answer the question of how countermeasures can be smoothly integrated into the VM to attain easy maintainability. Therefore, this work proposes to add an additional security layer into the VM architecture. In this security layer all run-time checks from this work are integrated.

Furthermore, this work shows the following additional advancements:

- Exploration of various countermeasure designs and implementation variants (e.g., type confusion and memory overflow countermeasures).

- Countermeasures are explored in terms of execution time, memory, and hardware overhead on a Java Card prototype.

- To counteract fault attacks this work moves checks which are statically performed at install time to the run-time.

### Chapter 3

## Design Evaluation for a Secure Future Java Card

This section provides an overview of publications concerning a HW/SW codesigned secure future Java Card. Various run-time security policies are shown which are fulfilled by this card. Run-time countermeasure designs are discussed which counteract, for example, type confusion or memory overflow attacks. Furthermore, this section shows the acceleration of the run-time security checks by specific HW support and the integration of the security mechanisms into the Java Card architecture.

### 3.1 Overview

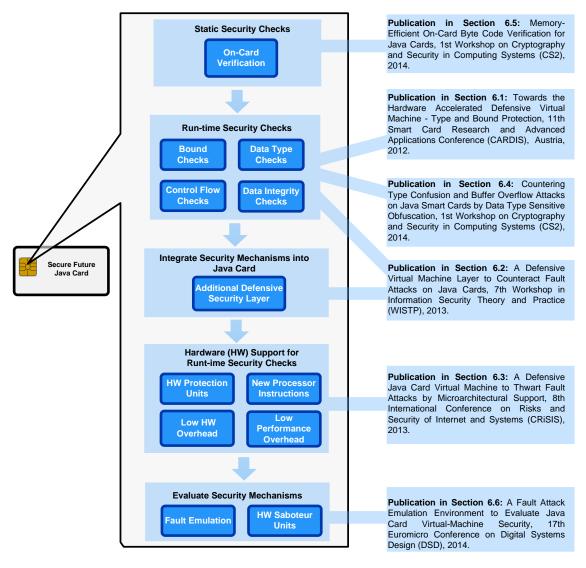

Different attacks exist which threaten Java Card security. To counteract these threats new security mechanisms must be integrated into the Java Card VM. The proposed mechanisms of this work aim at increasing security against fault attacks and logical attacks. The increased security of the card is reached by a static on-card verification step performed on every newly installed applet. Furthermore, run-time checks are executed which counteract various fault attacks during run-time. These run-time checks are accelerated in this work by microarchitectural HW mechanisms on the card. An overview of the individual contributions of this work and their mapping to scientific publications are illustrated in Figure 3.1.

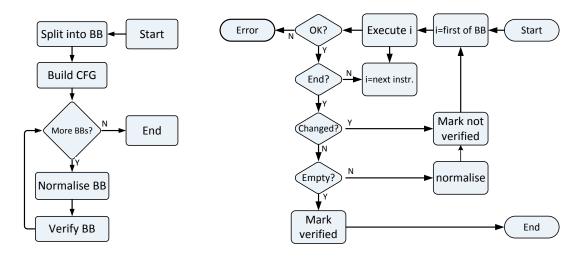

The basis of such a secure future multi-application Java Card is that an attacker is not able to install a malicious applet onto the card. In case a malicious applet can be installed onto the Java Card, then an attacker is able to illegally access security-critical code or data by a logical attack. To prevent this security threat, a static on-card verification step is needed. Such a memory efficient on-card bytecode verification process is described in detail in *Publication 1*.

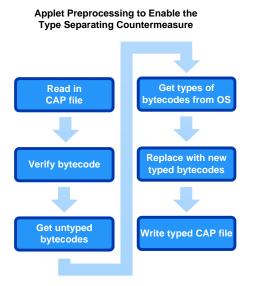

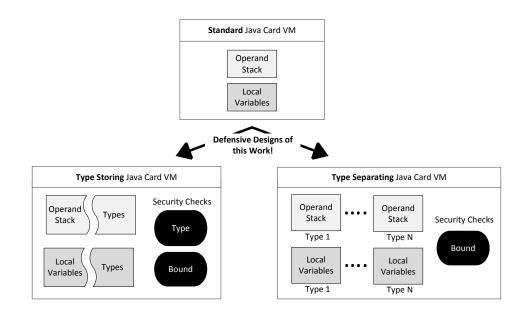

A verified applet cannot break the Java Card sandbox model and gain illegal memory accesses. Unfortunately, the sandbox model can be circumvented by fault attacks during the applet execution. Therefore, new countermeasures must be integrated into the Java Card VM. To counteract, for example, memory overflow attacks and type confusion attacks on Java Cards two different approaches are presented in *Publication 2*. These approaches counteract type confusion attacks between *integralData* (e.g., short, byte, boolean) and

Figure 3.1: Publication overview concerning a secure future Java Card with new HW and SW security features.

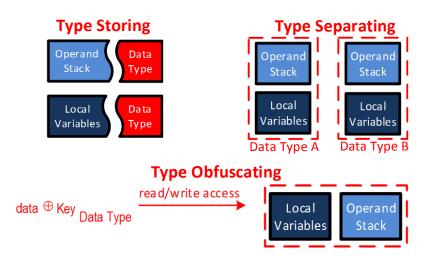

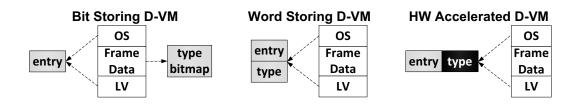

object *references* (e.g., short[], byte[], class A). The first countermeasure approach is called type storing and stores the data type information during run-time. Based on this stored information additional checks are performed during run-time to detect type confusion. The second approach is called type separating and separates the data into different memory regions depending on the data type. By this type separation it is no more possible to perform type confusion between *integralData* and *reference* during run-time. Furthermore, both approaches perform memory bound checks to counteract run-time buffer overflow attacks.

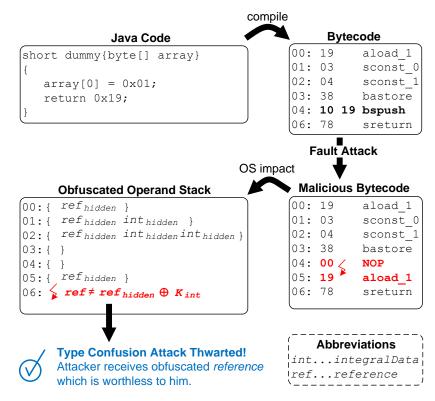

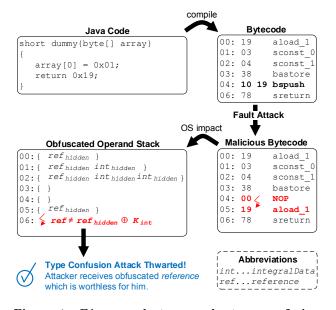

In Publication 3 it is shown how type confusion and buffer overflow attacks can be counteracted by data type sensitive obfuscation. The values inside the VM are obfuscated by different secret keys depending on the data type. For *integralData* the key  $K_{integralData}$  is used and for *references* the key  $K_{reference}$ . By this countermeasure an attacker will create unpredictable values with a type confusion attack. Furthermore, buffer overflow attacks are counteracted because the data which is read/written outside the buffer is also unpredictable for an attacker. The type obfuscation approach is more memory efficient and consumes less additional computational performance than the type storing and type separating approach.

All these run-time countermeasures have to be seamlessly integrated into the Java Card architecture. Therefore, *Publication 4* shows an additional SW security layer inside the Java Card architecture. All memory accesses to security-critical memory regions are processed over this novel layer. This security layer contains all the run-time security operations. Therefore, security operations can be easily added, disabled or modified inside the layer.

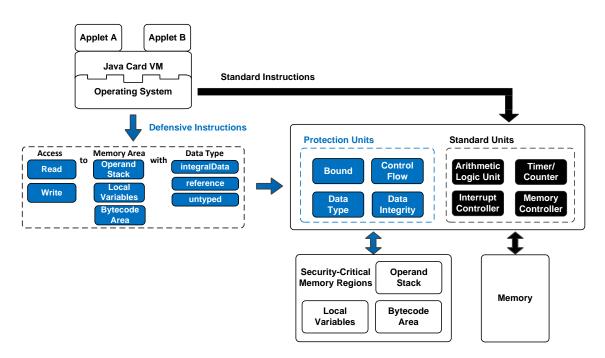

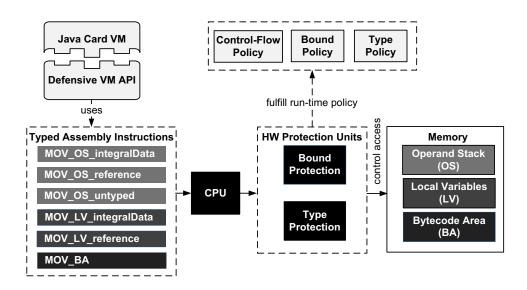

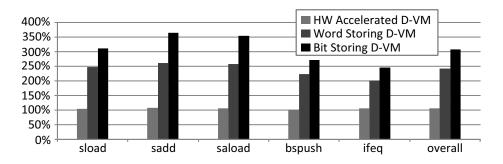

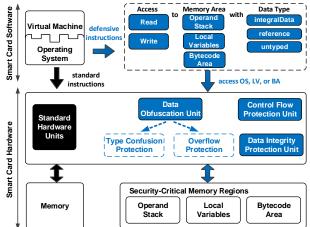

The execution of the run-time security operations in SW slows down the overall execution performance of the card. Therefore, *Publication 5* adds new HW protection units into the card to shift the run-time security operations from SW to HW. These units are the type protection unit, memory bound protection unit, control flow protection unit, and the data integrity protection unit. With the help of these additional HW units the performance overhead due to the run-time checks is dramatically reduced compared to a SW implementation.

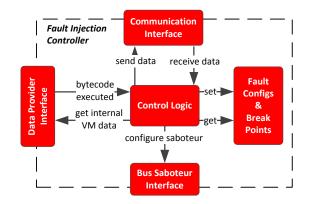

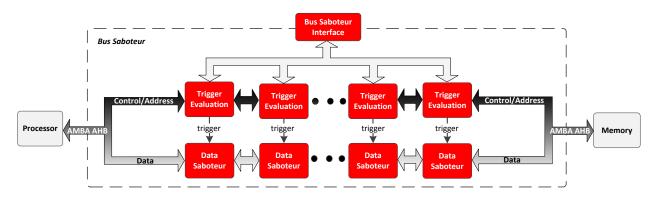

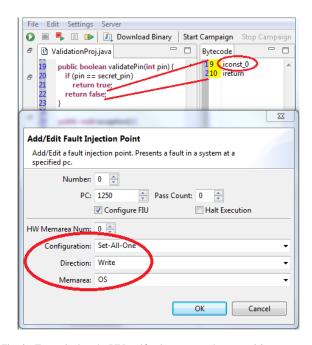

A fault emulation environment is presented in *Publication 6* to test different HW and SW countermeasures. By this environment different fault attacks can be recreated by a HW bus saboteur unit. This environment enables the design space exploration of new countermeasures. Furthermore, the effects of various fault attacks on the behavior of the VM can be analyzed.

### 3.2 Run-time Checks

The possible security threats for a future multi-application Java Card have been analyzed based on related work described in Section 2.2.1, the Java Card protection profile [50], and the Java Card specification [9, 10]. Based on these documents a run-time security policy has been created which counteracts the most dangerous threats. A detailed description of the policy and the countermeasures to fulfill this policy are shown in Section 6.3.

### 3.2.1 Run-time Security Policy

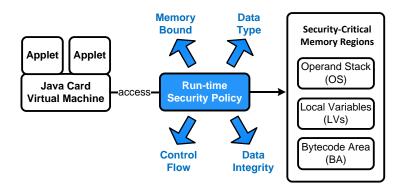

The goal of the run-time security policy is to counteract different run-time security threats on the security-critical data of the VM. Figure 3.2 depicts a schematic overview of the policy and the security-critical memory regions involved. The run-time security policy is based on four different sub-policies: (i) memory bound policy, (ii) data type policy, (iii) control flow policy, and (iv) data integrity policy.

• Memory Bound Policy: The memory bound policy counteracts buffer overflow attacks on the OS and LVs which is described in Section 6.1 [26]. The security of the bound policy is then improved in Section 6.3 by taking into account the fact that the OS can be seen as a FIFO (first in, first out) buffer [51]. Therefore, it is only

Figure 3.2: Overview of the run-time security policies for a future multi-application Java Card (obtained with modifications from [51]).

allowed to write data onto the top element of the OS. A read or write operation in the middle of the OS is not allowed.

- Control Flow Policy: The control flow policy checks that attacks are not able to illegally change the control flow of an applet by jumping outside the bytecode area of the applet. This control flow policy counteracts, for example, the threat of executing data instead of code and is described in more detail in Section 6.2 [28] and Section 6.3 [51].

- Data Integrity Policy: The data integrity policy counteracts the illegal manipulation of data which is read or written into the run-time data of the VM (OS and LVs) by a fault attack. The integrity policy is described in more details in Section 6.3 [51].

- Data Type Policy: The data type policy counteracts run-time type confusion attacks between the main data types *integralData* and *reference*. The counteracted threats and a more detailed description of the policy are shown in Section 6.1 [26].

### 3.2.2 Type Confusion Countermeasure Designs

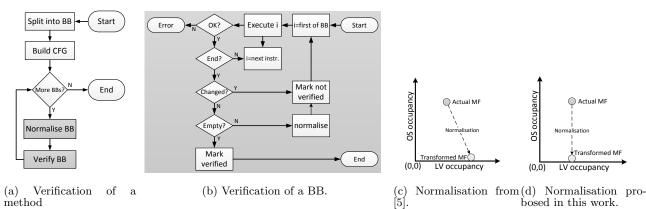

Based on the previously defined run-time security policies different implementations of countermeasures are designed and evaluated to fulfill the policies. For example to fulfill the type policy three different general countermeasure designs have been found. Type confusion can be counteracted by (i) storing the type information for every element, (ii) separating the data based on the data type or (iii) obfuscating the data dependent on the data type. A schematic overview of the three general type confusion countermeasure designs is illustrated in Figure 3.3.

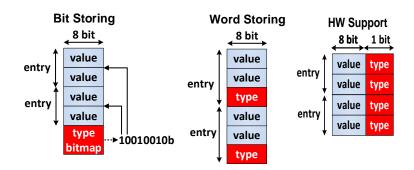

• **Type Storing:** For every element on the OS and LVs the type information is stored. Due to the fact that it is statically defined which bytecodes work on which types, it is possible to perform type checks during run-time. An evaluation of two different type storing designs is described in more detail in Section 6.2 [28] which are namely the word storing and bit storing approach. The difference between them is that the type information is either stored into a memory area with the same data size as

Figure 3.3: To fulfill the type policy of this work three different general countermeasure designs have been evaluated which are type storing, type separating, and type obfuscating.

the processor or into a type bit-map where every bit represents one entry of the OS or LVs. The two different designs vary in the memory consumption and execution speed.