# **Trusted Computing And Local Hardware Attacks**

Master's Thesis

at

Graz University of Technology

submitted by

#### **Johannes Winter**

Institute for Applied Information Processing and Communication (IAIK), Graz University of Technology A-8010 Graz, Austria

22 May 2014

© Copyright 2014 by Johannes Winter

Advisor: Univ.-Prof. M.Sc. Ph.D. Roderick Paul Bloem

## **Trusted Computing und lokale Hardware-Attacken**

Diplomarbeit

an der

Technischen Universität Graz

vorgelegt von

#### **Johannes Winter**

Institut für Angewandte Informationsverarbeitung und Kommunikation (IAIK), Technische Universität Graz A-8010 Graz

22. Mai 2014

© Copyright 2014, Johannes Winter

Diese Arbeit ist in englischer Sprache verfasst.

Begutachter: Univ.-Prof. M.Sc. Ph.D. Roderick Paul Bloem

#### Abstract

Trusted Computing is one technical approach to solving the complex question, whether a computer platform, and the software currently running on this platform, is trustworthy, or untrustworthy. To address this situation, Trusted Computing defines mechanisms that allow local, and remote parties to attest the a platform. The technical realization of these attestation mechanisms relies on a combination of platform firmware, application software, and ultimately the Trusted Platform Module (TPM), which is a dedicated smart-card like hardware security element.

A common assumption Trusted Platforms states that attackers can only perform software attacks. Even simple hardware attacks are usually considered out of scope. One important problem with this assumption is that it only holds, if platforms owners, *and* all other parties (including attackers!) with physical access to the platforms in question play by the rules.

This yields to a rather paradox situation: On the one hand proponents of Trusted Computing, like the Trusted Computing Group (TCG), state that the technology is designed with software-only attackers in mind, and consider any form of hardware attacks to be out of scope. At the same time significant effort is put into making Trusted Platform Modules tamper resistant, or at least tamper evident. The result is trusted platforms that come with highly secure little hardware security modules, the Trusted Platform Modules, which are embedded into widely open "trusted" platforms.

In this master thesis we consider the gap between software-only attacks, and high-effort hardware attacks that directly target the TPM chip itself. Our focus is on simple, low-budget hardware attacks. We claim that current protection mechanisms of typical Trusted Computing enabled platforms are insufficient to defend even against these simple hardware attacks. To prove this claim we present several novel hardware attacks against Trusted Computing enabled platforms.

### Kurzfassung

Trusted Computing ist ein technischer Ansatz zur Lösung der komplexen Frage, ob ein Computer und die darauf laufende Software vertrauenswürdig ist, oder nicht. Zur Beantwortung dieser Frage stellt Trusted Computing Mechanismen bereit, die es ermöglichen einen Computer entweder lokal, oder aus der Ferne, zu attestieren. Die technische Umsetzung dieses Attestierungsmechanismus basiert auf einer Kombination von Firmware, Software und dem Trusted Platform Modul (TPM).

Eine weitverbreitete Annahme zur Sicherheit von Trusted Computing Plattformen erlaubt es Angreifern ledligich Software-Attacken durchzuführen, während selbst einfachste Hardware-Attacken ausgeschlossen werden. Ein fundamentales Problem dieser Annahme ist, dass vorausgesetzt wird, dass sich alle Beteiligten, also auch die Angreifer, an die Regeln halten.

Daraus ergibt sich eine paradoxe Situation: Auf der einen Seite behaupten Trusted Computing Befürworter, wie die Trusted Computing Group (TCG), dass Hardware-Angriffe aus dem Bedrohungsmodell ausgeschlossen sind. Auf der anderen Seite werden Trusted Platform Module unter hohem Aufwand gegen Hardware-Angriffe und Manipulationsversuche abgesichert. Daraus resultieren Trusted Computing Plattformen, die sehr stark gesicherte kleine Hardware-Sicherheitsmodule, die Trusted Platform Module, einsezten um weit offene Plattformen abzusichern.

In dieser Diplomarbeit befassen wir uns mit der Lücke zwischen reinen Software-Angriffen und sehr aufwändigen Hardware-Angriffen, welche sich direkt gegen den TPM-Chip richten. Unser Augenmerk liegt auf einfache Hardware-Angriffe, die mit geringem Ressourcenaufwand durchführbar sind. Wir stellen die These auf, dass derzeitige Schutzmaßnahmen die auf typischen Trusted Computing-fähigen Plattformen implementiert sind nicht ausreichen, um sich selbst gegen einfachste Hardware-Angriffe zu schützen. Um unsere Behauptungen zu stützen, stellen wir in dieser Diplomarbeit eine Reihe sehr einfacher neuer Hardware-Angriffe gegen Trusted Computing Plattformen vor.

### **Statutory Declaration**

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

Place

Date

Signature

## Eidesstattliche Erklärung

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommene Stellen als solche kenntlich gemacht habe.

Ort

Datum

Unterschrift

# Contents

| Co | ontent            | S                                | ii |  |  |  |

|----|-------------------|----------------------------------|----|--|--|--|

| Li | List of Figures i |                                  |    |  |  |  |

| Li | st of ]           | fables                           | v  |  |  |  |

| Li | List of Listings  |                                  |    |  |  |  |

| Ac | know              | ledgements                       | ix |  |  |  |

| Cr | edits             |                                  | xi |  |  |  |

| 1  | Intro             | oduction                         | 1  |  |  |  |

|    | 1.1               | Overview                         | 1  |  |  |  |

|    | 1.2               | Outline                          | 4  |  |  |  |

|    | 1.3               | Related work                     | 6  |  |  |  |

| 2  | Trus              | sted Computing                   | 11 |  |  |  |

|    | 2.1               | History                          | 11 |  |  |  |

|    | 2.2               | Theory of Operation              | 12 |  |  |  |

|    | 2.3               | Criticisim                       | 14 |  |  |  |

|    | 2.4               | Platform Ownership               | 15 |  |  |  |

|    | 2.5               | Trusted Platform Modules         | 15 |  |  |  |

|    | 2.6               | Platform Configuration Registers | 16 |  |  |  |

| 3  | The               | TPM Interface Standard (TIS)     | 23 |  |  |  |

|    | 3.1               | The Initial Situation            | 23 |  |  |  |

|    | 3.2               | Localities                       | 25 |  |  |  |

|    | 3.3               | Register Interface               | 25 |  |  |  |

| Bil | Bibliography |                                                    |           |

|-----|--------------|----------------------------------------------------|-----------|

| B   | VHI          | DL Sources of the LPC Bus Emulator                 | 83        |

| A   | VHI          | DL Sources of the LPC Bus Frame Hijacker           | 79        |

| 10  | Con          | cluding Remarks                                    | 75        |

|     | 9.2          | TPMs and Embedded Platforms                        | 73        |

|     | 9.1          | Next Generation TPMs                               | 71        |

| 9   | Outl         | ook                                                | 71        |

|     | 8.4          | Physical TPM Transfer                              | 66        |

|     | 8.3          | Synthesis of Arbitrary Measurement Chains          | 65        |

|     | 8.2<br>8.2   | LPC Frame Suppression                              | 64<br>65  |

|     |              |                                                    | 63        |

| 8   |              | ond the Platform Reset Attack                      | <b>63</b> |

| 6   | D            |                                                    | 6         |

|     | 7.2          | Implementation Details                             | 59        |

|     | 7.1          | Emulating an LPC Bus Host Controller               | 57        |

| 7   | LPC          | Bus Emulation                                      | 57        |

|     | 6.6          | Using LPC Firmware Cycles Instead of Memory Cycles | 56        |

|     | 6.5          | Experimental Lab Setup                             | 52        |

|     | 6.4          | Practical Considerations                           | 51        |

|     | 6.3          | LPC Bus Memory and TPM Cycles                      | 49        |

|     | 6.2          | D-RTM Startup Sequence                             | 48        |

|     | 6.1          | Setting                                            | 48        |

| 6   | Fran         | ne Hijacking Attack                                | 47        |

|     | 5.3          | Platform Reset Attack                              | 41        |

|     | 5.2          | Classic TPM Reset Attack                           | 40        |

|     | 5.1          | Setting                                            | 39        |

| 5   |              | form Reset Attack                                  | 39        |

|     |              |                                                    |           |

|     | 4.6          | Direct Memory Access and Bus-mastering             | 36        |

|     | 4.5          | TPM-specific Extensions                            | 35        |

|     | 4.4          | Target Cycles                                      | 34        |

|     | 4.3          | Start Phase                                        | 33        |

|     | 4.2          | Properties of the LPC Bus                          | 31        |

|     | 4.1          | Trusted PC Platforms                               | 29        |

| 4   | The          | Low-Pin-Count (LPC) bus                            | 29        |

# **List of Figures**

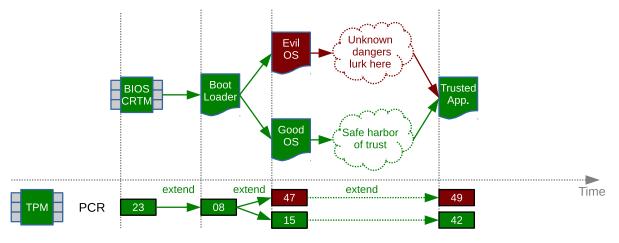

| 2.1 | Constructing a Chain of Trust [Win11]                                | 12 |

|-----|----------------------------------------------------------------------|----|

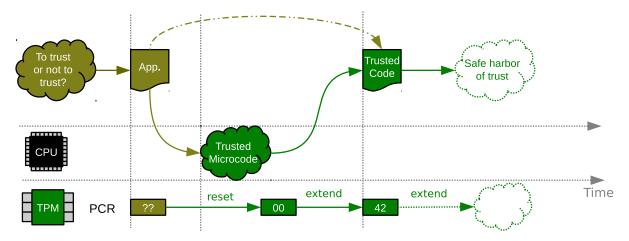

| 2.2 | Start of a Dynamic Root of Trust for Measurement [Win11]             | 19 |

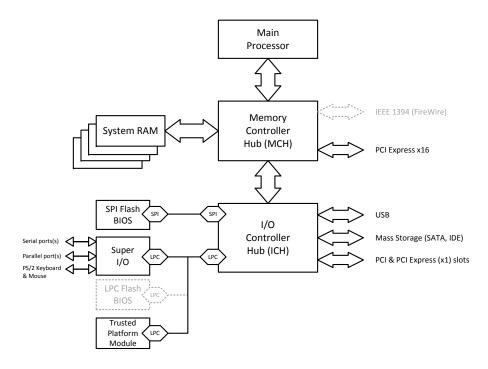

| 4.1 | Components of a Trusted Platform [WD13]                              | 30 |

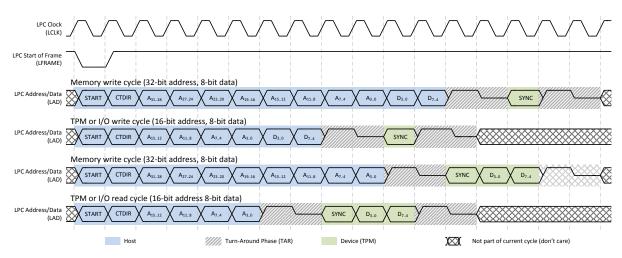

| 4.2 | LPC target Read and Write Cycle Waveforms                            | 32 |

| 4.3 | Reading the Locality 2 TPM Status Register                           | 36 |

| 5.1 | Classic TPM Reset Attack [WD13]                                      | 41 |

| 5.2 | Platform Reset Attack [WD13]                                         | 42 |

| 5.3 | Simple Platform Reset "disable" Switch [WD13]                        | 43 |

| 5.4 | Extended Platform Reset "disable" Switch [WD13]                      | 46 |

| 6.1 | TPM Interaction during D-RTM Startup [Win11]                         | 48 |

| 6.2 | TPM 1.2 TIS Registers used during D-RTM Startup [WD12]               | 49 |

| 6.3 | An LPC Memory Write Cycle compared to an LPC TPM Write Cycle         | 49 |

| 6.4 | Hijacking an LPC Memory Write Cycle [WD12]                           | 50 |

| 6.5 | Hardware setup (principle) for the LPC frame hijacking attack [WD12] | 52 |

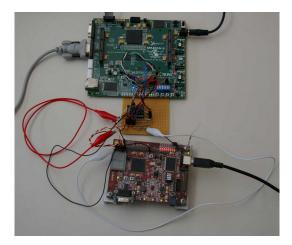

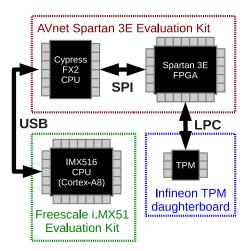

| 6.6 | Experimental Setup for the LPC Frame Hijacker [WD12]                 | 52 |

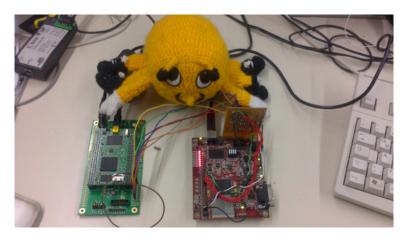

| 7.1 | Embedded Platform Setup used in [PWT12]                              | 58 |

| 7.2 | LPC Bus Emulator Hardware Setup [PWT12]                              | 58 |

| 7.3 | Format of LPC Bus Emulator Control/Status Byte                       | 60 |

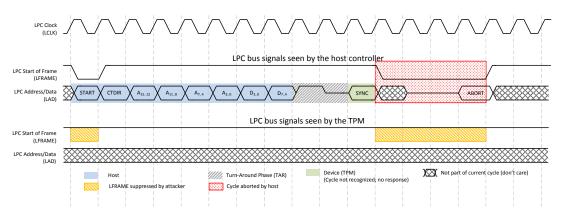

| 8.1 | LPC Frame Suppression                                                | 64 |

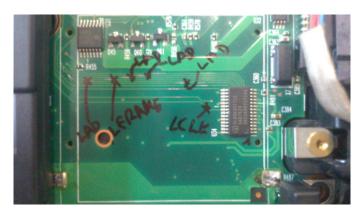

| 8.2 | TPM of an HP Compaq nx6325 Notebook                                  | 67 |

| 8.3 | TPM with Probe Wires                                                 | 67 |

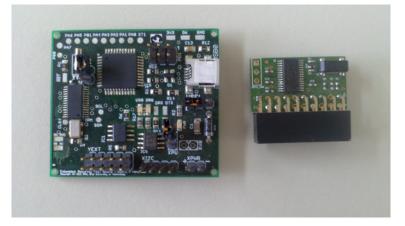

| 8.4 | Physical TPM Transfer Hardware Setup                                 | 68 |

| 9.1 | Prototype TPM v2.0 In-System Emulation                               | 71 |

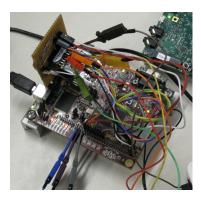

| 9.2 | The "GUSTL" Embedded Platform                                        | 73 |

# **List of Tables**

| 4.1 | START values for LPC bus cycles defined in [Int02] and [TCG05] | 33 |

|-----|----------------------------------------------------------------|----|

| 4.2 | Locality Address Mapping according to [TCG05]                  | 35 |

| 7.1 | Cycle Types supported by the LPC Bus Emulator                  | 61 |

# Listings

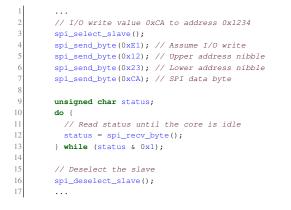

| 6.1         | Proof-of-concept D-RTM Startup Simulator Code [WD12]  | 54 |

|-------------|-------------------------------------------------------|----|

| 7.1         | Using to LPC Bus Emulator to Read Data                | 61 |

| 7.2         | Using to LPC Bus Emulator to Write Data               | 62 |

| A.1         | VHDL Source Code of the LPC Bus Frame Hijacker [WD12] | 79 |

| <b>B</b> .1 | LPC Bus Master Core                                   | 83 |

| B.2         | SPI Control Interface                                 | 89 |

# Acknowledgements

I am indebted to my colleagues at the IAIK, in particular to Kurt Dietrich (who now works at NXP Seminconductors), Martin Pirker, Daniel Hein, and Ronald Tögl, who have provided invaluable help and feedback during the course of my work. I wish to specially thank my advisor, Roderick Bloem, for his patience and support during the long time required for the genesis of this master thesis.

My initial work on simple hardware attacks against trusted computing platforms was only possible due to a research grant (257433) from the European Commission for FP7 project SEPIA. Development of the "GUSTL" embedded trusted computing test platform, and the TPM v2.0 in-system emulator discussed at the end of this thesis were made possible by a research grant (317753) from the European Comission for FP7 project STANCE.

Last but not least, without the support and understanding of my family, in particular of my late father, this thesis would not have been possible.

Johannes Winter Graz, Austria, April 2014

# **Credits**

I would like to thank the following individuals and organisations for permission to use their material:

• The thesis was written using Keith Andrews' skeleton thesis [And12].

Earlier version of several chapters of this master thesis have been published previously in a journal paper [WD13] and a conference paper [WD12]. Material from these publications is reused in this thesis under the provisions granted the LNCS Copyright and the Elsevier Author Rights (see below). Chapters that reuse text from these publications are *clearly marked once* at the beginning of the chapter. Reused figures explicitly carry a reference to their original source of publication in their caption.

#### LNCS Copyright Notice

The LNCS copyright form<sup>1</sup> states:

... Author retains the right to use his/her Contribution for his/her further scientific career by including the final published paper in his/her dissertation or doctoral thesis provided acknowledgment is given to the original source of publication. Author also retains the right to use, without having to pay a fee and without having to inform the publisher, parts of the Contribution (e.g. illustrations) for inclusion in future work, and to publish a substantially revised version (at least 30% new content) elsewhere, provided that the original Springer Contribution is properly cited ...

#### **Elsevier Author Rights**

The Elsevier Author Rights explicitly allow use in a thesis or dissertation. The journal publishing agreement for [WD13] explicitly states, that the authors retain rights for scholarly purposes, including *personal use*, without the need to obtain further permission. Personal use is defined by Elsevier<sup>2</sup> as:

... Use by an author in the author's classroom teaching (including distribution of copies, paper or electronic), distribution of copies to research colleagues for their personal use, use in a subsequent compilation of the author's works, inclusion in a thesis or dissertation, preparation of other derivative works such as extending the article to book-length form, or otherwise using or re-using portions or excerpts in other works (with full acknowledgment of the original publication of the article). ...

<sup>&</sup>lt;sup>1</sup>ftp://ftp.springer.de/pub/tex/latex/llncs/LNCS-Springer\_Copyright\_Form.pdf

<sup>&</sup>lt;sup>2</sup>http://www.elsevier.com/journal-authors/policies/open-access-policies/article-posting-policy# published-journal-article

# Chapter 1

# Introduction

"Who has begun has half done. Have the courage to be wise. Begin!"

[Horace, Epistles]

### 1.1 Overview

Desktop computers are complex systems comprising of a large number of interacting hardware, and software components. Users can customize their desktop computers to a large extent, for example by installing new software, changing the configuration of existing software, or installing new hardware components. For general purpose desktop computers there are hardly any restrictions on the extent of possible customizations: If the user does not like the operating system of his computer, he can simply replace it with an alternative operating system. Software settings, such as password policies, which may not match the preferences of the user, can typically be changed with small effort. Hardware components, like disk driver, network interface cards, or even the mainboards and processor can typically be changed. A direct consequence of this high degree of flexibility is that the number of possible system configurations, each comprising of a specific combination of hardware and software, is very large.

The situation is similar for many embedded computer platforms. Embedded system cover a broad range of diverse platforms. One end of the spectrum includes tiny microcontrollers used in washing machines, car engine control units, or similar devices, which typically only provide a very limited form of user-interaction, and limited possibilities for customization by normal users. The other end of the embedded systems' spectrum includes embedded x86-based computers that are used in industrial control systems, and multimedia oriented system-on-chip platforms that are used in set-top boxes, television sets, and mobile phones. This latter class of embedded system often provides rich user-interaction, and in particular in case of mobile phones, allows users to customize their system to a large degree.

Common to all types of platforms mentioned above is an increasing tendency to integrate remote control and management capabilities. In case of simpler systems, these capabilities may be as simple as a diagnostic port enabling read access to an on-device log buffer. In slightly more advanced systems these management capabilities can be used to modify device parameters, and to update the firmware of

1. Introduction

the entire device. Finally, complex embedded platforms, like mobile phones, can communicate with the outside world via the Internet.

Security increasingly becomes a major concern for all of these platforms. The overall complexity, and the large number of software, and hardware components, makes it extremely hard to maintain system security, over the entire lifetime of a platform. Even when all involved software and hardware components of the platform can be configured to operate securely, it is up to the user to do the required setup, and to ensure that components are kept up to date. In the worst case even a small error in either the hardware, the software, or the system configuration, can render an entire platform insecure.

**Threats and Assets** Typical assets that are found on user-centric devices like desktop computers, and mobile phones include authentication credentials, sensitive documents, privacy sensitive data, and cryptographic keys. In particular in context of embedded systems the firmware code, respectively the underlying intellectual properties, as well as the data generated by the system during operation, can be valuable assets.

Threats to these assets exist in manifold variety, and must generally be considered in context of the asset being protected, the owner of the asset, the user of the asset, and the adversary interested in the asset. Owner and user of an asset can be the same entity, for example in case of authentication credentials, where a user is interested in protecting the confidentiality of his or her password against hackers and malware. In other contexts, for example when viewing a digital rights management protected video broadcast, the situation can be more complicated: Here assets are the unencrypted video stream, and the corresponding content encryption keys. The owner of these assets is interested in protecting the confidentiality of these assets against unauthorized viewing, and copying. On the other hand the owner of the assets is also interested in ensuring availability to the users, given that the users stick to the policies set out by the owner. Apart from a content owner, and a user, there may be other stakeholders involved, such as the manufacturer of the computer hardware, or the vendor of the video playback software.

**Trusted Computing as Solution?** Failure of a computer system to appropriately defend against such threats may lead to breach of system security, and exposure of sensitive assets. In the worst case, a failure to properly defend against software threats can even lead to permanent physical damage.

Trusted Computing is one attempt to improve the situation. It aims to make guarantees about software load-time integrity, combined with a strong mechanisms to securely report the software configuration of a platform to local and to remote verifiers. To achieve this, Trusted Computing relies on a trustworthy log containing all security relevant software events that occurred since platform boot. Relevant events may include start of a program, or loading a configuration file. To protect the integrity of this log against any software attackers, a special smart-card like chip, the Trusted Platform Module (TPM) is used.

A standard assumption in common Trusted Computing settings is that attackers do not have unhindered access to the physical platform, or that they are incapable of modifying the platform hardware. Moreover, another common assumption in these settings is that the legitimate owner of a platform does not have any interest in attacking his or her own platform. These assumption on hardware attacks are summarized by a quote from David Grawrock: "... What is the definition of a simple hardware attack? [...] Going to a local electronic store, purchasing twenty dollars worth of parts, putting the parts together and defeating the [...] protection is a simple hardware attack. ..." [Gra09, Ch. 10, p.132]

At the first glance, Grawrock's definition may seem overly pessimistic, and one may expect the actual protection to be much stronger. However, on second consideration, we can find valid valid arguments, such as previously known attacks discussed in Section 1.3, that let even this definition shine in a very optimistic light.

We claim that current general-purpose Trusted Computing platforms lack a *verifiable and tamperproof* hardware binding between their Trusted Platform Module, and the remaining platform. Furthermore, we claim that the absence of this kind of secure binding opens the platform for man-in-the-middle attacks by local hardware attackers. To prove these claims, we develop variants of simple hardware attacks which are based around the man-in-the-middle idea. We take this as motivation to formulate three research questions, which we will try to answer in this master thesis:

- 1. Is it reasonable to assume that current trusted desktop computers can withstand simple hardware attacks according to the definition above?

- 2. Can we find attacks which are covered the definition above? What can be achieved by increasing the amount of resource available by raising to 15€ budget by one, or two orders of magnitude?

- 3. To whom would such attacks be a threat? Who, apart from curious master students, would be the attacker? What would be the assets?

Trusted Computing has received serious criticism right from its very beginning, for both, its technical realization, and its potential impact on users. Three of the main points of criticism brought up by security researchers were threats to privacy, threats to the freedom of users, and threats to the security of assets, software, and hardware. Within the scope of this master thesis, the former two types of threats will only receive a very brief treatment for sake of completeness. The main focus concentrates on threats to the security of software and hardware comprising a Trusted Computing enabled platform. The goal of this master thesis is to discuss technical aspects Trusted Computing, while trying to keep a neutral view on non-technical aspects.

**Selecting a Suitable Attack** The simple hardware attacks that are presented in this master thesis can be classified by their impact on platform security, and their implementation complexity. We implicitly assume that the platforms we are dealing with have their Trusted Platform Module soldered to the platform mainboard. Therefore, minimizing the hardware modifications required to perform an attack is always an implicit goal.

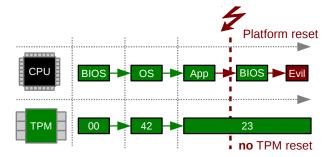

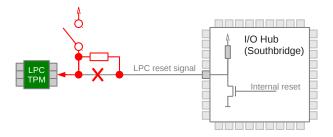

The existing classic TPM reset attack (cf. **??**) is the basis for our platform reset attack that is discussed later in Chapter 5. The classic TPM reset attack does not require any permanent changes to the platform, and allows attackers to exercise full control over large parts of the state measurements recorded in the Trusted Platform Module. It enables the attacker to construct arbitrary measurements chains from scratch, subject to restrictions imposed by the TPM and platform hardware. Our platform reset attack from Chapter 5 uses a man-in-the-middle style approach to suppress certain bus signals. It requires a small, permanent modification to the trusted platform, and enables the attacker to boot the platform into a trusted platform state, freeze the measurements recorded inside the TPM, and then reboot the platform into an untrusted state, while the old measurements are retained.

The bus hijacking that we discuss in Chapter 6 uses a similar man-in-the-middle style approach to actively manipulate a single bus signal. The hijacking attack requires a small, permanent modification to the trusted platform. This attack allows the attacker to modify parts of the state measurements recorded inside the TPM, which can not be changed using the classic TPM reset attack. Our attack can be combined with the classic TPM reset attack, to create arbitrary measurement chain from scratch, given that the platform is compatible with the bus hijacking attack.

Use of an LPC bus emulator, as discussed in Chapter 7, enables much more powerful attacks. Instead of relying on small hardware modifications, which does *not* involve removal of the TPM from the platform, the attacker now can remove the TPM from the original trusted platform. In Chapter 8 we discuss how this capability can be used to construct arbitrary measurement chains from scratch. Moreover we show how a TPM, and thus the identity and state of its platform, can be physically moved from a running trusted platform to an untrusted LPC bus emulator.

Potential attackers can choose the most appropriate attack from several possibilities: If no permanent hardware modifications are desirable, the attacker may choose the classic TPM reset attack. When the classic TPM reset attack is not powerful enough, the attacker can combine the classic TPM reset attack with our frame hijacking attack. Alternatively the attacker can go for our platform reset attack, if only small modifications to the platform are desired, and if repeatedly booting the platform into a trusted state is easy.

If neither the frame hijacking attack, nor the platform reset attack are suitable, the attacker can always physically remove the TPM from the platform. This opens the possibility of using an LPC bus emulator to create arbitrary fake measurement chains from scratch. Alternatively the attacker can apply our physical TPM transfer attack to bring a platform into a trusted state, and then to perform arbitrary manipulations with the TPM measurements, without further involvement of the trusted platform.

### 1.2 Outline

The backbone of this master thesis is formed by two of our publications [WD13; WD12] on simple hardware attacks against Trusted Platforms that I authored as primary author. Several chapters of this master thesis are based in larger parts on the text found in these two publications.

The remainder of this master thesis is structured into two major parts. The first part, consisting of Chapters 1 to 4, establishes the background and the embedding of this work in the context of related work. The second part, consisting of Chapter 7 to 10, discusses the contributions of this master thesis. At the end of the second part we give a conclusion for this master thesis, point to (ongoing) further research, and try to answer the three research questions formulated earlier.

Chapter 1 briefly motivates the work in this master thesis and discusses the embedding of this work in the context of related work.

Chapter 2 discusses Trusted Computing, as understood by the Trusted Computing Group (TCG), and gives a brief overview of the primitives relevant to this work. The description of these Trusted Computing primitives is strongly driven by the attacks discussed in later sections, and omits details, such as key hierachies or migration, that are not directly relevant to this work.

Chapter 3 describes the *TPM Interface Standard* (TIS) that is used for communication between the Trusted Platform Module and its host platform. This chapter only discusses the interface protocol, without going into details of bus specific bindings.

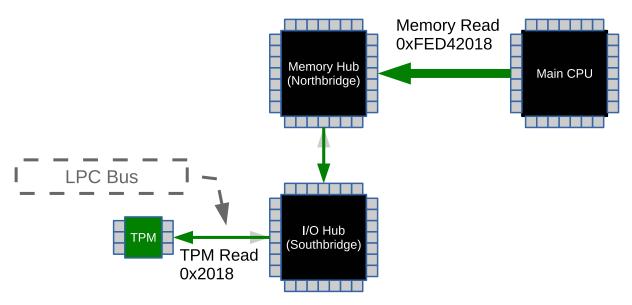

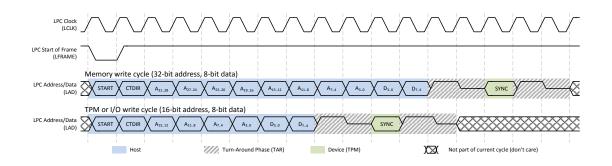

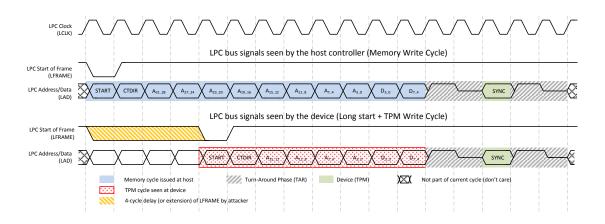

Chapter 4 discusses the Low-Pin-Count (LPC) bus that is currently used on most x86-based platforms to connect the Trusted Platform Module to the platforms I/O hub (Southbridge), and thus to the main processor. A key part of this chapter is the bus specific binding between the TPM TIS protocol and the Low-Pin-Count bus.

Chapter 5 introduces a simple hardware attack with close relation to the well-known *TPM reset attack*. The existing TPM reset attack breaks the chain of trust by resetting the TPM without resetting the platform, while the attack discussed in Chapter 5 aims to reset the host platform without resetting the TPM. This apparently small difference has a number of significant implications in practice, which are discussed in Chapter 5.

Chapter 6 presents a combined hardware and software attack that allows simulation of dynamic roots of trust, starting from an untrusted platform states. On the hardware side this attack exploits different length LPC bus transactions, combined with an FPGA-based *bus hijacking* device.

Chapter 7 presents an FPGA-based device that provides functionality to emulate the LPC bus host bridge found on typical x86 architectures.

Chapter 8 discusses simple hardware attacks, that extend beyond the reset attacks discussed earlier. The first part of this chapter investigate the suppression of framing signals on the LPC bus, to selective jam TPM communication. The second part of Chapter 8 discusses how the LPC emulator from Chapter 7 can be used to synthesize arbitrary measurement chains from scratch. The final part of Chapter 8 combines these results into a procedure for physically transferring a TPM between two platforms, without losing its current state.

Chapter 9 summarizes ongoing research, which was not yet concluded at the time of this writing, and gives an outlook to potential further research. The first part of Chapter 9 discusses work on the upcoming TPM 2.0 generation, and summarizes preliminary results. The second part of Chapter 9 summarizes preliminary results on trusted computing for embedded systems.

Finally, Chapter 10 concludes this master thesis.

## 1.3 Related work

Within this master thesis we restrict scope of our discussion to trusted platforms that build upon principles outlined by the Trusted Computing Group, and that use Trusted Platform Modules (TPMs) as their hardware anchor of trust. Alternative system-level approaches to building trusted platforms, such as ARM TrustZone [AF04], are out of scope for this master thesis.

**Software Attacks** Trusted Computing platforms are, in principle, susceptible to the same classes of software attacks as any standard computer platform without Trusted Computing. The architecture proposed by Trusted Computing Group does not explicitly require any special protection against buffer overflows, integer overflows, heap overflows, return-into-libX attacks, or return-oriented programming. We omit an explicit discussion of these standard attacks here, and concentrate on software attacks that specifically target Trusted Computing platforms in the remainder of this paragraph.

Several system-level software attacks against Trusted Platforms have been proposed in literature. In his paper on the OSLO boot-loader Kauer [Kau07] considers problems with malicious boot-loaders, BIOS firmware, and a software-only reset attack for version 1.1 TPMs from a particular vendor.

Kauer investigated a number several Trusted Computing enabled open-source bootloaders, including two variants of the well-known GRUB bootloader, and found discrepancies in the ways of how, and when parts of the boot-loaders, and the loaded kernel images were measured. One issue that appeared in some of the boot-loaders was to load the image twice, the first time for loading into system memory, and the second time for hashing into a PCR. According to Kauer's results [Kau07] this creates an exploitable time-of-check time-of-use (TOCTOU) vulnerability. To exploit the vulnerability, the attacker has to replace the kernel image on the boot medium between the two load operations, which is easily doable if the kernel is loaded via a network.

The BIOS firmware attack discussed by Kauer [Kau07] exploited a design weakness in the BIOS update mechanism of his target platform to flash a modified BIOS firmware image. This allowed Kauer to effectively disable the static root of trust for measurement in his BIOS, by patching the TPM transmit function in the BIOS firmware image, and flashing it to his test platform.

In addition to the hardware TPM reset attack, Kauer [Kau07] describes an implementation error of certain v1.1 TPM chips from a well-known vendor. By accident the vulnerable v1.1 TPM chips can be reset by malicious software. To trigger this reset it is sufficient to write a special value to a control register of the affected v1.1 TPM. The effects of this software attack on the TPM are similar to the hardware TPM reset attack discussed later. The notable difference to the hardware TPM reset attack is, that the vulnerable v1.1 TPMs can be reset by software with root access, without requiring the attacker to be physically present at the site where the victim platform is located.

In [DEG06] Duflot demonstrated a software attack, based on system management mode (SMM) BIOS vulnerabilities, against OpenBSD and NetBSD systems. Duflot's software attack took advantage of the graphic drivers of the vulnerable operating system to inject malicious code into a special region of system memory that holds the BIOS firmware code executing in system management mode. This system management code executes in parallel to the normal operating system, and is often responsible for low-level tasks, such as controlling the speed of the CPU's cooling fan. System management mode code runs

with elevated privileges, and can control parts of the platform, where even a normal operating system kernel has no access to. Duflot's software attack does not directly try to attack the measurements held inside a TPM. Nevertheless, it is a good starting point for compromising roots of trust. Certain platforms implement parts of their BIOS flash write-protection unlock code in system management mode firmware, thus potentially enabling an attacker to reflash the BIOS, even when proper digital signature verification is implemented for BIOS update images.

A practical software attack against Intel Trusted Execution Technology was shown by Wojtczuk and Rutkowska in [WR09a]. Later, Wojtczuk et al. [WRT09] presented a second related software attack against Intel TXT, using a different attack path. Both attacks exploit implementation weaknesses in the Authenticated Code Modules used by Intel TXT to initialize its dynamic root of trust for measurement. These Authenticated Code Modules are digitally signed by Intel, to ensure the integrity of the dynamic root of trust on Intel TXT platforms. The software attacks by Wojtczuk and Rutkowska exploit weaknesses in these pieces of trusted code, and enable software attackers to create fake dynamic roots of trust. The team around Rutkowska and Wojtczuk reported a couple of other software attacks with implications on trusted platforms, including hypervisor subversion [RT08; RW08] attacks and system management mode BIOS exploits [WR09b].

Software attacks can only be used to attack a subset of the measurement values stored inside the platform configuration registers of current generation v1.2 TPMs. The reason for this limitation is linked to introduction of localities in the v1.2 TPM specification, and to locality restrictions introduced alongside. Localities will be discussed in greater detail later. For now it is sufficient to know that a certain locality is not directly accessible by any software on the platform. This special locality can only be used be trusted CPU microcode during startup of a dynamic root of trust

None of the software attacks discussed above are able to fully control *all* values that are to be measured into platform configuration registers of a v1.2 TPM. The methods discussed by Kauer [Kau07] can only be used to measure arbitrary data into platform configuration registers that are *not* subject to locality restrictions.

The attacks by Wojtczuk and Rutkowska [WR09a; WRT09] can control data measured into locality restricted platform configuration registers *except* for the measurement of the (vulnerable) Authenticated Code Module that is created by trusted CPU microcode.

In theory an adversary could attempt create malicious CPU microcode. Such an adversary would likely need access to unpublished internal details of the CPU, and to the cryptographic keys required for signing the crafted CPU microcode. At the time of this writing we are not aware of any published results on successfully creating such evil CPU microcode for state of the art x86 CPUs.

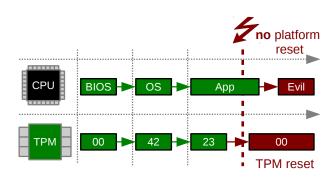

**Simple Hardware Attacks** Hardware attacks against Trusted Computing have been discussed publicly for an extended period of time. Probably the earliest publicly known active hardware attack against TCG-style trusted computing platforms is the *TPM Reset Attack*. This attack has been described independently by Kauer [Kau07] and by Sparks et al. [Spa+].

The principle behind the TPM reset attack is simple but powerful: Assuming that a Trusted Platform Module can be somehow tricked into performing a hardware reset *independently* of its host platform, it should be possible to reset the TPM and extend arbitrary fake measurement events into the TPM. The

1. Introduction

remaining platform would ideally remain unaffected.

Due to the implementation of the platform reset signal on typcial desktop computer, it is in principle possible to generate a fake reset condition by grounding the reset pin of the TPM. The video<sup>1</sup> by Sparks, and the related technical report [Spa07], clearly illustrates how easily the TPM reset attack can be mounted in practice.

One practical disadvantage of the original TPM reset attack is that other devices on the attacked bus, such as embedded controllers for power management and fan control, are affected by the fake reset as well. Depending on the exact design of the victim computer this can become an issue in practice. One problem we encountered while trying to reproduce the TPM reset attack in our own lab setup, was that PS/2 keyboard controllers did not always recover from the fake reset, leaving us with a system that was no longer accessible locally. A second problem we encountered was, that certain (newer) motherboards tended to immediately power off the entire platform on a fake reset, likely as a measure to prevent damage due to high current spikes caused by the short-circuit. The video by Sparks mentioned above shows similar problems, like stopping of the CPU fan, when the reset attack is performed.

The *locality* mechanism of v1.2 TPMs mentioned earlier provides a partial mitigation of the TPM reset attack, as it prevents fake measurements into platform configuration registers intended for use by dynamic roots of trust. Special boot-loaders, like the OSLO boot-loader presented by Kauer [Kau07] make use of special x86 processor extensions to set up a dynamic root of trust. As part of this setup process trusted CPU microcode produces an initial good measurement in a locality protected platform configuration register. Such measurements can not be reproduced with the TPM reset attack only.

Kursawe et al. [KSP05] pursued a different approach and passively listened to the communication between a (version 1.1) TPM and its host platform using a logic analyzer. One of their major observations was, that the protocols used by version 1.1 TPMs do not include sufficient cryptographic meausres, to protect the confidentiality of data exchanged over the bus.

In particular Kursawe et al. [KSP05] noted that, at least for version 1.1 TPMs, the *unsealing* command does not use any encryption, when transferring decrypted secret data from the TPM to the main processor. In response, the Trusted Computing Group added support for optionally encrypting the unsealed data returned by this command in version 1.2 of the TPM specification. To derive the required encryption keys, both the TPM and the software running on the main processor need a shared secret. Additionally *transport sessions* were introduced with in v1.2 TPMs, to enable establishment of trusted end-to-end channels between the TPM and the software running on the host processor. Transport sessions use a dedicated transport session command that accepts encrypted TPM commands as input, and produces encrypted TPM responses as output. To setup the session keys for a transport session, the TPM and the software on the host processor typically need a shared secret. We succeeded in reproducing the experiments discussed by Kursawe et al. [KSP05] in our own lab setup for the ETISS 2009 Educational Event<sup>2</sup>.

In a chapter of his dissertation [Sch12] Schellekens discusses various hardware attacks against Trusted Platforms, and refers to our work on LPC bus manipulation [WD13; WD12], and our experimental results [Win09] with passive LPC bus monitoring. Similar variantes of the platform reset attack discussed

http://www.cs.dartmouth.edu/~pkilab/sparks/

<sup>&</sup>lt;sup>2</sup>Our results can be found at [Win09]

#### 1.3. Related work

later in this master thesis were first discussed independently in our journal paper [WD13] and in the dissertation of Schellekens [Sch12].

Although the idea of attacking Trusted Platforms by attaching malicious devices, like micro-controllers, to an LPC bus has been around for several years<sup>3</sup> there exists relatively little published work on actual implementations of such devices targeting a TPM. Apart from the sources mentioned above, we are not aware of any practical implementations, apart from our own results, of malicious devices that specifically target the Trusted Platform Module on an LPC bus.

Passive LPC bus sniffing attacks, as discussed by Kursawe et al. [KSP05], are of limited use on v1.2 TPMs. The limitations are caused by improvements to the TPM unseal command, and the availability of transport sessions. Trusted software can, in principle, complicate the task of an attacker if at least one secure storage location is available for storing the required shared secrets. Arguably availability of a secure storage alleviates the need for a trusted platform module, while on the other hand absence of secure storage can lead to a chicken-and-egg situation, with respect to the shared key. Nevertheless, our own results [Win09] on passive LPC bus sniffing were crucial for implementing, and debugging, the bus modification attacks discussed in the remainder of this master thesis.

When applied against v1.2 TPMs, the TPM reset attack introduced by Kauer [Kau07] and by Sparks et al. [Spa+] suffers from similar limitations as the software attacks discussed earlier. Due to the restrictions on software access to certain TPM localities, an adversary can only control platform configuration registers that are used by the static root of trust. Platform configuration registers that are designated for use by a dynamic root of trust have locality constraints in place that thwart software attempts to measure fake data after a successful TPM reset attack.

Our work from [WD13; WD12] forms the backbone of this master thesis. We directly aim at the implementation of locality protection of v1.2 TPMs on the LPC bus. We build upon passive LPC bus sniffing techniques, and additionally allow active modification of a single bus signal. This enables us to circumvent the locality protection, and to allow *software on the victim machine* to simulate startup of am *arbitrary* dynamic root of trust. One primary design criteria for our simple bus modification attacks from [WD13; WD12] is to keep the hardware modifications to the victim platform as small as possible, and to ensure that the platform remains fully functional when no attack is in progress.

**Lab Attacks** At level of physical chip security Tarnovsky showed at the Black Hat 2012 conference [Tar10] that a TPM chip can be reverse engineered, and that its secrets can be extracted, by a knowledgeable adversary with sufficient resources.

Attacks similar to Tarnovsky's attack, which require access to highly specialized equipment like electron microscopes, are out of scope for this master thesis. Our focus is on low-budget and low-resource attacks that can by any motivated adversary with basic electronics knowledge.

# **Chapter 2**

# **Trusted Computing**

"What trusted computing provides is a way to understand the current state of a platform, have some entity evaluate the state, and then make a decision whether the platform is appropriate for the current job."

[David Grawrock, The Intel Safer Computing Initiative]

This chapter discusses the principles of Trusted Computing, as proposed by the Trusted Computing Group (TCG). The informationsummarized in this chapter is based on the TCG's documents on architecture of Trusted Platforms[TCG07a], on the Trusted Platform Module[TCG07d; TCG07c; TCG07b] and on the books by Grawrock[Gra09; Gra06].

#### **Declaration of Sources**

This chapter is based on and reuses material from the following sources, previously published by the author:

- Johannes Winter and Kurt Dietrich. "A Hijacker's Guide to Communication Interfaces of the Trusted Platform Module". In: *Computers & Mathematics with Applications* 65.5 (2013), pages 748–761. ISSN 0898-1221. doi:10.1016/j.camwa.2012.06.018

- Johannes Winter and Kurt Dietrich. "A Hijacker's Guide to the LPC Bus". In: *Public Key Infrastructures, Services and Applications*. Edited by Svetla Petkova-Nikova, Andreas Pashalidis, and Günther Pernul. Volume 7163. Lecture Notes in Computer Science. Springer Berlin / Heidelberg, 2012, pages 176–193. ISBN 978-3-642-29803-5. doi:10. 1007/978-3-642-29804-2\_12

References to these source are not always made explicit.

## 2.1 History

Initially the Trusted Computing Group started as an industry consortium called *Trusted Computing Plat*form Alliance (TCPA), and later was reorganized into its current form as *Trusted Computing Group* (TCG) (cf. Berger [Ber05]). At the time of this writing, the homepage of the  $TCG^1$  lists 12 active workgroups. Each of these workgroups is dedicated to a specific area related to the Trusted Computing Groups' view of what Trusted Computing should be. The topics include Trusted Platforms of varying type and size, infrastructure and architecture aspects, software stacks, Trusted Platform Modules, trusted storage and networking components, and virtualization. Given the scope and number of TCG workgroups, it becomes clear that Trusted Computing aims to be a security technology addressing platforms and their surrounding infrastructure as a whole.

## 2.2 Theory of Operation

The core idea of TCG-style Trusted Computing is to *measure* any events, like the start of a software components, which may affect the trustworthiness of the overall platform. Measurements in general include the type of event (e.g. start of a software component) being measured, combined with additional meta-data (e.g. cryptographic hash of the software component being started) describing the event.

This idea can be applied to produce a measurement log, which contains all events measured since the platform was booted, assuming that an initial *static root of trust for measurement* capable of performing an initial trustworthy measurement exists on the platform. The order of measurements in this log is important, as it reflects the temporal sequence of events. Any currently running *trusted* software component must ensure that it measures the next (potentially untrusted) component *before* executing it. This strategy implicitly creates a *chain-of-trust*, which starts at the *static root of trust* and extends over the measurements of trusted components in the measurement log. Measurement of the components does *not* automatically imply any kind of policy enforcement, such as rejecting software without a valid digital signature, or refusing to start malware.

Figure 2.1: Constructing a Chain of Trust [Win11]

The invariant maintained in the chain of trust is that every component is measured by its parent, before execution. This way untrusted components can not lie about the fact that they have been executed, as there always will be a trusted measurement of the untrusted component. Figure 2.1 illustrates how a chain of trust can be constructed using this invariant. Both execution paths shown in the figure start with

<sup>&</sup>lt;sup>1</sup>https://www.trustedcomputinggroup.org/developers; April 2014

the static root of trust for measurement, labeled in the figure as BIOS CRTM<sup>2</sup>. The the two execution paths shown in the figure start in the same trusted state, and end at the same trusted application. The upper path, however, includes an untrusted component. Measurements of individual components are sent to the Trusted Platform Module, and the measurement chains recorded by the TPM are shown near the bottom Figure 2.1. Before starting untrusted components — such as the "Evil OS" in Figure 2.1 — they are always measured by their trusted parent components — such as the trusted "Boot Loader" in Figure 2.1. This measurement is recorded by the Trusted Platform Module, and leads to a different measurement chain than in a trusted case.

**Roots of Trust** In order to realize the chain of trust it is necessary to have mechanisms to create, store, protect, and report the measurement log and the underlying measurements. The architecture proposed by the Trusted Computing Group [TCG07a; TCG07d] distinguishes between different roots of trust on a fine grained basis.

The following paragraphs give an overview of the roots of trust in a TCG-style Trusted Computing platform. More details on the operations and primitives provided by the Trusted Platform Module are discussed below in 2.6. Later in 3, and 4 we concentrate on the low-level software, and hardware interfaces of Trusted Platform Modules.

*Roots of trust for measurement (RTMs)* are responsible for establishing the initial good measurements at the start of a measurement chain. Typically a Trusted Platform has one *static root of trust for measurement (S-RTM)* that resides in the platform boot firmware or BIOS. This static root of trust for measurement should be immutable, and must not be modifiable by attackers, in order to ensure that an initial good measurement can be established at platform boot.

The length measurement chains produced by static roots of trust for measurement increases with software complexity. It is, by design, not possible to remove measurements from the measurement chain. Allowing such an "unmeasure" operation would enable malicious software to hide the fact that it had been started, which directly contradicts the basic idea of Trusted Computing. Long measurement chains are much harder to deal with by software that needs to attest the trustworthiness of a platform, based on measurement logs.

Newer platforms include a *dynamic root of trust for measurement (D-RTM)* that allow the running system to transition from an arbitrary software state into a well defined trusted state. The operations performed during start of the dynamic root of trust for measurement are similar to a special kind of software reset of the platform, combined with discarding parts of the measurements. Dynamic roots of trust require special support from the underlying platform, firmware and processor. Special boot-loaders, like the OSLO boot-loader by Kauer [Kau07], and operating system extensions, like the *Flicker* system by McCune et al. [McC+08] can take advantage of dynamic roots of trust.

Measurements produced by the root of trust for measurement must be protected against manipulation by malicious software. The challenge here is that measurement logs can, potentially, become infinitely large if the platform is never reset in case of a static root of trust, or the dynamic root of trust is never restarted. The TCG architecture addresses this problem by using chained cryptographic hashes as integrity protection for the entire measurement log. This way, it suffices to store integritycheck values of

<sup>&</sup>lt;sup>2</sup>Core Root of Trust for Measurement

the measurement log inside special shielded locations, which form the *root of trust for storage (RTS)*, while the actual measurement log can be kept in normal (unprotected) memory. On current Trusted Platforms, the shielded locations forming the *root of trust for storage* are always the Platform Configuration Registers of the Trusted Platform Module.

The values protected by the *root of trust for storage* reflect the current software state of the Trusted Platform: The measurement log contains the measurements that were produced by trusted software, since the platform was rebooted, respectively since the dynamic root of trust for measurement was started. To protect the integrity of the measurement log, chained cryptographic hashes of the message log are stored in the Platform Configuration Register, safe from attacks by malicious software, inside the Trusted Platform Module.

The last root of trust considered here<sup>3</sup>, the *root of trust for reporting (RTR)*, provides functionality to report the software state of the platform. On current Trusted Platforms, the shielded locations forming the root of trust for reporting is implemented inside the Trusted Platform Module, and can be accessed using special "seal" and "quote" commands, which are briefly discuss below in Section 2.6.7, and Section 2.6.5. The "seal command basically allows local users to cryptographically "seal" secrets to a given software state. The "quote" command enables the local platform to produce a digitally signed receipt vouching for the integrity of the measurement log that can be verified by remote users.

### 2.3 Criticisim

The "trusted platform" concept proposed by the TCG, and its predecessor the *TCPA*, was severely criticized as threat to the self-determination and freedom of platform users. Ross Anderson [And02] sketched a rather negative vision in context of Digital Rights Management (DRM) systems and of open-source software. The scenarios discussed in Anderson's paper depict a situation, where the choice of (trusted) hardware platform and installed software is imposed onto the users by large companies. The worst case fear in Andersons paper is, that any open-source software development could be killed by *TCPA*-style Trusted Platforms. Similar criticism and fears were shared by others. For example Stallman [Sta10] went to the extend to use the term *treacherous computing* instead of *trusted computing*, based on the reasoning that:

"Treacherous computing" is a more appropriate name, because the plan is designed to make sure your computer will systematically disobey you. In fact, it is designed to stop your computer from functioning as a general-purpose computer. Every operation may require explicit permission. [Sta10, p.205]

Proponents of Trusted Computing point out that the use of TPM and Trusted Computing functionality is voluntary and under the strict control of the user[Gra09; Gra06; TCG07a]. Actually the trusted platform module provides a complex set of commands and states related to activation, enablement and assignment of ownership. From the point of view of the platform owner, these functions indeed allow a high degree of control of the Trusted Computing function which should be enabled on the platform.

$<sup>^{3}</sup>$ Additional roots of trusts that where proposed by the TCG for mobile systems (e.g. root of trust for verification, root of trust for enforcement) are out of scope here.

## 2.4 Platform Ownership

One of the main points of disagreement between proponents, and opponents of Trusted Computing is the question of who *owns* or *controls* a platform. For a desktop computer used at home, the expectation might reasonably be, that the owner of the platform, the owner of the TPM and the user of the platform are the same person. For desktop computer used in an office the situation can be significantly different: Here the owner of the platform might be the company, the manager of the platform might be an IT department, and the user of the platform might be an employee.

The TCG architecture considers these different ownership situations in [TCG07a, p.23]. Three possible deployment scenarios for Trusted Platforms are discussed in [TCG07a, p.23]:

- **Consumer Owned Platforms** correspond to the home computing example discussed above. Platform and TPM management is under full control by the user (consumer).

- **IT-Owned and Managed Platforms** correspond to the corporate computing example discussed above. The platform and TPM are managed by a central authority, for example an IT department. This scenario envisions periodical monitoring of the platform for compliance with IT policies.

- **Consumer Owned Platforms with Outsourced Management** are a hybrid variant between user and third-party management of the platform. The scenario outlined in [TCG07a] assumes an external (outsourced) IT service provider, who has a service contract with the user. The IT service provider takes ownership of the TPM before the platform is shipped to the user. The user can decide if the TPM should be activated during normal platform operation. Interaction with the IT service provider requires the TPM to be (temporarily) activated.

This flexibility with respect to ownership is reflected in the TPM's command set (cf. [TCG07b]) by supporting separate authorization for the "owner" (TPM\_TakeOwnership command) and the "operator" (TPM\_SetOperatorAuth) of the TPM. Additionally the TPM provides a delegation mechanism that enables owners of TPM objects, like keys, to delegate certain rights, like using the key to sign data, to other users on a per-object basis.

From a Trusted Computing opponent's point of view the later two deployment scenarios are more problematic for the user or consumer, as they allow third-parties to enforce policies on the software installed on the user's platform. Such strong enforcement of software policies could prevent whistleblowers from leaking information as discussed in the examples of Anderson [And02] and Stallman [Sta10]. Similarly the consumer owned platform with outsourced management can be seen as possible instantiation of a Trusted Computing protected multimedia appliance with DRM capabilities.

## 2.5 Trusted Platform Modules

The *Trusted Platform Module (TPM)* is the primary hardware trust anchors of any TCG-style trusted computing platform. It implements the root of trust for reporting (RTR) and the root of trust for storage (RTS). Commonly TPMs for desktop usage are realized as dedicated hardware modules, either as

standalone chips, or as IP building block integrated into larger platform elements like the Southbridge<sup>4</sup> of an x86 platform. Pure software realizations<sup>5</sup> of TPMs are in principle possible, as demonstrated by Strasser's software TPM emulator [SS08; SS04] and IBM's virtual TPM approach [Ber+06; Gol+10]. Other implementations of software TPMs for use on mobile and embedded platforms, have been proposed in literature e.g. by Ekberg and Bugiel [EB09], England and Tariq [ET09], Dietrich and Winter [DW10], Winter et al [Win+12], and Winter [Win08].

This section discusses the functionality of the TPM that is relevant to the attacks discussed later in this master thesis. Most of the attacks discussed later have in common, that they focus on the link between the root of trust for measurement, which resides *outside* the TPM, and the Trusted Platform Module of the target platform. The TPM functionality discussed here is limited to the commands, and primitives that are directly relevant for the attacks discussed in this master thesis. We deliberately omit large parts the TPM command set, including ownership management, key handling, delegation, and authorization as they are not directly related our attacks, and thus can be considered as being out of scope.

## 2.6 Platform Configuration Registers

Platform Configuration Registers (PCRs) are special registers used to store the current software state of the platform. PCRs are implemented in *shielded locations* and together form the *root of trust for reporting* (RTM) inside the TPM. These registers are volatile, and take a well-defined initial state whenever the platform — or more precisely the TPM — is reset. The content of all PCRs is lost whenever the TPM is reset or powered off. There exists no command to directly set arbitrary PCRs to arbitrary user-specified values. Software can only change the content of PCRs in two restricted ways: To record a measurement, software can *extend* a PCR, via the PCR extend command discussed below. Certain special PCRs, which are mainly intended for debug purposes, can be reset under well-defined conditions using a dedicated PCR reset command.

When a dynamic root of trust for measurement (D-RTM) is started a special sequence of hardware bus transactions is initiated by trusted CPU microcode, to generate an initial good measurement in a dedicated PCR. Normal software is, at least in theory, not able to generate the special bus cycles required to signal the start of the D-RTM. Below we discuss the effects of invoking a D-RTM on the PCR values held by the TPM. Next, in Chapter 3 we analyze the low-level interface used by software drivers, and by CPU microcode, to communicate with the TPM. As part of this analysis we discuss *localities*, which are a simple mechanism that allows the TPM to identify the origin (e.g. software, CPU microcode) of requests at hardware level.

#### 2.6.1 Initial State

The initial content of a PCR at platform reset depends on its designated purpose. PCRs that are used by the static root of trust are reset to an all zeros initial value, while PCRs used by a dynamic roots of trust initially have all bits set to one. Let  $PCR_{i,0}$  denote the value of the *i*-th PCR immediatly after platform

<sup>&</sup>lt;sup>4</sup>For example on Intel ICH-10 chipsets [Int08, p.241]

<sup>&</sup>lt;sup>5</sup>Which run as "processes" on the main platform CPU, instead of being firmware embedded into dedicated security chips

reset, and let  $l_h^6$  be the fixed bitsize of a single PCR, then the initial PCR values of a typical version 1.2 TPM are given by:

$$\operatorname{PCR}_{i,0} := \begin{cases} \{0\}^{l_h} & \text{if } 0 \le i \le 16 \lor i = 23 & (\text{Static RTM}) \\ \{1\}^{l_h} & \text{if } 17 \le i \le 22 & (\text{Dynamic RTM}) \end{cases}$$

The design decision to initialize PCRs used by a dynamic root of trust to a well-defined non-zero value allows software to reliably detect if a dynamic root of trust was started since the last platform reboot, or not.

#### 2.6.2 Extend Operation

Software uses the *extend* command to measure "interesting" platform events into the Platform Configuration Registers. It is up to the software performing the measurements to define what constitutes an "interesting" event. Relevant events can for example be the start of additional software components, loading of configuration data, security relevant policy decisions, or policy violations. At TPM command-level the *extend* command makes no assumptions about data being extended into a PCR. The only restriction is that the data being extended must be encoded as a bit-string of fixed length  $l_m$ . For version 1.2 TPMs the length  $l_m$  is fixed to 160 bits by the choice of SHA-1 as the TPM's hash function. Trusted software stacks define their own mechanisms to map events to suitable bitstrings for the PCR extend primitive. The Trusted Software Stack (TSS) specified by the TCG [TCG06] defines an event data-structure which is mapped to the actual bit-string by application of a hash function.

Let  $PCR_{i,t}$  denote the value of the *i*-th PCR at time *t*, let H be the hash function<sup>7</sup> that is used by the TPM, and let  $l_m$  be a constant bitsize fixed<sup>8</sup> by the TPM specification. We assume for simplicity that all PCRs use a common global time *t* and that time increases whenever *any* PCR is extended. With || denoting the concatenation of two bitstrings, the effects of a state update at time *t* caused by extending  $PCR_i$  with a bitstring  $m \in \{0, 1\}^{l_m}$  can then be described as:

$$PCR_{i,t+1} := \begin{cases} H(PCR_{i,t}||m) & \text{if canextend}_{j,t} \land i = j & (\text{Extend the target PCR with message } m) \\ PCR_{i,t} & \text{if } \neg \text{ canextend}_{j,t} \lor i \neq j & (\text{Other PCRs are unaffected}) \end{cases}$$

$$canextend_{i,t} := \begin{cases} 1 & \text{if PCR } i \text{ can be extended (from current locality}) \\ 0 & \text{otherwise} \end{cases}$$

The new value of the PCR after the extend operation is obtained by computing the hash value over the concatenation of the old PCR value with the data to be extended. The computation of the new PCR value does not involve any TPM internal secrets. To recompute the value of a PCR it is sufficient, to know its initial value, and the sequence of measurements that were extended to reach the the current value. This is exactly the property required to protected the integrity of measurement logs. Note that the extendable<sub>*i*,*t*</sub> predicate captures the locality based PCR access restrictions discussed later n Section 3.2.

One important property of the PCR extend operation that it preserves the order of measurements in

$<sup>{}^{6}</sup>l_{h} = 160$  for TPM version 1.2

<sup>&</sup>lt;sup>7</sup>SHA-1 for TPM version 1.2

$<sup>{}^{8}</sup>l_{m} = 160$  for TPM version 1.2

the final value. Extending two distinct measurements A and B yields a different result than extending B and A. This property is required to ensure that relative order of measurements, respectively the temporal order of events leading to this measurements, in a measurement log can be protected properly.

#### 2.6.3 Software-controlled Reset

Certain special PCRs can be reset by trusted software with help of the TPM\_PCR\_Reset TPM command. Software reset of PCRs is useful for debugging trusted applications during development. Typical desktop TPMs provide one dedicated debug PCR ( $PCR_{16}$ ) that can be reset by any normal application running on the platform, without requiring any special authorization. Applications must not be able use the PCR software reset command to reset any non-debug PCRs, as doing so would compromise the chain of trust. The reset behavior of non-debug PCRs is controlled by TPM internal data-structures, which are fixed at TPM manufacturing time. In principle they can vary between TPM vendors, and even different firmware versions of TPMs from the same vendor. TPMs for desktop use typically implement the reset behavior as discussed in [TCG05], which is suitable for desktop computer systems with static and dynamic RTMs.

Let  $PCR_{i,t}$  denote the value of the *i*-th PCR at time *t* and let  $l_h$  be the bitsize of the PCR registers. Furthermore, let resettable<sub>*j*,*t*</sub> denote if the *j*-th PCR can be reset at time *t*, and let zeroreset<sub>*j*,*t*</sub> denote if the reset value of the *j*-th PCR at time *t* is all-zeros or all-ones. The effects of a TPM\_PCR\_Reset command on any PCR *j* at time *t* can be described as:

$$PCR_{i,t+1} := \begin{cases} \{0\}^{l_h} & \text{if } i = j \land \text{resettable}_{j,t} \land \text{zeroreset}_{j,t} & (\text{Reset to } 0 \times 0 \dots) \\ \{1\}^{l_h} & \text{if } i = j \land \text{resettable}_{j,t} \land \neg \text{zeroreset}_{j,t} & (\text{Reset to } 0 \times F \dots) \\ PCR_{i,t} & \text{if } i = j \land \neg \text{resettable}_{j,t} & (\text{Preserve on error}) \\ PCR_{i,t} & \text{if } i \neq j & (\text{Preserve others}) \end{cases}$$

$\operatorname{resettable}_{j,t} := \begin{cases} 1 & \text{if } j = 16 \quad (\text{Debug PCR 16 can be reset}) \\ 0 & \text{if } j \neq 16 \quad (\text{Any other PCR can not be reset}) \\ \operatorname{zeroreset}_{i,t} := 1 \end{cases}$

The resettable<sub>*j*,*t*</sub> and zeroreset<sub>*j*,*t*</sub> predicates depend on TPM internal data-structures, and are fixed at manufacturing time. For typical version 1.2 TPMs intended for use on desktop computer, the only resettable PCR should be  $PCR_{16}$ . This leads to the definitions of the resettable, and zeroreset predicates shown above.

#### 2.6.4 Invocation of a D-RTM

Dynamic roots of trust for measurement (D-RTMs) try to overcome the problems associated with long measurement chains by bringing the platform into a well-defined, trusted state, and starting a fresh (dy-namic) measurement chain. Trusted application like the OSLO boot-loader [Kau07] and the *Flicker* framework [McC+08] mentioned earlier use D-RTMs to establish fresh measurement chains after transitioning from an arbitrary platform start into a trusted platform state as part of the D-RTM invocation.

To practically realize D-RTMs special support from the TPM and the platform are needed. The TPM

has to provide a special mechanism to atomically resets a certain group of PCRs, and to perform a single extend operation to measure the new "trusted" software state. Let  $PCR_{i,t}$  denote the value of the *i*-th PCR at time *t* and let  $l_h$  be the bitsize of the PCR registers. Furthemore let and let  $l_m$  be a constant bitsize of PCR extend message and let  $m \in \{0, 1\}^{l_m}$  be the first measurement done during the dynamic RTM startup sequence. The effect of the dynamic RTM startup at time *t* can then be described as:

$$PCR_{i,t+1} := \begin{cases} H\left(\{0\}^{l_h} || m\right) & \text{if } i = 17 \\ \{0\}^{l_h} & \text{if } 18 \le i \le 22 \\ PCR_{i,t} & \text{if } i \ne j \end{cases}$$

(Reset PCRs 18-22 to 0x0000...)

It is critical for the security of D-RTMs that the special PCR measurements during D-RTM invocation can not be simulated by normal application software (cf. [Gra09]). The TPM uses a hardware-assisted mechanism, called localities, to protect against malicious applications trying to simulate fake a D-RTM startup sequences, and the associated measurements. All special PCRs involved in the D-RTM invocation sequence can neither be extended, nor reset by software. On a typical PC platform  $PCR_{17}$  is designated to receive the initial measurement done by CPU microcode. It requires the current locality to be locality 4, which should, at least in theory, only be accessible from trusted CPU microcode.

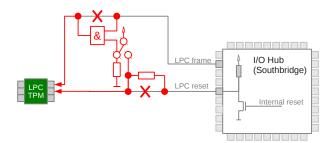

Figure 2.2: Start of a Dynamic Root of Trust for Measurement [Win11]

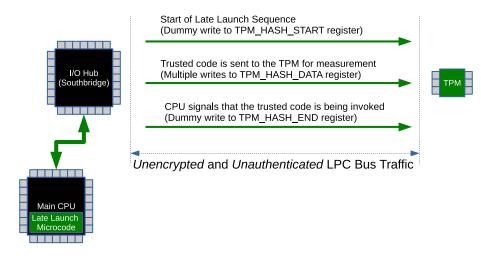

Figure 2.2 illustrates the startup process of a dynamic root of trust for measurement. To initiate the D-RTM invocation it is first necessary to load a special fragment of trusted application code into memory and to correctly setup the processor, and platform. These steps are performed while the system is still in a potentially untrusted, or unknown, system state. Once the preparation steps are complete, a special CPU instruction is used to trigger the actual start of the D-RTM startup sequence. In response trusted CPU microcode takes over control, produces the initial good measurement of the trusted application, and finally hands over the trusted application<sup>9</sup>.

For example the OSLO boot-loader, which was proposed by Kauer [Kau07] as a possible mitigation against the TPM reset attack, uses this mechanism. This boot-loader initiates a D-RTM startup sequence to create a fresh measurement chain, which starts with a piece of trusted code from the boot-loader itself. The assumption is that software can not simulate the initial D-RTM measurement. This implies that a

<sup>&</sup>lt;sup>9</sup>Depending on the CPU vendor there can be additional steps, which we omit here for brevity.

measurement of the trusted boot-loader in  $PCR_{17}$  indeed indicates that the trusted boot-loader has been started on the platform.

Our hardware attacks discussed later in Chapter 6, and Chapter 8 invalidate the assumption that *only* trusted CPU microcode can generate the low-level bus transaction needed to inform the TPM of D-RTM start.

#### 2.6.5 Remote Attestation

Remote attestation allows a trusted platform to report its software configuration state to a remote party. During remote attestation, the TPM generates a digitally signed receipt of its current PCR values, using the *quote* command. This receipt is then used as evidence to "prove" that the platform was in a given state at the time the quote blob was created.

**The Quote Operation** The central TPM command required for remote attestation is the *quote* command. In principle the quote command generates a digital signature over a special message of fixed structure. The signed message contains a set of PCR indices, a cryptographic hash over the current values of the corresponding PCRs, and a cryptographic nonce.

Let *pcrs* be a set of PCR indices of interest and let  $PCR_{i \in pcrs,t}$  be the concatenation of the selected PCR values at time t. Furthermore let n be a user supplied bit-string of fixed length as defined by the TPM specification. Finally let H be a hash-function used by the TPM. The platform state QuoteInfo<sub>t</sub>(n, {*pcrs*}) at time t can now be encoded as<sup>10</sup>:

$$QuoteInfo_t(n, pcrs) := (n || pcrs || H(PCR_{i \in pcrs, t}))$$

To produce a trusted receipt — or *quote* — of the platform state at time t the TPM signs<sup>11</sup> the encoded platform state with the private key of a key pair K, to produce a signature  $\sigma$ . With || denoting the concatenation of two bitstrings, construction of a *quote* blob by the TPM is given as:

$$m := \operatorname{QuoteInfo}_{t}(n, pcrs)$$

$$\sigma := \operatorname{Sign}_{K_{priv}}(m)$$

$$\operatorname{Quote}_{t}(K_{priv}, n, pcrs) := (m||\sigma)$$

The *quote* blob is used to give proof of the current software state of the platform, as reflected in the Platform Configuration Registers of the TPM, to a remote verifier. Freshness of the quote blob can be ensured by incorporating a verifier provided nonce value into n when generating the quote. To check the validity of a quote blob the verifier extracts the QuoteInfo structure and checks the signature on that structure using the public key of key pair K. Furthermore the verifier has to check that the software configuration described by the QuoteInfo matches the requirements.

<sup>&</sup>lt;sup>10</sup>The shown definition is simplified and omits several details of the real TPM structure for simplicity.

<sup>&</sup>lt;sup>11</sup> to RSA in TPM version 1.2

## 2.6.6 Approaches to Remote Attestation

**Attestation based on Known-good PCRs** There are two major approaches for validating the software configuration encoded in the *quote* blob at the verifier side. The first, simple approach is to keep a database of known good PCR value sets representing trusted configuration and matching them against the *quote* blobs. This simple approach requires only little communication between the prover and the verifier.

**Configuration Space Explosion** The drawback of this simple approach is that a dedicated database of known good software configurations, and an approval mechanism to add new software configurations is needed. This likely will not be a problem if the number of software components, and good software configurations is small. With growing number of components, the number of configurations that need to be approved in the database grows quickly.