Master Thesis

# Design and Implementation of Low Power Circuits for a Sensor Interface for Biological Applications

Michael Stadler

Institute of Electronics Graz University of Technology Department Head: Univ.-Prof. Dipl.-Ing. Dr.techn. Wolfgang Pribyl Advisor: Dipl.-Ing. Dr.techn. Mario Auer

% in Cooperation with Infine on Technologies Austria AG Graz, in August 2011

### Abstract

In order to connect an RFID tag with a sensor for biological applications, a sensor interface has to be implemented. The goal of the system is to be able to measure the physiologic condition, proliferation and concentration of microbiological cell structures using their impedance without having to rely on the usage of batteries. This application can primarily be used in biological laboratories as well as hospitals to detect infections such as sepsis.

Since the system is powered with an RF field, the tag, along with the sensor interface, has to have a low power consumption. The goal of this master thesis is to implement different low power circuits, which are to be used in the sensor interface. Specifically, a comparison between adaptively biased operational transconductance amplifiers (OTAs) has to be made as well as a peak detector implemented.

Given an input differential voltage, adaptively biased OTAs have the ability to increase their output current in order to follow an input signal step quickly. As soon as the difference of the input signals decreases, the output current is reduced, along with the power consumption. In order to accomplish this, a variety of approaches are analyzed. In addition, the advantages and disadvantages of a new rail-to-rail OTA are considered. The different topologies are then compared with each other using different figures of merit.

The second part of this thesis includes the implementation of three different approaches for detecting the amplitude of a sinusoidal signal. All of the topologies meet the given criteria, however, due to a smaller area as well as lower power consumption, the low leakage peak detector has been layouted to be included in the interface. To obtain the simulation results, as well as a layout, a 120 nm CMOS process has been used.

### Kurzfassung

Eine Sensorschnittstelle soll konstruiert werden, um einen RFID Tag mit Sensoren für biologische Applikationen zu verbinden. Ziel dieses Systems ist es, die Ausbreitung, Konzentration, sowie den physiologischen Zustand von Zellkulturen mittels einer Impedanzmessung zu erkennen, ohne auf die Verwendung von Batterien zurückgreifen zu müssen. Diese Applikation findet vor allem in biologischen Laboratorien Anwendung, kann aber auch in Krankenhäusern zur Detektierung von Infektionen wie Sepsis herangezogen werden.

Da das System über ein RF-Feld versorgt wird, muss der Tag und die Sensorschnittstelle energiesparend aufgebaut sein. Ziel dieser Diplomarbeit ist es, verschiedene stromarme Schaltungen zu implementieren, die in der Sensorschnittstelle zum Einsatz kommen sollen. Speziell handelt es sich hier um einen Vergleich zwischen 'adaptively biased' Transkonduktanzverstärkern (OTA) und einem Amplitudendetektor.

'Adaptively biased' OTAs besitzen die Eigenschaft ihren Ausgangsstrom bei anliegender Differenzeingangsspannung zu erhöhen, um einen Eingangssprung schneller folgen zu können. Sobald die Differenz der Eingangssignale wieder verringert wird, passt sich der Strom an um Energie zu sparen. Um dies zu erreichen werden verschiedene Lösungsansätze untersucht, sowie die Vor- und Nachteile eines neuen Rail-to-Rail Verstärkers erläutert. Die unterschiedlichen Topologien werden anhand von 'Figures of Merit' verglichen.

Für die Implementierung eines Amplitudendetektors werden drei verschiedene Lösungsansätze präsentiert. Alle Topologien erfüllen die Anforderungen, jedoch auf Grund des geringsten Platzbedarfs und Stromverbrauchs wurde schlussendlich der 'Low Leakage Peak Detector' im Layout umgesetzt. Für die Simulationen sowie das Layout wurde ein 120 nm CMOS Prozess verwendet. Ich versichere hiermit, diese Arbeit selbständig verfasst, andere als die angegebenen Quellen und Hilfsmittel nicht benutzt und mich auch sonst keiner unerlaubten Hilfsmittel bedient zu haben.

I hereby certify that the work presented in this thesis is my own and that work performed by others is appropriately cited.

Michael Stadler

## Acknowledgments

I would like to thank Univ.-Prof. Dipl.-Ing. Dr.techn. Wolfgang Pribyl for his support in enabling me to continue my studies at Graz University of Technology,

Dipl.-Ing. Dr.techn. Mario Auer, for his continued work with me throughout my master's degree as well as being the academic advisor for this thesis, and

Dipl.-Ing. Martin Wiessflecker, for his help as my thesis advisor from Infineon Technologies.

Thanks is also due to the Contactless and Radio Frequency Exploration Department at Infineon Technologies for enabling and supporting this thesis.

In addition, I would like to thank Dipl.-Ing. Stefan Gruber and Dipl.-Ing. Hannes Reinisch for their support with CAD tools,

Dipl.-Ing. Günter Hofer for always finding time to broaden my technical knowledge, and

Ing. Georg Skacel for providing a sounding board for problems and a productive source of ideas.

Last but not least, I thank my family for the support they have given me throughout my studies. I also thank Jessica Hedrick, B.B.A., for proofreading and providing encouragement.

# Contents

| 1 | Mot  | ivation                                          | 1  |

|---|------|--------------------------------------------------|----|

| 2 | Clas | s AB Operational Transconductance Amplifiers     | 4  |

|   | 2.1  | Objective                                        | 5  |

|   | 2.2  | Current Mirror OTA                               | 6  |

|   |      | 2.2.1 Basics                                     | 6  |

|   |      | 2.2.2 Implementation                             | 9  |

|   |      | 2.2.3 Results                                    | 10 |

|   | 2.3  | Class AB Current Mirror OTA: Source Degeneration | 12 |

|   |      | 2.3.1 Basics                                     | 13 |

|   |      | 2.3.2 Implementation                             | 14 |

|   |      | 2.3.3 Results                                    | 15 |

|   | 2.4  | Class AB Current Mirror OTA: High Swing Cascode  | 16 |

|   |      | 2.4.1 Basics                                     | 17 |

|   |      | 2.4.2 Implementation                             | 18 |

|   |      | 2.4.3 Variation                                  | 18 |

|   |      | 2.4.4 Results                                    | 19 |

|   | 2.5  | Flipped Voltage Follower                         | 21 |

|   |      | 2.5.1 Basics                                     | 22 |

|   | 2.6  | FVF OTA                                          | 23 |

|   |      | 2.6.1 Basics                                     | 23 |

|   |      | 2.6.2 Implementation                             | 24 |

|   |      | 2.6.3 Results                                    | 25 |

|   | 2.7  | FVF Rail-to-Rail                                 | 25 |

|   |      | 2.7.1 Basics                                     | 26 |

|   |      | 2.7.2 Implementation                             | 27 |

|   |      | 2.7.3 Results                                    | 28 |

|   | 2.8  | Adaptive Bias OTA Comparison                     | 29 |

| 3 | Peal | < Detector                                       | 32 |

|   | 3.1  | Objective                                        | 32 |

|   | 3.2  | Simple Peak Detector                             | 33 |

|   | 3.3  | Low Leakage Peak Detector                        | 35 |

#### Contents

|    |        | 3.3.1   | Implementation                 | 36   |

|----|--------|---------|--------------------------------|------|

|    |        | 3.3.2   | Results                        | 38   |

|    |        | 3.3.3   | Layout                         | 43   |

|    |        | 3.3.4   | Conclusion                     | 45   |

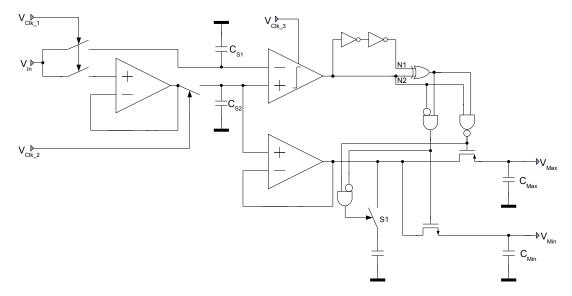

|    | 3.4    | Clocke  | d Signal Detector              | 46   |

|    |        | 3.4.1   | Implementation                 | . 47 |

|    |        | 3.4.2   | Results                        | 51   |

|    |        | 3.4.3   | Conclusion                     | 54   |

|    | 3.5    | Differe | entiator-Based Signal Detector | 55   |

|    |        | 3.5.1   | Implementation                 | 57   |

|    |        | 3.5.2   | Results                        | 60   |

|    |        | 3.5.3   | Conclusion                     | 62   |

| 4  | Cond   | clusion |                                | 65   |

| Α  | Sche   | ematics |                                | 66   |

| Bi | bliogr | aphy    |                                | 67   |

# List of Figures

| 1.1  | CellMonitor System                                       | 1              |

|------|----------------------------------------------------------|----------------|

| 1.2  | Block Diagram of the RFID Tag                            | 2              |

| 1.3  | Block Diagram of the Sensor Interface                    | 2              |

| 2.1  | Output Current Adaptively Biased OTA                     | 4              |

| 2.2  | Input Step Response                                      | $\overline{5}$ |

| 2.3  | Class A Current Mirror OTA                               | 6              |

| 2.4  | Bode Plot                                                | 7              |

| 2.5  |                                                          | 11             |

| 2.6  |                                                          | 13             |

| 2.7  |                                                          | 14             |

| 2.8  | 0                                                        | 16             |

| 2.9  | · ·                                                      | 17             |

| 2.10 | Class AB Current Mirror OTA High Swing Cascode Variation | 19             |

| 2.11 | Current Mirror OTA vs. Adaptively Biased OTA HSC 1       | 20             |

|      |                                                          | 21             |

| 2.13 | Flipped Voltage Follower and FVF Differential Pair       | 22             |

| 2.14 | FVF OTA                                                  | 23             |

| 2.15 | Current Mirror OTA vs. FVF OTA                           | 26             |

| 2.16 | Rail-to-Rail FVF                                         | 27             |

|      |                                                          | 29             |

| 2.18 | Rise Time & Energy Summary                               | 30             |

| 3.1  | Peak Detector Output Characteristics                     | 33             |

| 3.2  | 1                                                        | 33             |

| 3.3  | -                                                        | 36             |

| 3.4  |                                                          | 39             |

| 3.5  |                                                          | 40             |

| 3.6  |                                                          | 41             |

| 3.7  |                                                          | 43             |

| 3.8  |                                                          | 44             |

| 3.9  |                                                          | 45             |

| 3.10 |                                                          | 46             |

| 3.11 |                                                          | 47             |

|      |                                                          |                |

# List of Figures

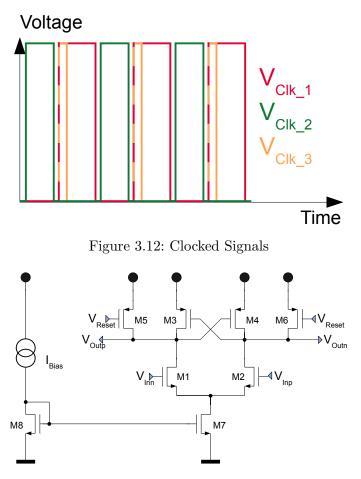

| 3.12    | Clocked Signals                                                    | 48 |

|---------|--------------------------------------------------------------------|----|

| 3.13    | Clocked Comparator                                                 | 48 |

| 3.14    | Current Starved Buffer                                             | 50 |

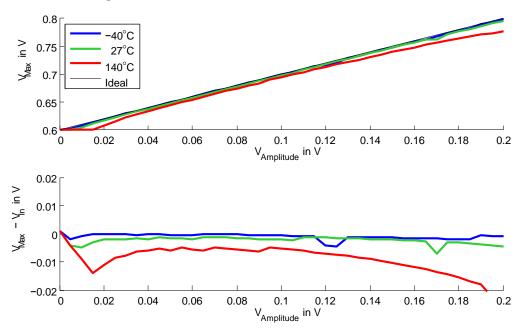

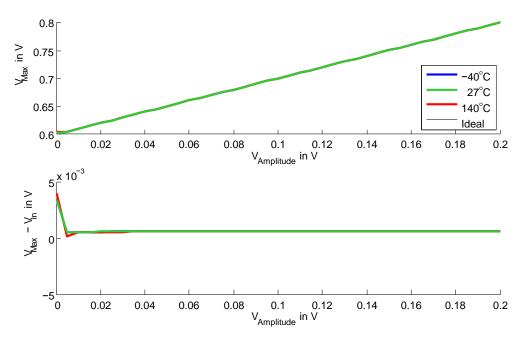

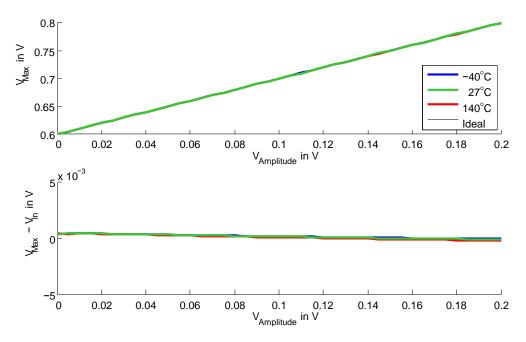

| 3.15    | CSD $V_{Max}$ : Amplitude Sweep at 1 kHz Sinusoidal Input Signal   | 51 |

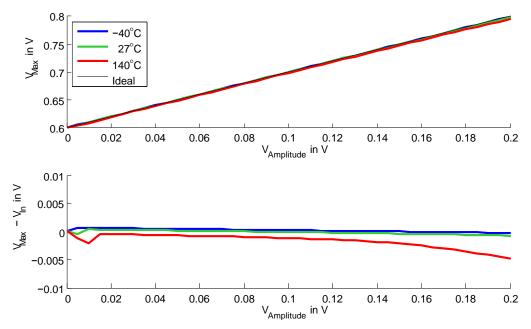

| 3.16    | CSD $V_{Max}$ : Amplitude Sweep at 10 kHz Sinusoidal Input Signal  | 52 |

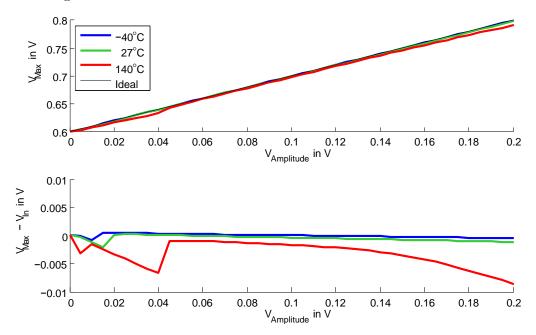

| 3.17    | CSD $V_{Max}$ : Amplitude Sweep at 100 kHz Sinusoidal Input Signal | 53 |

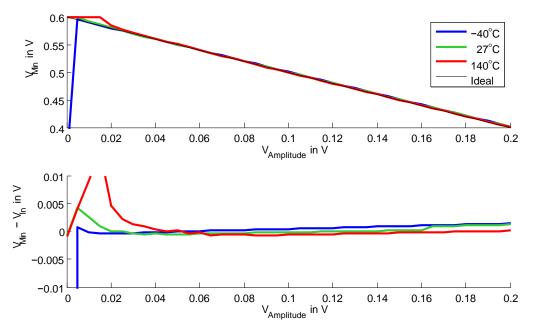

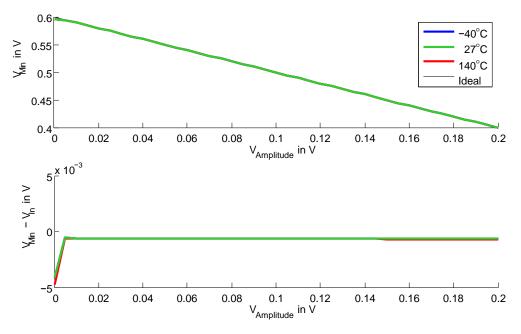

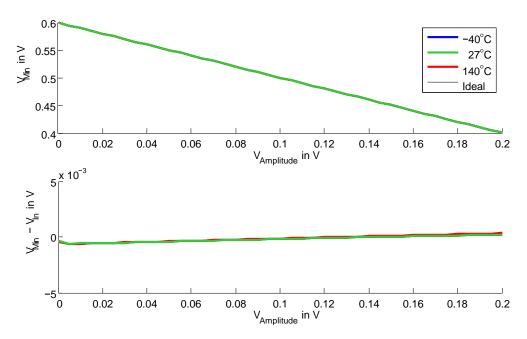

| 3.18    | CSD $V_{Min}$ : Amplitude Sweep at 1 kHz Sinusoidal Input Signal   | 54 |

| 3.19    | CSD $V_{Min}$ : Amplitude Sweep at 10 kHz Sinusoidal Input Signal  | 55 |

| 3.20    | CSD $V_{Min}$ : Amplitude Sweep at 100 kHz Sinusoidal Input Signal | 56 |

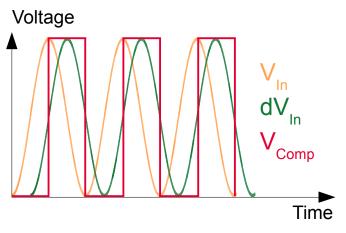

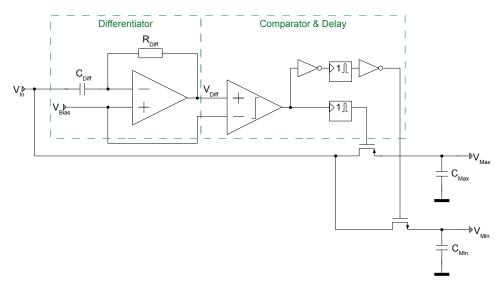

| 3.21    | Differentiator Signal Detector Principle                           | 57 |

| 3.22    | Differentiator Signal Detector Schematic                           | 57 |

| 3.23    | Differentiator Capacitance Network                                 | 58 |

| 3.24    | Comparator                                                         | 59 |

| 3.25    | Monoflop                                                           | 59 |

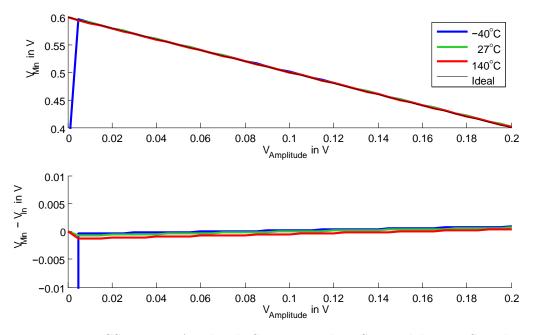

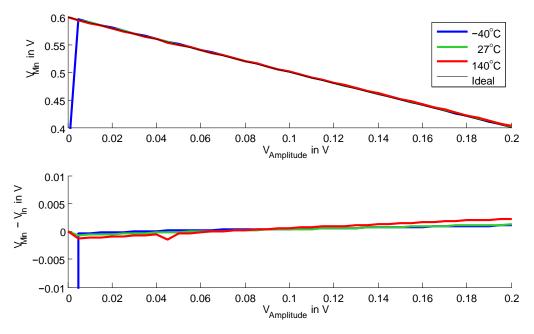

| 3.26    | DSD $V_{Max}$ : Amplitude Sweep at 10 kHz Sinusoidal Input Signal  | 61 |

| 3.27    | DSD $V_{Max}$ : Amplitude Sweep at 100 kHz Sinusoidal Input Signal | 62 |

| 3.28    | DSD $V_{Min}$ : Amplitude Sweep at 10 kHz Sinusoidal Input Signal  | 63 |

| 3.29    | DSD $V_{Min}$ : Amplitude Sweep at 100 kHz Sinusoidal Input Signal | 64 |

| A 1     | PMOS Current Mirror OTA                                            | 66 |

| * T • T |                                                                    | 00 |

# List of Abbreviations

| $A_v$               | Open Loop Gain                             |

|---------------------|--------------------------------------------|

| $C_{Load}$          | Load Capacitor                             |

| $g_m$               | Transconductance                           |

| $V_{DD}$            | Supply Potential                           |

| $V_{DSAT}$          | Saturation Voltage                         |

| $V_{DS}$            | Drain-Source Potential                     |

| $V_{GS}$            | Gate-Source Potential                      |

| $v_{id}$            | Differential Input Voltage                 |

| $V_{TH}$            | Transistor Threshold Voltage               |

| AC                  | Alternating Current                        |

| ADC                 | Analog to Digital Converter                |

| BJT                 | Bipolar Junction Transistor                |

| BW                  | Bandwidth                                  |

| FOM                 | Figure of Merit                            |

| FVF                 | Flipped Voltage Follower                   |

| FVFDP               | Flipped Voltage Follower Differential Pair |

| GBW                 | Gain Bandwidth Product                     |

| Gnd                 | Signal Ground                              |

| HF                  | High Frequency                             |

| HSC                 | High Swing Cascode                         |

| ICMR                | Input Common Mode Range                    |

| KCL                 | Kirchhoff's Current Law                    |

| LLPD                | Low Leakage Peak Detector                  |

| NMOS                | N-Channel Metal Oxide Semiconductor        |

| OPA                 | Operational Amplifier                      |

| OTA                 | Operational Transconductance Amplifier     |

| PM                  | Phase Margin                               |

| PMOS                | P-Channel Metal Oxide Semiconductor        |

| $\mathbf{RF}$       | Radio Frequency                            |

| RFID                | Radio Frequency Identification             |

| SD                  | Source Degeneration                        |

| $\operatorname{SR}$ | Slew Rate                                  |

| UGF                 | Unity Gain Frequency                       |

| $\mathrm{UHF}$      | Ultra High Frequency                       |

# Chapter 1 Motivation

A passive Radio Frequency Identification (RFID) tag shall be used to make impedance measurements of microbiological cell structures. As power consumption is an issue, different topologies of adaptively biased operational amplifiers need to be analyzed to be implemented effectively to increase the performance of the analog to digital converter (ADC). Furthermore, different approaches to detect a signal amplitude are analyzed. The peak detector is used to find the maximum of the measurand from an impedance measurement, which is then converted by the ADC.

In order to observe proliferation, concentration and the physiologic condition of microbiological cells, impedance measurements are often used. Depending on the application, sometimes the growth environment may not be disturbed from the outside, making measurements impossible without the use of batteries. However, due to the harshness of the environment, either product lifetime may be reduced or the space consumption due to the battery may have to be increased. Using RFID, one is able to achieve the needed measurements while still only having to include a single tag within the growth environment. A buffer capacitor stores the energy generated by the harvester from a Radio Frequency (RF) field. Once the field is deactivated an accurate impedance measurement can be accomplished and the result sent back to the reader unit [10, 13].

A CellMonitor system from [13] is shown in Fig. 1.1. The micro-titer plate, which encases the sensors along with their tags, sits on top of the reader unit.

Figure 1.1: CellMonitor System

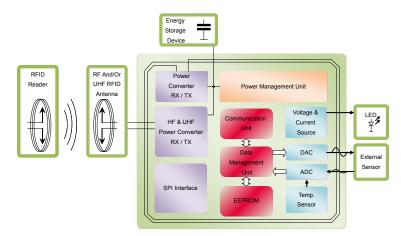

A block diagram of the functionality of the chip is shown in Fig. 1.2. The High Frequency (HF) and Ultra High Frequency (UHF) energy harvester converts the RF field and stores the gathered energy in the capacitor. The power management unit then supplies the different sections of the chip only as needed in order to reduce consumption. The reader activates a measurement and then turns off the field for a set amount of time. Therefore, the influence through the RF field upon the measurement is reduced. Once the measurement has finished, the collected data is stored via the data management unit. The reader unit requests the data which is then backscattered by the tag.

Figure 1.2: Block Diagram of the RFID Tag

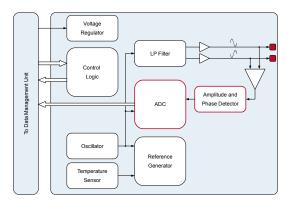

Fig. 1.3 shows a more detailed representation of the sensor interface. The sections which are to include the work of this thesis are highlighted.

Figure 1.3: Block Diagram of the Sensor Interface

The application range for the tag including the sensor system is fairly wide spread. Besides the usage in laboratories to gather information about the growth of cell cultures, the system may be used in a medical environment to quickly detect diseases such as sepsis. Sepsis leads to blood abnormalities which can be detected using an impedance measurement [1].

# Chapter 2

# Class AB Operational Transconductance Amplifiers

The Operational Transconductance Amplifier (OTA) is a commonly used building block in electronic circuits. In analog chip design specifically it serves as subcomponent in more complex circuits such as ADCs, Bandgap References, Peak Detectors and many more.

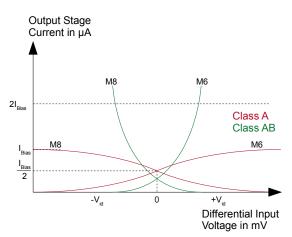

Class A OTAs are defined as having a constant output current, independent of the input signal. This is a major disadvantage with regard to power consumption. Class B circuits have an output current depending on the input signal. When a large differential input signal  $(v_{id})$  is applied, this is advantageous because the output is capable of adapting much quicker. However, if  $v_{id}$  is too small, the quiescent current becomes too small and the signal is distorted [9]. The class AB OTA tries to combine the advantages of class A and class B OTAs by having a large output current dependent on  $v_{id}$  and a quiescent current that is small to limit power consumption, but not too small in order to avoid distortion. The characteristics of the output current of a Class AB OTA can be seen in Fig. 2.1.

Figure 2.1: Output Current Adaptively Biased OTA

Transistors M 6, 8 represent the output stage of an OTA as shown in Figs. 2.3 and 2.6.

# 2.1 Objective

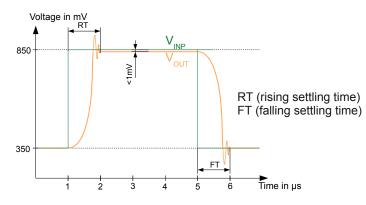

The task at hand is to find an OTA to be used as a buffer which is capable of following an input step in  $1 \mu$ s using as little energy as possible. The signal has to settle to less than 1 mV difference from the final value within the given time limit. In order to guarantee this, a monte carlo analysis has been made. It includes process and mismatch variations, where the standard deviation of the final value was chosen to be less than 1 mV. For the input step, a rise of 0.5 V was chosen due to the limitations of the 1.2 V technology. The input step along with the desired step response is shown in Fig. 2.2. The load capacitor to be used is 5 pF. Tab. 2.1 summarizes these requirements.

Figure 2.2: Input Step Response

| Parameter     | Value   | Unit          |

|---------------|---------|---------------|

| Settling Time | 1       | $\mu { m s}$  |

| Offset        | ±1      | mV            |

| Input Step    | 350-850 | mV            |

| $C_{Load}$    | 5       | $\mathrm{pF}$ |

Table 2.1: Requirements

Usually, small signal parameters as well as the slew rate (SR) defined in Sec. 2.2.1, are used to compare the performance of different topologies as well as for defining the dimensions of the components of the circuit. The small signal parameters are obtained by linearizing the circuit for a certain operating point (AC Analysis [3]). This analysis is no longer valid when using Class AB, because the operating point changes depending on the applied input signal. Due to this restriction, the OTA's performance will be measured and compared by their static power consumption, as well as the energy needed to follow an input step.

# 2.2 Current Mirror OTA

The class A Current Mirror OTA in Fig. 2.3, even though it is single ended, has a very symmetrical shape due to its current mirrors  $M_3$  and  $M_5$  as well as  $M_4$  and  $M_6$ . It is therefore much better suited to modifications than other OTA structures because the positive as well as the negative signal path have to be modified in the same way to increase the current given certain circumstances but limit it given others. The modification has to be equal on both sides in order to not decrease the overall performance of the OTA. Another advantage of this structure is the output stage. Given a technology with a maximum voltage of 1.2V, an output stage consisting of 4 transistors would significantly reduce the output swing, even though the gain would benefit due to the larger output resistance. If needed, cascode transistors can be included in this structure to increase the overall gain of the OTA.

Figure 2.3: Class A Current Mirror OTA

#### 2.2.1 Basics

The major performance characteristics of an OTA are the small signal characteristics, which can be found in the bode plot. Fig. 2.4 shows the open loop gain  $(A_v)$ , bandwidth (BW), phase margin (PM) and unity gain frequency (UGF). The transconductance  $(g_m)$ , needed to calculate  $A_v$  and the UGF, is usually determined by the input differential transistor pair. However, in this configuration it can be improved by the scaling factor of the PMOS current mirror (Eq. 2.2.1).

$$G_m = g_{m1} \frac{g_{m5}}{g_{m3}} = g_{m2} \frac{g_{m6}}{g_{m4}}$$

(2.2.1)

Even though the increase in  $g_m$  is a significant improvement of the performance of the OTA, it comes at the cost of power consumption, even in steady state.

Figure 2.4: Bode Plot

$A_v$  of the OTA is given by the product of the transconductance and the output resistance (2.2.2).

$$A_v = G_m \ (r_{ds6} \parallel r_{ds8}) \tag{2.2.2}$$

Assuming the OTA is stable it therefore has a PM of reasonable value. A PM of  $60^{\circ}$  is suggested by [12] as the step responce shows a good trade-off between settling time and ringing. Having this kind of PM means that the non-dominant pole is at a much higher frequency than the UGF. The non-dominant pole is at the nodes of the gates of  $M_3$  and  $M_4$  due to symmetry. Given the assumption, the gain bandwidth (GBW) product is estimated to be equal to the UGF. The GBW product is dependent on the transconductance as well as the total capacitance at the output node (2.2.3). This capacitance is approximately the size of the load capacitor ( $C_{Load}$ ).

$$GBW = \frac{G_m}{2\pi C_{Load}}$$

(2.2.3)

Furthermore the output swing has previously been mentioned. Its maximum can be calculated by subtracting the saturation voltage of  $M_6$  and  $M_9$  from  $V_{DD}$  (2.2.4).

$$V_{OutSwing} = V_{DD} - V_{DSAT-M6} - V_{DSAT-M8}$$

$$(2.2.4)$$

The topology in Fig. 2.3 shows an NMOS input stage, which enables the OTA to accept higher input voltages compared to a PMOS input stage. The input common mode range (ICMR) can be calculated by finding the upper and lower voltage limits in order for all of the OTA's transistors to stay in saturation. The former is found by subtracting all voltage drops from  $V_{DD}$  to the input gate (2.2.5). To find the latter all voltage drops from the input gate to ground (Gnd) are added together (2.2.6). Eq. 2.2.8 shows the result for the input common mode range. Similarly, the input range for an OTA with a PMOS input stage can be found in Eq. 2.2.8.

$$V_{InMax} = V_{DD} - V_{DSAT-M3} - V_{TH-M3} + V_{TH-M1}$$

(2.2.5)

$$V_{InMin} = V_{DSAT-M11} + V_{DSAT-M1} + V_{TH-M1}$$

(2.2.6)

$$V_{ICMR-N} = V_{DD} - V_{DSAT-M3} - V_{TH-M3} + V_{TH-M1}$$

$$-(V_{DSAT-M11} + V_{DSAT-M1} + V_{TH-M1})$$

$$(2.2.7)$$

$$V_{ICMR-N} = V_{DD} - 3 \cdot V_{DSAT} - V_{TH}$$

(2.2.8)

Another parameter to measure the performance of an OTA is the SR. It is a large signal measurement and uses an input step to see just how fast the OTA can respond when connected as follower. The theoretical maximum SR can be calculated as shown in Eq. 2.2.9. The SR of an OTA usually does not reach the maximum value for longer periods of time because this assumes that all of  $I_{Out}$ , which would be equivalent to  $I_{Bias}$ , is charging or discharging  $C_{Load}$ . This is only the case if there is a large differential voltage at the input. If the differential voltage decreases,  $I_{Bias}$  starts to split more evenly across the differential pair according to the voltage applied.

$$SR = \frac{I_{Bias} \frac{g_{m5}}{g_{m3}}}{C_{Load}}$$

(2.2.9)

Note: The equations are obtained from [4].

Given the equations above, it can be be seen that, if available in the technology, using an input transistor with a lower  $V_{TH}$  and larger  $g_m$  is advantageous as the ICMR as well as the GBW and  $A_v$  are increased.

#### 2.2.2 Implementation

Given the specifications in Sec. 2.1 as well as the functionality of the current mirror OTA in Sec. 2.2.1, the circuit shown in Fig. 2.3 was implemented. Instead of using the GBW to find  $g_m$  of the input stage and then the biasing current, by applying Eq. 2.2.10 the SR can be used to approximate the current needed to charge  $C_{Load}$  by 0.5 V. However, this is only an estimation, because the output current only equals  $I_{Bias}$  at a large  $V_{id}$ . Once the output approaches the input signal, the differential pair will start to divide the current, decreasing the output current. Therefore more biasing current will eventually be needed to achieve the desired input step response.

$$0 < \frac{g_m}{I_D} < 30 \ [9] \tag{2.2.10}$$

The above equation can be used to quickly estimate the operating region of a transistor. In most cases the transistor will be used in saturation. While a  $\frac{g_m}{I_D} <5$  is commonly used for current mirrors, a  $\frac{g_m}{I_D}$  between 10 and 15 is a good value for an input stage. Knowing the  $\frac{g_m}{I_D}$  at a given current, the transistor size can be found by implementing a circuit with an ideal current source and a transistor configured as diode. Using this circuit, simulations can be done to find the width and length according to the desired givens.

Having estimated the size of the input stage, the transconductance can further be improved by increasing the width of the transistor which will eventually result in forcing it into weak inversion. This results in the MOSFET becoming similar to a BJT[9]. The advantage of this is that it enables one is to obtain the highest  $g_m$  possible. This in turn increases the gain as well as the gain bandwidth product of the amplifier. The length of the input stage transistors should not be kept at the minimum length of the process to decrease the offset. Roughly quintupling the length, compared to its minimum results in a larger area which will decrease mismatch and therefore keep the offset lower.

The remaining transistors of the OTA in Fig. 2.3 are current mirrors. As mentioned above, a low  $\frac{g_m}{I_D}$  is generally desired. This will result in a small  $\frac{W}{L}$  which causes the diode connected transistor of the current mirror to set a higher gate-source voltage  $(V_{GS})$ . Increasing the length of a transistor stabilizes its threshold voltage  $(V_{TH})$  over process variations. It furthermore maximizes  $V_{GS}$  which in turn also reduces the effects of a varying  $V_{TH}$  allowing for the current to be mirrored more accurately. Given a process with different transistors, one implemented with a small  $g_m$  is to be used to further increase its  $V_{GS}$ .

As seen in Eq. 2.2.9, the output current can be further increased by scaling the PMOS current mirrors. This is a trade-off, however, as the SR will be increased proportionally but the static power consumption will be as well. For this comparison, these current mirrors were implemented with a ratio of 1:3.

The same approach was used to design an OTA with a PMOS input stage. However, it was a goal to roughly keep the layout area of the block similar for the two OTAs. This was achieved as seen in Tab. 2.2.

| Input Stage | Area in $\mu m^2$ |

|-------------|-------------------|

| NMOS        | 512               |

| PMOS        | 578               |

Table 2.2: OTA Size

#### 2.2.3 Results

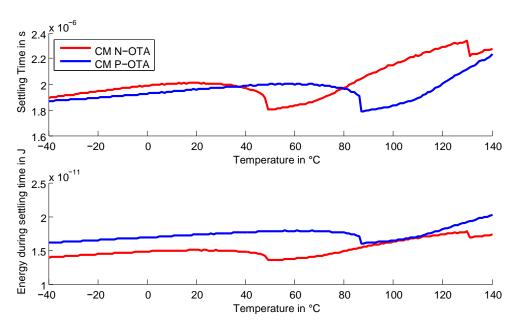

The top plot in Fig. 2.5 shows the sum of the rise and fall times of the current mirror OTA with an NMOS input stage (CM N-OTA, Fig. 2.3) as well as a PMOS input stage (CM P-OTA, Fig. A.1) over temperature. On the bottom of the plot, the total energy used during the respective settling times is shown. Since an NMOS input stage is compared to a PMOS, the energy during a positive as well as a negative input step has to be observed due to the differences in topology. Given a positive input step, the NMOS input stage causes  $I_{Bias}$  to flow through  $M_2$  and  $M_4$  (Fig. 2.3). Therefore,  $M_6$  will either have the same or a scaled current yielding a total of 2 branches with current flow. The PMOS input step, given the same input signal, draws the current through  $M_{1,3,5,7}$  and  $M_8$  where  $M_5$  and  $M_8$  are used as current mirrors (Fig. A.1). This in total yields three branches and will eventually result in a higher energy consumption. So in order to equally record the current consumption, both input steps are measured and their respective energies recorded. Note that the PMOS topology does in fact need one more branch to mirror the current from  $M_{12}$  to, eventually,  $M_9$ . This however is included, because the bias current usually is supplied to an NMOS transistor and not copied through a PMOS transistor.

Given a similar area for the two OTAs the one with the NMOS input stage is expected to perform better. At the same size the NMOS transistor will have a higher transconductance due to the higher mobility of electrons compared to holes, as can be found in [9],[5],[12] and [2]. As seen in Eq. 2.2.1, the  $g_m$  of the input stage determines the transconductance for the overall OTA. An OTA with a higher  $g_m$ , given the same output resistance, will have a higher gain and a higher GBW. Eq. 2.2.11, obtained from [11], shows the dependence of the amplifier error E, which is the difference between the ideal and actual output voltage of the amplifier, on the open loop gain.

$$E = \frac{V_{In}}{1 + A\beta} \tag{2.2.11}$$

While the applied differential voltage is much greater than the error, the OTA will distribute all of  $I_{Bias}$  accordingly to  $V_{id}$ , therefore achieving its maximum SR. As the output approaches the input voltage  $I_{Bias}$  will be divided up again until the voltages are equal. From this it is apparent that at a higher gain, the maximum SR will be achieved

Figure 2.5: Settling Time and Energy over Temperature NMOS vs. PMOS

for a longer period of time, therefore decreasing the overall settling time of the OTA. Since, as established above, the OTA with the NMOS input stage has a higher gain, it is expected to need less time to accomplish the input step responses.

Overall, looking at the curves, it can be seen that the settling time increases with temperature. At low temperatures  $V_{TH}$  is higher, causing a lower voltage at node N1 in Fig. 2.3 affecting the current through  $M_9$ . As temperature increases, the threshold voltage of a transistor decreases, yielding an increase in potential at node N1. This results in an increase in  $I_{Bias}$  over temperature. The transistors of the input stage operate in weak inversion at room temperature. An increase in their currents results in a decrease in  $\frac{g_m}{I_D}$  eventually driving the transistor into the saturation region. In consequence, the transconductance of the OTA decreases, affecting small signal parameters such as the gain, unity gain frequency and phase margin as well. As mentioned above, less gain will increase the settling time.

The sudden decreases in the curves occur due to the aforementioned changes in small signal parameters. A different phase margin represents changes in the settling behavior. Specifically, the overshoot is inversely proportional to the phase margin. Given the increase in current, no change in the pole locations in the bode plot results in an increase in phase margin. If the overshoot decreases to less than the 1 mV specified to be the maximum allowed offset, the final input step response time decreases significantly. This case happens to the NMOS input stage OTA if the temperature is increased from 48°C to 49°C and from 130°C to 131°C. While the former occurs given a positive input step,

the latter is a result of a negative input step response. The PMOS input stage OTA shows the same reaction given a positive input step and a temperature increase from 86°C to 87°C. At the cost of a smaller GBW, the phase margin could be increased to avoid those drop offs if a more linear application over temperature is needed.

The standard deviation of the output variation over process and mismatch was determined to be 0.97 mV for the NMOS input stage OTA. The PMOS input stage topology has a standard deviation of the final output value of 0.96 mV.

Tab. 2.3 shows the quiescent and active current consumption of the OTA as well as the maximum and minimum output current at room temperature. The quiescent current  $I_{V_{DD}}$  is measured at input voltages of 350 and 850 mV.

| Input Stage | I <sub>Out-Min</sub> | I <sub>Out-Max</sub> | $I_{Vdd}$   |

|-------------|----------------------|----------------------|-------------|

|             | in $\mu A$           | in $\mu A$           | in $\mu A$  |

| NMOS        | 2.24                 | 4.66                 | 6.01 - 6.32 |

| PMOS        | 2.14                 | 4.05                 | 7.35-7.76   |

Table 2.3: Quiescent Current Consumption regular current mirror OTAs

From the quiescent current it can be seen that the PMOS input stage uses more energy. In this comparison  $I_{Bias}$  is not scaled, therefore the extra branch makes a big difference. However even if a scaled version was implemented, the area consumption would increase.

Since no noise requirements are given, the NMOS input stage OTA will be used throughout this thesis because, as shown, it consumes less energy given a similar area to achieve the desired input step response.

### 2.3 Class AB Current Mirror OTA: Source Degeneration

Generally class AB OTAs can be split into two categories, one type modifies the current through the input, the other the output stage to achieve class AB. The modification of the input stage is done by using a Flipped Voltage Follower and will be discussed in Sec. 2.5.

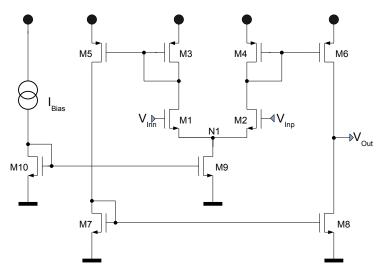

The first example of a modified output stage is shown in Fig. 2.6 taken from [8]. Transistors  $M_{11}$  and  $M_{12}$  have been added to the regular current mirror OTA from Fig. 2.3 similarly as if they were used as source degeneration. Even though the modification is done in the branch of the input stage, the current change occurs only in the output stages of the OTA, therefore not influencing the current through the input transistors  $M_1$  and  $M_2$ .

Figure 2.6: Class AB Current Mirror OTA Source Degeneration

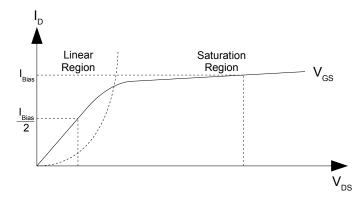

#### 2.3.1 Basics

Usually source degeneration with a resistor is used to increase the output resistance [12]. In this case the degeneration transistor is used to generate a voltage drop depending on the current through its branch. At  $v_{id}$  approximately zero, the transistor is biased in the linear region and therefore has a low  $V_{DS}$ . If  $v_{id}$  increases, the current through one branch increases and  $V_{DS}$  of the 'degeneration' transistor along with it. The current mirroring transistors  $M_5$  and  $M_6$  see the sum of  $V_{GS-M3,4}$  and  $V_{DS-M11,12}$  as their  $V_{GS}$ . This causes an increase in output current beyond the quiescent current, classifying it as class AB.

Achieving a higher output current using this structure comes at the price of having a higher quiescent current. Close examination of transistors  $M_{11}$  and  $M_{12}$  shows that they are capable of switching from the linear to saturation region, therefore increasing their  $V_{DS}$  just as planned. However, the minimum value for  $V_{DS}$ , if zero  $v_{id}$  is applied, is not equal to zero. Therefore the current flow of the overall circuit will be increased. Furthermore, the input common mode range should be considered when  $v_{id}$  is large because  $V_{DS}$  reaches its maximum at this point. The maximum for the ICMR of the circuit in Fig. 2.6 can be seen in Eq. 2.3.1.

$$V_{InMax} = V_{DD} - V_{DS-M12} - V_{TH-M4} - V_{DSAT-M4} + V_{TH-M2}$$

(2.3.1)

The maximum of  $V_{DS-M11,12}$  can be limited by increasing the ratio of  $\frac{W}{L}$  which then in turn decreases the maximum output current. Last but not least, an extra branch to generate  $V_{Bias}$  will always be needed and therefore cost energy even if a ratio to  $I_{Bias}$  is chosen.

#### 2.3.2 Implementation

The dimensions of the input pair transistors along with the current mirrors were implemented as described in Sec. 2.2.2. A factor of three has been used to permanently increase the output current, just as has been done with the regular current mirror OTA. In order to generate  $V_{Bias}$  for  $M_{11}$  and  $M_{12}$ , an extra branch with a diode connected transistor has to be used.  $M_{13}$  is used to generate a voltage which allows  $M_{11}$  and  $M_{12}$ to change their operating region if  $v_{id}$  is applied. The different operating regions are shown in Fig. 2.7. In order to determine how to chose the dimensions of  $M_{13}$ , the power consumption shall be temporarily neglected. In this case, the current mirrored by  $M_{14}$ is  $I_{Bias}$ . Eq. 2.4.2 states the condition for a transistor to be in saturation. Since the transition from linear to saturation region is given by Eq. 2.3.3, obtained from [9], the diode connected transistor will be comfortably in saturation.  $M_{13}$  sets  $V_{Bias}$  for  $M_{11}$  and  $M_{12}$ . If  $v_{id}$  is zero,  $I_{Bias}$  will be split equally and  $M_{11}$  and  $M_{12}$  each get  $\frac{I_{Bias}}{2}$ . As seen in Fig. 2.7, this puts  $M_{11}$  and  $M_{12}$  in the linear region, each therefore having a small  $V_{DS}$ . If a large  $v_{id}$  is applied,  $I_{Bias}$  will be steered according through either  $M_{11}$  or  $M_{12}$ . This transistor will then move into the saturation region, equaling the diode connected transistor  $M_{13}$  and generating a larger  $V_{DS}$ . As a result  $V_{GS-M5}$  consists of the sum of  $V_{GS-M3}$  and  $V_{DS-M11}$  and  $V_{GS-M6}$  consists of the sum of  $V_{GS-M4}$  and  $V_{DS-M12}$ . This yields the desired effect of an increased output current given a nonzero  $v_{id}$ .

Figure 2.7: Drain Current vs. Drain-Source Voltage

$$V_{DS} \ge V_{GS} - V_{TH} \tag{2.3.2}$$

$$V_{DS} = V_{GS} - V_{TH} (2.3.3)$$

Finally, in order to reduce the power consumption, especially of the branch generating  $V_{Bias}$ , a scaling factor can be used. However the aforementioned factor should be maintained for the circuit to work as described.

#### 2.3.3 Results

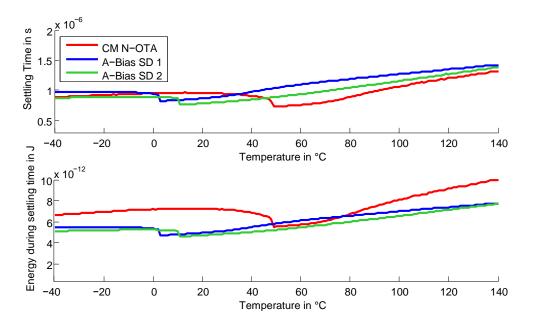

The result time and energy consumption if an input step is applied to the current mirror OTA with source degeneration (A-Bias SD1) is plotted against the regular current mirror OTA (CM N-OTA) in Fig. 2.8. At low temperatures the settling time of both OTAs, shown on top, is almost equivalent. A good comparison can be made, and it can be seen in the bottom half that the OTA with adaptive biasing needs slightly less energy to complete the input step response. However, a clear-cut advantage cannot be seen. Note that here only the positive input step settling time and energy are compared. This is possible because the input stage is NMOS in both cases, so the general functionality is the same, and there is no need to include the negative rise time as well, as it will show similar results. Having analyzed the rise time and energy of the regular current mirror OTA in 2.2.3, this current mirror OTA with adaptive biasing shows a very similar behavior over temperature. The settling time increases with temperature, as does the energy, due to the aforementioned events. The significant change in phase margin and overshoot occurs when increasing the temperature from 2°C to 3°C. Overall the source degeneration delivers a higher SR but the overall energy of the OTA increases, making the impact of adaptive biasing very minor. The standard deviation of the final output value over process and mismatch was simulated with 1 mV.

A third curve is shown in Fig. 2.8 labeled with A-Bias SD2. This is an improved version of the current mirror OTA with source degeneration with regards to settling time and energy used at the cost of an increasing offset. Reducing the length of the input stage transistors decreases the gate-source capacitance and therefore increases the transit frequency of the transistor itself. On the other hand, the threshold voltage fluctuates more due to mismatch. This substantially increases the offset of the circuit, as the input stage is still operated in weak inversion using the same ratio of  $\frac{W}{L}$  as A-Bias SD1. This is included to show that an improvement with this topology is possible. The final standard deviation of the offset was found to be 1.6 mV.

Table 2.4 shows the quiescent and active current consumption of the OTA architectures at room temperature.

Chapter 2 Class AB Operational Transconductance Amplifiers

Figure 2.8: Current Mirror OTA vs. Adaptively Biased OTA SD

| Input Stage | $I_{Out-Min}$ | $I_{Out-Max}$ | $I_{Vdd-Min}$ | $I_{Vdd-Max}$ |

|-------------|---------------|---------------|---------------|---------------|

|             | in $\mu A$    | in $\mu A$    | in $\mu A$    | in $\mu A$    |

| A-Bias SD1  | 1.5           | 4.15          | 3.86          | 5             |

| A-Bias SD2  | 1.22          | 4.14          | 3.14          | 4.87          |

| CM N-OTA    | 2.24          | 4.66          | 6.01          | 6.32          |

Table 2.4: Quiescent Current Consumption A-Bias SD1 & CM N-OTA

Even though the energy consumed during the input step is not reduced, the theory of adaptive biasing is clearly shown here. While the maximum output currents between the three types are very similar, the source degeneration implementations only needs about one half of the current of the regular OTA to maintain the output.

# 2.4 Class AB Current Mirror OTA: High Swing Cascode

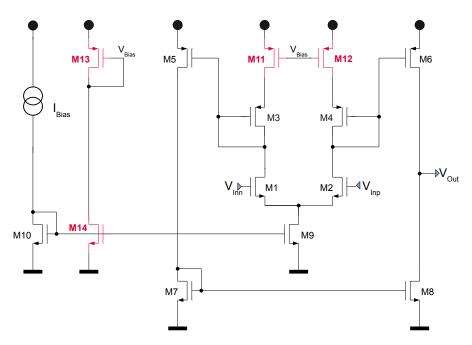

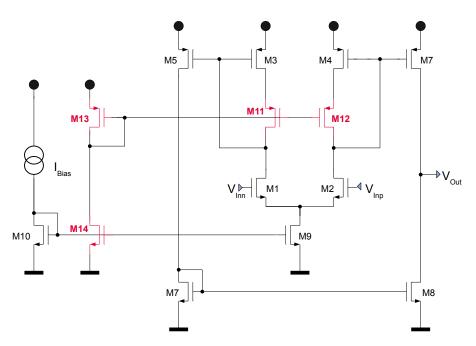

Another approach to increase the current of the output stage is to switch the degeneration transistor with the diode connected transistor. The result can be seen in Fig. 2.9.

Figure 2.9: Class AB Current Mirror OTA High Swing Cascode

#### 2.4.1 Basics

The final outcome of this approach is the same as previously. The goal is to increase the  $V_{GS}$  of the current mirror transistors  $M_5$  and  $M_7$  given a nonzero  $v_{id}$ . While in steady state, all transistors are in saturation and  $M_{11}$  and  $M_{12}$  act as cascode transistors just like a high swing cascode. In order to increase the output current when needed,  $M_{11}$  and  $M_{12}$  are used to force  $M_3$  and  $M_4$ , respectively, into the linear region when  $v_{id}$  is applied. More current and a stable  $V_{GS}$  for  $M_{11}$  and  $M_{12}$  will cause them to increase the potential at their sources. This decreases  $V_{DS}$  of  $M_3$  and  $M_4$ , eventually forcing them into the linear region. Once in triode region,  $V_{GS}$  increases, yielding the desired result.

In terms of quiescent current, this circuit should be better than the previous, because when  $v_{id}$  is zero,  $M_3$  and  $M_{11}$  as well as  $M_4$  and  $M_{12}$  work like a high swing cascode and do not generate any unnecessary voltage which could then be converted to current by the mirroring transistors. In comparison, the source degeneration topology, will always result in a larger  $V_{GS-M5,6}$  because  $V_{DS-M11,12}$  will not be zero even if there is no differential voltage applied. Considering the input common mode range while  $v_{id}$  is nonzero the voltage at the gate of  $M_3$  and  $M_4$  cannot drop lower than the sum of  $V_{DS-M9}$  and  $V_{DS-M1,2}$  in order for the circuit to work properly. Note that  $V_{DS-M1,2}$  at  $v_{id}$  nonzero can be of substantial size due to a large  $V_{GS}$ .

#### 2.4.2 Implementation

An extra branch consisting of  $M_{13}$  and  $M_{14}$  is creating  $V_{Bias}$  for  $M_{11}$  and  $M_{12}$  again. Eq. 2.4.1 shows the conditions for  $M_3$  and  $M_4$  to be in saturation. Similarly to before, the power consumption is temporarily ignored and  $I_{Bias}$  is chosen to generate  $V_{Bias}$ . This results in  $M_{11}$  and  $M_{12}$  having  $\frac{1}{2} V_{GS-M13}$ , therefore leaving enough of a voltage drop from their sources to  $V_{DD}$  for  $M_3$  and  $M_4$  to operate in saturation, given steady state conditions. Increasing  $v_{id}$  causes an increase in current through either  $M_{11}$  or  $M_{12}$ and an increase in their respective  $V_{GS}$  as seen in Eq. 2.4.2. This limits  $V_{DS}$  of  $M_3$  or  $M_4$ , eventually forcing it into the linear region. The conditions for entering the linear region are shown in Eq. 2.4.3, while the dependency of  $I_D$  and  $V_{GS}$  in triode is shown in Eq. 2.4.4.

$$V_{GS-M13} \ge V_{GS-M11,12} + V_{DS-M3,4} \tag{2.4.1}$$

$$I_D = \frac{\mu_n \ C_{ox}}{2} \ \frac{W}{L} (V_{GS} - V_{TH})^2 \ (1 + \lambda V_{DS})$$

(2.4.2)

where  $\lambda$  is the channel length modulation.

$$V_{DS} \le V_{GS} + V_{TH} \tag{2.4.3}$$

$$I_D = \mu_n \ C_{ox} \ \frac{W}{L} \ ((V_{GS} - V_{TH})V_{DS} - \frac{V_{DS}^2}{2})$$

(2.4.4)

Eqs. 2.4.4 and 2.4.2 show the change of  $V_{GS}$  by simply changing its operation region. Since the current stays the same,  $V_{GS}$  increases significantly. The mirror transistors, still in saturation, then transform this voltage increase into a current boost.

Simulations have shown that it is advantageous to use transistors with a somewhat smaller  $V_{TH}$  for  $M_{11}$  and  $M_{12}$  compared to  $M_{13}$ . This makes it easier to ensure that  $M_3$  and  $M_4$  are in saturation if no  $v_{id}$  is applied.

In order to decrease the power consumption, simple scaling of the bias current and the transistor size of  $M_{13}$  can be used to reduce the steady state current flow in this branch.

#### 2.4.3 Variation

Fig. 2.10 shows another possibility to complete the output class AB qualification. It is the same configuration as as shown in Fig. 2.9 except that  $M_{11}$  has been moved to the last diode in the negative signal path. This is an advantage with regard to power consumption because the increase in current is given by  $M_8$  instead of  $M_7$ . Looking at other requirements, such as the offset, this configuration becomes quite a problem. In order to avoid creating a new branch, the voltage at the gate is taken from the diode connected  $M_{10}$ . With proper scaling this can be done, but the difference in the operating points of the cascode transistors  $M_{11}$  and  $M_{12}$  at steady state is very difficult to overcome. This offset is due to different mobilities and uneven behavior over process, temperature and mismatch.

Figure 2.10: Class AB Current Mirror OTA High Swing Cascode Variation

#### 2.4.4 Results

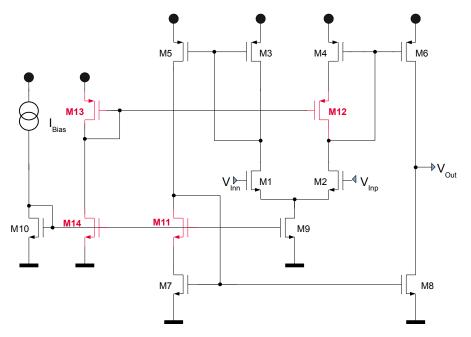

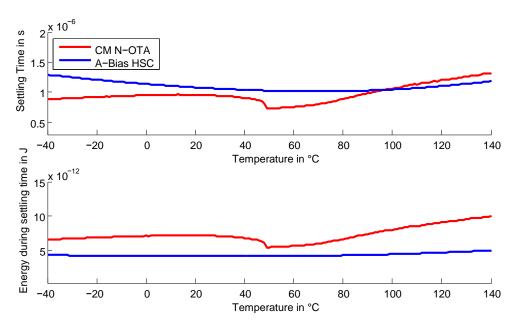

Fig. 2.11 shows the simulation results of the settling time as well as energy used during this time period for the regular current mirror OTA (CM N-OTA) as well as the implementation with the adaptive biased high swing cascode (A-Bias HSC). The first thing to notice is that the A-Bias HSC seems to have a high phase margin. This yields a constant settling behavior over the temperature without any sudden drops occurring. Even though the settling time is slightly longer compared to the time needed by the CM N-OTA, this adaptive biasing variation shows great improvement regarding energy consumption in the given time period. Once again, only the rise time is taken into account here due to the aforementioned reasons. It can also be seen that at low temperatures the rise time is a little bit longer due to a higher  $V_{TH}$ . As the temperature rises, the  $V_{GS-M3,4}$  increases due to a decrease in  $V_{TH}$ . Since this is the same  $V_{GS}$  for  $M_5$  and  $M_6$  the output current will change proportionally. At high temperatures the mobility effects control the behavior of the OTA. The mobility decreases with higher temperatures eventually increasing the settling time again.

Figure 2.11: Current Mirror OTA vs. Adaptively Biased OTA HSC 1

The standard deviation of the final output value over process and mismatch variations of the adaptive biased current mirror OTA with a high swing cascode was found to be 1 mV.

Next the sum of the rise and fall times of the regular current gain OTA will be compared to the OTAs in Figs. 2.9 and 2.10. The modified version of the OTA with a high swing cascode uses less current in the far left branch of the OTA because the adaptive biasing is implemented to increase the current through  $M_8$ , instead of  $M_5$  of the original version. Therefore, in order to get a useful comparison, the fall time has to be included, because when a negative input step is applied, the current will be mirrored through the far left branch, affecting the overall power consumption. These results are shown in Fig. 2.12.

It is obvious that the modified high swing cascode OTA (A-Bias HSC2) uses the least energy while settling just as quickly. This difference is mainly achieved during the negative input step as the regular high swing cascode OTA (A-Bias HSC1) has an extra branch carrying the output current which is quite large. Even though the total time of A-Bias HSC1 is higher than CM N-OTA, the energy used to do so is substantially less. Both adaptive biased OTAs show quite an improvement regarding energy conservation. However, as mentioned, the huge drawback of A-Bias HSC2 is its offset at 2 mV.

Tab. 2.5 summarizes the quiescent currents needed measured at room temperature. The difference in the quiescent currents between the two high swing cascode implementations is simply that the modified version multiplies the  $\frac{I_{Bias}}{2}$  by a factor of 3 at a later stage compared to the original. A-Bias HSC1 needs  $\frac{I_{Bias}}{2}$  through  $M_3$  and  $M_4$  each. Given

Chapter 2 Class AB Operational Transconductance Amplifiers

Figure 2.12: Current Mirror OTA vs. Adaptively Biased OTA HSC 2

that the current mirrors are scaled  $M_5$  and  $M_6$  then each has  $\frac{3I_{Bias}}{2}$ , each yielding a total of roughly  $4I_{Bias}$ . This does not take the branch generating the gate voltage for  $M_{11}$  and  $M_{12}$  into account because it is a fraction of  $I_{Bias}$  and therefore neglected for this quick approximation. Doing the same calculation yields a total of  $3I_{Bias}$  for A-Bias HSC2. These calculations are good reflections of the obtained results in Tab. 2.5.

| Input Stage | $I_{Out-Min}$ | $I_{Out-Max}$ | I <sub>Vdd-Min</sub> | I <sub>Vdd-Max</sub> |

|-------------|---------------|---------------|----------------------|----------------------|

|             | in $\mu A$    | in $\mu A$    | in $\mu A$           | in $\mu A$           |

| A-Bias HSC1 | .948          | 3.59          | 2.65                 | 4.35                 |

| A-Bias HSC2 | 1.02          | 4.42          | 2.04                 | 5.18                 |

| NMOS        | 2.24          | 4.66          | 6.01                 | 6.32                 |

Table 2.5: Quiescent Current Consumption A-Bias HSC1 & A-Bias HSC1 & CM N-OTA

## 2.5 Flipped Voltage Follower

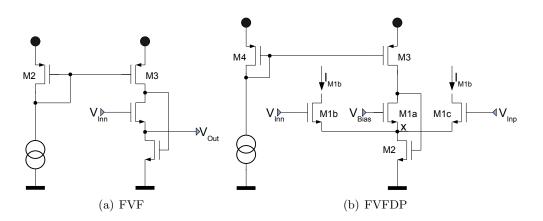

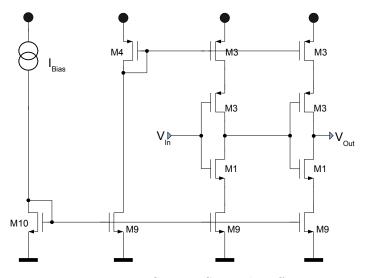

In order to achieve class AB behavior using the input stage, the flipped voltage follower (FVF) in Fig. 2.13(a) presented in [6] can be used. Adding a differential pair to the FVF (Fig. 2.13(b)) allows for it to be used as a differential to single ended converter capable of changing  $I_{Out}$  decisively, given a nonzero  $v_{id}$ .

Figure 2.13: Flipped Voltage Follower and FVF Differential Pair

#### 2.5.1 Basics

This circuit was originally designed to shift the input signal by a constant  $V_{GS}$ . In order to keep the applied voltage shift constant, the current through  $M_1$  has to be kept constant as well (Fig. 2.13(a)). Using Kirchhoff's Current Law (KCL) at the output node it can be seen that  $M_2$  supplies  $I_{Out}$  as well as  $M_1$ . Since  $I_{Out}$  can change but  $M_1$  needs to be constant,  $M_2$  has to be capable of adapting to the required sum of currents. This is done by connecting the gate of  $M_2$  to the drain of  $M_3$ . If a change in  $I_{Out}$  occurs,  $M_1$  and therefore  $M_3$  decrease. In normal operating conditions, the current through a transistor is given by Eq. 2.4.2. Given that  $V_{GS-M3}$  is held constant by  $M_4$ , only  $V_{DS}$  can change along with the change in current. This causes a change in  $V_{GS-M2}$  and therefore the desired change in supplied current.

Given the above,  $I_{Out}$  is now used as the bias current for the differential pair as seen in Fig. 2.13(b). Choosing a proper  $V_{Bias}$  however is dependent on the requirements of the circuit. For an NMOS differential input pair, choosing a lower value enables a high SR whereas a higher value limits the maximum power usage. Both can be explained by looking at node x in Fig. 2.13(b). In steady state, this voltage is determined by  $V_{Bias}$ -  $V_{GS}$ . Setting  $V_{Bias}$  at a lower potential results in a low potential at node x and will therefore cause a large  $V_{GS-M1}$  if a positive input step is applied. This also explains the higher power consumption at steady state when  $V_{Inn}$  is higher than  $V_{Bias}$ . Choosing a higher voltage to bias  $M_{1a}$  reduces both, the SR as well as the overall power consumption of the circuit.

Special attention has to be given to the current mirrors at the output node. The output transistors have to be in saturation and therefore fulfill Eq. 2.4.2. If an input step is applied, the class AB input stage creates a large  $V_{GS}$  at the respective diode connected transistor of the current mirror ( $M_8$  and  $M_{10}$  in Fig. 2.16). This  $V_{GS}$  is mirrored to

the output transistor and it cannot be larger than the sum of transistor's  $V_{DS}$  and  $V_{TH}$ . Using a transistor with higher transconductance causes the diode connected transistor to have a lower  $V_{GS}$  at the same current.

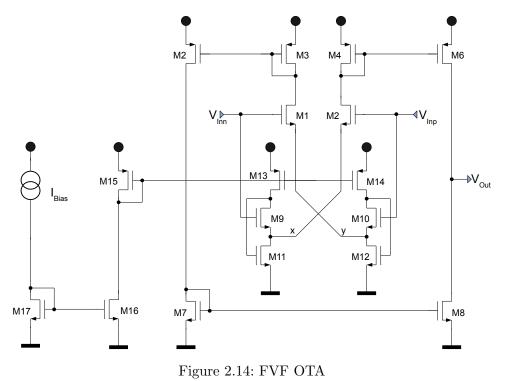

# 2.6 FVF OTA

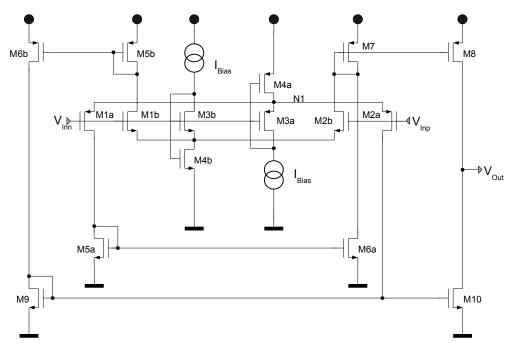

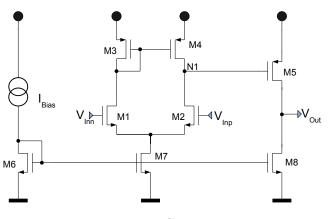

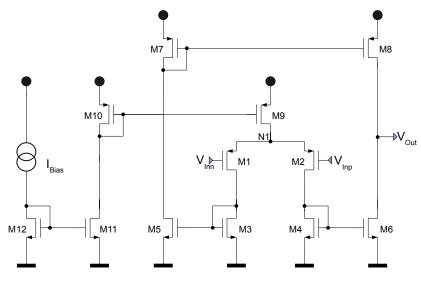

An implementation of a class AB input stage can be seen in Fig. 2.14 [8]. Compared to Fig. 2.16 this architecture uses one FVF for the positive and one for the negative signal path. Therefore, its ICMR is only capable of reaching the upper supply voltage.

#### 2.6.1 Basics

Instead of making use of a fixed  $V_{Bias}$  like the original FVF, this circuit uses the differential voltages as cross coupled supply bias voltages. The voltage at the non-inverting input controls the source of the input transistor of the inverting input and vice versa. If a positive input step is applied,  $I_{M2}$  increases due to an increase in  $V_{GS}$  at this transistor (Fig. 2.14). Since the current through  $M_{10}$  is held steady its  $V_{GS}$  is constant and causes an increase of the potential at node y. So a positive input step increases  $I_{M2}$  by raising

the voltage at its gate while at the same time  $I_{M1}$  is decreased due to an increase of the potential at its source.

Compared to the circuit in Fig. 2.16, this architecture (or a PMOS input stage) is capable of handling either, a positive and negative input step. Two FVF are used to supply the current to the input stage. This can be a disadvantage because  $I_{Bias}$  has to be present in both branches. If an increase in SR is needed, eventually  $I_{Bias}$  will have to be increased, consuming more power. Even though a large SR can be obtained it is difficult to choose the dimensions of the transistors to accurately obtain a given settling time. However this being said a rough estimate can be obtained by looking at  $M_{11}$  and  $M_{12}$ . Either transistor has to at least sink  $I_{Bias}$  from the FVF. The maximum current the transistor can handle is given by its dimensions as well as the maximum  $V_G$  which is equivalent to  $V_{DD}$  minus  $V_{DS-M13,14}$ . It must be kept in mind, however, that this is only the maximum available current and it can only be used for a short time since the output will adjust accordingly, which causes an increase of the potential at the inverting input. Another aspect of this circuit that needs to be analyzed carefully is the ICMR. It is dependent on the FVF rather than the differential input pair along with the current mirrors. As mentioned,  $M_9$  and  $M_{10}$  have to be in saturation in order for the circuit to work properly. The least amount of current through  $M_{11}$  and  $M_{12}$  is  $I_{Bias}$ . Given this current, a proportional voltage depending on the transistor parameters will be set at the gate of  $M_{11}$  and  $M_{12}$ . Ideally, the maximum of the input potential should not exceed this value by more than  $V_{TH-M9,10}$  in order for the FVF input transistor to stay in saturation. The minimum is given by the sum of  $V_{GS-M9,10}$  and  $V_{DS-M11,12}$ .

#### 2.6.2 Implementation

In order to obtain dimensions for the differential pair, the approach from Sec. 2.2.2 was used. Although commonly used in the current mirror OTA, the current mirrors here do not need to be a multiple of their respective diode connected transistors because the increase in current to get a higher SR is done by the input stage. Given that this input stage is capable of generating a high enough current by itself, a multiple mirror transistor would only cause a constant high current at the output even when in steady state, therefore unnecessarily using more power. Furthermore, the current mirrors are implemented with transistors with a higher transconductance in order to avoid a large  $V_{GS}$ during the input step. The input transistors of the FVF can have the same dimensions as the differential input pair. It is however crucial that  $M_{9,10}$  are in the same operating region at all times. If this is not the case, nodes x and y are subject to change depending on the operating region and the currents of  $M_1$  and  $M_2$  will adjust accordingly. To prevent this from happening,  $M_{11}$  and  $M_{12}$  have to have a large  $V_{GS}$  in order to avoid setting the voltage at the drain of  $M_{11}$  and  $M_{12}$  too low. Using a transistor with a higher  $V_{TH}$  will automatically increase the needed  $V_{GS}$  for it to be in saturation. Furthermore the length can be increased to force a larger difference in  $V_{GS}$ .

#### 2.6.3 Results

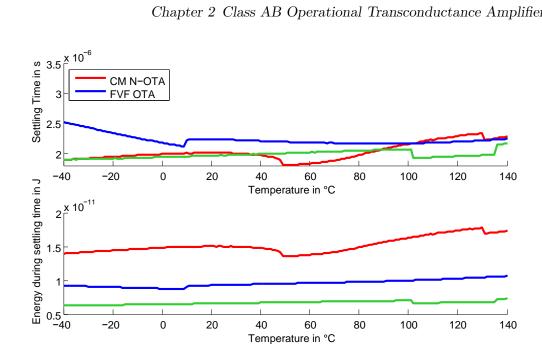

The rise time, along with the energy of the flipped voltage follower (FVF) OTA, is compared to the regular current mirror OTA (CM N-OTA) in Fig. 2.15. At low temperatures, the flipped voltage follower is clearly better, because even though it needs the same amount of energy, the time needed to complete the input step is about half that of the regular OTA. However, as the temperature rises so does the input step time period. The threshold does not affect the current over temperature because the voltage at node X is determined by Eq. 2.6.1.  $I_{M2}$  is determined by its gate-source voltage. Given that  $V_{TH-M2}$  changes with the temperature as well, this effect is limited.

$$V_X = V_{TH-M9} + V_{DSAT-M11} (2.6.1)$$

The effect forcing an increase in rise time and energy over temperature is the mobility. It is inversely proportional to the temperature and causes a reduction of the current through  $M_2$  as well as the output current.

As the current decreases over temperature the phase margin increases. Given that the pole locations of the OTA are the same, a decrease in current results in a reduction of GBW and therefore phase margin. This results in less peaking and a growth in settling time.

Between  $60^{\circ}$ C and  $61^{\circ}$ C the peaking in the input step response decreases to less than 1 mV, causing a drop in settling time as well as energy. The requirement of settling within 1 mV over process and mismatch variations was achieved with less than 0.9 mV for the standard deviation.

The quiescent and active current of the OTA as well as the output currents are shown in Tab. 2.6. It can be seen that the FVF has the largest increase in output current. However, since the bias current of the OTA is modified, the current consumption increases heavily as well, because the large current flows through several branches.

| Input Stage | $I_{Out-Min}$ | $I_{Out-Max}$ | $I_{Vdd-Min}$ | $I_{Vdd-Max}$ |

|-------------|---------------|---------------|---------------|---------------|

|             | in $\mu A$    | in $\mu A$    | in $\mu A$    | in $\mu A$    |

| FVF DP      | 1.44          | 12.1          | 7.75          | 25.7          |

| NMOS        | 2.24          | 4.66          | 6.01          | 6.32          |

Table 2.6: Quiescent Current Consumption FVF & CM N-OTA

### 2.7 FVF Rail-to-Rail

A rail-to-rail FVF can be seen in Fig. 2.16. This design is a little bit of a compromise, as instead of using a fixed  $V_{Bias}$ , it is connected to the negative input terminal. When used

Figure 2.15: Current Mirror OTA vs. FVF OTA

as a buffer, this gives an increased SR if needed, while still reducing power consumption once the signal has settled.

#### 2.7.1 Basics

Setting a fixed  $V_{Bias}$  means having to settle for either a smaller SR or more power consumption. Connecting the inverting input in its place gives another option which can be looked at as a compromise. In order to obtain the SR the transient behavior of the circuit is analyzed. Applying a positive input step yields a high SR, as explained in Sec. 2.5.1. However, as the output settles to its final value to follow the input signal,  $V_{Bias}$  is raised, and the potential at node x in Fig. 2.13(b) along with it. This only causes a reduction of the SR once the output value is close to the input. However, the overall power consumption is decreased for the same reason.

Although this circuit is a compromise between SR and power consumption it comes with many drawbacks. One is that the NMOS input stage can only support a positive input step. Assuming the circuit is in steady state and a negative input signal is applied,  $M_{1c}$  will shut off (Fig. 2.13(b)). This causes the current previously going through  $M_{1c}$  to divide evenly between  $M_{1a}$  and  $M_{1b}$ . An increase of  $I_{M1a}$  yields a lower  $V_{DS-M3}$ , which in turn decreases  $I_{D-M2}$ . This causes less current available to discharge  $C_{Load}$ . Due to this a rail-to-rail input stage can be implemented in which the NMOS stage is responsible

Figure 2.16: Rail-to-Rail FVF

for the positive while the PMOS handles the negative signal steps. Even though the inverting input signal controls the gate of  $M_{1a}$ , it is still necessary to have a path to the output as well. Once  $V_{OUT}$  is equal to  $V_{IN}$ , the negative output path is used to sink the current supplied by the positive output path in order not to change the value on the capacitor. Not having this branch would therefore cause the output signal to be either ground or  $V_{DD}$ . This yields many necessary but power consuming branches overall. An advantage of having to use an NMOS as well as a PMOS input stage is that the ICMR is increased, as shown in Eq. 2.7.1-2.7.3.

$$V_{InMax} = V_{DD} - V_{DSAT-MP5b} - V_{TH-MP5b} + V_{TH-MP1,2}$$

(2.7.1)

$$V_{InMin} = V_{DSAT-MN5a} + V_{TH-MN5a} - V_{TH-MN1,2}$$

(2.7.2)

$$V_{ICMR} = V_{InMax} - V_{InMin} \tag{2.7.3}$$

#### 2.7.2 Implementation

The dimensions of the input differential pairs along with  $M_{3a}$  and  $M_{3b}$  as well as all the current mirrors have been implemented as mentioned in Sec. 2.2.1. Given that the

circuit is rail-to-rail the PMOS input transistors have been chosen a factor three larger due to the higher mobility of electrons compared to holes (Sec. 2.2.3, see [12] among other). Keeping in mind that this is a class AB input stage, the circuit's dimensions can be implemented two different ways. One is to choose input transistors with a larger  $V_{TH}$  in order to cause an overall higher  $V_{GS}$ . This helps keep the voltage across  $V_{GS}$  of the diode connected  $M_{5a}$  and  $M_{5b}$  a little bit lower, in turn helping  $M_8$  and  $M_{10}$  stay in saturation if a large  $v_{id}$  occurs. The current mirrors along the path to the output can be scaled with larger width, decreasing  $V_{GS}$  and therefore allowing a higher SR. This, however, comes at the cost of accuracy. The current mirrored from the diode causes a low  $V_{GS}$  especially at low currents during steady state. Therefore the saturation voltage will be smaller and more susceptible to changes of  $V_{TH}$  due to process variations as well as mismatch. A different way to determine the dimensions is to settle for transistors with a smaller  $V_{TH}$  and more transconductance. Using this type of transistor for the input stage causes more current flow given the same applied voltages as well as dimensions. This in turn would cause the diode connected transistors  $M_{5a}$  and  $M_{5b}$  to increase their  $V_{GS}$ . Using the same type of transistor, however, yields a smaller voltage without having to increase the width of the transistor. Therefore, the same approach to determine the dimensions of the current mirror as described in Sec. 2.2.1 can be used. This also enables a better output swing for the circuit. Transistors  $M_{4a}$  and  $M_{4b}$  have been designed as described in Sec. 2.6.2.

#### 2.7.3 Results

Fig. 2.17 shows the results of the flipped voltage follower rail-to-rail implementation (FVR R2R) compared to the regular current mirror OTA (CM N-OTA). The FVF R2R does need more current but is also quicker to settle. Somewhat surprising is the fact that the settling time actually decreases with temperature. This occurs because of the rail-to-rail input stage. When the input voltage increases, the potential at N1 in Fig. 2.16 is elevated due to the  $V_{GS}$  of  $M_{3a}$  held constant by the current sink. At low temperatures  $V_{TH}$  is higher, therefore eventually forcing  $M_{4a}$  into the linear region because its  $V_{DS}$ becomes too small. If this happens, the current sink could also be affected because  $V_{GS-M4a}$  increases to supply the same current. An increase in  $V_{GS-M4a}$  causes less  $V_{DS}$ for the current sink, forcing it into the linear region. Overall this yields very little current through  $M_{1a}$  as well as  $M_{3a}$ , because their conditions are very similar. This current is then mirrored via  $M_{5a}$ ,  $M_{6a}$  to the diode connected  $M_7$  where it is combined with the current from  $M_{2b}$ . At high temperatures,  $V_{TH}$  decreases causing less of a raise in potential at N1. This difference is enough to keep  $M_{4a}$  in saturation at 140°C. As intended, the current sink stays saturated and the current stays steady through  $M_{3a}$ . Given only a different  $V_{DS}$ , the current through  $M_{1a}$  is very similar. Once again it is then added to the current through  $M_{2a}$  and mirrored at the output stage, resulting in less settling time.

The overall maximum and minimum total as well as output currents of the FVF R2R

Figure 2.17: Current Mirror OTA vs. FVF OTA R2R

are compared to those of the regular current mirror OTA in Tab. 2.7.

| Input Stage | $I_{Out-Min}$ | I <sub>Out-Max</sub> | I <sub>Vdd-Min</sub> | I <sub>Vdd-Max</sub> |

|-------------|---------------|----------------------|----------------------|----------------------|

|             | in $\mu A$    | in $\mu A$           | in $\mu A$           | in $\mu A$           |

| FVF R2R     | 1.37          | 16.2                 | 4.6                  | 27.2                 |

| NMOS        | 2.24          | 4.66                 | 6.01                 | 6.32                 |

Table 2.7: Quiescent Current Consumption FVF R2R & CM N-OTA

An increase in the output current given a  $v_{id}$  is clearly accomplished. However, the railto-rail needs a certain minimum amount of current through all the branches. Even when scaling the current, it will add to the energy consumption. The OTA was implemented with a standard deviation over process and mismatch of 1 mV.

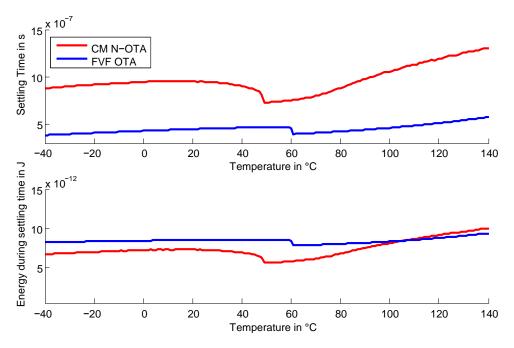

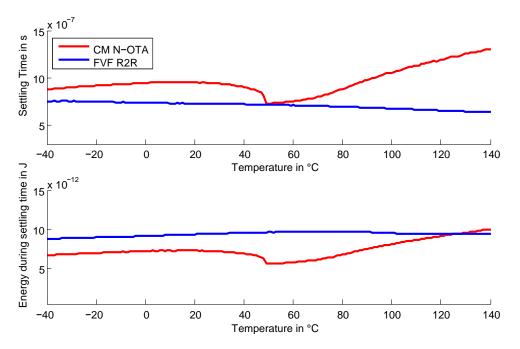

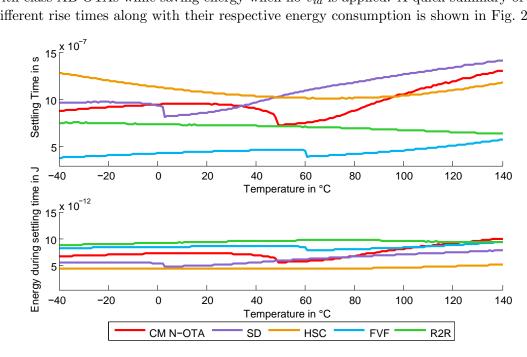

## 2.8 Adaptive Bias OTA Comparison

A variety of different ways to obtain class AB OTAs has been compared, stretching from a version with very little change, to the original current mirror OTA with the source degeneration or high swing cascode, to more complex implementations including the

FVF. Overall, it can be said that the output current can be heavily increased given a  $v_{id}$  with class AB OTAs while saving energy when no  $v_{id}$  is applied. A quick summary of the different rise times along with their respective energy consumption is shown in Fig. 2.18.

Figure 2.18: Rise Time & Energy Summary

The HSC and FVF implementations probably show the best results. Given that the FVF only needs about half of the time to complete the input step response, its energy would be halved if the response was to be completed at about  $1\,\mu$ s. While the HSC implementation has a limited common mode input voltage, the FVF is more likely to struggle with the offset of the OTA, as the voltages for the diode connected current mirrors should be smaller due to the larger current through the input stage. This results in a larger  $\frac{g_m}{I_D}$ , which is non-ideal for current mirrors. If a large common mode input voltage is required, the FVF R2R is probably the best choice. Overall, parameter requirements such as area, offset, as well as input common mode voltage, will dictate which of the above listed adaptively biased OTAs is best suited for a given application.

For completeness, figures of merit (FOM) obtained from [7] are shown in Tab. 2.8.  $FOM_S$  and  $FOM_L$  are defined by Eqs. 2.8.1 and 2.8.2 respectively.

$$FOM_S = \frac{\text{GBW} \cdot C_{Load}}{\text{Power}} [(\text{MHz} \cdot \text{pF})/\text{mW}]$$

(2.8.1)

$$FOM_L = \frac{\mathrm{SR} \cdot C_{Load}}{\mathrm{Power}} \left[ (\mathrm{V}/\mu \mathrm{s} \cdot \mathrm{pF})/\mathrm{mW} \right]$$

(2.8.2)

| OTA      | $FOM_S$ | $FOM_L$ |

|----------|---------|---------|

| CM N-OTA | 1127    | 544     |

| SD       | 1466    | 774     |

| HSC      | 1091    | 1025    |

| FVF      | 202     | 1011    |

| R2R      | 209     | 1460    |

Chapter 2 Class AB Operational Transconductance Amplifiers

Table 2.8: FOM

The advantage of those FOMs is that they can be easily calculated and applied to all OTAs compared to the approach in this work. However, an OTA can also be easily designed to achieve a large  $FOM_L$ : simply by scaling the current mirror  $M_3$  and  $M_4$ and  $M_5$  and  $M_6$  (Fig. 2.3) by a factor of three, the slew rate will triple while the steady state power consumption doubles. While this gives the best-case ratio between lowest power consumption and largest slew rate possible, the efficiency of the OTA while doing so gets lost. Furthermore, it is not defined in those figure of merits if the steady state or dynamic power consumption is to be used. For the work in this thesis, the dynamic power consumption was used, as it shows the worst case, which is when the OTA has a constant nonzero differential input voltage. Another concern in FOMs is the area consumption. The FVF for instance will most likely have a larger layout than a regular OTA. While it is difficult to include the area consumption in an FOM, it would still be more beneficial to use a ratio of slew rate and power consumption while achieving the former, instead of only during steady state.

## Chapter 3

## **Peak Detector**

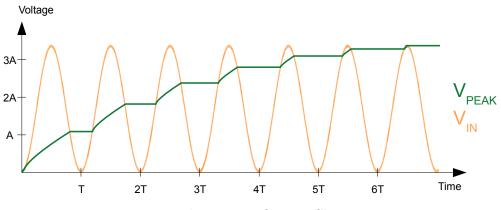

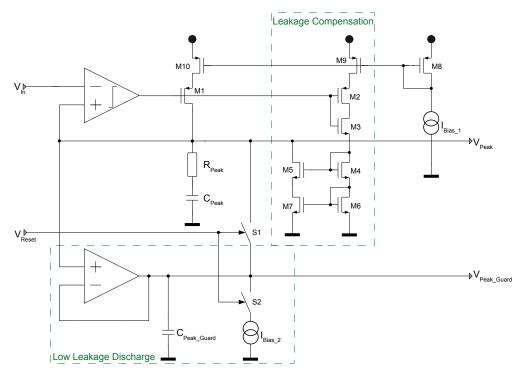

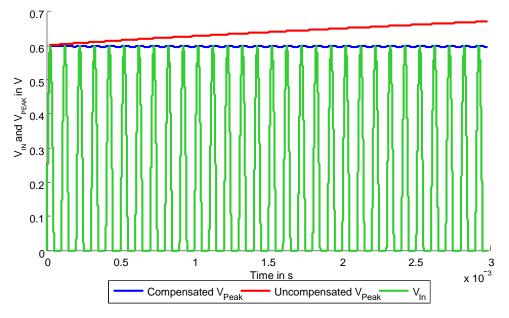

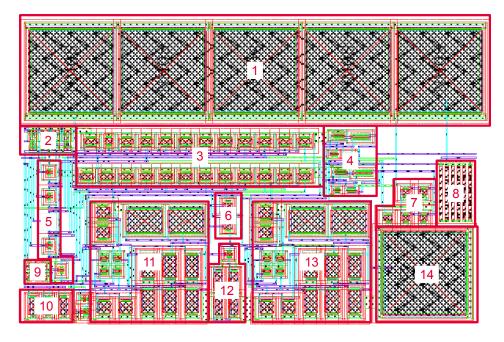

Another circuit block used in the sensor interface is the peak detector. It is the vital link between the differential to single ended amplifier and the input to the ADC as seen in Fig. 1.3. As its name suggests, the peak detector is used to detect the amplitude of the sinusoidal signal obtained from the impedance measurement.

## 3.1 Objective

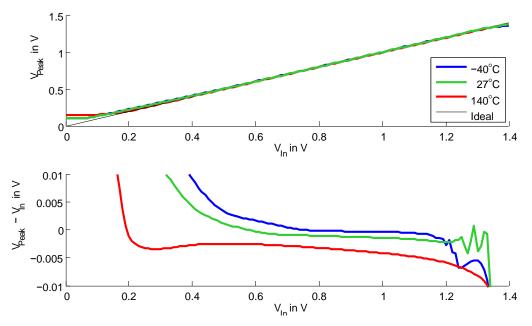

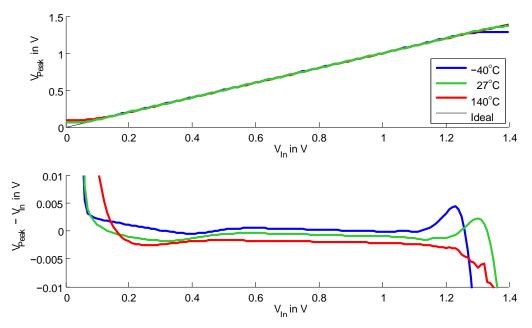

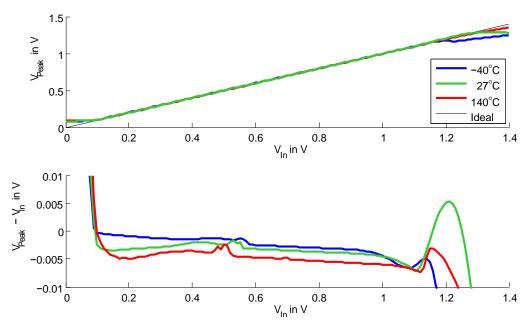

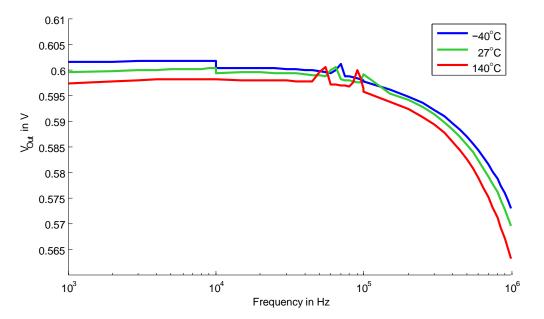

For this application the frequency of the sinusoidal signal used can vary from 1 kHz up to 100 kHz. The minimum detectable peak is at 200 mV while the maximum should be as close to  $V_{DD}$ , which is 1.5 V, as possible. However, the expected input signals are between 200 mV and 300 mV. The time allowed for the peak detector to find the maximum voltage is less than 10 periods of the input signal. Once the output settles to the peak, this value should be held the over time. Since the ADC used to convert the signal has a resolution of 10 bits, it would be ideal to implement the peak detector with an accuracy of 1 mV. More accuracy is not needed as the ADC will not be able to detect the changes anymore due to its resolution. Overall, the peak detector, along with any biasing circuitry needed, is expected to be as energy efficient as possible.

Table 3.1 summarizes the requirements for the peak detector.

| Parameter         | Value    | Unit    |

|-------------------|----------|---------|

| Frequency Range   | 1-100    | kHz     |

| Voltage Range     | 0.2-1.5  | V       |

| Detection Time    | $10\tau$ | s       |

| Offset            | 1        | mV      |

| Power Consumption | <10      | $\mu W$ |

Table 3.1: Peak Detector Requirements

The possible output characteristics of the desired peak detector are shown in Fig. 3.1.

Figure 3.1: Peak Detector Output Characteristics

### 3.2 Simple Peak Detector

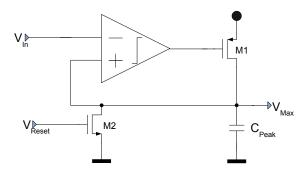

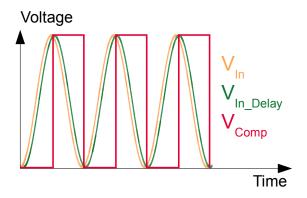

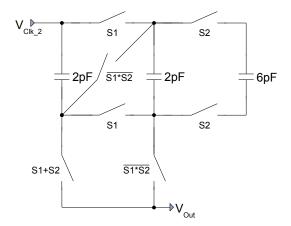

A very common implementation of a peak detector can be seen in Fig. 3.2[5]. A comparator is used to determine the greater between  $V_{In}$  and  $V_{Max}$ . It controls the gate of  $M_1$  to allow current flow to charge  $C_{Peak}$  as well as turns off  $M_1$  when  $V_{Max}$  equals  $V_{In}$ .  $M_2$  is used to reset the peak detector.

Figure 3.2: Simple Peak Detector Schematic

$M_1$  can be implemented as either an NMOS or PMOS transistor. When an NMOS transistor is used, the inverting and non inverting terminal of the comparator must first of all be exchanged. Further, the transistor will then be used in a common drain configuration. The output resistance can then be simplified to the reciprocal of the sum of  $g_m$  and  $g_{mb}$ . Using a PMOS transistor is equivalent to a common source stage with an output resistance of  $r_{ds}$ . Having a high output resistance of the overall circuit causes a higher gain resulting in more accuracy. The trade-off, however, is a lower pole frequency at this node limiting the circuit to the use at lower frequencies only. However, using a PMOS transistor also increases the output voltage swing. The current through the