Master Thesis Nr. 699

# RING OSCILLATOR FREQUENCY BASED CV and VARIABILITY CHARACTERIZATION

Jacob Reyes

Institute of Electronics Graz University of Technology Head of Institute: O. Univ.-Prof. Dipl.-Ing. Dr. techn. Wolfgang Bösch

Supervisor: Dipl.-Ing. Dr. techn. Mario Auer Supervisor at ams AG: Dipl.-Ing. Werner Posch

Graz, August 2012

This thesis was conducted in cooperation with ams AG.

## Kurzfassung

Diese Arbeit befasst sich mit verschiedenen messtechnischen Anwendungen von Ringoszillatoren. Anhand von Frequenz- und Strommessungen kann die mittlere Kapazität einer Ringoszillatorstufe bestimmt werden. Eine zusätzliche kapazitive Last in jeder Stufe ermöglicht gezielte Messungen von bauteilspezifischen Kapazitäten mit Auflösung im Picofarad-Bereich. Die Eingangskapazität des Inverters und parasitäre Elemente werden dabei durch Vergleich mit einem Referenzoszillator berücksichtigt. Vorteilhaft bei dieser Messmethode ist, dass lokale Parameterschwankungen über eine Vielzahl von Stufen gemittelt werden. Konkret werden die Überlappungskapazität von NMOS und PMOS Transistoren und die Oxidschichtdicke von PMOS Transistoren gemessen.

Eine weitere Anwendung finden Ringoszillatoren bei der Bestimmung von Mismatch Variationen. Werden die zusätzlichen Lasten entsprechend dimensioniert, so kann die Frequenz des Oszillators sensitiv gegenüber der Variation des gewünschten Parameters gemacht werden. In dieser Arbeit wird die Variation der Einsatzspannung von NMOS und PMOS Transistoren untersucht.

Zum Schluss wird der Einsatz von Ringoszillatoren zur Verifikation von Transistormodellen vorgestellt. Gegenstand dieser Untersuchungen sind Hochvolt-LDMOS Transistoren.

## Abstract

The focus of this thesis is the feasibility of ring oscillator structures for process controll and device characterization purposes. By measuring the oscillation frequency and the oscillator's current consumption, the average capacitance of one inverter stage can be deduced. Inserting an additional capacitive load makes measurements of specific device capacitances with picofarad resolution possible. The inverter's capacitance and parasitic elements are taken into account by comparisons with reference oscillators. The advantage of this method is that local variations are averaged over the number of stages. In particular, the overlap capacitance of PMOS and NMOS transistors and the oxide thickness of PMOS transistors are captured with this method.

On the other hand, ring oscillators can be used to determine mismatch variations. The oscillation frequency can hereby be made sensitive to a specific parameter by appropriately dimensioning the load. Investigations regarding the threshold voltage variability are conducted for NMOS and PMOS transistors.

Finally, ring oscillator structures to benchmark transistor models are introduced. This is done for high voltage LDMOS transistors.

## STATUTORY DECLARATION

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

August 2012

Jacob Reyes

# Contents

| 1        | Intr          | oduction                                                                                                   | 1         |

|----------|---------------|------------------------------------------------------------------------------------------------------------|-----------|

| <b>2</b> | $\mathbf{CV}$ | Characterization                                                                                           | 3         |

|          | 2.1           | Literature Studies                                                                                         | 3         |

|          |               | 2.1.1 Capacitance Measurement with Ring Oscillators                                                        | 3         |

|          |               | 2.1.2 Capacitance Modeling in BSIM3v3                                                                      | 6         |

|          |               | 2.1.3 Layout Considerations                                                                                | 9         |

|          | 2.2           | Parameter Extraction                                                                                       | 11        |

|          | 2.3           | Ring Oscillator Circuit Design                                                                             | 14        |

|          |               | 2.3.1 Simulation Environment in Matlab                                                                     | 14        |

|          |               | 2.3.2 Design of the Ring Oscillator Test Structures                                                        | 15        |

|          |               | 2.3.3 Matching Analysis and Sensitivity Investigations                                                     | 18        |

|          | 2.4           | Ring Oscillator Circuit Layout                                                                             | 28        |

|          |               | 2.4.1 Schematic Layout                                                                                     | 29        |

|          |               | 2.4.2 Layout                                                                                               | 30        |

|          |               | 2.4.3 Verification of the Layout                                                                           | 34        |

|          | 2.5           | Measurement Setup                                                                                          | 36        |

|          |               | 2.5.1 Measurement Equipment                                                                                | 37        |

|          |               |                                                                                                            | 41        |

|          | 2.6           |                                                                                                            | 42        |

|          |               | 2.6.1 Measurement Results                                                                                  | 42        |

|          |               | 2.6.2 Discussion $\ldots$ | 43        |

|          | 2.7           | Conclusion                                                                                                 | 52        |

| 3        | Var           | iability Characterization                                                                                  | <b>54</b> |

|          | 3.1           | Literature Studies                                                                                         | 54        |

|          | 3.2           | Ring Oscillator Circuit Design                                                                             | 56        |

|          |               | 3.2.1 Simulation Results                                                                                   | 59        |

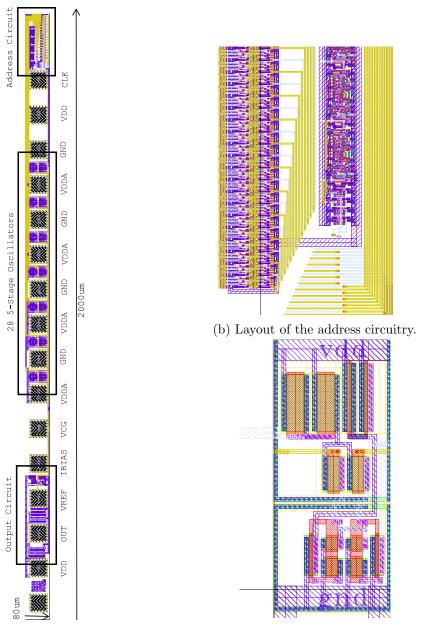

|          | 3.3           | Ring Oscillator Circuit Layout                                                                             | 61        |

|          | 3.4           | Conclusion                                                                                                 | 66        |

| 4        | Hig           | h-Voltage Ring Oscillator Investigations                                                                   | 67        |

|          | 4.1           |                                                                                                            | 67        |

|          | 4.2           | Simulation and Measurement Results                                                                         | 71        |

|          | 4.3           | Conclusion                                                                                                 | 72        |

#### $\mathbf{5}$ Summary **A** CV Characterization A.1 Simulation Environment Script: writehead.m A.1.1 A.1.2 A.1.3 Script: writeStage1.m A.1.4 Script: writeOptions.m A.1.5 A.1.6 Example Netlist A.1.7 Script: getdataoverlap.m. A.2 Final Design **B** Variability Characterization C High-Voltage Ring Oscillator Investigations

#### $\mathbf{74}$

77

77

78

79

81

83

84

86

89

92

100

103

# List of Figures

| 2.1  | Ring oscillator structure                                                               | 4  |

|------|-----------------------------------------------------------------------------------------|----|

| 2.2  | Schematic of one loaded ring oscillator cell.                                           | 5  |

| 2.3  | Principle for CV characterization with ring oscillators                                 | 5  |

| 2.4  | Illustration of the active area                                                         | 7  |

| 2.5  | Overlap voltage $V_{gd,overlap}$ from equation (2.12) and overlap capacitance           |    |

|      | parameter <b>cgds</b> from (2.14) plotted as functions of gate drain voltage $V_{gd}$ . | 8  |

| 2.6  | Schematic layout of inverter cells for loaded and reference oscillators                 | 9  |

| 2.7  | Schematic layout of a ring oscillator in a scribe line                                  | 10 |

| 2.8  | Layout with individual ring oscillators                                                 | 10 |

| 2.9  | Layout with ring oscillator macros                                                      | 11 |

| 2.10 | Expected mean values for NMOS and PMOS overlap capacitance parameters                   | 13 |

| 2.11 | Oscillator stage with ideal capacitor load                                              | 16 |

| 2.12 | Oscillator stage with PMOS load                                                         | 17 |

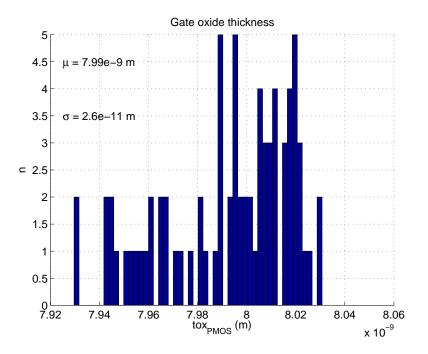

| 2.13 | Mismatch, oxide thickness.                                                              | 19 |

| 2.14 | Mismatch, PMOS overlap capacitance parameter                                            | 19 |

| 2.15 | Process and mismatch simulation for PMOS overlap capacitance parameter.                 | 20 |

| 2.16 | Process and mismatch simulation for NMOS overlap capacitance parameter.                 | 20 |

| 2.17 | Plots of the least squares approximation for an unloaded oscillator                     | 23 |

| 2.18 | Plots of the least squares approximation for design 1                                   | 24 |

| 2.19 | Plots of the least squares approximation for design 2                                   | 25 |

| 2.20 | Schematic layout and pin description of test chip 1                                     | 29 |

| 2.21 | Schematic layout and pin description of test chip 2                                     | 30 |

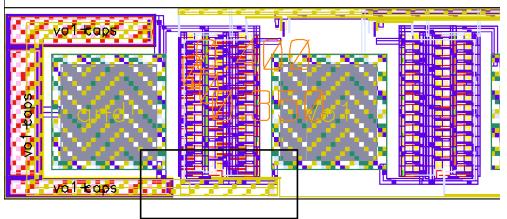

| 2.22 | Capacitor placement                                                                     | 31 |

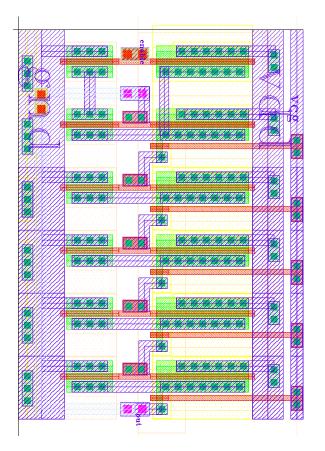

| 2.23 | Layout of test chip 1 and 2                                                             | 32 |

| 2.24 | Layout details of design 2                                                              | 33 |

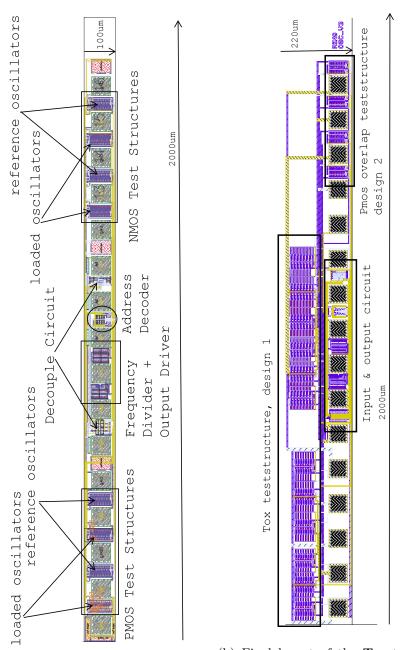

| 2.25 | Layout details of the $T_{ox}$ test structure, design 1                                 | 35 |

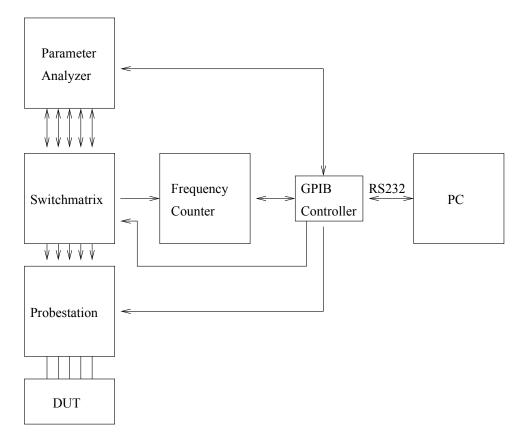

| 2.26 | Schematic Measurement Setup                                                             | 37 |

| 2.27 | Current Measurement Resolution                                                          | 38 |

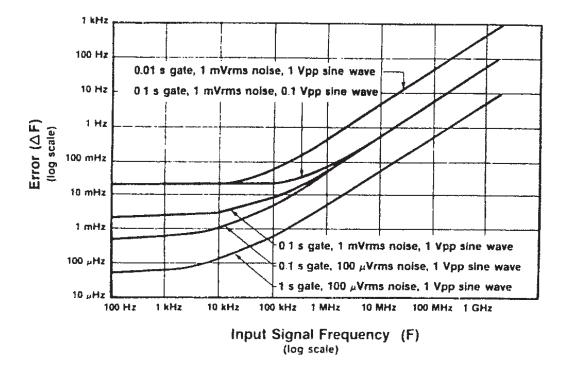

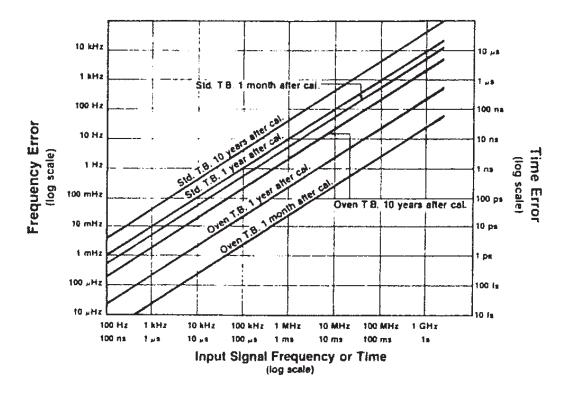

| 2.28 | Agilent 5334A Frequency Resolution Error                                                | 39 |

| 2.29 | Agilent 5334A Timebase Error                                                            | 40 |

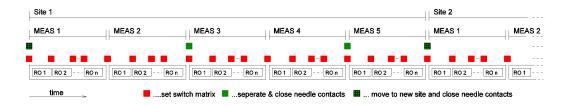

| 2.30 | Measurement Reproducibility                                                             | 43 |

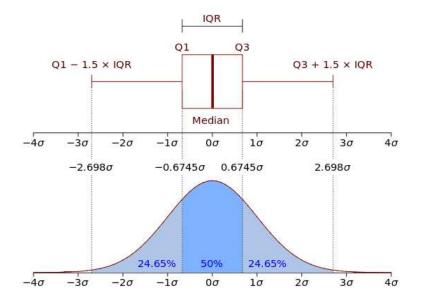

| 2.31 | Graphical description of the interquartile range criterion                              | 45 |

| 2.32 | $cgds_{PMOS}$ measurement results from test chip 1                                      | 46 |

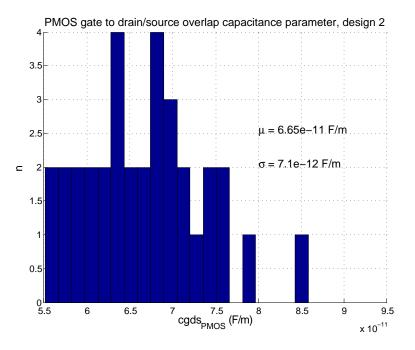

| 2.33 | $cgds_{PMOS}$ measurement results from test chip 2                                      | 46 |

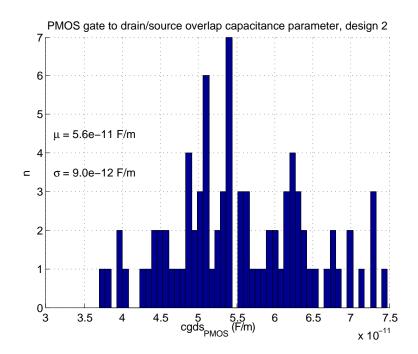

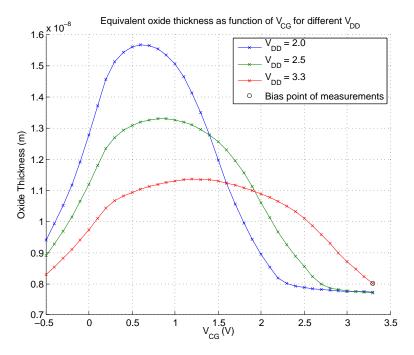

| 2.34 | Results for $V_{CG}$ and $V_{DD}$ sweep on loaded oscillators                           | 47 |

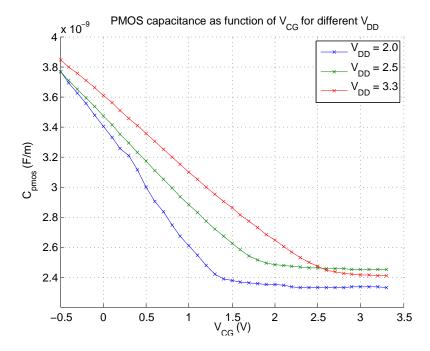

| 2.35 | Results for $V_{CG}$ and $V_{DD}$ sweep overlap capacitance parameter                                | 48  |

|------|------------------------------------------------------------------------------------------------------|-----|

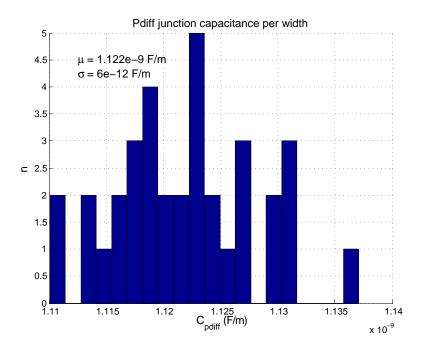

| 2.36 | $C_{\text{pdiff}}$ results from test chip 2                                                          | 48  |

| 2.37 | $\mathbf{cgds}_{\mathrm{NMOS}}$ results from test chip 1                                             | 49  |

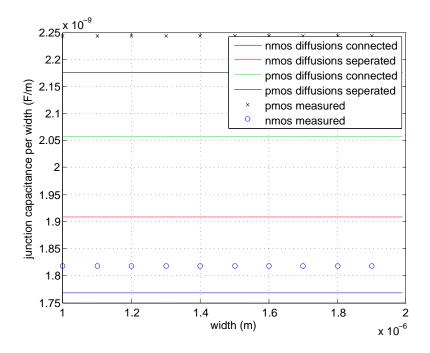

| 2.38 | Simulated and measured capacitance values per width for $n^+$ and $p^+$ diffusions                   | 50  |

| 2.39 | $T_{ox}$ measurement results from test chip 2                                                        | 51  |

| 2.40 | $\mathbf{T}_{\mathbf{ox}}$ measurement results from test chip 2. The gate voltage is sweeped and the |     |

|      | measurement performed for different oscillator supply voltages                                       | 51  |

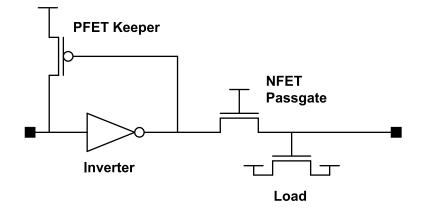

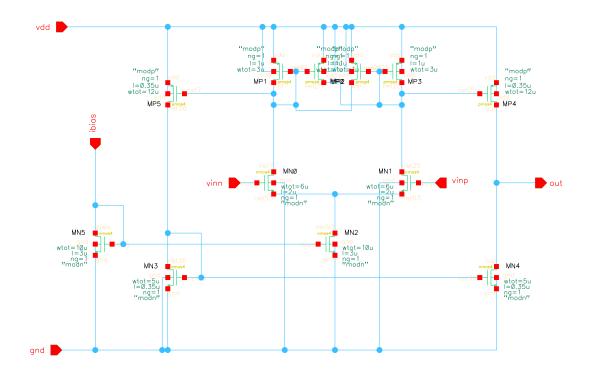

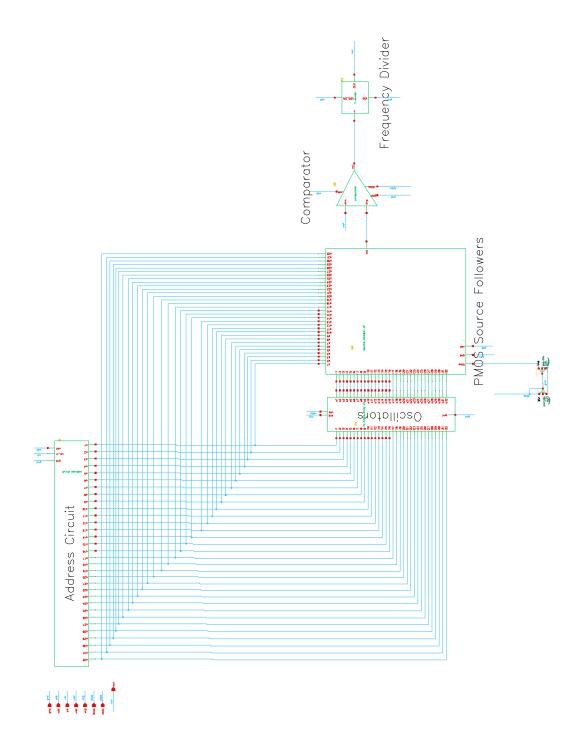

| 3.1  | Ring oscillator stage for variability monitoring.                                                    | 55  |

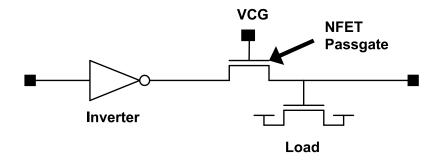

| 3.2  | Enhanced ring oscillator stage for variability monitoring                                            |     |

| 3.3  | Circuit schematic of the ring oscillator matrix                                                      |     |

| 3.4  | Circuit schematic for variability measurements                                                       |     |

| 3.5  | 5 bit counter schematic.                                                                             |     |

| 3.6  | PMOS passgate oscillator.                                                                            |     |

| 3.7  | NMOS source follower.                                                                                |     |

| 3.8  | Comparator design 1                                                                                  |     |

| 3.9  | Complete circuit for measurement of PMOS threshold voltage variability                               |     |

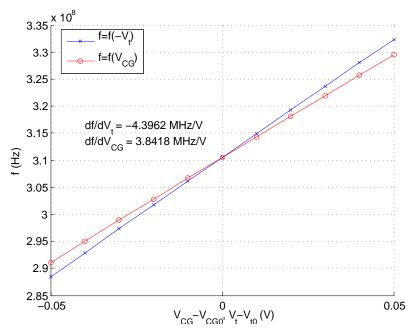

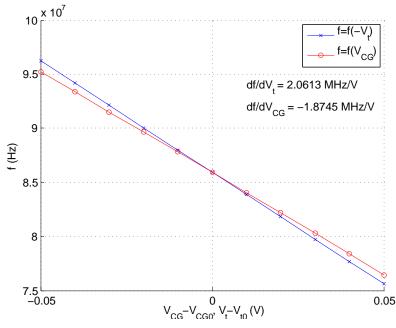

| 3.10 | Simulation results to determine $k$ for PMOS and NMOS passgate                                       |     |

| 3.11 | Variability oscillator layout.                                                                       |     |

| 3.12 | Layout details of variability test chip                                                              |     |

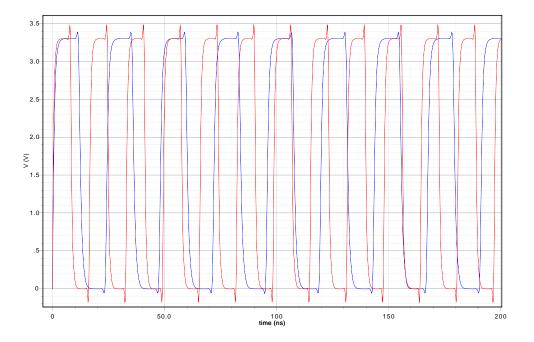

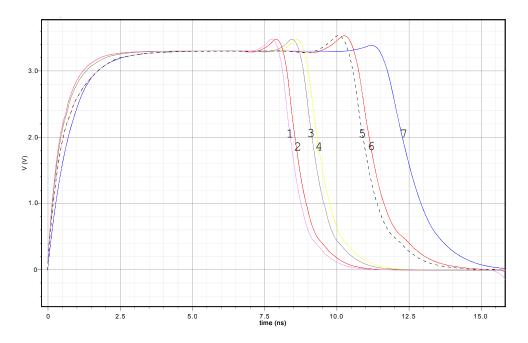

| 4.1  | Oscillation for HV_50M oscillator.                                                                   | 68  |

| 4.2  | CGG NMOS50m.                                                                                         |     |

| 4.3  | CGG NMOS50m-dlc.                                                                                     |     |

| 4.4  | CGG NMOS50m-cgdx                                                                                     | 70  |

| 4.5  | Comparison BSIM3v3 subcircuit vs. HiSIM_HV model with different pa-                                  |     |

|      | rameters.                                                                                            | 70  |

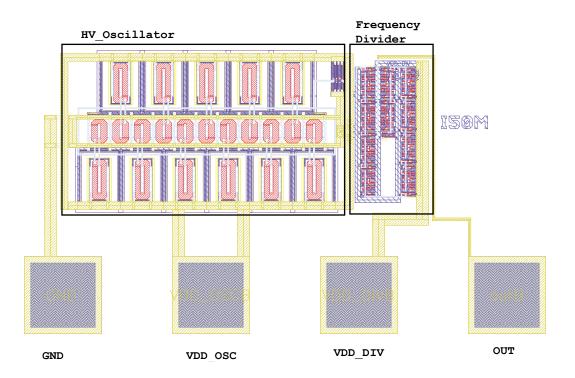

| 4.6  | Layout of HV oscillator with NMOS50m and PMOS50m transistors                                         | 72  |

| A.1  | Decoder design.                                                                                      | 92  |

| A.2  | Design schematic for test chip 1                                                                     | 93  |

| A.3  | Ring oscillator schematic.                                                                           | 94  |

| A.4  | Reference oscillator schematic.                                                                      |     |

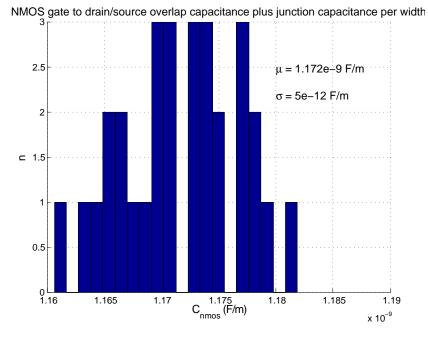

| A.5  | $C_{\rm NMOS}$ results from test chip 1                                                              | 96  |

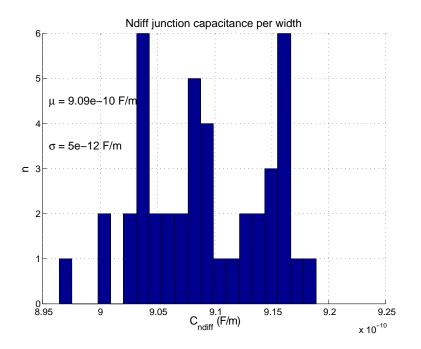

| A.6  | $C_{\text{ndiff}}$ results from test chip 1                                                          | 96  |

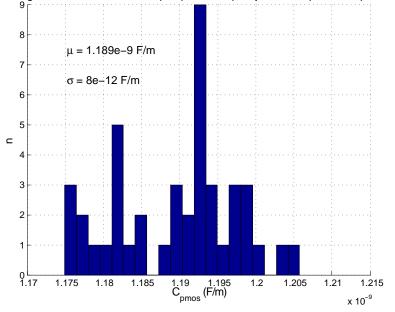

| A.7  | $C_{\rm PMOS}$ results from test chip 1                                                              | 97  |

| A.8  | $C_{\text{pdiff}}$ results from test chip 1                                                          | 97  |

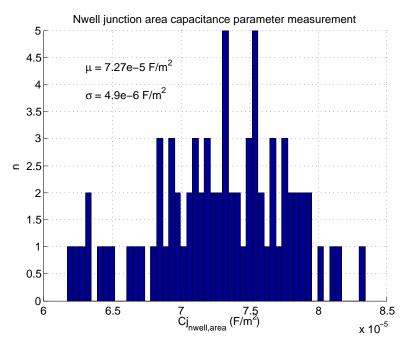

| A.9  | $Cj_{\text{nwell,area}}$ results from test chip 2                                                    | 98  |

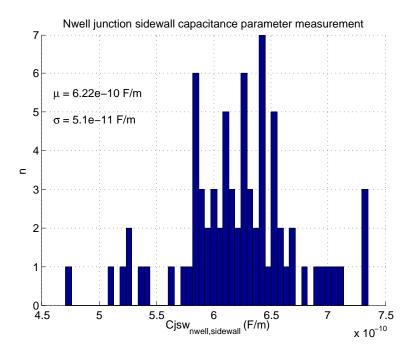

| A.10 | $Cjsw_{nwell, sidewall}$ results from test chip 2. The parameter corresponds to the side-            |     |

|      | wall scaling with length.                                                                            | 98  |

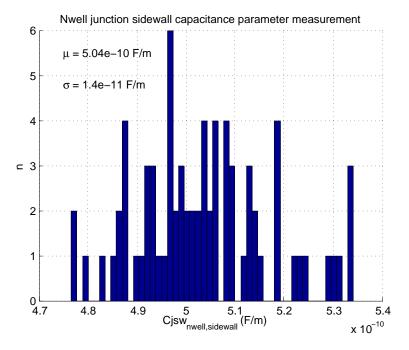

| A.11 | $Cjsw_{nwell, sidewall}$ results from test chip 2. The parameter corresponds to the side-            |     |

|      | wall scaling with width.                                                                             | 99  |

| B.1  | Schematic of the NMOS passgate oscillator.                                                           | 100 |

| B.2  | PMOS source follower                                                                                 | 101 |

| B.3  | Comparator with NMOS differential pair                                                               | 101 |

| B.4  | Complete circuit for measurement of NMOS threshold voltage variability                               | 102 |

| C.1 | Comparison of the overlap capacitance of the NMOS50m for BSIM3v3 and      |

|-----|---------------------------------------------------------------------------|

|     | HiSIM_HV                                                                  |

| C.2 | Comparison of the gate capacitance of the PMOS50m for BSIM3v3 and         |

|     | HiSIM_HV                                                                  |

| C.3 | Comparison of the overlap capacitance of the PMOS50m for BSIM3v3 and      |

|     | HiSIM_HV                                                                  |

| C.4 | Influence of BSIM3v3 parameter <b>dlc</b> on overlap capacitance 105      |

| C.5 | Influence of BSIM3v3 parameter $\mathbf{cgdx}$ on overlap capacitance 105 |

# List of Tables

| 2.1 | Simulation Data for ring oscillator with an ideal capacitor as load                                                        | 16 |

|-----|----------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Device dimensions for design 1 and 2                                                                                       | 17 |

| 2.3 | Model parameters which are varied for a Monte Carlo process simulation                                                     | 26 |

| 2.4 | Sensitivities $a_j$ resulting from the least square fit for the product $I \cdot t$ of the unloaded                        |    |

|     | oscillator                                                                                                                 | 27 |

| 2.5 | Sensitivities $a_j$ resulting from the least square fit for the oxide thickness $T_{ox}$ .                                 |    |

|     | $(Design 1)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                              | 27 |

| 2.6 | Sensitivities $a_j$ resulting from the least square fit for the overlap capacitance pa-                                    |    |

|     | rameter <b>cgds</b> . (Design 2) $\ldots$ | 28 |

| 2.7 | Simulation and measurement results for test chip 1 and 2                                                                   | 36 |

| 2.8 | Measurement Results and Comparison with Manufacturing Acceptance Parameters                                                |    |

|     | (MAP)                                                                                                                      | 44 |

| 2.9 | MOS diode model parameters                                                                                                 | 52 |

| 3.1 | Inverter dimensions for both PMOS and NMOS passgate oscillators.                                                           | 58 |

| 3.2 | Pin description for the variability test chip                                                                              |    |

|     |                                                                                                                            |    |

| 4.1 | Ring oscillator dimensions.                                                                                                |    |

| 4.2 | Simulation and measurement results                                                                                         | 73 |

## Chapter 1

# Introduction

Modeling the behavior of integrated devices is essential for the design process of integrated circuits. With the help of simulations, the designer develops his/her product to fulfill the specifications the customer requires. To completely characterize the product, prototypes are produced and measurements compared to simulations and specifications. Therefore, the specific device models need to be appropriately accurate to correctly predict the behavior of the integrated circuit.

A fundamental step of modeling devices consists of determining how physical properties influence the device operation. A field effect transistor's (FET) capacitance, for instance, strongly influences the switching speed and parasitic effects such as the Miller capacitance. It is therefore necessary to accurately determine the gate oxide thickness that specifies the transistor's gate and overlap capacitances. Furthermore, this particular property is part of a set of parameters that semiconductor foundries provide to characterize their different technologies. Thus, monitoring the gate oxide thickness early on during fabrication allows the foundry to center its line and achieve improved conformity between different lots, for which device parameters can vary quite considerably otherwise.

This project investigates the feasibility of ring oscillator structures for parameter measurements. The first part in Chapter 2 focuses on transistor capacitances, specifically the overlap capacitance and oxide thickness. Ring oscillators with dozens of stages are designed with additional load transistors in each stage. The load capacitances are determined through frequency and current measurements. Compared to DC measurements, this technique is dynamic and more closely resembles device operation on products. Moreover, by using many stages in series, statistical variations are reduced and average values obtained for the parameters. Ideally, matching influences are thereby reduced and only process variations are of significance. Thus, the variation of the parameter from die to die, wafer to wafer and lot to lot can be monitored. The goal is to develop circuits and implement them in scribe lines to monitor the parameters and their variation.

Chapter 3 deals with the threshold voltage variation. Ring oscillators can be designed to be very sensitive to a specific parameter whose variation strongly influences the oscillation frequency. Compared to the structures in Chapter 2, these oscillators comprise only a small number of stages. Therefore, mismatch between the devices will have the greatest impact on the measurement results. The influence of process variation is minimized by comparing only devices in close proximity to each other. Again the goal is to develop a circuit for scribe line monitoring.

Finally, ring oscillators are used to benchmark transistor models. In Chapter 4 this is demonstrated for high voltage FET devices for which simulations are compared to measurements on silicon. The performance of the device models can thus be evaluated.

## Chapter 2

# **CV** Characterization

In this chapter MOSFET capacitances are investigated with the help of ring oscillators (RO). To begin with a study of the available literature on CV characterization with ring oscillators is conducted in section 2.1, with a focus on a number of papers published by a group at IBM [1–3] and the BSIM3v3 manual [4]. In section 2.2 measurement techniques to extract the oxide thickness and overlap capacitances are developed. The corresponding circuits are introduced in section 2.3. The goal is to develop circuits that can be used to measure manufacturing acceptance parameters (MAP). The layout for these circuits will be introduced in section 2.4. Sections 2.5 and 2.6 deal with the measurement setup and measurement results. Finally, a conclusion regarding this measurement technique will be given in section 2.7.

### 2.1 Literature Studies

#### 2.1.1 Capacitance Measurement with Ring Oscillators

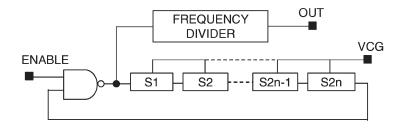

Ring oscillators are built up of n identical stages connected in a loop as illustrated in figure 2.1. The resulting oscillation is the consequence of the delay each stage introduces when it switches states. The frequency f can be determined as in equation (2.1), where d is the delay per stage and n the number of stages. This is a good approximation for  $n \gg 1$  consistent with Bhushan *et al.* [3].

$$f = \frac{1}{2 \cdot n \cdot d} \tag{2.1}$$

As mentioned, the delay d is the time it takes a single stage to change states from low to high. According to [1] it is characterized by the series resistance  $R_{sw}$  in the respective path and the capacitances  $C_s$  that need to be charged.

$$d = R_{sw} \cdot C_s \tag{2.2}$$

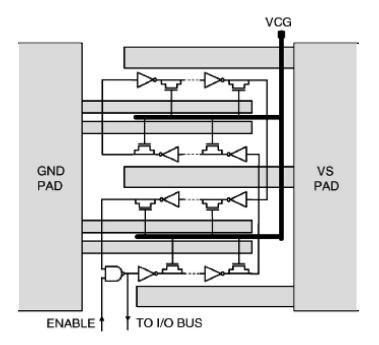

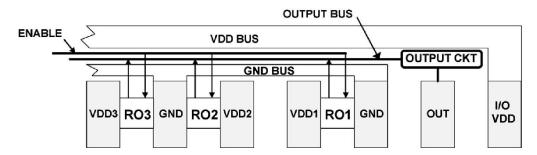

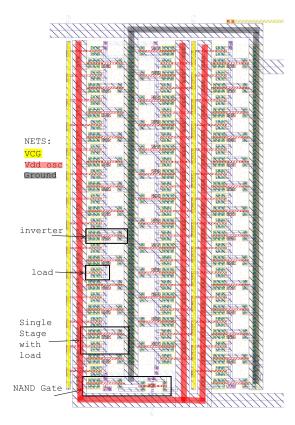

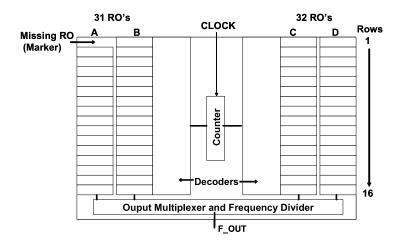

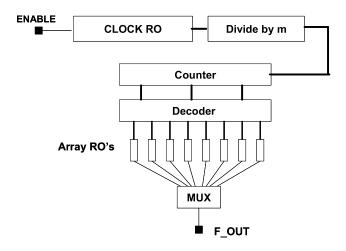

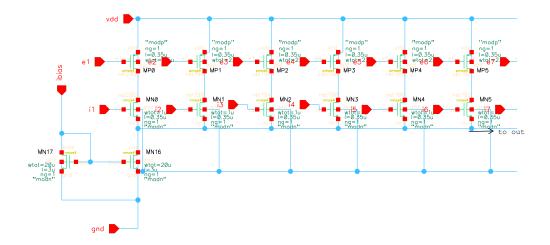

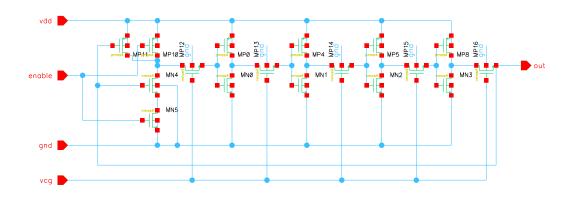

Figure 2.1: Schematic of a ring oscillator structure taken from [3]. Here, the oscillator is made up of 2n identical inverter stages with loads  $(S_1...S_{2n})$ , a NAND gate to enable the oscillation and a frequency divider. V<sub>CG</sub> is the voltage applied to the MOSFET loads between each inverter stage.

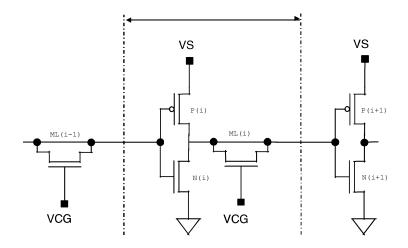

Therefore, inserting a capacitive load  $C_L$  in between each stage – for example a MOSFET load as in figure 2.2 – increases the delay proportional to  $C_L$ . Given in [3], the capacitance  $C_S$  of one stage is calculated as

$$C_s = \frac{2d(I_{DDA} - I_{DDQ})}{V_s} \tag{2.3}$$

with  $I_{DDA}$  and  $I_{DDQ}$  being the average oscillator current in its oscillating and quiescent states and  $V_s$  the inverter's supply voltage. Comparing loaded ring oscillators – i.e. ring oscillators with an additional load between each stage – with a reference oscillator solely comprised of inverter stages makes it possible to accurately measure the load capacitances. The result is an average value over the number of stages n. For the designs in [3] the quiescent current  $I_{DDQ}$  plays a more prominent role as they are implemented in a 65-nm technology. This project, however, is designed in a 0.35- $\mu$ m technology in which leakage currents are orders of magnitudes smaller than the currents in the oscillating state. Thus, their influence is negligible.

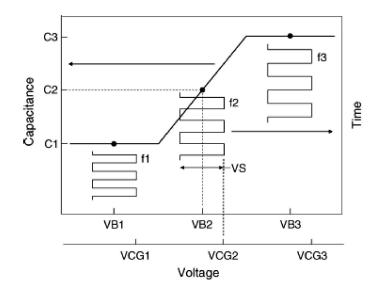

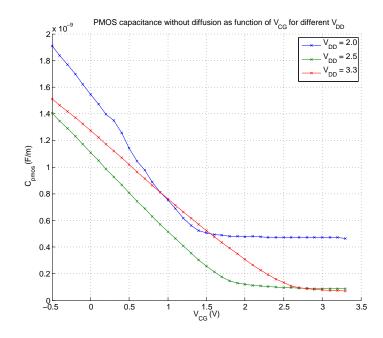

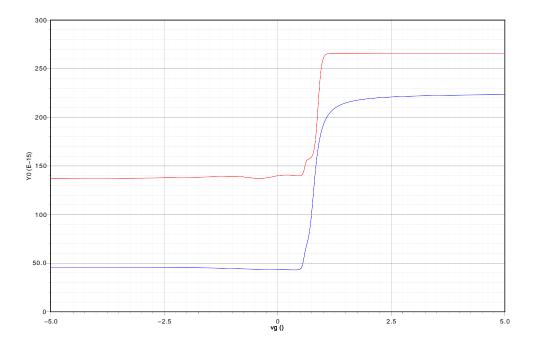

One measurement described in [3] is a CV characteristic of the MOSFET load. The gate voltage  $V_{CG}$  is increased after each capacitance measurement so that the transistor passes through all of its operating regions. The load capacitance is then plotted as a function of gate voltage. As the voltage at the drain and source oscillates between the negative and positive supply voltage of the inverter stages, the resulting capacitance represents an average over a cycle of oscillation. Figure 2.3 depicts what the result should look like theoretically.

When the transistor is switched off only the gate to drain and gate to source overlap capacitances are active, which corresponds to capacitance  $C_1$  in fig. 2.3. This is the case as only capacitances that are recharged each period have an influence on the delay. Once the transistor is switched on and a channel has formed, the gate to channel capacitance increases the overall load capacitance,  $C_3$ . In between, the channel is forming and the capacitance increases linearly. From the capacitance in inversion and depletion an estimate for the active electrical channel length can be obtained. A silicon on insulator (SOI) process is used for the described technique. For a standard CMOS technology parasitic effects due

Figure 2.2: Schematic of one cell of a loaded ring oscillator as illustrated in [3];  $P_{(i)}$  and  $N_{(i)} \cdots$  inverter transistors,  $ML_{(i)} \cdots$  load transistor,  $V_S \cdots$  supply voltage,  $V_{CG} \cdots$  gate voltage of load transistor.

Figure 2.3: The load capacitance is measured for different gate voltages  $V_{CG}$  to obtain the above curve which is taken from [3]. The results  $C_1, C_2$  and  $C_3$  are values averaged over the voltage swing  $V_s$  at the drain and source. The average voltage is denoted as  $V_B$ .

to the interaction with bulk, i.e diffusion capacitances, channel to bulk capacitance and bulk to substrate capacitance, also need to be considered.

#### 2.1.2 Capacitance Modeling in BSIM3v3

The FET model used in this project is the BSIM3v3 model [4]. A basic calculation of a MOSFET capacitance is given in equation (2.4). Bulk capacitances are not included in this equation. The gate to drain and gate to source potentials are the same for these considerations and thus the overlap capacitances for the respective regions. This is accounted for by the parameter **cgds** in equation (2.4). The quantity C(W, L) represents the sum of the overlap capacitances and the oxide capacitance as function of width W and length L of the transistor, and is given by

$$C(W,L) = \mathbf{C_{ox}} \cdot \underbrace{(W - 2 \cdot \delta W)}_{L_{\text{eff}}} \cdot \underbrace{(L - 2 \cdot \delta L)}_{L_{\text{eff}}} + \mathbf{cgbo} \cdot \underbrace{(L - 2 \cdot \delta L)}_{L_{\text{eff}}} + 2 \cdot \mathbf{cgds} \cdot \underbrace{(W - 2 \cdot \delta W)}_{W_{\text{eff}}}$$

(2.4)

with the gate capacitance parameter  $\mathbf{C}_{ox}$ , gate to bulk overlap capacitance parameter **cgbo** and gate to drain/source overlap capacitance parameter **cgds**. L and W are the drawn length and width respectively. The parameter  $\mathbf{C}_{ox}$  depends on the permittivity  $\epsilon = \epsilon_{SiO_2} \cdot \epsilon_0$  and the thickness  $\mathbf{T}_{ox}$  as in

$$\mathbf{C_{ox}} = \frac{\epsilon}{\mathbf{T_{ox}}}.$$

(2.5)

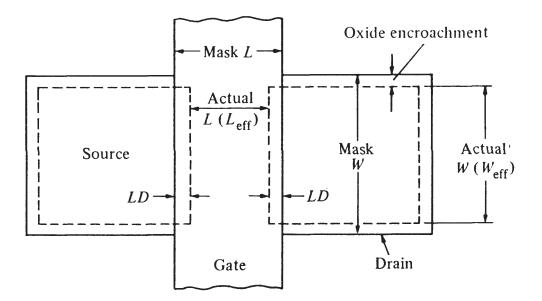

The effective channel length  $L_{\text{eff}}$  and width  $W_{\text{eff}}$  are calculated with equations (2.6) - (2.9) which are taken from the BSIM3v3 CV model [4]. Due to unideal effects during the fabrication process, the device's actual geometry deviates from the drawn values. Some of these effects are illustrated in figure 2.4. The effective length of the transistor is mostly determined by the lightly doped drain (LDD) and source implants. The transistor is entrenched by field oxide, which does not stop abruptly once it reaches the transistor's boundaries but grows to a certain amount into the device. The width is decreased by this effect called bird's beak. Furthermore, the gate does not grow perfectly flat and rectangular but varies in thickness and area. This influences all of the device's capacitances toward the gate.

$$\delta W = \mathbf{DWC} + \frac{\mathbf{Wl}}{L^{\mathbf{Wln}}} + \frac{\mathbf{Ww}}{W^{\mathbf{Wwn}}} + \frac{\mathbf{Wwl}}{L^{\mathbf{Wln}} \cdot W^{\mathbf{Wwn}}}$$

(2.6)

$$\delta L = \mathbf{DLC} + \frac{\mathbf{Ll}}{L^{\mathbf{Lln}}} + \frac{\mathbf{Lw}}{W^{\mathbf{Lwn}}} + \frac{\mathbf{Lwl}}{L^{\mathbf{Lln}} \cdot W^{\mathbf{Lwn}}}$$

(2.7)

$$L_{\rm eff} = L - 2 \cdot \delta L \tag{2.8}$$

$$W_{\rm eff} = W - 2 \cdot \delta W \tag{2.9}$$

Figure 2.4: Active area of a FET transistor as illustrated in [5]. The drawn length is reduced by two times LD and the width by the oxide encroachment on both sides. LD corresponds to  $\delta L$  in equation (2.8).

Further attention needs to be paid to the parameter  $\mathbf{cgds}$  from equation (2.4). The drain and source are connected to the same potential as stated above. Due to the symmetry MOSFET devices generally show, it therefore suffices to inspect only one side. Instead of keeping separate parameters for the gate to drain and gate to source overlap their influence is combined in the parameter  $\mathbf{cgds}$ .

The overlap capacitances are calculated in the BSIM3v3 model according to the following equations [4]. CGDO and CGDL are the overlap capacitance parameters.

$$T0 = V_{gd} + \delta \quad (\delta = 0.02)$$

(2.10)

$$T1 = \sqrt{(T0 \cdot T0 + 4.0 \cdot \delta)} \tag{2.11}$$

$$T2 = 0.5 \cdot (T0 - T1) \tag{2.12}$$

$$T3 = \sqrt{\left(1 - \frac{4 \cdot T2}{\mathbf{Ckappa}}\right)} \tag{2.13}$$

$$\mathbf{cgds} = \mathbf{CGDO} + \mathbf{CGDL} - \mathbf{CGDL} \cdot \left(1 - \frac{1}{T3}\right) \cdot \left(0.5 - \frac{0.5 \cdot T0}{T1}\right)$$

(2.14)

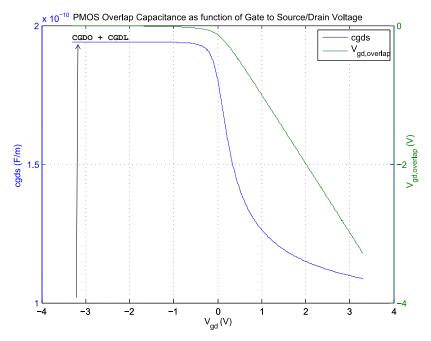

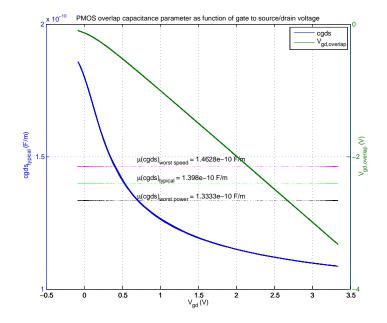

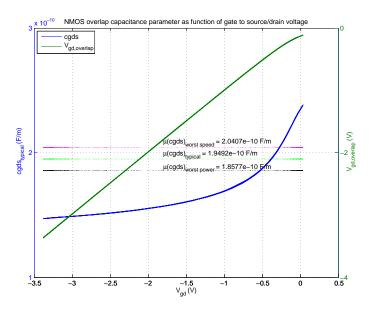

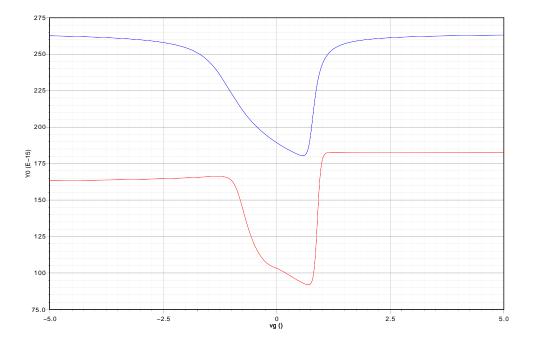

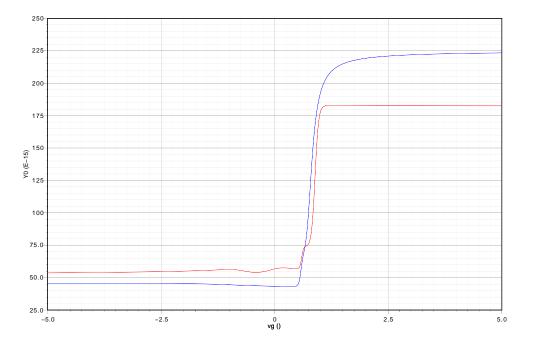

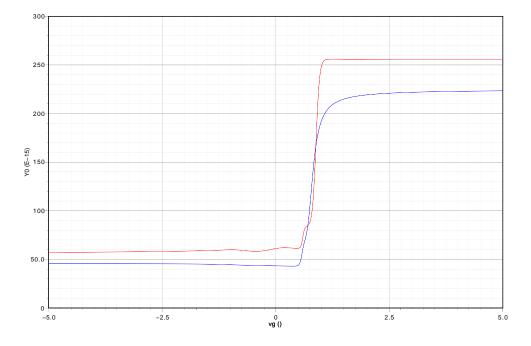

with the BSIM3v3 parameters **CGDO**, **CGDL**, **Ckappa** and  $\delta$ . Plotting these equations as function of gate to drain voltage  $V_{gd}$  yields figure 2.5a for a PMOS device. The overlap capacitance is modeled as a function of gate to drain/source voltage ( $V_{gd}$ ). For negative gate to drain voltages (positive for NMOS), the model parameter  $V_{gd,overlap} = T2$  (2.12) is approximately zero and constant. Also constant is the gate to drain overlap capacitance, which has a value of **CGDO** + **CGDL**. Figure 2.5b shows the result for a NMOS device.

(a) PMOS gate to drain overlap capacitance parameter **cgds** and  $V_{gd,overlap}$  as a function of  $V_{gd}$ . **CGDO** =  $8.6 \cdot 10^{-11} \frac{\text{F}}{\text{m}}$ ; **CGDL** =  $1.08 \cdot 10^{-10} \frac{\text{F}}{\text{m}}$ ; **Ckappa** =  $6 \cdot 10^{-01}$ V.

(b) NMOS gate to drain overlap capacitance parameter **cgds** and  $V_{gd,overlap}$  as a function of  $V_{gd}$ . **CGDO** =  $1.2 \cdot 10^{-10} \frac{\text{F}}{\text{m}}$ ; **CGDL** =  $1.31 \cdot 10^{-10} \frac{\text{F}}{\text{m}}$ ; **Ckappa** =  $6 \cdot 10^{-01}$ V.

Figure 2.5: Overlap voltage  $V_{gd,overlap}$  from equation (2.12) and overlap capacitance parameter **cgds** from (2.14) plotted as functions of gate drain voltage  $V_{gd}$ .

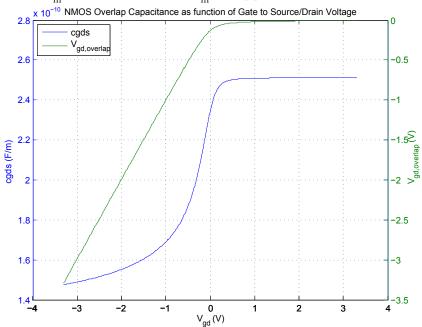

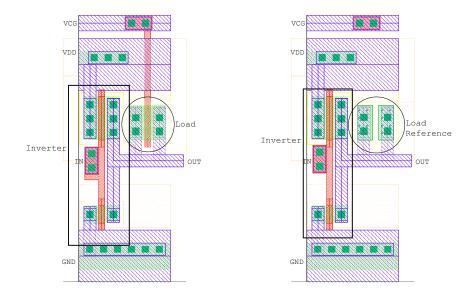

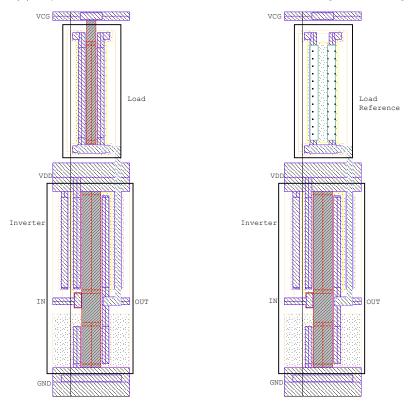

(b) Schematic layout of an inverter stage with a MOSFET load as shown in [1].

Figure 2.6: Schematic layout of inverter cells for loaded and reference oscillators.

The dependency on the gate voltage complicates the methods inspected so far enormously. Especially the technique for estimating  $L_{\text{eff}}$  is questionable, at least using the BSIM3v3 models. Since the overlap capacitances vary with the gate voltage,  $(C_i - C_d)$  – the capacitance of the MOSFET in inversion minus the capacitance in depletion – does not only depend on the channel, which is an important assumption for extracting  $L_{\text{eff}}$ . Returning to the capacitance model from equation (2.4), it is essential to accurately determine its parameters to get a correct capacitance model. Theoretically, these could be extracted if the capacitance of the load is measured for different combinations of W and L. This is the focus of the next section and will therefore not be further elaborated here.

#### 2.1.3 Layout Considerations

A crucial step for this measurement technique to be accurate is the layout of the circuit. The device currents in each inverter vary by a certain percentage due to mismatch which directly influences the delay per stage. Moreover, the extracted capacitance of the reference oscillator is subtracted from the capacitance of the loaded oscillator to correctly determine the load capacitance. In order to accomplish this, the inverter stages and parasitic elements in the unloaded oscillator need to be ideally identical with the respective devices in the loaded oscillator. Thus, the most important aspect of the layout is the best possible matching of the parasitic elements. With a good layout a frequency mismatch of smaller 1% is possible according to Bhushan *et al.* [3]. An example for the loaded and unloaded stage can be seen in figures 2.6a and 2.6b, where the only difference between the two stages is the transistor that makes up the load. Everything else is identical.

Figure 2.7: Basic layout of a ring oscillator for scribe line monitoring taken from [3].

Other considerations depend on the intended usage of the test structures. Ring oscillators designed for process monitoring should be preferably as small as possible in order to fit into a scribe line, for example as shown in figure 2.7. A layout using one metal layer only makes the test structures available as early as possible during fabrication [1].

Designs for parameter extraction each need their separate supply if absolute values are to be determined. Otherwise, the quiescent current will be the sum of  $I_{DDQs}$  of all the ring oscillators connected to the same supply. Oscillators which are put directly on a product circuit to monitor performance and aging are necessarily connected with the circuit's supply. Thus, only performance measurements are possible, for example the change in frequency over time [3]. These considerations regarding the supply are necessary when the quiescent current has a noticeable effect. For structures designed in a 0.35- $\mu$ m

Figure 2.8: Schematic layout of individual ring oscillator designs illustrated in [1].

Figure 2.9: Schematic layout of macros containing several ring oscillators shown in [1].

technology, the quiescent current is orders of magnitudes smaller than the current drawn during oscillations and can therefore be neglected. Figures 2.8 and 2.9 present two different cases. In the first layout in figure 2.8 each ring oscillator has its own supply pad. The second example, on the other hand, requires much less space as a number of ring oscillators share one supply.

### 2.2 Parameter Extraction

The basic idea is to extract the parameters in equation (2.4) from frequency and current measurements of ring oscillators with different load dimensions. Those are specifically the oxide capacitance parameter  $C_{ox}$  which is inversely proportional to the oxide thickness  $T_{ox}$ , the gate to drain/source overlap **cgds** and gate to bulk overlap **cgbo** capacitance parameters. Let us first look at the case with no corrections to the width and length (2.15) and without parasitics like diffusion capacitances and channel to bulk capacitance.

$$C = \mathbf{C}_{\mathbf{ox}} \cdot W \cdot L + \mathbf{cgbo} \cdot L + 2 \cdot \mathbf{cgds} \cdot W$$

(2.15)

If for example the length of the load transistor is changed  $(L_1 < L_2)$ , then the capacitance should change by

$$\Delta C = \underbrace{\left(\mathbf{C_{ox}} \cdot W + \mathbf{cgbo}\right)}_{a_{\Delta L}} \cdot \underbrace{\left(L_2 - L_1\right)}_{\Delta L} \tag{2.16}$$

where  $a_{\Delta L}$  is the rate of change with respect to the length of the load. Obviously,  $a_{\Delta L}$  is a function of the width of the load transistor. Thus, its slope can be extracted by changing the width  $(W_1 < W_2)$ .

$$\Delta a_{\Delta L} = \mathbf{C}_{\mathbf{ox}} \cdot \underbrace{(W_2 - W_1)}_{\Delta W} \tag{2.17}$$

The slope  $\mathbf{C}_{\mathbf{ox}}$  of equation (2.17) corresponds to the oxide thickness  $\mathbf{T}_{\mathbf{ox}}$  as in  $\mathbf{C}_{\mathbf{ox}} = \frac{\epsilon_{SiO2}}{\mathbf{T}_{\mathbf{ox}}}$ . Thus, for this ideal case, the oxide thickness can be measured with the following oscillators:  $RO_1$  ( $W_1$ ,  $L_1$ ),  $RO_2$  ( $W_1$ ,  $L_2$ ),  $RO_3$  ( $W_2$ ,  $L_1$ ) and  $RO_4$  ( $W_2$ ,  $L_2$ ).  $W_i$  and  $L_i$  are the width and length of the transistor load, the inverters themselves remain the same. **cgds** can be extracted by calculating the regression line for equation (2.15) with respect to L and calculating the slope of the resulting offset  $b_{\Delta L}$ .

$$C = \underbrace{(\mathbf{C}_{\mathbf{ox}} \cdot W + \mathbf{cgbo})}_{a_{\Delta L}} \cdot L + \underbrace{2 \cdot \mathbf{cgds} \cdot W}_{b_{\Delta L}}$$

(2.18)

The same procedure results in **cgbo** if it is first performed with respect to W and then L.

$$C = \underbrace{(\mathbf{C}_{\mathbf{ox}} \cdot L + 2 \cdot \mathbf{cgds})}_{a_{\Delta W}} \cdot W + \underbrace{\mathbf{cgbo} \cdot L}_{b_{\Delta W}}$$

(2.19)

As only capacitance differences are processed there is no need for a reference oscillator, provided that the inverter stages introduce the same delay in every macro.

Applying this extraction method to equation (2.4), where the width and length corrections are included, yields the same result for the oxide thickness. **cgds** and **cgbo**, however, are not so easily determined anymore. The offsets  $b_{\Delta L}$  and  $b_{\Delta W}$  now become

$$b_{\Delta L} = 2 \cdot \mathbf{cgds} \cdot (W - 2 \cdot \delta W) - [\mathbf{C_{ox}} \cdot (W - 2 \cdot \delta W) + \mathbf{cgbo}] \cdot 2 \cdot \delta L$$

(2.20)

$$b_{\Delta W} = \mathbf{cgbo} \cdot (L - 2 \cdot \delta L) - [\mathbf{C}_{\mathbf{ox}} \cdot (L - 2 \cdot \delta L) + 2 \cdot \mathbf{cgds}] \cdot 2 \cdot \delta W.$$

(2.21)

Without knowledge of  $\delta L$  and  $\delta W$ , cgds and cgbo cannot be extracted anymore.  $\delta L$  and  $\delta W$  could be taken from other measurements. However, this would also introduce additional uncertainties.

These considerations assume that all capacitances are active. As stated in section 2.1 only capacitances which are charged each period effectively influence the stage delay. Consequently, the gate to drain/source capacitance can be isolated by turning the load transistor off. If parasitic effects are still neglected, the total load capacitance is then simply given by

$$C = 2 \cdot \mathbf{cgds} \cdot (W - 2 \cdot \delta W). \tag{2.22}$$

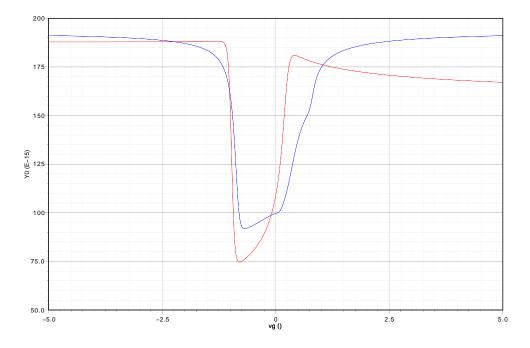

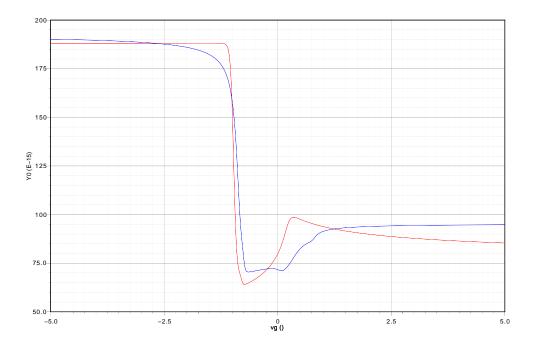

Now two oscillators with load transistors of different widths suffice to extract **cgds**. As the overlap capacitance is modeled as a function of the gate to drain/source voltage, the measured value will represent an average over the range the voltage swings at those terminals. This is equal to the inverter supply voltage. The overlap capacitance parameter is constant only when the transistor is turned on and the source and drain regions are in accumulation. Figure 2.5a for instance shows the overlap parameter for a PMOS device. An estimate for this average value can be seen in figures 2.10a and 2.10b. It is obtained by calculating the capacitance parameter at each point of a simulated waveform and averaging over the resulting values.

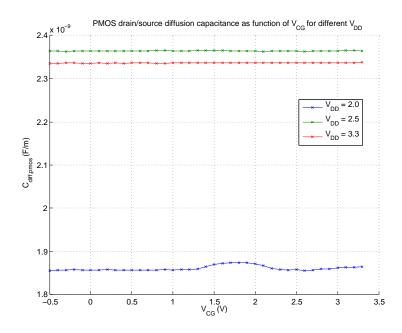

The parasitics which have been neglected up to now are the drain and source to bulk capacitances, the channel to bulk capacitance and the bulk to substrate capacitance. The

(a) PMOS gate to drain overlap capacitance parameter  $\mathbf{cgds}_{\mathrm{typical}}$  and  $V_{gd,overlap}$  as a function of  $V_{gd}$ . All values are calculated for simulated data points in the region from 0V to 3.3V. Also shown are the overlap capacitance parameters calculated with worst case conditions  $\mathbf{cgds}_{\mathrm{worst power}}$  and  $\mathbf{cgds}_{\mathrm{worst speed}}$ .

(b) NMOS gate to drain overlap capacitance parameter  $\mathbf{cgds}_{\mathrm{typical}}$  and  $V_{gd,overlap}$  as a function of  $V_{gd}$ . All values are calculated for simulated data points in the region from 0V to 3.3V. Also shown are the overlap capacitance parameters calculated with worst case conditions  $\mathbf{cgds}_{\mathrm{worst\ power}}$  and  $\mathbf{cgds}_{\mathrm{worst\ speed}}$ .

Figure 2.10: Expected mean values for NMOS and PMOS overlap capacitance parameters

channel to bulk capacitance makes it impossible to derive the oxide thickness from the measurements described above. The reason is that in this case it is in parallel to the gate to channel capacitance once the device is turned on. Thus, its influence must be eliminated. This is achieved by shorting source, drain, and bulk. Now when the channel has formed the channel potential and bulk potential vary synchronously. Furthermore, the drain to bulk and source to bulk capacitances are also deactivated. The only parasitic capacitance remaining is the bulk to substrate capacitance. To eliminate it the bulk well is included in the reference oscillator. This will increase the size of the test structure considerably as a separate reference is now needed for each loaded oscillator. But otherwise the measurement extraction does not work for the investigated devices. The reference is now basically the same oscillator as the respective loaded oscillator without the load transistor gates. Another drawback is that basic NMOS devices, which are placed directly in the substrate, cannot be used for the oxide thickness extraction. Moreover, the above considerations also do not work for a test structure to measure cgds. Equation (2.22) holds when the only capacitance active is the overlap capacitance. However, connecting the bulk to source and drain will also activate the bulk to gate capacitance. Thus, to measure the overlap

and drain will also activate the bulk to gate capacitance. Thus, to measure the overlap capacitance the bulk is tied to a fixed potential and the transistor turned off. Then, comparing that to a reference that takes the source and drain to bulk capacitances into account, should make it possible to deduce the overlap capacitance. This works for both NMOS ans PMOS transistors. Consequently, different test structures are necessary to extract the oxide thickness and the overlap capacitance. In total that would be twelve oscillators – eight for the oxide thickness measurement and four for the measurement of cgds.

### 2.3 Ring Oscillator Circuit Design

#### 2.3.1 Simulation Environment in Matlab

Given the nature of ring oscillators, creating a netlist mostly consists of copying the initial stage for as how many times as stages are desired. This type of work can be elegantly done by programming the structure in a loop, reducing the work from placing n stages to placing one stage. Matlab is an excellent tool for handling this type of work, which is why the bulk of the design process is done with the help of Matlab scripts. Furthermore, Matlab is a powerful tool for data analysis – both simulated and measured data – rendering the use of extraction and calculation methods possible that can be verified with simulated data.

The spectre simulator netlist is created with the help of Matlab scripts as stated above. Specifically, for the overlap capacitance characterization structure, these can be seen in the appendix in section A. The script writeStage1OV.m shown on page 81 creates the basic oscillator stage. It assembles a subcircuit consisting of the inverter and the load. These subcircuits are then assembled in the script writeNet\_ov\_nand.m (page 79). The task of writing the framework for the netlist is accomplished by writehead.m and writeOptions\_ov.m which can be seen on pages 78 and 83. Although there are some differences between the loaded and reference ring oscillator, the basic structure of the netlist remains

the same. A complete netlist for a loaded ring oscillator can be seen in the appendix on page 86 following the mentioned scripts.

The oscillation period and average current consumption are calculated in getdataoverlap.m (page 89). To accomplish this, the indices where the amplitude is closest to  $\frac{V_{DD}}{2}$  on every rising edge are saved. The period for each oscillation is calculated with these indices and the average taken. As the data points are not spaced equally around  $\frac{V_{DD}}{2}$ , a slight variation will result. Typically, the standard deviation is in the range of 0.1% and therefore  $\frac{0.1\%}{\sqrt{n_p}}$  for the mean value, where  $n_p$  is the number of periods. The average current is calculated by numerically integrating the current over time using the trapezoidal rule and dividing by the total time.

#### 2.3.2 Design of the Ring Oscillator Test Structures

With the simulation environment in place, the initial design was chosen to have 41 inverter stages. The reason for this choice was that a 41 stage oscillator has already been implemented for a standard 0.35- $\mu$ m process. Although the inverter stages for the CV structures are smaller, the frequencies are not too far apart. Thus, the existing ring oscillator can be used to compare measurements done with the setup described in section 2.5 with monitored data in order to determine whether the setup is adequately accurate.

#### First Simulations with Ideal Capacitor Load

After having set up a design for the inverter stage, the next step was to verify the accuracy of the extraction method. First, an ideal capacitor is used as load for the inverter stages as illustrated in figure 2.11 to determine the accuracy of this extraction. The capacitance is calculated as

$$C_{cap} = C_{ox} \cdot W \cdot L$$

$$C_{ox} = \frac{\epsilon}{T_{ox}}.$$

(2.23)

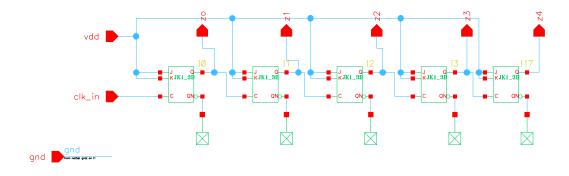

The capacitance is extracted from the data as described in equation (2.3) and the resulting values compared to the actual capacitance of equation (2.23). With the design in figure 2.11 the capacitance was simulated with 0.2% accuracy (simulated:  $\mathbf{T}_{ox} = 7.736$ nm; model value:  $\mathbf{T}_{ox} = 7.754$ nm). The simulation data can be seen in table 2.1.

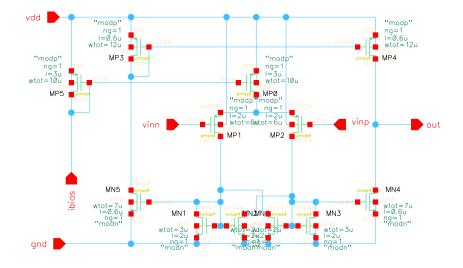

#### **Ring Oscillator with PMOS Load**

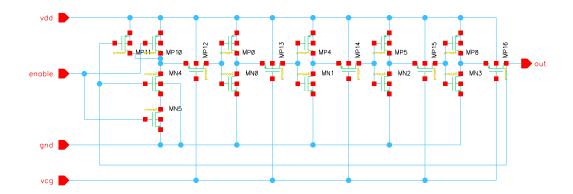

Having reached an appropriate accuracy, the ideal capacitor was replaced with the PMOS load as shown in figure 2.12. The simplest model available in the design kit was first investigated, to ensure that the fundamental effects are understood before adding parasitic effects. The reason for choosing a PMOS device over a NMOS for the initial design is because the bulk of the NMOS cannot be shorted to source and drain as described in the previous section. The parameters of interest are  $T_{ox}$ , cgbo and cgds from equation (2.4).

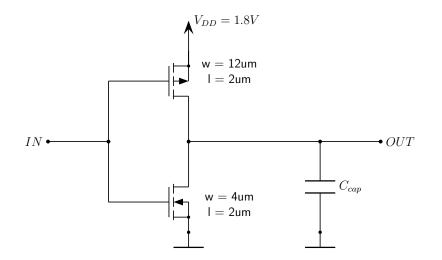

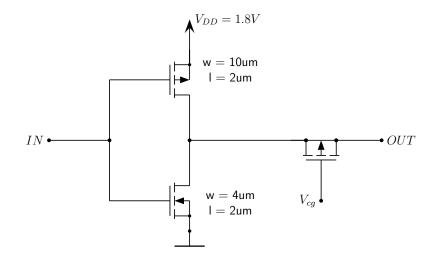

Figure 2.11: Ring oscillator stage with ideal capacitor as load. The complete ring oscillator consists of 41 of these stages.

Table 2.1: Simulation Data for ring oscillator with an ideal capacitor as load.  $I_{DDA}$ ...average current consumption, f...oscillation frequency,  $w_{pl}, l_{pl}$ ...width and length of load, T...oscillation period.

| $I_{DDA}$   | f          | $w_{pl}$ | $l_{pl}$ | $\sigma(T)$ | Т           |

|-------------|------------|----------|----------|-------------|-------------|

| А           | Hz         | m        | m        | s           | s           |

| 9.59071e-05 | 2.20225e06 | 1e-05    | 1e-05    | 1.7e-11     | 4.54080e-07 |

| 9.54438e-05 | 6.70461e05 | 1e-05    | 4e-05    | 3e-11       | 1.49151e-06 |

| 9.54438e-05 | 6.70461e05 | 4e-05    | 1e-05    | 3e-11       | 1.49151e-06 |

| 9.53120e-05 | 1.77277e05 | 4e-05    | 4e-05    | 1.9e-10     | 5.64088e-06 |

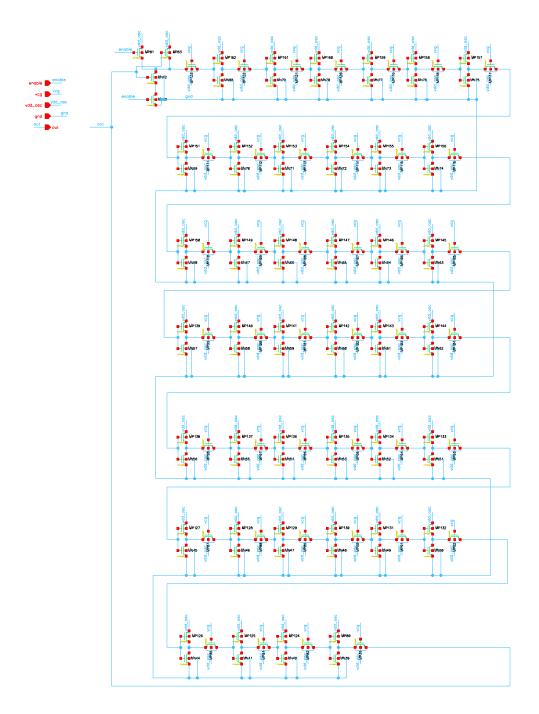

Several simulations with different geometries for the loads were performed until an adequate accuracy for the parameters was reached. It was found that the extraction process does not work very well with minimum size devices. Especially the structure to measure  $\mathbf{T}_{ox}$  requires big devices, which disqualifies it as a monitoring structure. In order to reduce the size, the design is reduced to 23 stages instead of 41. The transistor dimensions used in the oscillator design can be seen in table 2.2a for the  $\mathbf{T}_{ox}$  structure and in table 2.2b for the **cgds** structure. The **cgds** design pretty much has minimum size devices. The first layout was done with 41 stages, being just barely too big for a scribe line. Therefore, the number of stages for the **cgds** structure was reduced to 31 after the first test chip.

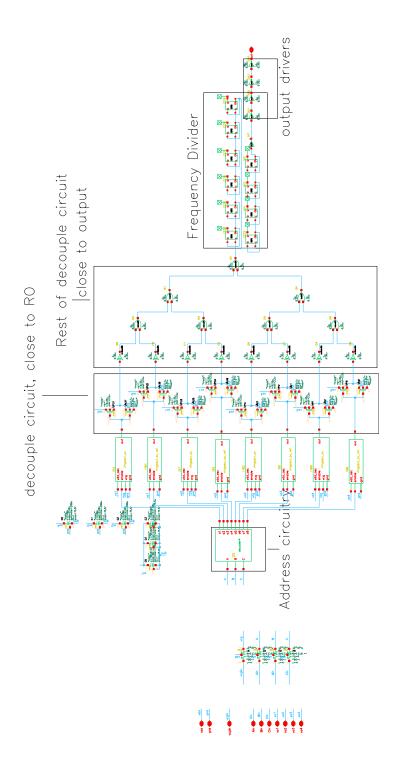

The first stage of each oscillator is made up of a NAND gate. With the NAND gate the oscillator can be enabled or disabled via a digital signal. An address circuitry is used to select each of the oscillators separately. It is a decoder made up of NOR gates that sets the targeted NAND gate high. Thereby, the respective circuit is put into its oscillating state. In case the selection input to the NAND gate is low, the ring oscillator is in a stable

Figure 2.12: Single oscillator stage with a PMOS load. Source, bulk and drain are connected to OUT.

Table 2.2: Device dimensions for design 1 and 2.

(a) Dimensions of the final design for extraction of  $T_{ox}$ . One oscillator has 23 stages. This design will be referenced as design 1.

| RO        | inverter     | inverter width | inverter width | load         | load         |

|-----------|--------------|----------------|----------------|--------------|--------------|

| structure | length       | (NMOS)         | (PMOS)         | width        | length       |

|           | $\mu { m m}$ | $\mu { m m}$   | $\mu { m m}$   | $\mu { m m}$ | $\mu { m m}$ |

| 1         | 2.0          | 4.0            | 10.0           | 10.0         | 1.0          |

| 2         | 2.0          | 4.0            | 10.0           | 10.0         | 3.0          |

| 3         | 2.0          | 4.0            | 10.0           | 20.0         | 1.0          |

| 4         | 2.0          | 4.0            | 10.0           | 20.0         | 3.0          |

(b) Dimensions of the final design for extraction of **cgds**. The oscillators on the first test chip have 41 stages, which are then reduced to 31 stages after that. This design will be referenced as design 2.

| RO        | inverter         | inverter width | inverter width | load         | load         |

|-----------|------------------|----------------|----------------|--------------|--------------|

| structure | length           | (NMOS)         | (PMOS)         | width        | length       |

|           | $\mu \mathrm{m}$ | $\mu { m m}$   | $\mu { m m}$   | $\mu { m m}$ | $\mu { m m}$ |

| 1         | 0.35             | 1.0            | 2.5            | 1.0          | 0.35         |

| 2         | 0.35             | 1.0            | 2.5            | 2.0          | 0.35         |

state with a constant high at its output. All of these gates are designed with minimum dimensions. An additional inverter stage of the same size as the oscillator's is used to decouple the signal from the oscillator. However, if this inverter runs on the same supply as the ring oscillator itself, then the total current will include the current required by that single inverter stage. This is undesired, as it is not part of the oscillator are powered by the supply voltage of a currently deactivated oscillator.

After the inverters the signal passes through a Schmitt trigger, which is placed close to the logical gates of the multiplexer. Due to the long routing from the oscillators at the periphery the Schmitt trigger's input signal can be distorted. The Schmitt trigger has a fixed level at which it triggers and thus restores the edges of the signal without changing the frequency. Then all signals are multiplexed with NAND and NOR gates to the output. Only the oscillating signal will pass through. A large buffer is at the output to drive any capacitances that arise from the measurement devices. The size of each stage is increased in order to provide enough current for the next stage but not drastically increase the capacitance that the previous stage sees. Schematics of the designs can be seen in appendix A, figures A.1, A.2 and A.3.

#### 2.3.3 Matching Analysis and Sensitivity Investigations

#### Matching Analysis

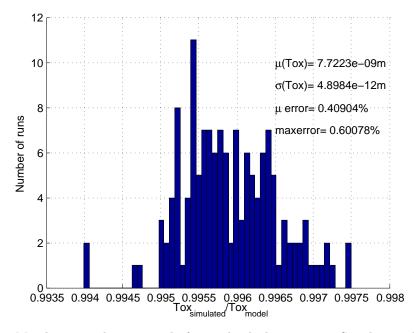

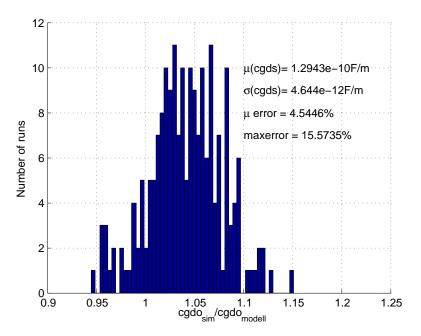

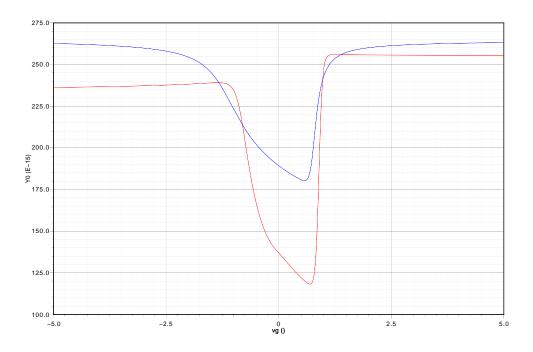

The accuracy with which the measurements can be expected to work is determined with the help of Monte Carlo mismatch simulations. To this end, the designs are simulated with around 200 Monte Carlo runs. The results are shown in figures 2.13 and 2.14. The supply voltage for design 1 is set at 1.8V to diminish the range over which the capacitance is averaged. The inverter supply voltage for design 2 had to be raised to higher values than in design 1, otherwise the results from the analysis are too inaccurate due to mismatch. With 1.8V an accuracy of  $\mu \text{error} = 28\%$  is reached for the mean value of design 2, compared to the  $\mu \text{error} = 4.5\%$  shown in figure 2.14.

The maximum errors that are given in the plots are calculated with nominal values from the simulation models. For the overlap capacitance parameter, the value averaged over the voltage range as pointed out in figures 2.10a and 2.10b is used as reference value. Especially the oxide capacitance measurement can be performed with high accuracy.

#### Sensitivity Analysis

In order to derive a mathematical model for an unknown function of which the results are known, the criterion to minimize the least square error is generally used. This means that the deviations of the results calculated with the model are minimized with respect to the actual outcomes. Those outcomes can be for example measurement results or simulation results. Different approaches exist to achieve this goal, for example non-linear fitting algorithms or also linear algorithms. The motivation for deriving such a model in this particular case is to investigate the parameters that have the most influence on the

Figure 2.13: Matching simulation, result for oxide thickness  $\mathbf{T}_{ox}$ . Simulation design 1. The deviation of the average value from the model value is denoted as  $\mu$  error. The maximal occurring deviation as maxerror.  $V_S = 1.8V$ .

Figure 2.14: Matching simulation, result for overlap capacitance parameter **cgds**. Simulation design 2. The deviation of the average value from the model value is denoted as  $\mu$  error. The maximal occurring deviation as maxerror.  $V_S = 3.3V$ .

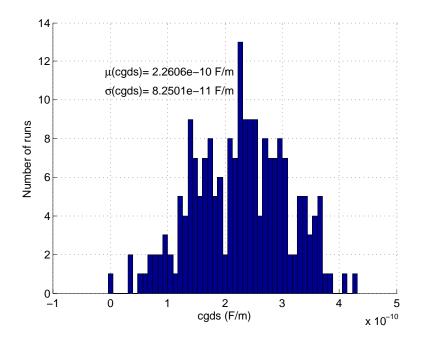

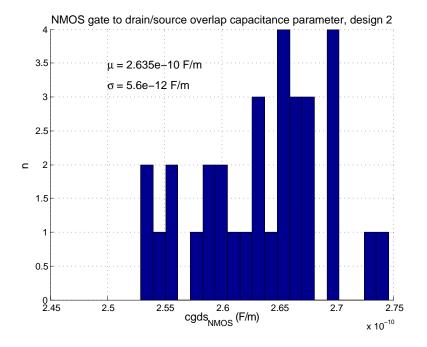

Figure 2.15: Distribution of the simulated overlap capacitance parameter **cgds** with process and mismatch variation for design 2 with a PMOS load.  $V_S = 3.3V$ .

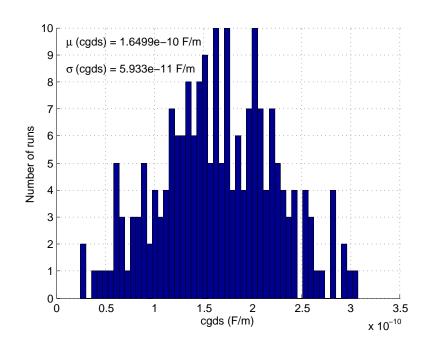

Figure 2.16: Distribution of the simulated overlap capacitance parameter **cgds** with process and mismatch variation for design 2 with a NMOS load.  $V_S = 3.3V$ .

outcome. That is to say that the goal is to find out whether the above introduced designs are especially sensitive toward the parameters that they are intended to measure, or if there are other influences that need to be considered. Therefore, a general least square fit approach is adapted to the problem at hand.

Using numerical techniques as described in [6], especially the methods found in chapter 15.4, a sensitivity analysis with regard to parameters that are varied during a Monte Carlo simulation can be performed. Spectre offers the option for a process Monte Carlo simulation to store each input parameter and its value in separate files. As this is done for each run, the complete parameter variation as it occurs during the simulation is available. The goal is to calculate the sensitivity of the oscillation period toward these parameters. It is hereby assumed that the simulation results for the oscillation period t have a linear dependency on the varied parameters.

The mathematical expression with which the period t is modeled as a function of the Monte Carlo parameters has the following form:

$$t(i) = t_0 + \sum_{j=1}^{M} a_j \cdot \Delta p_j(i) \quad i = 1...N$$

(2.24)

where N is the number of Monte Carlo runs and M the number of varied parameters. The sensitivity of the period t(i) with respect to parameter  $p_j$  is defined as  $a_j$ .  $t_0$  is hereby the value that results when the parameters  $p_j$  take on their mean value, i.e.  $\Delta p_j = 0$ . With the mean values and the distribution around them, which are both gained from simulations, matrix **A** and vector **b** can be formed.

$$A_{ij} = \frac{\Delta p_j(i)}{\sigma_i}$$

$$b_i = \frac{t(i) - t_0}{\sigma_i} = \frac{\Delta t(i)}{\sigma_i}$$

(2.25)

with  $\sigma_i$  being the standard deviations of the measurement error of the  $i^{th}$  data point. These can be set to the constant value  $\sigma_i = 1$  if they are not known according to [6]. This will be done for the following equations. The solution to equation (2.24) can be found by minimizing the merit function  $\chi^2$ , which is defined as

$$\chi^{2} = \sum_{i=1}^{N} \left[ \Delta t(i) - \sum_{j=1}^{M} \mathbf{a}_{j} \cdot \Delta p_{j}(i) \right]^{2}.$$

(2.26)

The minimum occurs for a set of parameters **a** for which the derivative of  $\chi^2$  with respect to the parameters  $a_j$  vanishes.

$$0 = \sum_{i=1}^{N} \left[ \Delta t(i) - \sum_{k=1}^{M} \mathbf{a}_k \cdot \Delta p_k(i) \right] \cdot \Delta p_j(i) \quad \text{for } j = 1...M$$

(2.27)

Using matrix **A** and vector **b** the calculations are:

$$\begin{aligned} [\alpha] &= \mathbf{A}^T \cdot \mathbf{A} \\ [\beta] &= \mathbf{A}^T \cdot \mathbf{b} \\ \mathbf{a} &= [\alpha]^{-1} \cdot [\beta] \,. \end{aligned}$$

(2.28)

Inverting singular or badly conditioned matrices can be problematic. Therefore it is suggested in [6] to use singular value decomposition to solve the problem. The Matlab function  $svd(\mathbf{A})$  computes three matrices  $\mathbf{U}, \mathbf{S}$  and  $\mathbf{V}$ , that return the matrix  $\mathbf{A}$  when multiplied.

$$\mathbf{A} = \mathbf{U} \cdot \mathbf{S} \cdot \mathbf{V}' \tag{2.29}$$

${\bf U}$  and  ${\bf V}$  are unitary matrices and  ${\bf S}$  has a diagonal structure. Solving equations (2.28) yields

$$\mathbf{a} = \sum_{i=1}^{M} \frac{\mathbf{U}_i \cdot \mathbf{b}}{w_i} \cdot \mathbf{V}_i \tag{2.30}$$

with  $w_i$  being the diagonal elements of **S**. In case a  $w_i$  is zero, the reciprocal value is set to zero, thereby eliminating the discontinuity.

In order to get a better feeling for the impact that different parameters have, a relative sensitivity is defined as

$$\frac{\Delta t(i)}{\bar{t}} = \sum_{j=1}^{M} \left( a_j \cdot \frac{\bar{p}_j}{\bar{t}} \right) \cdot \frac{\Delta p_j(i)}{\bar{p}_j}$$

(2.31)

where  $a_j \cdot \frac{\bar{p}_j}{\bar{t}}$  is the relative sensitivity.  $\bar{p}_j$  is hereby the average value of one parameter across the range of Monte Carlo runs and  $\bar{t}$  the average value of the fitted result.

The following table 2.3 gives the parameters that are varied for the Monte Carlo process simulation. In addition to the parameters below, four other parameters are also varied, i.e. npeak1, npeak5, drdiffn and drdiffp, which vary the channel doping concentration and the source/drain diffusion sheet resistance of the NMOS and PMOS devices. These are not included in the least squares fit as they tend to worsen the fit.

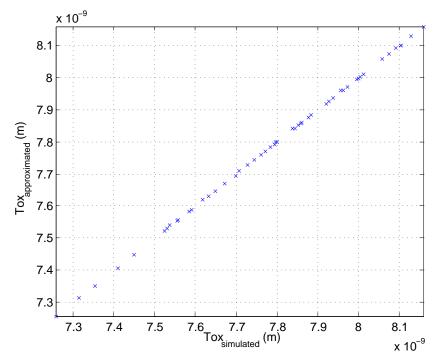

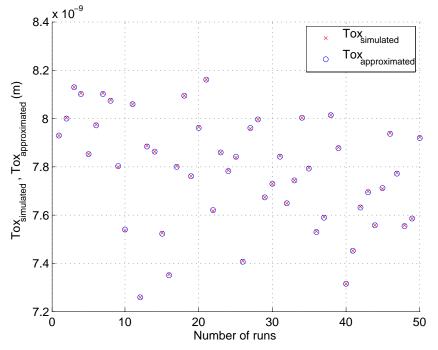

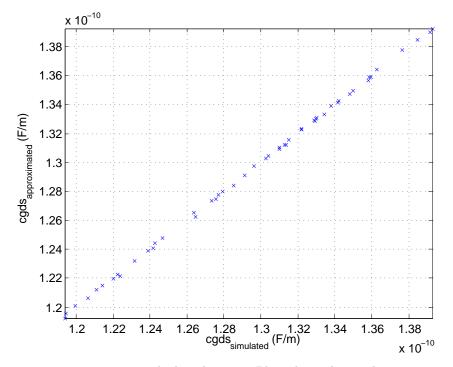

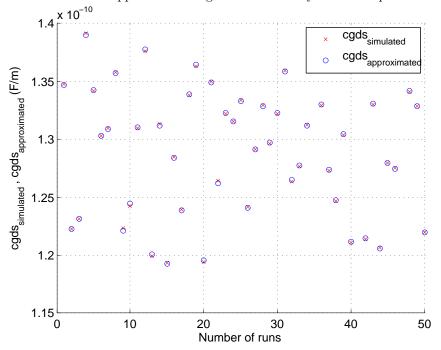

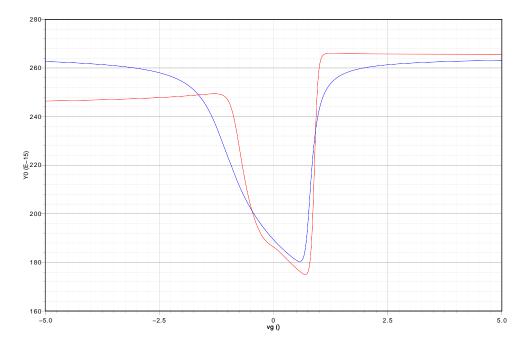

Applying this method to the current I and the oscillation period t yields the results shown in figures 2.17, 2.18 and 2.19, and tables 2.4, 2.5 and 2.6. The simulations are performed for three different structures: first with an unloaded ring oscillator, then with design 1 oscillator structures which extract the oxide thickness, and finally with design 2 oscillators used to extract the overlap capacitance.

The sensitivity analysis is performed for the oxide thickness  $\mathbf{T}_{ox}$ , the gate to drain and gate to source overlap capacitance, and the product of the mean current times the oscillation period of the unloaded ring oscillator.

(a) Least squares approximation applied to an unloaded oscillator. Plotted are the charges  $q = I \cdot t$  calculated with the approximation against the simulated charge values ( $q_{\text{simulated}}$  vs  $q_{\text{approximated}}$ ).

(b) Least squares approximation applied to an unloaded oscillator. Plotted are the simulated and approximated charge values for each Monte Carlo run.

Figure 2.17: Plots of the least squares approximation for an unloaded oscillator.

(a) Least squares approximation applied to design 1. Plotted are the oxide thickness values calculated with the approximation against the simulated values.

(b) Least squares approximation applied to design 1. Plotted are the approximated parameter values for  $T_{ox}$  and the simulated values for each Monte Carlo run.

Figure 2.18: Plots of the least squares approximation for design 1.

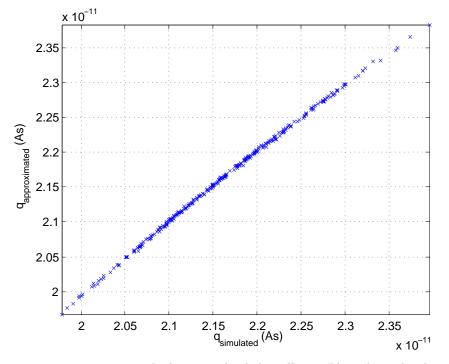

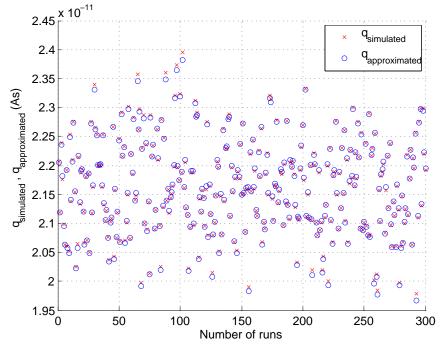

(a) Least squares approximation applied to design 2. Plotted are the overlap capacitance parameters **cgds** calculated with the approximation against the actually simulated parameter values.

(b) Least squares approximation applied to design 2. Plotted are the approximated overlap parameter values and the simulated values for each Monte Carlo run.

Figure 2.19: Plots of the least squares approximation for design 2.

| Input parameters to<br>the least square fit | Dimension                           | Model parameters influenced by these variations                                      |

|---------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------|

| $\Delta$ cgsdop                             | $\frac{F}{m}$                       | PMOS model parameter for the gate to drain<br>and gate to source overlap capacitance |

| $\Delta$ cgbop                              | $\frac{F}{m}$                       | PMOS model parameter for the gate to bulk overlap capacitance                        |

| $\Delta cj5$                                | $\frac{F}{m^2}$                     | p diffusion area capacitance parameter                                               |

| $\Delta cjsw5$                              | $\frac{F}{m}$                       | p diffusion perimeter capacitance parameter                                          |

| $\Delta$ deluop                             | $\frac{m^2}{Vs}$                    | PMOS mobility parameter                                                              |

| $\Delta$ delvtop                            | V                                   | PMOS threshold parameter                                                             |

| $\Delta$ cgsdon                             | $\frac{F}{m}$                       | NMOS gate to drain and gate to source overlap parameter                              |

| $\Delta$ cgbon                              | $\frac{F}{m}$                       | NMOS gate to bulk overlap parameter                                                  |

| Δcj1                                        | $\frac{\frac{F}{m^2}}{\frac{F}{m}}$ | n diffusion area capacitance parameter                                               |

| $\Delta cjsw1$                              | $\frac{F}{m}$                       | n diffusion perimeter capacitance parameter                                          |

| $\Delta$ deluon                             | $\frac{m^2}{Vs}$                    | NMOS mobility parameter                                                              |

| $\Delta$ delvton                            | V                                   | NMOS threshold parameter                                                             |

| $\Delta$ deltox                             | m                                   | Oxide thickness parameter                                                            |

| $\Delta$ dell                               | m                                   | length offset parameter                                                              |

| $\Delta delw$                               | m                                   | width offset parameter                                                               |

Table 2.3: Model parameters which are varied for a Monte Carlo process simulation.

As the results show, sensitivities are found which closely fit the set of varied model parameters to the actual change of the simulation outcome. Therefore, the assumptions regarding the linear dependency on the model parameters (2.24) hold.

Closer inspection of the resulting parameter sets **a** given in tables 2.5 and 2.6 for the oxide thickness and overlap capacitance extraction further confirms the validity of the designs. The extracted oxide thickness is very sensitive toward changes of the oxide thickness parameter  $\Delta$  deltox, which is as expected. The overlap capacitance is very sensitive toward changes of the overlap capacitance parameter for the PMOS. As the load is a PMOS device, this is also straightforward. The sensitivity in this case is not 100% as it is for the oxide thickness, however. The reason for this is that the overlap capacitance depends on two parameters **CGDO** and **CGDL**. Here only **CGDO** is varied. Thus, increasing **CGDO** by for example one hundred percent does not mean that the overlap capacitance increases by the same amount, but only by 69%.

Moreover, these results also show that the extraction method works as intended: by comparing the loaded with the unloaded ring oscillators the desired parameters can be isolated and extracted almost regardless of how other parameters vary, as long as the variation occurs for the unloaded and loaded structures equally. Thus, by placing them close together, the influence of process variation on the parameter of interest can be investigated.

| Varied parameters | Sensitivities $a_j$                                           | Relative Sensitivities |

|-------------------|---------------------------------------------------------------|------------------------|

| $\Delta$ cgsdop   | $6.5199 \cdot 10^{-03} \text{ Vm}$                            | 2.6%                   |

| $\Delta$ cgbop    | $6.2986 \cdot 10^{-04} \text{ Vm}$                            | 0.32%                  |

| $\Delta cj5$      | $7.7978 \cdot 10^{-10} \mathrm{Vm}^2$                         | 4.9%                   |

| $\Delta cjsw5$    | $1.3311 \cdot 10^{-03} \text{ Vm}$                            | 1.9%                   |

| $\Delta$ deluop   | $-1.3394 \cdot 10^{-15} \frac{\mathrm{VAs}^2}{\mathrm{m}^2}$  | -1.1%                  |

| $\Delta$ delvtop  | $4.3942 \cdot 10^{-12} \frac{\text{As}}{\text{V}}$            | -15%                   |

| $\Delta$ cgsdon   | $2.2048 \cdot 10^{-03} \text{ Vm}$                            | 1.2%                   |

| $\Delta$ cgbon    | $-2.5874 \cdot 10^{-04} \text{ Vm}$                           | -0.13%                 |

| $\Delta cj1$      | $2.4879 \cdot 10^{-10} \mathrm{Vm}^2$                         | 1.1%                   |

| $\Delta cjsw1$    | $6.3936 \cdot 10^{-04} \text{ Vm}$                            | 0.73%                  |

| $\Delta$ deluon   | $4.2196 \cdot 10^{-16} \ \frac{\mathrm{VAs^2}}{\mathrm{m^2}}$ | 0.93%                  |

| $\Delta$ delvton  | $-3.0202 \cdot 10^{-12} \frac{\text{As}}{\text{V}}$           | -7.0%                  |

| $\Delta$ deltox   | $-2.3936 \cdot 10^{-03} \frac{\text{As}}{\text{m}}$           | -86%                   |

| $\Delta$ dell     | $9.3334 \cdot 10^{-06} \ \frac{\mathrm{As}}{\mathrm{m}}$      | -0.061%                |

| $\Delta delw$     | $2.9886 \cdot 10^{-06} \frac{\text{As}}{\text{m}}$            | 0.051%                 |

Table 2.4: Sensitivities  $a_j$  resulting from the least square fit for the product  $I \cdot t$  of the unloaded oscillator.

| Table 2.5: Sensitivities $a_j$ | resulting from | the least square fit for | the oxide thickness <b>T</b> | $-\infty$ ( | Design 1) |  |

|--------------------------------|----------------|--------------------------|------------------------------|-------------|-----------|--|

|                                |                |                          |                              |             |           |  |

| Varied parameters | Sensitivities $a_j$                                       | Relative Sensitivities |

|-------------------|-----------------------------------------------------------|------------------------|

| $\Delta$ cgsdop   | $1.1984 \cdot 10^{-01} \frac{\mathrm{m}^2}{\mathrm{F}}$   | 0.13%                  |

| $\Delta$ cgbop    | $-6.1771 \cdot 10^{-02} \frac{\mathrm{m}^2}{\mathrm{F}}$  | -0.087%                |

| $\Delta cj5$      | $-5.6545 \cdot 10^{-09} \frac{\mathrm{m}^3}{\mathrm{F}}$  | -0.099%                |

| $\Delta cjsw5$    | $1.7208 \cdot 10^{-03} \ \frac{\mathrm{m}^2}{\mathrm{F}}$ | 0.0072%                |

| $\Delta$ deluop   | $1.5917 \cdot 10^{-13} \frac{\mathrm{Vs}}{\mathrm{m}}$    | 0.35%                  |

| $\Delta$ delvtop  | $-1.1292 \cdot 10^{-10} {	ext{m} \over V}$                | 1.1%                   |

| $\Delta$ cgsdon   | $-1.1109 \cdot 10^{-02} \frac{\mathrm{m}^2}{\mathrm{F}}$  | -0.017%                |

| $\Delta$ cgbon    | $-1.8973 \cdot 10^{-02} \frac{\mathrm{m}^2}{\mathrm{F}}$  | -0.027%                |

| $\Delta cj1$      | $-7.4415 \cdot 10^{-09} \frac{\mathrm{m}^3}{\mathrm{F}}$  | -0.089%                |

| $\Delta cjsw1$    | $1.5314 \cdot 10^{-02} \ \frac{\mathrm{m}^2}{\mathrm{F}}$ | 0.049%                 |

| $\Delta$ deluon   | $4.9362 \cdot 10^{-14} \ \frac{\mathrm{Vs}}{\mathrm{m}}$  | 0.30%                  |

| $\Delta$ delvton  | $1.3647 \cdot 10^{-10} {	ext{m}}{	ext{V}}$                | 0.88%                  |

| $\Delta deltox$   | $9.9696 \cdot 10^{-01}$                                   | 100%                   |

| $\Delta$ dell     | $-2.6148 \cdot 10^{-05}$                                  | 0.0012%                |

| $\Delta$ delw     | $8.5151 \cdot 10^{-06}$                                   | -0.00042%              |

| Varied parameters | Sensitivities $a_j$                                            | Relative Sensitivities |

|-------------------|----------------------------------------------------------------|------------------------|

| $\Delta$ cgsdop   | 1.0394                                                         | 69%                    |

| $\Delta$ cgbop    | $-4.1097 \cdot 10^{-04}$                                       | -0.035%                |

| $\Delta cj5$      | $-1.1349 \cdot 10^{-10} \text{ m}$                             | -0.12%                 |

| $\Delta cjsw5$    | $8.6542 \cdot 10^{-05}$                                        | 0.021%                 |

| $\Delta$ deluop   | $6.8595 \cdot 10^{-15} \frac{\mathrm{As}^2}{\mathrm{m}^3}$     | 0.91%                  |

| $\Delta$ delvtop  | $1.1238 \cdot 10^{-11} \frac{\text{As}}{\text{V}^2\text{m}}$   | -6.4%                  |

| $\Delta$ cgsdon   | $1.6834 \cdot 10^{-03}$                                        | 0.16%                  |

| $\Delta$ cgbon    | $-4.1434 \cdot 10^{-04}$                                       | -0.035%                |

| $\Delta cj1$      | $4.7497 \cdot 10^{-10} \text{ m}$                              | 0.34%                  |

| $\Delta cjsw1$    | $-1.8866 \cdot 10^{-03}$                                       | -0.37%                 |

| $\Delta$ deluon   | $4.3887 \cdot 10^{-15} \frac{\mathrm{As}^2}{\mathrm{m}^3}$     | 1.62%                  |

| $\Delta$ delvton  | $-8.5186 \cdot 10^{-12} \frac{\text{As}}{\text{V}^2 \text{m}}$ | -3.3%                  |

| $\Delta deltox$   | $1.5181 \cdot 10^{-05} \frac{\mathrm{As}}{\mathrm{Vm}^2}$      | 0.092%                 |

| $\Delta$ dell     | $-8.4107 \cdot 10^{-06} \frac{\mathrm{As}}{\mathrm{Vm}^2}$     | -0.017%                |

| $\Delta delw$     | $1.5028 \cdot 10^{-06} \frac{\mathrm{As}}{\mathrm{Vm}^2}$      | -0.0091%               |

Table 2.6: Sensitivities  $a_j$  resulting from the least square fit for the overlap capacitance parameter cgds. (Design 2)

The biggest impact on the frequency of the unloaded ring oscillator show the threshold voltage variation  $\Delta$ delvtop of the PMOS and the oxide thickness. The oxide thickness affects the biggest capacitances in the structure, and therefore is the most influential. Other parameters that directly affect the capacitances also show a relatively big influence on the simulation outcomes.

## 2.4 Ring Oscillator Circuit Layout

As stated before in section 2.1.3 the frequency of the oscillator is very sensitive to its layout. Two different designs have been presented in the previous section, the first one to determine the oxide thickness and the second one to determine the overlap capacitance. If the different parts of the characterization structures do not match, it will not be possible to measure the desired properties. There are two different aspects that need to be considered here. First, the stages of a single oscillator should be ideally identical to each other with the same length of routing and surrounding. Second, not only should the inverters be the same in the loaded and reference oscillator, but also all parasitics that are introduced through the routing and diffusions. Basically the reference is then the same circuit as its respective loaded oscillator without the load transistors' gates. A correct layout can achieve a frequency mismatch of smaller than one percent, as described in section 2.1.3. As the layout of the overlap characterization design, which has been introduced as design 2, was completed earlier than design 1, the first test chip is made up of structures from

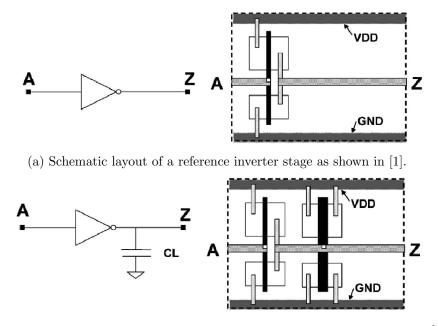

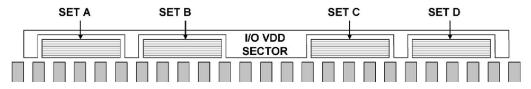

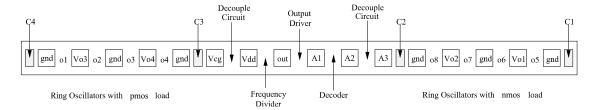

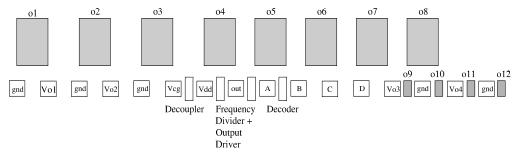

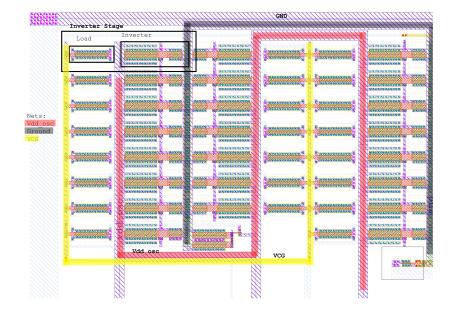

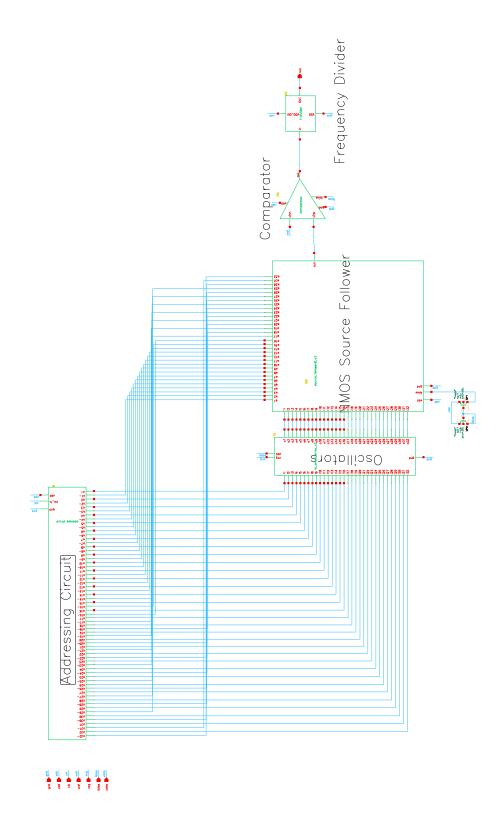

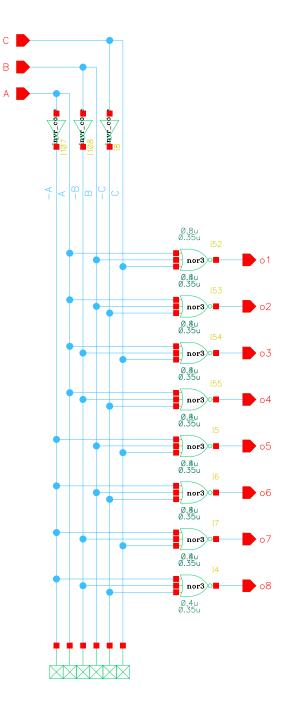

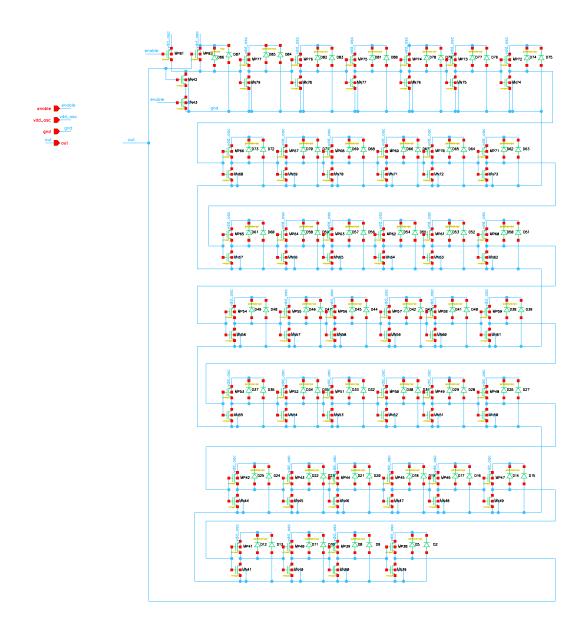

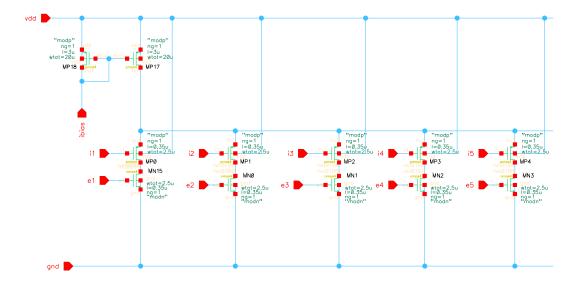

(a) Schematic layout of test chip 1 to monitor the NMOS and PMOS overlap capacitance parameters. The oscillator structures are placed between their respective supply pads. The test structures are from design 2.

(b) Pin description for the first test chip

| PAD             | Description                                     |

|-----------------|-------------------------------------------------|

| gnd             | Ground connection; the separate pads are not    |

| giiu            | connected on the chip itself                    |

| V <sub>o1</sub> | Supply pad for oscillators o5 and o6            |

| V <sub>o2</sub> | Supply pad for oscillators o7 and o8            |

| V <sub>o3</sub> | Supply pad for oscillators o1 and o2            |

| V <sub>o4</sub> | Supply pad for oscillators o3 and o4            |

| V <sub>CG</sub> | Connection to the gates of the load transistors |

| V <sub>DD</sub> | Supply pad for address and output circuit       |

| out             | Output pad at which frequency can be measured   |