# Christian Pendl christian.pendl@student.tugraz.at

# $100\,{\rm Gbit/s}$ Authenticated Encryption Based on Quantum Key Distribution

# Master's Thesis

to achieve the university degree of Master of Science

Master's degree programme: Telematics

submitted to

# Graz University of Technology

Institute for Applied Information Processing and Communications (IAIK) Graz University of Technology Inffeldgasse 16a 8010 Graz, Austria

Integrated Systems Laboratory (IIS) Swiss Federal Institute of Technology Gloriastrasse 35 CH-8092 Zürich, Switzerland

- Supervisors: Thomas Korak, TU Graz Christoph Keller, ETH Zürich Michael Mühlberghuber, ETH Zürich

- Assessors: Prof. Stefan Mangard, TU Graz Prof. Hubert Kaeslin, ETH Zürich

December, 2014

Deutsche Fassung: Beschluss der Curricula-Kommission für Bachelor-, Master- und Diplomstudien vom 10.11.2008 Genehmigung des Senates am 1.12.2008

# EIDESSTATTLICHE ERKLÄRUNG

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe.

Graz, am .....

(Unterschrift)

Englische Fassung:

# STATUTORY DECLARATION

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

|    |     | <br> |

|----|-----|------|

| da | ate |      |

(signature)

# Acknowledgements

I would like to thank the members of the Institute for Applied Information Processing and Communications (IAIK) at the Graz University of Technology (TUG) and the Swiss Federal Institute of Technology (ETH) Zürich for giving me the chance to do my thesis abroad. I would also like to thank my supervisors Michael Hutter and Thomas Korak from the TUG, and Michael Mühlberghuber and Christoph Keller from the ETH Zürich and all members of the Microelectronics Design Center from the Department of Information Technology and Electrical Engineering (D-ITET) at ETH for their remarkable support during the months of working on this thesis. Particular thanks go to Michael Hutter for his excellent advice on writing and presenting scientific papers.

Last but not least, the biggest thanks go to my family. They showed almost endless patience and supported me during every phase of my studies, especially during the time of writing this master thesis. I know that my decisions and my acting were not always easy to understand and accept, but they were always behind me. Because of this I would like to dedicate this work to my family.

# Abstract

The QCrypt project aims at providing a future proof cryptographic engine and to considerably improve cryptography on both, the key distribution level and the encryption level. It combines Quantum Key Distribution (QKD) with classical cryptographic primitives to provide authenticated encryption (AE). QKD is a secure way to generate and distribute cryptographic keys based on the fundamental laws of quantum mechanics. In today's standard applications data exchange rates continue to increase. The Ethernet standard IEEE 802.3ba already allows data rates of up to 100 Gbit/s. Consequently, a future proof encryption engine has to support up to 100 Gbit/s.

This work is part of the QCrypt project with the goal to extend the currently applied AE engine. The existing engine is based on the Galois Counter Mode of Operation (GCM) with AES as the underlying block cipher. Alternatives for both, the block cipher as well as the mode of operation should be evaluated. Besides exploring more efficient hardware implementations, this work is also motivated by providing an alternative AE scheme, in case successful attacks against primitives used in the existing system are developed. The main design goal is to achieve high throughput on FPGA platforms and to be compatible and easily interchangeable with the existing AE engine. The Serpent block cipher and the Offset CodeBook mode of operation figured out to be the best alternatives to the current system. Therefore, we evaluate the Serpent block cipher and the OCB mode of operation/block cipher combinations, namely: GCM-Serpent, OCB-AES and OCB-Serpent. All three authenticated-encryption engine variants are capable of providing authenticated encryption at a rate of over 100 Gbit/s.

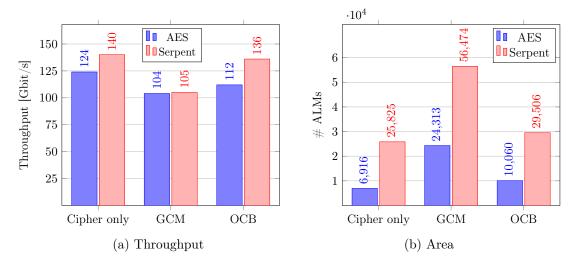

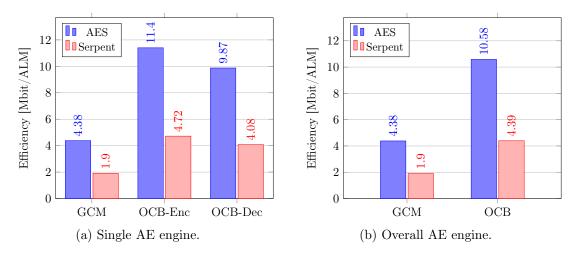

To the best of our knowledge, GCM-Serpent and OCB-Serpent are the first hardware architectures targeting high-throughput authenticated encryption that are based on a block-cipher other than AES. Additionally, no design using AES as a block cipher, that is capable of reaching throughputs of over 100 Gbit/s, and that is based on a different mode of operation than GCM has been published so far. Our fastest design is based on OCB-Serpent and reaches a throughput of 136 Gbit/s at a maximum frequency of 267 MHz when using four cipher cores in parallel. This design outperforms all GCM-AES implementations available on FPGAs to date. Furthermore, our results show, that OCB is twice as efficient compared to GCM when taking the throughput/area ratio as an indicator.

**Keywords:** Cryptography, Authenticated encryption, GCM, OCB, Serpent, AES, FPGA, Quantum key distribution

# Kurzfassung

Das QCrypt Projekt hat sich das Ziel gesetzt, eine zukunftssichere Kryptografielösung anzubieten und die Kryptografie sowohl hinsichtlich der Verschlüsselung als auch hinsichtlich der Schlüsselverteilung zu verbessern. Das System kombiniert die Quantenschlüsselverteilung, welche auf Basis der Gesetzte der Quantenmechanik eine sichere Methode zur Verteilung kryptografischer Schlüssel bietet, mit klassischen kryptografischen Methoden um gleichzeitig Authentifizierung und Verschlüsselung von Daten anzubieten. Die heute in Standardanwendungen verwendeten Datenraten steigen beständig und der Ethernet Standard IEEE 802.3ba erlaubt bereits Datenraten bis zu 100 Gbit/s. Als Folge muss eine zukunftssichere Lösung zur Authentifizierung und Verschlüsselung Datenraten von 100 Gbit/s unterstützen.

Diese Arbeit ist Teil des QCrypt Projekts und untersucht alternative Blockchiffren und Betriebsmodi zur Authentifizierung und Verschlüsselung zum existierenden AE-System. Dieses basiert auf dem Galois Counter Mode of Operation (GCM) mit AES als zu Grunde liegender Blockchiffre. Neben der Erforschung von effizienteren Hardwareimplementierungen, wird die Arbeit auch von dem Ziel angetrieben, alternative Methoden zur Authentifizierung und Verschlüsselung anzubieten, falls erfolgreiche Attacken gegen die derzeit verwendeten Methoden gefunden werden sollten. Das Hauptdesignziel ist es, hohen Datendurchsatz auf FPGA-Plattformen zu erreichen und gleichzeitig kompatibel und einfach austauschbar zur existierenden AE-Implementierung zu sein. Im Rahmen dieser Arbeit evaluieren wir die Blockchiffre Serpent und den Betriebsmodus Offset CodeBook (OCB) und präsentieren die Ergebnisse von Implementierungen verschiedener Kombinationen von Betriebsmodi und Blockchiffren. Diese sind: GCM-Serpent, OCB-AES und OCB-Serpent. Alle drei Varianten erreichen Datenraten von über 100 Gbit/s.

Laut aktueller Recherche sind GCM-Serpent und OCB-Serpent die ersten Hardwarearchitekturen, welche auf hohen Datendurchsatz abzielen, die nicht auf AES basieren. Zudem ist bisher kein auf AES-basiertes Design veröffentlicht worden, das einen Durchsatz von 100 Gbit/s erreicht und auf einem anderen Betriebsmodus als GCM basiert. Unser schnellstes Design basiert auf OCB-Serpent und erreicht einen Datendurchsatz von 136 Gbit/s bei einer maximalen Frequenz von 267 MHz. Es übertrifft somit alle bisher auf FPGA verfügbaren GCM-AES Implementierungen. Außerdem zeigen unsere Ergebnisse, dass der OCB-Modus doppelt so effizient wie der GCM-Modus ist.

**Stichwörter:** Kryptografie, Authentifizierung, Verschlüsselung, GCM, OCB, Serpent, AES, FPGA, Quantenschlüsselaustausch

# Contents

| 1        | Intr | oducti | on                                                                                                                                                          | 1 |

|----------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|          | 1.1  | Relate | d Work                                                                                                                                                      | 2 |

|          | 1.2  | Outlin | le                                                                                                                                                          | 4 |

| <b>2</b> | Cry  | ptogra | phic Goals                                                                                                                                                  | 5 |

|          | 2.1  | The M  | Iajor Cryptographic Goals                                                                                                                                   | 5 |

|          | 2.2  |        |                                                                                                                                                             | 6 |

|          | 2.3  | Attack | $\mathbf{x} \operatorname{Model} \ldots $   | 7 |

| 3        | Cry  | ptogra | phic Primitives                                                                                                                                             | 9 |

|          | 3.1  |        |                                                                                                                                                             | 9 |

|          |      | 3.1.1  | Public-Key Encryption Schemes                                                                                                                               | С |

|          |      | 3.1.2  | Symmetric Encryption Schemes                                                                                                                                | Э |

|          |      | 3.1.3  | Symmetric versus Asymmetric Encryption                                                                                                                      | 2 |

|          | 3.2  | Authe  | ntication Schemes $\ldots \ldots 13$        | 3 |

|          |      | 3.2.1  | Unkeyed Hash Functions                                                                                                                                      | 3 |

|          |      | 3.2.2  | Keyed Hash Functions                                                                                                                                        | 4 |

|          | 3.3  | Quant  | um Cryptography                                                                                                                                             | 5 |

|          |      | 3.3.1  | Example of the BB84 Protocol                                                                                                                                | 6 |

|          |      | 3.3.2  | Other Protocols                                                                                                                                             |   |

|          |      | 3.3.3  | Security of Quantum Cryptography                                                                                                                            | 3 |

|          |      | 3.3.4  | Summary and Discussion                                                                                                                                      | 9 |

|          | 3.4  | Conclu | r usion                                                                                                                                                     | 9 |

| 4        | Key  | -Distr | ibution Problem 20                                                                                                                                          | 0 |

| -        | DI.  |        |                                                                                                                                                             | n |

| 5        |      | -      | hers Used for the Thesis 23                                                                                                                                 |   |

|          | 5.1  | U      | $\operatorname{ael} (\operatorname{AES}) \dots \dots$ | - |

|          |      | 5.1.1  | Data Representation                                                                                                                                         |   |

|          |      | 5.1.2  | Round Transformation                                                                                                                                        |   |

|          |      | 5.1.3  | Round-Key Generation                                                                                                                                        |   |

|          | 5.2  | Serper |                                                                                                                                                             |   |

|          |      | 5.2.1  | Data Representation                                                                                                                                         |   |

|          |      | 5.2.2  | The Cipher         20                                                                                                                                       |   |

|          |      | 5.2.3  | Key Scheduler                                                                                                                                               | ) |

| 6  | Aut  | henticated Encryption                                                     | 32        |

|----|------|---------------------------------------------------------------------------|-----------|

|    | 6.1  | Approaches to Achieve Authenticated Encryption                            | 32        |

|    | 6.2  | Properties and Features of Authenticated Encryption Algorithms            | 33        |

|    | 6.3  | ССМ                                                                       | 35        |

|    | 6.4  | CWC                                                                       | 36        |

|    | 6.5  | Galois Counter Mode of Operation                                          | 36        |

|    |      | 6.5.1 Authenticated Encryption                                            | 36        |

|    |      | 6.5.2 Authenticated Decryption                                            | 37        |

|    |      | 6.5.3 GHASH                                                               | 38        |

|    | 6.6  | Offset CodeBook (OCB)                                                     |           |

|    |      | 6.6.1 Authenticated Encryption                                            | 39        |

|    |      | 6.6.2 Authenticated Decryption                                            | 42        |

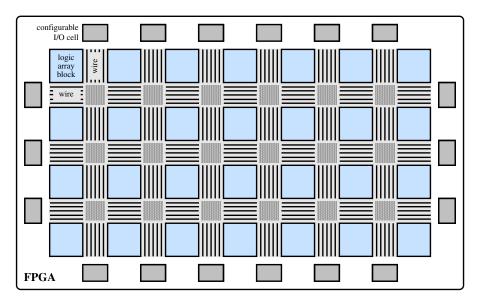

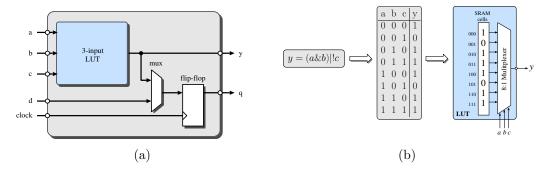

| 7  | Rec  | onfigurable Hardware                                                      | 44        |

|    | 7.1  | Introduction to Reconfigurable Hardware                                   | 44        |

|    | 7.2  | Field-Programmable Gate Arrays (FPGAs)                                    | 45        |

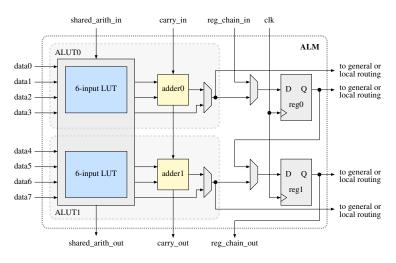

|    |      | 7.2.1 Logic Array Blocks (LABs) and Arithmetic Logic Modules (ALMs) .     | 45        |

|    |      | 7.2.2 Configurable I/O Blocks                                             | 46        |

|    |      | 7.2.3 Programmable Interconnect and Clock Circuitry                       | 46        |

|    |      | 7.2.4 Programming and Configuration of FPGAs                              | 47        |

| 8  | Ove  | rview of the Hardware Platform                                            | 48        |

|    | 8.1  | System Overview                                                           | 48        |

|    | 8.2  | The Quantum Key-Distribution System                                       | 48        |

|    | 8.3  | The Fast-Encryptor System                                                 | 49        |

|    | 8.4  | The Altera Stratix IV EP4S100G5 FPGA                                      | 50        |

|    |      | 8.4.1 $$ Logic Array Blocks (LABs) and Adaptive Logic Modules (ALMs) $$ . | 50        |

| 9  | The  | Existing Authenticated-Encryption Engine                                  | 52        |

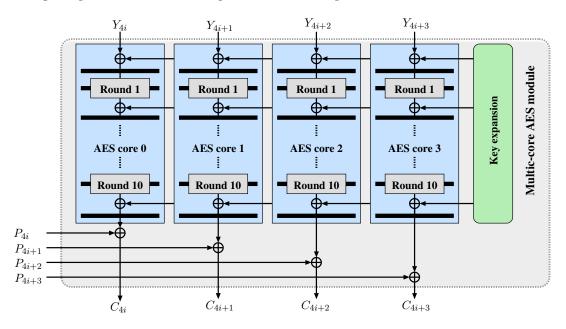

|    | 9.1  | Multi-Core AES Design                                                     | 53        |

|    | 9.2  | The Parallel Pipelined GHASH Design                                       | 53        |

|    | 9.3  | GCM Design                                                                | 56        |

| 10 | Ana  | lysis of Alternatives to the Existing System                              | <b>58</b> |

|    | 10.1 | Analysis of Requirements                                                  | 58        |

|    | 10.2 | Alternative Block Cipher                                                  | 61        |

|    |      | 10.2.1 AES                                                                | 61        |

|    |      | 10.2.2 Serpent                                                            | 62        |

|    |      | 10.2.3 Comparison and Choice of an Alternative Blockcipher                | 63        |

|    | 10.3 | Alternatives Modes for Authenticated Encryption                           | 64        |

|    |      | 10.3.1 GCM                                                                | 66        |

|    |      | 10.3.2 OCB                                                                | 66        |

|    |      | 10.3.3 Comparison and Choice of an Alternative Mode for Authenticated     |           |

|    |      | Encryption                                                                | 67        |

| 11 Serpent - Implementation of an Alternative Block Cipher | 69              |

|------------------------------------------------------------|-----------------|

| 11.1 Single-Core Design                                    | 69              |

| 11.1.1 The Substitution Stage                              | 69              |

| 11.1.2 The Linear Transformation                           | 70              |

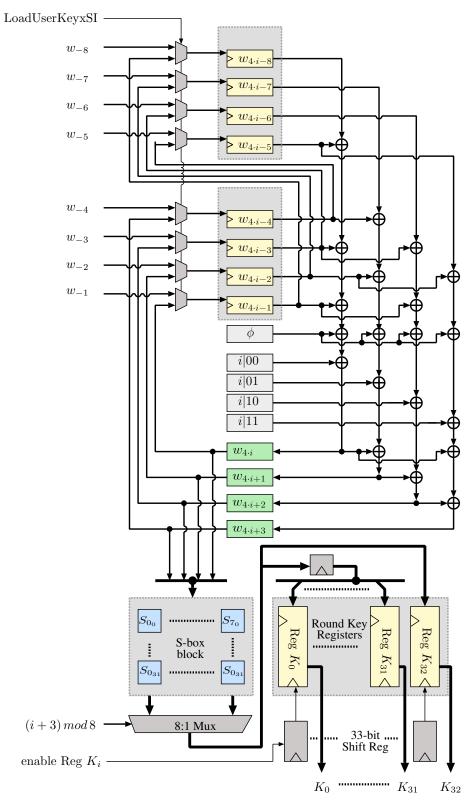

| 11.1.3 The Key Scheduler                                   | 71              |

| 11.2 Multi-Core Design                                     | 73              |

| 11.3 Summary                                               | 74              |

| 12 OCB - An alternative for Authenticated Encryption       | 75              |

| • =                                                        | 75              |

|                                                            | 78              |

| · *                                                        | 79              |

|                                                            | 80              |

|                                                            |                 |

|                                                            | 82              |

|                                                            | 82              |

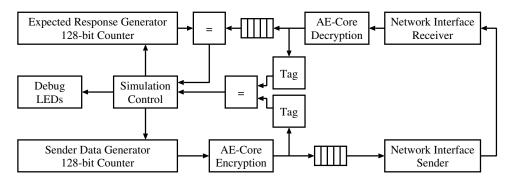

| 13.2 FPGA Testbench Design                                 | 84              |

| 14 Results                                                 | 86              |

| 14.1 Block Ciphers                                         | 86              |

| *                                                          | 87              |

|                                                            | 88              |

|                                                            | 90              |

|                                                            | 93              |

| 15 Conclusion                                              | 96              |

|                                                            | <b>90</b><br>97 |

|                                                            | 91<br>98        |

| 15.2 Outlook                                               | 90              |

| Appendices                                                 | 99              |

| A Definitions                                              | 99              |

|                                                            | 99              |

| A.2 Used Symbols                                           | .00             |

|                                                            |                 |

|                                                            | 01              |

|                                                            | .01             |

| B.2 OCB                                                    | .04             |

| C Original Assignment 1                                    | 05              |

| C Original Assignment                                      |                 |

# Chapter

# Introduction

Today, the dominating part of communication is transmitted over public channels. The amount of data transferred as well as the communication speed increases continuously. The Ethernet standard IEEE 802.3ba already allows data rates of up to 100 Gbit/s. However, all this communication needs to be protected by cryptographic primitives to ensure the privacy and authenticity of the data transmitted.

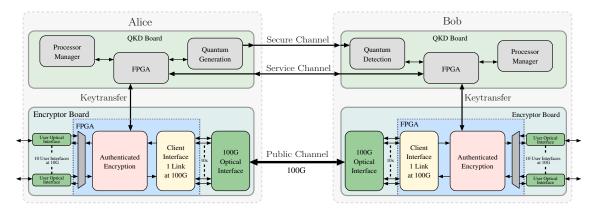

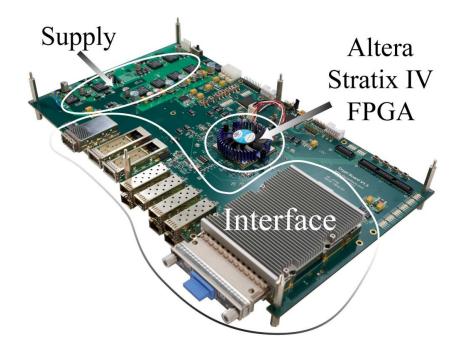

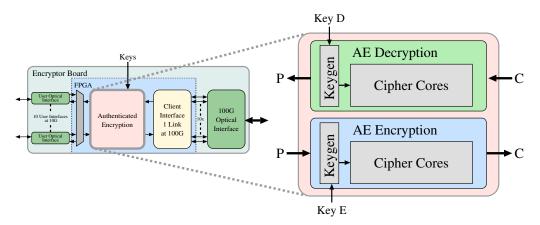

The contribution of this work is part of the QCrypt project [85] which aims at providing a future-proof, secure, high-speed communication platform based on a quantum keydistribution (QKD) system. The system can be divided into two parts: the quantum key-distribution system and the fast-encryptor system. The fast-encryptor system is based on an Altera Stratix IV EP4S100G5 FPGA. It handles the high-speed network communication and provides authenticated encryption (AE) for the data stream at a throughput of 100 Gbit/s using the user-keys supplied by the QDK-system. This stream is then transmitted to the communication partner over a public 100 Gbit/s channel. The existing authenticated-encryption engine is based on the Galois Counter Mode of Operation (GCM) with four parallel AES cores as underlying block cipher and is referred to as GCM-AES.

The main contribution of this work was to elaborate possible alternatives to the existing authenticated-encryption engine, that are capable of encrypting at data rates of over 100 Gbit/s. On the one hand the idea was to be prepared for unexpected security flaws in the existing system by providing alternative subcomponents and on the other hand there was a desire to possibly find a better solution compared to the existing system. In order to be able to identify promising alternatives we analyzed existing the authenticatedencryption engine and identified the requirements the authenticated-encryption engine has to fulfill. Then, we evaluated alternative subcomponents and algorithms in regard to the previously defined requirements. Finally, the most promising candidates were designed, implemented in hardware and tested on the target system. We laid a strong emphasis to ensure easy integration into the existing system, high throughput, an efficient use of resources, low latency and minimal delays. During the evaluation of alternatives to the AES block cipher, Serpent emerged as a promising candidate and was then implemented in hardware. In order to reach the desired throughput of 100 Gbit/s, 33 pipeline stages had to be introduced and four cipher cores had to be used in parallel. The resulting architecture is able to achieve a throughput of 140 Gbit/s at a maximum frequency of 275 MHz which is an increase of 8.3% compared to the existing AES architecture. The design requires 33,067 arithmetic logic modules (ALMs) and does not use any block RAM memory (BRAM). Based on the multi-core Serpent design, we developed a mode for AE that uses GCM with Serpent as the underlying block cipher. This design reached a throughput of 104 Gbit/s at a maximum frequency of 203 MHz while consuming 56,474 ALMs of a total of 212,480 ALMs available on the target platform. In addition we have chosen the Offset CodeBook (OCB) mode in its third version as an alternative mode for authenticated encryption. The OCB-encryption architecture is based on four parallel block cipher cores. while the OCB-decryption architecture uses four cipher cores in parallel for decryption and an additional cipher core that is in encryption mode. When using AES as the underlying block cipher OCB achieves a throughput of  $112 \,\mathrm{Gbit/s}$  at a maximum frequency of  $220 \,\mathrm{MHz}$ and only needs 10,060 ALMs for encryption and 11,614 ALMs for decryption. Compared to GCM-AES this is an increase of over 7% in throughput. The fastest authenticatedencryption design is OCB-Serpent, which reaches a throughput of 136 Gbit/s at 276 MHz while consuming 29,506 ALMs for encryption and 33,891 ALMs for decryption. This is an increase in throughput of 27 % compared to GCM-AES. Overall, the throughput/area ratio of the OCB implementation is more than twice as high as of the existing GCM architecture.

Parts of this thesis have been published in [74] and [111] and in [73] Muehlberghuber et al. present a follow-up work based on this work. For a full description of the original assignment of this work please refer to Appendix C.

# 1.1 Related Work

In the early 1990s it became obvious that the security of the Data Encryption Standard (DES) [43] was not future proof any more. Therefore, in 1997, the National Institute of Standards and Technology (NIST) together with the industry and the cryptographic community started the Advanced Encryption Standard (AES) competition in search for a new standardized symmetric-key scheme. In 1999, after multiple rounds of public discussion, five candidates were presented that made it to the final round: MARS [26], Rivest Cipher 6 (RC6) [90], Rijndael [31], Serpent [10] and Twofish [98]. Those five candidates, also called AES finalists, were then extensively analyzed and explored in regard to their security, performance in software and performance in hardware. Since Rijndael was announced as the winner of the AES competition, it is referred to as AES, and most of the high speed implementations of block ciphers target this algorithm.

In 2011, Ali et al. [6] published an AES design accomplishing a throughput of 36.2 Gbit/s on a Altera Stratix-2 FPGA. In order to improve the throughput they used full loop unrolling with two pipeline stages per AES round and employed offline key calculation. Furthermore, they combined the SubBytes, the ShiftRows and the MixColumns operations, which are the fundamental building blocs of the AES round function, into a single step and precomputed a look-up table (LUT). This reduces the number of stages in an AES round and minimizes the critical path. Using the same principle, Cai, Sun, and Liu [28] reached a throughput of 40.96 Gbit/s on a Xilinx Spartan-6. They only introduced one pipeline stage per AES round and could thus reduce the latency to 10 clock cycles. Qiong and Jianwu [86] present an AES implementation reaching a throughput of 62.8 Gbit/s on an Altera Stratix-3 FPGA. Their design is fully unrolled with three pipeline stages for each round of AES and makes extensive use of block RAM (BRAM). In 2013, Liu, Xu, and Yuan [65] described an fully unrolled AES design with two pipeline stages for each round of AES that reaches a throughput of 66.1 Gbit/s on a Xilinx Virtex-7 FPGA without using BRAM. A throughput of 70 Gbit/s is reached on a Virtex-5 by Soliman and Abozaid [102] with a fully unrolled design that

uses two pipeline stages per AES round. Farashahi, Rashidi, and Sayedi [41] reached a throughput of 86 Gbit/s on a Xilinx Virtex-5 by introducing numerous pipeline stages.

Apart from AES, most of the research on high-speed implementations of block ciphers was done during the discussion phase of the AES competition [3] from 1997 to 2000. Only few implementations of thoroughly investigated block cipher algorithms have been published. In 2004, Lázaro et al. [64] present a Serpent design capable of encrypting 42.8 Gbit/s on a Xilinx Virtex-2 XC2V2000 FPGA. Their architecture is fully unrolled with two pipeline stages for each round of Serpent. In order to increase the throughput, the encryption pipeline is clocked at double frequency compared to the key scheduler. Sugier [103] describes an implementation of Serpent that uses full outer-loop pipelining and a key scheduler in combinational logic which achieves a throughput of 19.7 Gbit/s targeting an Xilinx Spartan-3E FPGA. A design employing pipelining for the cipher rounds of Serpent as well as for the key scheduler that reaches a throughput of 17.5 Gbit/s is presented in the same paper.

In order to use block ciphers to provide authenticated encryption, special modes of operation have been developed. These include GCM-AES which was standardized by the NIST [78] and thus is used for many protocols such as TLS [95], SSH [54] and IPSec [25] Consequently GCM-AES received significant attention from the research community, and several implementations targeting FPGAs can be found in the literature. However, GCM-AES is widely seen as an unsatisfactory and brittle standard that comes with some disadvantages that can compromise security [83]. Thus, in 2014, a new competition called *CAESAR* (Competition for Authenticated Encryption: Security, Applicability, and Robustness) was launched by the international cryptographic research community [27]. Its main goal is to identify authenticated ciphers that offer advantages over AES-GCM and that are suitable for widespread adoption. The whole competition is based on a public evaluation. For the first round of the competition, launched in march 2014, 57 authenticated cipher candidates were submitted, some of which have already been withdrawn because of security flaws that could be identified. Some of the submissions like ASCON [35] or MORUS [109], are fully parallelizable and only use functions that are cheap to implement in hardware and could prove to be very fast. However, as the competition is in a very early stage it is not yet foreseeable which submissions will finally be approved and currently only few hardware implementations of proposals have been published. Among those published, none is targeting a throughput near 100 Gbit/s. So, still most high-throughput implementations of authenticated encryption schemes are still based on GCM-AES.

In 2009, Zhou et al. [113] presented a single-core GCM-AES design, which targets a Xilinx Virtex-5 FPGA and achieved a throughput of 41.5 Gbit/s based on the 128-bit version of AES. Henzen and Fichtner [49] showed that it is possible to break the 100 Gbit/s barrier on a Virtex-5. They made use of four fully unrolled AES cores for the encryption part and used four Karatsuba-Ofman (KO) multipliers in order to realize the authentication part. Their design reaches a throughput of 119.3 Gbit/s. Abdellatif, Chotin-Avot, and Mehrez [2] describe a GCM-AES design reaching a throughput of 102.4 Gbit/s on a Virtex-5 FPGA. Their implementation is based on four fully unrolled, pipelined AES cores for encryption and four parallel authentication cores. However, their design uses a fixed secret key which allows them to precalculate the round keys for AES and the key-constants required for the authentication part and to synthesize those into their design. This reduces the complexity for both, the encryption part as well as for the authentication part but requires to reprogram the FPGA in case a key change is needed. Using the same principle they also report a single core design capable of 30.9 Gbit/s on a Virtex-5 in [1].

When using GCM, the most complex operation during the computation of a message

digest is actually the multiplication in the binary finite-field  $GF(2^{128})$ , which is part of the universal hashing function called GHASH. Therefore, most of the effort in improving GCM implementations has been spent on speeding up this calculation. Wang et al. [106] presented a GHASH architecture based on four GHASH cores that achieved a throughput of 123.1 Gbit/s on a Virtex-5. In [29], Crenne et al. reached 238.1 Gbit/s by using 8 parallel finite-field multipliers, also targeting a Xilinx Virtex-5 FPGA.

To the best of our knowledge, no hardware architecture based on a block cipher other than AES and targeting a high-throughput AE implementation has been presented so far. Moreover, no AES design, which makes use of an operation mode different than GCM in order to achieve throughputs up to 100 Gbit/s, has been published to date.

# 1.2 Outline

The remainder of this thesis is organized as follows. Chapter 2 defines the main cryptographic goals. It also introduces a communication model from a cryptographic point of view and describes basic attacks that try to break the main cryptographic goals. Chapter 3 introduces the concepts of symmetric-key cryptography and public-key cryptography. Furthermore, basic cryptographic primitives used in classical cryptography such as block ciphers, secure hash functions and message authentication codes are explained. The chapter also includes an introduction to quantum cryptography and raises the key-distribution problem which is then elaborated and discussed in Chapter 4. In Chapter 5, two block ciphers relevant for this thesis, namely the AES cipher and the Serpent cipher are described in detail. Next, Chapter 6 introduces the concept of authenticated encryption and shows methods to achieve AE. In addition, the Galois Counter mode of operation (GCM) and the Offset CodeBook (OCB) mode of operation, which are two special block-cipher modes for AE relevant for this work are explained in detail. The contribution of this work is based on an existing, specially designed FPGA-based hardware platform and an existing authenticated encryption implementation. The whole system was designed to provide a future-proof secure high-speed communication platform that is based on a quantum key-distribution system. Thus, first, Chapter 7 gives an introduction to reconfigurable hardware and second, Chapter 8 gives an overview on the actual system's hardware platform. Chapter 9 then describes the existing AE implementation in detail. In order to identify promising alternatives to the existing AE engine, Chapter 10 first investigates the requirements of the AE engine and then discusses and analyzes different block ciphers and modes for authenticated encryption in regard to their suitability for the previously defined requirements. In the end of this chapter, one alternative block cipher and one alternative AE mode are selected for implementation. Next, in Chapter 11, the actual implementation of a parallel pipelined Serpent cipher which achieves an throughput of over 100 Gbit/s is presented in detail. The design of the alternative AE engine which is based on the Offset CodeBook mode is then illustrated in Chapter 12. Chapter 13 describes how the implemented system was tested an verified and implementation results and a comparison with related work is given in Chapter 14. Finally, Chapter 15 summarizes the results and draws conclusions.

# Chapter

# Cryptographic Goals

There has been a dramatic increase of communication systems in the 20<sup>th</sup> century. Today's information society heavily relies on cryptographic systems that protect information and communication by providing confidentiality, data integrity, entity authentication and data origin authentication.

This chapter, in Section 2.1 lists and explains the main cryptographic goals. Then Section 2.2 defines a common model of communication and describes the different aspects and goals of information security based on this model. Finally, Section 2.3 defines an attack model and shows how malicious adversaries try to attack the communication between valid entities.

# 2.1 The Major Cryptographic Goals

Following [71] the **major cryptographic goals**, from which all other cryptographic goals can be derived are defined as follows:

- 1. **Confidentiality** or *privacy* is a method to keep the information secret from all but those parties authorized to have it.

- 2. **Data integrity** is a method providing protection of unauthorized alteration of data. It allows to detect data manipulation such as deletion, insertion and substitution by unauthorized parties.

- 3. Authentication is a method related to identification. It applies to communicating entities as well as to information. Whenever two start communicating they should identify each other and the information delivered over the channel should be authenticated with regards to origin, data content, date of origin, etc. This is why the aspect of authentication in cryptography is often subdivided into two main classes: *entity authentication* and *data origin authentication*. Data integrity implies data origin authentication, because a modification of the data also means that the origin of data has changed.

- 4. **Non-repudiation** is a method that prevents entities from disavowing previous commitments or actions.

# 2.2 Communication Model

In order to show how the cryptographic goals aim to achieve communication security a communication model needs to be defined. Using a standard model of communication helps to identify security problems that arise in practice. Section 2.3 will later clarify how this model can be violated with respect to a particular cryptographic goal.

Following [99] a standard model of communication can be defined as follows:

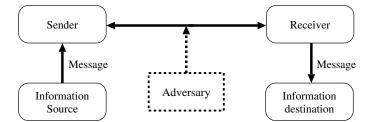

Figure 2.1: Standard communication model.

The communication model is divided into five main parts:

- 1. An *information source* which produces the message to be transmitted.

- 2. A *transmitter* or *sender* which processes the message such that it can be transmitted over the channel.

- 3. A communication channel is the medium used to transmit the message from transmitter to receiver. In a general case this channel is *insecure* and accessible to a third party, called *attacker* or *adversary* which can read, alter, delete and add messages. In contrast, a channel is said to be *secure* if only the two communication parties are able to read, alter, delete or add information transmitted over the channel. One method to make a channel secure is to make it physically inaccessible. However it is a very difficult task to achieve this *physical security*.

- 4. Receiver(s) which receives the message and which performs the inverse actions done by the transmitter to reconstruct the message.

- 5. A *destination* is the entity the message is addressed to.

All the parties that communicate over different channels together form a communication network. When the message is received correctly by the receiver as intended by the sender we speak of a normal communication flow. In reality however, many factors influence the communication flow and a correct flow is hard to achieve. On the one hand, there are non-malicious interferences on the channel. These interferences do not occur by intent and can be caused by technical or accidental problems. On the other hand, malicious interferences exist that are caused by intentional acts of an adversary.

As previously mentioned physical security is hard to realize. Thus, in order to prevent malicious attacks cryptography offers a set of primitives and methods to secure the channel.

# 2.3 Attack Model

Attacks, as previously mentioned are malicious actions performed by an unauthorized third party called *attacker* or *adversary* which aim to get an advantage out of the information transmitted over the channel by the legitimate communication partners.

There are three general types of attacks that are threats to the major cryptographic goals and that violate Shannon's model of communication [99, 100]. Using these attack schemes an adversary attempts to violate the goal of channel availability and the cryptographic goals of confidentiality, data integrity, authentication and non-repudiation.

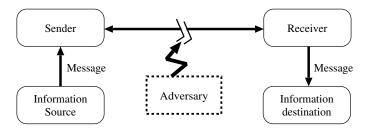

1. Attack on **availability:** The adversary actively disturbs the communication channel and attacks the communication flow intended by the sender. The attack prevents the messages sent by the sender to be received by the intended receiver.

Figure 2.2: Attack on availability.

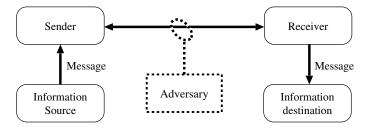

2. Attack on **confidentiality:** The adversary eavesdrops the communication and reads the messages sent between the communication partners and such violates their privacy.

Figure 2.3: Attack on confidentiality.

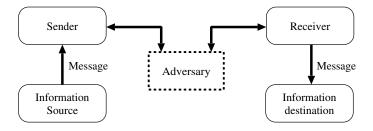

3. Attack on authenticity: The adversary alters the normal communication flow. In

Figure 2.4: Attack on authenticity.

an *impersonation attack* the adversary sends messages to the receiver and pretends to be a valid and intended sender. If the adversary intercepts a message, modifies its

## CHAPTER 2. CRYPTOGRAPHIC GOALS

content and sends it to the receiver intended by the legitimate sender, she performs a *substitution attack*. In an *deception attack* the adversary can either impersonate another entity, replay messages intercepted from a valid entity, or actively intervene in protocol executions by selectively combining multiple parallel protocol executions. In all three cases the authenticity of the sender is attacked.

Depending on the adversary's behavior and its role, all types of attacks can be divided into two groups:

- 1. *Passive attacks:* The adversary eavesdrops the communication between the legitimate communications partners. By doing so the confidentiality of the data is being attacked.

- 2. Active attacks: The adversary attempts to alter, delete and add data. By actively changing the normal communication flow the attacker threatens the integrity and/or the authenticity of the data.

Cryptography tries to treat and prevent these attacks in theory and in practice. However, multiple methods exist to realize the different cryptographic goals. The following chapter introduces some of the primitives that cryptography provides.

# Chapter 3

# Cryptographic Primitives

In order to prevent an adversary from successfully breaking the cryptographic goals cryptographic primitives are put into place. The aim of this chapter is to introduce important methods and to show how these methods can be used in order to secure a public channel. All the primitives presented in this chapter are based on the Kerckhoff's Principle [57] which states, that the security of a cryptographic system should solely rely on the use of a secret key but not on the use of secret primitives. Section 3.1 deals with symmetric and asymmetric encryption that can be used to provide confidentiality of data. Methods to ensure data origin authentication are treated in Section 3.2 and Section 3.3 explains the ideas and principles of quantum cryptography.

# 3.1 Encryption Schemes

A cipher or encryption scheme is a primitive that aims at providing the goal of confidentiality. In order to do so an encryption scheme enciphers a plaintext P, using a key K, to give a resulting message C called ciphertext. This transformation is called encryption. The inverse of this transformation, named decryption, deciphers a ciphertext C using the same or a different key  $\hat{K}$ , resulting in the original plaintext P again.

Encryption schemes have a long history. Already some thousand years ago cryptography was used to protect information. Over the centuries many different cryptographic methods have been developed, that now are categorized into classical and modern (or newer) ciphers. Classical ciphers typically encrypt at the level of letters using substitutions, where a plaintext letter is substituted with a ciphertext letter, or using transpositions where the plaintext symbols are reordered following given rules in order to give the ciphertext. However, modern ciphers usually work on bit level and can be categorized into symmetric ciphers and asymmetric ciphers.

Symmetric encryption schemes use identical keys for both communicating partners, that are kept secret and that are used for encryption and decryption. In contrast, in asymmetric encryption schemes (also known as public-key encryption schemes) each communication party owns two different keys. One key, called public key, is provided publicly and used for encryption whereas the second key, which is called private key and which is kept secret by its owner, is used for decryption. To be secure, the public key strictly needs to be authenticated.

In the following we formalize the definition of public-key encryption schemes and

symmetric encryption schemes and show the existing variants.

#### 3.1.1 Public-Key Encryption Schemes

Public-key cryptography uses a pair of associated keys  $\{K_e, K_d\}$  instead of a single secret key.  $K_e$  is called the public key and  $K_d$  is called the private key. It has to be infeasible to determine the  $K_d$  when knowing  $K_e$ .  $E_{K_e}()$  is the one-way function used for encryption and  $D_{K_e}()$  is the corresponding inverse one-way function that can be used for decryption.

When the two communication partners Alice and Bob want to communicate, Bob creates a key-pair  $\{K_e, K_d\}$  and sends his public key  $K_e$  to Alice but keeps his private key  $K_d$  secret. It is important, that the channel used to transmit the public key has to be authenticated. Alice can then encrypt a message P and send it to Bob using Bob's public key  $K_e$  and by applying the transformation  $C = E_{K_e}(P)$ . Bob can then decrypt this message using his private key by applying  $P = D_{K_d}(C)$ .

Public-key cryptography is able to fulfill all cryptographic goals defined in Section 2.1. In order to do so it only requires an authenticated channel. The authenticity of the channel is important as otherwise an adversary can distribute wrong public keys, for which she knows the corresponding private keys. In such case, the encrypted message would not be private anymore.

Public-key cryptography is much more complex than symmetric-key cryptography. Thus, in general, public-key cryptography is usually used to agree on secret keys that are then used for symmetric encryption schemes.

#### 3.1.2 Symmetric Encryption Schemes

Following [14] a symmetric encryption scheme can be defined as follows:

**Definition 1** (Symmetric Encryption Scheme). A symmetric encryption scheme,  $S\mathcal{E}$ , consists of three algorithms ( $\mathcal{K}, \mathcal{E}, \mathcal{D}$ ), as follows:

- 1.  $\mathcal{K}$  is a randomized *key-generation* algorithm that returns a string K. If  $\mathsf{Keys}(\mathcal{SE})$  is the set of all strings that have non-zero probability of being output by  $\mathcal{K}$ , then the members of this set are called *keys*.  $K \xleftarrow{\$} \mathcal{K}$  denotes the operation of executing  $\mathcal{K}$  to get the random key K returned.

- 2. The encryption algorithm  $\mathcal{E}$  can be stateful or randomized.  $\mathcal{E}$  takes a key  $K \in \mathsf{Keys}(\mathcal{SE})$  and a plaintext  $P \in \{0,1\}^*$  to return some ciphertext  $C \in \{0,1\}^*$ .  $C \xleftarrow{} \mathcal{E}_K(P)$  denotes the operation of  $\mathcal{E}$  on K and P.

- 3. The decryption algorithm  $\mathcal{D}$  takes a key  $K \in \mathsf{Keys}(\mathcal{SE})$  and a ciphertext  $C \in \{0,1\}^*$ to return some string  $P \in \{0,1\}^*$ , such that  $P \stackrel{\$}{\leftarrow} \mathcal{D}_K(C)$ . It is required that  $\mathcal{D}_K(C)$  returns P for each  $C \stackrel{\$}{\leftarrow} \mathcal{E}_K(P)$  for any key  $K \in \mathsf{Keys}(\mathcal{SE})$  and any message  $M \in \{0,1\}^*$ .

As the definition indicates, the key-generation algorithm  $\mathcal{K}$  is randomized. It takes no input but flips coins internally and uses these to select a key K. Usually the key is a random string of a fixed length that is called the key length of a scheme. Two parties that want to use a scheme need to generate a key K using  $\mathcal{K}$ . Once both parties share K, the sender is able to run the encryption operation  $\mathcal{E}$  with key K and plaintext P to produce the ciphertext C which is then transmitted to the receiver.

#### CHAPTER 3. CRYPTOGRAPHIC PRIMITIVES

The encryption algorithm may either be randomized or stateful. When randomized the algorithm, each time it is called, flips coins internally and uses those to compute the output for a given pair K, P. Consequently, performing the operation  $C_i = \mathcal{E}_K(P)$  twice may result in different results  $C_i$ . A stateful encryption algorithm in contrast, depends on a state that is initialized in a algorithm-specified an well-defined way. Whenever invoked, the algorithm computes the ciphertext C based on P, K and the current state. Finally, it updates and stores the state. There is no need for synchronization (apart from an initial synchronization) between the receiver and the sender. An encryption scheme that does not maintain a state is called stateless.

The receiver, upon receiving a ciphertext C computes the original message using  $P = \mathcal{D}_K(C)$  using the same key used to generate C. The decryption algorithm itself is never randomized or stateful but deterministic. Depending on the allowed lengths of the input message P, symmetric encryption schemes are classified as *block ciphers* or *stream ciphers*.

#### **Block Ciphers**

Block ciphers can either be symmetric-key or public-key. However, in the following only symmetric-key block ciphers are treated.

Block ciphers are set of Boolean permutations operating on *n*-bit vectors [32]  $V_n$  of fixed size, where *n* denotes the *block length* of the cipher, such that the cipher maps *n* input bits to *n* output bits under the use of a *k*-bit cipher key *K* that takes values out of the key-space *Keys*.

**Definition 2** (Block Cipher). An *n*-bit block cipher is a function  $\mathcal{E} : V_n \times \text{Keys}(\mathcal{SE}) \to V_n$ , such that for all keys  $K \in \text{Keys}(\mathcal{SE})$ , the encryption function  $\mathcal{E}(P, K)$  is an invertible mapping from  $V_n$  to  $V_n$  written as  $\mathcal{E}_K(P)$ . The decryption function which is denoted as  $\mathcal{D}_K(C)$  is the inverse mapping of  $\mathcal{E}_K(P)$  such that  $P = \mathcal{D}_K(C)$ .

Block ciphers operate on blocks of length n. In order to process messages exceeding the length of one block n those messages are processed by *modes of operation* which are cryptographic primitives based on block ciphers. Using these modes of operation, block ciphers can be used to accomplish a wide variety of cryptographic tasks. An introduction to some concrete modes of operation follows in Chapter 5.

## Stream Ciphers

Stream ciphers are another class of symmetric encryption algorithms. While block ciphers typically operate on larger blocks of multiple bits of data, stream ciphers usually operate on smaller sets of data. Additionally, stream ciphers use transformations that vary over time. So, in contrast to block ciphers, the encryption result  $C_i$  not only depends on the secret key K and the plaintext message  $P_i$  but also on the current state  $\sigma_i$  of the encryption engine. Typically stream ciphers are fast and less complex to realize in hardware. Furthermore, as they have a limited error propagation they might be advantageous for systems where transmission errors are likely to occur. However, one thing to mention is, that no stream cipher that is standardized exists by today. Still, by using special modes of operation block ciphers can be turned into a stream cipher.

Typically stream ciphers are defined by two functions, f and g such that,

$$\sigma_{i+1} = f(\sigma_i, P_i, K_i)$$

$$C_i = g(\sigma_i, P_i, K_i)$$

where f is the function to compute the next state  $\sigma_{i+1}$  and g is the actual encryption function.  $P_i$  is the bit (or number of bits) of the plaintext message P currently being processed and  $K_i$  is the corresponding key stream and  $\sigma_i$  is the present state.

In general, stream ciphers can be divided into two classes: *synchronous stream ciphers* and *asynchronous stream ciphers*.

Synchronous stream ciphers generate the key stream independently of the plaintext P and the cipher text C. So prior to communication the sender and the receiver have to be synchronized, to operate under the same key K and the same internal state  $\sigma_i$ . Synchronous stream cipher can be characterized by:

$$\sigma_{i+1} = f(\sigma_i, K_i)$$

$$Z_i = g(\sigma_i, K_i)$$

$$C_i = h(Z_i, P_i)$$

where f is the function to compute the next state and g is the function to produce the keystream and h is the output function that combines the keystream and the input message.

An *asynchronous stream cipher* is a stream cipher that generates the keystream as a function of the key and a fixed number of previous ciphertext bits:

$$\sigma_{i+1} = f(C_{i-t}, C_{i-t+1}, \dots, C_{i-1})$$

$$Z_i = g(\sigma_i, K_i)$$

$$C_i = h(Z_i, P_i)$$

where the next state  $\sigma_{i+1}$  is ciphertext dependent and where an initial state  $\sigma_0$  exists. As the state—and thus the keystream—is only dependent on a few previous ciphertext bits, the cipher is self-synchronizing even if some ciphertext bits are transmitted erroneous.

#### 3.1.3 Symmetric versus Asymmetric Encryption

When comparing symmetric encryption algorithms and asymmetric encryption algorithms the following advantages and disadvantages can be found:

- Symmetric encryption schemes typically execute much faster in software as well as in hardware than asymmetric encryption schemes with a comparable security level.

- Symmetric encryption scheme implementations usually are less resource consuming in terms of required area, power, energy, memory, etc.

- Symmetric encryption schemes require both parties to share a secret key. Distributing the secret key over a (secure) channel is known as the *Key Distribution Problem* and comes at some cost. To provide a high level of security, this shared secret key often needs to be changed and kept secure. The procedure of generating, managing, redistributing, storing and adopting the key in a secure way often is a complicated task to accomplish.

Increasing speeds of networks clearly favors fast encryption schemes. Thus, in this work we rely on symmetric encryption schemes.

# **3.2** Authentication Schemes

Data integrity is closely related to data origin authentication. In case a message is altered its integrity has been attacked and consequently the sender is not authenticated any more. Thus, data integrity and data origin authentication are intrinsically tied together. Consequently, when one of them is compromised also the other one has to be doubted. Hence, mechanisms for data authentication have to provide data origin authentication and data integrity.

An important class of cryptographic primitives used for authenticity is called *hash* functions. Hash functions in general can be divided into *unkeyed hash functions* which are also called *modification detection codes (MDCs)* and *keyed hash functions* also known as message authentication codes (MACs).

**Definition 3** (Hash Function). A hash function h (in its most unrestricted definition) has to provide to properties:

- 1. The function h has to provide *compression* by mapping an input x of arbitrary (finite) bitlength to an output y = h(x) of fixed bitlength n.

- 2. Given h and an input x the output y = h(x) has to be easy to compute.

The basic idea of hash functions is that the hash tag serves as a small-sized representative for the input string and can be used as a unique identifier for that string and can thus warrant the integrity of the string. However, as a hash function maps messages of arbitrary finite length of a domain D to an output of n-bit length in range R where |D| > |R|, there have to exist collisions where two distinct input messages x and x' map to the same output y = h(x) = h(x').

In the remainder of this section we will first describe unkeyed hash functions and then show how to transform these into keyed hash functions to create concrete authenticity primitives.

#### 3.2.1 Unkeyed Hash Functions

An unkeyed hash function, also called modification detection code (MDC) takes an input of arbitrary length and compresses it to a fixed length output called hash value or hash tag. As per definition, the space of possible outputs y = h(x) is restricted to  $2^n$ , where n is the bitlength of the hash tag, whereas the space of the input x is unlimited (but still finite). An cryptographic hash function, in addition to the properties given in Definition 3 has to fulfill the following properties [71]:

- 1. **Preimage resistance:** It should be computationally infeasible to find a preimage x' hashing to a given prespecified hash value y such that y = h(x').

- 2. Second preimage resistance: It should be computationally infeasible to find any input x' that hashes to the same output as a given input x. So it should be hard to find any input  $x' \neq x$  hashing to y = h(x') = h(x). Another term for second preimage collision resistance is weak collision resistance.

## CHAPTER 3. CRYPTOGRAPHIC PRIMITIVES

3. Collision resistance: It should be computationally infeasible to find any two inputs x and x' hashing to the same value y = h(x) = h(x'). Collision resistance is also called strong collision resistance.

In addition, for cryptographic MDCs the following properties are of interest:

- 1. *Non-correlation:* Input bits and output bits should not correlate and it is desirable to have an avalanche effect where every input bit effects every output bit.

- 2. Near-collision resistance: It should be hard to find any two input messages x and x' such that the output of h(x) and h(x') differ only in a small number of bits.

- 3. *Partial preimage resistance* or *Local one-wayness:* It should be hard to recover any substrings or even the entire input message even if parts of the input message are known.

## 3.2.2 Keyed Hash Functions

Hash functions that involve the use of a secret key are called *keyed hash function* or *message authentication codes (MACs)*. MACs, in contrast to MDCs, can also be used to provide data origin authentication and data integrity.

**Definition 4** (Message Authentication Code (MAC)). A message authentication code is a class of functions  $h_k$  that is parametrized by a secret key k and that is characterized by the following properties [71]:

- 1. For a function  $h_k$  and a given input message x and a given key k the output of  $h_k(x)$  has to be *easy to compute*. The resulting output is called *MAC-value* or *MAC*.

- 2. The function  $h_k$  has to provide *compression* by mapping an input x of arbitrary (finite) bitlength to an output  $h_k(x)$  of fixed bitlength n.

In addition, for a given function h and for all fixed allowable (but unknown to the adversary) key values k, the following properties have to hold:

3. It has to provide *computation resistance* by making it infeasible to compute any text-MAC pairs  $(x, h_k(x))$  for any new input  $x_i \neq x$  (including possibly  $h_k(x) = h_k(x_i)$ for some *i*), given zero or more text-MAC pairs  $(x_i, h_k(x_i))$ .

MACs can be constructed using different approaches. Based on their underlying compression function they can be classified into the following groups:

- **Based on block ciphers:** Many MAC algorithms used are based on block ciphers and often use these in cipher-block-chaining mode (CBC) [76] or electronic codebook mode (ECB) [76].

- Based on hash functions: These constructions use MDCs (hash functions) in combination with a secret key that is part of the input. An example for this type of construction is the HMAC [60, 75] construction with SHA-3 [82] as underlying MDC.

- **Customized MACs:** Those MAC algorithms are specially designed ("from scratch") for the purpose of message authentication. Often these algorithms exploit the properties of hash function families and are called universal hash based MACs.

# 3.3 Quantum Cryptography

Quantum cryptography (QC) is not a classical cryptographic primitive but has been topic of extensive research in recent years and has clearly evolved to a practical level. The idea of QC was first proposed by Wiesner [107] (1983) and by Charles H. Bennett and Gilles Brassard [18] (1984). It is based on the existence of indivisible quanta and entangled systems and some of the fundamental principles of quantum mechanics [47]:

- 1. Every measurement perturbs the measured system.

- 2. According to the Heisenberg uncertainty principle it is impossible to simultaneously determine the position and the momentum of a particle precisely.

- 3. It is impossible to determine the polarization of a photon in vertical-horizontal basis simultaneously to the diagonal basis.

- 4. It is impossible to draw pictures of individual quantum processes.

- 5. It is impossible to copy or duplicate an unknown quantum state.

These negative characteristics of quantum mechanics turn out to be useful in QC. As mentioned, a principle of quantum mechanics is:

Every measurement perturbs the system.<sup>1</sup>

$$(3.1)$$

This fact can be used to detect eavesdropping when used in QC. Imagine, Alice codes information into single photons she sends to Bob, then Bob can determine eavesdropping by checking that he receives the photons unperturbed. If an evil attacker Eve wants to catch information on the photons she has to do measurements and consequently perturbs the system. To check whether someone listened to their communication all Alice and Bob have to do is to compare a random subset of the transmitted data using a public channel. If this subset is equal there was no eavesdropping.

So Alice and Bob can detect eavesdropping but only after having transmitted a message. This is not practicable when secret information has to be exchanged. Thus, in order to ensure privacy in advance Alice and Bob only exchange a random secret key over the quantum channel and use this key to later encrypt the actual secret data typically over a classical channel. If they realize eavesdropping while exchanging the secret key they simply discard it and exchange a new one. Consequently they can assure that no secret information of value is lost.

In order to ensure that Axiom (3.1) applies the data has to be encoded into nonorthogonal states. In practice individual photons that are either sent over optical fibres or over free space are used to encode the quanta or qubits (for quantum bits). For example the horizontal and the vertical polarization of a photon could be used to code the bit values of bit 0 and bit 1. As a second and diagonal base the  $\pm 45^{\circ}$  linear polarization with  $+45^{\circ}$ for bit 1 and  $-45^{\circ}$  for bit 0 could be used. Alternatively, the circular polarization basis could be used as a second base.

Section 3.3.1 will show a practical example that make use of the principles described above.

<sup>&</sup>lt;sup>1</sup> Except if the quantum state is compatible with the measurement.

### 3.3.1 Example of the BB84 Protocol

The BB84 protocol was proposed in 1984 by Bennet and Brassard in [18]. In its original description the protocol uses photon polarization states to transmit the information. However any two conjugate pairs of states can be used to implement the protocol. The following description of BB84 will stick with the original proposal.

## Principle

The protocol uses four quantum states that can be represented as up  $|\uparrow\rangle$ , down  $|\downarrow\rangle$ , left  $|\leftrightarrow\rangle$  and right  $|\rightarrow\rangle$  which constitute two bases. The two bases conjugate as all vectors of one base have equal-length projections in the vectors of the other base, e.g.  $|\langle\uparrow| \leftrightarrow\rangle|^2 = \frac{1}{2}$ . By convention the two states  $|\uparrow\rangle$  and  $|\rightarrow\rangle$  represent a binary 0 and the states  $|\downarrow\rangle$  and  $|\leftrightarrow\rangle$  denote a binary 1. The four spin states can also be represented as polarization states "horizontal" and "vertical" (belonging to the base +) and "+45°" and "-45°" (belonging to the base  $\times$ ).

First, Alice sends random individual spins which represent random bits to Bob over a quantum channel that allows a one-to-one communication between the two parties. Next, Bob chooses a random base for each incoming qubit and measures its spin according to the chosen base. So, whenever Alice and Bob chose the same base they get correlated results but when they pick different bases they get uncorrelated results. Thus, on average Bob receives a string of bits with an error rate of 25%, called the *raw key*.

| Alice's random bit               | 0          | 1             | 1          | 0          | 1          | 0          | 0          | 1             |

|----------------------------------|------------|---------------|------------|------------|------------|------------|------------|---------------|

| Alice's random sending basis     | +          | +             | ×          | +          | ×          | Х          | ×          | +             |

| Photon polarization Alice sends  | $\uparrow$ | $\rightarrow$ | $\searrow$ | $\uparrow$ | $\searrow$ | $\nearrow$ | $\nearrow$ | $\rightarrow$ |

| Bob's random measuring basis     | +          | ×             | ×          | ×          | +          | Х          | +          | +             |

| Photon polarization Bob measures | $\uparrow$ | rand          | $\searrow$ | rand       | rand       | $\nearrow$ | rand       | $\rightarrow$ |

| Public discussion of basis       | OK         | drop          | OK         | drop       | drop       | OK         | drop       | OK            |

| Shared sifted key                | 0          |               | 1          |            |            | 0          |            | 1             |

Table 3.1: Example key agreement using the BB84 protocol.

In order to perform an error correction Bob announces the base he has chosen for measuring each corresponding qubit over a public channel. Alice then publicly tells Bob whether the base he has chosen is compatible with the state she has chosen to encode the qubit. In case the states is compatible they keep the bit and otherwise they discard it. So, around 50% of the bit string is discarded which results in a shorter key called *sifted key*. Note, that the error correction is performed on a public channel that Eve can listen to. To prevent Eve from modifying the information transmitted in this process this channel has to be authentic (but not necessarily confidential).

#### **Attack Scenarios**

If Eve intercepts a qubit, Bob will simply inform Alice that he didn't receive it as expected and tell her to discard it. Thus, Eve has no information gain and can only lower the transmission rate. So, for real eavesdropping Eve needs to send a new qubit (that ideally would be a copy of the intercepted one) to Bob after intercepting the qubit sent by Alice. However, it can be proved that perfect copying is impossible in the quantum world [72, 108]. A simple and practical eavesdropping strategy that Eve could use is called intercept-resend. Eve measures each qubit in one of the two bases, and then transmits another qubit to Bob that correlates to the state she measured. As Eve does not know the base Alice chose she will be lucky in about 50% and resend a qubit with the correct base to Bob such that the legitimate communication partners will not realize her intervention. However, in the other halve of the tries she will be wrong and use a basis incompatible with Alice's and Alice and Bob will notice the intrusion. This clearly emphasizes the importance that Alice chooses the basis truly random. Using the intercept-resend strategy Eve can get about 50% information gain, while Alice and Bob will have about 25% errors in their sifted key which would definitely reveal the presence of Eve. In case Eve only applies the strategy in 10% of the cases, this will give her an information gain of around 5% while Alice and Bob will have an error rate of around 2.5% in their sifted key. The next subsection will show how such attacks can be countered.

## Error Correction, Privacy Amplification

The sifted key Alice and Bob have been sharing so far contains errors due to technical imperfections and eventually due to the intervention of Eve. With today's technologies typical error rates lie around a few percent (which is beyond comparison with typical optical communication with error rates of about  $10^{-9}$ ). So in the first step called *information reconciliation*, Alice and Bob use classical error correction algorithms in order to get rid of the errors. Then, to lower Eve's information on the final key, they use a strategy called *privacy amplification*. In practice Alice and Bob often use a cascading protocol and compare the parity of blocks of the sifted key. In case of an error a binary search is performed to find and correct the error as proposed in [23]. This process is performed recursively until all blocks have been compared. Then the key stream is reordered and the procedure is repeated for several rounds. In the end Alice and Bob have identical keys with high probability. However, Eve has gained additional information on the key because of the parity bits exchanged. Privacy amplification is then used to lower Eve's information on the key to a arbitrarily low value. This could be done using a hash function that takes a string of length equal to the key and outputs a final key string of chosen shorter length.

## 3.3.2 Other Protocols

A variety of protocols for QC using either non-orthogonal or entangled quantum states have been published. In the following, a small selection of these will be presented. First, the *Two-State Protocol* and the *Six-State Protocol* which are both based on non-orthogonal quantum states will be described and then the *EPR Protocol* which uses entangled quantum states will be introduced. For a more complete overview of protocols please refer to [36, 47].

### **Two-State Protocol**

The two-state or B92 protocol by Bennet [16] only uses two non-orthogonal states. Alice randomly sends one of the two states and Bob then performs projections onto subspaces orthogonal to the signal states. In case Bob chooses a base non-orthogonal to the one Alice used he will obtain a result in 50% of the cases whereas he will obtain an inconclusive outcome if he chooses a base orthogonal to the one the qubit was encoded with. After transmission Bob tells Alice when he detected a bit but he does not announce the base he used because the base uniquely identifies the bit Alice sent.

However, in practice this system is only secure in lossless systems because while it is true that two non-orthogonal states cannot be distinguished precisely without perturbation it can be done at the cost of some losses. Eve could intercept the qubits and perform measurements. If she obtains an inconclusive result she blocks the qubit while she retransmits a copy in the correct state to Bob if she detects a state (because she then knows the state with certainty). To disguise the photons she blocked, Eve could send a pulse of higher intensity, such that Bob cannot realize a decrease in transmission rate.

One way to counter this attack is to encode the bits into phase differences between a strong reference pulse and a dim pulse (with less than on photon on average). In this case Bob can monitor the bright pulses and make sure that Eve does not remove any of them. Furthermore Eve can not remove one of the dim pulses because the interference of the strong pulse with vacuum would introduce errors that would be detected.

#### Six-State Protocol

In the six-state protocol [11, 24] three non-orthogonal bases are used for encoding the qubits with six states. Accordingly, the probability that Alice and Bob choose the same base is only  $\frac{1}{3}$ . However, this disadvantage of compared to the BB84 protocol is outweighed by the fact that eavesdropping inducts higher error rates. In case Eve tries to perform the previously mentioned intercept-resend attack and measures every qubit, this results in an error rate of around 33%, compared to 25% when applied in the BB84 protocol.

## EPR Protocol

The original EPR protocol is based on quantum entanglement and Bell's inequalities and was originally proposed by Ekert [37]. A simplified version that does not invoke Bell's inequalities was presented by Bennett, Brassard and Mermin [17].

The idea of the simplified version is to replace the quantum channel between Alice and Bob by a channel carrying two entangled qubits from a common source. Both communication parties Alice and Bob measure the qubits independently using random bases. They then compare their bases and only keep the bits in case of congruence. In fact this protocol is very much alike the BB84 protocol. The only difference is that Alice does not send particles but she measures her particle of the entangled pair within one of the two bases.

# 3.3.3 Security of Quantum Cryptography

The security of QC is based on basic quantum-mechanic principles. Classical QC protocols consist of two phases:

- 1. A physical device generates quantum mechanic signals that are distributed and measured. They are then transformed into classical data.

- 2. Alice and Bob use a classical channel to discuss their data and to perform error correction and privacy amplification.

The unconditional security of those phases can be proved for theoretical systems [68, 69, 101] and even for imperfect devices [48]. However, it should be noted that real world systems suffer from technical imperfections that allowed practical attacks on real word

implementation. For a good overview on the security of QC and attacks theoretic as well as practical attacks that were possible due to imperfect implementations please refer to [89, 97].

### 3.3.4 Summary and Discussion

As shown, QC does not provide a complete solution for all cryptographic goals but can only be used in conjunction with classical symmetrical cryptographic primitives. Thus, a more precise name for QC is *quantum key distribution* as this is the purpose of QC. In addition it should be noted once more, that QC requires the two communication partners to be authenticated. Consequently, Alice and Bob need to share a small secret prior to communication. QC can then provide them a longer one and parts of his longer key could then be used as a starting secret for the next session.

For a wider and more complete overview as well as detailed discussions on quantum cryptography, the security of QC, attacks and technical realizations please refer to [7, 36, 47].

# 3.4 Conclusion

Cryptographic primitives based on the Kerckhoff's Principle, rely on the use of secret keys. In order to provide confidentiality symmetric or asymmetric encryptions can be used. MACs can be used to provide data origin authentication and data integrity. The problem of distributing these secret keys required for these primitives among the communication partners is know as the *key-distribution problem*. One possible solution to this problem is the use of public-key cryptography and another solution is based on the use of quantum cryptography. However, more solutions to this problem exist. Chapter 4 will discuss these solutions in detail.

# Chapter

# Key-Distribution Problem

The security of modern cryptographic algorithms, based on Kerckhoff's Principle, does not rely on the obscurity of an algorithm but only on the use of a secret key. Thus, secure distribution of secret keys among legitimate users is a central problem in cryptography that is known as the *Key-Distribution Problem* or as the *Key-Establishment Problem*. Basically there are five cryptographic ways to solve the Key Establishment Problem [7]:

- 1. Classical Information-theoretic schemes: Cryptosystems are called information-theoretically secure if they derive their security solely from information theory and thus do not make any assumptions on the hardness of any mathematical problems. Consequently, such systems are still secure even if an adversary has unbounded computing power. A well known example for an information-theoretically secure scheme is the One-Time Pad (OTP). If two parties are in possession of correlated strings that feature more correlation than any string that an eavesdropper could possess, it is possible to establish an information-theoretically secure key over a classical channel using public discussion, as shown in [66]. In fact, as will be shown later in this section, the use of a quantum channel allows a practical realization to provide such correlated strings of information.

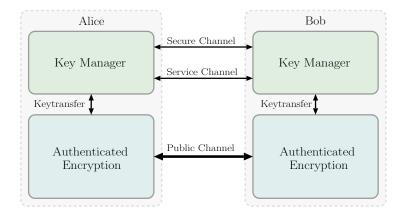

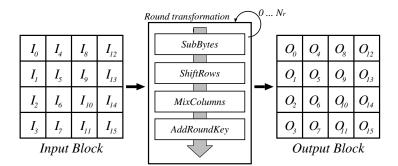

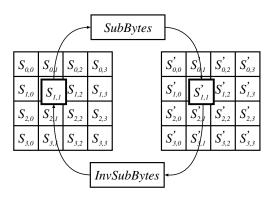

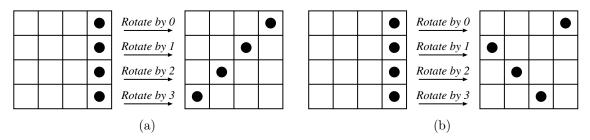

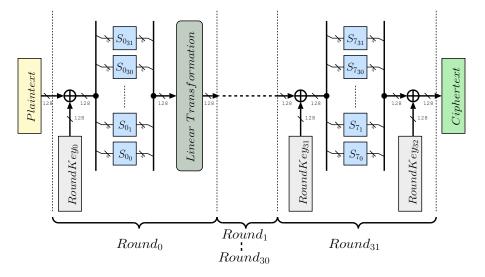

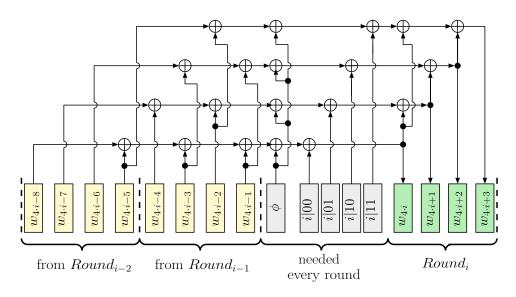

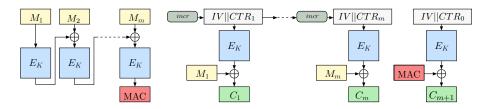

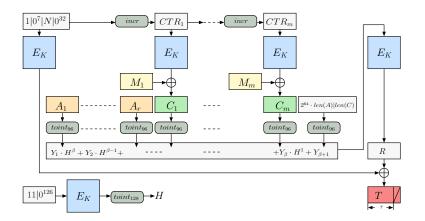

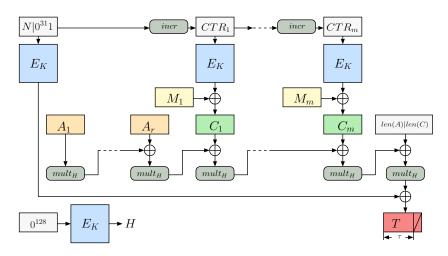

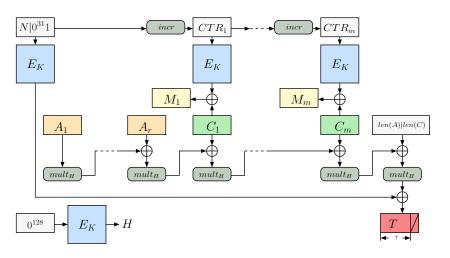

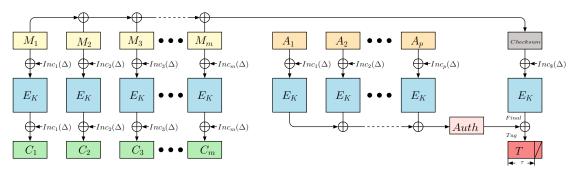

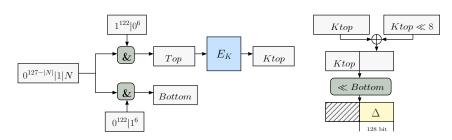

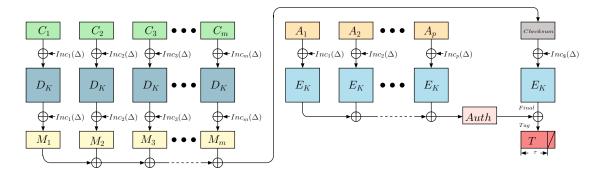

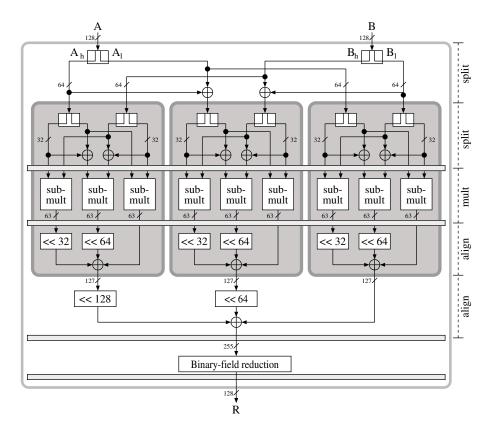

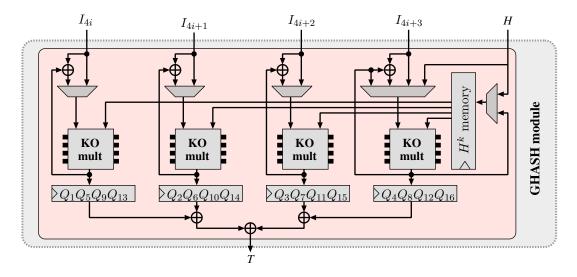

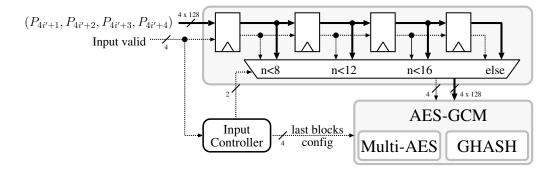

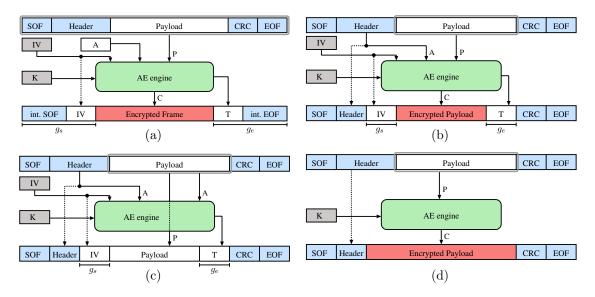

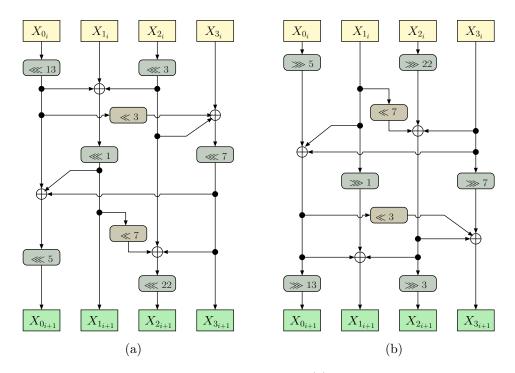

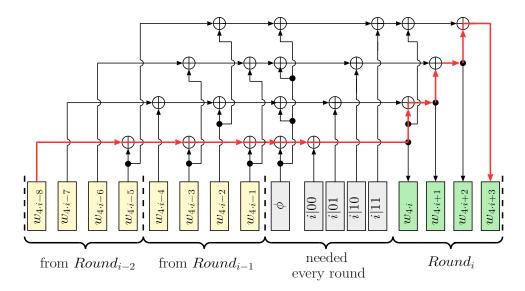

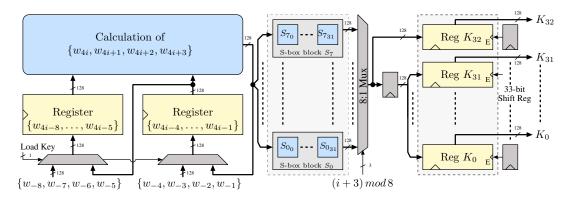

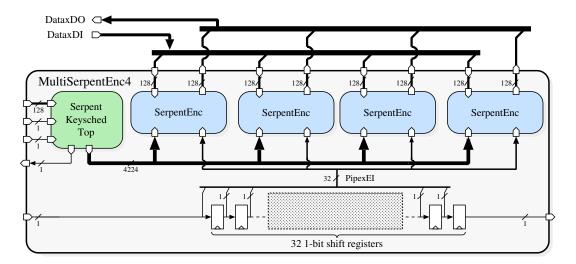

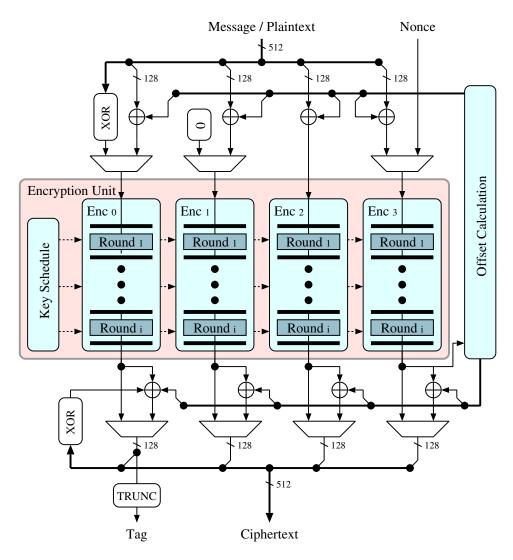

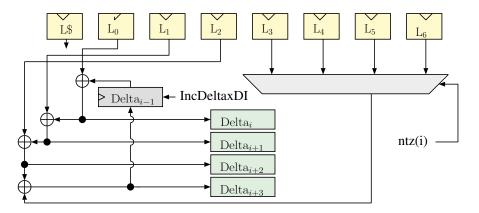

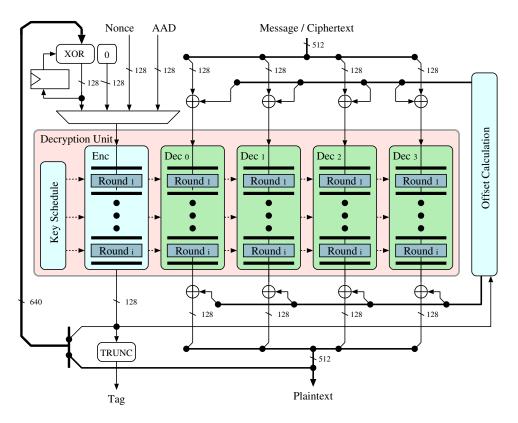

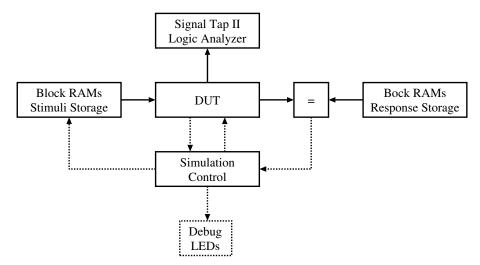

- 2. Classical public-key cryptography: Public-key cryptography or asymmetric encryption is based on the difficulty of mathematical problems for which no polynomial algorithm exists to solve them. Therefore, by using secret keys that are long enough the computing resources to find solutions to these problems become infeasible. Publickey cryptography relies on "provable computational security". However, it should be noted, that it is not unconditionally secure as the underlying mathematical problems are not unsolvable and as the non-polynomial complexity has not been proven yet.