Master's Thesis

# Emulation-based Sub-module Activity Analysis to Accelerate Fault Injection Campaigns

Daniel Böhmer, BSc

Institute for Technical Informatics Graz University of Technology Austria

Assessor: Ass. Prof. Dipl.-Ing. Dr. techn. Christian Steger Advisor: Ass. Prof. Dipl.-Ing. Dr. techn. Christian Steger Dipl.-Ing. Dr. techn. Johannes Grinschgl

Graz, April 2013

Deutsche Fassung: Beschluss der Curricula-Kommission für Bachelor-, Master- und Diplomstudien vom 10.11.2008 Genehmigung des Senates am 1.12.2008

# EIDESSTATTLICHE ERKLÄRUNG

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe.

Graz, am .....

(Unterschrift)

Englische Fassung:

# STATUTORY DECLARATION

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

date

(signature)

# Abstract

Fault injection is a hardware and software verification method in research and industry. It is used to detect flaws and weaknesses in the hardware description of complex digital designs. It gives the verification engineer the possibility to examine the system-under-test in the occurrence of faults. The emulation of digital hardware designs upon FPGAs has become a standard methodology to test the digital design extensively before going into production. And the emulation of the hardware can further be used to inject faults directly into the design. Such a process is then known as fault emulation.

Usually the verification engineer has to decide how a fault can be injected, but modern systemon-chip designs have gotten very complex and now they provide a big spectrum of fault injection targets. Not all locations and timings can be covered in fault injection campaigns.

This thesis studies and develops a novel method to gain pre-injection knowledge. The activation and the deactivation of selected modules shall give information about possible fault injection targets. The activity of those modules is observed during a normal execution with an expected behavior, also known as a golden-run. Subsequent fault injections afterwards can build up on the knowledge about the activity of those modules. To observe the activity of hardware modules, those modules are extended by sensors. A measurement unit is placed into the system-under-test and the sensors on the modules inform the measurement unit about the activity where it is processed and recorded. The fault injection is performed with an additional fault injection framework. It exists parallel to the activity measurement unit within the digital design. An external controller logic decides afterwards which fault injection will be executed upon the design.

The activity and fault injection experiments were performed on a general purpose processor. A processor usually consists of many different and independent modules. The in VHDL freely available LEON3 processor was selected for the experimentation.

# Kurzfassung

Fehlerinjektion ist eine Verifikationsmethode in Forschung und Industrie für digitales Hardware-Design. Damit können Fehler und Schwächen in einem Sicherheitskonzept nachgewiesen werden. Verifikationsingenieure können das System unter der direkten Einwirkung von Fehlern beobachten und evaluieren. Die Emulierung von Hardware-Designs auf einem FPGA ist eine Standard-Anwendung, um das Design während der Entwicklung ausgiebig zu testen. Eine solche Hardware-Emulierung kann nun auch verwendet werden, um absichtlich Fehler während des Funktionsbetriebes in die digitalen Schaltkreise einzubringen. Eine solche Anwendung bezeichnet man dann auch als Fehler-Emulation.

Normalerweise muss der Verifikationsingenieur selbst entscheiden, wo und wie er einen Fehler einbringen soll. Aber komplexe System-on-Chip-Designs (SoC-Designs) bieten ein zu breites Spektrum an Möglichkeiten. Eine vollständige Abdeckung kann manuell nicht erreicht werden.

Diese Arbeit untersucht eine neuartige Möglichkeit, Vorwissen über das System zu erlangen um damit Fehler-Injektionen gezielt einsetzen zu können. Die Aktivierung und Deaktivierung ausgewählter Module soll Informationen über mögliche Fehlerinjektions-Ziele geben. Die Aktivität dieser Module wird während einer normalen Ausführung mit bekanntem Verhalten (Golden-Run) beobachtet. Anschließende Fehlerinjektionen werden mit dem Wissen über die Aktivität ausgewählt und gesteuert. Um diese Aktivität beobachten zu können, werden die Module mit Sensoren erweitert. Weiters wird das System mit einer zentralen Aktivitäts-Messungs-Einheit ausgestattet. Die Sensoren informieren diese Einheit über die aktuelle Aktivität ihrer Module. Die Fehlerinjektionen werden mit einem zusätzlichen Framework eingebracht. Dieses Framework existiert parallel zur Aktivitäts-Messung im digitalen Hardware-Design. Ein externer Controller entscheidet anschließend, welche Strategie zur Fehlerinjektion auf dem Design angewandt wird.

Die Experimente zur Aktivitätsanalyse und zur Einbringung der Fehler wurden an einem *General Purpose Processor* durchgeführt. Ein solcher Prozessor enthält generell ein großes Spektrum an verschiedenen unabhängigen Modulen und eignet sich daher besonders für das Forschungsgebiet der Fehlerinjektionen. In dieser Diplomarbeit wurde der in VHDL frei verfügbare LEON3 Prozessor verwendet.

# Danksagung

Ich möchte mich zuallererst bei meinen Eltern bedanken, die mir das Studium der Telematik durch ihren finanziellen und emotionalen Beistand ermöglicht haben.

Ein weiterer großer Dank geht an meine Freunde und Mitstudenten, im Speziellen an die Mitglieder der Basisgruppe Telematik, deren Gemeinschaft mich durch mein ganzes Studium begleitet hat und mich so vieles lehrte, was nicht durch Lehrveranstaltungen abgedeckt werden konnte.

Ich möchte ich mich bei meinem Betreuer Dipl.-Ing. Dr. Johannes Grinschgl dafür bedanken, dass er es mir ermöglichte in diesem Gebiet zu arbeiten und dass er mich mit all seinem Wissen und seiner Geduld während der Diplomarbeit über alle Maße unterstützte. Weiters möchte ich meinen Dank an Dipl.-Ing. Manuel Menghin richten. Er unterstützte mich bei der Korrektur und beim Abschluß meiner Diplomarbeit.

Ein herzliches Dankeschön gilt besonders Ass.-Prof. Dr. Steger. Im besonderen für die Möglichkeit am Institut für Technische Informatik als studentischer Forschungsassistent im Gebiet des Hardware/Software Co-Designs tätig zu sein. Aus dieser Tätigkeit hat sich ein großer Teil dieser Diplomarbeit ergeben.

# Acknowledgements

Firstly, I would like to thank my parents, for the possibility to study telematics and for their support and assistance through all the years.

Special thanks to all my friends and fellow students, especially the members of "Basisgruppe Telematik". The community and friendship accompanied me through the entire studies. Also they thought me all those things that lectures can not teach.

I want to thank my advisor Dipl.-Ing. Dr. Johannes Grinschgl. I am grateful for the opportunity to work in this field of research and for all the support and patience he gave to me. Further I would like to thank Dipl.-Ing. Manuel Menghin for supporting me at the end of my thesis.

A very big thanks goes to Ass-Prof. Dr. Steger. Especially for giving me the possibility of working at the Insitute for Technical Informatics as a research assistant in the field of hard-ware/software codesign. A big part of my thesis arised from this work.

# Contents

| 1 | Intr | oduction                                          | 11 |

|---|------|---------------------------------------------------|----|

|   | 1.1  | Context                                           | 11 |

|   | 1.2  | Thesis approach                                   | 12 |

|   | 1.3  | Thesis organization                               | 13 |

| 2 | Fun  | damentals                                         | 14 |

|   | 2.1  | Faults                                            | 14 |

|   |      | 2.1.1 Terminology                                 | 14 |

|   |      | 2.1.2 Types of faults                             | 14 |

|   |      | 2.1.3 The source of faults                        | 15 |

|   | 2.2  | Fault injection                                   | 15 |

|   |      | 2.2.1 Physical fault injection                    | 16 |

|   |      | 2.2.2 Simulated fault injection                   | 16 |

|   |      | 2.2.3 Emulated fault injection                    | 16 |

| 3 | Rela | ated work                                         | 19 |

| - | 3.1  | Optimize fault injection campaigns                | 19 |

|   | 0.1  | 3.1.1 Using pre-injection analysis                | 19 |

|   |      | 3.1.2 Optimize the fault space                    | 20 |

|   |      | 3.1.3 Detect dependencies                         | 21 |

|   |      | 3.1.4 Optimizing emulated fault injections        | 21 |

|   | 3.2  | Power emulation                                   | 22 |

|   |      | 3.2.1 Power emulation using access counters       | 22 |

|   |      | 3.2.2 Power emulation using sensors on components | 22 |

| 4 | Con  | icept                                             | 24 |

| • | 4.1  | General                                           | 24 |

|   | 4.2  | The LEON3 processor                               | 24 |

|   | 4.3  | The Modular Fault Injector (MFI)                  | 25 |

|   | 4.4  | The FPGA and development environment              | 27 |

|   | 4.5  | The concept of the activity analysis              | 28 |

|   | 4.6  | Fault injection optimization                      | 30 |

| 5 | lmn  | lementation                                       | 31 |

| Ŭ | 5.1  | Architecture of the activity measurement unit     | 31 |

|   | 0.1  | 5.1.1 Activity Sensors                            | 31 |

|   |      | 5.1.2 The activity measurement                    | 32 |

|   |      | 5.1.3 Usage on the FPGA                           | 33 |

|   |      | 5.1.4 Configuration Registers                     | 34 |

|   |      | 5.1.5 Activity Memory Entry                       | 34 |

|   | 5.2          | Modules                                                                                    | 35             |

|---|--------------|--------------------------------------------------------------------------------------------|----------------|

|   |              | 5.2.1 Multiplier - smul $32$                                                               | 35             |

|   |              | 5.2.2 Divider - sdiv $32$                                                                  | 38             |

|   |              | 5.2.3 Data cache - dcache                                                                  | 40             |

|   |              | 5.2.4 Instruction cache - icache                                                           | 48             |

|   |              | 5.2.5 Register file - regfile                                                              | 48             |

|   |              | 5.2.6 Gaisler General Purpose Input/Output - GRGPIO                                        | 49             |

|   |              | 5.2.7 AES coprocessor                                                                      | 50             |

|   | 5.3          | Fault injection unit                                                                       | 52             |

|   | 5.4          | Automatic module analysis                                                                  | 53             |

|   |              | 5.4.1 Simulation of the modules                                                            | 53             |

|   |              | 5.4.2 Preparation of the simulation results                                                | 54             |

|   |              |                                                                                            | 56             |

|   |              |                                                                                            | 58             |

|   | 5.5          |                                                                                            | 58             |

|   |              |                                                                                            |                |

| 6 | Ехр          |                                                                                            | 60             |

|   | 6.1          | 1                                                                                          | 60             |

|   | 6.2          | The emulation observance software on the PowerPC processor                                 | 61             |

|   |              |                                                                                            | 61             |

|   |              | 5                                                                                          | 62             |

|   |              | 1                                                                                          | 63             |

|   | 6.3          | Fault injections                                                                           | 64             |

|   |              | $6.3.1  \text{Saboteurs}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 64             |

|   |              | 6.3.2 Fault injection with permanent faults                                                | 65             |

|   |              | 6.3.3 Transient faults (randomly and activity based)                                       | 67             |

|   |              | 6.3.4 Results                                                                              | 70             |

|   |              | 6.3.5 Further observations                                                                 | 70             |

| 7 | Can          | clusion                                                                                    | 72             |

| ' | 7.1          |                                                                                            | 72             |

|   | $7.1 \\ 7.2$ |                                                                                            | 72<br>73       |

|   | 1.2          |                                                                                            | 73<br>73       |

|   |              | 1                                                                                          | 73<br>73       |

|   |              | 0                                                                                          |                |

|   |              | 7.2.3 Automatic insertion of sensors                                                       | 73             |

| 8 | App          | endix                                                                                      | 74             |

|   | 8.1          |                                                                                            | 74             |

|   | 8.2          | Synthetization of the LEON3 with the Activity Unit and Fault Injection Con-                |                |

|   |              | Ŭ Ŭ                                                                                        | 74             |

|   | 8.3          |                                                                                            | 75             |

|   | 8.4          |                                                                                            | . o<br>76      |

|   | 8.5          |                                                                                            | . o<br>77      |

|   |              |                                                                                            | $\frac{1}{77}$ |

# List of Figures

| 3.1  | Pre-injection analysis on resource usage for path based injections, as described   | 20              |

|------|------------------------------------------------------------------------------------|-----------------|

| 3.2  | by Tsai et al. [31]                                                                | 20              |

| 0.2  | et al. [9]                                                                         | 21              |

| 3.3  | Power emulation concept of Genser et al. [16]                                      | $\frac{21}{23}$ |

| 0.0  |                                                                                    | 20              |

| 4.1  | Main components of the LEON3 processor [4].                                        | 25              |

| 4.2  | Golden Run flow as proposed by [18]                                                | 27              |

| 4.3  | An activity sensor of a module                                                     | 28              |

| 4.4  | The module activity send by the activity sensors                                   | 29              |

| 5.1  | Implementation principle of a sensor                                               | 31              |

| 5.2  | Modules of the LEON3 processor are extended with sensors and connected to the      |                 |

|      | activity measurement unit.                                                         | 32              |

| 5.3  | The LEON3 processor extended with activity sensors and the activity measure-       |                 |

|      | ment unit that communicates with the PowerPC of the FPGA.                          | 33              |

| 5.4  | The configuration registers of the activity data collection module                 | 34              |

| 5.5  | The arrangement of the modules within the module mask                              | 34              |

| 5.6  | A single entry in the memory of the Activity Measurement Unit                      | 34              |

| 5.7  | Block diagram of the mul32 module                                                  | 36              |

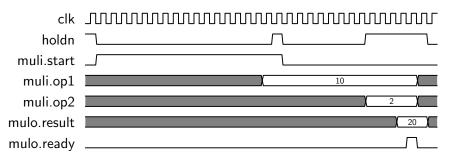

| 5.8  | Signal waveforms of the multiplier                                                 | 36              |

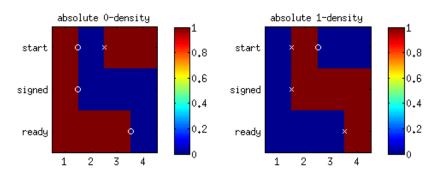

| 5.9  | Result of the VCD analysis of several multiplier initiations                       | 37              |

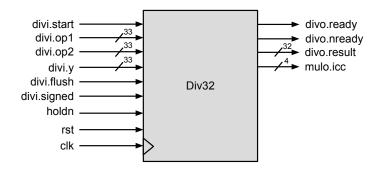

| 5.10 | Block diagram of the div32 module.                                                 | 39              |

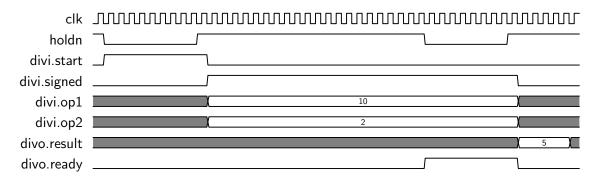

| 5.11 | Signal waveforms of the divider                                                    | 39              |

|      | Result of the VCD analysis of several divider initiations                          | 40              |

| 5.13 | Block diagram of the data cache.                                                   | 42              |

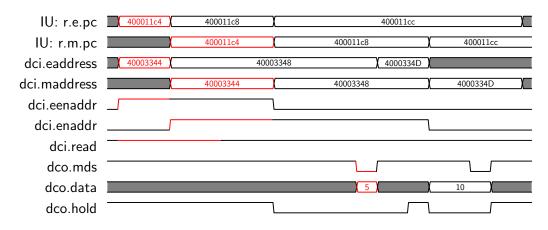

|      | Signal waveforms of the data cache on a cache-miss.                                | 43              |

|      | High/Low Density for a data cache-miss with only 1 load instruction                | 43              |

| 5.16 | Signal waveforms of the data cache on a cache-miss with two sequential loading     |                 |

|      | instructions                                                                       | 44              |

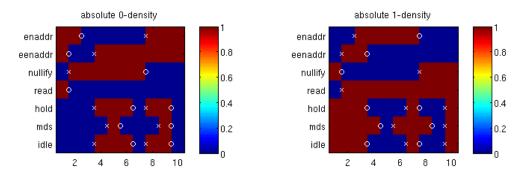

|      | High/Low Density for a data cache-miss with 2 load instructions                    | 44              |

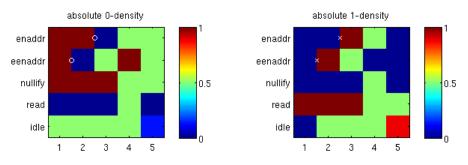

|      | Signal waveforms of the data cache on a cache-hit.                                 | 45              |

|      | High/Low Density for a data cache-hit with only 1 load instruction.                | 45              |

|      | High/Low Density for a data cache-hit with 2 load instructions                     | 46              |

|      | Signal waveforms of the data cache with a write instruction                        | 46              |

|      | High/Low Density for a cache write instruction.                                    | 47              |

|      | Block diagram of the register file module.                                         | 48              |

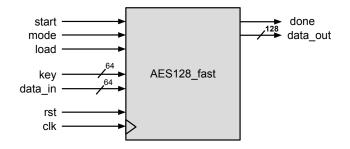

|      | Block diagram of the AES module.                                                   | 51              |

| 5.25 | Modular fault injector with trigger configuration and saboteurs (S) in multiplier, |                 |

|      | data cache and instruction cache.                                                  | 52              |

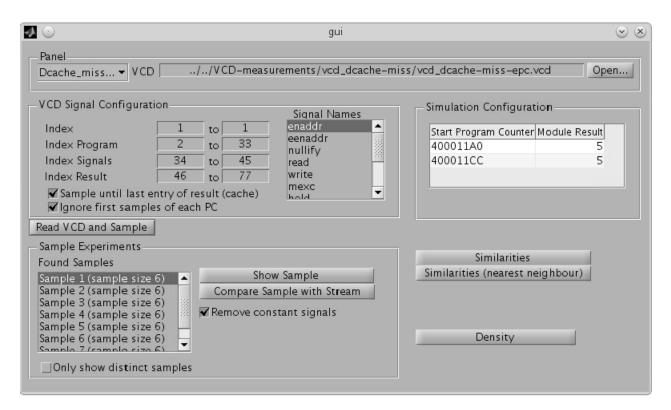

| 5.26 | GUI for the MATLAB script to analyse the VCD data.                                 | 54              |

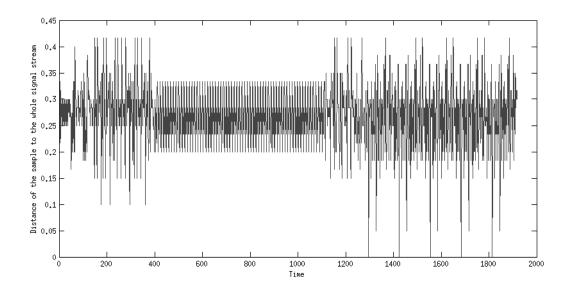

| 5.27 | The distance of sample 1 of a recorded read procedure of the data cache                            | 56 |

|------|----------------------------------------------------------------------------------------------------|----|

| 5.28 | The density matrices for the measurement of a read procedure                                       | 57 |

| 5.29 | The final densities for the measurement of a read procedure                                        | 57 |

| 5.30 | Data path of the automatic module analysis technique                                               | 59 |

| 6.1  | Trigger adjustment of the fault injection unit.                                                    | 62 |

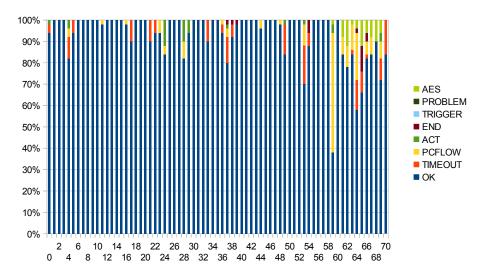

| 6.2  | Statistic of the fault classifications for randomly injected stuck-at-zero faults                  | 67 |

| 6.3  | Statistic of the fault classifications for randomly injected stuck-at-one faults                   | 68 |

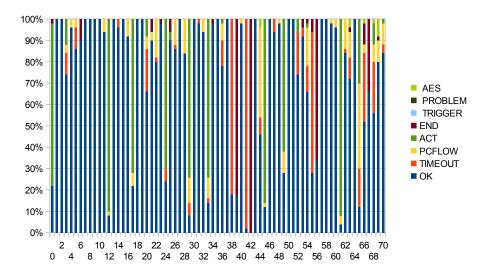

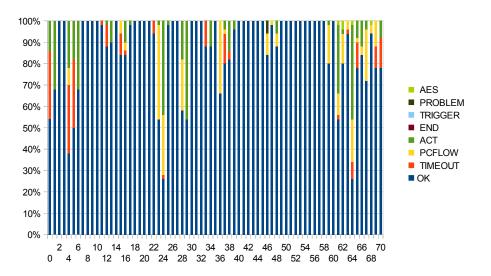

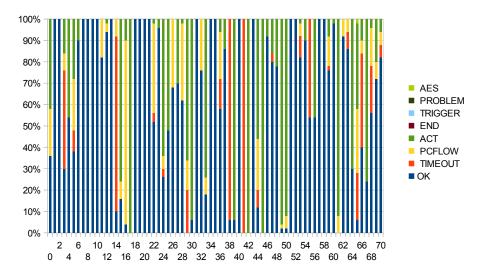

| 6.4  | Statistic of the fault classifications for stuck-at-zero fault injections based on activity timing | 69 |

| 6.5  | Statistic of the fault classifications for stuck-at-one fault injections based on ac-              |    |

|      | tivity timing                                                                                      | 69 |

# List of Tables

| 2.1 | Saboteur operation types [18]                                       | 18 |

|-----|---------------------------------------------------------------------|----|

| 4.1 | Example of an activity record for 4 different resources             | 29 |

| 5.1 | A single sample of read procedure with cache-miss of the data cache | 55 |

|     | The signals that were equipped with saboteurs                       |    |

|     | Results of the experiments with transient fault injections.         |    |

| 0.0 | Results of the experiments with transfert fault injections          | 10 |

# 1 Introduction

# 1.1 Context

Today most semiconductor-based technology has reached a very high level of integration. The density of logic gates within a chip is increasing with every decade. As integrated circuits (IC) get smaller, single gates get more prone to all kind of faults. The reason can be found in the reduced voltage and the reduced internal capacities that increase the sensitivity to noise and radiations [22]. But the small gate level size also allows the integration of further functionality. Today, many integrated circuits are system on chips (SoC). They combine various components of a computer on a single die. Multi-core processors, memories, interfaces, signal processing functions and peripherals on a single chip raise the complexity of the design. And with the increasing complexity the fault threat increases as well.

Faults can be either of natural source or originate from attacks. Especially attack faults are a challenging field in research, since attackers have gotten very creative in bypassing implemented fault recovery mechanisms. Faults that arise from natural sources are mostly dependent on the environment close to the circuit, like electro-magnetic waves or simply alpha-particles or neurons [29], [12].

When a SoC device is designed and implemented, engineers have to make sure that the future device is immune to natural faults and secure to fault attacks. Implemented fault recovery mechanisms have to be tested carefully. Developers also must understand how the device reacts in occurrence of a fault. The more complex hardware devices get, the harder the dependence of different modules can be understood. A fault that may occur in one module may propagate through several other modules until it raises an error or hopefully recovers.

Fault Injection is one possibility to understand how the system reacts under the occurrence of faults. They are induced on purpose by the developers and the effect of the fault is observed in a controlled environment. Fault injection can be done in many different ways. The device can be injected with a fault in its physical form, where it already exists as a prototype. A different method is the simulation of the hardware description. Hardware simulation is used as a functional verification method in early design stages. It is a simple and flexible approach to debug the design. Beside the functional verification, the simulated injection of faults can lead to the detection of design flaws and test specific fault detection and recovery mechanisms. A further important method is the fault emulation. Emulation is the mapping of a hardware design - the system-under-test - into a specific hardware platform [6]. The platform imitates the behavior of the hardware design. That means that the platform can act like the real physical device itself. This is done with the usage of an FPGA (Field Programmable Gate Array).

Those three methods differentiate heavily in their advantages and disadvantages [34]. Using the simulation and emulation method, the big advantage is that a prototype does not have to exist yet. A simulation is very flexible. All signals can be observed and manipulated very easily. It is easy to debug the hardware functionality. However, simulation approaches usually need excessive CPU times, especially for complex systems. This depends mostly on the level of abstraction. While the functional simulation can be fast, a gate-level simulation can be very time consuming for fault injection purposes. The emulation approach overcomes this issue since the hardware is imitated in real-time. However, FPGAs do lack of limited debugging capabilities. Compared to the simulation, the current states of hardware components and their signals can not be observed and manipulated as easy as in simulation approaches. Further techniques have to applied to use fault injection in emulated environments.

The security and dependability verification of system-on-chips is expensive and very time consuming, despite the used techniques and approaches. For example, complex SoC designs have many possible targets for fault injections. It is the responsibility of the verification engineer to select security critical modules and signals for testing. The fault space that covers timing, locality and type of possible faults is usually very big and not even remotely comprehensible. A primary approach is the injection of faults on specific signals and timings. A further approach is to automatically inject faults on a random selection. Both approaches are very exhausting if fault coverage must be achieved. In the first case, the test developer has to decide manually where and when an injection has to take place. In the second a huge amount of faults is going to be induced and their effect has to be analyzed. So research and industry is constantly investigating new methods for security and dependability evaluations.

## 1.2 Thesis approach

This thesis studies a novel optimization method of a fault emulation technique upon FPGAs. The idea is to raise the number of fault injections that have a higher probability of bringing the system into an unintended behavior. Such faults are denoted as activated faults. On the opposite, the number of fault injection campaigns which do not have any effect to the system should be reduced to a minimum.

The primary approach is to observe and record the activity of different independent modules of a complex System-on-chip design during a normal execution. Such an execution is called a golden run. In subsequent identical executions, faults can be injected automatically into the system using the recorded activity information. Since this information contains the location and timing of active hardware modules, the number of useless faults can be avoided in the first place.

To observe the activity of the components, they are extended with specifically adjusted sensors. The sensors observe the input and output signals, as well as selected registers of those modules. To build up the sensors, every module has to be studied in detail. Two different approaches to create the sensor logic are carried out. The first is the manual inquiry of the module, by examining the hardware description. The second is done on an automatic basis. The complete hardware design is simulated once, whereby the module in question is activated several times. The simulation results are then analyzed by a MATLAB script, whereby the activation is filtered out of the complete signal traces. Similar signal progressions are detected and exhibit the important signals for an activity of the module. The sensor can then be build upon the obtained simulation results.

It is important that the sensors differentiate between an intentional and an unintentional activation. An intentional activation happens, if the output generated by the module is further used. An unintentional activation would be the activation of a module whose input signals are changing, but the output is never considered to be used further on. So, the sensors have to contain some digital logic to decide autonomously when an activation is taking place.

Further, those sensors provide the runtime information to a central component, the activity measurement unit. It consists of a controller, memory and a communication interface. The controller is responsible for the selection of the sensors, the activity recording period and the storage. The communication interface is needed for the configuration and to read the recorded activity information after the golden run. An external controller can download the activity information and decide which strategy for a fault injection shall be used. The golden run, the fault injection experiments and the evaluation of the experiment is done automatically. The fault injection framework from Grinschgl et al. [18] builds the basis for the experimentation.

The approach of detecting the activity is closely related to power emulation approaches. Power emulation is a technique to estimate the current power profile of a system-under-test (SUT). The SUT is loaded into an FPGA and the current needed power can be calculated with power emulation techniques. Of course, simulation approaches or physical measurements can be far more accurate. But emulation techniques were developed to overcome the same issues that exist in this field as in the domain of fault injections. Therefore, this technique can be used as basis for a novel fault emulation method.

# 1.3 Thesis organization

Next, Chapter 2 introduces the reader into the fundamentals of faults and fault injections. Chapter 3 describes different approaches in science and research to optimize fault injections. It also shows a technique to estimate the power consumption of digital design. Those approaches and techniques inspired the design and implementation of a novel fault injection optimization method. The concept of this new method is presented in Chapter 4. The implementation upon this concept is shown further in Chapter 5. Fault injection experiments are presented in Chapter 6. In Chapter 7, the conclusion to the implementation and the experiments is given. A comparison to the related work of other research is drawn. Also a hint for further work is given. The appendix in Chapter 8 shows the configuration of the software and gives instructions about the usage of the implemented work.

# 2 Fundamentals

In this chapter the fundamentals of faults and fault injections are described. The different types of faults and their corresponding terminology are explained. Their intentional insertion into a system is called fault injection. In research fault injection is a technique to understand the behaviour of the system under the occurrence of faults.

# 2.1 Faults

### 2.1.1 Terminology

When it comes to faults, it is important that the terms are well defined. Avižienis et al. [7] differentiated in his work about the fundamental concepts of dependability between **fault**, **fault tolerance**, **failure** and **error**.

A failure is depicted as an event that occurs when a system fails to deliver the correct service. It is said that the system fails because it does not comply with its specification anymore. An error is the specific part of the systems state that may raise a failure. In fact when an error influences the service of the device, a failure occurs. A fault, which is considered as the cause of an error can be active or dormant [7]. An active fault produces an error, while a dormant fault doesn't. The capability of a system to provide a correct result (the expected service) in the presence of faults is called fault tolerance.

### 2.1.2 Types of faults

Faults that usually occur within integrated circuits can be differentiated between permanent and transitional faults [34].

- Permanent faults (hard errors) are faults that originate from destructed digital parts. For example, a gate that is not switching anymore is either providing a constant or an undefined signal. Through the influenced structure of the chip, the fault remains even after a reset. So the behavior of the system may not be consistent anymore. An example for such a permanent fault is a single event latch-up (SEL), which is a self-sustained short circuit [8]. It can be caused by short time overvoltage or electrostatic discharge. This may destroy several parts of a component, due to high currents flows through the short circuit.

- Transient faults are faults that only occur during a time period. The fault can either disappear after a few clock cycles, for example because the signal state changes, or it will be removed with a reset. However, the typical classification of this type is that the system can return to its normal, consistent behavior after the fault vanishes. Such a soft error often appears as a single event upset (SEU). This is a bit flip in a register or memory cell. A multiple event upset (MEU) is the occurrence of multiple SEUs at the same time [8]. This fault type is especially important for buses on SoCs.

Transient faults can arise due to cosmic particles or cosmic rays that interact with electronics, especially in satellite or aircraft electronics at high altitudes. But due to the increasing density of logic gates, the lower supply voltage and the higher clock frequency the number of randomly injected faults is also raising at sea level [27].

### 2.1.3 The source of faults

The correct function of SoCs depends on many parameters. Bar-El et al. [8] gives an wellarranged overview of causes that provoke faults like SEUs. In the first place, the system developers have to make sure that the device is not exposed to this kind of faults:

- Fluctuation in the supply voltage are well studied and understood. As an overvoltage may destroy the circuits, a too low voltage may provoke the CMOS gates to fail.

- Clock cycle variations may result in asynchronous signal and data propagation.

- The temperature of the device and its environment can have an heavy impact on the function of the device. The manufacturers provide temperature thresholds. As long as the device operates within these thresholds the function of the circuits is guaranteed.

- Electromagnetic waves or radiation can cause spurious currents within the system and provoke a bit flip [34].

Additionally to the previous fault sources, an attacker may use further techniques and possibilities to insert faults to devices:

- With a laser a high amount of photons can be directed onto the circuitry. The photoelectric effect drives a current that itself can drive a gate and inject a SEU.

- X-rays and ion-beams have the same influence, but it is not even required to remove the body of the chip.

# 2.2 Fault injection

Fault injection is the intended temporal insertion of faults into a hardware design. Carreira et al. [11] refers to three major benefits of using fault injections:

- To understand the effects of real faults

- To gain feedback for a system correction

- To forecast the expected behaviour of the system

To describe it simply, the motivation is to see how the system behaves when a fault occurs on circuit level. It must be observed if the built-in fault recovery mechanism detects and repairs the fault, or if the system reaches an insecure state.

As mentioned previously in the introduction, there are 3 main approaches to introduce faults deliberately to a system [12]:

- Physical or hardware implemented fault injection

- Fault injections using hardware simulation

- Fault injections using hardware emulation

In research all approaches are examined, but while the physical approach exists since a long time, the emulation approach can be considered as a fairly new domain of fault injections. All approaches do have different advantages and disadvantages and they are needed in different domains, to test a system in terms of security and dependability.

### 2.2.1 Physical fault injection

Physical fault injection, also called hardware implemented fault injection is done by stressing the hardware [30]. The device itself in its physical representation is attacked. Which means, a prototype is needed for fault injections. Flaws and bugs that are found at this time result in high redevelopment costs. For most of the attacks specific knowledge about the device is needed and for a test developer it is hard to cover the large area of possible internal faults. However, a physical access is very easy for an attacker to a big range of systems, like smart-cards, mobilephones or multimedia devices. The injection of transient faults by manipulating the supply voltage is very common [29]. Faults can further be injected using electromagnetic interference or pin-level injection. Karlsson et al. [21] states that especially the pin-level injection is the most used technique for physical fault injection. There, the pin of a circuit is directly connected to ground or a voltage source. So research in this field is very relevant in terms of security.

### 2.2.2 Simulated fault injection

A simulation of the hardware description language is the first choice when it comes to test a design. Simulators are very effective, especially in early design stages when a prototype is still not available yet [12]. For fault injections, simulators offer the most flexible approach since all signals can be supervised and manipulated easily. Some simulators like ModelSim [25] allow the alteration of selected signals to different values. The HDL code does not have to be modified. Rohani et al. [30] divides all simulated fault injection techniques into two groups:

- Those which can use simulator commands, like the previous example.

- Those which need code modifications. The HDL code is extended with mutants and saboteurs. They are described in the next section.

The advantage of simulators is that the fault propagation can be analysed easily. This means that the impact that a fault causes, can be traced until it raises an error or it gets detected and resolved. Depending on the simulation environment faults can be simulated at all levels, e.g. at gate-level (GL), at register-transfer-level (RTL) or at system-level (SL).

A big drawback is that a simulation needs a big amount of CPU time on complex systems, especially for low level simulations. When it comes to simulate a big amount of fault injections, e.g. at the register-transfer-level, the simulation approach reaches its limits very fast. However, research is trying to reduce the needed CPU time by using checkpoints or fault collapsing [30]. Fault list collapsing is an optimization method, in which many similar faults with the same outcome are replaced with a single fault injection. Using checkpoints means that the simulator saves the state of the SUT right before a fault injection, and restarts the simulation exactly from that checkpoint.

### 2.2.3 Emulated fault injection

Hardware emulation allows the execution of hardware circuits during the development phase. The hardware description is synthesized and loaded into an FPGA. The execution, especially for very complex systems, is much faster than a simulation since it executes in real-time. But it has the disadvantage of a reduced observability and controllability. It is harder to observe and manipulate certain signals directly. Grinschgl et al. [19] states that the advantage that comes with the speed-up compensates the disadvantages. A huge amount of attacks can not be handled with simulations, whereby this can be done with the emulation on FPGAs. There are three main approaches to use fault injection on emulated platforms:

- Partial reconfiguration

- Mutant based fault injection

- Saboteurs

While this thesis concentrate on the usage of saboteurs as the fault injection approach of choice, the others constitute possible alternatives. They can be used similarly with the implemented idea.

**Partial reconfiguration** allows the change of certain parts of the hardware circuits that are emulated on an FPGA during runtime. While a specific part is altered, the other parts of the system can still operate. This technique has to be supported by the development FPGA and is therefore limited to the chosen platform [18]. There are several methods available to inject faults using partial reconfiguration. One possibility is to modify the bitstream that is loaded to the FPGA. Another approach is, to change the configuration memory of the FPGA [20]. Currently, partial reconfiguration is slower than modern approaches with saboteurs. The reconfiguration processes suffers from long delays, but research deals with the problem of accelerating partial reconfiguration [20].

**Mutants** are modules in the system that got altered by the test developer. The general idea is that they behave like the original module during normal operation. But when a fault shall be injected for validation then the mutant behaves faulty. For example, it provides an output that is wrong in one bit. This technique is similar to mutation testing in software engineering, where code sequences are altered, e.g. the exchange of an addition operation with a subtraction. This technique has the huge disadvantage that the test developer has to bring a big effort to understand the hardware description. This means that the automatic generation of mutants is also very complex task [30].

**Saboteurs** are modules that are placed on signals lines. During normal operation of the systemunder-test saboteurs are fully transparent. When they are activated, they influence the signal and inject a fault. Table 2.1 gives an overview of possible modes of how a saboteur can disturb a signal.

The consequence of using saboteurs is that the hardware description language has to be modified for the security testing. After changing the hardware description of a system, the synthetisation has to undergo the full process again. And this is a very time consuming process. So it is advisable, to place saboteurs on all security and dependability relevant signals. The saboteurs can then be activated individually through a controller from the outside. So multiple synthetisation processes are avoided.

Complex systems can have a big spectrum of security and dependability relevant signals. This can be a bit-flip on a single signal, but also multiple bit-flips on a bus. For security concerns, multiple fault injections on different signals at the same time have to be considered as well.

| Saboteur mode                               | Fault type | Description                              |  |  |

|---------------------------------------------|------------|------------------------------------------|--|--|

| Stuck-at-zero                               | Permanent  | Signal value is set to 0                 |  |  |

| Stuck-at-one Permanent S                    |            | Signal value is set to 1                 |  |  |

| Indetermination Permanent                   |            | Undefined signal state until reload      |  |  |

| Negation of inputPermanentBit-flipTransient |            | No output propagation until reload       |  |  |

|                                             |            | Undefined signal state until reload      |  |  |

|                                             |            | Output inverts input for one cycle (SEU) |  |  |

|                                             |            | Input to output propagation delay        |  |  |

Table 2.1: Saboteur operation types [18].

So the placement of a high number of saboteurs is an exhaustive and time consuming process, when done manually. In the work of Grinschgl et al. [17] a tool is introduced that automatically places a high amount of saboteurs directly into VHDL code [1]. So a maximum test coverage can be obtained by manipulating all security relevant signals. The placement of saboteurs to every signal of a critical module in the design is suggested in this work.

If the amount of saboteurs is very high, the emulation effort raises as well. To keep the cost of the past-injection analysis low, research has to focus several optimization methods. They are discussed in the next chapter.

While saboteurs can imitate nearly all kind of functional faults due to their modes, they have also the disadvantage that they cannot model faults below the gate level [13]. Mutants can do that, because there the fault response is generated internally. So Coppens et al. [13] states that any fault model is possible with mutants.

# 3 Related work

In this chapter related scientific works are presented. The first part of this chapter, Section 3.1 covers research papers that deal with different approaches to optimized fault injection campaigns. The presented papers show optimal fault injection timings and locations. The paper presented in Section 3.1.4 shows how the impact of emulated fault injections can be supervised.

In Section 3.2 two power emulation concepts are outlined. Power emulation is a concept of estimating the power consumption of digital circuits during the design phase.

## 3.1 Optimize fault injection campaigns

As many systems are very complex, so are the fault injection validation techniques. As mentioned previously, fault injections in simulations are usually very time consuming. This is why security and dependability verification methods for complex systems are also done with emulation platforms based upon FPGAs. Nevertheless, the analysis of the effect of a single fault injection can still be an exhausting procedure that has to be done by the test developer. In this chapter several research methods are shown. They outline the task of reducing the number of fault injections. The target is to reduce the overhead that comes with the impact analysis of a fault injection.

### 3.1.1 Using pre-injection analysis

Tsai et al. [31] state in their work

Faults should be injected in locations with a high probability of being activated. Conversely, faults must not be placed where activation is very unlikely.

The motivation to this statement can be found in the fact that a fault that is never activated it simply useless. It should be avoided since it only costs injection time. The injection of faults that are never activated is very likely if the injection targets are chosen randomly. So a smart election of possible targets has to be done.

Therefore, Tsai et al. [31] introduces two basic methodologies to increase the efficiency of fault injections on a micro controller:

- Stress based injections: The run-time workload activity at system level is monitored and recorded. This means that the usage of different parts of the system is supervised and fault injections are done based upon these values. For example, if a threshold of the usage per second is exceeded a fault is injected in exactly this part. This is based upon the proven fact that stressed parts of the system are more prone to faults than non-stressed parts are [31].

- Path based injections: This is a method that uses the analysis of the program flow and its resources at the application level. Based on this knowledge fault injection targets can be selected more specifically. This includes also the dependence of the program input, as

stated by Tsai et al. [31]. But a more generalized term would be that the path based injection is heavily dependent on the used environmental constraints, like input and the beginning state. To guarantee full coverage, the tester has to make sure that every possible path is taken somehow.

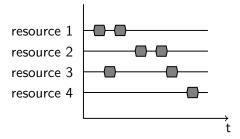

As can be seen, both methods build up on the analysis of resource activities. Possible targets are chosen upon this information. Figure 3.1 gives an overview of how this information can be depicted. The resources usage is shown in a sequential manner after the analysis.

Figure 3.1: Pre-injection analysis on resource usage for path based injections, as described by Tsai et al. [31].

In the experiments of Tsai et al. [31], they analysed the workload by the number of accesses to memory and the time the simulated CPU is active. For path based injection they analysed the assembly language of the executed code on the simulated CPU. They injected faults directly with the simulation environment, e.g. by changes to the system state, like the contents of the registers. Using random injection they had only 1 fault activation on 4 injected faults. But they received a fault injection rate of 100% with their path-based injection method, as they used the knowledge which register is going to be used exactly. Of course, fault activation means that the fault did only propagate through the system, either to an error or to the activation of a fault recovery mechanism. The stress based injection method was very dependent on the used target. While fault injections on the memory had little impact it was very successful at the input/output (I/O) interface to the file system.

### 3.1.2 Optimize the fault space

The fault space is the quantity of all kind of faults at every possible time at every possible location. Compared to the previous techniques not only the injection targets are taken into account, also their function and timing. Barbosa et al. [9] provided the following motivation as basis for another optimization of fault injection campaigns:

# Faults should only be placed in a resource immediately before the resource is read by an instruction.

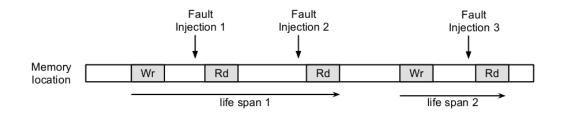

This statement is very logical, since it makes no sense to inject faults into registers or memory locations that are either not used or overwritten later. By parsing the assembly code of the program that is executed on the microcontroller, the activated resources and their functional usage were detected. Figure 3.2 shows an example of memory accesses and possible fault injection timings.

Figure 3.2: Possible fault injections on a memory location following the principle of Barbosa et al. [9].

The assembly code was obtained by disassembling the high-level language code. During the golden run, the program counters and the values of the general purpose registers where traced. So knowledge of used resources including the time, when they are going to be used, was gained. For the fault injections, they targeted the processor registers and some data memory locations of the executed program with single bit flips. Using this technique the fault effectiveness raised one order of magnitude, from approximately 4% to more than 40% for fault injections in the registers and from about 2% to 20% in the memory.

### 3.1.3 Detect dependencies

Munkby et al. [26] developed a method to detect certain patterns of fault injections. They have created a life span analysis of the operands that are used during execution. They are widening the idea of Barbosa et al. [9] to adapt it to a controller, which is constantly calculating an output out of an input. So as a first optimization of their approach, they target faults only during the lifetime of an operand. For example, the life span of a data variable begins with its initialization and ends with the last read instruction. Further, they created a program dependence graph out of the assembly code. The nodes of the graph represent instructions and the edges the control or data dependencies. This graph visualizes if an instruction uses a variable that is defined by another instruction as a data dependency. Further, a control dependency exists if an instruction is guarded by another, like an if-then-else construct would do.

By visualizing the detected and the undetected injected faults in the graph, they were able to detect similar patterns. Those patterns can be used, to keep the number of needed faults smaller by predicting the outcome of other possible injections. Further the patterns can be used to adapt the fault detection mechanisms in their hardware, to harden the fault tolerance of the device.

#### 3.1.4 Optimizing emulated fault injections

All previously described methods use fault injections on simulated circuits. Simulation approaches have the advantage that the outcome of the fault injection is easier to analyse since the propagation of the fault can be easier followed. A simulation can be compared with white box testing, where internal states and signals can be observed easily. Because the emulated fault injection does not provide exactly this advantage, the impact of an injected fault can not be observed that easily. Research is done to overcome this issue. Grinschgl et al. [19] implemented a module that checks the outcome of an emulated fault injection automatically based on a golden run. Such a golden run, also called reference run, is an execution of the system-under-test without interference of any faults. By checking memory accesses, output signals and the program counter, dangerous alterations of the system-state can be detected at runtime. The fast differ-

entiation between flow, memory and input/output manipulation allows the easier classification of critical attacks.

### 3.2 Power emulation

There are several different approaches to gain information about the energy consumption of a SoC. Embedded devices need to make sure that the consumption does not exceed the power that can be provided. Especially when the device is powered by battery or by magnetic radio frequency (RF) fields. The requirement for developers is the same as in the security and dependability domain. The information about the future power consumption of a new developed system must be available as soon as possible. Emulation approaches, based upon an FPGA, were developed to avoid the disadvantages of simulation or physical methods. A Physical measurement is the most accurate, but also the most expensive method. When the designed circuitry is already available in its physical form, any changes are probably only going to implemented in the next device generation. Gate-level simulations are very accurate, but unfortunately very slow. This may be a big problem if the circuitry is going to be a very complex one, like a system-on-chip usually is. And especially for software designer the energy consumption of a SoC is interesting. A big potential for energy savings can be found in the application layer [16]. But low-level hardware simulations are often not available to the SoC software designer. They usually use system-level approaches.

### 3.2.1 Power emulation using access counters

Bhattacharjee et al. [10] developed a power emulation method that is based upon component accesses. They modified the VHDL code of a LEON3 processor to extend the design with their functionality. When selected components start one of their functions, called an event, then a pulse is triggered to a corresponding counter. For example, if the data cache is accessed and produces a cache-hit, then the counter for a cache-hit is incremented. Using this counter value the consumed power for a component can be computed using the following formula

$$P = P_{idle} + \sum_{i} (E_i n_i f) / cycles$$

$E_i$  represents the energy that is needed for the event *i*, e.g. a memory access or a cachehit.  $n_i$  is the corresponding count that states how often this event happened. The energy per event was gained by gate-level simulations with micro-benchmarks. A functional simulation with *ModelSim* generated a "Value Change Dump" (VCD) file that contains all signal changes during runtime. This file was given as input to *Synopsys PrimeTime PX* which estimates the power consumption on a gate-level simulation basis.

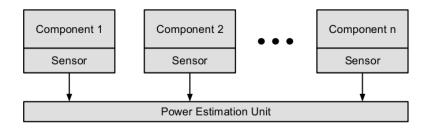

### 3.2.2 Power emulation using sensors on components

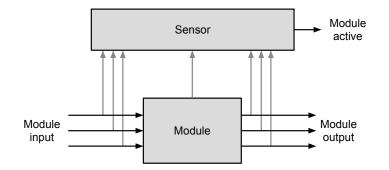

Genser et al. [16] developed an emulation approach to estimate the power consumption of a SoC. The design of the SoC was augmented with an power estimation unit. Selected components were equipped with sensors, containing a power model that is specific for that model. Register values and input and output signals of an component were routed to the sensor. Figure 3.3 pictures this concept.

Figure 3.3: Power emulation concept of Genser et al. [16].

Each sensor has a power model stored. It covers enough states so that an accurate overall power estimation can be achieved. The power model was pre-calculated with the value of the signal and register values using a linear regression method.

$$P = \sum_{i} c_i x_i + \epsilon$$

The values  $x_i$  are the current states that consist of the *n* routed signals from the component. The corresponding coefficients  $c_i$  and the deviation  $\epsilon$  are obtained through a preceding power measurement process. This was done by executing benchmarks on the SoC within a gate-level simulation. The obtained power model calculates the current consumed power y based on the current state.

# 4 Concept

## 4.1 General

Goal of this thesis is an optimization of verification processes using emulated fault injections.

The digital design of choice for this thesis is a general purpose processor. Simply because a processor consists usually of big spectrum of different modules. A stable and verified behavior is crucial for its function and a single fault in one module can have a big influence in the overall function. Especially in harsh environments faults can propagate through the entire system, provoking inconceivable system failures. Another central point is the fact that system-on-chip designs have become an ubiquitous part in modern technology. Future trends to smart devices lead to the development of powerful chips containing a big spectrum of different components, interfaces and peripherals. A general purpose processor like the LEON3 from Aeroflex Gaisler [2] is freely available under the GNU GPL open source license. It is designed with VHDL [1] and can be used and modified freely in research and education. The characteristics of this processor is described later in Section 4.2.

The design of the LEON3 processor is extended with functionality that records the activity of selected modules and components. The extension consists of sensors that are implanted into the modules. They detect when a module is getting active and inactive. These sensors sends this information to a measurement unit that records this data, when a given observation period is set. With the records stored in a memory an appropriate fault injection strategy can be chosen and applied. Chapter 5 depicts the implementation of this part.

The fault injection system, called Modular Fault Injector (MFI) is taken from [18]. It comes with a fault injection controller that enables the storage of different fault patterns and the activation of an arbitrary amount of saboteurs. In Section 4.3 the MFI is presented. The hardware description of the modified LEON3 processor is further extended with the modular fault injector and some saboteurs. The saboteurs are placed on all relevant control signals of the modules and components whose activity is supervised.

The modified design of the LEON3 processor is synthesized and loaded upon a development board with Virtex 5 FPGA. The used FPGA is presented in Section 4.4.

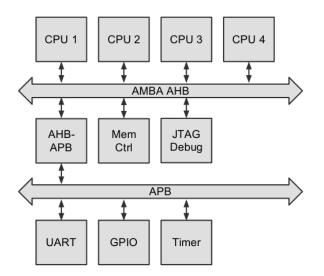

## 4.2 The LEON3 processor

The LEON3 is a 32-bit multi-core processor that implements the SPARCv8 architecture. It was developed by the European Space Agency (ESA) and is now maintained by Gaisler Research. The processor design is a synthesizable VHDL model that is configurable through VHDL generics. The amount of CPU cores can vary between 1 and 4 and nearly all components can be removed, added or adapted by the developer. Components and peripherals are connected over an AMBA AHB and APB bus. Figure 4.1 shows the principle architecture with the main components of the LEON3 processor.

Figure 4.1: Main components of the LEON3 processor [4].

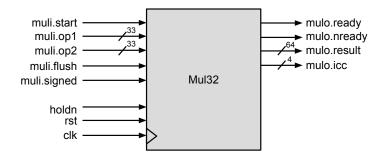

A single CPU core consists of a 7-stage integer unit and a 3-port register file. In the default configuration it includes the parts shown in the next listing. Each of those can be removed to minimize the number of gates:

- A hardware multiplier and a hardware divider module. If they are available, sdiv and smul instructions can be used in the assembly code. Otherwise the compiler has to implement the calculation within the binary code. With these modules multiplications and divisions can be finished in a few clock cycles.

- A data cache and an instruction cache enables the accelerated access to previously cached data and instructions.

- A floating point unit (FPU) can accelerate operations on floating point numbers.

- A memory management unit (MMU) enables the usage of virtual memory addresses.

During this thesis the FPU and the MMU are not used. So they are not synthesized into the design. For commercial purpose there exists also a fault-tolerant processor that is mainly used for space applications. Unfortunately, it is only available with a commercial license.

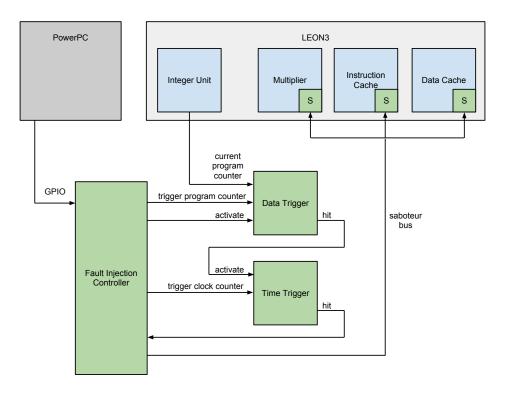

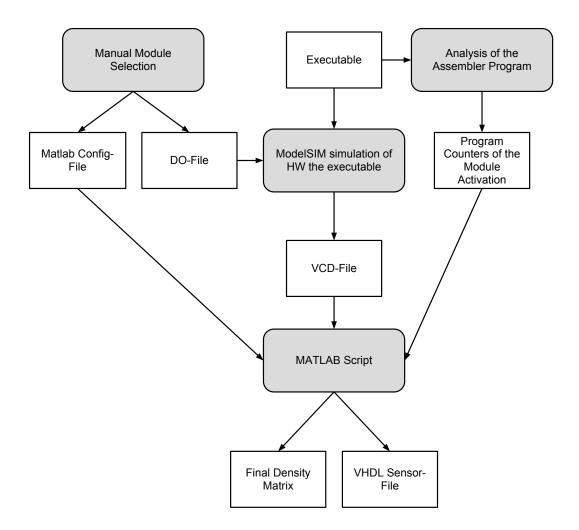

# 4.3 The Modular Fault Injector (MFI)

The modular fault injector that is used for all fault injections during the experimentation phase was taken from Grinschgl et al. [18]. It consists of a fault injection controller, triggers and an arbitrary amount of saboteurs. The saboteurs can be placed on all kind of signals within the LEON3 processor. They support all modes that were described previously in this document in Section 2.2.3 in Table 2.1.

The controller supports multi-bit fault injections. This means that more than a single signal can be disturbed at the runtime of the system-under-test. The disturbance of a complete or even bigger part of a bus can emulate a physical fault attack more precisely than a single event upset could do. In exchange a SEU emulates a fault that can happen on natural basis, like a bit flip induced by alpha particles.

The fault injection controller provides the following functionality:

- It can store multiple different fault patterns within a memory. A single fault pattern consists of the information which saboteurs shall be activated when a trigger is fired.

- It can activate and deactivate triggers. The triggers are responsible for activating the saboteurs at a given time or at a given register value. Time is specified as the number of clock cycles that passes since the activation of the time trigger.

- A general purpose input/output (GPIO) interface is provided as the communication interface for the configuration.

- A saboteur interface that can control an arbitrary amount of saboteurs.

- Saboteurs can be activated for one clock cycle, more than one clock cycles or permanently.

In this configuration the GPIO interface is used to connect the fault injection controller to the PowerPC processor of the development board. The PowerPC can be programmed and controlled by the developer.

There are two different triggers available within the MFI. But an arbitrary amount of triggers can be used:

- A multi-bit trigger that compares a register value with a preset value. If they are the same the trigger sends a hit signal. It is used to supervise the program counter of the LEON3 processor. It triggers the saboteurs when a specific instruction is executed.

- A counter trigger that sends a hit signal to the saboteurs when a previous set number of clock cycles passed by.

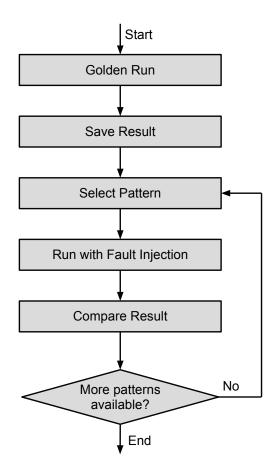

The fault injection flow will be done based on a golden run, as proposed in the work of Grinschgl et al. [18]. Figure 4.2 pictures the basic flow of the fault injection strategy. A golden run is a complete run of the system-under-test without any influence of the fault injection framework. But the golden run is supervised by the framework and the result, which is the output and the program flow, is stored. Next, a fault pattern is selected and activated. After a reset of the system-under-test a run with a fault injection is started and the result of this run can then be compared with the golden run. Since such an interfered run can directly lead into an infinite loop, a timeout is needed. After the check of the result the next fault injection pattern is selected. This is done until all patterns are probed.

Figure 4.2: Golden Run flow as proposed by [18].

## 4.4 The FPGA and development environment

Maxfield [24] describes an FPGA (Field Programable Gate Array) as an IC (Integrated Circuit) that consists of configurable logic blocks and configurable interconnections between those logic blocks. The configuration is the programing of the FPGA. It can be loaded with any synthesizable digital hardware description. Usually, FPGAs are used when the functionality of a digital circuit may still be changed later on. Because modern FPGAs can be reprogramed easily. But also because an FPGA is much cheaper than an ASIC (application specific integrated circuit). An ASIC is an IC whose implementation is "frozen in silicon" [24]. And the manufacturing of ASICs is far too expensive for little amounts of units. So FPGAs provide a cheap possibility of using system-on-chip designs in special fields.

A very important approach is to test and verify complex integrated circuits during the development. The simulation of big designs is not only a very CPU-time consuming process. A simulation is also an insular environment. Using FPGAs, the design can be used in combination with their future components and peripherals and the function of the design can be verified very soon during the development phase. Lately, FPGAs are also becoming very cheap and newer applications and usages arise in the industry. The market of reconfigurable computing was split into the following segments by Maxfield [24]:

- ASIC: FPGAs are used to protype ASICs, but nowadays when the usage of FPGAs are cheaper than a small amount of ASICs they can also fully replace them.

- **Digital signal processing (DSP)**: FPGAs can be used easily for massive parallel algorithms.

- **Physical layer communications**: Based on the possible high frequencies of the emulated circuits, low level and high level protocols can be implemented in a single device.

- Embedded microcontrollers: FPGAs are big enough to contain the functionality of a complete microprocessor and they provide usually enough input and output ports to emulate them.

- **Reconfigurable computing:** Modern FPGAs posses the ability for partial reconfiguration. The hardware description can change during the runtime. This enables many new algorithmic possibilities.

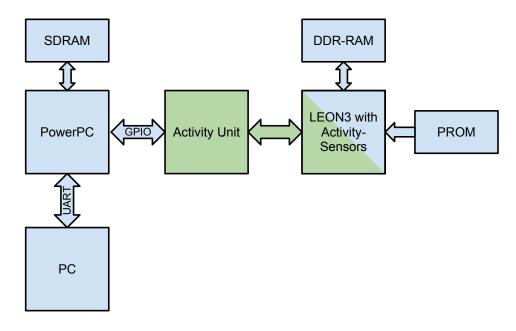

For the experiments and verification of the concept a Xilinx ML 507 emulation platform [32] builds the basis. The board comes with a Virtex5 FPGA (Field Programmable Gate Array) that is big enough to load the full equipped LEON3 and gives some room for adjustments and enhancements. Additional to the FPGA the platform comes with a PowerPC processor that can be used to control and supervise the emulated hardware. Further the development board comes with all general interfaces like DVI, USB, PS/2, Audio, Ethernet, an LCD and much more.

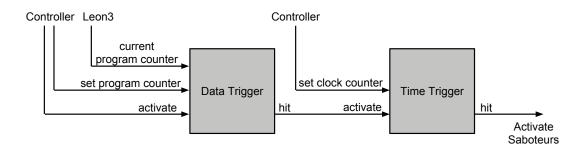

## 4.5 The concept of the activity analysis

Similar to the power emulation techniques presented in Section 3.2 an activity measurement unit shall record the timings where a single module is getting active and when it is getting inactive. Modules of the LEON3 processor are extended with sensors that provide the information, when a resource or a module is activated. A sensor observes the input and output signals, optionally also register values (internal states) of the module to detect if a module is active or not. Figure 4.3 shows that principle.

Figure 4.3: An activity sensor of a module.

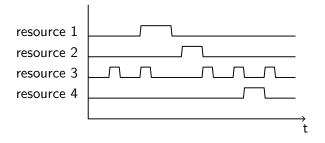

The input and output ports of the module must be chosen carefully after some investigation of every module. The idea is that the sensor only shows activity when the output of the module is also used after the activity. It maximizes the influence of any fault injection during the recorded activity period. This marks also the big difference to the concept of power emulation. It has to differentiate between a supposed and a not intended activity. The LEON3 processor does not use any clock gating techniques. This means the components of this processor are actually always active. Power emulation has to respect that the modules are consuming energy even when a module is not directly used. Here the system has to make sure, that any component can take inputs and produce output even when the module is not needed. But if this output is not used during the runtime of the system, it was no intended activity and must therefore be ignored. The sensor must contain combinational logic to make this decision. Figure 4.4 shows the signals that are send from the sensors to the activity measurement unit. When the signal is high, then a module is active on purpose.

Figure 4.4: The module activity send by the activity sensors.

The activity measurement unit stores the activity states for further analysis. The activity is recorded during a golden run. In a successive identical run a fault can be injected at the time and the location that is achieved through the analysis of the activity. Table 4.1 shows the exemplary activity data record as it would belong to the activity stream shown in Figure 4.4.

| time  | res1 | res2 | res3 | res4 |

|-------|------|------|------|------|

| $t_1$ | 0    | 0    | 0    | 0    |

| $t_2$ | 0    | 0    | 1    | 0    |

| $t_3$ | 0    | 0    | 0    | 0    |

| $t_4$ | 1    | 0    | 1    | 0    |

| $t_5$ | 1    | 0    | 0    | 0    |

| $t_6$ | 0    | 0    | 0    | 0    |

| $t_7$ | 0    | 1    | 0    | 0    |

| $t_8$ | 0    | 0    | 0    | 0    |

| $t_9$ | 0    | 0    | 0    | 0    |

Table 4.1: Example of an activity record for 4 different resources.

The entry  $t_9$  in Table 4.1 is the final entry that is stored at the end of the recording period. It can be used to gain the information about the duration.

# 4.6 Fault injection optimization

When it comes to inject a fault into a several parameters have to be chosen at first:

- The type of fault: As shown in Table 2.1 in Section 2.2.3 about the fundamentals of fault injections, there are several different fault types that can be injected with saboteurs. For example, a stuck-at-one fault has a completely different influence to the system than a stuck-at-zero fault.

- The time the fault will be injected: Especially on SoCs the timing of a fault is an essential parameter. Supposed that a signal is only used in 5% of the time, the other 95% may not have any influence. But to provide nearly full testing coverage many faults have to be injected on the chosen signal.

- The time duration the fault lasts: The longer an injected fault lasts, the higher is the probability of getting activated.

- The signal that is influenced: SoC consists of a high amount of signals. The more signals are tested, the longer the overall testing time takes. Either the number of signals that should be tested with fault injection methods is kept low by selecting them manually or a pre-injection method tells which signals may be interesting.

Time, time duration and location of the fault can be selected previously with the knowledge about the activity.

# **5** Implementation

## 5.1 Architecture of the activity measurement unit

This section describes the architecture and implemention of the activity measurement unit. It is implemented in VHDL. The activity measurement unit consists of sensors and those are extensions to the existing hardware modules of the LEON3 processor. Further the implementation of the activity measurement unit and the usage on the FPGA is described.

### 5.1.1 Activity Sensors

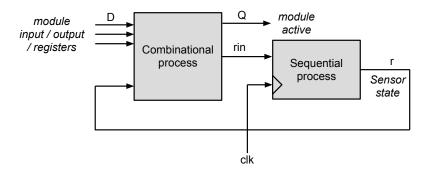

The basic design of a sensor was shown previously in Figure 4.3. The observed input and output signals of the modules are combined using combinational logic. The activity information is stored within the sequential logic of the sensor and driven to the output of the sensor. Figure 5.1 shows this general principle, which is also know as a two process entity.

Figure 5.1: Implementation principle of a sensor.

The design principle conforms not only with the VHDL design of the LEON3 processor, it also provides an easy possibility for further extensions and adaptations [15]. By using this design principle, the risk of reaching the critical path is also reduced.

The combinational process takes the module signals D that are observed as input and creates the register states

$$rin = f_r(D, r)$$

and

$Q = f_q(D, r)$

whereby rin states the non-registered value and r the register value that is held after an raising clock edge. The output Q is driven within the combinational logic out of the register r. The activation signal will always be set 1 clock cycle too late due to the clocked register. The analysis process of the activity data has to make sure that this value is corrected later on.

A descriptive example of an implemented sensor in VHDL is later shown in Listing 5.3 in Chapter 5.4.

### 5.1.2 The activity measurement

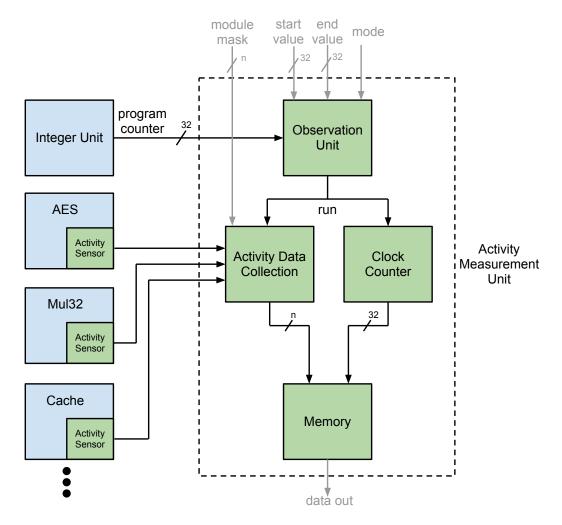

Every interesting and abstractable module of the LEON3 processor is further extended with such a sensor. The activity signals are directed to the **activity measurement unit**. Next, in Figure 5.2 the concept of the measurement unit with the modules and their sensors is shown. The blue parts are from the LEON3 processor, while the green parts illustrate the extensions. The grey paths show the wiring to the outside controller to program the function and the register values.

Figure 5.2: Modules of the LEON3 processor are extended with sensors and connected to the activity measurement unit.

The activity unit consists of the following parts:

• The Observation Unit keeps track of the program counter of the integer unit. When the program counter of the LEON3 processor reaches the predefined start value the observation unit sets an output signal to high until the end value is reached. The runtime between the start value and the end value is called *observation period*. The start value and the end value can either be programmed by the software that runs on the LEON3 over the AMBA AHB bus or from the outside using a GPIO interface. The GPIO interface is used by the PowerPC processor of the development board. Alternatively, instead of an end

value as program counter, the observation period can be stopped after a certain amount of clock cycles. This functionality enables the observation of specific program function and periods.

- The Activity Data Collection Unit collects all signals from the activity sensors. When the observation unit informs the data collection unit about an ongoing observation period, the activity data is directed to the memory. A module mask, which can be set from the outside at runtime (AMBA AHB bus or GPIO interface), can deactivate or activate certain sensors.

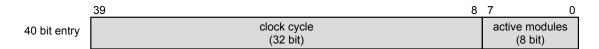

- The Memory Unit receives the data from the activity data collection and stores it for further analysis together with the current clock cycle as time stamp. Furthermore, the memory only stores a new data entry when the vector from the activity data collection changes. This means, that only the changes in the activity stream of the modules are stored, as it was shown previously in Table 4.1.

#### 5.1.3 Usage on the FPGA

The FPGA used for development and experimentation comes with a PowerPC processor to control and observe the hardware that is emulated.

Figure 5.3: The LEON3 processor extended with activity sensors and the activity measurement unit that communicates with the PowerPC of the FPGA.

To configure the start/end value and to read out the memory of the activity measurement unit a GPIO interface connects the PowerPC with the activity unit. The interface enables flexibility and interchangeability. So the hardware design does not depend on the currently used FPGA development board. Any controller can access and implement the GPIO interface. The PowerPC processor itself is connected over an UART interface with the development PC and can be controlled and programmed from there.

When the LEON3 processor is reset, it runs the program that is stored within its PROM memory. The processor executes the instructions and activates and deactivates certain hardware

modules. When an observation period is active, the sensors start to notice the activity. It directs the information to the activity unit where it it will be stored in the memory for further analysis.

After the run the PowerPC can read out the memory, filter and process the data and finally start to decide which fault injection strategy is used. This is described later in Section 5.3.

#### 5.1.4 Configuration Registers

As mentioned previously, the registers of the Activity Measurement Unit can be set

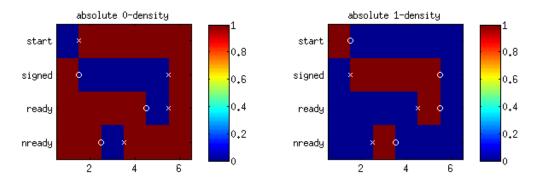

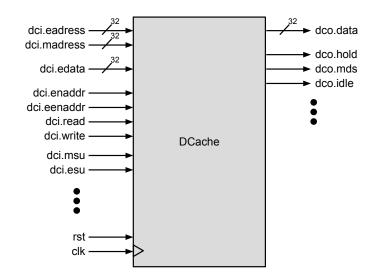

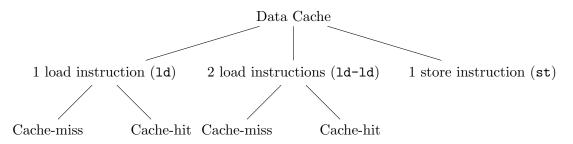

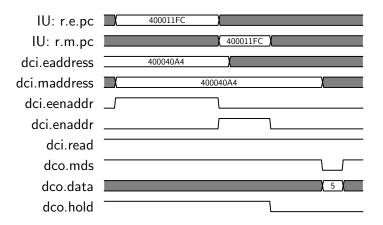

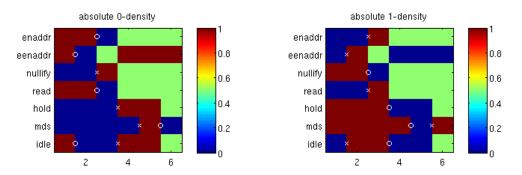

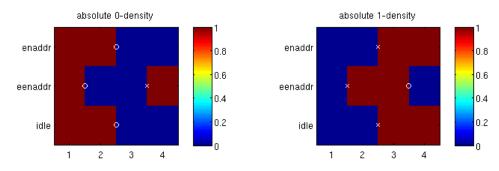

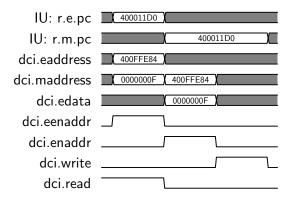

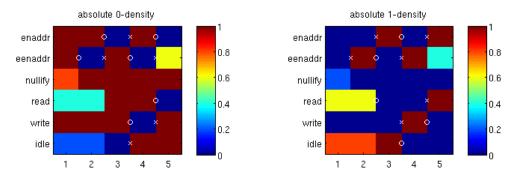

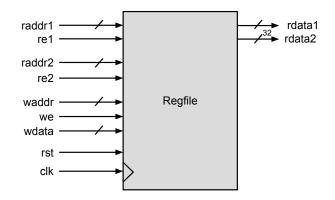

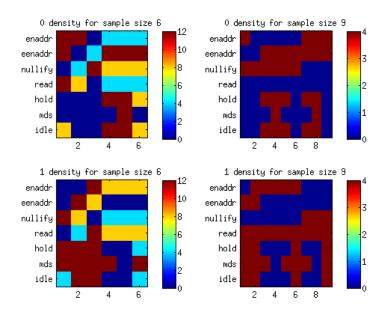

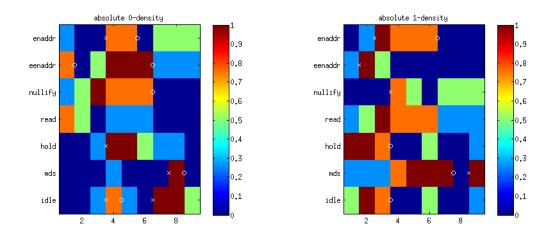

- by the software that runs on the LEON3 processor out of the PROM using the AMBA interface