# Putting Together What Fits Together - GrÆStl

A Combined Hardware Architecture for AES and Grøstl

Markus Pelnar, BSc. m.pelnar@student.tugraz.at pelnarm@student.ethz.ch

Institute for Applied Information Processing and Communications (IAIK) Graz University of Technology Inffeldgasse 16a 8010 Graz, Austria

Integrated Systems Laboratory (IIS) Swiss Federal Institute of Technology Gloriastrasse 35 CH-8092 Zurich, Switzerland

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

#### Master Thesis

Supervisors: Dipl. Ing. Michael Mühlberghuber, ETH Zürich Dipl. Ing. Beat Muheim, ETH Zürich Dr. Michael Hutter, TU Graz Assessor: Dr. Karl-Christian Posch, TU Graz Dr. Norbert Felber, ETH Zürich

May, 2012

Deutsche Fassung: Beschluss der Curricula-Kommission für Bachelor-, Master- und Diplomstudien vom 10.11.2008 Genehmigung des Senates am 1.12.2008

# EIDESSTATTLICHE ERKLÄRUNG

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommene Stellen als solche kenntlich gemacht habe.

Graz, am .....

.....(Unterschrift)

Englische Fassung:

# STATUTORY DECLARATION

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

date

(signature)

# Acknowledgements

First of all I would like to thank my supervisors Michael Hutter from Graz University of Technology (TUG), Michael Mühlberghuber and Beat Muheim from Swiss Federal Institute of Technology (SFIT) Zurich and all members of the Microelectronics Design Center from the Department of Information Technology and Electrical Engineering (D-ITET) for their outstanding support during the last months I was working on this thesis and the possibility to gain experience on taping out a functional chip. I would particularly like to thank Michael Hutter for the excellent advices on writing scientific papers. A special thanks also to Frank K. Gürkaynak for giving me tips for the future and sharing pieces of his knowledge regarding Application-Specific Integrated Circuit (ASIC) design. I am sure some tips will help me out in the future. Christian Pendl a former tutor of mine and from the master studies on a steady companion receives a special thanks too. Working with him on projects was always a pleasure whilst (at the same time) a challenge as targets were always set very ambitious. Two highlights from this collaboration must be highlighted. First, a scientific paper which got accepted and also presented at the RFIDSec 2011. Second, going together abroad to write the master thesis at the SFIT Zürich. Last but not least the biggest thanks goes to my family and my girlfriend for the patience and support during the whole studies, especially during the time of being abroad to write the master thesis. A special thanks to my big brother who was and will always be a shining example. I know it was not always easy to understand my decisions and acting but they got always behind me. Because of this I want to dedicate this thesis to my family.

# Abstract

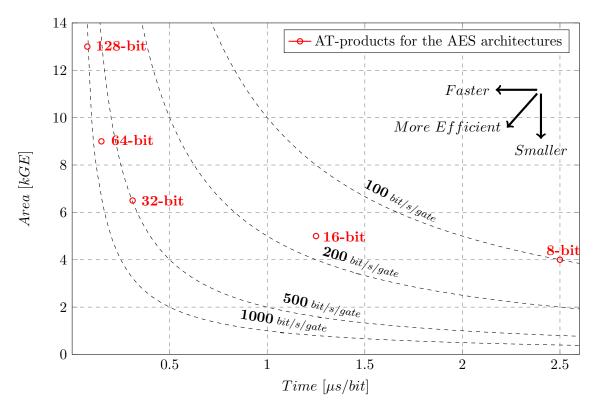

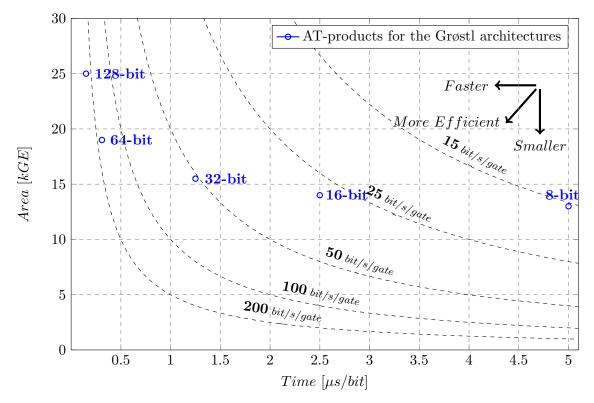

This thesis comprises of two constructive parts. First, GrÆStl, a combined hardware architecture for the Advanced Encryption Standard (AES) and Grøstl, developed for lowresource devices and aiming for high flexibility by targeting both Application-Specific Integrated Circuit (ASIC) and Field Programmable Gate Array (FPGA) platforms. The former is the most important encryption specification known so far, which was announced by the National Institute of Standards and Technology (NIST) in November 2001. Grøstl on the other hand is one of the final candidates of the cryptographic hash-algorithm competition initiated by NIST. The winner will augment the Federal Information Processing Standard (FIPS) 180-3, Secure Hash Standard (SHA) and become therefore maybe as important as AES. Combining these two primitives looks promising for the future as the integration of AES-128 into Grøstl-224 can be achieved with an area overhead of only 10% when aiming for ASIC platforms and furthermore might be used for authenticated encryption in resource-constrained environments. Using a 0.18 µm fabrication process while targeting a maximum frequency of 125 MHz delivered a complexity for GrÆStl of around 17.1 kGE after the backend design. The stand-alone versions for AES-128 and Grøstl-224 from which GrÆStl was build upon require 15.5 kGE and 5 kGE, respectively. All designs were realized with standard cells only and no technology or platform-dependent components such as Random Access Memory (RAM) macros, Digital Signal Processors (DSPs), or Block RAMs were used. On FPGA platforms even better results can be reported as the stand-alone versions for both AES and Grøstl outperform all existing work by a factor of 4.8 and about 1.6. This impressive results were achieved through exploiting the Shift Register Logic (SRL) functionality of Xlinix FPGAs. AES-128 and Grøstl-224 occupy therefore only 442 and 488 slices on a Xilinx Spartan-3. The combined version requires 956 slices. With respect to timing the results on the two platforms are equal. An AES encryption can be fulfilled within 652 clock cycles. Decryption on the other hand requires by default 1,269 clock cycles whereas a reduction to 955 clock cycles occurs when an AES operation with the same master key has been applied immediately before. Grøstl requires 3,061 clock cycles to process one message block.

Second, an FPGA system encompassing a programmable microcontroller, namely the openMSP430 and the dedicated hardware components from the first part designed to evaluate the impact of the highly flexible four-phase handshaking protocol and to enable a fair hardware/software comparison. The FPGA system was evaluated by increasing the frequency of the dedicated hardware components from 5 to 20 MHz while leaving the microcontroller constantly at 5 MHz, which resulted in a speedup reduction from 4 to only 1.3 up to 1.6. On the other hand, outsourcing of software routines on dedicated hardware accelerates the computation by a factor of 50 up to 360.

Keywords: AES, Grøstl, GrÆStl, SRL-16, ASIC, FPGA

# Kurzfassung

Diese Abschlussarbeit besteht aus 2 aufeinander aufbauenden Teilen. Erstens, GrÆStl, eine kombinierte Hardware-Architektur für den Advanced Encryption Standard (AES) und Grøstl, die für Geräte mit stark beschränkten Ressourcen entwickelt wurde und weiters auf eine hohe Flexibilität bezüglich dem Einsatz auf Application-Specific Integrated Circuit (ASIC) und Field Programmable Gate Array (FPGA) Plattformen abzielt. Ersteres ist die bis jetzt wichtigste Verschlüsselungsspezifikation welche im November 2001 vom National Institute of Standards and Technology (NIST) angekündigt wurde. Grøstl ist auf der anderen Seite einer der Finalisten eines vom NIST gestarteten Wettbewerbes für kryptographische Hash-Algorithmen, wo der Gewinner den Federal Information Processing Standard (FIPS) 180-3, auch Secure Hash Standard (SHA) genannt, erweitern und deswegen womöglich auch gleichbedeutend wie AES wird. Eine Kombination dieser beiden Primitive schaut für die Zukunft vielversprechend aus, da eine Integration von AES-128 in Grøstl-224 auf ASIC Plattformen mit einem zusätzlichen Flächenmehraufwand von nur 10 % möglich ist. Des weiteren könnte dadurch eine authentifizierte Verschlüsselung in Umgebungen mit beschränkten Ressourcen ermöglicht werden. Bei einem 0,18 µm Fabrikationsprozess und einer Auslegung auf maximal 125 MHz weißt GrÆStl nach dem Backend-Design eine Komplexität von rund 17,1 kGE auf. Die autarken Versionen für AES-128 und Grøstl-224, auf welchen GrÆStl aufbaut, benötigen 15,5 kGE beziehungsweise 5 kGE. Alle Designs wurden nur mit Standardzellen und ohne die Benutzung von Technologie oder plattformabhängigen Komponenten wie zum Beispiel Random Access Memory (RAM) Makros, Digital Signal Processors (DSPs) oder Block-RAMs realisiert. Auf FPGA-Plattformen können sogar noch bessere Resultate erzielt werden, da die autarken Versionen für AES und Grøstl bestehende Arbeiten um den Faktor 4,8 bis 1,6 übertreffen. Diese eindrucksvollen Resultate konnten durch das Ausnutzen der Shift Register Logic (SRL) Funktionalität von Xlinx FPGAs erreicht werden. AES-128 und Grøstl-224 verbrauchen hierbei auf einem Xlinx Spartan-3 nur 442 beziehungsweise 488 Slices. Die kombinierte Version benötigt 956 Slices. Bezüglich des zeitlichen Verhaltens sind die Resultate auf den beiden Plattformen identisch. Eine AES-Verschlüsselung kann mit 652 Taktzyklen erfüllt werden. Eine Entschlüsselung benötigt standardmäßig 1.269 Taktzyklen, wobei eine Reduktion auf 955 Taktyzklen erfolgt, sofern eine AES-Operation mit dem selben Hauptschlüssel unmittelbar davor durchgeführt wurde. Grøstl benötigt 3.061 Taktzyklen um einen Nachrichten-Block zu verarbeiten.

Zweitens, ein FPGA-System welches einen programmierbaren Mikrocontroller, den openMSP430, und die dedizierte Hardware aus dem ersten Teil enthält. Es wurde dazu entwickelt um die Auswirkung des höchst flexiblen 4-Phasen Handshake-Protokolls aufzuzeigen und einen fairen Hardware/Software vergleich zu ermöglichen. Das FPGA-System wurde durch das Erhöhen der Frequenz der dedizierten Hardwarekomponenten von 5 auf 20 MHz evaluiert, während der Mikrocontroller konstant mit 5 MHz betrieben wurde und

lieferte als Resultat eine Beschleunigungsreduktion von 4 auf nur 1,3 bis 1,6. Auf der anderen Seite konnte eine Beschleunigung durch das Auslagern der Software-Routinen auf die dedizierte Hardware im Bereich von 50 bis 360 erreicht werden.

Stichwörter: AES, Grøstl, GræStl, SRL-16, ASIC, FPGA

# Contents

| 1        | Inti                                          | oducti  | ion                                                                                                             | 1  |  |  |  |  |

|----------|-----------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

| 2        | Selected Chapters of Cryptography             |         |                                                                                                                 |    |  |  |  |  |

|          | 2.1                                           | Symm    | etric-Key vs. Public-Key Cryptography                                                                           | 3  |  |  |  |  |

|          |                                               | 2.1.1   | Unsecured Communication and Its Risks                                                                           | 3  |  |  |  |  |

|          |                                               | 2.1.2   | Requirements for Secure Communication                                                                           | 4  |  |  |  |  |

|          |                                               | 2.1.3   | Symmetric-Key Cryptography                                                                                      | 5  |  |  |  |  |

|          |                                               | 2.1.4   | Public-Key Cryptography                                                                                         | 5  |  |  |  |  |

|          | 2.2                                           | Block   | Ciphers                                                                                                         | 6  |  |  |  |  |

|          |                                               | 2.2.1   | Electronic Code Book (ECB) Mode                                                                                 | 7  |  |  |  |  |

|          |                                               | 2.2.2   | Cipher Block Chaining (CBC) Mode                                                                                | 8  |  |  |  |  |

|          | 2.3                                           | Stream  | n Ciphers                                                                                                       | 10 |  |  |  |  |

|          |                                               | 2.3.1   | Cipher Feedback (CFB) Mode                                                                                      | 10 |  |  |  |  |

|          |                                               | 2.3.2   | Output Feedback (OFB) Mode                                                                                      | 10 |  |  |  |  |

|          |                                               | 2.3.3   | Counter (CRT) Mode                                                                                              | 11 |  |  |  |  |

|          | 2.4                                           | Messa   | ge Authentication Codes (MAC)                                                                                   | 12 |  |  |  |  |

|          | 2.5                                           | Hash I  | Functions                                                                                                       | 14 |  |  |  |  |

|          | 2.6                                           | Hash-I  | Based Message Authentication Code (HMAC)                                                                        | 16 |  |  |  |  |

| 3        | Rij                                           | ndael - | Winner of the NIST AES Competition                                                                              | 17 |  |  |  |  |

|          | 3.1                                           |         | l Transformation                                                                                                | 18 |  |  |  |  |

|          |                                               | 3.1.1   | SubBytes/InvSubBytes                                                                                            | 19 |  |  |  |  |

|          |                                               | 3.1.2   | ShiftRows/InvShiftRows                                                                                          | 19 |  |  |  |  |

|          |                                               | 3.1.3   | MixColumns/InvMixColumns                                                                                        |    |  |  |  |  |

|          |                                               | 3.1.4   | AddRoundKey                                                                                                     |    |  |  |  |  |

|          | 3.2                                           | Round   | d-Key Generation                                                                                                |    |  |  |  |  |

| 4        | Grøstl - A NIST SHA-3 Competition Finalist 23 |         |                                                                                                                 |    |  |  |  |  |

|          | 4.1                                           |         | ression Function                                                                                                | 24 |  |  |  |  |

|          | 4.2                                           | -       | It Transformation                                                                                               |    |  |  |  |  |

|          | 4.3                                           | -       | $A$ and $Q$ in Detail $\ldots$ |    |  |  |  |  |

|          |                                               | 4.3.1   | AddRoundConstant                                                                                                |    |  |  |  |  |

|          |                                               | 4.3.2   | SubBytes                                                                                                        |    |  |  |  |  |

|          |                                               | 4.3.3   | ShiftBytes                                                                                                      |    |  |  |  |  |

|          |                                               | 4.3.4   | MixBytes                                                                                                        |    |  |  |  |  |

| <b>5</b> | $\mathbf{Rel}$                                | ated V  | Vork                                                                                                            | 29 |  |  |  |  |

| 6  | Asynchronous Interfaces 33          |                                                             |                 |  |  |  |  |  |  |

|----|-------------------------------------|-------------------------------------------------------------|-----------------|--|--|--|--|--|--|

|    | 6.1                                 | Synchronous Digital Circuits                                | 33              |  |  |  |  |  |  |

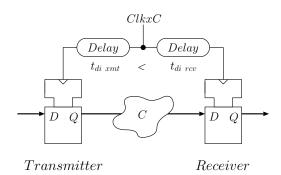

|    | 6.2                                 | Asynchronous Interfaces for Synchronous Digital Circuits    | 36              |  |  |  |  |  |  |

|    |                                     | 6.2.1 Inconsistent Data                                     | 36              |  |  |  |  |  |  |

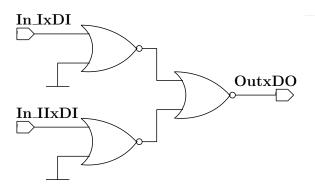

|    |                                     | 6.2.2 Measures Against Inconsistent Data                    | 37              |  |  |  |  |  |  |

| 7  | Bas                                 | Basics on Xilinx FPGAs 4                                    |                 |  |  |  |  |  |  |

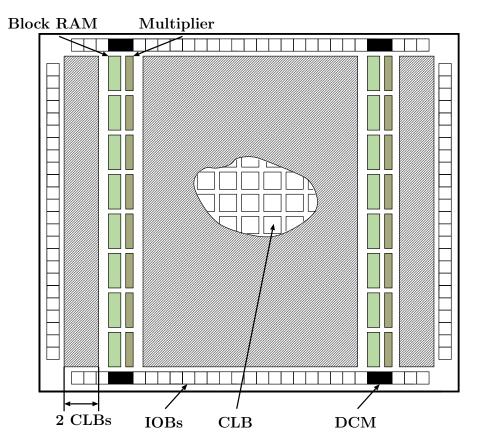

|    | 7.1                                 | General Structure                                           | 41              |  |  |  |  |  |  |

|    |                                     | 7.1.1 Configurable Logic Block (CLB)                        | 42              |  |  |  |  |  |  |

|    |                                     | 7.1.2 Slice                                                 | 42              |  |  |  |  |  |  |

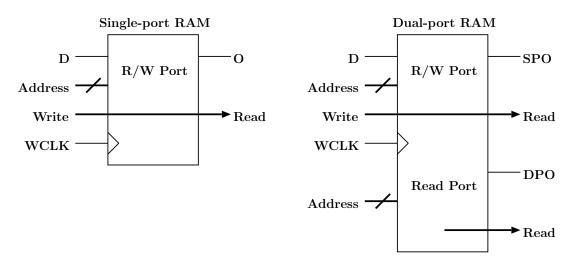

|    | 7.2                                 | Memory Variants for Spartan-3 FPGAs                         | 43              |  |  |  |  |  |  |

|    |                                     | 7.2.1 Block RAM (BRAM)                                      | 43              |  |  |  |  |  |  |

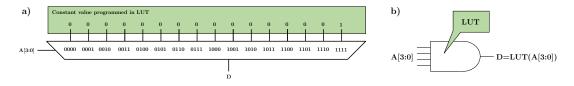

|    |                                     | 7.2.2 Distributed RAM (LUT RAM)                             | 44              |  |  |  |  |  |  |

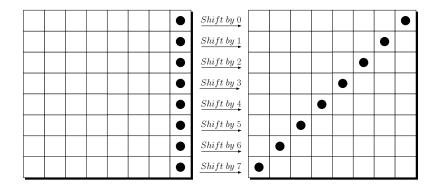

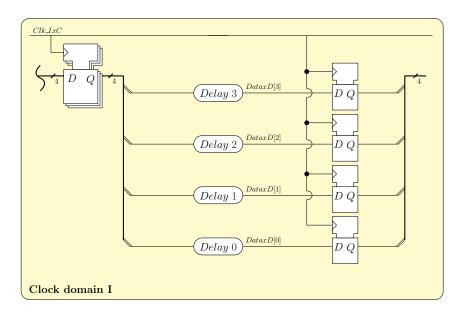

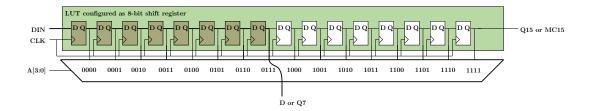

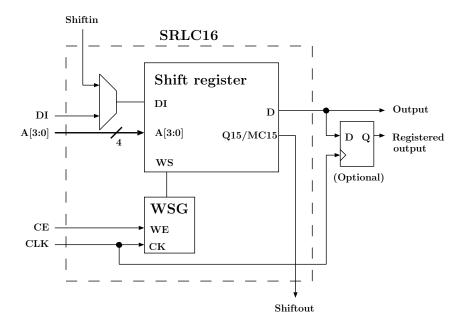

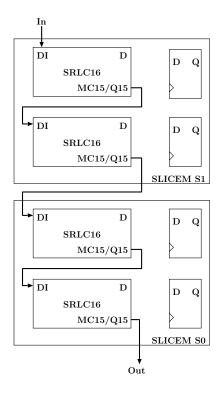

|    |                                     | 7.2.3 Shift-Register Logic (SRL16)                          | 45              |  |  |  |  |  |  |

| 8  | GrA                                 | EStl - A Combined AES/Grøstl HW Architecture                | 49              |  |  |  |  |  |  |

|    | 8.1                                 | On the Search for Optimal Resource Management               | 49              |  |  |  |  |  |  |

|    | 8.2                                 | Hardware Architecture                                       | 55              |  |  |  |  |  |  |

|    |                                     | 8.2.1 Top Layer                                             | 55              |  |  |  |  |  |  |

|    |                                     | 8.2.2 Common Datapath                                       | 58              |  |  |  |  |  |  |

|    | 8.3                                 | Results                                                     | 62              |  |  |  |  |  |  |

|    |                                     | 8.3.1 Application-Specific Integrated Circuit (ASIC)        | 62              |  |  |  |  |  |  |

|    |                                     | 8.3.2 Field Programmable Gate Array (FPGA)                  | 66              |  |  |  |  |  |  |

|    | 8.4                                 | Comparison with Related Work                                | 68              |  |  |  |  |  |  |

|    |                                     | 8.4.1 Comparison of ASIC Results                            | 68              |  |  |  |  |  |  |

|    |                                     | 8.4.2 Comparison of FPGA Results                            | 69              |  |  |  |  |  |  |

| 9  | FPGA System for HW/SW Evaluation 77 |                                                             |                 |  |  |  |  |  |  |

| 0  | 9.1                                 | General System Requirements                                 | 71              |  |  |  |  |  |  |

|    | 9.2                                 | System Architecture                                         |                 |  |  |  |  |  |  |

|    |                                     | 9.2.1 Xilinx Spartan 3                                      |                 |  |  |  |  |  |  |

|    |                                     | 9.2.2 openMSP430                                            |                 |  |  |  |  |  |  |

|    |                                     | *                                                           |                 |  |  |  |  |  |  |

|    |                                     | 9.2.4 Cryptographic Library                                 | 80              |  |  |  |  |  |  |

|    | 9.3                                 | Results                                                     | 83              |  |  |  |  |  |  |

|    |                                     | 9.3.1 Influence of External Data Transfer on Overall Timing | 83              |  |  |  |  |  |  |

|    |                                     | 9.3.2 Software/Hardware Evaluation                          | 85              |  |  |  |  |  |  |

| 10 | 0 Cor                               | nclusions                                                   | 87              |  |  |  |  |  |  |

|    | D.£                                 |                                                             | 01              |  |  |  |  |  |  |

| A  |                                     | initions Abbreviations                                      | <b>91</b><br>91 |  |  |  |  |  |  |

| -  |                                     |                                                             |                 |  |  |  |  |  |  |

| В  |                                     | ameleon - ASIC                                              | 93              |  |  |  |  |  |  |

|    | B.1                                 | General Features                                            | 93              |  |  |  |  |  |  |

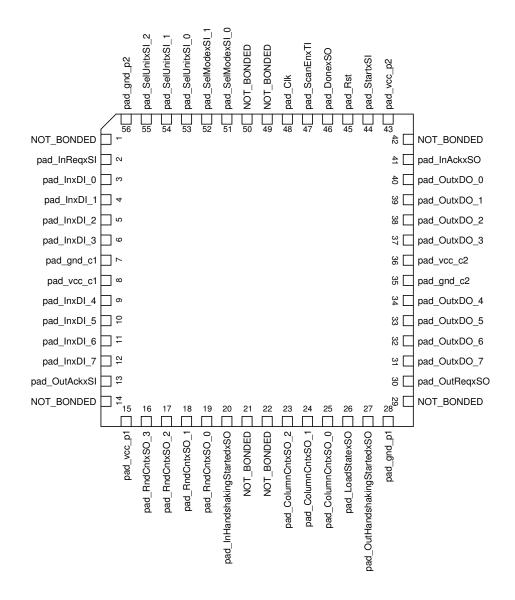

|    | B.2                                 | Pinout                                                      | 95              |  |  |  |  |  |  |

|    | B.3                                 | Pad Description                                             | 96              |  |  |  |  |  |  |

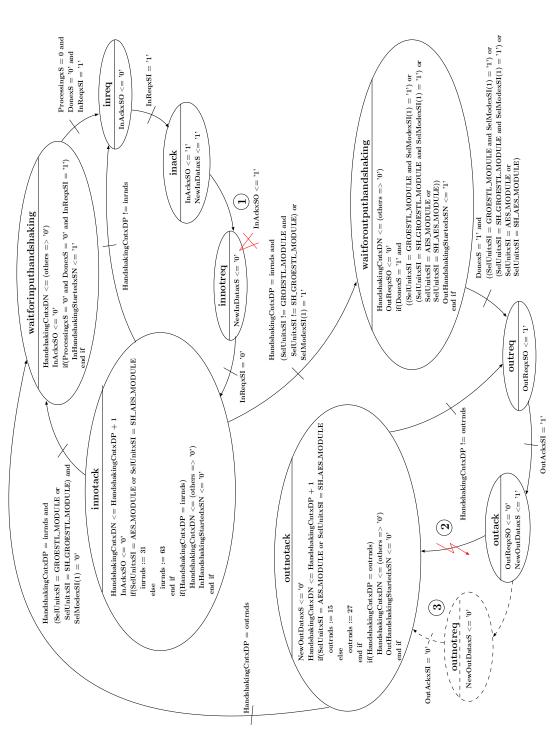

|    | B.4                                 | Interface Description                                       | 97              |  |  |  |  |  |  |

| $\mathbf{C}$ | Cham             | neleon - FPGA                                    | 99  |  |  |

|--------------|------------------|--------------------------------------------------|-----|--|--|

|              | С.1 У            | Xilinx Spartan-3 and Spartan-6 Results           | 99  |  |  |

|              | С.2 У            | Xilinx Virtex-5 and Virtex-6 Results             | 99  |  |  |

| D            | A System - AddOn | 101                                              |     |  |  |

|              | D.1 E            | Basic Linker Script for openMSP430 MCUs          | 101 |  |  |

|              | D.2 I            | Installation Script for MSPGCC Toolchain         | 105 |  |  |

|              | D.3 ]            | Test Program for Verifying Cryptographic Modules | 114 |  |  |

| $\mathbf{E}$ | Origi            | nal Assignment                                   | 123 |  |  |

| Bi           | Bibliography     |                                                  |     |  |  |

# Chapter 1 Introduction

Among the most commonly used cryptographic primitives in classical communication protocols are block ciphers and hash functions. The Advanced Encryption Standard (AES) [51] is by far the most widely spread block cipher since its standardization in 2001 by the National Institute of Standards and Technology (NIST). Grøstl [15] on the other hand is one of the final round candidates of the Secure Hash-Algorithm (SHA) competition [50], which will announce its winner in late of 2012. Therefore, AES is already and Grøstl could become an algorithm widely used to achieve data confidentiality, integrity and authenticity. In short, these three data properties can be fulfilled through authenticated encryption which plays a major role in the world of communication systems. In combination with the trend for ultra-mobile devices—containing evermore confidential information—equipped with an arbitrary communication interface there is the need for compact and power-efficient implementations. Due to the fact that AES and Grøstl feature several similarities such as a common S-box or similar diffusion layers an integration into one module looks promising for the future. In addition to the cost savings regarding area occupation, authenticated encryption could be fulfilled within one step. The consequential drawback that a parallel computation of an encryption/decryption and a hash computation is not supported anymore is mitigated by the circumstance that the most limiting factor in such ultra-mobile devices is area and low energy and not performance.

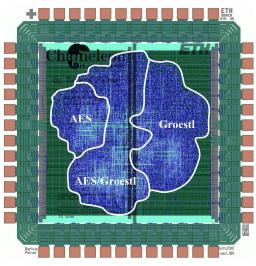

This work has been split into two constructive parts. First, GrÆStl a hardware architecture combining the functionality of AES-128 and Grøstl-224 in one piece of silicon. The design aims for high flexibility supporting both Application-Specific Integrated Circuit (ASIC) and Field Programmable Gate Array (FPGA) platforms without using technologydependent components such as Random Access Memory (RAM) macros, Digital Signal Processors (DSPs), or Block RAMs. Various optimization techniques were exploited to reduce the area footprint, for example, by sharing registers and a common datapath. The ASIC version of the design with the name Chameleon has been fabricated using the 0.18 µm Complementary Metal Oxide Semiconductor (CMOS) process technology from UMC and represents the first taped-out version of a combined AES/Grøstl architecture in literature. It requires only 17.1 kGE —backend results including eight parallel scanchains and clock gating—in total and needs 652/1,269 clock cycles for AES encryption/decryption and 3,061 clock cycles for hashing. The stand-alone implementations of AES and Grøstl consume around 5 and 15.5 kGE. Due to the chosen design were all large register banks are based on shift registers, backend results differ in only about 3% to the synthesis results. This nearly negligible overhead is reasonable as the storage elements are already connected together in a favourable manner. The small area requirements and

also the low power consumption of about 20  $\mu$ W at 100 kHz make the design applicable to resource-constrained devices. Porting the implementation on an FPGA was easy as no platform-dependent components were used. Due to a recommendation from Xilinx regarding the removal of the reset functionality from shift registers, c.f. [7], the design was altered in a suitable manner to ease the usage of the SRL-16 mode where the Look-Up Tables (LUTs) of slices can be reconfigured to form an 16-bit shift register. As the design perfectly fits this mode, it shows that the implementations outperform existing FPGA solutions in terms of low area. They require up to 79% less resources on a Spartan-3 compared to existing implementations. In addition, it shows that for FPGA platforms it is recommended to prefer the single versions as they are in sum smaller as the shared one. The reason for this is the state matrix which had to be adapted in order to integrate the AES state as well as also the master key and the actual round key, respectively.

In the second part an FPGA system was designed to enable a hardware/software comparison of the stand-alone implementations and the combined implementation. For this a microcontroller was required which was taken from OpenCores, c.f. [16]. The chosen Microcontroller Unit (MCU) is named openMSP430—RAM and ROM are located externally and connected to the core over two buses—and is compatible to the MSP430 of Texas Instruments, c.f. [61]. It is supported by the port of the GCC toolchain for the Texas Instruments MSP430 family (MSPGCC) which is important for setting up the design flow. Additionally, an interface to the cryptographic modules described in part one was required which was realized over the peripheral bus and a piece of software. For verification of the system, two test ROMs including testvectors for AES-128 and Grøstl-224 were attached to the design. As different clock domains were used for the MCU and the cryptographic modules a four-phase handshaking was incorporated to handle the communication. The clock of the cryptographic modules was designed for 5 and 20 MHz, respectively and is switchable over software. The expected speedup due to the increase of the clock frequency was reduced from 4 to about 1.3 up to 1.6 depending on the operation applied. Comparing software implementations targeting a low-memory footprint with the low-area implementations from part one resulted in a speedup between 50 and 360 depending on the mode of operation and the clock frequency used for the cryptographic modules.

The remainder of this thesis is organized as follows. In Chapter 2, an overview of symmetric-key and public-key cryptography is given. Furthermore, basic cryptographic primitives used in classical cryptography like block ciphers, secure hash functions and message authentication codes are explained. Chapter 3 presents the NIST AES competition and describes in detail its winner, the Advanced Encryption Standard (AES) followed by the NIST SHA-3 competition in Chapter 4 with a detailed explanation of Grøstl, one of the five finalists. Afterwards in Chapter 5 related work targeting low-area ASIC and FPGA implementations for AES and Grøstl are summarized. As an FPGA system with different clock domains is required in the second part of the thesis problems with interfaces between two independent subsystems—clock signals not synchronized—are addressed in Chapter 6 before in Chapter 7 basics on Xilinx FPGAs are stated. In Chapter 8 details on the taped-out chip, named Chameleon are given. Results and a comparison with related work is given for the ASIC as well as for the version ported on various Xilinx FPGAs. Afterwards, Chapter 9 presents the developed FPGA system targeting a Xilinx Spartan-3 FPGA, which contains an MSP430 MCU and the previously developed cryptographic modules. Finally, in Chapter 10 a summary of the results combined with drawn conclusions is given.

# Chapter 2

# Selected Chapters of Cryptography

This chapter gives a short introduction into the field of cryptography, especially targeting symmetric-key cryptography and public-key cryptography. Furthermore, it explains in detail general cryptographic primitives like block ciphers, hash functions and (hash-based) message authentication codes.

# 2.1 Symmetric-Key vs. Public-Key Cryptography

Symmetric-key and public-key cryptography are both used in various fields of application. In order to understand their need this section first introduces the risks of an unsecured communication. Afterwards, a list of requirements for secured communication is given. These requirements on the one hand can be fulfilled partly by symmetric-key cryptography and on the other hand fully by public-key cryptography. The reason why still both schemes are used should be clear after the subsections targeting these primitives.

#### 2.1.1 Unsecured Communication and Its Risks

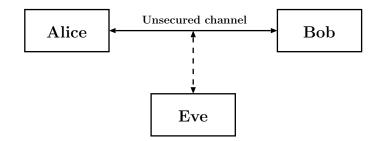

Before going into details of symmetric-key cryptography and public-key cryptography one must understand the basic communication scenario all further explanations will be based on. This scenario is given in Figure 2.1. Alice and Bob represent the two parties aiming to exchange data with each other without getting eavesdropped by a third party named Eve. All data exchange is established over an unsecure channel which means that it is not fully under control of the communication partners and therefore at risk that an adversary gets access to it. State-of-the-art mobile phones featuring several interfaces like Wi-Fi, bluetooth, infrared and so on are the best example for an infinitely seeming connectivity. This convenient way of exchanging data features also a drawback as all communication paths are not fully under control of the user because no one can tell on which path data is transmitted from Alice to Bob and vice-versa. Therefore a smart adversary could modify one stage of the path to eavesdrop the communication without the knowledge of either Alice or Bob, modify parts of the data or even exchange the whole. Impersonating Alice or Bob is in addition possible. These serious threats in combination with keeping a message secret—data confidentiality—were the reason cryptography was developed for.

Figure 2.1: Basic communication model.

#### 2.1.2 Requirements for Secure Communication

Through the mentioned attack scenarios the following fundamental objectives for a secure communication were revealed and stated by several authors, e.g., Hankerson et. al. [20]:

• Confidentiality

Data should be only readable by parties to which access was granted to. Therefore, messages sent from Alice to Bob should not be readable by Eve.

• Data integrity

Third parties like Eve should not be able to modify the message sent from Alice to Bob without getting detected by Bob.

- Data origin authentication Bob should be able to verify that data purportedly coming from Alice was indeed originated from Alice.

- Entity authentication Alice and Bob should be convinced of the identity of each other.

- Non-repudiation

If Alice sends a message to Bob, Alice cannot deny of having sent this message and Bob can prove this to others. Furthermore, Bob is able to recognize if the message was originated from Alice.

In the early days of cryptography secured communication was all done with symmetrickey cryptography as it was the only scheme known so far. As the technical aids and the mathematical knowledge were not as sophisticated as today, the efforts were all on the side of finding more efficient and more secure symmetric-key primitives than as to find an alternative to it. With the technical improvement and the better mathematical background, the key-distribution problem and the unreachable **non-repudiation** were not negligible any more. Therefore, industry and cryptographic community focused more on finding an alternative which solves all the shortcomings of symmetric-key cryptography than improving the efficiency of it. In 1975, such a variant named public-key cryptography was introduced by Diffie, Hellman and Merkle, c.f. [38]. Today, around 37 years later, still both schemes are widely spread which seems awkward when remembering the mentioned

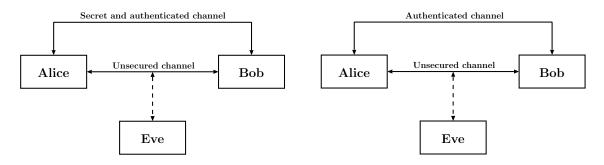

Figure 2.2: Symmetric-key communication model.

problems. The reason for this is the much higher efficiency of symmetric-key cryptography compared to public-key cryptography. Therefore, most communication protocols are based on both primitives. As example public-key cryptography could be used for exchanging the secret key required for symmetric-key cryptography. Both primitives are described in Subsection 2.1.3 and Subsection 2.1.4.

### 2.1.3 Symmetric-Key Cryptography

Symmetric-key cryptography is based on a shared secret over which encryption/decryption of data is being enabled. The basic scheme is shown in Figure 2.2. Alice and Bob want to communicate in a secure way over an unsecure channel. In order to establish this behavior, in addition a secret and authenticated channel is required to distribute the secret key. This additional channel is one of the shortcomings. The reason for this is the difficult and expansive way of establishing such a channel. The other drawback is the keymanagement problem. In the basic model where only Alice and Bob—two persons—are communicating with each other, only one secret key is required. Adding another person which should be able to communicate with the other two implicates that already three secret keys are necessary. An alternative would be an on-line trusted third-party which creates and distributes the keying material on demand to prevent storing of unnecessary keys. Finally, as communication between multiple persons is still possible—sharing all the same secret key—the possibility of impersonating communication partners is given. Therefore non-repudiation would be desirable which in fact cannot be established with this primitive.

#### 2.1.4 Public-Key Cryptography

Public-key cryptography uses a key pair—a public and a private key—instead of a single secret key. It was developed to eliminate all the shortcomings of symmetric-key cryptography and fulfills therefore all the security goals mentioned in Subsection 2.1.2. The basic scheme is shown in Figure 2.3. Alice and Bob want to communicate again in a secure way over an unsecure channel. The only difference in the communication model between the symmetric-key and the public-key scheme is in the additional channel between the two communication partners. For the public-key cryptography the channel must only be authentic and not secure. Therefore, it is possible for everyone to read the content but not to modify it in an unperceived manner. The authenticity is highly important as otherwise an adversary would be able to distribute wrong public keys, namely ones from

which the corresponding private key is known. In such a scenario the encrypted message would not be safe anymore. If the channel is authentic then the instance which receives the public key can be sure that the corresponding private key is in possession of the right instance. Therefore, sending an encrypted message only intended to be readable by the receiver is easy as the encryption step can be fulfilled through the exposable public key of the receiver. The encrypted message can be afterwards decrypted with the corresponding private key which must be in possession of the receiver only.

Public-key cryptography is much more complex as symmetric-key cryptography. As public-key cryptography eliminates all the shortcomings of symmetric-key cryptography and furthermore requires only an additional authenticated but not secure channel it makes sense to use this primitive to distribute a secret key between two parties that want to communicate in a secure way. Through this combination the high efficiency of symmetrickey cryptography can be used while avoiding the need for a secret and authenticated channel.

# 2.2 Block Ciphers

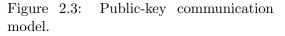

Block ciphers are widely spread throughout various communication protocols which are based on symmetric-key cryptography. The reason for is the high efficiency for encrypting/decrypting data with a secret key, from now on called k. Basic idea is that the transformation step operates on a full data block and not on single bits. Therefore, it must be guaranteed that the input data can be split up in a multiple of the data-block size. This is done through a padding function which is specially defined for each block-cipher algorithm. The output of a block cipher is determined by the input data, the secret key kand the chosen algorithm. As block ciphers are deterministic algorithms—no randomness included—two instances stimulated with the same data set consisting of the input data and the secret key k deliver the same output.

Noteable algorithms are the Data Encryption Standard (DES) [47], Triple DES [47], Rivest Cipher 5 (RC5) [55], Blowfish [58] and Rijndael [10] which became in 2000 the Advanced Encryption Standard (AES) [51]. DES, triple DES and AES are algorithms standardized by the National Institute for Standards and Technology (NIST). DES was introduced first followed by the Triple DES variant which is simply an improved version of DES to mitigate weaknesses found during cryptanalysis. Triple DES, as the name implies, operates on three single DES units whereas either two or three independent secret keys can be used. The three-key variant has the advantage of a higher bit-security compared to the two-key version and should therefore be preferred. The cryptographic community still was not satisfied with these algorithms and their corresponding bit-security levels. Hence a competition was started to find a successor of these two variants. In 2000, NIST announced the Rijndael algorithm [10] as winner which became after some small modifications—e.g. block size fixed to 128 bits, key size selectable between 128/192/ 256 bits—the most valuable and widespread block cipher AES [51].

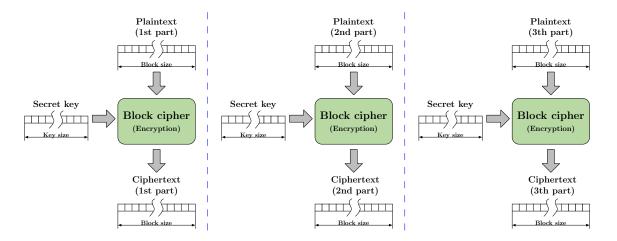

Still the question remains how to act on block ciphers in detail. Figure 2.4 represents the easiest way to encrypt data through the aid of a block cipher. The data to be encrypted is first padded up to a multiple of the block length before it gets split up in blocks of same size. These represent in combination with the secret key k—remains the same for each block to be encrypted—the input data to the block cipher instance. As the transformations are independent from each other either one instance or multiple instances can be used. The maximum speedup can be achieved when as many block cipher instances

Figure 2.4: Encryption and decryption with an arbitrary block cipher.

as input blocks exist as then the encrypted data is available after the computation time of one block. The full ciphertext is received through a concatenation of the block-cipher outputs.

As this variant—called the Electronic Code Book (ECB) mode—exhibited some security flaws during the last years, modes of operation were introduced in order to increase the security level. Two modes during which the instances are still operated as block ciphers are explained in detail in the next two subsections. For more explanations on Block Ciphers, c.f. [35, 39].

#### 2.2.1 Electronic Code Book (ECB) Mode

How to encrypt/decrypt data regarding the Electronic Code Book (ECB) mode is shown in Figure 2.5 and Figure 2.6. It represents the native mode as the data to be encrypted/decrypted is first padded up to a multiple of the block length—not explicitly shown—before it gets processed by the chosen block cipher instance in combination with the secret key k. As this key remains the same for all encryption/decryption procedures, the security level decreases as more plaintext/ciphertext pairs—generated with the same secret key k—are available to an attacker from which information on the used secret key can be revealed. Furthermore, as block ciphers are deterministic algorithms identical plaintext blocks are being transformed to identical ciphertext blocks and vice versa if the pair consisting of the block-cipher algorithm and the secret key k remains the same. Therefore, the message confidentiality is not unconditionally given as if a plaintext/ciphertext pair once is being revealed it gets easily recognized if no change in the secret key k or the block-cipher algorithm has been applied. Last but not least it hides poorly data patterns. For example, a change in the first data block gets isolated as the change cannot propagate into other blocks as well [35, 39].

Figure 2.5: Encryption according Electronic Code Book (ECB) mode.

Figure 2.6: Decryption according Electronic Code Book (ECB) mode.

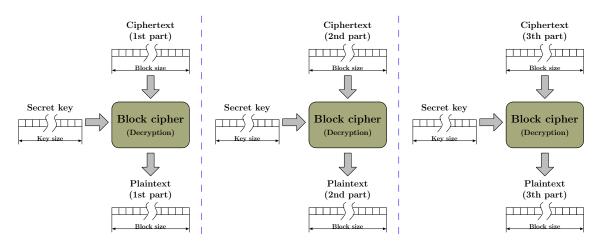

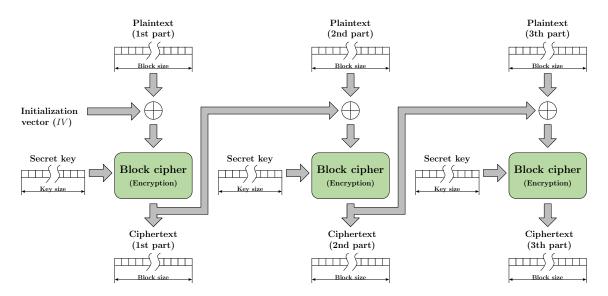

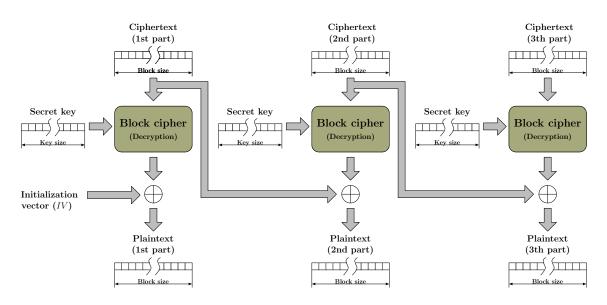

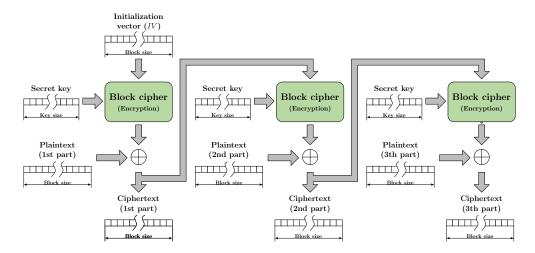

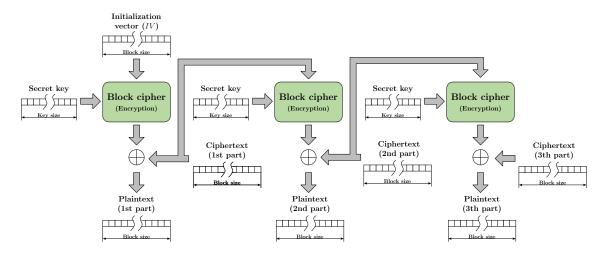

## 2.2.2 Cipher Block Chaining (CBC) Mode

In order to mitigate the security flaws introduced through the ECB mode, the Cipher Block Chaining (CBC) mode was invented. In that mode of operation the plain text is never directly applied to the block cipher as shown in Figure 2.7. Instead, an initial vector ideally changes each time—gets XORed with the first input data block. The output of the block cipher represents afterwards on the one hand a part of the ciphertext and on the other hand the value which gets XORed with the second input block. Therefore, a change in the initial vector propagates through all steps. If this initial vector changes each time it is guaranteed that the same input data never corresponds to the same output data. Hence one of the security flaws of the ECB mode namely the confidentiality has been resolved. The other problem regarding the pattern hiding was improved but not fully removed. A change of one bit in the initialization vector will affect the whole ciphertext. Changes in the plaintext instead affect only following ciphertext blocks but not the already processed ones. If an attacker somehow achieves to apply multiple times the same initial vector it would be able to identify patterns through changing bits at various locations and observing the corresponding output. This improvement related to the ECB mode

Figure 2.7: Encryption according Cipher Block Chaining (CBC) mode.

Figure 2.8: Decryption according Cipher Block Chaining (CBC) mode.

has also a drawback regarding performance as a parallelization of the encryption is not possible anymore as the various steps are depending on their predecessors. This changes for the decryption shown in Figure 2.8 as there a plaintext can be computed out of two ciphertext blocks and so a parallelization is again feasible. The computation of the first plaintext block differs from the rest as there is only one ciphertext block and the initial vector. Therefore, if a wrong initial vector is applied only the first plaintext block is invalid. This differs from the encryption process where the whole ciphertext would be wrong. Furthermore, a change of one bit in a ciphertext block would make the whole corresponding plaintext block invalid whereas only one bit of the following plaintext block will be flipped. All the other following plaintext blocks will be valid again [35, 39].

## 2.3 Stream Ciphers

Block ciphers are algorithms which take as input the plaintext and a secure key k and deliver as result the corresponding ciphertext. As these operations are block based a parallelization generally can be applied through multiple instances of the same algorithm. Stream ciphers instead compute a pseudorandom keystream which is combined bit-by-bit with the plaintext. This combination step itself represents the encryption of the plaintext and delivers therefore the corresponding ciphertext. As stream ciphers are also used in symmetric-key cryptography both the transmitter and receiver must be able to compute the same keystream. This is done over an initial value from which the keystream can be derived, for instance, through digital shift registers. Therefore, the initial value can be seen as secret key k. Furthermore, both sides must have agreed before the transaction on the algorithm used to derive the pseudorandom keystream. Another difference is the fact that stream ciphers require for both encryption and decryption an encryption-only unit whereas block ciphers need both. The keystream is generally computed over a digital shiftregister circuit like for example with a Linear Feedback Shift Register (LFSR). Another possibility is to use block ciphers as explained in the next three subsections. For more explanations on Stream Ciphers, c.f. [35, 40].

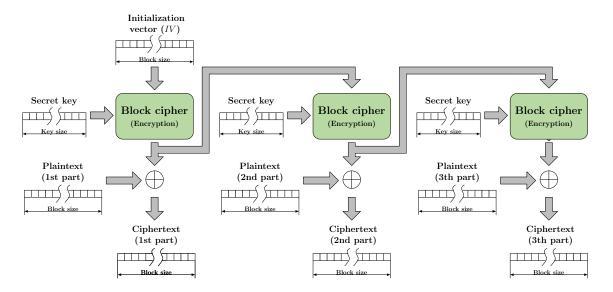

## 2.3.1 Cipher Feedback (CFB) Mode

Figure 2.9 and Figure 2.10 present encryption and decryption for the Cipher Feedback (CFB) mode which uses an arbitrary block cipher for the keystream generation. The stimulation of the first instance takes place with the initial vector IV which must be known to both the transmitter and receiver and therefore represents the secret key k. The ouput of the first block cipher is afterwards combined with the plaintext and forms the corresponding ciphertext. Furthermore, this result is the input data to the next instance in order to create a keystream depending on the previous result. As the encryption step itself is simply an XOR operation of the block-cipher output with the plaintext, it can be easily reversed by exchanging the plaintext with the ciphertext. In order to perform a complete decryption the input to the next instance is again the ciphertext as the keystream must be exactly the same for both the encryption and the decryption procedure. An advantage of this scheme is the fact that it contains a self-synchronization as only the initial value must be known to both the transmitter and the receiver. The internal state doesn't matter as both sides are able to encrypt/decrypt the data independently from each other. Furthermore, a parallelization of the decryption can be applied as the keystream is derived from the different already known ciphertext parts. A drawback is that a loss of data permanently throws off decryption. Regarding pattern hiding flipping one bit of the plaintext during data encryption produces a flipped bit in the corresponding ciphertext. Furthermore, this modification propagates along as the ciphertext represents the data input to the next block cipher unit and therefore modifies up from this position the derived keystream. Flipping one bit of the ciphertext during the decryption effects at maximum two plaintexts and stays therefore locally restricted as the modification doesn't propagate further [35, 40].

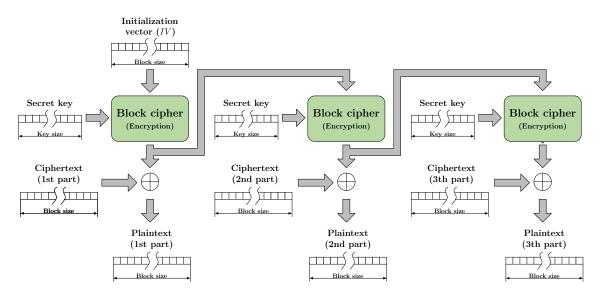

### 2.3.2 Output Feedback (OFB) Mode

The Output Feedback (OFB) mode is very similar to the CFB mode and is shown in Figure 2.11 and Figure 2.12. Difference is that the keystream modification is achieved

Figure 2.9: Encryption according Cipher Feedback (CFB) mode.

Figure 2.10: Decryption according Cipher Feedback (CFB) mode.

without taking the plaintext or ciphertext into account. On the first sight this looks like an improvement regarding performance but it isn't as the decryption cannot be parallelized. The reason for is that the input to a block-cipher unit is originated from the previous one which has to be computed first. Furthermore, pattern hiding is also lagging behind as flipping one bit of the plaintext during encryption or one bit of the ciphertext during decryption has only a locally restricted impact [35, 40].

#### 2.3.3 Counter (CRT) Mode

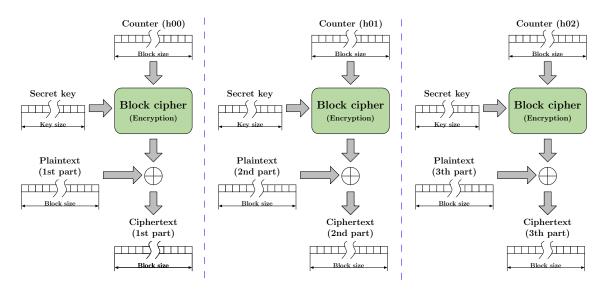

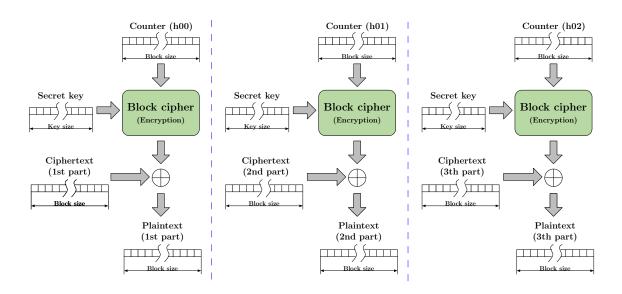

Last but not least the Counter (CRT) mode gets described where the input to the various block-cipher units originates from a counter function as shown in Figure 2.13 and Figure 2.14. A requirement for this is that it produces a long sequence which is allowed to repeat afterwards. The keystream can therefore be computed in parallel as only the initial counter value and the corresponding function must be known. As both the plaintext for encryption or the ciphertext for decryption are simply combined with the pseudorandom keystream in order to achieve the desired output, the pattern hiding lags in the same way

Figure 2.11: Encryption according Output Feedback (OFB) mode.

Figure 2.12: Decryption according Output Feedback (OFB) mode.

behind as described in the modes of operation before.[35, 40]

# 2.4 Message Authentication Codes (MAC)

Message authentication codes can be used to achieve data integrity by computing a checksum over the message while using a secret key k. As only the transmitter and the receiver are aware of this key it is not possible to modify the transmitted message by a third party without getting recognized. In order to achieve this, the transmitter computes a checksum over the message using the secret key k. Afterwards the message and also the computed checksum is transmitted to the receiver which computes the checksum on its own and compares it to the received one. It they match no modification of the message has been taken place.

Figure 2.13: Encryption according Counter (CTR) mode.

Figure 2.14: Decryption according Counter (CTR) mode.

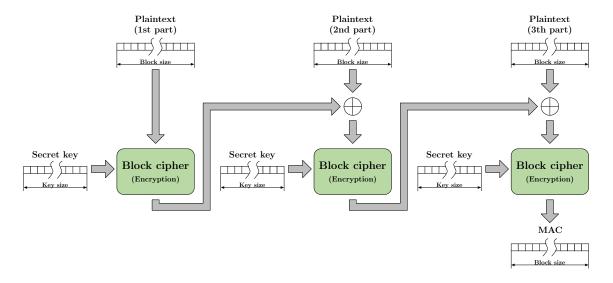

Block ciphers for instance can be used to achieve this behaviour like for example with the Cipher Block Chaining Message Authentication mode (CBC-MAC) shown in Figure 2.15. This mode of operation is very similar to the CBC mode with the difference that the initial vector is set to zero and that only the last cipherblock is used. An available block cipher in CBC mode can therefore be easily reconfigured for MAC computation. Regarding security only fixed-length messages should be allowed for the standard CBC-MAC mode as an attack exists during which an attacker is able to append an arbitrary message which delivers as result the same MAC as before. For this, two messages and their corresponding MACs are required. A remedy would be to encode the data length into the first block. With this modification also variable lengths can be supported [35, 41].

Figure 2.15: Computing the Message Authentication Code (MAC) for an arbitrary message using the CBC-MAC mode.

## 2.5 Hash Functions

Cryptographic hash functions compute of a given message m the corresponding hash h = hash(m) which is referred to in literature as message digest or simply digest. The length of it depends only on the algorithm used and not on the length of the given message m. Through this functionality data integrity of a message can be assured.

The cryptographic hash functions Message-Digest 4 (MD4) [56], MD5 [54], Secure Hash-Algorithm 1 (SHA-1) [48], SHA-2 [48] and also some candidates of the SHA-3 competition like Grøstl [15], Skein [12] or Blake [2] operate similarly to block ciphers on blocks of data which implies the need for a padding function. For the sake of completeness it must be stated that also other approaches exist, like for example, JH or Keccak which are also both final candidates for the SHA-3 competition.

Secure cryptographic hash functions must fulfill the following three requirements: **preimage resistance**, **second-preimage resistance** and **collision resistance**. More details on each of these requirements are given in the following list.

• Preimage resistance

Given a message digest h it should be difficult to find any message m such that h = hash(m) is fulfilled (similar to one-way functions).

#### • Second-preimage resistance

Given a message  $m_1$  it should be difficult to find any message  $m_2 - m_2$  must be not equal to  $m_1$ -such that  $hash(m_1) = hash(m_2)$ .

• Collision resistance

It should be difficult to find any two messages  $m_1$  and  $m_2 - m_2$  must be not equal to  $m_1$ -such that  $hash(m_1) = hash(m_2)$ .

The simplest scheme for achieving data integrity would be to transmit the message  $m_1$ and also its message digest  $h_1$  to the receiver, which can recompute the message digest and obtains therefore  $h_2$ . If these digests coincide, no modification of the message has

#### 2.5. HASH FUNCTIONS

Figure 2.16: Man-in-the-middle attack on a communication scheme using only hash functions to obtain data integrity.

Figure 2.17: Communication scheme using cryptographic hash function in combination with symmetric-key encryption in order to obtain data integrity and data origin authentication (if only two instances knowing the secret key k).

occurred. The only drawback is the fact that a man-in-the-middle attack as shown in Figure 2.16 is possible where a third party exchanges both the original message  $m_1$  and the corresponding digest  $h_1$  with it's own message  $m_e$  and the corresponding digest  $h_e$ . The receiver is only in the position of checking message modifications but not from whom the message was originated.

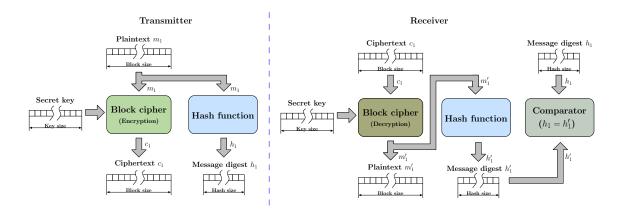

A better approach is given in Figure 2.17 where first the message  $m_1$  is encrypted using the secret key k which is only known to the transmitter and receiver. The plaintext on the other hand gets hashed and forms therefore the message digest  $h_1$ . Both the encrypted message  $c_1$  and the digest  $h_1$  get transferred. After receiving both data blocks the receiver first decrypts the ciphertext  $c_1$  to obtain  $m'_1$  which should be the original message sent by the transmitter. In order to proof the validity of the data the receiver computes out of the decrypted message  $m'_1$  the hash value  $h'_1$  and compares it to the received one. If they match it is guaranteed that no modification of the data has occurred [36, 42].

# 2.6 Hash-Based Message Authentication Code (HMAC)

Hash-based message authentication codes are another variant how to achieve data integrity and data origin authentication. The last aspect only applies if the instances knowing the secret key k is limited to two. General idea behind is that the keying material k is combined (e.g., using XOR operation) with the message m. The so gained message digest h = Hash(m||k) and the original message m get transferred to the receiver. In contrast to the scheme in Figure 2.17, the data is transmitted in a readable manner. After receiving the message m it gets again combined with the keying material k over the same function used at transmitter side. If the received digest and the computed one match, no corruption of the message has occurred [36, 43].

# Chapter 3

# Rijndael - Winner of the NIST AES Competition

In the early 1990s the U.S. Government stated its interest in a more secure way of encrypting data. Therefore, the National Institute of Standards and Technology (NIST) in combination with industry and the cryptographic community started the search for a standardized symmetric-key scheme in January 1997. Their goal was a Federal Information Processing Standard (FIPS) for an unclassified, publicly disclosed and worldwide royaltyfree block cipher with a minimum supported block size of 128 bits and key sizes of 128, 192 and 256 bits. In August 1998, the First AES Candidate Conference (AES1) was held with the outcome of 15 potential candidates going for a detailed review. The results of the analysis conducted by the global cryptographic community were presented in March 1999 at the AES2 followed by a public comment period. NIST used both the analysis and the comments to select the five finalists, namely MARS [4], Rivest Cipher 6 (RC6) [57], **Rijndael** [10], **Serpent** [1] and **Twofish** [59]. This selection was also the end of round one and the starting shot for round two. The first initiative in the second round was a detailed analysis of the five finalists followed by a search for public comments including cryptanalysis, intellectual property and much more. For the last conference, the AES3, held on April 13-14, 2000 all submitters were invited to take a stand on comments of their algorithms. With the gained information from the last conference NIST announced in October 2000 Rijndael as winner of the competition [52].

As last step NIST published in February 2001 the Federal Information Processing Standard (FIPS) 197 [51] describing the algorithm nowadays known under the name Advanced Encryption Standard which restricts the block size to 128 bits and the key size to 128, 192 and 256 bits. Dependent on the key size used the algorithm is referred to as AES-128, AES-192 or AES-256. The original Rijndael algorithm [9] alternatively allows the independent choice of the key and block size out of the set of 128, 160, 192, 224 and 256 bits.

The AES algorithm was developed for symmetric-key cryptography and is a block cipher which encrypts blocks of data independent from each other. As this block cipher requires always 128 bits of data for encryption/decryption a padding function which fills up the data to a multiple of 128 bits is inevitable. Afterwards the data is split up into blocks of 128-bits size and iteratively or parallel processed by AES implementations consisting of the round transformation described in Section 3.1 and the round-key generation described in Section 3.2. For more details see [51].

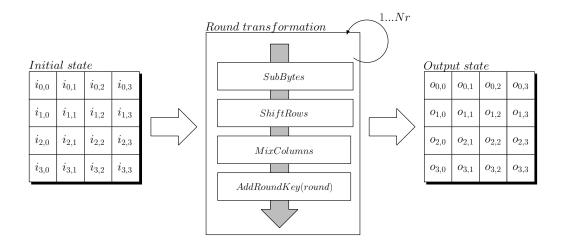

Figure 3.1: Scheme of the AES encryption.

# 3.1 Round Transformation

The round transformation is build upon four operations: SubBytes, MixBytes, MixColumns and ShiftRows. As both encryption and decryption are supported the inverse operations are required in addition. Figure 3.1 and Figure 3.2 show the AES encryption and decryption scheme. Both are slightly simplified as the initial key addition, the round-key generation and also the last round (MixColumns/InvMixColumns operation skipped) are not illustrated.

The initial state matrix for encryption is obtained through the initial AddRoundKey operation where the master key is added (XORed) with the input message. Afterwards, the round transformation starts executing iteratively the SubBytes, ShiftRows, MixColumns and AddRoundKey operations as shown in Figure 3.1. For the AddRoundKey operation the appropriate round key is required which can be computed on-the-fly or precomputed and stored in memory. The on-the-fly computation is described in Section 3.2. The number of rounds to be executed depends on the key size. A key size of 128 bits implies 10 rounds, 192 bits 12 rounds and 256 bits 14 rounds. The last round is slightly different as the MixColumns operation is bypassed. The final state matrix represents the encrypted message.

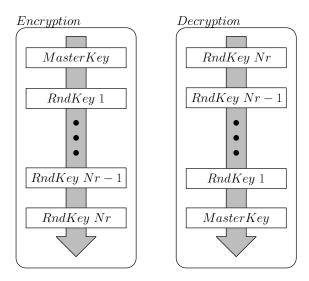

Decryption is the inverse operation of encryption and is used to obtain the plaintext from a ciphertext. In order to achieve this behaviour a few modifications are necessary. First of all, the initial AddRoundKey operation requires the last round-key instead of the master key as for the decryption the round keys must be applied in an inverse manner to the encryption. Consequently an on-the-fly generation requires a longer computation time. At least as much longer as the time required to derive the last round key from the master key. The order of the round keys can be seen in Figure 3.9. Next, instead of the operations used during encryption their counterparts InvShiftRows, InvSubBytes, AddRoundKey, InvMixColumn must be used. The AddRoundKey transformation stays the same as only the input changes according to the previously described round-key generation. Last but not least the sequence of the round transformation must be adapted as shown in Figure 3.2. Similar to the encryption step the InvMixColumns operation is bypassed during the last round. The final state matrix represents the decrypted message. In the following, the components of the round transformation are described in more detail.

Figure 3.2: Scheme of the AES decryption.

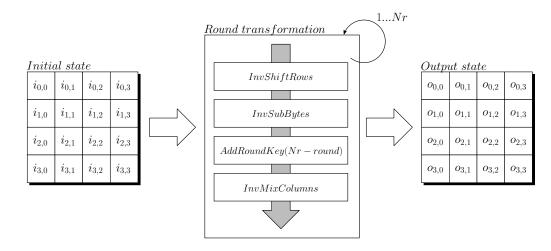

Figure 3.3: An *InvSubBytes* transformation is the inverse of the *SubBytes* transformation.

Figure 3.4: Scheme of the SubBytes/InvSubBytes transformation.

## 3.1.1 SubBytes/InvSubBytes

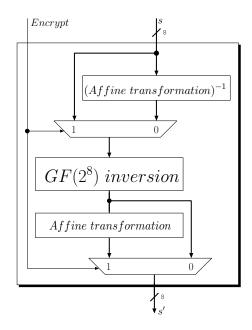

The SubBytes and InvSubBytes transformation, respectively is a non-linear byte substitution that substitutes each byte of the state as shown in Figure 3.3. They can be realized either over a Look-Up Table (LUT) or by an on-the-fly computation. The latter is shown in Figure 3.4. In order to get the SubBytes functionality the encryption signal must be set to one which implies that first the multiplicative inverse in the finite field  $GF(2^8)$  is taken followed by a subsequent affine transformation. In order to get the InvSubBytes functionality this sequence must be reversed. For more details see [51].

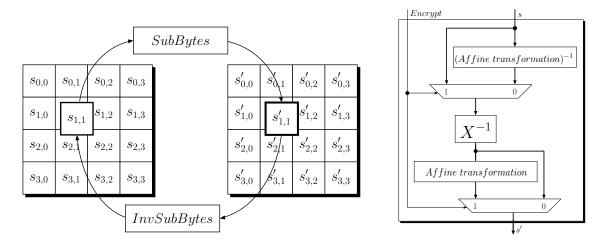

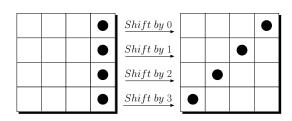

## 3.1.2 ShiftRows/InvShiftRows

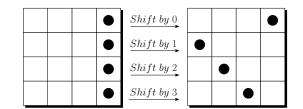

Both transformations are rotate operations and equal regarding the offset of each row. The only difference is the rotate direction because it is a left rotate for the ShiftRows and a right rotate for the InvShiftRows transformation. The impact of the ShiftRows

Figure 3.5: The effect of the ShiftRows transformation on the state.

Figure 3.6: The effect of the InvShiftRows transformation on the state.

transformation and the InvShiftRows transformation on the state matrix is shown in Figure 3.5 and Figure 3.6.

### 3.1.3 MixColumns/InvMixColumns

These transformations can be seen as a matrix multiplication and operates on a complete column instead of a single byte. The matrices used for both transformations are circulant meaning that each row has the same content but is shifted to the right by one with respect to the row above. In short, we may write for the *MixColumn* matrix

$$B = circ(02, 03, 01, 01) \tag{3.1}$$

and for the InvMixColumn matrix

$$B = circ(0e, 0b, 0d, 09).$$

(3.2)

The detailed notation for the MixColumns multiplications can be seen in Formula 3.3 and for the InvMixColumns multiplication in Formula 3.4.

$$\begin{bmatrix} s_{0,c}'\\ s_{1,c}'\\ s_{2,c}'\\ s_{3,c}' \end{bmatrix} = \begin{bmatrix} 02 & 03 & 01 & 01\\ 01 & 02 & 03 & 01\\ 01 & 01 & 02 & 03\\ 03 & 01 & 01 & 02 \end{bmatrix} \begin{bmatrix} s_{0,c}\\ s_{1,c}\\ s_{2,c}\\ s_{3,c}' \end{bmatrix}$$

(3.3)

$$\begin{bmatrix} s_{0,c}'\\ s_{1,c}'\\ s_{2,c}'\\ s_{2,c}'\\ s_{3,c}' \end{bmatrix} = \begin{bmatrix} 0e & 0b & 0d & 09\\ 09 & 0e & 0b & 0d\\ 0d & 09 & 0e & 0b\\ 0b & 0d & 09 & 0e \end{bmatrix} \begin{bmatrix} s_{0,c}\\ s_{1,c}\\ s_{2,c}\\ s_{2,c}'\\ s_{3,c} \end{bmatrix}$$

(3.4)

#### 3.1.4 AddRoundKey

The *AddRoundKey* transformation XORes each byte of the round key—either available over an on-the-fly computation or through a lookup in the memory in case of precomputation—with the appropriate byte of the state. Details on the generation can be found in Section 3.2.

Figure 3.7: Scheme of the forward round-key generation.

Figure 3.8: Scheme of the backward roundkey generation.

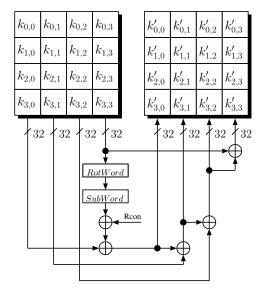

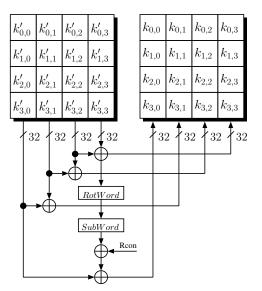

## 3.2 Round-Key Generation

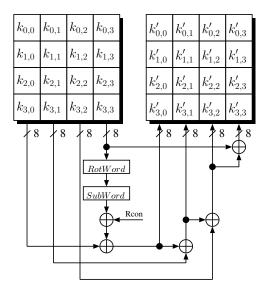

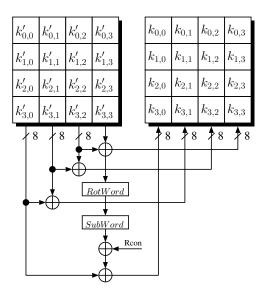

All round keys can be computed with the aid of a *SubWord* transformation that applies four times the *SubBytes* function, a *RotWord* transformation that rotates four bytes to the left by one and a small Look-Up Table (LUT) named Rcon containing the round constants (one for each round).Details on the round constants can be found in FIPS-197 [51]. The scheme for the forward round-key generation and also its inverse are shown in Figure 3.7 and Figure 3.8. Both can be computed on-the-fly.

For the forward round-key generation it is the easiest to start with the first column of the key matrix which can be updated through an XOR operation with the modified values–*RotWord*, *SubWord* and Rcon applied—of the last column. Afterwards, the rest is straight forward as always the previously gained result is taken and XORed with the next column until all are updated.

For the backward round-key generation the last column must be saved in a temporary place as it is required later on. Afterwards, it is updated through an XOR operation with the column before. This is repeated another two times (third column is updated with second column and afterwards the second column is updated with the first column). The final step is achieved by taking the temporary values, applying the *RotWord*, *SubWord* and Rcon and XORing it afterwards to the first column. In that way the predecessor from a specific round key can be computed.

Restricted environments typically claim for an on-the-fly computation of the round keys as the storage is simply often not available. Hence, it is important to know that a decryption has a big drawback regarding computation time. The reason for this is that the order of the round keys must be applied in a reverse manner. As most of the time an AES implementation obtains the master key and a ciphertext to be decrypted, it is necessary to first compute all the round keys down to the last one before the real computation can start. This fact is also illustrated in Figure 3.9.

Figure 3.9: Order of the round keys depending on the mode of operation.

### Chapter 4

# Grøstl - One of the Finalists of the NIST SHA-3 Competition

The Federal Information Processing Standard (FIPS) 180-3 [48] specifies cryptographic hash algorithms converting a variable-length message into a fixed-length message digest. The algorithms specified can be grouped into SHA-1 and SHA-2. SHA-0 is no longer included as it contains a weakness which has been fixed in SHA-1 that is now its replacement. SHA-2 encompasses the functions SHA-224, SHA-256, SHA-384 and SHA-512 and is significantly different to SHA-1, which is the most widely used secure hash algorithm. In 2005, a possible mathematical weakness of SHA-1 was identified. As SHA-2 is algorithmically similar, it is assumed that this security flaw might occur in the group of algorithms summarized as SHA-2 too. Until today no successful attacks on SHA-2 have been reported. Because of the advances in cryptanalysis and the disclosed weaknesses of SHA-1 and probably SHA-2, NIST started a public competition searching for a successor of these algorithms in November 2007. The winner will be named SHA-3 and will extend the algorithms currently specified in FIPS 180-3. 64 candidates were submitted by October 2008 but only 51 of them were selected for the official first round which started in December 2008. 14 out of 51 candidates made it to the second round with the starting shot in July 2009. NIST allocated a year for public comments and internal reviews on the 14 chosen candidates. Based on the information gained, 5 finalists were selected for the third and also final round, namely BLAKE, Grøstl, JH, Keccak and Skein. This last round started in December 2010 and is still ongoing. From the beginning of round three until January 2011 submitters of the final candidates were allowed to make minor changes on their algorithms to incorporate improvements gained through public comments and internal reviews. NIST planned afterwards again an additional year for public comments. The final SHA-3 conference was held in March 2012. Submitters of the final candidates were invited to take a stand on comments to their algorithms. The winner of the competition is planned to be announced in late 2012[44, 48, 53].

Grøstl is one of the finalists of the SHA-3 competition and is used to compute a fixed-length message digest out of a message with variable length. During the SHA-3 competition all the authors were allowed to make once minor changes on their algorithms in order to incorporate improvements triggered by public comments and internal reviews. Due to that, the specification from the 31st of October, 2008 was adapted to the newer one from the 2nd of March, 2011. The former one is since then known as Grøstl-0 specification. The following algorithmic description is targeting the newer specification from the 2nd of

Figure 4.1: The Grøstl hash function.

March 2011. Differences to Grøstl-0 will be highlighted through an information field.

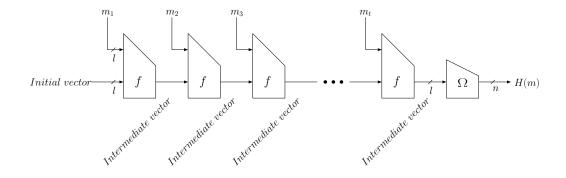

#### 4.1 Compression Function

Grøstl supports the variants Grøstl-224, Grøstl-256, Grøstl-512 and Grøstl-1024. The appended number represents the bit length of the message digest from now on called n. For Grøstl-224 and Grøstl-256 the input width represented by l is 512 bits whereas it is increased to 1024 bits for Grøstl-512 and Grøstl-1024. The basic concept of the hash function is shown in Figure 4.1 and reminds on a block cipher in cipher-block chaining mode (CBC). A padding function is inevitable for the same reason as for block ciphers (input width must be always of same size - either 512 bits or 1024 bits). Figure 4.1 assumes that the padding has been already applied. The message is furthermore split up in blocks of size 512 bits and 1024 bits, respectively. As no intermediate hash value is available for the first compression function f a well defined initial vector is used.

**Info:** In order to improve the overall security the initial vectors differ to the ones from the Grøstl-0 specification.

The output of the compression function represents an intermediate hash value acting in combination with the next message block as input to the subsequent compression function. After processing of the last message part an output transformation is applied to reduce the amount of bits to the desired digest size.

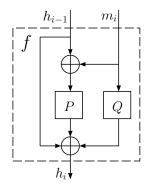

The compression function is shown in detail in Figure 4.2 and consists mainly of two blocks P and Q, both *l*-bit permutations. For the input to the Q-block no computational effort is required as the message part goes straight in. This differs to the P-block as there the input is the result of the intermediate hash value XORed with the input message. Both outputs are XORed to the intermediate hash value and form so the new one.

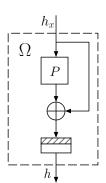

#### 4.2 Output Transformation

Figure 4.3 presents the output transformation  $\Omega$ . The intermediate hash value—output of the last compression function—is applied to the *P*-block and the result is afterwards XORed to it. Last but not least a truncation step is required as the message digest must have a size of 224, 256, 512 or 1024 bits. Therefore, as many leading bits as to form the desired digest size are cut off. For more information see the Grøstl specification [15].

Figure 4.2: The compression function f build upon a pair of *l*-bit permutations (P/Q).

Figure 4.3: The output transformation computes  $P(h_x) \oplus h_x$  and cuts off the leading bits to obtain the *n*-bit message digest.

#### 4.3 Permutations *P* and *Q* in Detail

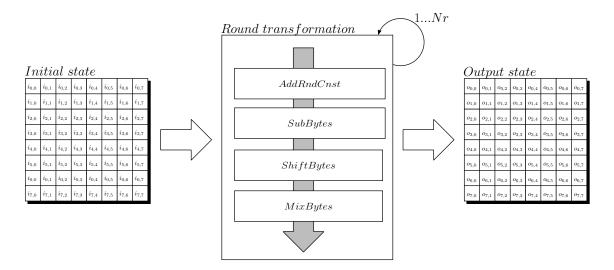

The *l*-bit permutations P and Q come each in two variants from now on named  $P_{512}$  and  $P_{1024}$  as well as  $Q_{512}$  and  $Q_{1024}$ . The reason for is the input size *l* which can be either 512 bits or 1024 bits depending on the variant used. For Grøstl-224 and Grøstl-256 an input size of 512 bits is mandatory whereas for the other two variants the size must be extended to 1024 bits. The inner structure of a permutation is shown in Figure 4.4 and is equal for P and Q. It consists of four round transformations: AddRoundConstant, SubBytes, ShiftBytes and MixBytes. The execution order is also presented in Figure 4.4. Beside, note the similarity between the permutation structure and the AES round transformation. The difference between the two variants of each permutation is the number of rounds and the behaviour of the four round transformations. For the small variants including Grøstl-224 and Grøstl-256 10 rounds are mandatory which increases to 14 rounds for the other two variants. The behaviour of the round transformations will be explained for Grøstl-224 and Grøstl-256 only. Details for the others can be found in the Grøstl specification, cf. [15].

#### 4.3.1 AddRoundConstant

The AddRoundConstant transformation adds a round-dependent constant to the state matrix. Equation 4.1 presents the round constant used for a P permutation whereas Equation 4.2 targets the Q permutation.

**Info:** In order to improve the overall security the round constants differ to the ones from the Grøstl-0 specification. In Grøstl-0, only a single byte gets modified for both permutations.

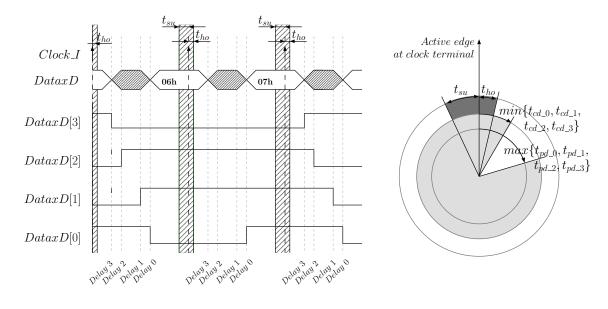

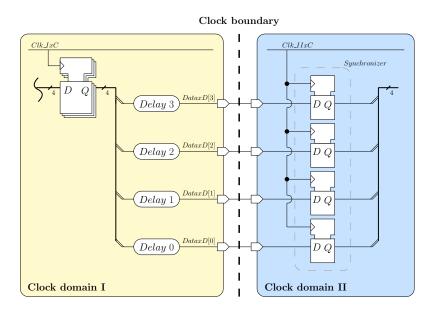

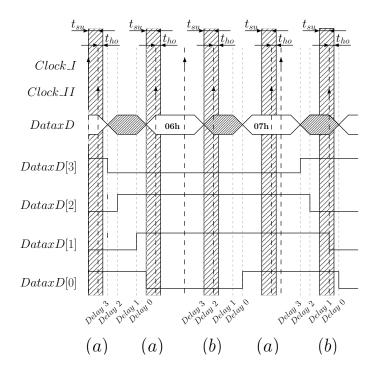

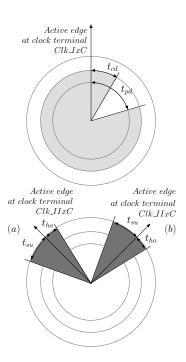

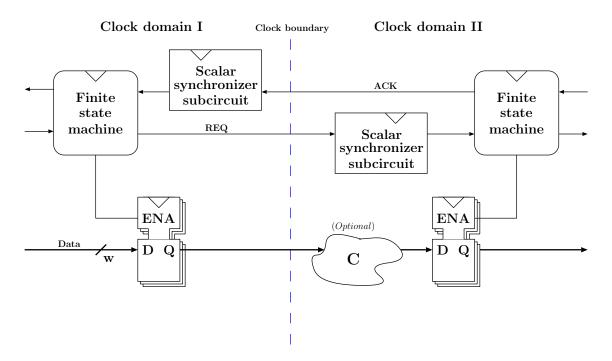

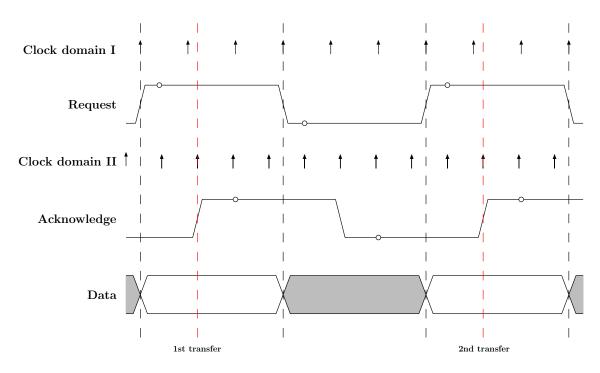

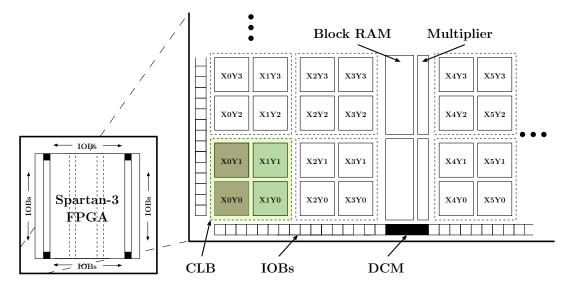

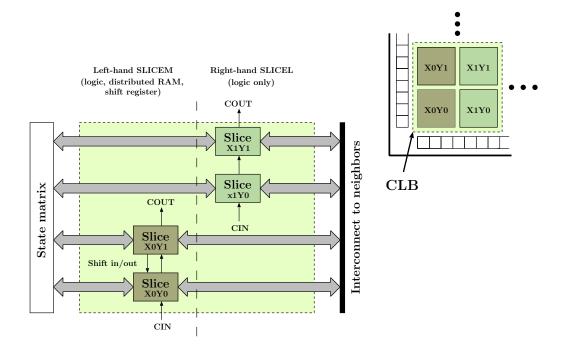

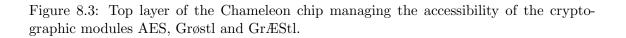

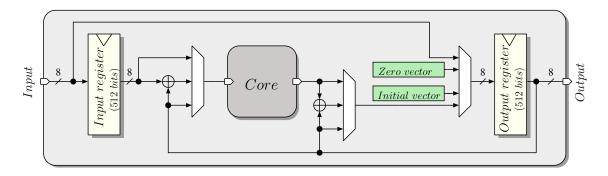

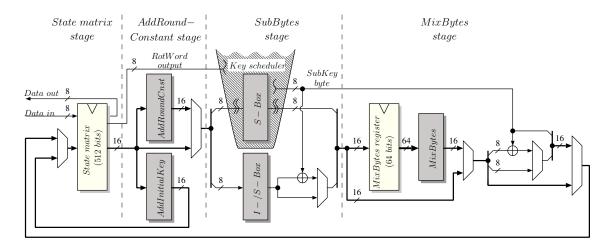

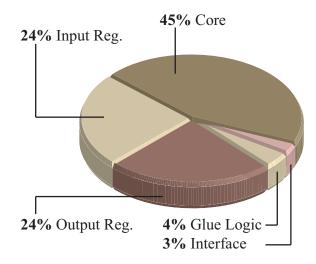

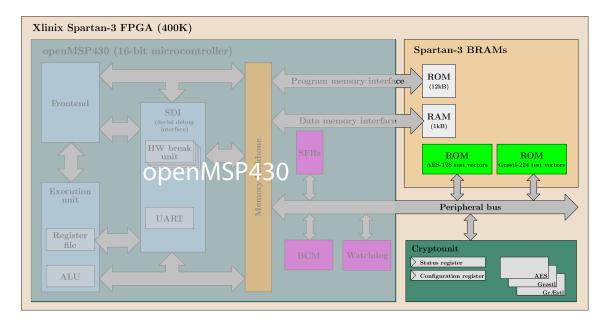

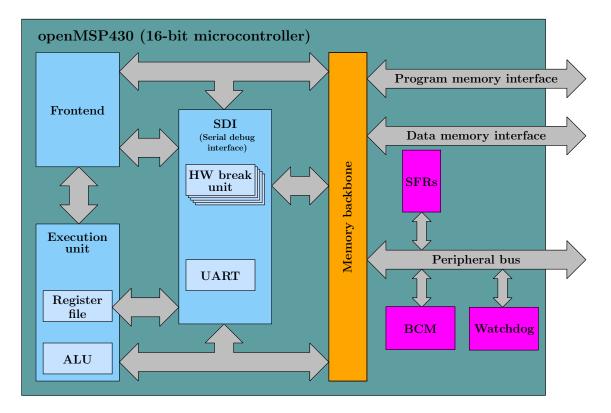

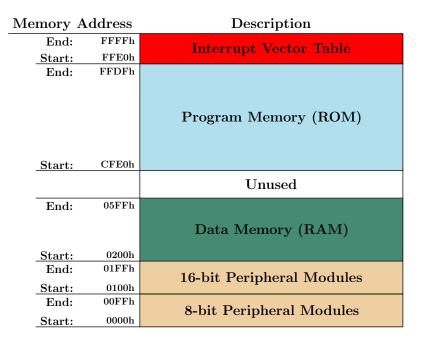

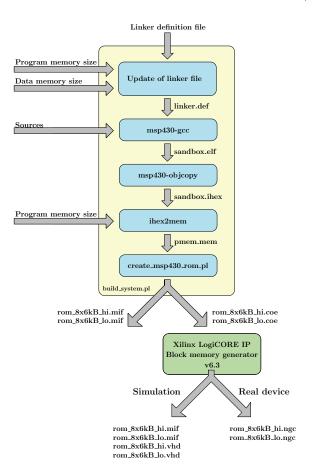

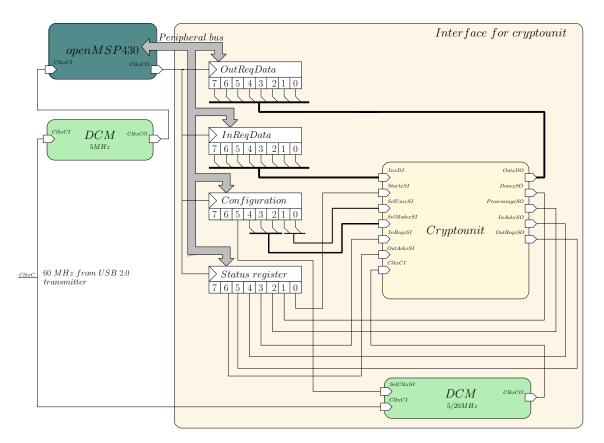

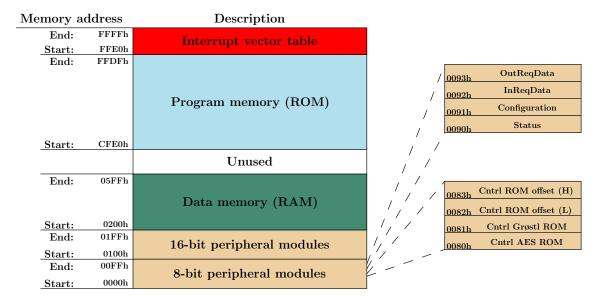

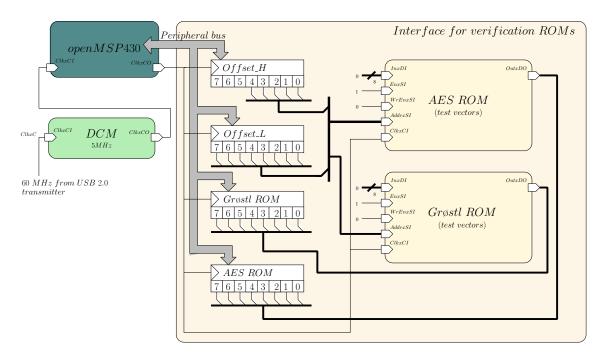

Figure 4.4: Structure of the P and Q l-bit permutation.