Master's Thesis MA684

# Efficient VHDL Implementation of Decimation Filters for a Next Generation Wireless Receiver

Ralph Gruber

Institute for Electronics Graz University of Technology Head: Univ.-Prof. Dipl.-Ing. Dr. techn. Wolfgang Pribyl

Supervisor: Univ.-Ass. Dipl.-Ing. Dr. techn. Peter Söser External Supervisor: Dipl.-Ing. Andreas Lessiak

Graz, May 2011

# Kurzfassung

Durch die rasche Entwicklung von Kommunikationstechnologie in den vergangenen Jahren hat auch der Bedarf an Systemen mit digitaler Signalverarbeitung zugenommen. In immer mehr Bereichen kommen Mixed-Signal-Schaltungen, die sowohl analoge als auch digitale Signale verarbeiten, zur Anwendung. Für hochauflösende  $\Sigma \Delta$  A/D-Umsetzer werden Dezimierungsfilter benötigt, welche die Abtastfrequenz verringern und Rauschen ausfiltern. Dieser an sich einfache Vorgang nimmt in einer integrierten Schaltung, bei der Größe und Stromverbrauch eine dominierende Rolle spielen, an Komplexität zu.

Ziel dieser Arbeit ist es, unterschiedliche Dezimierungsfilter für den Einsatz in einem linearen Empfänger zu untersuchen. Ein  $\Sigma\Delta$  A/D-Umsetzer mit 14 Bit Auflösung liefert dabei das digitale Datensignal. Darauf basierend werden verschiedene Filtertypen mit besonderen Eigenschaften diskutiert. Zwei effiziente Hardware Implementierungen werden vorgestellt sowie sämtliche Schritte vom Entwurf bis zur Verifikation beschrieben. Um die korrekte Funktionalität der Filter zu verifizieren und deren Verhalten zu vergleichen wurde eine Testumgebung aufgesetzt. Dort werden mit Hilfe von SNR Analysen die Implementierungen evaluiert. Um auch eine Größenabschätzung der Filter zu erhalten, wurden diese für eine 130 nm CMOS Technologie synthetisiert.

## Abstract

Digital signal processing in communication technology has strongly evolved in the recent years. The need for highly efficient and power aware digital systems has increased as their field of application has enlarged. Mixed signal systems with A/D and D/A converters are implemented in many devices nowadays. For high precision  $\Sigma\Delta$  A/D converters, decimation filters are required for noise filtering and sampling rate reduction. What sounds simple in the first instance, is an challenging task for integrated systems where size and power consumption matters.

Therefore the objective of this work is to evaluate decimation filters for application in a linear receiver architecture. A  $\Sigma\Delta$  A/D converter with 14 bits resolution delivers the digital input data to the decimation filter. Different types of decimation filters with various properties are compared and two efficient VHDL implementations are presented. Thereby design considerations as well as hardware implementation issues are discussed in detail. Finally a test bench for verification and evaluation of the implemented filters is presented. In order to compare the implementations regarding to their efficiency, SNR simulations are performed. To get an estimation of the required chip area the filters are synthesized for a 130 nm CMOS technology.

# STATUTORY DECLARATION

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

date

-----

(signature)

# Acknowledgement

This thesis was written from October 2010 to May 2011 at Institute for Electronics at Graz University of Technology in cooperation with Infineon Technologies Austria.

First I would like to thank my parents for supporting me during my years of study and making it possible for me to follow my own interests.

I want to thank my external supervisor Andreas Lessiak who supported me during my work at Infineon and always had good advice for my thesis.

Furthermore I have to thank my supervisor Peter Söser for his fast and uncomplicated help, especially at the end of my thesis.

Last but not least I want to thank all my friends and colleagues for making the years of study in Graz an unforgettable time with great memories.

# Contents

| 1        | Intr | oducti            | on                                                                                             |   |     |       |   |       | 1  |

|----------|------|-------------------|------------------------------------------------------------------------------------------------|---|-----|-------|---|-------|----|

|          | 1.1  | Motiva            | tion $\ldots$ | • |     |       |   |       | 1  |

|          | 1.2  | Object            | ives                                                                                           | • |     |       |   |       | 1  |

|          | 1.3  | Outlin            | e                                                                                              | • | • • | <br>• | • | <br>• | 2  |

| <b>2</b> | Lite | erature           | research                                                                                       |   |     |       |   |       | 4  |

|          | 2.1  | $\Sigma \Delta A$ | D Converters                                                                                   | • |     |       |   |       | 4  |

|          |      | 2.1.1             | Quantization                                                                                   | • |     |       |   |       | 5  |

|          |      | 2.1.2             | Oversampling                                                                                   | • |     |       |   |       | 7  |

|          |      | 2.1.3             | Noise Shaping                                                                                  | • |     |       |   |       | 7  |

|          |      | 2.1.4             | Continuous vs. Discrete Time $\Sigma\Delta$ A/D Converters                                     | • |     |       |   |       | 9  |

|          |      | 2.1.5             | Digital Filtering                                                                              |   |     |       |   |       | 9  |

|          | 2.2  | CMOS              | Technology                                                                                     |   |     |       |   |       | 11 |

|          |      | 2.2.1             | Power Consumption                                                                              | • | • • | <br>• | • | <br>• | 11 |

| 3        | Con  | cept              |                                                                                                |   |     |       |   |       | 13 |

|          | 3.1  | Overvi            | ew                                                                                             |   |     |       |   |       | 13 |

|          | 3.2  | Archit            | ecture                                                                                         | • |     |       |   |       | 13 |

|          | 3.3  | Specifi           | cations                                                                                        | • |     |       |   |       | 14 |

|          | 3.4  | Decim             | ation Filters                                                                                  | • |     |       |   |       | 17 |

|          |      | 3.4.1             | Conventional FIR and IIR Filter Design                                                         | • |     |       |   |       | 18 |

|          |      |                   | 3.4.1.1 FIR Filter                                                                             | • |     |       |   |       | 18 |

|          |      |                   | 3.4.1.2 IIR Filter                                                                             | • |     |       |   |       | 20 |

|          |      | 3.4.2             | Cascaded Integrator Comb Decimation Filter                                                     | • |     |       |   |       | 22 |

|          |      |                   | 3.4.2.1 Characteristics                                                                        | • |     |       |   |       | 23 |

|          |      |                   | 3.4.2.2 Non-Recursive Structure                                                                | • |     |       |   |       | 26 |

|          |      |                   | 3.4.2.3 Recursive vs. Non-Recursive                                                            | • |     |       |   |       | 28 |

|          |      |                   | 3.4.2.4 CIC Sharpening                                                                         | • |     |       |   |       | 30 |

|          |      | 3.4.3             | Half-band Filters                                                                              | • |     |       |   |       | 33 |

|          |      | 3.4.4             | Wave Digital Filters                                                                           | • |     |       |   |       | 36 |

|          |      |                   | 3.4.4.1 Lattice Wave Digital Filter                                                            | • |     |       | • |       | 39 |

|          |      |                   | 3.4.4.2 Bi-Reciprocal Lattice Wave Digital Filter                                              | • |     |       | • |       | 41 |

| 4  | Ver   | ification                                      | <b>44</b> |

|----|-------|------------------------------------------------|-----------|

|    | 4.1   | Test Bench                                     | 44        |

|    |       | 4.1.1 Test Procedure                           | 45        |

|    |       | 4.1.2 Reference Channel Filter                 | 45        |

|    | 4.2   | SNR Analysis                                   | 46        |

|    |       | 4.2.1 Minimum Sinusoidal Error Method          | 46        |

|    |       | 4.2.2 Spectral Analysis with Coherent Sampling | 47        |

| 5  | Imp   | blementation                                   | 48        |

|    | 5.1   | Overview                                       | 48        |

|    | 5.2   | Tools and Design Flow                          | 48        |

|    | 5.3   | Sharpened CIC Filter                           | 49        |

|    |       | 5.3.1 Filter Design                            | 49        |

|    |       | 5.3.2 Bit-Widths                               | 51        |

|    |       | 5.3.3 Hardware Effort                          | 53        |

|    |       | 5.3.4 Filter Verification                      | 54        |

|    | 5.4   | CIC and Bi-Reciprocal LWDF                     | 55        |

|    |       | 5.4.1 Filter Design                            | 56        |

|    |       | 5.4.2 Bit-Widths                               | 57        |

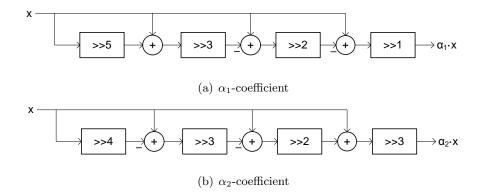

|    |       | 5.4.3 Coefficients                             | 60        |

|    |       | 5.4.4 Limit Cycles                             | 60        |

|    |       | 5.4.5 Hardware Effort                          | 61        |

|    |       | 5.4.6 Filter Verification                      | 62        |

| 6  | Res   | ults                                           | 64        |

|    | 6.1   | Comparison of Implementations                  | 64        |

|    | 6.2   | Filter Characteristics                         | 64        |

|    | 6.3   | SNR Simulations                                | 65        |

|    | 6.4   | Area and Power Estimations                     | 67        |

| 7  | Cor   | nclusion                                       | 69        |

|    | 7.1   | Summary                                        | 69        |

|    | 7.2   | Outlook                                        | 70        |

| Re | efere | nces                                           | 71        |

# List of Figures

| 1.1          | Low-pass filtering of a $\Sigma\Delta$ A/D converted signal                                                                                        | 2             |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| $2.1 \\ 2.2$ | Resolution vs. signal bandwidth of different A/D converter architectures [4] Structure of a first order $\Sigma\Delta$ A/D converter               | $\frac{4}{5}$ |

| 2.3          | Quantization error signal approximated to a sawtooth function                                                                                      | 6             |

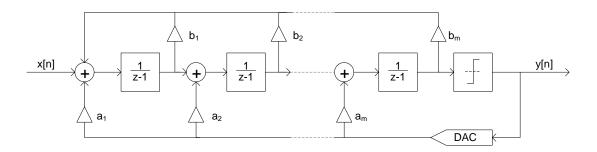

| 2.4          | Structure of an $M^{th}$ order $\Sigma \Delta$ A/D converter from [11]                                                                             | 8             |

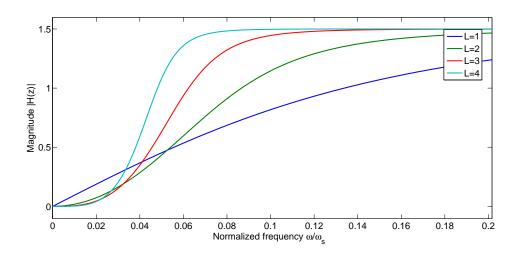

| 2.5          | Noise shaping property dependent on number L of loop filter stages                                                                                 | 8             |

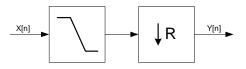

| 2.6          | Basic decimation filter built of low-pass filter and decimation stage                                                                              | 10            |

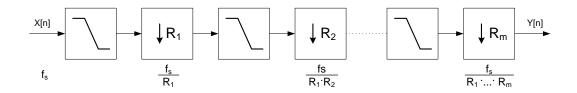

| 2.7<br>2.8   | Multi stage decimation filter with reduction of sampling frequency $f_s$<br>Charge transfer during switching activity in a CMOS equivalent circuit | 10            |

| 2.0          | diagram                                                                                                                                            | 12            |

| 3.1          | Analog front-end of the wireless receiver                                                                                                          | 14            |

| 3.2          | Digital signal processing in the wireless receiver                                                                                                 | 15            |

| 3.3          | Sigma delta ADC system transfer function and noise transfer function                                                                               | 15            |

| 3.4          | Frequency specification of the decimation filter                                                                                                   | 16            |

| 3.5          | Dynamic range specification                                                                                                                        | 17            |

| 3.6          | Frequency and phase response of the FIR equiripple filter                                                                                          | 19            |

| 3.7          | Frequency response and group delay of multiple IIR filter design methods .                                                                         | 21            |

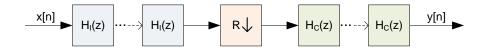

| 3.8          | $N^{th}$ order recursive CIC filter structure $\ldots \ldots \ldots$                | 23            |

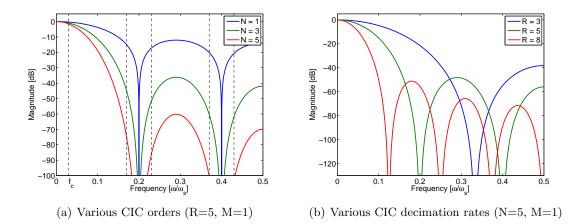

| 3.9          | Frequency response of a CIC filter with variation of order N and decimation                                                                        |               |

|              | rate R $\ldots$                                                                                                                                    | 24            |

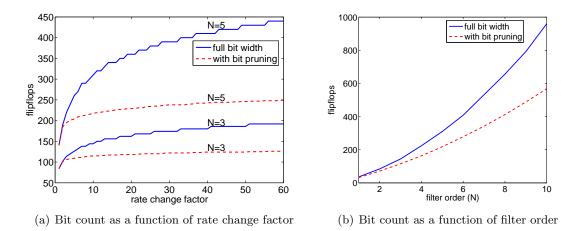

| 3.10         | Bit count comparison of implementations with and without pruning method                                                                            | 26            |

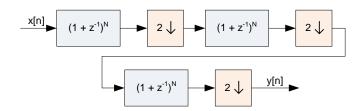

| 3.11         | $N^{th}$ order non-recursive CIC filter with rate decimation factor R=8                                                                            | 27            |

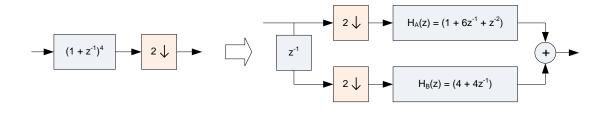

| 3.12         | Polyphase decomposition of one non-recursive CIC stage with order N=4 $$ .                                                                         | 27            |

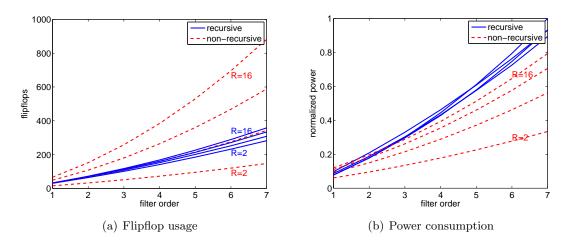

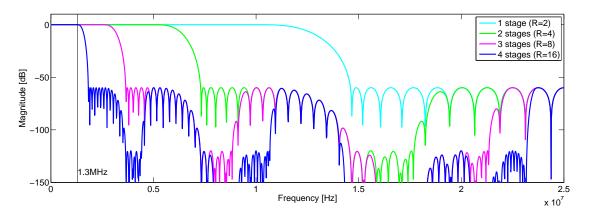

|              | Comparison of recursive and non-recursive CIC filter with $R=2,4,8,16$                                                                             | 29            |

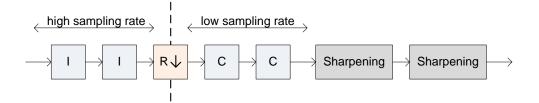

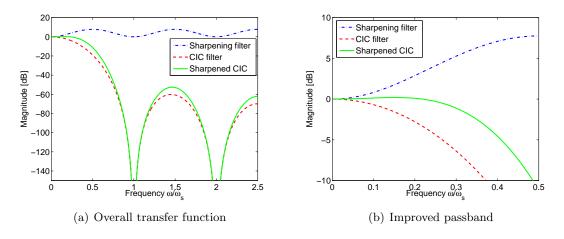

|              | Sharpened CIC filter with order N=2                                                                                                                | 31            |

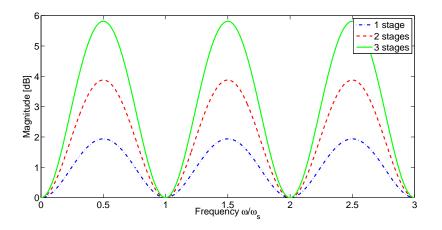

|              | Frequency response of sharpening filter                                                                                                            | 31            |

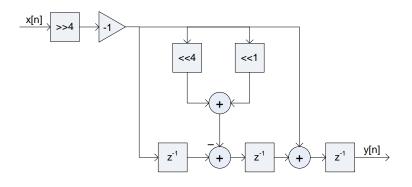

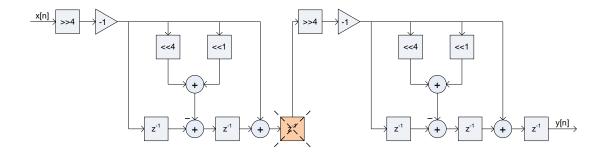

|              | Hardware implementation of one sharpening stage                                                                                                    | 32            |

|              | Register saving for implementations with multiple sharpening stages                                                                                | 32            |

|              | CIC sharpening filter: $N = 5$ , $R = 5$ , $M = 1$                                                                                                 | 32            |

|              | FIR half-band filter frequency response                                                                                                            | 33            |

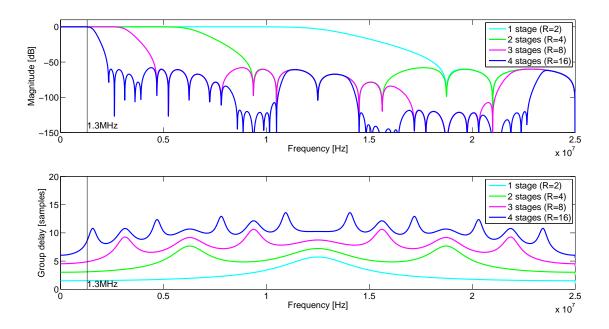

|              | Frequency response of cascaded FIR half-band filters                                                                                               | 35            |

|              | Frequency response and group delay of cascaded IIR half-band filters                                                                               | 35            |

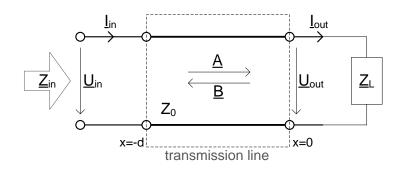

|              | Transmission line characteristics                                                                                                                  | 37            |

| 3.23         | $5^{th}$ order Lattice Wave Digital Filter structure $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                            | 40            |

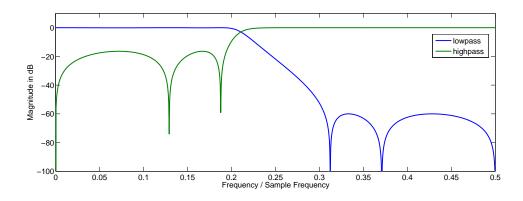

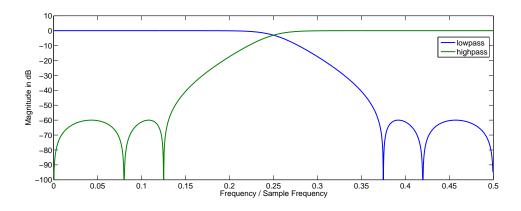

|      | Frequency response of a $5^{th}$ order LWDF                                                                                                                                                                                                       | 41 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

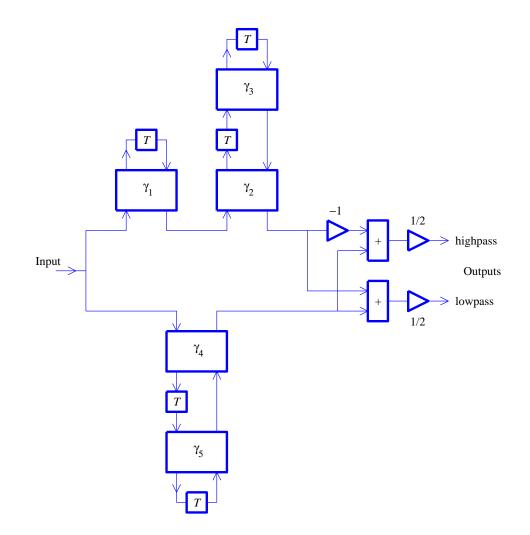

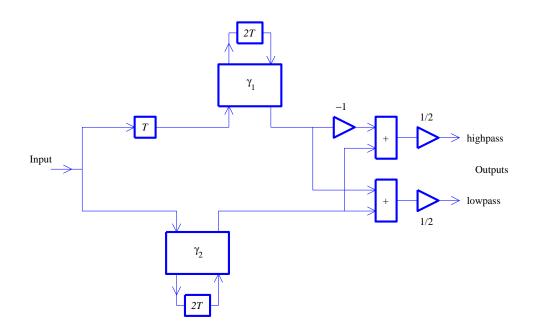

|      | Signal path of a $5^{th}$ order Bi-Reciprocal LWDF                                                                                                                                                                                                | 42 |

|      | Frequency response of a $5^{th}$ order Bi-Reciprocal LWDF $\ldots \ldots \ldots$                                                                                                                                                                  | 42 |

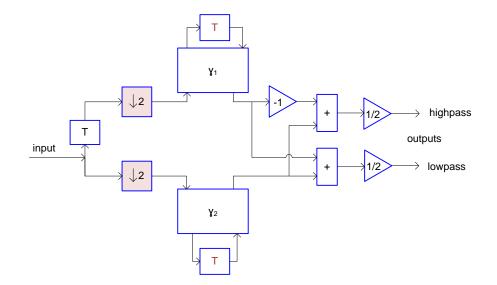

| 3.27 | $5^{th}$ order Bi-Reciprocal LWDF with rate decimation factor of two                                                                                                                                                                              | 43 |

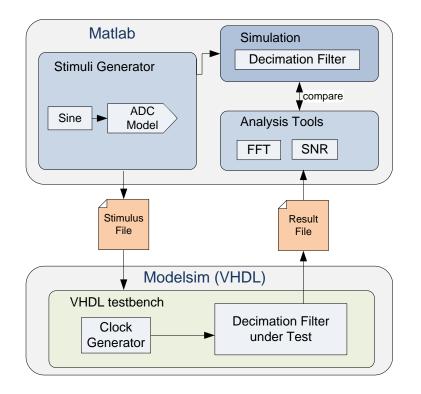

| 4.1  | Test environment for verification and evaluation of VHDL modules                                                                                                                                                                                  | 44 |

| 4.2  | Frequency response of the channel filter                                                                                                                                                                                                          | 46 |

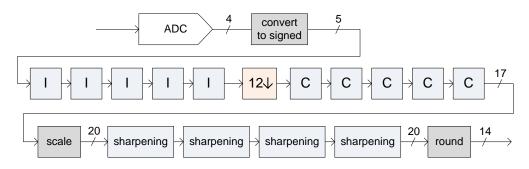

| 5.1  | Sharpened CIC filter block diagram                                                                                                                                                                                                                | 49 |

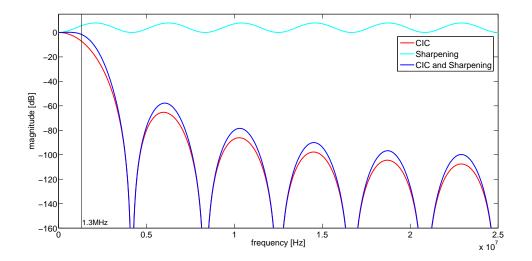

| 5.2  | CIC filter frequency response                                                                                                                                                                                                                     | 50 |

| 5.3  | Frequency response of CIC and sharpening filter separately and in combi-                                                                                                                                                                          |    |

|      | nation                                                                                                                                                                                                                                            | 50 |

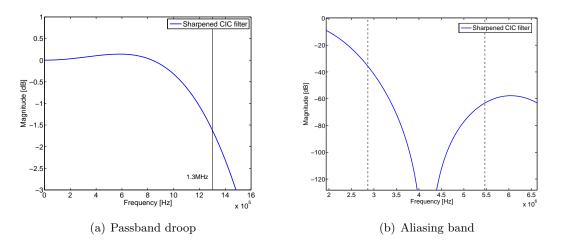

| 5.4  | Sharpened CIC filter frequency response                                                                                                                                                                                                           | 51 |

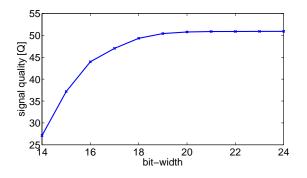

| 5.5  | SNR simulation for various bit-widths of the Sharpening stage                                                                                                                                                                                     | 52 |

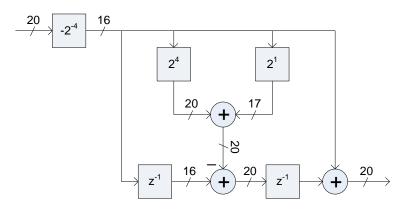

| 5.6  | Sharpening stage bit-widths                                                                                                                                                                                                                       | 53 |

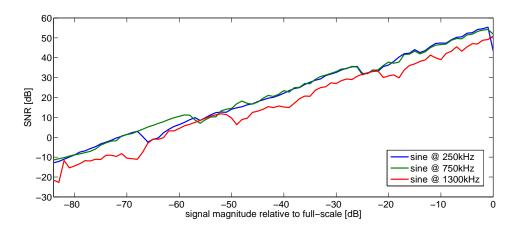

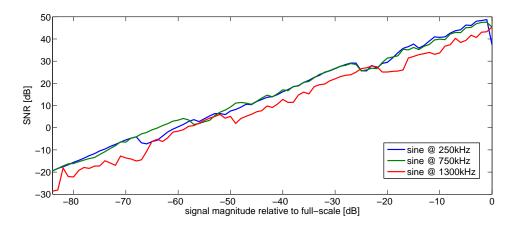

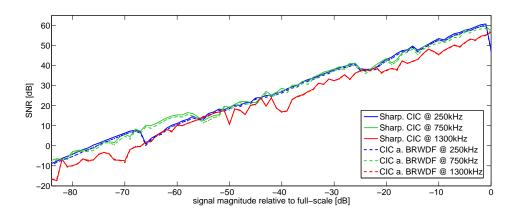

| 5.7  | SNR in relation to signal magnitude for three input signals with different                                                                                                                                                                        |    |

|      | frequencies                                                                                                                                                                                                                                       | 54 |

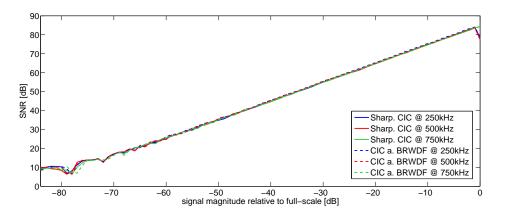

| 5.8  | SNR simulation of three input signals with different frequencies using a                                                                                                                                                                          |    |

|      | ${\rm channel\ filter\ }\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$ | 55 |

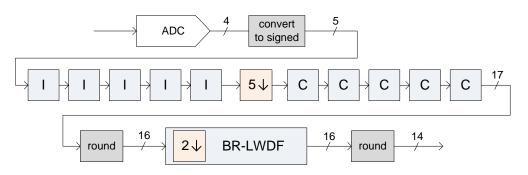

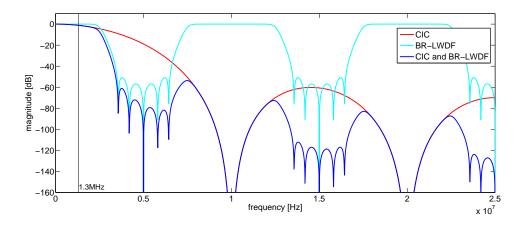

| 5.9  | CIC and BR-LWDF filter block diagram.                                                                                                                                                                                                             | 55 |

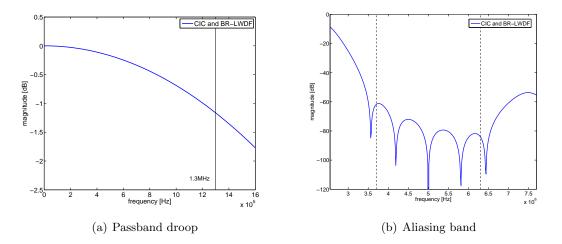

| 5.10 | Frequency response of each filter separately and combined                                                                                                                                                                                         | 56 |

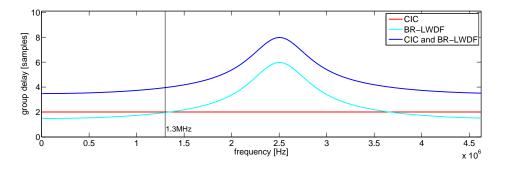

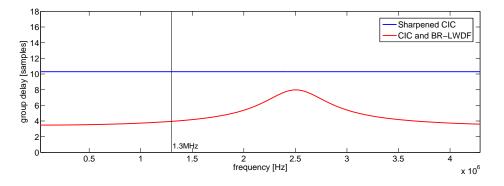

|      | Group delay of each filter separately and combined                                                                                                                                                                                                | 57 |

| 5.12 | CIC and BR-LWDF combined frequency response                                                                                                                                                                                                       | 58 |

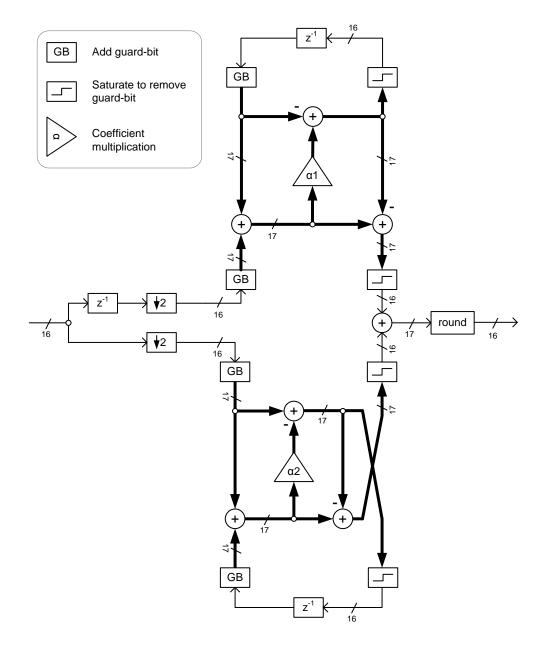

| 5.13 | Bi-Reciprocal LWDF hardware implementation                                                                                                                                                                                                        | 59 |

| 5.14 | Hardware implementation of the coefficients                                                                                                                                                                                                       | 61 |

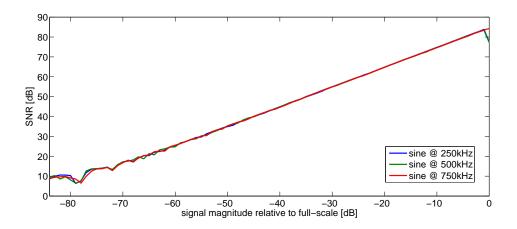

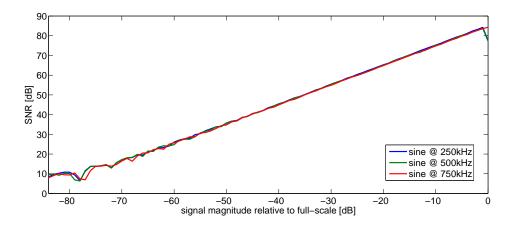

| 5.15 | SNR in relation to signal magnitude for three input signals with different                                                                                                                                                                        |    |

|      | frequencies                                                                                                                                                                                                                                       | 62 |

| 5.16 | SNR simulation for three input signals with different frequencies using a                                                                                                                                                                         |    |

|      | channel filter                                                                                                                                                                                                                                    | 63 |

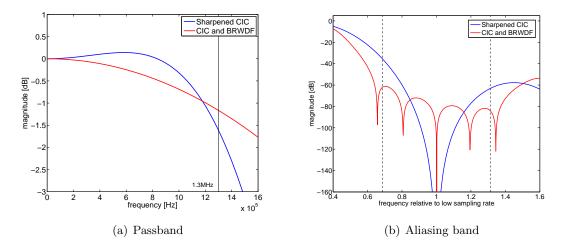

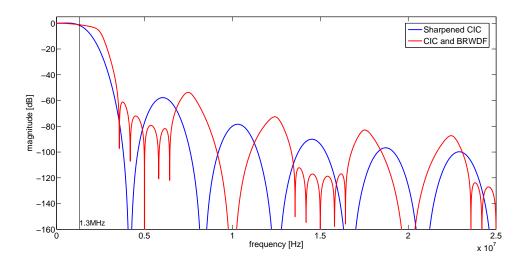

| 6.1  | Comparison of passband and aliasing bands                                                                                                                                                                                                         | 65 |

| 6.2  | Comparison of frequency response                                                                                                                                                                                                                  | 65 |

| 6.3  | Comparison of group delay                                                                                                                                                                                                                         | 66 |

| 6.4  | SNR simulations within 1.3 MHz frequency band                                                                                                                                                                                                     | 66 |

| 6.5  | SNR simulations with channel filter                                                                                                                                                                                                               | 67 |

# List of Tables

| 3.1 | Comparison between FIR and IIR filter properties                                                                        | 19 |

|-----|-------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Relationship between $\psi$ and Z-domain $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 39 |

| 4.1 | Parameters of the channel reference filter                                                                              | 45 |

| 5.1 | Parameters of the CIC filter                                                                                            | 49 |

| 5.2 | Bit-widths for each CIC filter stage                                                                                    | 52 |

| 5.3 | Usage of flip-flops(full-adders) in relation to clock rates                                                             | 54 |

| 5.4 | CIC filter parameters                                                                                                   | 56 |

| 5.5 | Bit-widths for each CIC filter stage                                                                                    | 58 |

| 5.6 | Bi-Reciprocal LWDF coefficients                                                                                         | 60 |

| 5.7 | Usage of flip-flops (full-adders) in relation to clock rates                                                            | 62 |

| 6.1 | Comparison of filter implementations                                                                                    | 64 |

| 6.2 | Comparison of chip area usage                                                                                           | 67 |

| 6.3 | Comparison of power consumption with the help of power indices                                                          | 68 |

# Chapter 1

# Introduction

## 1.1 Motivation

This work is developed in the context of an European Union project called *Pollux* where research for automotive electronics is expedited. *Infineon Technologies* is taking part in the project with a concept for a new linear wireless receiver for automotive applications. In a modern car there are several dozens of electronic control units communicating with each other. Rain sensors, window openers and temperature sensors are only some of the components mounted in a vehicle. In order to reduce costs and weight, wireless communication is preferred more and more over conventional wire lines.

A linear receiver architecture offers several advantages compared to a non-linear architecture. First of all lower bandwidths can be used by means of digital filtering which leads to higher sensitivity as well as higher ranges. Because of it's linear architecture this type of receiver is suitable for other modulation schemes like QAM or multi-level FSK. This makes the receiver suitable for a wider field of applications. Another advantage due to the digital implementation of filters is a lower production spread, no need for calibration and less test time.

The conversion from analog to digital signals requires high resolution in order to maintain the signal information. High sampling rates and large bit-widths make the digital signal processing a challenging task. A fixed point hardware implementation of digital filters involves the risk that overflows occur or that coefficient quantization leads to improper behavior. By carefully choosing proper filter architectures and bit-widths these problems can be circumvented. At the same time chip size as well as power consumption should be kept low. In a multi-rate digital signal processing chain, early decimation is the key to a power efficient implementation.

## 1.2 Objectives

Linear receiver architectures require the implementation of high resolution A/D converters in order to maintain the full signal information in the digital domain. In this project a  $\Sigma\Delta$  A/D converter with 14 bits resolution is used. ADC properties like noise shaping and high oversampling require the application of a decimation filter. Reduction of sampling rate and noise are the most important features of this filter.

The main objective of this work is to find an efficient hardware design for a decimation filter under consideration of chip area and power consumption. There are specifications for the receiver which have to be satisfied by the implementation. Because the decimation filter is the first digital signal processing block in the receiver it's performance is influencing the whole digital processing chain.

For the filter implementation VHDL should be used and the correct functionality has to be verified by means of simulations. For this reason a test bench was set up which allows various simulations of the VHDL code.

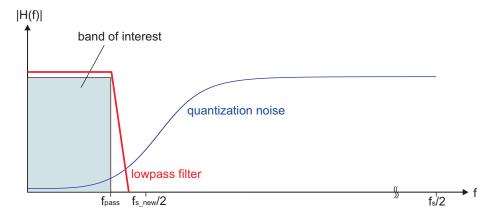

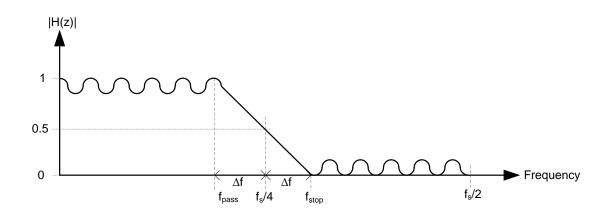

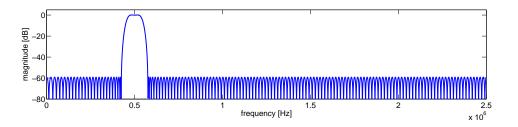

Figure 1.1, which shows the frequency spectrum of a  $\Sigma\Delta$  A/D converted signal, illustrates the process of decimation filtering. Due to the noise shaping property of the ADC, quantization noise is moved to higher frequencies. Therefore the signal within the band of interest can easily be separated from noise by low-pass filtering. The high oversampling of the signal is indicated by  $f_s$  which is much higher than the Nyquist frequency of the band of interest  $f_{pass}$ . Therefore it is reduced to a lower sampling frequency  $f_{s\_new}$ . The resulting signal still contains the whole information but got rid of unnecessary noisy frequency components.

Figure 1.1: Low-pass filtering of a  $\Sigma\Delta$  A/D converted signal

### 1.3 Outline

The main work starts with chapter 2 where literature research is done. In this chapter  $\Sigma\Delta$  A/D converters and their properties are discussed. This is important to get an understanding for the need of decimation filters. At the end of the chapter an overview of power consumption in the CMOS technology is given.

In chapter 3 the architecture and the specifications of the linear receiver are presented. They build the basis for the filter concept. In section 3.4 various filter types and design methods are discussed. The focus is concentrated on filter structures particularly suitable for rate decimation as well as efficient hardware implementations.

The verification process of the implemented filters is summarized in chapter 4. Test bench, setup and method are described. Additional functions used for simulation purposes are explained as well.

Chapter 5 describes the design process and implementation of two different decimation filters. They were implemented in VHDL and simulated with the test bench introduced before.

In chapter 6 the simulation results of both implementations are compared with each other in order to get to a conclusion which structure is more efficient. Area and power estimations as well as SNR simulations are performed.

At the end of the thesis in chapter 7 a summary and outlook is done.

# Chapter 2

# Literature research

# 2.1 $\Sigma \Delta A/D$ Converters

Analog-to-digital conversion is a key feature in nowadays communication systems and signal processing applications. Signals are converted from the analog domain to the digital for several reasons.

- Digital data is easier to process and store

- Digital signals are insensitive to environmental influences

- Digital signal processing is more flexible than analog processing

- Digital signals are not influenced by component tolerances or temperature coefficients

- Mostly digital filters need less chip area than their analog counterparts

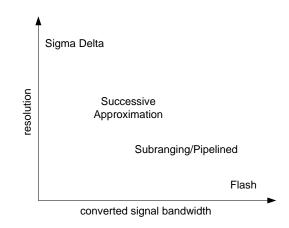

In this section the advantages of  $\Sigma\Delta$  A/D converters, particularly continuous time implementations, are investigated. Below there is a comparison of A/D converter architectures in terms of resolution and signal bandwidth.

Figure 2.1: Resolution vs. signal bandwidth of different A/D converter architectures [4]

From figure 2.1 it can be seen that  $\Sigma\Delta$  converters are best suited for low sampling rates and high resolution conversion whereas flash converters have low resolution at high sampling rates. So  $\Sigma\Delta$  ADCs are mainly deployed for high precision signal conversion of e.g. measured sensor data. Also in communication systems they are widely spread because of their high performance and low power implementations. The need for high performance A/D converters comes with a higher level of integration and higher degree of digitalization. By moving digital signal processing of receivers more and more towards the antenna, the performance requirements of the ADC grow. The demands on linearity and dynamic range are increasing. At the same time power consumption should be kept low to fulfill the requirements of battery based mobile devices.

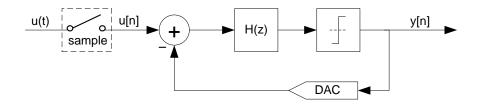

In figure 2.2 the structure of a sigma delta converter is depicted, it is composed of the following components:

- Integrator

- Quantizer

- 1 bit DAC

Figure 2.2: Structure of a first order  $\Sigma \Delta$  A/D converter

The loop transfer function H(z) in figure 2.2 is a simple integrator expressed as  $\frac{1}{z-1}$ . Basically the loop filter can be implemented in the discrete time or continuous time domain. Continuous time sigma delta converters are discussed in section 2.1.4 in more detail.

#### 2.1.1 Quantization

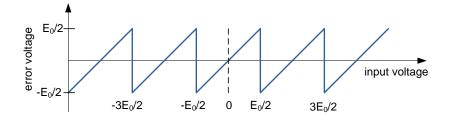

Quantization errors occur when input signals with infinite amplitude levels are mapped to a finite number of output values called quantization steps. In literature this quantization error is mostly described by a simplified noise model introduced by W. R. Bennett [5]. It approximates the real quantization error, the difference between input and quantized output, by a sawtooth function with amplitude  $E_0$  and slope s. This is accurate enough for most applications. In figure 2.3 the sawtooth error function e(t), which is expressed with equation 2.1, is depicted. So the root mean square error can be calculated by equation 2.2.

$$e(t) = st, -\frac{E_0}{2s} < t < \frac{E_0}{2s}$$

(2.1)

Figure 2.3: Quantization error signal approximated to a sawtooth function

$$\overline{e(t)^2} = \int_{\frac{-E_0}{2s}}^{\frac{E_0}{2s}} e(t)^2 dt = \frac{E_0^2}{12}$$

$$e_{rms} = \frac{E_0}{\sqrt{12}}$$

(2.2)

With this equation in mind an approximation for the Signal to Quantization Noise Ratio (SQNR) of A/D converters can be expressed (2.3). As input signal the rms value of a full scale sine s(t) is assumed. The number of output bits is denoted by N.

$$s_{rms} = \frac{E_0 \cdot 2^{N-1}}{\sqrt{2}}$$

$$e_{rms} = \frac{E_0}{\sqrt{12}}$$

$$SQNR = 20 \cdot \log_{10} \left(\frac{s_{rms}}{e_{rms}}\right) = 1.76 \, dB + 6.02 \cdot N \tag{2.3}$$

Because signal and noise function have a different signal form the value of 1.76 dB comes up. In literature [16] the quantization noise is often assumed to be uncorrelated to the input signal and equally distributed over the whole spectrum. This is not always true. In [15] it was shown that for single tone inputs and sampling rates with an integer multiple of the signal frequency, the error is correlated to the input. This leads to an concentration of quantization noise around the harmonic frequencies of the input signal. Although the mean value of the noise keeps the same, this has an impact on other measured data like the Spurious-Free Dynamic Range (SFDR) or the Total Harmonic Distortion (THD). But for most application scenarios where the input is not a spectrally clear single tone but more or less a band of frequencies summed with noise the assumption of uncorrelated and randomly spread noise is valid.

#### 2.1.2 Oversampling

In section 2.1.1 it was mentioned that quantization noise power can be assumed to be uniformly distributed over the whole spectrum for most cases. If the signal is oversampled, the quantization noise is scaled over a wider spectrum. Because the overall noise power has to stay the same, the noise per frequency unit decreases compared to Nyquist sampling. This fact is used to reduce the signal's in-band quantization noise. The higher the oversampling ratio the less noise is in the band of interest. Increasing the oversampling ratio M of a traditional A/D converter by a factor of four results in a SQNR change of  $+6 \, dB$  - or one bit - as equation 2.4 shows.

$$SQNR = 1.76 \, dB + 6.02 \cdot N + 10 \log_{10}(M) \tag{2.4}$$

For sigma delta converters the achievable SQNR calculation from [16] is shown in equation 2.5. Here the number of loop filter stages L has a strong effect on the SQNR because of the noise shaping ability which is discussed in the next section in more detail. Furthermore only an oversampling ratio M greater than  $\pi$  shows an improvement compared to traditional oversampled A/D converters.

$$SQNR = 1.76 \, dB + 6.02 \cdot N + (2L+1) \cdot 10 \log_{10}(M) + 10 \cdot \log_{10}(2L+1) - (2L) \cdot 10 \log_{10}(\pi)$$

(2.5)

#### 2.1.3 Noise Shaping

The quantization process at the output of the converter is strongly non-linear. To analyze its influence on the system transfer function we linearize the quantizer by replacing it with an additive white noise source. This noise is independent of the input signal and adds noise so that the output corresponds exactly to the next quantization level. Considering the sigma delta converter depicted in figure 2.2, the output Y(z) can be written as described in equation 2.6 where  $H(z) = \frac{1}{z-1}$  denotes the loop filter [11].

$$Y(z) = \frac{H(z)}{1 + H(z)} \cdot U(z) + \frac{1}{1 + H(z)} \cdot E(z)$$

=  $STF(z) \cdot U(z) + NTF(z) \cdot E(z)$  (2.6)

Noise transfer function and system transfer function derived from equation 2.6 result in equation 2.7.

$$NTF(z) = 1 - z^{-1}$$

$STF(z) = z^{-1}$  (2.7)

It can be seen that the output is a delayed version of the input signal plus the high-pass filtered noise, hence the noise is shaped and moved to higher frequencies while the input signal stays unchanged. For higher orders N the hardware effort scales linearly. The structure of a higher order  $\Sigma\Delta$  A/D converter is shown in figure 2.4. The order of sigma delta modulators plays an important role when it comes to noise shaping. Figure 2.5 shows that higher order modulators shape the noise more efficiently to higher frequencies. For every doubling of the oversampling ratio the SQNR improves by 6 L + 3 dB. This results in lower sampling frequency compared to lower order modulators [11].

**Stability Issues:** On the other hand stability issues rise for loop filter orders above two. Integrator overload is one of the main concerns. Thereby the output amplitude of the integrators next to the quantizer are overloading and the signal goes into saturation. This causes harmonic distortion in the output signal.

But also finding suitable poles and zeros for the transfer functions can become a sophisticated task. Further information on the topic of instability is found in [11].

Figure 2.4: Structure of an  $M^{th}$  order  $\Sigma\Delta$  A/D converter from [11]

Figure 2.5: Noise shaping property dependent on number L of loop filter stages

#### 2.1.4 Continuous vs. Discrete Time $\Sigma \Delta$ A/D Converters

In the previous sections it was mentioned that sigma delta modulators can be implemented with discrete time or continuous time loop filters. Now the implementation differences as well as advantages and trade offs are discussed.

Discrete time sigma delta modulators are build of loop filters which are often implemented in switched capacitor or switched current circuits [11]. The input signal is time discretized before it is integrated in the loop filters. Advantages of continuous time sigma delta modulators are:

- inherent anti aliasing filter

- higher sampling rates

- low power consumption

- no noise introduced by switched capacitors

One drawback of continuous time loop filters is their more sophisticated design. Compared to discrete time sigma delta converters continuous time implementations are considered to be insensitive against aliasing [16]. This results from the fact that the signal sampling happens at the output of the loop filter. So the signal is first low-pass filtered before it is sampled and aliasing is introduced. This way, spectral components around multiples of the sampling frequency  $M \cdot f_s$  are attenuated. After sampling, the aliased signal is fed into the quantizer and shaped by the feedback loop the same way quantization noise is processed. In contrast to discrete time modulators this anti aliasing filter comes with no additional effort. For higher order loop filters the anti aliasing performance rises because of the higher number of integrators [11].

Discrete time sigma delta converters sample the input signal in front of the loop filter. Therefore aliasing has already taken place when the loop filter processes the bit stream. That's why these modulators need additional analog anti-aliasing filters at their inputs. This contributes negatively to the implementation size and power consumption.

### 2.1.5 Digital Filtering

After converting the signal from analog to the digital domain the data is processed further by means of digital filtering. The goal of digital filtering is described by the following points:

- reduce oversampling

- prevent in-band aliasing introduced by decimation

- preserve the band of interest

- eliminate noise, especially the quantization noise of the A/D converter

#### CHAPTER 2. LITERATURE RESEARCH

The simplest decimation filtering structure would consist of a low-pass filter with subsequent decimation stage as shown in figure 2.6. It was proved in [20] and [25] that the same filter can be implemented more easily and with relaxed specifications in a multi stage filter approach. The main idea is to have multiple filters running at different sampling rates by factorizing the decimation rate R into m factors.

Figure 2.6: Basic decimation filter built of low-pass filter and decimation stage

$$R = R_1 \cdot R_2 \cdot R_3 \cdot \ldots \cdot R_m \tag{2.8}$$

Compared to a single filter design the advantage is a reduction of the sampling rate at an early stage in the filter chain. This has a positive effect on power consumption as the filters in the next stages are running at lower clock rates. Derived from equation 2.11 the power consumption can be assumed to reduce linearly with frequency. The following two sections give an overview of these practices.

Figure 2.7: Multi stage decimation filter with reduction of sampling frequency  $f_s$

**Low-pass Filtering:**  $\Sigma\Delta$  A/D converted signals are highly oversampled and contain quantization noise due to the conversion from analog to digital signals. But fortunately the noise is shaped to higher frequencies outside the wanted signal bandwidth. The first step of the digital processing has to deal with low-pass filtering. This filter, often called *anti-aliasing filter* in literature, attenuates spectral components situated around the decimated sampling frequency  $f_s$ . These frequencies would fold down into the band of interest  $f_{bw}$  as a result of decimation. Therefore it is crucial to suppress spectral components around  $f_s \pm f_{bw}$ .

**Decimation:** After low-pass filtering the sampling rate can be adapted. This is done by dropping each R'th sample. In a hardware design, down sampling can be realized by clocking a register at lower clock rate. That way no additional hardware is required and the subsequent circuit is clocked with the decimated clock what in turn reduces power consumption.

## 2.2 CMOS Technology

Complementary Metal Oxide Semiconductor Technology (CMOS) is the most common process technology used for integrated digital circuits nowadays. It is known to be very power efficient. In the following section the influences on power consumption in CMOS networks are discussed.

#### 2.2.1 Power Consumption

The total power consumption in CMOS processes is composed of static and dynamic power consumption as described in equation 2.9.

$$P_{tot} = P_S + P_D \tag{2.9}$$

Static power consumption is a consequence of current leakage in CMOS transistors. Although no switching activity is present a very small leakage current flows from  $V_{CC}$  to ground. This is expressed as the overall leakage current  $I_{leak}$  flowing into a circuit with supply voltage  $V_{CC}$ . The resulting dissipated power is described in equation 2.10.

$$P_S = V_{CC} \cdot I_{leak} \tag{2.10}$$

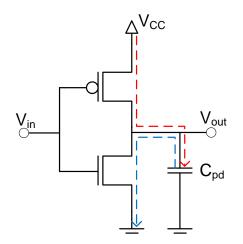

When it comes to dynamic power consumption we have to take several effects into account. One part is the switching current that has to load the output nodes of CMOS structures. This process is illustrated in figure 2.8. Another contribution to the dynamic power consumption is the short-circuit current  $I_{SC}$ . It originates from switching NMOS and PMOS transistors with finite slope at the same time. A short-circuit exists and current is flowing for a short period.

In CMOS technology the dynamic power consumption is calculated by equation 2.11.  $C_{pd}$  defines the power-dissipation capacitance,  $V_{CC}$  the voltage supply and  $f_0$  the switching frequency. It can be seen that the supply voltage  $V_{CC}$  has the largest impact on the power consumption followed by the switching frequency.

$$P_D = P_{switching} + P_{short-circuit}$$

$$P_D = C_{pd} \cdot V_{CC}^2 \cdot f_0 + V_{CC} \cdot I_{sc} \cdot f_0$$

(2.11)

Figure 2.8: Charge transfer during switching activity in a CMOS equivalent circuit diagram

# Chapter 3

# Concept

## 3.1 Overview

This chapter gives an overview on the design process of the digital decimation filter. To get a deeper understanding of the overall system where the decimation filters should be applied, the receiver architecture is introduced. Afterwards the specifications of the filter are formulated. They depend on different properties of the whole signal processing chain and must be kept in mind during the design process.

Beside these specifications there are other objectives like chip area and power consumption that should be satisfied. The goal of this chapter is to find a concept for decimation filters which comply with the system requirements and at the same time have low power consumption and small size. Different implementations are summarized and their advantages and disadvantages are compared.

## **3.2** Architecture

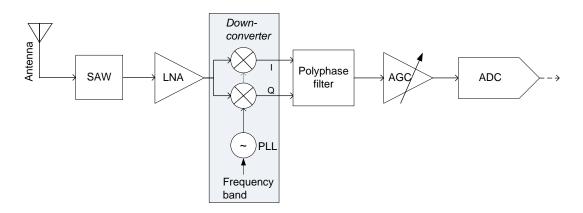

Now the proposed receiver architecture for the wireless receiver is presented. The block diagrams in figure 3.1 and 3.2 show the main structure of the linear receiver. The concept involves one  $\Sigma\Delta$  A/D converter quite early in the signal processing chain so that the vast majority of processing is done in the digital domain. First the analog and then the digital architecture is described in more detail.

Analog Processing: In the analog front-end the signal, received from the antenna, is filtered by a broadband SAW filter with high stopband attenuation. It belongs to the group of mechanical filters and is connected to the receiver externally. Then the signal is amplified by a Low Noise Amplifier (LNA) before it is down converted to an Intermediate Frequency (IF). To achieve a simple mixer structure and to avoid additional circuitry for image suppression, a Hartley image reject down converter is used. By mixing the RF signal with a 90° phase-delayed sinus, real and quadrature signals (I and Q) are generated. The polyphase filter does passband filtering on both of the two signals and introduces an additional 90° phase-shift on one of them. This results in an inverse image component which is completely extinguished when both signals are added together. Under the assumption that the circuit components have no tolerances this would be true. Under real conditions the image is not perfectly suppressed.

The next stage in the analog domain is an Automatic Gain Control (AGC) which controls the dynamic range of the A/D converter. By adjusting the signal strength, the input of the sigma delta converter should be kept in range. This is necessary to avoid clipping and nonlinear side effects in the sigma delta modulator when full scale signals are converted. The last analog stage in the architecture is the continuous time  $\Sigma\Delta$  A/D converter. With its inherent anti-aliasing filter property, discussed in section 2.1.4, further analog filtering can be neglected at this stage.

Figure 3.1: Analog front-end of the wireless receiver

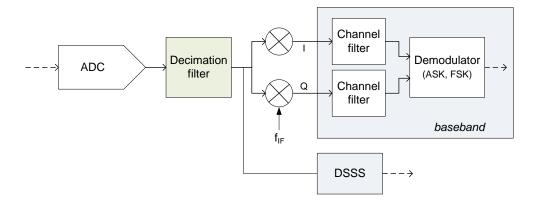

**Digital Processing:** The output of the  $\Sigma\Delta$  A/D converter is strongly oversampled and quantization noise is introduced during conversion. Therefore the first digital filter's purpose is down sampling and removing the shaped quantization noise. The further signal path depends on the receiver application. In the case of FSK or ASK modulation the signal is complex down-converted from its intermediate frequency to baseband. Then the real and quadrature path is channel filtered and further decimated. Afterwards FSK or ASK demodulation is done.

Another application of the receiver is Direct Sequence Spread Spectrum (DSSS) where the signal is processed in a separate path. This is an optional parallel signal processing unit that uses the decimation filter output as input signal. The whole digital signal path is illustrated in the block diagram in figure 3.2.

### 3.3 Specifications

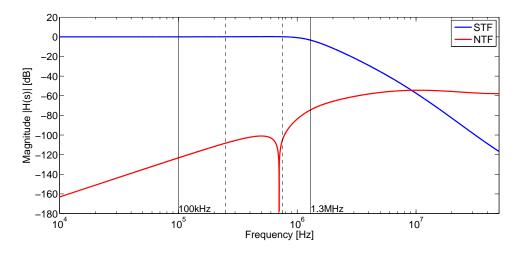

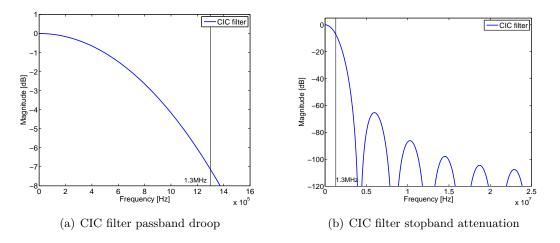

A/D Converter: Figure 3.3 shows the system transfer function (STF) as well as the noise transfer function (NTF) of the continuous time sigma delta converter which was designed for use in this linear receiver. It can be observed, that through noise shaping the band of interest, which ranges from 250 kHz to 750 kHz, has very low noise components. Even the DSSS application that uses frequencies up to 1.3 MHz has at least 60 dB noise attenuation. An optimization of the NTF was done by placing one zero around 700 kHz.

Figure 3.2: Digital signal processing in the wireless receiver

In this way the highest noise amount in the band of interest is additionally reduced.

The system transfer function depicts a characteristic low-pass curve. This is explained by the inherent anti-aliasing filter in continuous time sigma-delta converters. The cut-off frequency around 1.3 MHz is specified for DSSS applications.

Figure 3.3: Sigma delta ADC system transfer function and noise transfer function

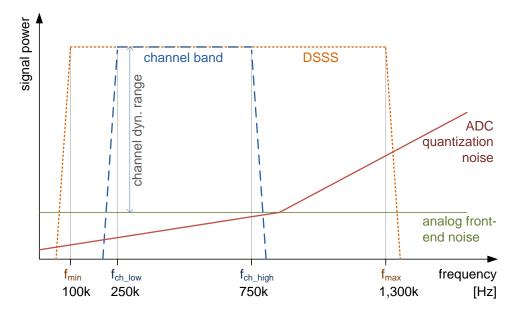

**Frequency Band:** The properties of  $\Sigma\Delta$  A/D converters have been discussed in detail in section 2.1. With this knowledge we state the requirements of the decimation filters. In figure 3.4 the frequency specification of the digital receiver is depicted. This implies, that the signal has already been down-converted from radio frequency to the intermediate frequency (IF), or channel center frequency. The communication channel is placed within the channel band from 250 kHz to 750 kHz. The bandwidth should be variable between 10 kHz and 500 kHz for different applications. Optionally Direct Sequence Spread Spectrum should be implemented with the same architecture. This technique spreads the signal spectrum and therefore it is more robust against interferer. A bandwidth of 1.2 MHz is designated for DSSS mode ranging from 100 kHz up to 1.3 MHz. So the cutoff frequency of the low-pass filter in the decimation stage is specified with 1.3 MHz or higher to maintain frequencies required by DSSS. For the other case, where a channel is placed between 250 kHz and 750 kHz, the cut-off frequency could be even lower and consequently more quantization noise would be filtered. But this would require either one filter with adjustable cut-off frequency or two separate filters, one for each application. Two filters in parallel is no option when chip area should be kept small. Finding a filter structure in hardware that can be switched between two different states to satisfy different requirements is not trivial.

Figure 3.4: Frequency specification of the decimation filter

**Decimation Factor:** The decimation factor depends on two conditions. The first is the frequency specifications of the receiver defined in the previous paragraph. From sampling theory it is known that the minimum required sampling frequency is  $2 \cdot f_{max}$ , hence  $2 \cdot 1.3 MHz = 2.6 MHz$ . The sampling rate  $f_s$  of the A/D converter is 50 MHz, so the maximum possible decimation factor where the signal is not yet undersampled is calculated in equation 3.1.

$$R_{max} = \left\lfloor \frac{f_s}{f_{sig} \cdot 2} \right\rfloor = \left\lfloor \frac{50 \, MHz}{2.6 \, MHz} \right\rfloor = 19 \tag{3.1}$$

Second the decimation depends on constraints in the baseband down-converter. There an oversampling ratio of two is desired for better signal quality. As the channel band is specified from 250 kHz to 750 kHz, the highest possible frequency is 750 kHz with the Nyquist sampling rate  $f_{s_Nyq}$  of 1.5 MHz. To achieve an additional oversampling ratio of two the Nyquist frequency  $f_{s_Nyq}$  is doubled and results in the minimum sampling

frequency  $f_{s\_min}$ . Both,  $f_{s\_min}$  and the resulting maximum decimation factor  $R_{max}$  are calculated by equation 3.2.

$$f_{s\_min} = f_{s\_Nyq} \cdot 2 = 3 MHz$$

$$R_{max} = \left\lfloor \frac{f_s}{f_{s\_min}} \right\rfloor = \left\lfloor \frac{50 MHz}{3 MHz} \right\rfloor = 16$$

(3.2)

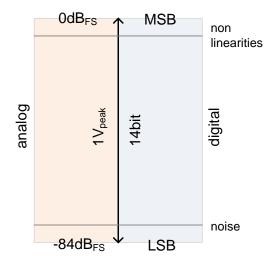

**Dynamic Range:** Specifications on the system's dynamic range are shown in figure 3.5. This can be verified with the help of equation 2.5 where the achievable SQNR of  $\Sigma\Delta$  A/D converters is calculated. In our case the sampling rate of the ADC is 50 MHz and the band of interest is specified with 1.3 MHz. This results in an oversampling ratio of approximately 19. With 4 bits at the ADC output and loop filter order of 4, the achievable SQNR results with equation 2.5 in 111 dB. This result reflects the dynamic range of the average quantization noise over the band of interest. When comparing this value with the noise transfer function in figure 3.3, one has to bare in mind that this is the average SQNR over the frequency band from zero to 1.3 MHz.

For input signals with maximum amplitude non-linearities occur within the A/D converter due to integrator overload. In the receiver architecture the Automatic Gain Control is responsible for adjusting the signal so that this is prevented. The Least Significant Bits (LSB) of the digitized signal contain the highest amount of noise.

Figure 3.5: Dynamic range specification

### **3.4** Decimation Filters

With the system specifications in mind suitable decimation filters are investigated. The filter should be implemented in VHDL and is later applied to a CMOS process for a wireless receiver integrated circuit. This requires a small and power efficient hardware implementation. Most straight forward filter design methods usually result in very large filter structures with a huge amount of coefficients. In a hardware implementation, the number of coefficients is tried to be kept low because they consume a lot of space. They have to be stored in registers or implemented in combinatorial logic. The first case requires hardware multipliers whereas the combinatorial logic implements the multiplication inherently.

First of all simple FIR and IIR filters, created with the Matlab Signal Processing Toolbox, are investigated. This is a very simple and fast approach to get a feeling for the filter complexity. Criteria for the filter complexity are the filter specifications which are configured by the filter designer:

- filter bandwidth

- transition bandwidth

- stop-band attenuation

- pass-band ripple

If the filter specifications are too tight, e.g. the filter bandwidth relative to the sampling frequency is very narrow, the stopband attenuation is too high or the passband ripple is too low, then the complexity as well as the filter order grows. So a trade off between suitable filter characteristics and complexity has to be found.

In the next step more sophisticated filter structures are investigated and multi stage approaches are introduced. The list of literature dealing with decimation filtering is quite long so the most promising techniques and tricks for sampling rate conversion are presented.

#### 3.4.1 Conventional FIR and IIR Filter Design

Filters with Finite Impulse Response (FIR) have some advantages over Infinite Impulse Response (IIR) filters that are of great demand in some applications. On the other hand IIR filters can be built with much smaller order than FIR filters to satisfy the same frequency specifications. Table 3.1 gives an overview on the main differences between FIR and IIR filters. When designing a filter, the trade offs always have to be kept in mind.

#### 3.4.1.1 FIR Filter

In literature [18] different methods for designing FIR filters are introduced, e.g. window design, Parks-McClellan algorithm, frequency sampling and weighted least squares. The most popular method probably is the algorithm proposed by Thomas Parks and James McClellan in 1972 [21]. It is a variation of the Remez exchange algorithm and makes use of the Chebyshev approximation theory. Most software packages available nowadays implement this algorithm.

| Property                | FIR        | IIR            |

|-------------------------|------------|----------------|

| number of coefficients  | high       | low            |

| stable                  | yes        | not inherently |

| phase                   | $linear^1$ | non-linear     |

| limit cycles            | no         | yes            |

| quantization influences | low        | high           |

<sup>1</sup> for symmetrical coefficients

Table 3.1: Comparison between FIR and IIR filter properties

The Parks-McClellan algorithm is used to estimate the order of a FIR equiripple lowpass filter that satisfies the system's specifications mentioned in section 3.3. The following design parameters are considered:

- Low-pass filter

- Sampling frequency: 50 MHz

- Cut-off frequency: 1.3 MHz

- Pass-band ripple: 0.5 dB

- Stop-band attenuation: 60 dB

- Transition band: 525 kHz

- Decimation factor: 16

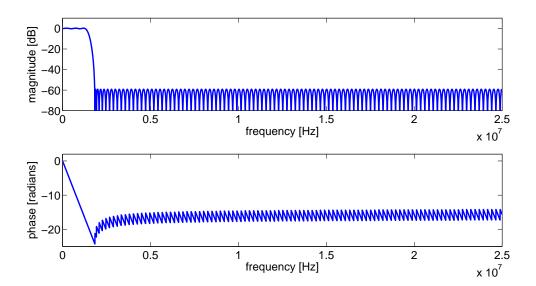

Figure 3.6: Frequency and phase response of the FIR equiripple filter

The transition band has been calculated to fit exactly the decimation factor. After decimation the Nyquist frequency is defined by equation 3.3. The transition bandwidth results from the fact that no aliasing should be introduced in the band of interest below 1.3 MHz. Equation 3.4 represents the frequency band which is outside the band of interest, where aliasing has no influence. To get the transition bandwidth of the filter this band has to be doubled and results in 525 kHz.

$$\frac{F_s/2}{16} = 1.5625 \, MHz \tag{3.3}$$

$$1.5625 MHz - 1.3 MHz = 0.2625 MHz \tag{3.4}$$

**Filter Order:** The result is a filter of order 210 that requires the same amount of coefficients to fulfill the specifications. To attain less pass-band ripple or even more stop-band attenuation the order would be even higher.

**Group Delay:** The filter has linear phase which means that the group delay is constant over the whole pass-band and no distortion is introduced. The constant delay is related to the order of the filter.

**Decimation Factor:** Rate decimation with a factor of 16 can be done after filtering without introducing aliasing to the band of interest. Therefore the transition band has been kept small and the transition center frequency  $f_{tc}$  has been chosen so that the new sampling frequency  $F_{s,new}$  (after decimation of 16) fulfills the condition in equation 3.5.

$$F_{s\_new} = 2 \cdot f_{tc} \tag{3.5}$$

**Coefficient Quantization:** When it comes to coefficient quantization the FIR transfer function is roughly the same for fixed point quantized coefficients with 12 bits as it is for a floating point implementation with 32 bit.

**Remark 1** Nevertheless a hardware implementation of this filter would be inefficient concerning area and power consumption. One has to take into consideration that the whole filter operates at the high frequency before decimation is done. From section 2.2 we know that with higher frequency comes higher power consumption. Summarized it can be said that this filter with linear phase suits the requirements but the very high order makes a low power hardware implementation not possible.

#### 3.4.1.2 IIR Filter

Infinite impulse response filters are in general designed by discretization of analog feedback filters which have well understood design methods. Bilinear transformation or the impulse invariance method are used for the transformation into the Z-domain. Examples of equivalent analog filters are: Elliptic, Chebyshev and Butterworth. Most software packages nowadays use optimized design methods that iteratively find the optimum filter coefficients for a set of design parameters. Those parameters are e.g. cut-off frequency, transition bandwidth, filter order, pass-band, stop-band ripple and more.

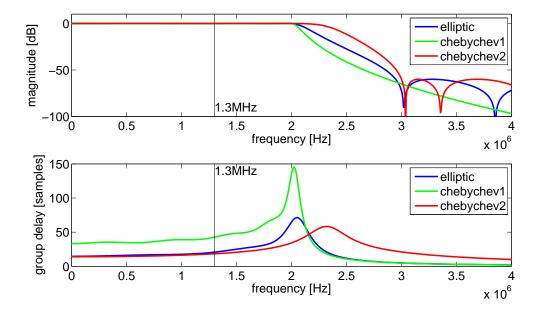

For comparing different IIR design methods the specifications from section 3.3 are used. Again Matlab is used to calculate the filter coefficients. Figure 3.7 shows frequency response and group delay of various IIR filter implementations with the following specifications:

- Low-pass filter

- Sampling frequency: 50 MHz

- Cut-off frequency: 2 MHz

- Pass-band ripple: 0.2 dB

- Stop-band attenuation: 60 dB

- Transition band: 1 MHz

- Decimation factor: 11

Figure 3.7: Frequency response and group delay of multiple IIR filter design methods

It has to be noted that these filter specification values vary from the values used for the FIR filter. The reason for this variation are the different filter properties especially the non-linear phase response of IIR filters that introduces distortions. For this reason the cut-off frequency is chosen higher so that the band of interest has *quasi* linear phase characteristics. This can be observed in figure 3.7. Consequently the decimation factor had to be reduced to a value of 11. Also the pass-band ripple was lowered in order to minimize the influence on the group delay. This adjustment had no impact on the filter order. Filter Order: The resulting filter orders are varying from 6 to 21. The Elliptic filter implementation (blue) is of order six and requires 13 coefficients, the two Chebychev implementations (green and black) have order 10. A Butterworth design was also done but without satisfying success. Its filter order would have been 21 but the resulting filter coefficients in the Z-domain were too small for Matlab to produce a reasonable filter transfer function. Therefore it has been excluded from this comparison. From the filter orders it can be concluded that IIR filters in general satisfy the specification with much less coefficients compared to FIR filters.

**Group Delay:** Because of distortions, introduced by non-linear group delay, the cutoff frequency was shifted to higher frequencies. The purpose of this shift is to get an approximately linear phase in the band of interest from 100 kHz to 1.3 MHz. For this band the group delay amounts to a maximum of 12 samples difference between two frequency points.

**Decimation:** The maximum decimation rate had to be reduced for the IIR filter as a consequence of the shifted cut-off frequency. Otherwise aliasing would occur during decimation because of the wider pass-band that would fold into the signal band. Equation 3.6 and 3.7 clarify the decimation factor considerations.  $F_{s\_new}$  is the sampling rate after decimation,  $f_{high}$  specifies the highest signal frequency,  $f_{st}$  the filter's stop-band frequency and R the decimation factor.

$$F_{s\_new} = 2 \cdot \left( f_{high} + \frac{f_{st} - f_{high}}{2} \right)$$

=  $2 \cdot \left( 1.3 + \frac{3 - 1.3}{2} \right) = 4.3 \quad [MHz]$  (3.6)

$$R = \left\lfloor \frac{F_s}{F_{s.new}} \right\rfloor = \left\lfloor \frac{50 \, MHz}{4.3 \, MHz} \right\rfloor = 11 \tag{3.7}$$

**Remark 2** With an elliptic IIR filter it is not possible to decimate the signal with the maximum factor because either distortion would be introduced or aliasing would occur. Thus a higher cut-off frequency and lower decimation rate is unavoidable. The lack of noise filtering has to be compensated with the channel filter that follows the decimation stage. This may lead to more complex filter structures there. Because group delay is the limiting factor for rate decimation a phase equalization filter would be the key for even higher decimation factors. But it has to be investigated if the additional costs for an (approximated) linear phase IIR filter really pays off compared to a smaller filter with the subsequent digital receiver blocks running on a higher sampling rate.

#### 3.4.2 Cascaded Integrator Comb Decimation Filter

The last section about FIR and IIR filters demonstrated that a straight forward implementation of these filters is not appropriate for our requirements, therefore alternative filter structures particularly suitable for rate decimation are investigated.

#### **3.4.2.1** Characteristics

The Cascaded Integrator Comb (CIC) filter was introduced by Eugene B. Hogenauer in 1981 [10]. Since then, it has become very popular in digital signal processing applications because of its simple and efficient implementation. It consists of integrators and comb sections only. By swapping these components, the filter can be used for rate decimation or interpolation. The main advantages of CIC filters are summarized in the following list:

- decimation factor can be changed without altering the filter structure

- multiplier free design

- no need for coefficient storage

- half the filter runs at the lower sampling rate

- finite impulse response

- linear phase

Disadvantages of CIC filter implementations are:

- large register bit-widths for high rate change factors or filter orders

- limited parameters to change the filter characteristics

- rather large passband droop for higher decimation factors and filter orders

The CIC filter consists of integrator and comb sections in a cascaded form. The system transfer function is shown in equation 3.8 where  $H_I(z)$  is the integrator's and  $H_C(z)$  the comb's transfer function, R the rate decimation, N the order and M the differential delay.

$$H_{I}(z) = \frac{1}{1 - z^{-1}}, \qquad H_{C}(z) = 1 - z^{-RM}$$

$$H(z) = H_{I}^{N}(z) \cdot H_{C}^{N}(z) = \frac{(1 - z^{-RM})^{N}}{(1 - z^{-1})^{N}}$$

(3.8)

The implementation of the filter is shown in figure 3.8. It can be seen that N integrators are followed by the same amount of differentiators with a rate decimation block in between.

Figure 3.8:  $N^{th}$  order recursive CIC filter structure

One parameter of the filter is the differential delay M. It controls the differentiation stage only and introduces additional zeros in the frequency response for higher values. In general this parameter is set to one or two. By increasing the filter order the number of integrators and comb sections is also equally increased. With higher order comes higher aliasing rejection at the cost of increased passband droop. The same side effect of passband droop is valid for the rate decimation parameter. To illustrate this behavior, figure 3.9(a) shows the transfer function of CIC filters with different orders and figure 3.9(b) shows transfer functions for various decimation factors.

Figure 3.9: Frequency response of a CIC filter with variation of order N and decimation rate R

Aliasing: The problem of aliasing, which is introduced by rate decimation, is also visualized in figure 3.9(a). The signal band ranges from zero to the cut-off frequency  $f_c$ . Those frequency bands that will fold down into the signal band are located at the zeros of the transfer function. They are marked with vertical dashed lines. Although the zeros heavily attenuate these bands and help minimizing aliasing there are always some frequency components suppressed less efficiently. The frequency component with the highest aliasing contribution is mostly situated where the first aliasing band cuts the main lobe of the transfer function.

**Filter Order:** In can be seen that higher filter orders attenuate the aliasing bands better than lower orders because they have much steeper transition bands. As a drawback, higher orders have lower passband cut-off frequencies. Consequently this leads to higher passband droop.

**Decimation Factor:** Figure 3.9(b) illustrates frequency responses of CIC filters with various decimation factors. It can be seen that for higher decimation rates the filter's passband gets narrower. The discussed effect of passband droop appears if the signal band is not scaled with the decimation factor.

In [10] two tables can be found that help choosing the filter parameters. One table lists passband attenuation values for different signal bandwidths and filter orders. The other table is listing aliasing attenuation values for certain filter orders under respect of signal bandwidth.

**Gain:** Due to their composition of integrators, CIC filters do have strong signal gain. The maximum gain can be calculated by equation 3.9, introduced by [10].

$$G_{max} = (R \cdot M)^N \tag{3.9}$$

The maximum register growth is then calculated by formula 3.10 [10] with  $B_{in}$  defining the number of input bits and  $B_{max}$  being the Most Significant Bit (MSB).

$$B_{max} = \left\lceil N \cdot \log_2(R \cdot M) + B_{in} - 1 \right\rceil \tag{3.10}$$

**Bit Pruning:** With this maximum number of bits at each stage the signal can be represented without overflows because  $B_{max}$  is an upper bound for register growth. This means that the number of bits necessary at each stage can be further reduced. Therefore an appropriate mechanism has been introduced in [10]. The main idea behind this theory is that the process of quantizing the signal at the output stage from  $B_{max}$  bits to the desired output length introduces the same amount of quantization error as if the signal bit-width was pruned already inside the 2N filter stages. There exists a total of 2N + 1 error sources introduced by bit pruning. 2N sources occur at the input of the stages and one error appears when truncating or rounding the last stage's result to fit into the output register. A distinction between rounding and truncation is not necessary because it was shown by the author that the error statistics of both operations are the same except for the first stage and the output register. In most implementations full precision is used in the first stage and rounding is done at the output.

An example should illustrate the bit pruning method. A filter with order 5, rate change factor 10 and differential delay 1 is assumed. Input and output registers should be 14 bits wide. The determination of the maximum bit-width  $B_{max}$  is done by equation 3.10. The pruned bit-width vector  $B_{pruned}$  is calculated with the help of Hogenauer's formulas described in [10].

$$B_{max} = \begin{bmatrix} 5 \cdot log_2(10 \cdot 1) + 14 \end{bmatrix} = 31$$

$$B_{pruned} = \begin{bmatrix} 31 & 27 & 25 & 23 & 21 & 20 & 19 & 18 & 17 & 17 \end{bmatrix}$$

(3.11)

In equation 3.11 the effective number of bits saved per stage, when applying the pruning method, is shown. The vector  $B_{pruned}$  represents the bit count from the first integrator stage to the last comb stage (2 N). All together the bit count was reduced from  $B_{max} \cdot N = 310$  to 218 bits. This means a saving of 92 bits. The example also illustrates that the first stage was not truncated and it can be observed that the bit-width is reducing from the first to the last stage. For different rate change factors the flipflop effort is shown in figure 3.10(a). Input and output registers are 14 bits wide. It can be seen that the bit pruning method has an remarkable impact on the size of a CIC filter. In figure 3.10(b) it is shown that with higher filter orders also the profit of this method grows.

Figure 3.10: Bit count comparison of implementations with and without pruning method

#### 3.4.2.2 Non-Recursive Structure

In the previous section the recursive CIC structure with integrator and comp sections has been introduced. Now the system function from equation 3.8 is expressed as geometric series to get the non-recursive structure representation shown in equation 3.12.

$$H(z) = \left[\sum_{k=0}^{RM-1} z^{-k}\right]^N = (1 + z^{-1} + z^{-2} + \dots + z^{-RM+1})^N$$

(3.12)

This implementation has no more feedback loops and therefore minimizes register growth and the need for very large registers. By factorizing equation 3.12 we get the expression in 3.13. The decimation factor has to be an integer power of two  $R = 2^{K}$  with a positive integer K.

$$H(z) = (1+z^{-1})^N \cdot (1+z^{-2})^N \cdot (1+z^{-4})^N \dots (1+z^{-2^{K-1}})^N$$

(3.13)

This factorization allows us to implement the filter with K stages, each having a rate decimation factor of two. Compared to the recursive implementation this form has multiple rate decimations along the signal path and not only one centered in the middle of the filter. In this way the sampling rate is constantly reduced throughout the signal path. In [18] it was mentioned that the power consumption for this implementation is lower for filter orders greater than three and rate change factors above eight. Figure 3.11 shows the non-recursive implementation for a  $N^{th}$  order CIC filter with rate decimation factor of eight and a differential delay of one. The decimation factor R can be represented as  $8 = 2^3$ , so three structures are necessary for the implementation.

Figure 3.11:  $N^{th}$  order non-recursive CIC filter with rate decimation factor R=8

When the transfer functions of these stages are investigated it can be seen that they are all the same. The higher order polynomials in the second and third stage have been reduced by the rate decimation stage before. Therefore it is essential for the decimation factor to be an integer power of two, otherwise this advantageous factorization can not be performed in this way. Another approach based on the factorization of the decimation factor into prime numbers may also be applied. This method is explained in [18]. Consequently the decimation factor can be chosen arbitrarily and the total non-recursive filter is composed of stages where the respective rate change is equal to the prime factors.

**Polyphase Decomposition:** The next step toward a more efficient implementation is the so called polyphase decomposition. This method helps reducing sampling rate at an early stage in the signal path. Thereby a transfer function is decomposed into two separate functions that can be evaluated in parallel because they are completely decoupled from each other. Afterwards they are added again to get the overall result. Applied to each non-recursive stage, this would look like depicted in figure 3.12 for a  $4^{th}$  order CIC filter. The equivalent transfer function is derived in equation 3.14.

$$H(z) = (1 + z^{-1})^4 = 1 + 4z^{-1} + 6z^{-2} + 4z^{-3} + z^{-4}$$

= (1 + 6z^{-2} + z^{-4}) + (4 + 4z^{-2}) \cdot z^{-1}

= H\_A(z) + H\_B(z) \cdot z^{-1} (3.14)

Figure 3.12: Polyphase decomposition of one non-recursive CIC stage with order N=4

**Implementation Issues:** The result of factorization and polyphase decomposition has following advantages and trade offs. Obviously the advantage of this structure is the rate