Roman Gerhard Silberschneider

## **Replay Resistant Secure Boot for Industrial Internet of Things Devices**

### Master's Thesis

to achieve the university degree of

Master of Science

Master's degree programme: Information and Computer Engineering

submitted to

### Graz University of Technology

Supervisor Thomas Unterluggauer

Evaluator Prof. Stefan Mangard

Institute of Applied Information Processing and Communications

Graz, July 2018

This document was written with Vim, is set in Palatino, compiled with  $pdf \square T_E X_{2e}$  and  $\square D_{1e}$ .

The LATEX template from Karl Voit is based on KOMA script and can be found online: https://github.com/novoid/LaTeX-KOMA-template

## Affidavit

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZONLINE is identical to the present master's thesis.

Date

Signature

## Abstract

The importance of the Industrial Internet of Things (IIoT) is increasing rapidly. IIoT devices live in production environments as well as in the public infrastructure and hence typically contain security-relevant software that is responsible for controlling critical tasks. Their deep integration into the environment, however, often allows attackers to gain physical access to IIoT devices. This physical access represents a huge attack surface for these devices. In particular, memory safety attacks, replay attacks, and side-channel attacks are serious threats to the software in the IIoT. For example, an attacker can exploit a memory safety vulnerability in the software to take control of a device. To repair these software vulnerabilities, vendors hence continuously create and deploy security updates. However, an attacker with physical access can revert these updates by using replay attacks, where they force a device to use an old and flawed version of the software. Even further, an attacker can use side-channel attacks to learn data processed on the device. These side-channel attacks, for example, allow to learn cryptographic keys used by mechanisms that aim to protect the confidentiality and authenticity of software executed on these devices, such as secure boot. Eventually, all these attacks threaten the software executed on an IIoT device and therefore the processed data as well. As a result, the whole IIoT system is endangered.

In this thesis, we improve the security of IIoT devices by presenting a bootloader concept that prevents replay attacks. The bootloader uses secure storage, located in a Trusted Platform Module (TPM), to verify that the latest firmware version is being loaded. This verification is based on a cryptographic hash calculated over the encrypted firmware image that represents a unique identifier of the version. This value is stored inside the TPM and compared to the hash of the loaded image on every system boot. After

successful verification, the firmware image is decrypted. To protect the decryption against side-channel attacks, we use a leakage-resilient encryption scheme. We use the modern programming language Rust to prevent against memory safety issues. With a proof-of-concept implementation running on a physical device, we verify the practical feasibility of the bootloader concept.

**Keywords:** Secure Boot, Replay Attacks, Side-Channel Attacks, Memory Safety, Rust

## Kurzfassung

Das Industrielle Internet der Dinge (IIoT) verbreitet sich zunehmend und wird direkt in unsere Umwelt integriert. Aus diesem Grund bieten IIoT Geräte eine große Angriffsfläche. Im Speziellen können Angreifer Schwachstellen in der Software ausnutzen. Solche Schwachstellen werden mit Sicherheitsupdates zwar behoben, jedoch kann ein Angreifer mit physikalischem Zugriff ein eingespieltes Update mit einer sogenannten Replay Attacke rückgängig machen. Weiters kann ein Angreifer Seitenkanalinformationen nutzen um im Gerät verarbeitete Daten zu extrahieren. Besonders interessant sind dabei kryptographische Schlüssel, wie sie zum Beispiel für verschlüsselte Firmware verwendet werden. Mit den genannten Angriffen kann ein Angreifer die volle Kontrolle über ein Gerät übernehmen und so auch das gesamte IIoT System gefährden.

Wir verbessern in dieser Arbeit die Sicherheit von IIoT Geräten indem wir ein Bootloader Konzept zur Verhinderung von Replay Attacken vorstellen. Dafür wird über die verschlüsselte Firmware ein kryptographischer Hash berechnet und in einem sicheren Speicher abgelegt. Als sicherer Speicher dient uns ein Trusted Platform Module (TPM). Bei jedem Systemstart wird der Hash der geladenen Firmware berechnet und mit dem gespeicherten Wert verglichen. Nur bei Gleichheit wird die Firmware entschlüsselt. Um den Entschlüsselungsvorgang gegen Seitenkanalangriffe zu schützen, verwenden wir sogenannte Leakage-Resilient Cryptography. All diese Funktionen sind in Software implementiert und müssen daher gegen Softwareschwachstellen, speziell Speicherzugriffsverletzungen, geschützt werden. Dafür verwenden wir die moderne Programmiersprache Rust, welche Speichersicherheit garantiert. Wir zeigen die Machbarkeit des Konzepts mit einer praktischen Implementierung, welche auf einem pysikalischem Gerät läuft.

**Schlüsselwörter:** *Secure Boot, Replay* Angriffe, Seitenkanalangriffe, Speicherzugriffssicherheit, Rust

## Contents

| Abstract iv |                                                                                                                                                                                                                                    |                                                                                                            |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1           | Introduction1.1Attacks on Industrial Internet of Things (IIoT) Devices1.2Contributions                                                                                                                                             | <b>1</b><br>2<br>4                                                                                         |  |  |  |  |

| 2           | Memory Safety         2.1       Vulnerabilities         2.2       Attacks and Mitigations         2.3       Modern Programming Languages         2.3.1       Rust                                                                  | 6<br>7<br>11<br>15<br>16                                                                                   |  |  |  |  |

| 3           | Physical Attacks3.1Motivation3.1.1Recent Incidents3.2Replay Attacks3.2.1Mitigations3.3Side Channels3.3.1Differential Power Analysis (DPA)3.3.2Advanced Encryption Standard (AES)3.3.3Hash function3.3.4Message Authentication Code | <ol> <li>18</li> <li>21</li> <li>23</li> <li>24</li> <li>27</li> <li>29</li> <li>35</li> <li>36</li> </ol> |  |  |  |  |

| 4           | Building Blocks         4.1       Secure Boot         4.2       Random Number Generation         4.3       Trusted Platform Module (TPM)         4.3.1       TPM Features         4.3.2       TPM2 Commands                        | <b>38</b><br>38<br>40<br>43<br>44<br>46                                                                    |  |  |  |  |

### Contents

|    |                 | 4.3.3   | Hardware TPM / Low Level Protocol    | 48 |  |  |  |

|----|-----------------|---------|--------------------------------------|----|--|--|--|

| 5  | Prototype       |         |                                      |    |  |  |  |

|    | 5.1             | Conce   | pt                                   | 52 |  |  |  |

|    |                 | 5.1.1   | Side Channel Mitigations             | 53 |  |  |  |

|    | 5.2             | Platfor | rm                                   | 55 |  |  |  |

|    | 5.3             | Struct  | ure of Bootloader Implementation     | 59 |  |  |  |

|    |                 | 5.3.1   | Crates                               | 60 |  |  |  |

|    | 5.4             | rs-zynı | <i>q-boot</i>                        | 63 |  |  |  |

|    |                 | 5.4.1   | Authorized TPM Session               | 64 |  |  |  |

|    |                 | 5.4.2   | Verification and Start of Next Stage | 66 |  |  |  |

|    |                 | 5.4.3   | Security Properties                  | 67 |  |  |  |

|    |                 | 5.4.4   | TPM2 Software Stack                  | 67 |  |  |  |

|    | 5.5             | Provis  | ioning                               | 70 |  |  |  |

|    | 5.6             | Evalua  | ation                                | 74 |  |  |  |

|    | 5.7             | Future  | e Work                               | 80 |  |  |  |

| 6  | Con             | clusion |                                      | 81 |  |  |  |

| Bi | Bibliography 85 |         |                                      |    |  |  |  |

|    |                 |         |                                      |    |  |  |  |

# **List of Figures**

| 2.1  | Memory layout for the example program shown in Listing 2.1.  | 9  |

|------|--------------------------------------------------------------|----|

| 2.2  | Example Return-Oriented Programming (ROP) chain.             | 13 |

| 3.1  | Industrial Internet of Things (IIoT) device.                 | 19 |

| 3.2  | Replay Attack on firmware images.                            | 22 |

| 3.3  | Measurement setup for power analysis attacks                 | 25 |

| 3.4  | Example power trace of an Advanced Encryption Standard       |    |

|      | (AES) encryption on an embedded device                       | 25 |

| 3.5  | Measurement setup for a Differential Power Analysis (DPA).   | 27 |

| 3.6  | Example correlation of a DPA attack on an eight-bit AES      |    |

|      | implementation. The correct key guess is 66                  | 29 |

| 3.7  | Block cipher for encryption and decryption.                  | 30 |

| 3.8  | Electronic Code Book (ECB) mode for encryption               | 32 |

| 3.9  | Cipher Block Chaining (CBC) mode for encryption              | 32 |

| 3.10 | Leakage-resilient mode of operation                          | 33 |

| 3.11 | Re-keying function.                                          | 34 |

| 4.1  | Chain of Trust                                               | 39 |

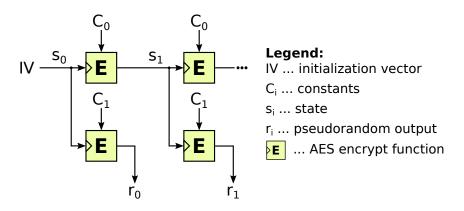

| 4.2  | Advanced Encryption Standard (AES) based 2PRG scheme         |    |

|      | used as Pseudo-Random Number Generator (PRNG)                | 41 |

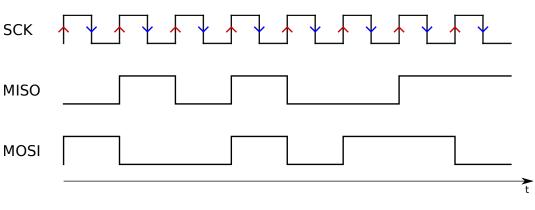

| 4.3  | The timing diagram of an example Serial Peripheral Interface |    |

|      | (SPI) communication                                          | 48 |

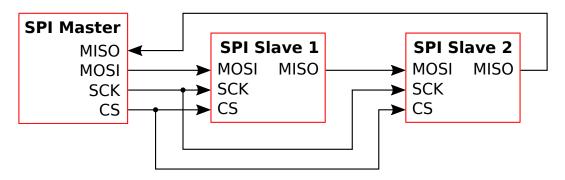

| 4.4  | Example usage of the SPI bus with chained clients and a      |    |

|      | single Chip Select (CS)                                      | 49 |

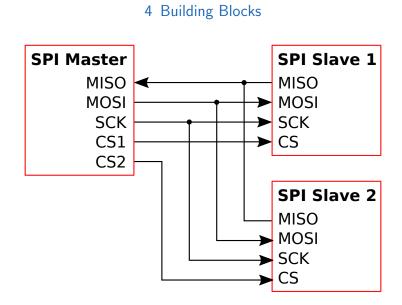

| 4.5  | Example usage of the SPI bus with multiple CSs               | 50 |

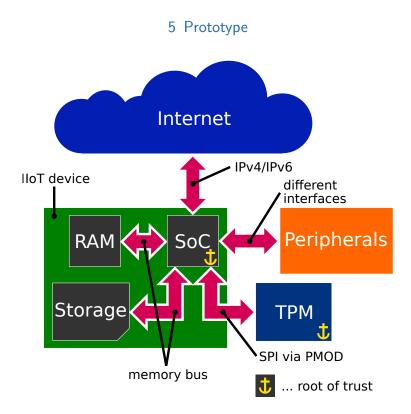

| 5.1  | IIoT device with TPM                                         | 55 |

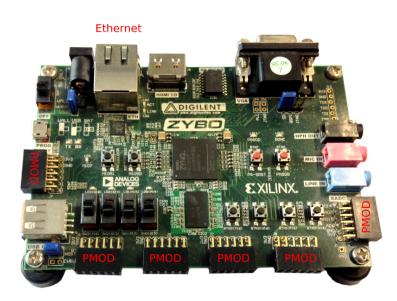

| 5.2  | Zybo platform and TPM                                        | 56 |

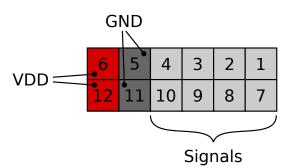

| 5.3  | Peripheral Module (PMOD) pin assignment, front view          | 57 |

|      |                                                              |    |

## List of Figures

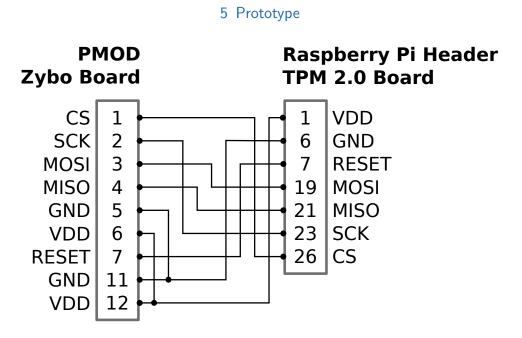

| 5.4  | Wiring diagram between Zybo PMOD connector and the               |    |

|------|------------------------------------------------------------------|----|

|      | TPM board.                                                       | 58 |

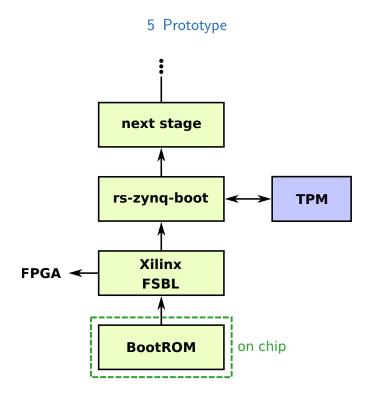

| 5.5  | Chain of Trust implemented.                                      | 60 |

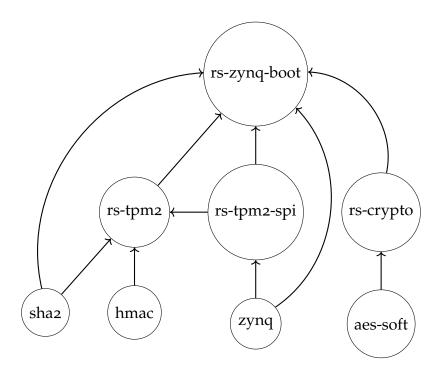

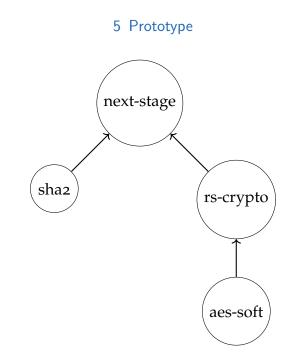

| 5.6  | Dependency graph of <i>crates</i> used inside the bootloader     | 61 |

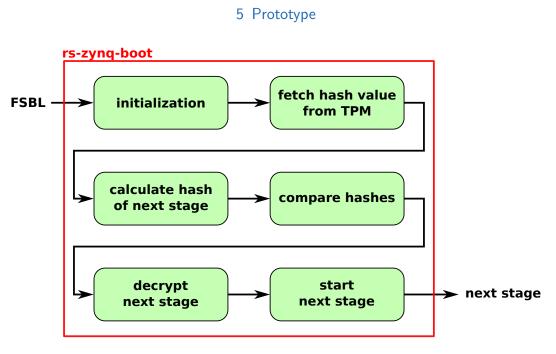

| 5.7  | Processing sequence performed by <i>rs-zynq-boot</i>             | 63 |

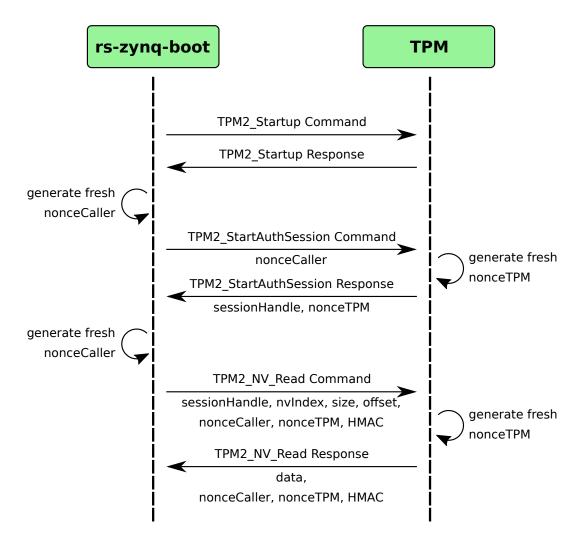

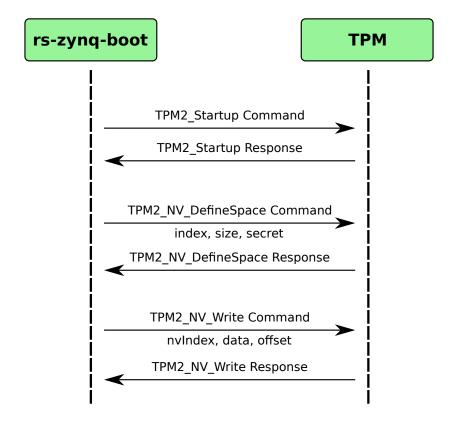

| 5.8  | Sequence diagram TPM communication                               | 65 |

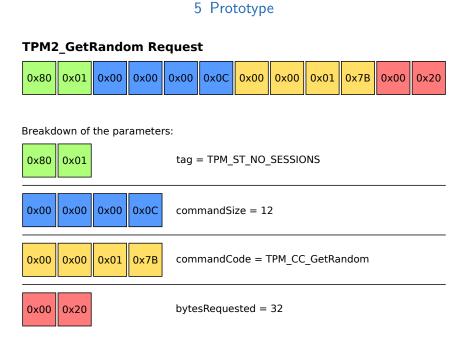

| 5.9  | TPM2_GetRandom request.                                          | 70 |

| 5.10 | TPM_GetRandom response                                           | 71 |

| 5.11 | Dependency graph of <i>crates</i> used to prepare the next stage |    |

|      | firmware                                                         |    |

| 5.12 | Sequence diagram TPM provisioning                                | 73 |

- AES Advanced Encryption Standard.

- API Application Programming Interface.

- ASLR Address Space Layout Randomization.

- CAN Controller Area Network.

- CBC Cipher Block Chaining.

- CFI Control Flow Integrity.

- CI Continuous Integration.

- CMOS Complementary Metal-Oxide-Semiconductor.

- COOP Counterfeit Object-Oriented Programming.

- CPU Central Processing Unit.

- CS Chip Select.

- DoS Denial of Service.

- DPA Differential Power Analysis.

- DRM Digital Rights Management.

- ECB Electronic Code Book.

- ELF Executable and Linking Format.

- EM Electromagnetic.

- FIFO First In First Out.

- FPGA Field Programmable Gate Array.

- FSBL First Stage Bootloader.

- GC Garbage Collector.

| GND   | Ground Voltage Level.                           |

|-------|-------------------------------------------------|

| GPIO  | General Purpose Input Output.                   |

| HMAC  | Hash-based Message Authentication Code.         |

| I/O   | Input/Output.                                   |

| IDE   | Integrated Development Environment.             |

| IIoT  | Industrial Internet of Things.                  |

| IoT   | Internet of Things.                             |

| IP    | Intellectual Property.                          |

| IV    | Initialization Vector.                          |

| JOP   | Jump-Oriented Programming.                      |

| libc  | C Standard Library.                             |

| LIFO  | Last In First Out.                              |

| LOP   | Loop-Oriented Programming.                      |

| MAC   | Message Authentication Code.                    |

| ME    | Management Engine.                              |

| MISO  | Master In Slave Out.                            |

| MMIO  | Memory Mapped Input/Output.                     |

| MOSI  | Master Out Slave In.                            |

| NIST  | National Institute of Standards and Technology. |

| nonce | number only used once.                          |

| OS    | Operating System.                               |

| PC    | Personal Computer.                              |

| PCR   | Platform Configuration Registers.               |

| PIC   | Position-Independent Code.                      |

| PLC   | Programmable Logic Controller.                  |

- PLL Phase-Locked Loop.

- PMOD Peripheral Module.

- PRG Pseudo-Random Generator.

- PRNG Pseudo-Random Number Generator.

- PTP PC Client Platform TPM Profile.

- RAM Random-Access Memory.

- RILC Return-Into-libc.

- RNG Random Number Generator.

- ROM Read-Only Memory.

- ROP Return-Oriented Programming.

- RSA Rivest–Shamir–Adleman.

- SCK Serial Clock.

- SoC System on Chip.

- SPA Simple Power Analysis.

- SPI Serial Peripheral Interface.

- SROP Sigreturn-Oriented Programming.

- SSH Secure Shell.

- TCG Trusted Computing Group.

- TCP Transmission Control Protocol.

- TLS Transport Layer Security.

- TPM Trusted Platform Module.

- TPM2 Trusted Platform Module version 2.

- TRNG True Random Number Generator.

- TV Television.

- UART Universal Asynchronous Receiver Transmitter.

- USB Universal Serial Bus.

- VDD Positive Supply Voltage.

- $W \oplus X$  Write Xor Execute.

- XOR Exclusive OR.

The Internet of Things (IoT) is getting more and more relevant today. The IoT contains *things* that are connected to the Internet. These *things* are interconnected computers, called IoT devices, that are spread all over the world to fulfill tasks of our everyday life.

A modern home is full of IoT devices. Smart Televisions (TVs), smartwatches, smartphones, smart household appliances and smart homes are interconnected and fulfill different tasks of our private lives. IoT devices connect to a cloud via the Internet. The cloud acts as central storage and control point for the IoT system. For example, a smartphone can be used to control the room temperature of a smart home via the Internet, even if the operator is not at home or even on the other side of the planet.

The IoT gets popular not only in the private world but also for the industry. The cloud can be used to monitor, evaluate or control industrial systems. Different industrial computers, so-called Industrial Internet of Things (IIoT) devices, connect to the cloud. These devices are for example found in a power plant, in traffic management or controllers of a production machine. Programmable Logic Controllers (PLCs) are controlling production machines and are responsible for the production progresses. With a connection to the internet, the PLCs turn into IIoT devices and benefit from this connection. The usage of the IIoT offers the possibility to provide customized production. E.g., a factory for sport shoes can fit the product to the customer's needs. Based on a 3D scan of the customer's feet, it is possible to produce a pair of shoes with the perfect fit. The data is transferred over the Internet to the factory where a fully automatic production process fabricates the individual pair of shoes. This concept of individualization is adaptable to many other products. Further, it is possible to monitor the production machine and detect mechanical problems before the machine

fails. Therefore, the analysis is performed in the cloud, and the machine owner gets notified over the Internet. Although there are many benefits of using IIoT systems, there is the risk of broken cybersecurity. Different adversaries are, e.g., cybercriminals, competitors or secret services endanger the IIoT devices. Attackers can use the Internet access to espionage or sabotage on IIoT devices. Further, an attacker can use physical access if the IIoT devices are located in unsafe environments, like smart meters of a smart grid located in a private household or a PLC of a production machine located in a foreign country. IIoT devices contain secret information like domain knowledge of a process that is Intellectual Property (IP) of a company. Further, cryptographic secrets used to authorize against the cloud are stored on the device. Protecting these assets is necessary. Whenever an attacker gains access to the assets, the operator of the IIoT system gets into trouble. For example, the misusage of cloud credentials can threaten the whole IIoT system. Further, the attacker can duplicate IIoT devices or send fake data into the cloud. This behavior risks the production and makes the IIoT system unusable. Therefore, an attack can threaten a whole company and hence the economy. When using IIoT for power grids, attacks endanger the energy supply of whole nations. Today's population depends on the electrical energy. A permanent loss would be a significant threat to our society. For this reason, IIoT systems require strongest protections against cyber attacks.

## 1.1 Attacks on Industrial Internet of Things (IIoT) Devices

However, IIoT devices are distributed all over the world and therefore cannot always be protected against physical access of an attacker. E.g., production machines can be located in a foreign country, where malicious persons have physical access to the machine. This physical access is a problem for the IIoT device, a computer deeply embedded in the environment.

Like almost every computer, it consists of Central Processing Units (CPUs), Random-Access Memory (RAM) and some storage, like a hard disk or an SD-card. Further, the IIoT device has a network connection to establish a

link to the cloud. On the other hand, the IIoT device is connected to the environment. The IIoT device interacts with the environment using sensors and actors. With a sensor, the device can monitor environmental values from a process. With an actor, the device can influence a process.

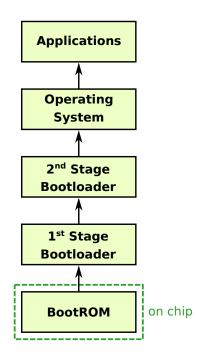

A physical attacker can target every part of the device. By opening the housing of the IIoT device, the attacker can tamper with the inner structure, including measuring signals and modifying the device. For example, when attacking the storage medium, the attacker can read or write data and software that is executed by the IIoT device. This attack gives the attacker full access to the assets and therefore needs to be protected. A state-of-theart mechanism to protect storage is secure boot. Based on cryptography, the integrity and confidentiality of the executed software and stored data are guaranteed. Confidentiality in this context is the protection against unpermitted reads that is reached with encryption. The integrity is reached with Message Authentication Codes (MACs) to prevent the execution of unintended firmware. These two cryptographic mechanisms require secure places to store keys. Therefore, the hardware of the IIoT device needs to support secure boot and therefore verify and decrypt the firmware before execution. In detail, the device starts a bootloader and this bootloader starts the firmware. The bootloader and the firmware are implemented as a software and therefore are at risk of software bugs. These bugs are programming errors that can lead to security vulnerabilities. Vulnerabilities are quite common in modern software as shown in the list of common vulnerabilities and exposures [Cor18]. A particular class of vulnerabilities are memory-safety problems. These problems are caused by unsafe memory handling. For example, a stack-based buffer overflow belongs to this class of vulnerabilities. A vulnerability can be exploited by an attacker so that it can lead to full control over the device. This means that the attacker can execute arbitrary software on the IIoT device and therefore obtains access to the assets. With security updates, vulnerabilities are fixed and the security problem is repaired. However, with a so-called replay attack, an old firmware image can be restored even if secure boot is in place. Due to the fact, that secure boot is based on cryptographic keys that are only once writeable to secure storage in hardware, an old firmware image stays valid. This attack can bring back old vulnerabilities, and allows to exploit the IIoT device.

Another problem resulting from physical access for an attacker are sidechannel attacks. The IIoT device leaks information through side channels while processing data. Namely, processing data generates side effects, like timing differences, EM emanation, heat, and power consumption. These side channels allow concluding on the processed data. For example, the decryption of a firmware image while secure boot is a target for a side-channel attack. The attacker wants to get knowledge of the firmware plaintext to extract secrets and IP. In order to do so, the attacker can use a Differential Power Analysis (DPA), a common side-channel attack based on the power consumption of the device, while decrypting. With this attack, it is possible to extract the cryptographic key and further decrypt the firmware image. Again, this gives the attacker permissions to reproduce IIoT devices as well as impersonating the IIoT device when connecting to the cloud.

We conclude that the mitigation of memory-safety, replay and side-channel attacks are a necessary property for building secure IIoT devices. Robust mechanisms are required to ensure these properties. Currently, there is no solution available that prevents all attacks covered in this thesis. IIoT devices need to be secure and trustworthy, otherwise, IIoT devices run into danger to threaten our world.

## **1.2 Contributions**

This thesis covers three main contributions:

- 1. Replay resistance for operating system updates.

- 2. Memory safety for the implemented bootloader.

- 3. Side-channel mitigations for operating system decryption.

We verify the feasibility of these security mechanisms with a proof-ofconcept implementation of a secure bootloader. To protect against replay attacks, a cryptographic hash over the encrypted next stage is stored inside a Trusted Platform Module (TPM). The TPM guarantees that this data can not be modified. On every system start, the bootloader then computes a hash over the encrypted next-stage and compares it against the securely stored value. This approach prevents executing old next stage copies and thus

a replay attack. We implemented a bootloader using the modern system programming language Rust. Rust guarantees memory safety without a Garbage Collector (GC) by enforcing a robust ownership model for program variables. To cope with side-channel attacks on the bootloader, we use a leakage-resilient cryptographic mode of operation, such as proposed by Pereira et al. [PSV15], for the encryption of the next stage. However, as discussed by Dobraunig et al. [Dob+17], leakage-resilient encryption schemes are yet vulnerable to side-channel attacks where attackers maliciously alternate the ciphertext. To also protect the decryption at startup, we hence check the hash of the ciphertext before actually performing the decryption. In this respect, this work shows that secure modifiable storage can help to mitigate side-channel attacks during the decryption of boot images.

Our results further indicate that it is possible to secure a device against replay attacks and mitigate side-channel attacks without being in danger of memory safety issues. From our results, we suggest using Rust for new IoT implementations and encounter replay and side-channels as potential threats.

#### Outline

In Chapter 2, the fundamental property of memory safety is covered, and different attacks and mitigations are explained. Chapter 3 focuses on physical attacks, particularly replay, and side-channel attacks. Moreover, cryptographic primitives are described in the context of side-channel attacks. Basic concepts of secure systems, including secure boot, random number generation, and the TPM, can be found in Chapter 4. Chapter 5 gives details on the actual implementation. Chapter 6 concludes this thesis.

Devices in the Internet of Things (IoT) are computers integrated into an embedded world. These computers run software written by programmers. C and C++ are currently the standard programming languages for lowlevel programs like operating system kernels, device drivers, or bare-metal applications. Therefore, a large share of software running on IoT devices is written in C/C++. C/C++ is well established and offers easy hardware access. Memory mapped Input/Output (I/O) is used to control interfaces, timers or interrupts. Hardware interrupts can be implemented to get notifications on events so that real-time applications can be programmed. However, C/C++ is error-prone in the sense of dealing with memory. The language does not prevent the introduction of different flaws and therefore expects the programmer to deal with all these problems. Using C/C++, it is easy to implement a program that accidentally allows illegal access to memory. If such an implementation is introduced unintentionally, a so-called software bug occurs. Such a software bug could be exploited by an attacker to threaten the security of the IoT device. An exploitable bug in this context is called a vulnerability. As shown in the list of common vulnerabilities and exposures [Cor18], security vulnerabilities commonly occur in software products.

A particular class of vulnerabilities are memory safety issues, commonly found in applications written in C/C++. Memory safety is a central property in information processing promising that no memory area can be illegally read or written. However, memory safety vulnerabilities often occur in software today. By exploiting memory safety vulnerabilities, an attacker can reach different goals, up to full control over a device. Recent programming languages can assure the absence of memory safety issues, but are not widely used or do not fulfill the requirements of embedded programming. These languages often introduce a massive overhead in execution time

and hardware requirements so that C/C++ was not replaced by now. A promising, new system programming language, which tackles memory safety issues with a novel concept of an ownership model, is Rust, covered in Section 2.3.

Memory safety issues often lead to code execution attacks. This class of attacks allows an attacker to execute malicious software on the device under attack. The attacker hereby crafts a user input which causes a special behavior of a software program. In this way, the attacker exploits a vulnerability and therefore gains more permissions as intended for a user of the program. Memory safety attacks can give an attacker full control over the device, including unauthorized access to data, taking control over the behavior of the system and Denial of Service (DoS) attacks. A so-called DoS attack threatens the availability of a device. For example, this can be achieved by crashing the application. A DoS attack already is a serious problem, but other attacks are more powerful and even more harmful.

Section 2.1 gives a brief overview of common vulnerabilities found in today's software. Section 2.2 covers state-of-the-art attacks and mitigations of memory safety vulnerabilities.

### 2.1 Vulnerabilities

As already motivated, exploitable software bugs lead to vulnerabilities. There exist many different classes of vulnerabilities that can lead to memory safety attacks. Serious vulnerabilities found in popular software are collected and rated in the list of common vulnerabilities and exposures [Cor18]. This list is extensive and visualizes that vulnerabilities are a severe problem in present information processing systems. In the following, we give an overview of the most relevant types of vulnerabilities.

**Buffer Overflow.** Stack-based buffer overflows were first shown by Levy [Lev98] in the 90s and enable an attacker to gain unauthorized access to a system by rewriting the stack. In general, a stack is a data structure following the Last In First Out (LIFO) principle. With a push operation, data can be

Listing 2.1: Buffer overflow example written in C.

```

1 #include <stdbool.h>

#include <stdio.h>

#include <stdlib.h>

int main()

5

{

6

char buffer[10];

7

bool is_admin = false;

8

printf("Please enter your name: ");

9

scanf("%s", buffer);

10

printf("Hello %s\n", buffer);

11

12

if(is_admin == true)

13

{

14

printf("Welcome Administrator, here is your shell:\n");

15

system("/bin/sh");

16

}

17

return 0;

18

}

19

```

placed on the stack and with a pop instruction the last *pushed* value can be retrieved. The stack, as used by C/C++ compilers, is a memory region inside the Random-Access Memory (RAM) and is used to store arguments, local variables and return addresses.

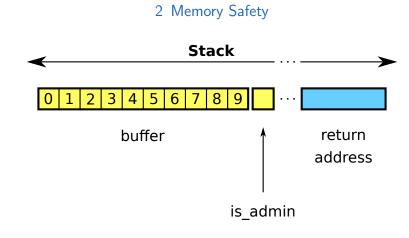

User input is typically stored in buffers, meaning every character is stored next to another in a memory range defined while programming. Listing 2.1 shows a small code snippet receiving user input and storing it to the array buffer. The code provides a maintenance access if the is\_admin flag is set to true. Although the code seems correct, the implementation is vulnerable. Missing bounds checks on a memory buffer can lead to a buffer overflow in the variable buffer. In the example, scanf accepts more characters than can be stored into the buffer. As shown in Figure 2.1, is\_admin and buffer are located on the stack. By writing out of bounds, the variable is\_admin is overwritten. Doing so, the condition is\_admin == true in line 13 in

Figure 2.1: Memory layout for the example program shown in Listing 2.1.

Listing 2.2: Console output of Listing 2.1.

- <sup>1</sup> Please enter your name: ABCDEFGHIJK

- <sup>2</sup> Hello ABCDEFGHIJK

- 3 \$ uname

- 4 Linux

Listing 2.1 can be triggered to evaluate to true. In this way, the maintenance entrance is unlocked as demonstrated in Listing 2.2, which shows the console output of the program execution. The bug in the example is easy to fix within the scanf format string: scanf("%9s", buffer). With this modification, no more than nine characters are accepted. Since strings are zero-terminating in C, only nine characters can be stored in a ten-byte buffer.

**Integer Overflow.** Integral data types, as used in modern computers, have limited memory footprints, and therefore a restricted range of possible values. For example, an unsigned eight-bit datatype can hold values from 0 to 255. When incrementing over this limit, the variable overflows. The equation 255 + 1 results in the value 0. A similar behavior occurs when decrementing the variable. Integer Overflows also occur on signed datatypes. This vulnerability is a class of hard-to-find software bugs. If this problem occurs in a length check of a buffer, the attacker is able to write out of bounds. In this case, the attacker can overflow a buffer, as shown before.

**Use After Free.** A Use After Free attack abuses the dynamic memory management. While programming C or C++, the programmer can allocate memory on the heap, which is the memory region for dynamic memory. The programmer is entirely responsible for initialization, usage, and freeing this memory. If the program frees such a memory element, no automatic mechanism will clear the content nor invalidate any pointer to this memory. By abusing a weak implementation, an attacker can leak information or execute malicious code from these unchecked memory regions.

**Type Confusion.** A C++ object can contain function pointers located in the virtual method table. As discussed by Jeon et al. [Jeo+17], these function pointers can be abused by type conversion. If an illegal type conversion, an illegal cast, is performed, an unintended function call can arise.

**Format Strings.** A format string is the format representation used in the C standard library. For example, printf uses format strings to determine the output format. If a user can control the format string, e.g., through the user input, the program is in general exploitable. Listing 2.3 shows the usage of the format string of the printf function. If fmt results from user input, a malicious user can gain arbitrary read and write access to the program memory, which in turn can result in code execution. A vulnerable format string used in printf is *Turing complete*, as shown by Carlini et al. [Car+15]. This property means that the exploitation is universal programmable. As a consequence, an attacker can program the vulnerability to perform malicious actions.

Modern compilers are aware of this vulnerability and can output warnings to inform the programmer. Unfortunately, large software projects tend to be full of compiler warnings. In this case, essential warnings can easily be missed.

Listing 2.3: Format string example written in C.

1 char\* fmt = "%d";

2 printf(fmt, 42);

### 2.2 Attacks and Mitigations

This section covers state-of-the art attacks that allow an attacker to execute code on the device under attack. The attacker gains full control over a system if malicious code is executed. Of course, there exist defensive mechanisms, so-called mitigations, that hinder an attacker from exploiting a vulnerability. New mitigations lead to the development of new attacks and vice versa. The following list contains attacks and mitigations showing the efforts of both sides.

Attack: Shellcode. The simplest case is to write a so-called shellcode through user input to the memory. A common goal when attacking binaries is to get access to the computer's command line, which is also known under the name shell. A shellcode contains machine instructions that the attacked computer executes in order to gain access to the shell. Therefore, the shellcode attack belongs to the group of code injection attacks. Of course, there are mitigations in place that lead to an evolution of this attack.

**Mitigation: Write Xor Execute.** Write Xor Execute  $(W \oplus X)$  is a state-ofthe-art mechanism that limits the scope of code injection attacks by using memory privileges. The mechanism prohibits that a memory area is both writeable and executable, analogous to the truth table of the Exclusive OR (XOR) function. In that way, an attacker cannot write instructions to the memory and execute it afterwards. This approach mitigates code injection attacks since user-writeable memory regions are no longer executable. A simple shellcode attack is made impossible.

**Attack: Return into Libc.** As discussed in Section 2.1, a stack-based buffer overflow can overwrite other elements on the stack. Unfortunately, return addresses are also stored on the stack. This behavior is necessary, because whenever a called function returns, the program should continue right after the point, where the function was called. Therefore, before a function is called, the so-called return address is pushed to the stack. However, instead of returning to the calling function, the attacker can use a function

return to call arbitrary functions by overwriting the return address on the stack. Therefore, Return-Into-libc (RILC) belongs to the group of code reuse attacks. Hereby, an attacker typically uses functions of the C Standard Library (libc) to exploit a program. The libc is the standard library on GNU Linux for programs written in C, including functions for file I/O and process execution. These functions are powerful tools for an attacker to gain full control over the system. Even when  $W \oplus X$  is in place, it is possible to perform a RILC attack. RILC is *Turing complete*, as shown by Tran et al. [Tra+11].

**Mitigation: Stack Canary.** As a mitigation against buffer overflows, as shown in Section 2.1, the compiler inserts a magic value, the so-called stack canary, between buffers and return addresses on the stack. By exploiting a buffer overflow, the attacker will overwrite the stack canary. An added piece of code checks the canary value before returning from a function because the return address is a common goal for attackers. If the canary value alters, the program will stop its execution. However, a stack canary can be tricked if the program leaks the exact value of the stack canary. In this way, the attacker can read out the stack canary and knows what to write to the critical position.

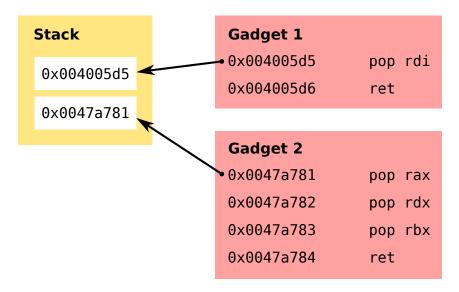

**Attack: Return oriented Programming.** Return-Oriented Programming (ROP) is a well-established attack. Existing tools [Gal18; Sch18; Sal17] help attackers to exploit vulnerabilities with ROP. ROP gadgets are automatically searched and the toolchains can orchestrate them together.

ROP is a generalization of RILC, which was described before, and is classified as a code reuse attack. There is no need to call an entire library function, also small chunks of instructions work. If such a chunk ends with a return instruction, it is considered as a so-called ROP gadget. Gadgets can be linked to a so-called ROP chain. When executing a ROP chain, one gadget returns and therefore calls the next gadget. As a result, the attacker can write a program in the shape of a ROP chain, by writing a sequence of addresses of ROP gadgets as return addresses on the stack. Figure 2.2 shows an example ROP chain. The gadgets consist of a few instructions and end with the ret instruction. Libraries, like the libc, and the binary itself are

Figure 2.2: Example ROP chain built out of two ROP gadgets. The address shows the location of the gadgets. The stack contains the entry points of each ROP gadget.

mapped to the memory. The gadgets found in the mapped memory can be used for ROP. The program returns to the start address of the gadget and executes the instructions. Another interesting fact is, that for architectures with variable length instructions, like x86, one binary blob can result in different ROP chains. In this way, the number of ROP gadgets is increased. The ROP chain is packed into user input, as so-called payload, and sent to the process under attack. The ultimate goal is to get control over the process. This approach is known as process owning. By process owning, an attacker can, for example, get access to a command line interface on an online server. Using this command line interface the attacker can connect to other services, maybe a local network of the server, or can use other bugs to get more privileges on the server. If a so-called privilege escalation is successful, the attacker can gain full control over the server and all processes running there. Full control means that the attacker can kill every process, delete all data, destroy data, write data, run programs, read all data and especially copy all data to the local computer.

**Mitigation:** Address Space Layout Randomization. Randomization approaches were invented to prevent code reuse attacks. Address Space Layout Randomization (ASLR) is a state-of-the-art mitigation technique to prevent memory safety attacks. Hereby, the location of essential memory regions is randomized. On every execution of a binary, the position of memory sections, like the stack, is randomized. As the location of the stack changes, the memory addresses are randomized. An attacker cannot rely on the position of a library and is handicapped in performing a code reuse attack.

**Mitigation:** Position Independent Code. Position-Independent Code (PIC) is a randomization approach to hide memory regions. The compiler removes absolute addresses so that the code runs on arbitrary position. Compared to ASLR, also the position of the main binary is moved. This approach mitigates code injection and code reuse attacks. However, for both ASLR and PIC, an attacker can recompute target locations if the program leaks a memory offset of a location of interest.

**Mitigation: Control Flow Integrity.** A software program consists of instructions. While execution, different paths of instructions can be taken. These paths form the control-flow graph, which is a graph with finite size. During normal operation, the execution follows the edges of the control-flow graph. When the control-flow graph is left, a vulnerability is exploited, or a fault occurred. A fault can be caused by a defective memory cell or a power glitch. Control Flow Integrity (CFI), proposed by Abadi et al. [ABE05], is a mechanism to ensure that the control-flow graph is never left. Usually, CFI schemes require hardware support integrated into the Central Processing Unit (CPU). The CFI scheme mitigates code injection and code reuse attacks but does not prevent against type confusion vulnerabilities as mentioned in Section 2.1.

Advanced Attacks. Multiple attacks, like Jump-Oriented Programming (JOP) [Ble+11], Sigreturn-Oriented Programming (SROP) [Mab16] and Loop-Oriented Programming (LOP) [Lan+15], were developed to overcome different mitigations. An exciting attack further is Counterfeit Object-Oriented Programming (COOP), proposed by Schuster et al. [Sch+15], that circumvents CFI.

The sum of all attacks against memory safety issues shows that they are a serious threat to current software. Mitigation techniques were bypassed by new types of attacks and never solved the original problem of software containing vulnerabilities. As a result, it is time that a compiler can guarantee memory safety.

### 2.3 Modern Programming Languages

Most of the vulnerabilities described in Section 2.1 are closely related to the programming languages C and C++. C was introduced in the year 1972, when the security threat situation was different. With the invention of the Internet, much more threats arose. Before the Internet, exploiting a vulnerability on a local computer would mean to attack the own computer. Security was not a big deal for a long time. Nowadays, millions of computers are connected to the Internet and vulnerabilities offer attack capabilities to attackers from all over the world. More recent programming languages like Java, Python or Go offer stronger guarantees for memory safety, but are not that valuable for embedded programming as a system language. These programming languages are focused on higher-level applications.

#### 2.3.1 Rust

Graydon Hoare introduced Rust, a modern programming language, in the year 2010. Today Mozilla Research is the driving force behind the project. Mozilla uses Rust in the currently experimental browser engine Servo [Moz17]. Further, Rust is found in the release of Firefox Quantum, where the CSS rendering engine was rewritten in Rust. Clark [Cla17] praises Quantum CSS for the high performance.

Rust is designed for the same purpose as C/C++, as a system language. It is suitable for applications running on a modern Operating System (OS) as well as embedded programming. Further, Rust guarantees memory safety by design. The guarantee is based on a strong ownership model for program variables, which also protects against data races in concurrent executions. Rust introduces a concept named lifetimes, which replaces a Garbage Collector (GC). Based on the concept of lifetimes, use after free vulnerabilities can be excluded. By using zero-cost abstractions, Rust implementations reach execution times that are competitive with programs written in C/C++.

The language is compiled with the Rust compiler (rustc), that itself is written in Rust. The compiler uses an LLVM backend, a state-of-the-art toolchain capable of cross-compilation to many different CPU architectures. The Rust package manager (cargo) manages dependencies to different *crates*. A *crate* is a project that could be a either an executable or a library. Dependencies are distributed as source code and automatically fetched from the repository and built locally. It is easy to include external library *crates* into a software project.

As discussed by Wilson [Wil16], integer overflows are not always checked for performance reasons. The current default strategy is to perform the tests in debug builds and skip the tests in performance-optimized release builds. Of course, the programmer can override the default behavior. Another way is to use library functions, offered for all integral types, to perform a check manually.

**Unsafe Rust.** Low-level programming requires direct access to hardware registers. This requirement can not fulfill the memory safety guarantees of Rust. Unsafe Rust solves this problem. The unsafe keyword is used to define blocks that override all security mechanisms. Such a block can be embedded in a Rust program, where the remaining source code will be handled as safe Rust. A good practice is to keep the amount and size of unsafe blocks as small as possible.

**Embedded Rust.** At the time of programming the project behind this thesis, embedded Rust was still in development. Unstable features were required to compile a bare-metal project for an embedded platform. Therefore, a nightly built Rust compiler (rustc) and the tool Xargo were required. Xargo is an extension for Cargo with the ability to compile the core library for all kinds of platforms. The Rust developers are currently working on stabilizing these features [Apa18a]. Moreover, the features Xargo provides will be merged into Cargo [Apa18b]. With this work, the Rust developers make Rust even more attractive for embedded programming. These efforts are planned to be finished by the end of 2018 [Tea18c].

## **3 Physical Attacks**

Physical attacks are the class of attacks on a computing device where the attacker has physical access to the device. Because Industrial Internet of Things (IIoT) devices are widespread and operate in unsafe environments, they are in high danger of physical attacks. Therefore we need to protect IIoT devices against physical attacks where an attacker has hands-on access to the device. Because of this access, the attacker can open the housing of the device, replace components, measure signals or introduce faults.

Two families of physical attacks are in the focus of this work. The first family are physical replay attacks. Replay attacks are not only limited to physical attacks and allow an attacker to use obsolete information to bypass security mechanisms. This attack is a critical threat to communications as well as for software running on an IIoT device. The attacker can replay an old software image with a physical attack even if the image is encrypted. The second family of physical attacks are side-channel attacks. Side-channel attacks allow an attacker to break cryptography and gain knowledge of secret information from observing physical device properties. With a side-channel attack, the attacker can leak the encryption key and decrypt the software image.

Section 3.1 gives details on the IIoT device and the different attack vectors. Section 3.2 covers replay attacks and mitigations. Section 3.3 discusses side-channel attacks with the focus on cryptographic algorithms.

### 3.1 Motivation

IIoT devices are deeply integrated into the environment to fulfill sophisticated tasks. However, this deep integration causes the risk of physical

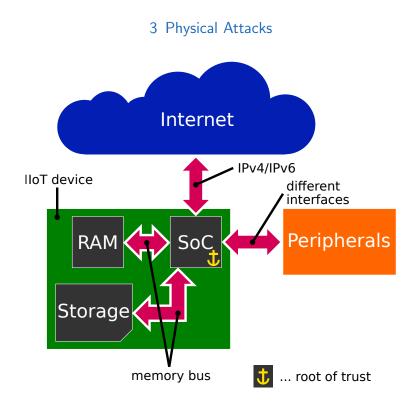

Figure 3.1: General structure of an IIoT device embedded into the environment.

attacks. For example, a device located in a data center is protected by physical barriers, and therefore the attacker needs to break the physical barrier before mounting a physical attack. For an IIoT device, usually it is impossible to protect the device with physical barriers. Attackers can gain physical access to the device and therefore can access and tamper with the physical properties.

The attackers want to steal or manipulate data on the IIoT device or want to clone the device itself. Figure 3.1 shows the basic structure of an IIoT device embedded into its environment and gives a basic overview of what parts can be attacked. On the one hand, the device is connected to the internet, shown as a cloud. Through this connection, the IIoT device communicates with servers that belong to cloud services. In this way, the IIoT device is associated to an overall IIoT system. On the other hand, the IIoT device is connected to peripherals. Through these connections, the device can gain insights or control the physical world. In other words, an IIoT device is a computer that connects the physical world with a cloud backend. It consists of memory

#### 3 Physical Attacks

storage, like an SD-card, to save firmware and data. Also, Random-Access Memory (RAM) is part of the IIoT device that is used as a working memory for the computations. Both memory types are connected to a System on Chip (SoC), the core component of the IIoT device, through memory busses. The heart of a SoC are one or multiple Central Processing Units (CPUs), but also memory controllers and interface controllers are included in a SoC. For example, General Purpose Input Output (GPIO), Universal Asynchronous Receiver Transmitter (UART), Controller Area Network (CAN) or Serial Peripheral Interface (SPI) are common interfaces offered by a SoC design.

A physical attacker has the opportunity to attack every single point of the IIoT device. For example, the connection to the cloud can be intercepted. There exist proper standard protocols that ensure protection on this channel. The linkage to the peripherals is another entry point. First, the applied interfaces, e.g., CAN, often implement no security measures at all. Second, physical parameters can be manipulated directly. For example, the temperature that is measured by a temperature sensor can be modified by an attacker. Further, a physical attacker can access the inner structure of an IIoT device, even on the inner structure of the SoC.

In this thesis, we do not encounter attacks on the inner structure of IIoT devices. These attacks are expensive and require sophisticated knowledge of chip structures. Attacks on peripherals are also not considered in this work. For example, protecting a temperature sensor against manipulation is not easy at all in the presence of physical access. Further, we do not encounter attacks on the connection to the cloud since there are well-established standard protocols like Transport Layer Security (TLS).

The considered attacks focus on all components the IIoT device consists of. An attacker can gain access to the memory by tampering with memory busses or getting direct access to a storage medium, e.g., an SD-card. Further, an attacker can measure all kinds of physical properties, like Electromagnetic (EM) emanation, heat, and power consumption. Through all these possibilities, an attacker can reach the goals defined before. Section 3.1.1 gives some examples of practical, physical attacks.

#### 3 Physical Attacks

#### 3.1.1 Recent Incidents

A possible attack vector is to manipulate values inside the RAM. By rewriting memory, an attacker can hijack the device. For example, Jacob et al. [Jac+17] proposed to rewrite bootloader arguments to force the device to boot from a malicious network location. The described attack uses hardware trojans to manipulate memory, but unprotected memory is also at risk of being modified by an attacker. To prevent such attacks, memory can be protected with transparent memory encryption and authentication as proposed by Werner et al. [Wer+17].

A simple physical attack is to clone the device by cloning the hardware design and duplicating the firmware. Although there exist countermeasures, still a large number of devices are vulnerable to this type of attack. The attacker can read all secrets from the storage and use them for malicious actions. Similar to this, parts of the firmware can be modified on an unprotected device, so that the device executes software written by an attacker. For example, sensor values that are reported to the cloud can be manipulated.

Muellner and Kammerstetter [MK17] showed on the 34<sup>th</sup> Chaos Communication Congress that Hoermann BiSecur devices include a cryptographic vulnerability, allowing to deduce the cryptographic key and to clone a remote control for garage door systems. They were able to read out and reverse engineer the firmware. This analysis is a good example of a physical attack. Using the recovered firmware, the cryptographic flaw was detected.

## 3.2 Replay Attacks

When performing a replay attack, an attacker records a message and replays it later. This type of attack is simple, but powerful, and often used to overcome specific security features. Originally, replay attacks were performed on network communication, but these could also be applied to our everyday life. For example, if a concert ticket is used and not devalued correctly, an attacker can reuse a copy to get access to the event.

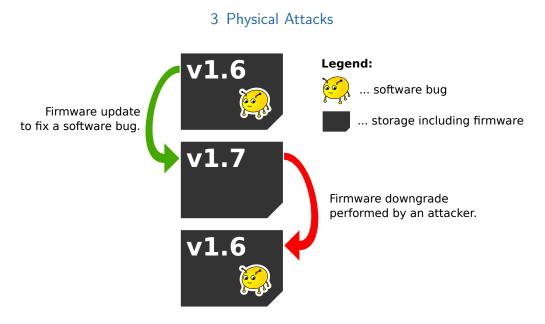

Figure 3.2: Replay Attack on firmware images.

As indicated in Figure 3.2, the same concept can be applied to firmware images. An attacker with physical access can always take copies from the storage and replay it at a time of choice. An old firmware version can be replayed by an attacker with physical access to the device. A replay attack on firmware images is dangerous, because firmware updates often include security updates, where vulnerabilities are removed. Performing the attack brings back the vulnerabilities that can be exploited afterwards. Even if the firmware image is encrypted and the encryption key is not known by the attacker, a replay attack can be accomplished. Further, secure boot, a state-of-the-art mechanism to protect storage discussed in more detail in Section 4.1, does not protect against replay attacks.

A prominent example by Skorobogatov [Sko16] showed how to mirror the storage of an iPhone 5c. The phone could be configured with a security feature which deletes all data if a wrong passcode was entered too often. By replaying the old image one could circumvent this security feature. Namely, it allows to reset the password counter and therefore apply a brute-force attack to crack the passcode. Further, all possible combinations of the passcode can be tested because there is no limit for the number of tries anymore.

Similar to the password counter in the previous example, devices may contain sensitive data like counters for pricing, bank account balance or a usage counter of a machine. In any of these cases, a replay attack has to be considered.

# 3.2.1 Mitigations

One way to prevent replay attacks is to use a tamper-resistant single-chip computer. In this case, the firmware storage is inside the chip and can not be modified by an attacker. Therefore a built-in firmware update solution is required. When performing an update, the firmware update tool checks if the version is increasing to prevent replay attacks. For example, secure microcontrollers or smart cards fulfill the requirement that memory cannot be manipulated. Physical barriers prevent an attacker from accessing the built-in memory.

Another option is a secure, writeable memory inside the SoC, to store the version number. This number is then matched while boot. A popular implementation of such a secure storage are fuses, a memory that is only writeable once. With this instrument, every version needs to consume one bit. In turn, the number of possible firmware update depends on the number of fuse bits integrated into the SoC. Indeed, not all SoC chips available include custom programmable fuses.

The best solution is an on-chip secure writeable memory to keep track of the software version, but this is rare in current SoC implementations. As a workaround, an external secure element, like a Trusted Platform Module (TPM), can offer tamper-resistant secure storage. In this case, it is essential to pay attention to secure communication between the secure element and the SoC. If the attacker can impersonate the secure element, replay attacks are feasible again.

# 3.3 Side Channels

A computer leaks information through side channels when processing data. Timing, EM emanation, heat or power are well known physical side channels. For example, if the execution time depends on the processed data, a timing side channel exists. In this case, the time can be measured and under certain circumstances the processed data can be reconstructed. Timing leakage can be mitigated with constant time implementations. If the execution time is independent of the processed data, no timing information can be exploited. In general, the information leakage through side channels depends on implementation characteristics. Two implementations of the same algorithm can have different exploitability.

Side-channel attacks are potentially dangerous for cryptographic algorithms, where secret keys are involved. The goal of an attacker is to learn these keys and to use them later. In this way, an attacker can decrypt ciphertexts, or even impersonate as an authenticated user.

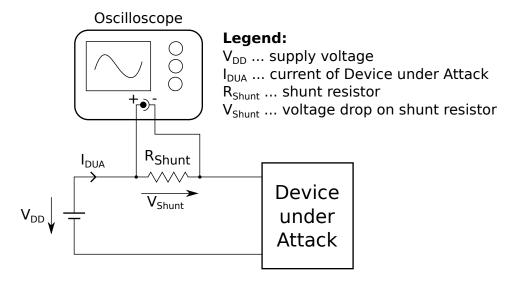

In this thesis, we focus on the power side channel. Based on the power consumption of the device different attacks are applied. The basis of all analysis is the measurement of power ( $P_{DUA}$ ) on the device under attack. More precisely, a time series of values proportional to the power ( $P_{DUA}$ ) is required. Since computers are supplied with a constant voltage, the current is such a proportional value to the power as shown in Equation 3.1.

$$P_{DUA} = V_{DD} \cdot I_{DUA} \tag{3.1}$$

$$V_{Shunt} = R_{Shunt} \cdot I_{DUA} \tag{3.2}$$

An oscilloscope is an instrument that allows the measurement of time series. Figure 3.3 shows a basic measurement setup by using an oscilloscope to measure the voltage drop on the shunt resistor. Based on Ohm's law, as shown in Equation 3.2, the voltage drop ( $V_{Shunt}$ ) on the shunt resistor is proportional to the current, and therefore proportional to the power consumption of the device under attack. By using an oscilloscope with a current probe or a shunt resistor, it is possible to record time series of

Figure 3.3: Measurement setup for power analysis attacks.

Figure 3.4: Example power trace of an AES encryption on an embedded device.

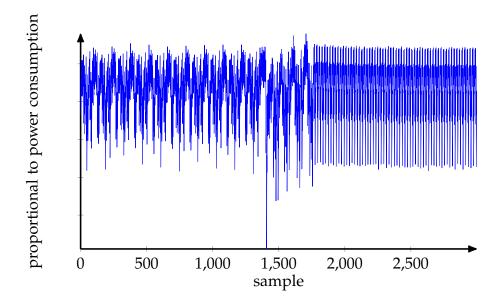

power values, so-called traces. Generating multiple traces means to repeat the recording with different inputs for the device under attack. Figure 3.4 shows an example power trace. Side-channel attacks perform analysis on these traces to extract the information that is leaked through the power side channel.

**Simple Attacks.** On the one hand, there are single-trace attacks, where the measurement of a single event is enough to extract the data of interest. For example, Courrège et al. [CFR10] show a Simple Power Analysis (SPA) on an implementation of the Rivest–Shamir–Adleman (RSA) algorithm [RSA78]. Based on the shape of a single power consumption trace [CFR10, Figure 3], the exponent used in the computation can be determined. Squaring uses different parts of a chip than multiplying, and hence generates a distinguishable power consumption. Some implementations produce obvious traces so that the value can be determined by visual inspection only.

**Differential Attacks.** On the other hand, there are differential attacks. Multiple, up to thousands, of traces are used to expose minimal differences that arise in a computation. One example of differential attacks is Differential Power Analysis (DPA), a state-of-the-art attack proposed by Kocher et al. [KJJ99], based on power side channels. Recording the power consumption of a system while encrypting or decrypting different inputs with the same key generates traces. With these traces, an attacker can deduce the key used. The reason for this is while processing data, the power consumption of the system depends on the processed data. For example, a Complementary Metal-Oxide-Semiconductor (CMOS) transistor consumes more energy, if the state changes. The reason is that the electrical charge of the gate capacity needs to be changed. This event occurs just for a very short time but depends on the data processed. Since a DPA requires multiple traces capturing this event, they need to be aligned. This means that the recording has to start every time at the same point and the executed instructions always happen at the same position in the recorded trace. This can be done by using the oscilloscope trigger input. Of course, an event is required that is used for this trigger. It is possible to improve the alignment in the analysis phase, for

Figure 3.5: Measurement setup for a DPA.

example, by maximizing the correlations between traces by shifting them on the time axis.

# 3.3.1 Differential Power Analysis (DPA)

DPA is a well established physical attack on cryptographic devices. One advantage is that it is possible to perform this attack with relatively cheap equipment. Namely, an oscilloscope or similar device like the ChipWhisperer [Inc18] is required to record timing power traces. These devices are affordable for a few hundred dollars. Figure 3.5 shows the basic setup of a DPA. It consists of a device under attack, an oscilloscope to measure traces and a Personal Computer (PC) for processing. The PC is the attacker's tool to feed the device under attack with inputs and receive the associated traces from the oscilloscope.

**Intermediate Result**. The first task to perform in a DPA is to select a function inside the algorithm that uses the secret and a selectable value as an input. The function's output is an intermediate result that is the target of the attack. The power consumed while storing the intermediate result in some memory depends on the value of the intermediate result and therefore, information is leaked.

**Measurement**. The second step is to record traces. Therefore, the measurement setup is installed, and the cryptographic operation is performed multiple times with different inputs. The attacker needs to inject these inputs, for example, with a PC. Within this process, the power consumption of the device is recorded. Essential for this step is that the operation under attack is inside the time frame of the recorded trace. As mentioned before, proper alignment of the traces is required for the following analysis.

**Hypothesis.** As a third step, possible intermediate values need to be computed, the so-called hypothesis. Therefore, the selected function under attack is calculated locally for one selected input value and all possible values for the secret. This is continued for all selected input values and results in a matrix with the shape of all possible secret values times all selected inputs.

**Power Model.** As the fourth step, the power model is applied to the hypothesis. The power model is a function that maps the value of a specific intermediate result to the expected power consumption. A common model is the Hamming weight, which counts the number of bits that are true. This follows the assumption that enabling more bit requires more power.

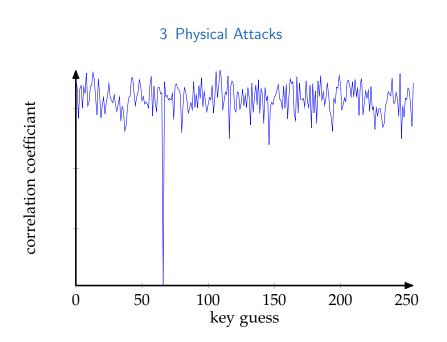

**Compare.** The last step is to compare the result of the power model to the hypothesis with the measured data. A popular method is to use a correlation function to compare a vector containing the power model of all selected input values for one particular possible secret value. This vector is correlated with every timestep of all recorded traces. For every timestep, a correlation factor is computed. At the timestep, where the operation of interest is

Figure 3.6: Example correlation of a DPA attack on an eight-bit AES implementation. The correct key guess is 66.

performed, the correlation of the correct key will be highest. Depending on the type of correlation, this can also mean the lowest correlation coefficient, as in the following example. Figure 3.6 shows the minimal correlation coefficient of all traces for different key guesses. The correct key guess is clearly visible. Therefore, a secret is extracted out of the recorded power traces.

### 3.3.2 Advanced Encryption Standard (AES)

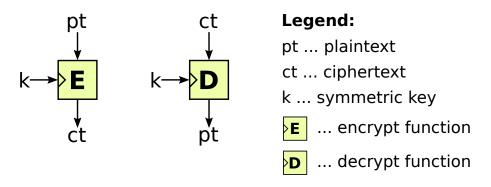

Cryptographic algorithms are a common goal for side-channel attacks. The attacker's ambition is to learn the key involved that, for example, can be used to decrypt ciphertexts. Symmetric encryptions are used to encrypt and decrypt big blocks of data. The same key is used for encryption and decryption, therefore this mechanism is called symmetric encryption. The AES is the current standard for symmetric encryption. A competition was started in 1997 to find the best algorithm for the new standard. As the winner of the selection process, the Rijndael algorithm proposed by Daemen and Rijmen [DR98] was standardized in the year 2000 by the

Figure 3.7: Block cipher for encryption and decryption.

National Institute of Standards and Technology (NIST). The AES encryption and decryption functions perform cryptographic operations with a secret key involved. The operations can leak information through sidechannels. We take a closer look at the AES and different modes of operation, including a leakage resilient mode.

AES is a block cipher, that means the algorithm operates on fixed-size data blocks. The AES algorithm has a block size of 128 bits and the possible key sizes are 128, 192, and 256 bits. The left part of Figure 3.7 illustrates a block cipher encryption function. The encryption function encrypts the plaintext (pt) with the key (k) and hence generates a ciphertext (ct). Plaintext (pt) and ciphertext (ct) have the same size as the block size. The decryption function decrypts the ciphertext (ct) with the same key (k) as used for encryption, shown right in Figure 3.7.

**DPA on AES.** The AES encryption and decryption functions are often a target of DPA attacks with the goal to extract the secret key. One essential part of the AES algorithm is the S-box. It is a substitution step that can be implemented using a lookup table, as shown in Listing 3.1. Within the AES algorithm, the input plaintext and key get connected with an Exclusive OR (XOR) and then the S-box is applied, as shown in Listing 3.2. This part of the algorithm is a good intermediate result to mount a DPA attack. The measurement is focused on the timestep where the described operation is performed and uses a lot of different input plaintexts. Further, Listing 3.2 is used to generate the hypothesis by calculating this equation for every

|    | Listing 3.1: ALS 5-box implemented as lookup table in C/C++. |        |        |       |       |       |       |       |       |       |  |

|----|--------------------------------------------------------------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--|

| 1  | $uint8_t$                                                    | sbox[2 | 256] = |       |       |       |       |       |       |       |  |

| 2  | {                                                            |        |        |       |       |       |       |       |       |       |  |

| 3  | 0x63,                                                        | 0x7C,  | 0x77,  | Ox7B, | 0xF2, | Ox6B, | 0x6F, | 0xC5, | 0x30, | 0x01, |  |

| 4  | 0x67,                                                        | 0x2B,  | OxFE,  | 0xD7, | OxAB, | 0x76, | OxCA, | 0x82, | 0xC9, | 0x7D, |  |

| 5  | OxFA,                                                        | 0x59,  | 0x47,  | 0xF0, | OxAD, | 0xD4, | OxA2, | OxAF, | 0x9C, | OxA4, |  |

| 6  | 0x72,                                                        | OxCO,  | 0xB7,  | OxFD, | 0x93, | 0x26, | 0x36, | 0x3F, | 0xF7, | OxCC, |  |

| 7  | 0x34,                                                        | OxA5,  | 0xE5,  | 0xF1, | 0x71, | 0xD8, | 0x31, | 0x15, | 0x04, | 0xC7, |  |

| 8  | 0x23,                                                        | OxC3,  | 0x18,  | 0x96, | 0x05, | 0x9A, | 0x07, | 0x12, | 0x80, | 0xE2, |  |

| 9  | OxEB,                                                        | 0x27,  | 0xB2,  | 0x75, | 0x09, | 0x83, | 0x2C, | Ox1A, | Ox1B, | 0x6E, |  |

| 10 | Ox5A,                                                        | OxAO,  | 0x52,  | Ox3B, | 0xD6, | 0xB3, | 0x29, | 0xE3, | 0x2F, | 0x84, |  |

| 11 | 0x53,                                                        | OxD1,  | 0x00,  | OxED, | 0x20, | OxFC, | 0xB1, | 0x5B, | Ox6A, | OxCB, |  |

| 12 | OxBE,                                                        | 0x39,  | Ox4A,  | 0x4C, | 0x58, | OxCF, | OxDO, | OxEF, | OxAA, | OxFB, |  |

| 13 | 0x43,                                                        | 0x4D,  | 0x33,  | 0x85, | 0x45, | 0xF9, | 0x02, | 0x7F, | 0x50, | 0x3C, |  |

| 14 | 0x9F,                                                        | OxA8,  | 0x51,  | OxA3, | 0x40, | 0x8F, | 0x92, | 0x9D, | 0x38, | 0xF5, |  |

| 15 | OxBC,                                                        | 0xB6,  | OxDA,  | 0x21, | 0x10, | OxFF, | 0xF3, | 0xD2, | OxCD, | OxOC, |  |

| 16 | 0x13,                                                        | OxEC,  | 0x5F,  | 0x97, | 0x44, | 0x17, | 0xC4, | OxA7, | Ox7E, | 0x3D, |  |

| 17 | 0x64,                                                        | 0x5D,  | 0x19,  | 0x73, | 0x60, | 0x81, | 0x4F, | OxDC, | 0x22, | 0x2A, |  |

| 18 | 0x90,                                                        | 0x88,  | 0x46,  | OxEE, | 0xB8, | 0x14, | OxDE, | 0x5E, | OxOB, | OxDB, |  |

| 19 | 0xE0,                                                        | 0x32,  | Ox3A,  | OxOA, | 0x49, | 0x06, | 0x24, | 0x5C, | 0xC2, | 0xD3, |  |

| 20 | OxAC,                                                        | 0x62,  | 0x91,  | 0x95, | 0xE4, | 0x79, | OxE7, | 0xC8, | 0x37, | 0x6D, |  |

| 21 | 0x8D,                                                        | 0xD5,  | 0x4E,  | OxA9, | 0x6C, | 0x56, | 0xF4, | OxEA, | 0x65, | Ox7A, |  |

| 22 | OxAE,                                                        | 0x08,  | OxBA,  | 0x78, | 0x25, | 0x2E, | Ox1C, | OxA6, | 0xB4, | 0xC6, |  |

| 23 | 0xE8,                                                        | 0xDD,  | 0x74,  | Ox1F, | 0x4B, | OxBD, | 0x8B, | 0x8A, | 0x70, | Ox3E, |  |

| 24 | 0xB5,                                                        | 0x66,  | 0x48,  | 0x03, | 0xF6, | OxOE, | 0x61, | 0x35, | 0x57, | 0xB9, |  |

| 25 | 0x86,                                                        | OxC1,  | Ox1D,  | Ox9E, | OxE1, | 0xF8, | 0x98, | 0x11, | 0x69, | 0xD9, |  |

| 26 | 0x8E,                                                        | 0x94,  | 0x9B,  | Ox1E, | 0x87, | 0xE9, | OxCE, | 0x55, | 0x28, | OxDF, |  |

| 27 | 0x8C,                                                        | OxA1,  | 0x89,  | OxOD, | OxBF, | OxE6, | 0x42, | 0x68, | 0x41, | 0x99, |  |

| 28 | 0x2D,                                                        | OxOF,  | 0xB0,  | 0x54, | OxBB, | 0x16  |       |       |       |       |  |

| 29 | };                                                           |        |        |       |       |       |       |       |       |       |  |

Listing 3.1: AES S-box implemented as lookup table in C/C++.

Listing 3.2: AES S-box usage implemented in C/C++.

1 intermed = sbox[plaintext ^ key];

Figure 3.9: Cipher Block Chaining (CBC) mode for encryption.

possible value of the key byte. Next, the power model is applied and compared to the recorded traces using a correlation coefficient. In the end, the correct key guess leads to the highest correlation to the measurement. This procedure is repeated for every key byte, and the attacker finally knows the whole secret key. A DPA is successfully applied to the AES algorithm.

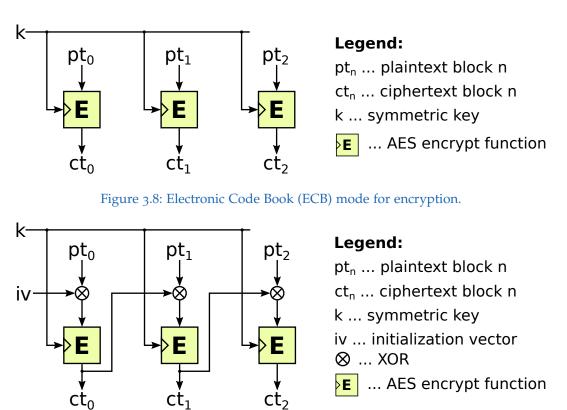

**Modes of Operation**. Block ciphers, like AES, are used in so-called modes of operations to deal with memory junks bigger than a single block. The most straightforward example is the Electronic Code Book (ECB) mode, where the input is split up into blocks and then fed into the block cipher, as shown in Figure 3.8. The ECB mode is however not recommended since equal plaintext blocks result in the same ciphertext block. This problem is fixed in chained operation modes like the Cipher Block Chaining (CBC)

Figure 3.10: Leakage-resilient mode of operation.

mode. In CBC, an initialization vector (iv) is used to get freshness for each ciphertext. With this additional randomness, two identical messages get different initialization vectors and therefore a different ciphertext. As shown in Figure 3.9, every cipher block operates with the same key (k). Therefore the scheme is vulnerable to differential attacks, even if only one ciphertext/plaintext pair is processed because every block creates a trace belonging to the same key (k). By exploiting all the traces, an attacker can gain knowledge of the key.

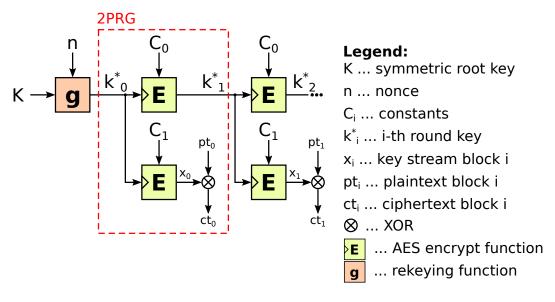

**Leakage Resilience.** To overcome DPA vulnerabilities in modes of operations, Pereira et al. [PSV15] proposed a leakage resilient encryption scheme. The underlying construction is shown in Figure 3.10 and uses an AES encryption function as a Pseudo-Random Generator (PRG). This structure of two PRGs driven with one key is called 2PRG. The scheme is a stream cipher, creating a key stream ( $x_i$ ), the so-called pad. This pad is then applied with the XOR operation on a plaintext to encrypt, or on a ciphertext to decrypt. First, the round key  $k_1^*$  is generated by encrypting the constant  $C_0$  with the key  $k_0^*$ . Second, a pad, used later as a key stream, is generated by encrypting the constant  $C_1$  with the key  $k_0^*$ . As a result, one key, e.g.,

Figure 3.11: Re-keying function (g) used in Figure 3.10.

$k_0^*$  is used no more than twice in an AES encryption function. Therefore, an attacker can observe no more than two different traces using the same key. This property is called 2-limiting. It is a common assumption in the literature [Sta+10] that two traces using the same key are not enough to successfully perform a DPA.

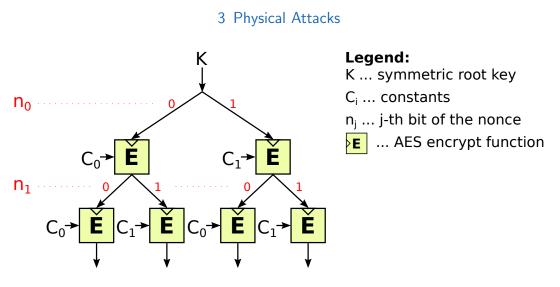

A number only used once (nonce) is included in the scheme to get freshness. If the same content is encrypted twice, the ciphertext will differ, since on every encryption a fresh nonce is used. In perspective of side-channel attacks, this means, that the applied round keys  $(k_0^*, k_1^*, ...)$  will differ and the attacker can not collect more traces with the same key. The re-keying function *g* is used to apply the nonce on the root key *K*. The re-keying function also uses the 2PRG construction using symmetric encryption and is shown in Figure 3.11. Depending on the value of the nonce *n*, a different path through the graph is taken. Every nonce bit decides whether the constant  $C_0$  or the constant  $C_1$  will be encrypted. The output of the re-keying function is derived from the root key *K* and used as first round key  $k_0^*$ . Every possible key inside the re-keying function is only used in two different encryption runs, particularly for the constant  $C_0$  and the same argument regarding differential side-channel attacks as stated before holds.

### 3.3.3 Hash function

Hash functions are fundamental and necessary building blocks in today's cryptography. A hash function is a cryptographic one-way function. MD5, SHA-1 and the families of SHA-2 and SHA-3 are well-known hash functions. A big data block, a so-called image x, is mapped to a constant-size hash value h, e.g., with a size of 256 bits for SHA256, by computing h = H(x). For example, when downloading Linux images, hash values of different algorithms are displayed on the webpage to check for transmission errors after downloading. In this way, a hash function fulfills the same requirements as a checksum, but has additional cryptographic requirements. The requirements are *collision resistance*, *preimage resistance* and *second preimage resistance*.

A collision occurs, if it is computationally feasible to find two images  $x \neq x'$  that result in the same hash value h = H(x) = H(x'). Due to the fact that the hash value computed on a large input is of limited size, usually only a few hundred bits, there will always exist collisions. This problem is known as birthday paradox. The requirement for the hash function is to hinder the calculation of collisions, which is known as *collision resistance*.