Georg Neubauer, BSc.

## A Multi-GPU Implementation of the Discrete Element Method

## MASTER'S THESIS

to achieve the university degree of

**Diplom-Ingenieur**

Master's degree programme: Telematics

submitted to

## **Graz University of Technology**

Supervisor

Ass.Prof. Dipl-Ing. Dr. techn. Christian Steger

Institute for Technical Informatics

Advisor: Ass.Prof. Dipl-Ing. Dr. techn. Christian Steger

In cooperation with Research Center of Pharmaceutical Engineering GmbH

Graz, February 2018

## AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present master's thesis dissertation.

.....

.....

date

(signature)

## Kurzfassung

Ursprünglich von Cundall im Jahre 1971 konzipiert ist die Diskrete-Elemente-Methode (DEM) heutzutage eine der Standardmethoden zur numerischen Bestimmung von Teilchenbewegungen in Simulationen. Grundlegend ist es für diese Methode zu erkennen ob und wann Partikel miteinander kollidieren und aus der dadurch resultierenden Kraftwirkung die neuen Bewegungsparameter (Richtung, Geschwindigkeit, Rotation) pro Teilchen zu errechnen.

Bei der Abbildung von realen Prozessen müssen oft große Partikelsysteme, mit relativ kleinen Partikeln (z.B.: Schüttgut, Puder, etc.) simuliert werden. Um das Simulationsergebnis so akkurat wie möglich zu machen benötigt die DEM jedoch sehr kleine Zeitschritte, wodurch die Berechnungsdauer oft jegliche vernünftige Zeitspanne übersteigt. Aufgrund der zugrundeliegenden Methodik der Diskretisierung wird jedes Partikel für sich separat betrachtet. Dies führt zu einem hohen Grad an Parallelisierbarkeit. Anfangs oft auf CPUs berechnet, werden heutzutage geeignetere Plattformen (z.B.: GPUs, CUDA®, Vektor-Rechner) verwendet um die benötigte Ausführungszeit zu senken.

Ziel dieser Arbeit ist es nun, die bereits im bestehenden Programm (XPS) vorhandene Algorithmik dahingehend zu erweitern, dass durch die Verwendung von mehreren GPUs eine höhere Stufe von Parallelität erreicht wird. Zudem soll im bestehenden Programm die Möglichkeit geschaffen werden die Simulation in Echtzeit zu überwachen ohne dadurch zu viel Prozesszeit zu verschwenden. Nach der Beschreibung der notwendigen Änderungen und der Implementierung wird anhand von Testfällen gezeigt, dass ein deutlicher Speedup erreicht wurde. Zudem wird auch noch darauf hingewiesen, dass durch die Verwendung von mehreren GPUs die abbildbare Problemgröße gesteigert werden kann.

## Schlüsselwörter

Diskrete-Elemente-Methode, Partikelsimulation, CUDA<sup>®</sup>, Multi GPU, Shared memory

## Abstract

Invented by Cundall in the year 1971, the Discrete-Element-Method (DEM) is a standard method for numerical determination particle motions in simulations. A fundamental aspect for this method is to determine if and when particles will collide with each other. By giving the resulting contact force the new motion parameter (like direction, velocity and rotation) can be calculated for each particle separably.

To illustrate real-world processes huge particle sets, consisting of relatively small particles (e.g. bulk solids, powders, etc.), have to be simulated. While getting the simulation outcome as accurate as possible the DEM needs rather small time-step sizes. This leads to unreasonable long total simulation times. The method itself is looking on the particles in a discrete way. With this it is possible to look at each discretization separately, leading to a high degree of parallelism. Modern vectorizing architectures (e.g. GPUs, CUDA) provide many advantages on simulating huge particle systems over the CPUs used formerly, resulting in much faster simulations.

The goal of this thesis is to extend an already existing simulation software (XPS) by introducing new algorithmic features. This is mostly enabling multi-GPU support to achieve a higher level of parallelism. Additionally a method should be invented to observe the simulation in real-time by not wasting to much of it's process's time. After describing the necessary changes and the implementation a result section will show some test cases. It will be shown there how the simulation data can now be shared and which significant speed-ups can be observed. Last but not least, it will be mentioned that the maximum illustratable problem size was increased.

#### Keywords

Discrete-Element-Method, particle simulation, CUDA<sup>®</sup>, multi GPU, shared memory

## Acknowledgment

This master thesis was carried out during the years 2015 to 2018 on the Institute for Technical Informatics at Graz University of Technology.

First, I want to thank Mr. Christian Steger for the possibility to write my master thesis at the Institute for Technical Informatics.

I also want to express my special gratitude to Charles Radeke, who supported me with all of his possibilities over the whole time of this thesis.

A thank goes to Hermann Kureck, Eva Siegmann, Dalibor Jajcevic, Eyke Slama and all of my former colleagues from RCPE which supported me to finish the work.

Special thanks go to my wife Margit, who supported me with some graphical stuff, my daughter Eva and my son Tobias for their excitation.

Last but not least I want do thank my parents, my parents-in-law and all of my siblings and friends, who supported me throughout my student time and I am sure that they will support me in my future.

Graz, February 2018

Georg Neubauer, BSc.

# Contents

| 1        | Intr | roduction 1                           |  |  |  |

|----------|------|---------------------------------------|--|--|--|

|          | 1.1  | Motivation                            |  |  |  |

|          | 1.2  | Objectives                            |  |  |  |

|          | 1.3  | XPS - eXtended Particle System        |  |  |  |

|          | 1.4  | Outline                               |  |  |  |

| <b>2</b> | The  | bry 6                                 |  |  |  |

|          | 2.1  | Discrete Element Method (DEM)         |  |  |  |

|          | 2.2  | Compute Unified Device Architecture   |  |  |  |

|          |      | 2.2.1 Programming Model               |  |  |  |

|          |      | 2.2.2 Hardware Implementation         |  |  |  |

|          |      | 2.2.3 Multi-GPU                       |  |  |  |

|          |      | 2.2.4 Thrust                          |  |  |  |

|          |      | 2.2.5 CUDA Profiling Tools            |  |  |  |

|          | 2.3  | Inter-process Communication (IPC)     |  |  |  |

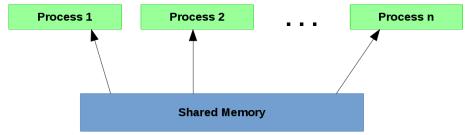

|          |      | 2.3.1 Shared Memory                   |  |  |  |

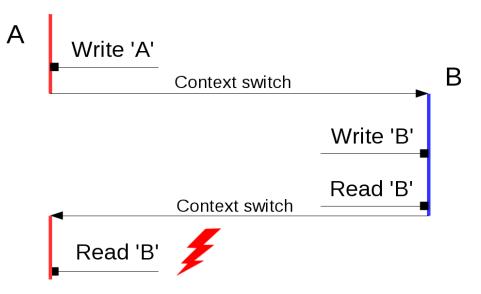

|          |      | 2.3.2 Resource Locking                |  |  |  |

|          |      | 2.3.3 Message-Passing Interface (MPI) |  |  |  |

|          | 2.4  | Program Libraries                     |  |  |  |

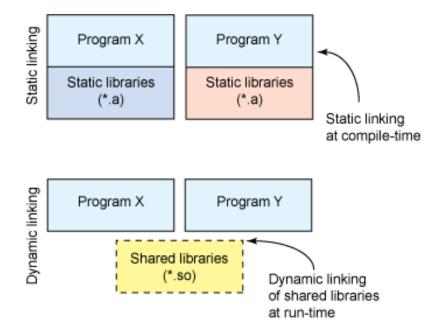

|          |      | 2.4.1 Static Linking                  |  |  |  |

|          |      | 2.4.2 Dynamic Linking                 |  |  |  |

|          |      | 2.4.3 The BOOST C++ Libraries         |  |  |  |

|          | 2.5  | XPS - eXtended Particle System        |  |  |  |

|          |      | 2.5.1 Overview                        |  |  |  |

|          |      | 2.5.2 Current Implementation          |  |  |  |

|          |      | 2.5.3 Implemented DEM Algorithmic     |  |  |  |

| 3        | $\mathbf{Sha}$ | Shared Simulation Data   |                                                                                                                                                  |    |  |  |  |

|----------|----------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

|          | 3.1            | Design                   |                                                                                                                                                  | 34 |  |  |  |

|          |                | 3.1.1                    | Pipes                                                                                                                                            | 34 |  |  |  |

|          |                | 3.1.2                    | Streams                                                                                                                                          | 34 |  |  |  |

|          |                | 3.1.3                    | Shared Memory                                                                                                                                    | 35 |  |  |  |

|          |                | 3.1.4                    | Actual Design                                                                                                                                    | 35 |  |  |  |

|          | 3.2            | Implem                   | $nentation \ldots \ldots$ | 36 |  |  |  |

|          |                | 3.2.1                    | Define data to be shared                                                                                                                         | 36 |  |  |  |

|          |                | 3.2.2                    | The data sharing infrastructure                                                                                                                  | 37 |  |  |  |

|          |                | 3.2.3                    | View and update simulation data                                                                                                                  | 39 |  |  |  |

|          |                | 3.2.4                    | Deploy as program library                                                                                                                        | 40 |  |  |  |

|          |                | 3.2.5                    | Command line arguments                                                                                                                           | 40 |  |  |  |

|          | 3.3            | Results                  | 5                                                                                                                                                | 40 |  |  |  |

|          |                | 3.3.1                    | Usage                                                                                                                                            | 41 |  |  |  |

|          |                | 3.3.2                    | Example                                                                                                                                          | 41 |  |  |  |

| 4        | Mu             | Multi-GPU DEM - Design 4 |                                                                                                                                                  |    |  |  |  |

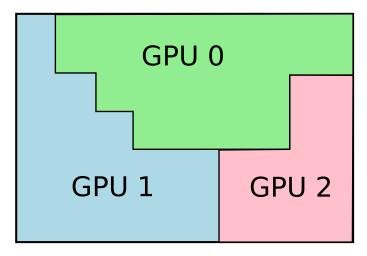

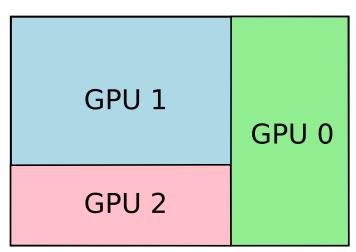

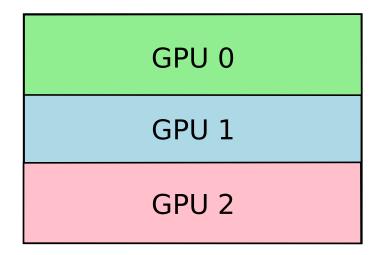

|          | 4.1            | Subdiv                   | riding the simulation world $\ldots$                            | 43 |  |  |  |

|          |                | 4.1.1                    | Choosing a reasonable sub-division                                                                                                               | 43 |  |  |  |

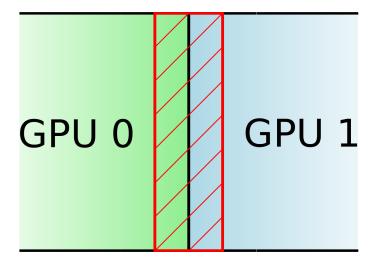

|          |                | 4.1.2                    | Subdivision overlap and halo distribution                                                                                                        | 45 |  |  |  |

|          | 4.2            | Hiding                   | GPU memory transfers                                                                                                                             | 46 |  |  |  |

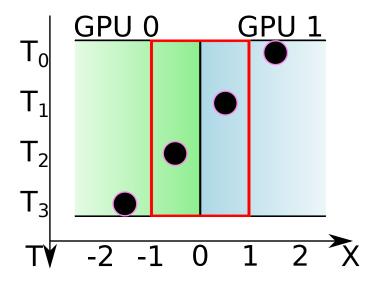

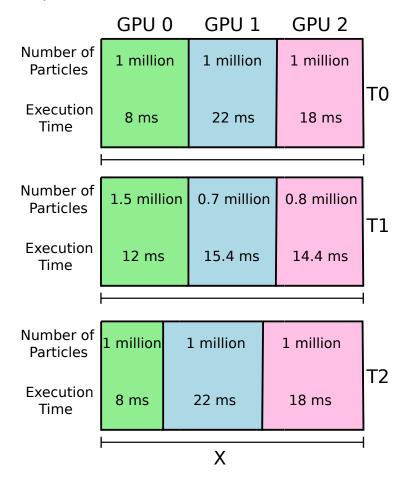

|          | 4.3            | Load balancing           |                                                                                                                                                  |    |  |  |  |

|          | 4.4            | Possibl                  | le implementations                                                                                                                               | 50 |  |  |  |

|          |                | 4.4.1                    | Single-Threaded Multi-GPU (ST-MGPU)                                                                                                              | 52 |  |  |  |

|          |                | 4.4.2                    | Multi-Threaded Multi-GPU (MT-MGPU)                                                                                                               | 52 |  |  |  |

|          |                | 4.4.3                    | Multi-Process Multi-GPU (MP-MGPU)                                                                                                                | 52 |  |  |  |

| <b>5</b> | Mu             | ltiGPU                   | DEM - Implementation                                                                                                                             | 53 |  |  |  |

|          | 5.1            | Prelimi                  | inary work and re-factoring of the existing code                                                                                                 | 53 |  |  |  |

|          | 5.2            | Top-Do                   | own view                                                                                                                                         | 54 |  |  |  |

|          |                | 5.2.1                    | Algorithm solvers                                                                                                                                | 54 |  |  |  |

|          | 5.3            | Multi-                   | Threaded implementation                                                                                                                          | 57 |  |  |  |

|          | 5.4            | Optimi                   | izing execution speed                                                                                                                            | 58 |  |  |  |

|          | 5.5            | Load b                   | Palancing                                                                                                                                        | 59 |  |  |  |

|          |                |                          |                                                                                                                                                  |    |  |  |  |

| 6            | Multi-GPU DEM - Results 6 |                                           |    |  |  |  |

|--------------|---------------------------|-------------------------------------------|----|--|--|--|

|              | 6.1                       | The Test System                           | 60 |  |  |  |

|              | 6.2                       | The Test Case                             | 61 |  |  |  |

|              |                           | 6.2.1 Evaluation Of Memory Usage          | 61 |  |  |  |

|              |                           | 6.2.2 Test Case Variations                | 63 |  |  |  |

|              | 6.3                       | Test 1: Performance Gain                  | 65 |  |  |  |

|              |                           | 6.3.1 Expectations                        | 66 |  |  |  |

|              |                           | 6.3.2 Results                             | 67 |  |  |  |

|              |                           | 6.3.3 Discussion                          | 71 |  |  |  |

|              | 6.4                       | Test 2: Reaching The Test System's Limits | 72 |  |  |  |

| 7            | Con                       | clusion and Outlook                       | 75 |  |  |  |

|              | 7.1                       | Future Work                               | 75 |  |  |  |

| $\mathbf{A}$ | Acro                      | onyms and Glossaries                      | 76 |  |  |  |

| Bi           | bliog                     | graphy                                    | 79 |  |  |  |

# List of Figures

| 1.1  | Simulation of a pharmaceutical mixing device in labor/academic scale $\ldots$        | 3  |

|------|--------------------------------------------------------------------------------------|----|

| 1.2  | Simulation of a pharmaceutical coating device in labor/academic scale $\ . \ .$      | 4  |

| 2.1  | Grid of two-dimensional thread blocks organized in a two-dimensional grid .          | 10 |

| 2.2  | CUDA memory hierarchy                                                                | 12 |

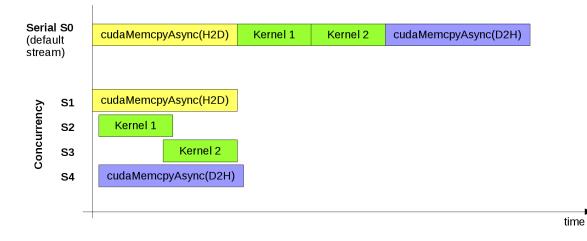

| 2.3  | CUDA stream concurrency                                                              | 14 |

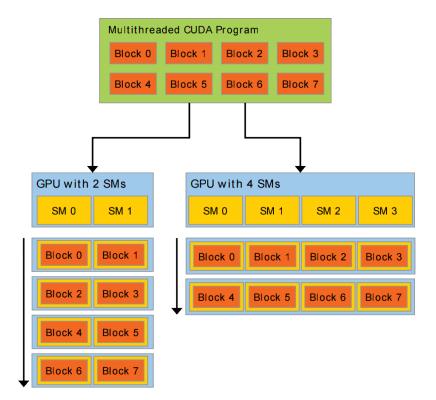

| 2.4  | Dynamic thread-block assignment to available Streaming Multiprocessors .             | 15 |

| 2.5  | Example views of the NVIDIA Visual Profiler                                          | 17 |

| 2.6  | Multiple processes map to same shared memory region                                  | 19 |

| 2.7  | Race condition, two threads using same memory resource $\ldots \ldots \ldots \ldots$ | 20 |

| 2.8  | Static vs. dynamic linking for the Linux operating system                            | 24 |

| 2.9  | The XPS Logo                                                                         | 25 |

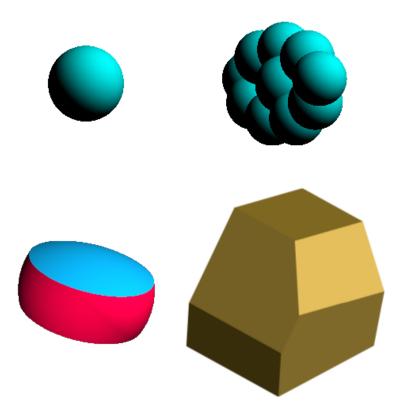

| 2.10 | Particle shapes available in XPS                                                     | 27 |

| 2.11 | Spherical objects sorted into a uniformed grid                                       | 28 |

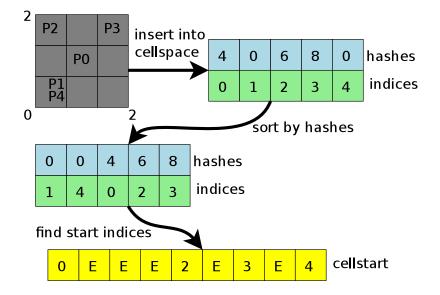

| 2.12 | DEM Preparation phase: From particles in cellspace to $\mathit{cellstart}$ vector    | 29 |

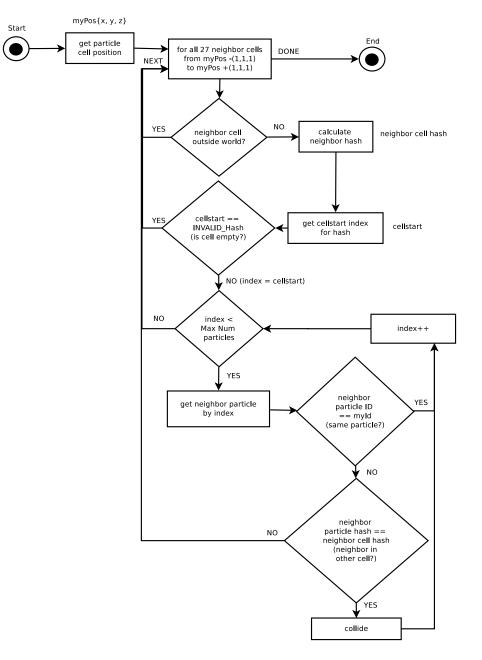

| 2.13 | DEM Collision phase - neighbor search via uniform grid $\ldots \ldots \ldots \ldots$ | 31 |

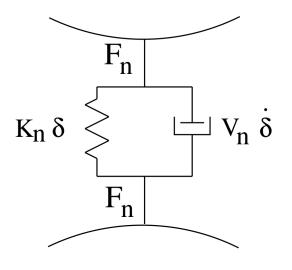

| 2.14 | The spring/damper model that is used for particle collisions                         | 32 |

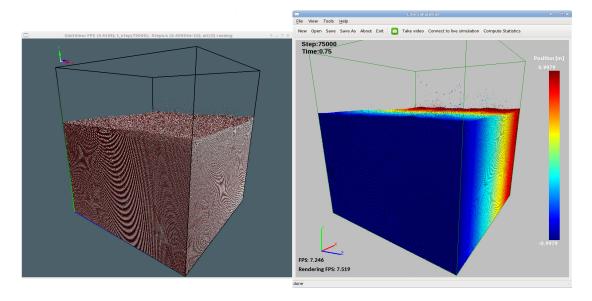

| 3.1  | Connect Live Simulation                                                              | 41 |

| 3.2  | Left internal deprecated viewer, right external live viewer                          | 42 |

| 4.1  | Splitting a 2D domain along an arbitrary path of cell boundaries                     | 44 |

| 4.2  | Splitting a 2D domain along vertical and horizontal planes                           | 44 |

| 4.3  | Splitting a 2D domain along vertical or horizontal planes                            | 45 |

| 4.4  | The boundary between two sub-domains on grid cell layer, with the halo               |    |

|      | highlighted in red.                                                                  | 46 |

| 4.5  | A single particle traveling to another GPU domain                                    | 47 |

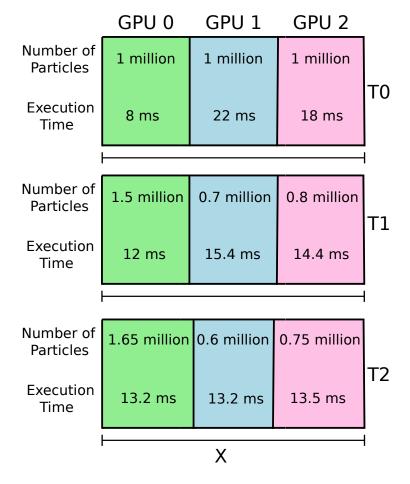

| 4.6  | Example of load balancing by particle number, of a setup with GPUs of                |    |

|      | different speed.                                                                     | 48 |

| 4.7  | Example of load balancing by execution time, of a setup with GPUs of different speed.                                     | 49 |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

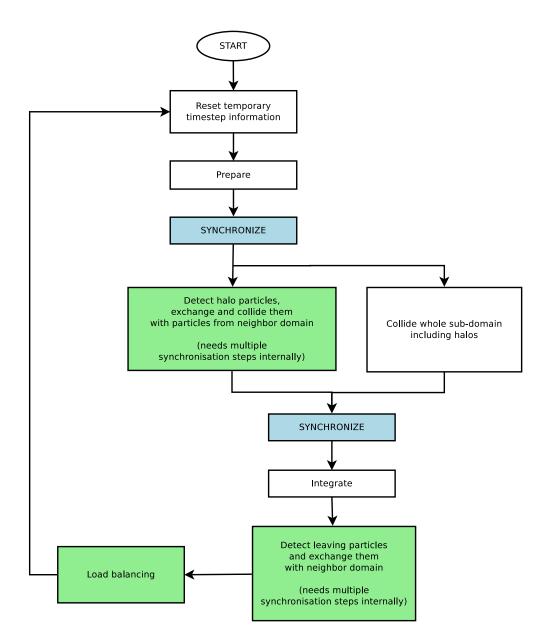

| 4.8  | Simplified flow-chart for a Discrete Element Method (DEM) implementation                                                  |    |

|      | computed on n Graphics Processing Units (GPUs)                                                                            | 51 |

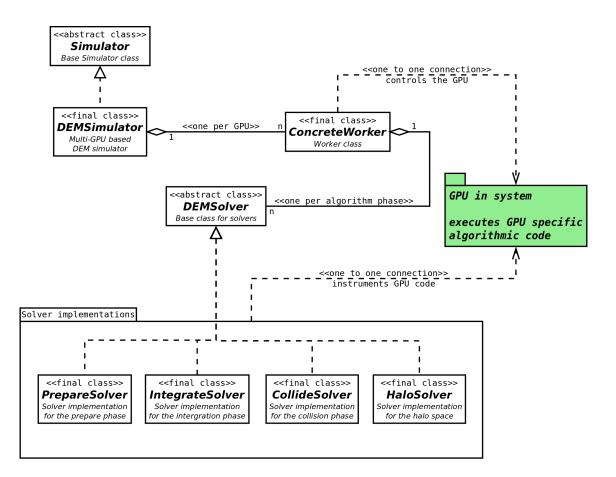

| 5.1  | Class diagram of the minimal <i>Simulator</i> interface                                                                   | 53 |

| 5.2  | Collaboration diagram of the multi-GPU implementation of the DEM                                                          | 55 |

| 5.3  | Class diagram of the minimal <i>DEMSolver</i> interface                                                                   | 55 |

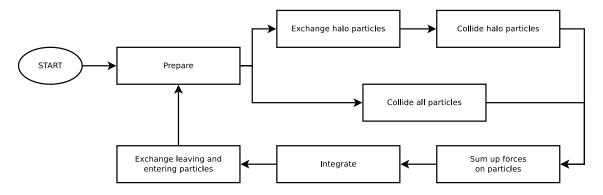

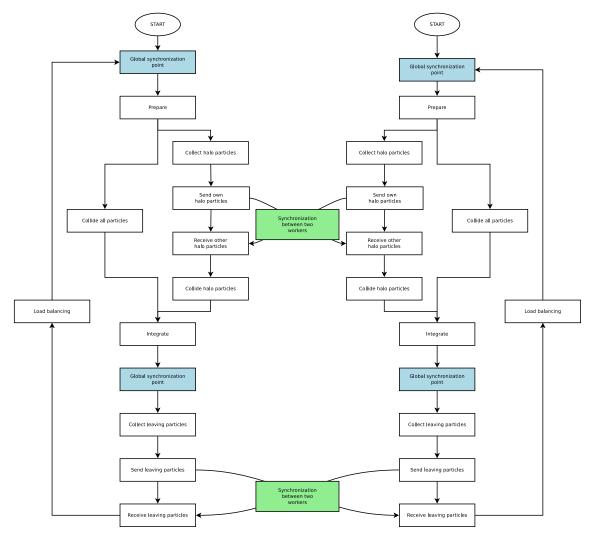

| 5.4  | Dedicated footsteps for the multi-GPU based DEM                                                                           | 56 |

| 5.5  | Detailed flow chart with marks for needed synchronization points between                                                  |    |

|      | workers                                                                                                                   | 58 |

| 6.1  | A view on the test system as used to evaluate the Multi-GPU implementation                                                | 61 |

| 6.2  | Particles falling into a box test case                                                                                    | 62 |

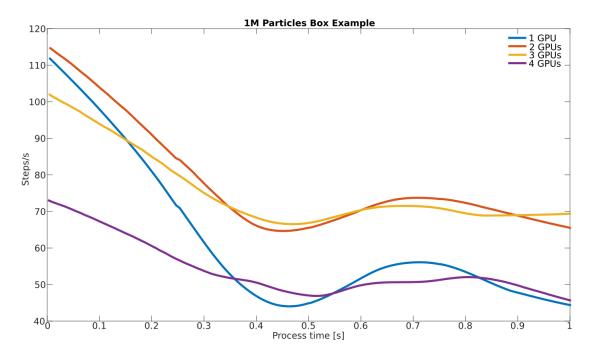

| 6.3  | Test 1: Sub-domain division for the 1 million particles example $\ldots \ldots \ldots$                                    | 66 |

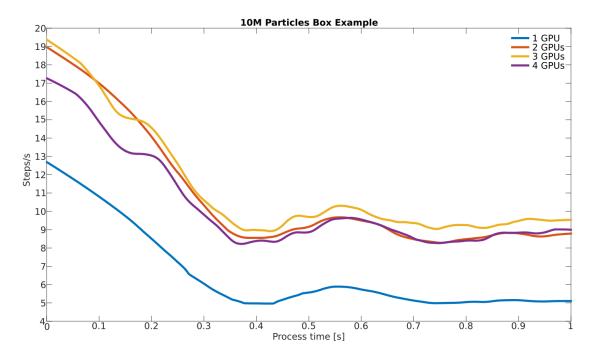

| 6.4  | Test 1: Evolution of processed simulation steps per seconds over the process                                              |    |

|      | time for 1 million particles. $\ldots$   | 68 |

| 6.5  | Test 1: Evolution of processed simulation steps per seconds over the process                                              |    |

|      | time for 10 million particles. $\ldots$  | 68 |

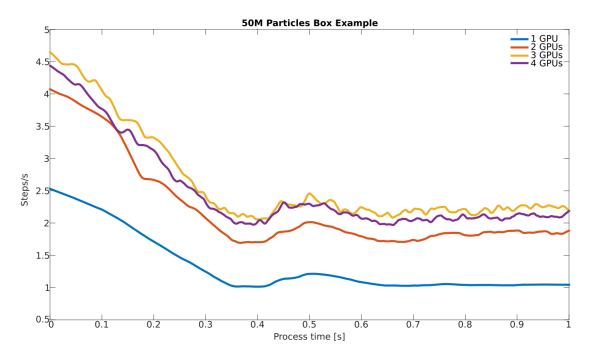

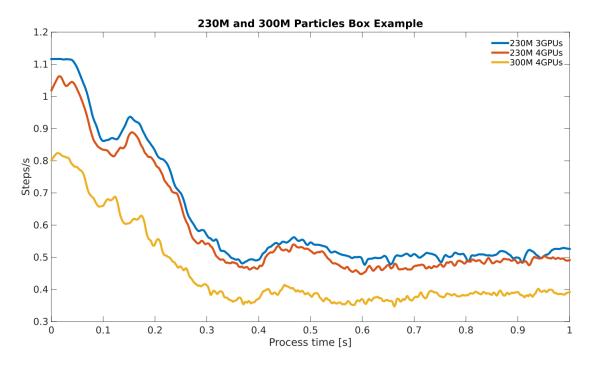

| 6.6  | Test 1: Evolution of processed simulation steps per seconds over the process                                              |    |

|      | time for 50 million particles. $\ldots$  | 69 |

| 6.7  | Test 1: Evolution of processed simulation steps per seconds over the process                                              |    |

|      | time for 100 million particles. $\ldots$ | 69 |

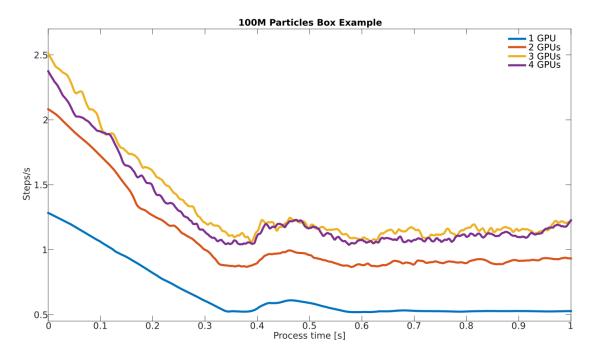

| 6.8  | Test 1: Evolution of processed simulation steps per seconds over the process                                              |    |

|      | time for 230 and 300 million particles. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                             | 70 |

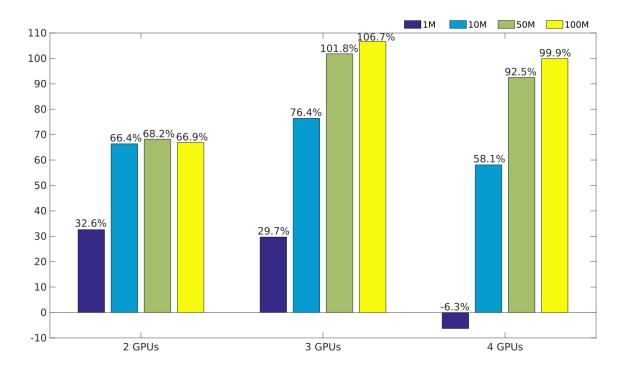

| 6.9  | Test 1: Performance gain in percent compared from using 1 GPU to 2, 3 $$                                                  |    |

|      | and 4 GPUs                                                                                                                | 72 |

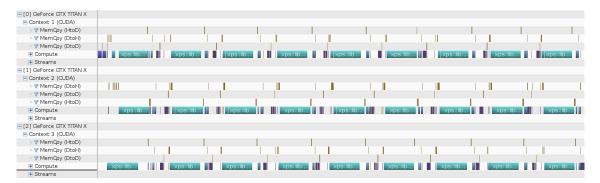

| 6.10 | Test 1: Kernel schedule analysis for the 100 million particles example run-                                               |    |

|      | ning on three GPUs                                                                                                        | 72 |

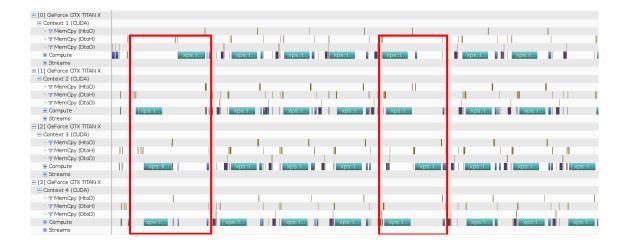

| 6.11 | Test 1: Kernel schedule analysis for the 100 million particles example run-                                               |    |

|      | ning on four GPUs                                                                                                         | 73 |

|      |                                                                                                                           |    |

# List of Tables

| 2.1 | Currently available CUDA <sup>®</sup> compute capabilities (as of 2016) $\ldots \ldots$  | 8  |

|-----|------------------------------------------------------------------------------------------|----|

| 3.1 | Description of data that needs to be shared between simulation and any observing process | 36 |

| 6.1 | Specifications of the test system as used to evaluate the Multi-GPU imple-               |    |

|     | mentation                                                                                | 60 |

| 6.2 | Minimum GPU memory consumption per particle                                              | 63 |

| 6.3 | Test case variations.                                                                    | 64 |

| 6.4 | Test 1: Mapping number of particles examples on number of GPUs                           | 65 |

| 6.5 | Test 1: Average simulation steps per second                                              | 70 |

| 6.6 | Test 1: Wall clock times                                                                 | 70 |

## Chapter 1

# Introduction

This chapter is intended to give a short overview of this master thesis, which was carried out in cooperation with the Research Center Pharmaceutical Engineering (RCPE) and the Institute for Technical Informatics of the Graz University of Technology.

This introduction starts with some words about the motivation and objectives of this thesis. Adjacent I will give a short explanation of the XPS Project from which this thesis arises from. At the end of this chapter you will find an outline of the structure of this master thesis.

## 1.1 Motivation

Many industrial fields are confronted with the optimization of their production processes. Especially companies operating in the fast growing market of pharmaceutical, cosmetic and food industries invest plenty of time and funds in process and prototype development. Common problems in these areas occur with the need for mostly specialized devices. Such devices might be used for mixing raw materials (e.g. powders), coating pills with active and inactive fluids and materials, tablet production (pressing), capsule filling and many other things.

Over the last centuries computer aided simulations were taking up an important role in the development stage of such industrial devices. Not only that simulations are able to vastly improve the development speed of new processes, but they will give also a deeper understanding on well known methods. A very potent simulation method is the DEM.

The DEM [Cun71], [CS79] is suitable to calculate the overall behavior of arbitrary particle flows providing really accurate results. Designed to work with discrete elements it basically acts on all forces emerging from any collisions a single element undergoes. As long as all major forces from different sources, like gravity, particle collisions or wall collision, considered, this method is indeed capable of handling a large number of concrete elements. Elements can be chunks of any kind, like single well-shaped particles, clumps of particles but also more or less of abstract type, like used by Smoothed Particle Hydrodynamics (SPH). The algorithm itself does not care about chunk sizes. So the process will work for small scale (like in powders) as good as for large ones (like rocks).

Existing commercial solutions are acting mostly on Central Processing Units (CPUs). Due to the enormous computation effort needed for the simulation of high amounts of particles, such solutions will reach their reasonable limits in the sub-million range (even on mid-sized clusters). Other solutions follow a different approach. They use a technology introduced a few years ago by NVIDIA where massive parallel processors embedded into commercially available graphic cards can be used to perform miscellaneous computation tasks. This technology is called Compute Unified Device Architecture (CUDA<sup>®</sup>). You'll find an introduction about this technology in section 2.2.

However plain particle simulations are often not enough to take account of all industrial processes. For example, a common production task in pharmaceuticals is to stream fluids into the treated powders. Therefore, more complex simulations are needed. The good news is that the DEM can be extended by considering any forces targeting the particles. So, it is even possible that the introduced forces arose even from other simulations. Such a simulation using different input sources for their calculations is called *coupled*.

The RCPE invented a solver using CUDA<sup>®</sup> within their academic software eXtended Particle System (XPS). Although this programs main business is performing particle simulations on capable graphic cards, it also supports the coupling with a Computational Fluid Dynamics (CFD) simulation provided by AVL FIRE<sup>®</sup>. An introduction about XPS is given in section 1.3. Additionally, you will find a detailed explanation about XPS in section 2.5.

## 1.2 Objectives

The intention behind this thesis is to extend the existing XPS functionality. The first goal is to provide a procedure to share its simulation outcome with other programs in a quick and easy-to-use way. Once provided, the technique should enable the use of external programs providing an online view and analysis of the current internal simulation states.

As a second goal of this work a new DEM solver which utilizes more than one GPU by time was developed. This method is commonly known by the term *Multi-GPU*. On the one hand, this extends the maximal number of particles usable in one single simulation run. On the other hand, the total calculation time will be decreased for a certain number of

particles. As a drawback, massive synchronization issues must be solved and will produce timing overheads.

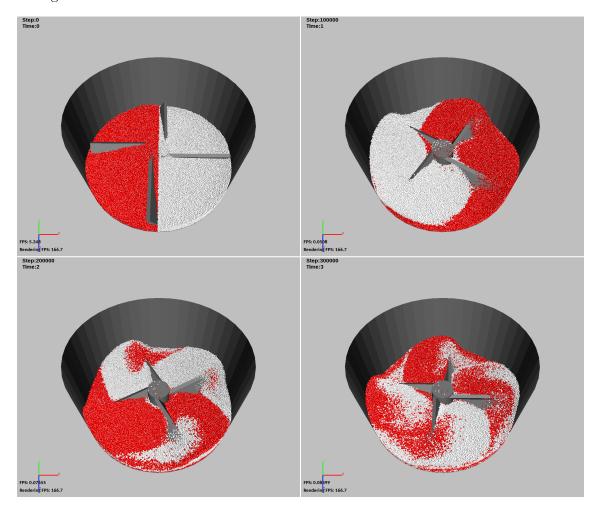

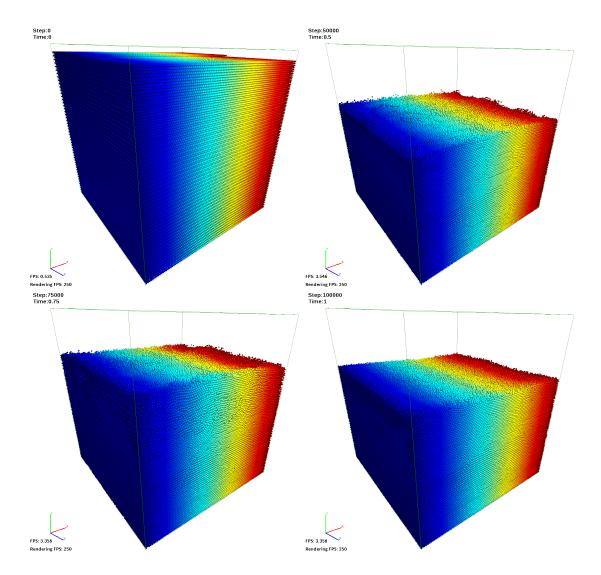

Figure 1.1: Simulation of a pharmaceutical mixing device in labor/academic scale. The blades are rotating with 40 revolutions per minute. Filled in particles are color tagged to allow a visible evaluation of the mixing quality. Upper-left is the initial state at t = 0s. From left to right and up to down are snapshots at t = 1s, t = 2s and t = 3s, respectively. (Source: RCPE GmbH)

## 1.3 XPS - eXtended Particle System

In 2011 the RCPE started with the development of a software prototype named XPS within a joint research project together with some industrial partners. The program acts as a simulation framework embedding DEM based methodologies for usage with miscellaneous sized particles and varying characteristics. By utilizing CUDA<sup>®</sup> compatible

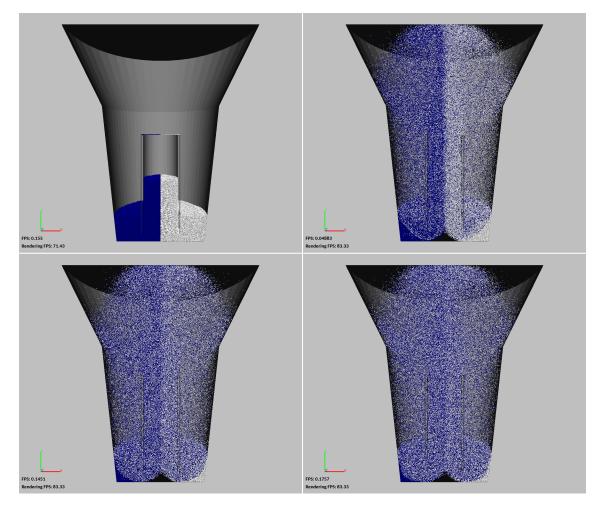

graphic cards of the newest generations, with a *compute compatibility* of 2.0 or higher, this software takes advantage of cutting edge technology. Real world geometries can be processed and may act as impenetrable walls. As shown in figure 1.1, allowing single parts of the geometries to move (e.g. translate or rotate) special devices can be simulated as well. Furthermore XPS supports coupling possibilities between a running simulation with the output of a fluid simulation, shown in figure 1.2. The fluid calculation is provided by AVL FIRE<sup>®</sup> which is a dedicated CFD software.

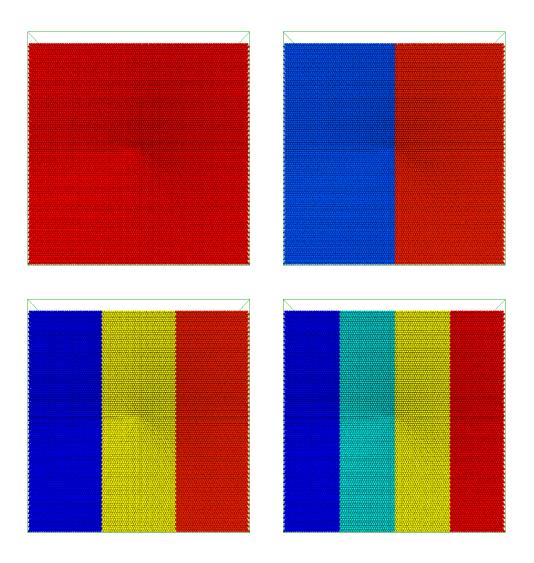

Figure 1.2: Simulation of a pharmaceutical coating device in labor/academic scale, a socalled Wurster-Coater. The particles get fluidized through the inner tube. Usually there sits a coating nozzle on the top of the tube - which is neglected here. Filled in particles are color tagged to allow a visible evaluation of the mixing quality. Upper-left is the initial state at t = 0s. From left to right and up to down are snapshots as time goes on. (Source: RCPE GmbH)

## 1.4 Outline

A short overview of the chapters and structure of this thesis is shown here. The first part is about theory in chapter 2. It shows current state of the art, explaining the DEM and  $CUDA^{\textcircled{R}}$ . Since the implementation part of this thesis heavily depends on them, some background about Inter-process Communication (IPC) and Program Libraries are given. A short overview about BOOST C++ libraries (BOOST) is given as well. The theory chapter ends with an introduction to the simulation framework XPS, showing the current implementation at start of this work. Especially the implemented DEM methodology is outlined.

Starting with the first objective (shared simulation data), described in chapter 3, possible designs are shown and evaluated. Afterwards, the evidently best method is nominated and a possible implementation is shown. At the end of that chapter the results of this work is presented. This is done by explaining by the usage and showing some use cases.

The design of the second objective (Multi-GPU DEM) is presented in chapter 4, giving some background basics and explaining design decisions. Afterward, the implementation is shown in chapter 5. Test cases and their results are shown, evaluated and discussed in chapter 6. Finally, discussion about future development and a conclusion are given in chapter 7.

## Chapter 2

# Theory

### 2.1 Discrete Element Method (DEM)

The *DEM* is a numerical method for computing the stresses and motions of a large quantity of chunks in a limited space. It was originally designed by Cundall in 1971 [Cun71], [CS79] for two dimensional spaces only and was adopted to the third dimension later on. The algorithmic main idea is to handle materials consisting of a set of separate discrete elements. Those elements exist in a limited volume and get handled by the calculation method individually, meaning all contacts, impact forces and displacements are calculated for each particle separately. Mostly all chunks within the simulation space are simplified as regular spherical particles, but the calculation scheme can be extended to various kinds of other shaped elements [GWKE14]. Possible shapes as currently available within XPS are shown in figure 2.10.

The calculation steps are triggered on a time-step based approach successively. All forces the chunks are exposed to get calculated in each single step. The emerging position and velocity changes are integrated by a numerical integration scheme solving Newton's equations of motion.  $\vec{F_i}$  donates the total Force and  $\vec{M_i}$  the total torque affecting the particle *i*. In addition  $\vec{p_i}$  and  $\vec{L_i}$  names the translational and angular momentum of particle *i*.

$$\vec{F}_{i} = \frac{\mathrm{d}\vec{p}_{i}}{\mathrm{d}t}$$

$$\vec{M}_{i} = \frac{\mathrm{d}\vec{L}_{i}}{\mathrm{d}t}$$

(2.1)

The time step size depends on the set of particles, used materials and overall properties. These are for instance the size, shape, stiffness, damping or maximum amount of velocity. A value of around  $T_{step} = 10^{-5}s$  might be useful for particle sizes in the millimeter range. For bigger sized particles a working time step value might be much bigger. In any case a trade-off between accuracy and calculation speed must be taken. Assume having a value of  $T_{step} = 10^{-5}s$  and processing a single step takes 0.1s then calculating a reasonable process time of 10s will take more than one day  $(10^5s)$ .

On initialization time all particles must be positioned in the simulation domain giving an initial velocity and rotation information if desired. It is advisable that there are no overlaps between particles in the basic arrangement. Starting from this initial condition the time-step based method calculates all kinds of forces exposed to the particles. Except from collision impacts also other influences can be considered, like gravitation or a fluid surrounding the particles.

As the number of particles increases the complexity of neighbor search used for the collision detection increases. A trivial algorithm will loop over all particles trying to detect any existing overlaps by any two particles. Although such an approach might be fine for low particle numbers (e.g. <1000), it will suffer in terms of speed for larger simulations, as it shows a time complexity of  $\Theta(n^2)$ . Therefore using a feasible neighbor search algorithm gets important. The approach to increase this limit as followed by XPS is shown in section 2.5.

### 2.2 Compute Unified Device Architecture

Introduced by *NVIDIA* in 2006, the CUDA<sup>®</sup> is a general purpose massive parallel computing architecture. It enables access to the new computational features of any modern *GPU* developed by *NVIDIA*. Thus software developers can use implementations of this architecture to solve complex computational problems in a much more efficient way than on *CPUs*. CUDA<sup>®</sup> imposes new instruction sets and a new programming model to well known computer languages. The Application Programming Interface (API) extends well known programming languages by some special functionality and new keywords. In this section only the binding to the C/C++ programming language will be shown since the concrete practical part of this thesis uses this language. Anyway nearly all assumptions on the bindings can be transferred to all other programming languages supported (e.g. Fortran, JAVA, Matlab or .NET). Since GPUs are currently subject of heavy research and development efforts, the hardware architectures and CUDA<sup>®</sup> are evolving quickly. Therefore *NVIDIA* releases new computational capabilities on a regular basis, introducing more architectural features, like more sophisticated on-device scheduling and parallelism. Table 2.1 shows available architectures and their corresponding computational capabilities.

| Name    | Compute capability |

|---------|--------------------|

|         | 1.0                |

| Teale   | 1.1                |

| Tesla   | 1.2                |

|         | 1.3                |

| Fermi   | 2.0                |

| reimi   | 2.1                |

|         | 3.0                |

| Kepler  | 3.2                |

| Repier  | 3.5                |

|         | 3.7                |

|         | 5.0                |

| Maxwell | 5.2                |

|         | 5.3                |

| Pascal  | 6.0                |

| 1 ascal | 6.1                |

| Volta   | 7.0                |

Table 2.1: Currently available CUDA  $^{\textcircled{R}}$  compute capabilities (as of 2016) (Source: [NVI18])

#### 2.2.1 Programming Model

The CUDA C Programming Guide [NVI18] defines  $CUDA^{\textcircled{R}}$  as a scalable programming model. Enabling development of application software that transparently scales its parallelism with the increasing number of computation cores. Furthermore  $CUDA^{\textcircled{R}}$  keeps the leaning curve for already experienced C and C++ developers low. Therefore the three key abstractions (thread group hierarchies, shared memory and barrier synchronization) are integrated into the C/C++ language. Developers simply have to use newly introduced keywords to invoke CUDA<sup>(R)</sup> related operations.

#### Kernels

For the C/C++ programming language CUDA<sup>®</sup> allows the software developer to define some specialized functions. Those are called *kernels*. A kernel is defined using the \_\_\_\_global\_\_\_\_ declaration specifier. When a kernel is called it gets executed **N** times in parallel by **N** different CUDA<sup>®</sup> threads. In difference to a normal C function which would only be executed once. Beside the \_\_\_\_global\_\_\_\_ also \_\_\_\_device\_\_\_\_ and \_\_\_\_host\_\_\_\_ specifiers exist. The \_\_\_\_device\_\_\_\_ keyword determines solely device sided callable functions which can be called from a kernel only. Beside that, the \_\_\_\_host\_\_\_\_ keyword determines functions callable from CPU threads only. By using a special execution configuration syntax (<<<...>>>) the developer can specify the number of blocks, the thread count (**N**) per block, the size of shared memory and a CUDA<sup>®</sup> stream the kernel should be executed on. For convenience only the first two parameters are mandatory. If not given the shared memory size will default to zero and the stream to be used is the default stream.

Listing 2.1 illustrates a simple kernel call. Two vectors A and B of size N are added together by N different threads. Each thread is given a unique *thread ID* that is accessible within the kernel through the built-in **threadIdx** variable. This ID is used to determine the elements a thread should work with. The output is stored into the vector C.

```

// The kernel: each thread executes one pair-wise addition

__global__ void VecAdd(float* A, float* B, float* C) {

// Get current index

3

int i = threadIdx.x;

4

5

C[i] = A[i] + B[i];

6

}

7

int main() {

8

//\ {\rm Create} data arrays on GPU and prepare data

9

10

11

// Execute the kernel, N times using one single block

VecAdd \ll 1, N \gg (A, B, C);

12

13

14

}

```

Listing 2.1: Simple CUDA C kernel

#### Thread and Block Hierarchy

In the CUDA<sup>®</sup> programming model threads are defined as independent run-able instances utilizing exact one single core within a Streaming Multiprocessor (SM, SMX). This is analogous to the programming model on the host sided CPU core. A single thread is always bounded into a so called *thread block*. Blocks can be arranged in one-, two- or three-dimensional matters. Therefore the **threadIdx** is a 3-component vector identifying the explicit position of a thread within its block. A natural way of invoking computation across different shaped structures, such as a vectors, matrix or volume is achieved by doing so.

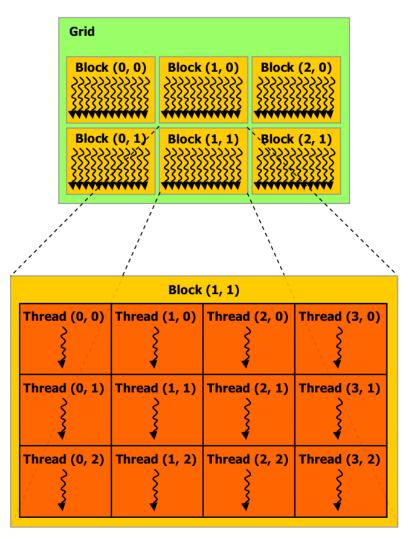

For a one-dimensional block the thread ID is given by the x component of the **threadIdx** vector. For a two-dimensional block of size  $(D_x, D_y)$ , the thread ID of a thread with index (x, y) is given by  $(x + yD_x)$  and for three dimensions  $(D_x, D_y, D_z)$  by  $(x + yD_x + zD_yD_x)$  respectively. Since all threads of a block reside on the same processor core sharing the limited processor resources, the maximum number of threads per block is bound by architecture details. Currently available GPUs support up to 1024 threads per block. Anyway, a kernel can be executed by multiple equally-shaped thread blocks. Therefore the total number of executable threads equals the number of blocks multiplied by the number of threads per block. Thread blocks are organized within one-, two- or three-dimensional grids as shown in figure 2.1

Figure 2.1: Grid of two-dimensional thread blocks organized in a two-dimensional grid (Source: [NVI18])

#### **CUDA** Thread Synchronization

Within a single thread block threads can cooperate with each other. This is done by sharing data through a special *shared memory* block. Therefore the programmer can specify explicit synchronization points within the kernel by calling the \_\_syncthreads() intrinsic function. This acts as a barrier at which all threads in a block have to wait until all others have reached this point. The shared memory is expected to be of low-latency near each processor core.

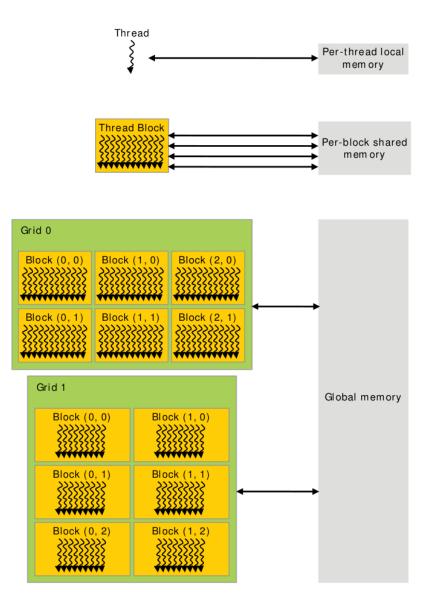

#### Memory Hierarchy

In CUDA<sup>®</sup> different memory regions are defined which can be accessed by threads either in a read-write or a read-only manner, as shown in figure 2.2. Each thread has its own register set and some local memory with private access only. Every thread block shares a general purpose memory along all of his threads. This is the *shared memory* region. On the most recent architecture in 2015, the implementation year of this work, this region had a size of 96kB per block. This was compute capability 5.x (Maxwell).

The *global memory* region is the biggest memory block on the GPU. This region is globally accessible from every thread belonging to any block. Recent graphics cards, e.g. the Titan X, have global memory resources of 12GB or more.

Beside the read-write-able memory also two read-only memory regions exist. Those are the *constant* and *texture* memory spaces. As the name suggests, constant data should be placed into the constant space. Those might be pointers to huge data structures residing in the global space or various steady configuration variables. Through the *texture cache* read-only requests to the global memory can be accelerated. Additionally textures provide addressing calculations, e.g. transparent interpolation, are offered for arrays. Global, constant and texture regions are persistent across kernel launches by the same application.

#### **Streams and Events**

To enable more concurrency within the execution progress the CUDA<sup>®</sup> programming model introduces so called Streams. A Stream is defined as a sequence of operations that execute in the same order as they are issued, similar to a pipeline. Usually all operations issued to a CUDA<sup>®</sup> capable card are scheduled in a special Stream, known as the *NULL Stream* or *Default Stream*. The architecture allows to schedule a set of Streams to do multiple things in parallel, as long as the required resources are available. By default a single card can execute a device kernel and run up to two memory copy processes

Figure 2.2: CUDA memory hierarchy (Source: [NVI18])

in parallel. One copying data from host to device and the second from device to host. However, since the introduction of *compute capability* 2.0+ (*FERMI*) streams may also be used to address concurrency between kernel executions, as long as there are unused resources. So, in theory it is possible to utilize a single card completely, nowadays. Listing 2.2 shows such an example. Figure 2.3 shows a possible execution order as well, as the situation would look like if stream concurrency is not used.

```

// Assume we have two host sided vectors *h_a* and *h_b* and two

// device sided once *d_a* and *d_b*. We now want to make a H2D copy from

3 / / *h_a * to *d_a * and a concurrent D2H copy from *d_b * to *h_b *.

// Also, we will address concurrency for our two kernels.

// Therefore we use four cuda streams *s1*, *s2*, *s3* and *s4*.

// Assume there is no (!) data dependency.

8

// trigger H2D copy async (s1)

cudaMemcpyAsync(h_a, d_a, sizeof(h_a), cudaMemcpyHostToDevice, s1);

9

10

// trigger kernel executions async (s2)

11

kernell \ll grid, block, smem, s2 >>> ();

12

13 kernel2 <<< grid , block , smem, s3 >>> ();

14

// trigger H2D copy async (s4)

15

16 cudaMemcpyAsync(d_b, h_b, sizeof(d_b), cudaMemcpyDeviceToHost, s4);

```

Listing 2.2: Using Multiple CUDA Streams

As a special feature the default stream is always guaranteed to be synchronized with all other streams. Therefore, it is advisable to disclaim the use of the default stream if one wants to exploit stream concurrency. In contrast there is absolutely no implicit synchronization between all other streams. To circumvent this situation CUDA<sup>®</sup> defines some explicit synchronization methods. The first is **cudaDeviceSynchronize**. This function blocks host execution until all work in every used stream is finished, preventing the host program to issue more work to any stream. Another, not so restrictive, method is **cudaStreamSynchronize** which blocks host execution until all work in a specific stream is done. It can be said that both methods act as barriers for the host side only.

To use more convenient synchronization methods, CUDA<sup>®</sup> implements so called Events. Applications can record events to any stream, to keep track of progress within that certain stream. All events work by writing a shared memory location when all previous submitted work on the stream is done. By querying the event (**cudaEventQuery**) one can introduce specific synchronization points within streams. Furthermore, events can also be used to measure GPU execution time of work portions. Therefore, events use a high resolution in device's hardware to store a trigger time stamp. The elapsed time between the triggering of two events can be elected through by the use of **cudaEventElapsedTime**. [NVI18], [Neu13], [Wil13], [Ren11], [Har12]

#### 2.2.2 Hardware Implementation

In general a CUDA<sup>®</sup> capable GPU is built around a certain number of SMs. A SM uses the little-endian representation. If a kernel is called for a specific grid size, all execution blocks

#### CHAPTER 2. THEORY

Figure 2.3: CUDA stream concurrency, possible device side execution sequence in case of sequenced execution (Serial) compared to concurrent execution (with multiple streams) (Source: RCPE GmbH)

are enumerated and distributed to the multiprocessors with free execution capacity. All threads of a thread block execute concurrently on the same multiprocessor. Also, multiple thread blocks can execute on the same multiprocessor in parallel. Once thread blocks finish work new ones will be launched on the abandoned processors. Therefore a GPU containing more SMs will often execute a program faster than one having less computing units. Figure 2.4 shows how a multithreaded program is split into a set of thread-blocks and distributed to all available SMs.

#### Single-Instruction Multiple-Thread (SIMT)

Since a multiprocessor is designed to run hundreds of threads in parallel it is built on a unique architecture called Single-Instruction Multiple-Thread. Every SM creates, manages, schedules and executes threads in groups of 32. This is called a thread warp, which is the smallest execution unit in CUDA<sup>®</sup>. All threads within a warp start together at the same program address and they are constrained to execute the same low level operation at the same time. But each thread has its own instruction address counter and register state. Therefore they are free to branch and execute independently. As a warp executes the same instruction for all of its threads, full efficiency is realized only if all of its 32 threads agree on their execution path. Therefore branching inside single thread warps will cause stalls which will decrease computation speed directly. [Kre11], [NVI18], [Wil13]

Figure 2.4: Dynamic thread-block assignment to available SMs (Source: [NVI18])

#### 2.2.3 Multi-GPU

CUDA<sup>®</sup> has always supported multiple GPUs. Systems with several GPUs generally contain motherboards with two or more GPUs plugged in. There are also special GPUs, implementing a PCI Express bridge chip featuring multiple GPUs on the same board (e.g. GeForce GTX 690, GeForce Titan Z). Furthermore, a multi-GPU experience might also be exploited by having concrete computer nodes containing its own GPUs.

#### Single-Threaded Multi-GPU (ST-MGPU)

Till the release of CUDA<sup>®</sup> 4.0 each GPU has to be controlled by a separate CPU thread. For workloads that require a lot of CPU power, this was never very onerous. However, for programs that do not require multiple CPU threads at all this fact adds additional, mostly unwanted, IPC duties. So, by using a modern CUDA<sup>®</sup> runtime, a single thread can drive multiple GPUs. Therefore, it has to keep track of the currently used GPU and needs to switch between the GPUs as needed. This is done by calling the **cudaSetDevice** function. The most important advantage of this method is that one does not need to keep an eye on pitfalls which can occur in a multi-threaded/process environment. This includes locking and race condition issues. As a drawback it has to be stated that managing multiple GPUs

#### CHAPTER 2. THEORY

in one single thread will cause the program code to get much more complicated.

#### Multi-Threaded Multi-GPU (MT-MGPU)

As already said, workloads that require a lot of CPU power can also utilize a set of GPUs in separate CPU threads. So, the full power of modern multi-core processors can be unlocked through multi-threading. As for the single threaded approach each thread has to be sure that its GPU is currently set as active device. That requires some inter-thread locking methodologies. Finally spoken, multi-threading just for driving multiple GPUs might add tremendous locking and inter-thread communication issues, but it might simplify the code base and reduce controlling overheads.

#### Multi-Process Multi-GPU (MP-MGPU)

As for the multithreaded approach it is as well possible to use multiple GPUs within a program splitting its work on several CPU processes. Like for normal multi-process programs one has to implement interprocess communication, such as Massage-Passing Interface (MPI). Beyond that, a multi-process-multi-GPU implementation will not differ that much from the multithreaded approach. At least every CPU process might utilize its assigned GPUs in a multithreaded way as well. So, the biggest advantage of porting multi GPU programs to many computing nodes is that it will give one a tremendous boost in speed and maximum problem size. [NVI18], [Wil13]

#### 2.2.4 Thrust

Thrust, developed by NVIDIA and shipped within its parallel execution toolkit, is a remarkable and overall useful extension to the CUDA<sup>®</sup> functionality. It provides a C++ template library based on the Standard Template Library (STL), which is indeed fully interoperable with CUDA<sup>®</sup> C. By using this high level interface it only takes a minimum of effort to implement a maximum performance parallel application. Basically Thrust defines two template based container object types. The first one (*thrust::host\_vector*<*T*>) is host side based and the other one resides on the device. Except from their GPU binding both of them are truly comparable to their STL relative (*std::vector*<*T*>). The usage of this vectors hides any nested calls to low level functions like *cudaMalloc*, *cudaFree* and *cudaMemcpy* behind their object oriented API.

Additionally Thrust brings in generic and fast algorithms for data manipulation of parallel primitives, like scan, sort and reduce. Since all algorithms work for both provided vector types, they can be composed together and extended by own ones implementing concise and readable source code. The data exchange procedure is simplified by the use of class operators. Listing 2.3 shows how Thrust simplifies CPU and GPU data utilization seamlessly.

In earlier CUDA<sup>®</sup> versions Thrust calls always used the default stream only. That leads to some performance issues if Thrust based algorithms were used in implementations driving multiple execution streams. In newer versions, this problem is solved. Now, there is an implementation using **cuda::par.on(stream)** do support multiple streams [NVI15].

```

// initialize random values on host

thrust:: host_vector \langle int \rangle h_vec (1000);

3

thrust::generate(h_vec.begin(), h_vec.end(), rand);

// copy values to device

5

thrust :: device_vector <int> d_vec = h_vec;

6

7

// compute sum on host

8

int h_sum = thrust::reduce(h_vec.begin(), h_vec.end());

9

10

11

// find extremas on device

12 int d_min = thrust::min_element(d_vec.begin(), d_vec.end());

13 int d_max = thrust::max_element(d_vec.begin(), d_vec.end());

```

Listing 2.3: Simple Thrust Example

| Image: Second Control Contecontrol Control Control Control Control Cont                                | File View Run Help                          |               |                                  |                       |                            |                               |              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------|----------------------------------|-----------------------|----------------------------|-------------------------------|--------------|

| 161.7 ms       161.9 ms       161.9 ms       162.ns         Process: 11119       1117 ms       161.8 ms       161.9 ms       162.ns         Process: 11119       Thread: :439413584       CUDAkernel1DCT(float*, int.)       Name       Value         Statt       101.322 ms       Duration       106.132 ms       101.322 ms         Driver AR       CuDAkernel1DCT(float*, int.)       Statt       106.132 ms         I Of Gefore GTX 480       CuDAkernel1DCT(float*, int.)       Block Size       [64.64.1]         Block Size       [68,1]       Begisters/Thread       14         Shared Memory/Block       Size       [68,1]       Begisters/Thread       14         Shared Memory/Block       CuDAkernel1DCT(float*, int.)       Memory Clobil Store Efficiency       100%         I O Goods Store Efficiency       100%       DRAM Utilization       10.9% (18.4:       Instruction         I O Shi 10 CUDAke       CUDAkernel1DCT(float*, int.)       Memcpy DtoH [sync]       Stated Memory Relay Overhood       515%         Stream 1       CUDAkernel2UDAke       CUDAkernel1DCT(float*, int.)       Memcpy DtoH [sync]       Stated Memory Relay Overhood       515%         Stream 1       CUDAkernel2UDAke       O%       O%       Stated Memory Relay Overhood       515%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | iii 2 4                                     |               |                                  |                       |                            |                               |              |

| Process: 11119   Thread: .149413584   Buttime API   Driver API   El 10] Geforce GTX 480   El Consult (CUDA)   Y MemCpy (Itab)   Y 0.75 [101] CUDAke   Y 0.76 [11] CUDAke                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 🜒 *dct8x8.vp 🛿                              |               |                                  |                       | - 0                        | 🖬 Properties 🛿 🖬 Detail Graph | is 🗖         |

| Thread: -1494115584       Value         Runtime AP       CudaMemcpy2D         Driver AP       CudaMemcpy2D         Gl () Geforce GTX 400       Grid Size         Control () CudaKemel ()                                                                                                                                                                             |                                             | 161.7 ms      | 161.8 ms                         | 161.9 ms              | 162 ms                     | CUDAkernel1DCT(float*, int,   | int, int)    |

| Image: Thread: -1494415584       Start       161.329 ms         Buntime API       CudaMemcpy2D         Image: Context 1 (CUDA)       Image: Context 1 (CUDA)         Image: Context 1 (CUDA)       Image: CudAkemel1DCT(float*, int         Image: CudAkemel2Uca       CUDAkemel2Uca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Process: 11119                              |               |                                  |                       |                            | Name                          | Value        |

| Runtime API       CudaMemcpy2D         Diver API       Grid Size         I (0) Geforce GTX 480       [64,64,1]         Block Size       [64,64,1]         Block Size       [68,8,1]         Y MemCpy (thto)       Memcpy DtoH [sync]         I (0) Global Load Efficiency       1/4         Shared Memory/Block       Size by Size         I (0) Global Load Efficiency       1/0%         I (0) Katemel (0) Global Load Efficiency       1/0%         I (1) Cubke       CUDAkemel (0) Global Load Efficiency       1/0%         I (1) Cubke       CUDAkemel (0) Global Load Efficiency       0%         I (1) Cubke       Global Load Efficiency       0%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Thread: -1494415584                         |               |                                  |                       |                            |                               |              |

| Unvert AM       Grid Size       [64,64,1]         © Iol Geforce GTX 480       Grid Size       [64,64,1]         © Context 1 (CUDA)       Memcpy (Into)       Islock Size       [63,81]         W Memcpy (Into)       Memcpy (Into)       Islock Size       [64,64,1]         © Context 1 (CUDA)       Memcpy (Into)       Islock Size       [64,64,1]         W Memcpy (Into)       Memcpy (Into)       Islock Size       [64,64,1]         © Compute       CUDAkemelQua       CUDAkemelQua       CUDAkemelQua         V 0.0% 10 (UDAke       CUDAkemelQua       CUDAkemelQua       CUDAkemelQua         V 0.0% 11 (UDAke       CUDAkemelQua       CUDAkemelIDCT(float*, int       Memcpy DtoH [sync]         W 0.0% 11 (UDAke       CUDAkemelIDCT(float*, int       Memcpy DtoH [sync]       Islock Size       0 Sis         Stream 1       CUDAkemelQua       CUDAkemelIDCT(float*, int       Memcpy DtoH [sync]       Islock Size       0 Sis         Stream 1       CUDAkemelQua       CUDAkemelIDCT(float*, int       Memcpy DtoH [sync]       Islock Size       0 Sis         Stream 1       CUDAkemelQua       CUDAkemelIDCT(float*, int       Memcpy DtoH [sync]       Islock Size       0 Sis         I console I Settings       Malysis Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Runtime API                                 |               |                                  |                       | cudaMemcpy2D               |                               |              |

| Bio Deficie Vi (CUDA)       Block Size       [8,8,1]         W Memcpy (Itob)       Memcpy (DtoH)       Registers/Thread       14         W Memcpy (Itob)       Memcpy (DtoH)       Shared Memory/Block       512 bytes         CUDAkemel/Qua       CUDAkemel/LIDCT(float*, int       Memory       Global Load Efficiency       n/a         W 0.0% 11 CUDAke       CUDAkemel/LIDCT(float*, int       CUDAkemel/LIDCT(float*, int       Branch Divergence Overhee 0%         W 0.0% 11 CUDAke       CUDAkemel/LIDCT(float*, int       Memcpy DtoH [sync]       Instruction         W 0.0% 11 CUDAke       CUDAkemel/LIDCT(float*, int       Branch Divergence Overhee 0%       Site         W 0.0% 11 CUDAke       CUDAkemel/LIDCT(float*, int       Memcpy DtoH [sync]       Shared Memory Replay Overhee 0%       Site         Streams       CUDAkemel/Qua       CUDAkemel/LIDCT(float*, int       Memcpy DtoH [sync]       Shared Memory Replay Overhee 0%       Site         Malysis Streams       CUDAkemel/Qua       CUDAkemel/LIDCT(float*, int       Memcpy DtoH [sync]       Streams       Site       Sit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Driver API                                  |               |                                  |                       |                            |                               |              |

| Y Memcpy (httoD)       Registers/Thread       14         Y Memcpy (httoD)       CUDAkemel/Qua       Shared Memory/Block       512 bytes         Y 0.75 (1b11 CUDAke       Wemcpy DtoH (sync)       Wemcpy (btoD)       Wemcpy (btoD)       Wemcpy (btoD)         Y 0.75 (1b11 CUDAke       CUDAkemel/Qua       CUDAkemel/Qua       CUDAkemel/Qua       10.9% (18.4:         Y 0.75 (1b11 CUDAke       CUDAkemel/Qua       CUDAkemel/Qua       10.9% (18.4:       Instruction         Y 0.0% (11 CUDAke       CUDAkemel/Qua       CUDAkemel/Qua       CUDAkemel/Qua       0%         Y 0.0% (11 CUDAke       CUDAkemel/Qua       CUDAkemel/Qua       0%       0%         Streams       CUDAkemel/Qua       CUDAkemel/Qua       CUDAkemel/Qua       0%         Streams       CUDAkemel/Qua       CUDAkemel/Qua       Memcpy DtoH (sync)       0%         Global Kernel/Qua       CUDAkemel/Qua       Memcpy DtoH (sync)       0%       0%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | [0] GeForce GTX 480                         |               |                                  |                       |                            |                               |              |

| Wemcpy (DtoH)       Memcpy DtoH [sync]         Wemcpy (DtoO)       CuDAkemelQua         CUDAkemelQua       CuDAkemelQua         Y 0.7% [101] CuDAk       CuDAkemelQua         Y 0.0% [11] CuDAke       CuDAkemelQua         Y 0.0% [12] CuDAke       CuDAkemelQua         Y 0.0% [12] CuDAke       CuDAkemelQua         Y 0.0% [12] CuDAke       CuDAkemelIDCT(float*, int         Y 0.0% [12] CuDAke       0%         Y 0.0% [12] CuDAke       0%         Stream 1       CuDAkemelQua         CuDAkemelQua       CuDAkemelIDCT(float*, int         Memcpy DtoH [sync]       0%         Global Memory Replay Overhead       51%         Stream 1       CuDAkemelQua         CuDAkemelQua       CuDAkemelIDCT(float*, int         Memcpy DtoH [sync]       0%         Global Memory Replay Overhead       51%         Global Memory Replay Overhead       51%         Global Memory Replay Overhead       0%         Global Memory Replay Overhead       0%         Global Memory Replay Over                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |               |                                  |                       |                            | Block Size                    | [ 8,8,1 ]    |

| WemCpy (DtoD)       Duble of the provided of the provi                                         |                                             |               |                                  |                       |                            | Registers/Thread              | 14           |

| CUDAkemelQua CUDAkemelQua.                                                                                                                                                                                                                                                                                                                                                                                               |                                             |               |                                  | Me                    | emcpy DtoH [sync]          | Shared Memory/Block           | 512 bytes    |

| Image: Stream 1       CUDAkemelQua       CUDAkemelQua       CUDAkemelQua       Global Store Efficiency       100%         Image: Stream 1       CUDAkemelQua       CUDAkemelQua       Instruction       Branch Divergence Overhe       0%         Image: Stream 1       CUDAkemelQua       CUDAkemelQua       CUDAkemelQua       Shared Memory Replay Overhead       6 51%         Image: Stream 1       CUDAkemelQua       CUDAkemelIDCT(float*, int       Memcpy DtoH [sync]       Global Cache Replay Overhead       6 51%         Image: Stream 1       CUDAkemelQua       CUDAkemelIDCT(float*, int       Memcpy DtoH [sync]       Global Cache Replay Overhead       6 51%         Image: Stream 1       CUDAkemelQua       CUDAkemelQua       CUDAkemelQua       CUDAkemelQua       Memcpy DtoH [sync]         Image: Stream 1       CUDAkemelQua       CUDAkemelQua       CUDAkemelQua       Memcpy DtoH [sync]       Incal Cache Replay Overhead       6 0%         Image: Stream 1       CUDAkemelQua       CUDAkemelQua       Memcpy DtoH [sync]       Incal Cache Replay Overhead       0%         Image: Stream 1       CUDAkemelQua       CUDAkemelQua       Memcpy DtoH [sync]       Incal Cache Replay Overhead       0%         Image: Stream 1       CUDAkemelQua       Memcpy Overhead [ 35.1% avg. for k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 A A A A A A A A A A A A A A A A A A A     |               |                                  |                       |                            | - Memory                      |              |

| Y 0.7% [101] CUDAk       CUDAkemelQua       Global Store Efficiency       100%         Y 0.0% [1] CUDAk       CUDAkemelQua       CUDAkemelQua       10.9% [18:4]         Y 0.0% [1] CUDAke       CUDAkemelQua       CUDAkemelQua       10.9% [18:4]         Y 0.0% [1] CUDAke       Y 0.0% [1] CUDAke       0%       10.9% [18:4]         Y 0.0% [1] CUDAke       Streams       51%       51%         Streams       CUDAkemelQua       CUDAkemel1DCT(float*, int       Memcpy DtoH [sync]       0%         Global Memory Replay Over       0%       51%       51%       51%         Streams       CUDAkemel1DCT(float*, int       Memcpy DtoH [sync]       0%       0%         Analysis 2%       Details       Console       Settings       0%         Multiprocessor       Malysis Results       High Branch Divergence Overhead [ 35.1% avg, for kernels accounting for 39.1% of compute ]       More         A combination of global, shared, and local memory replays are causing significant instruction issue overhead.       More         High Global Memory       Wistruction Replay Overhead [ 45.9% avg, for kernels accounting for 39.1% of compute ]       Accombination of global, shared, and local memory replays are causing significant instruction issue overhead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             | CUDAkernelQua | CUDAkernel1IDCT(float*, i        | nt                    |                            | Global Load Efficiency        | n/a          |