Christian Liebminger, BSc

## A PVT tolerant 16 MHz RC-Oscillator for Automotive Applications

### MASTERARBEIT

zur Erlangung des akademischen Grades

Diplom-Ingenieur

Masterstudium Elektrotechnik

eingereicht an der

### Technischen Universität Graz

Betreuer

Dipl.-Ing. Dr.techn. Mario Auer

Institut für Elektronik

## EIDESSTATTLICHE ERKLÄRUNG AFFIDAVIT

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe. Das in TUGRAZonline hochgeladene Textdokument ist mit der vorliegenden Masterarbeit identisch.

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present master's thesis.

Datum / Date

Unterschrift / Signature

### Abstract

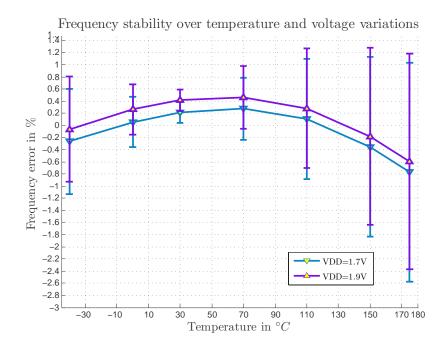

In this thesis, I designed and implemented a RC-Oscillator which is optimized for a high frequency accuracy over PVT variations. The oscillator uses a voltage averaging feedback concept, which fully compensates the comparator delay. A test-chip with a typical frequency of 16 MHz was fabricated in a  $0.14\mu m$  CMOS ABCD9-Power SOI process. The results of the test chips aren't available yet. However, the simulation results show that there is a  $\pm 6\sigma$  frequency stability of  $\pm 1.65\%$  over a temperature and supply voltage range of  $-40^{\circ}C$  to  $150^{\circ}C$  and 1.7V to 1.9V respectively.

#### Kurzfassung

In der folgenden Diplomarbeit entwickelte ich einen RC-Oszillator, welcher für eine hohe Frequenzstabilität über PVT-Variationen optimiert wurde. Das Grundkonzept des Oszillators nützt eine mittelwertbildende Rückkopplung, wodurch das Komparator Delay vollständig kompensiert wird. Nach der Entwicklung des 16 MHz Oszillators wurde dieser in einem Test Chip ( $0.14\mu m$  CMOS ABCD9-Power SOI Prozess) verifiziert. Diese Daten sind jedoch noch ausständig. Die Simulationsergebnisse ergaben eine  $\pm 6\sigma$  Frequenzstabilität von  $\pm 1.65\%$  bei einer Temperatur und Versorgungspannungsvariation von  $-40^{\circ}C$  -  $150^{\circ}C$ , und 1.7V - 1.9V.

## Acknowledgment

Here I would like to thank everyone, who has contributed through his professional and personal support to the success of this thesis. First of all I would like to thank Mr. Sven Simons, who has supported me by all means the whole way. Furthermore I would like to thank Mr. Robert Kofler for providing the interesting topic of the thesis. And I would also like thank to Mr. Mario Auer for reviewing this thesis. In the end I would like to give my special thanks to my loving parents for being there all the time for me and giving me the motivation.

I dedicate this thesis to my dear friend Jürgen Karner, who died far too young in an avalanche accident.

### About NXP Semiconductors

NXP (which stands for Next eXPerience) Semiconductors is a Dutch semiconductor manufacturer with the headquarter in Eindhoven, the Netherlands. Originally NXP arose from the Philips internal semiconductor group, also known as "Philips Semiconductors". NXP was founded in 2006 as Philips sold its semiconductor group to private investors. In the meantime, NXP has become one of the world's leading semiconductor manufacturers with operations in more than 25 countries and sales of 4.36 billion dollars in 2012 [60] [61].

NXP Semiconductors has over 55 years of experience in different business areas such as High Performance Mixed Signal, Automotive, Identification, Infrastructure and Industrial and Computing [42].

This thesis is done in collaboration with NXP.

## Contents

| 1        | $\mathbf{Intr}$                               | oduction                                                                                                                                                                                                                                                    | 19                                                                                             |

|----------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|          | 1.1                                           | Motivation and target specification                                                                                                                                                                                                                         | 21                                                                                             |

|          |                                               | 1.1.1 Target specification of the oscillator                                                                                                                                                                                                                | 23                                                                                             |

| <b>2</b> | Osc                                           | illator topologies                                                                                                                                                                                                                                          | <b>25</b>                                                                                      |

|          | 2.1                                           | MEMS-oscillators                                                                                                                                                                                                                                            | 25                                                                                             |

|          | 2.2                                           | LC-oscillators                                                                                                                                                                                                                                              | 26                                                                                             |

|          | 2.3                                           | RC-harmonic oscillator                                                                                                                                                                                                                                      | 28                                                                                             |

|          | 2.4                                           | Relaxation-oscillators                                                                                                                                                                                                                                      | 29                                                                                             |

|          | 2.5                                           | Ring-oscillators                                                                                                                                                                                                                                            | 30                                                                                             |

|          | 2.6                                           | Conclusion and design choice                                                                                                                                                                                                                                | 31                                                                                             |

|          |                                               |                                                                                                                                                                                                                                                             |                                                                                                |

| 3        | $\mathbf{The}$                                | eoretical design considerations                                                                                                                                                                                                                             | 35                                                                                             |

| 3        | <b>The</b><br>3.1                             | coretical design considerations           Start-up and oscillation mechanism                                                                                                                                                                                | <b>35</b><br>35                                                                                |

| 3        |                                               | ů – Elektrik                                                                                                                                             |                                                                                                |

| 3        |                                               | Start-up and oscillation mechanism                                                                                                                                                                                                                          | 35                                                                                             |

| 3        | 3.1                                           | Start-up and oscillation mechanism                                                                                                                                                                                                                          | $\frac{35}{37}$                                                                                |

| 3        | 3.1                                           | Start-up and oscillation mechanism                                                                                                                                                                                                                          | 35<br>37<br>40                                                                                 |

| 3        | 3.1                                           | Start-up and oscillation mechanism            3.1.1       Start-up sequence           Power-down mode            3.2.1       Bias temperature instability                                                                                                   | 35<br>37<br>40<br>40                                                                           |

| 3        | 3.1                                           | Start-up and oscillation mechanism            3.1.1       Start-up sequence           Power-down mode            3.2.1       Bias temperature instability           3.2.2       Hot carrier injection                                                       | <ul> <li>35</li> <li>37</li> <li>40</li> <li>40</li> <li>42</li> </ul>                         |

| 3        | 3.1<br>3.2                                    | Start-up and oscillation mechanism             3.1.1       Start-up sequence             Power-down mode              3.2.1       Bias temperature instability             3.2.2       Hot carrier injection             3.2.3       Design considerations  | <ul> <li>35</li> <li>37</li> <li>40</li> <li>40</li> <li>42</li> <li>43</li> </ul>             |

| 3        | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Start-up and oscillation mechanism             3.1.1       Start-up sequence             Power-down mode              3.2.1       Bias temperature instability             3.2.2       Hot carrier injection              3.2.3       Design considerations | <ul> <li>35</li> <li>37</li> <li>40</li> <li>40</li> <li>42</li> <li>43</li> <li>44</li> </ul> |

|   | 3.5  | Maximum frequency spread across temperatures                                       | 47 |

|---|------|------------------------------------------------------------------------------------|----|

|   | 3.6  | Influence of the offset of the OTA                                                 | 47 |

|   |      | 3.6.1 Frequency changes due to offset voltage                                      | 47 |

|   | 3.7  | Influence of the comparator offset voltage                                         | 18 |

|   |      | 3.7.1 Duty-cycle variation due to mismatch                                         | 49 |

|   | 3.8  | Period time equation and sensitivity analyses                                      | 52 |

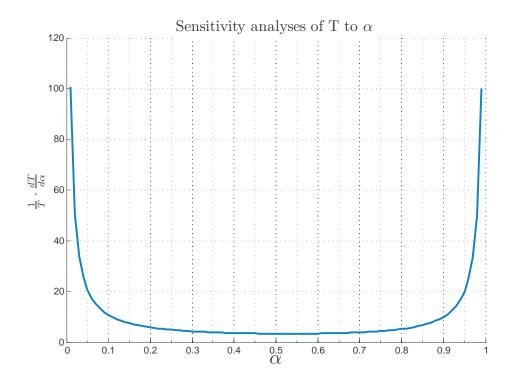

|   |      | 3.8.1 Sensitivity of T to $\alpha$                                                 | 56 |

|   |      | 3.8.2 Sensitivity of T to the comparator threshold                                 | 59 |

|   | 3.9  | Ideal temperature compensation                                                     | 60 |

|   |      | 3.9.1 Theoretical, non-linear optimization approach $\ldots \ldots \ldots \ldots $ | 31 |

| 4 | Cire | cuit Design 6                                                                      | 35 |

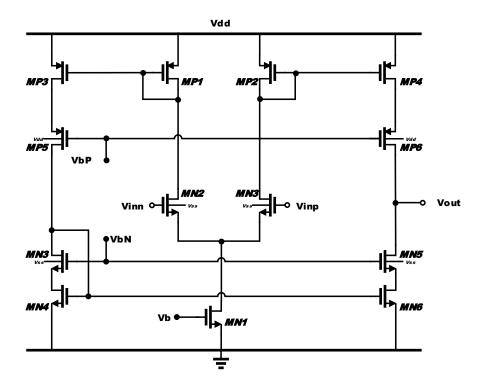

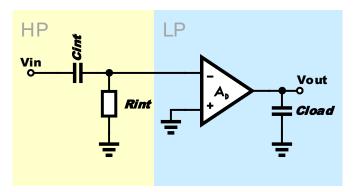

|   | 4.1  | Active filter, Integrator                                                          | 35 |

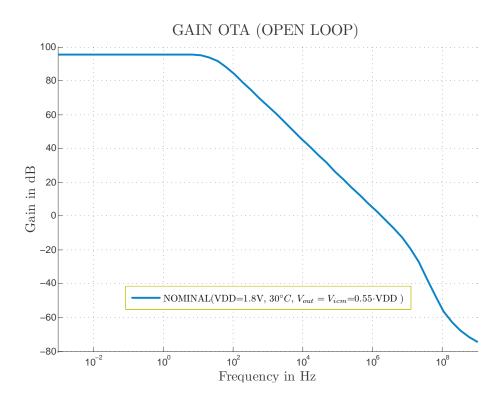

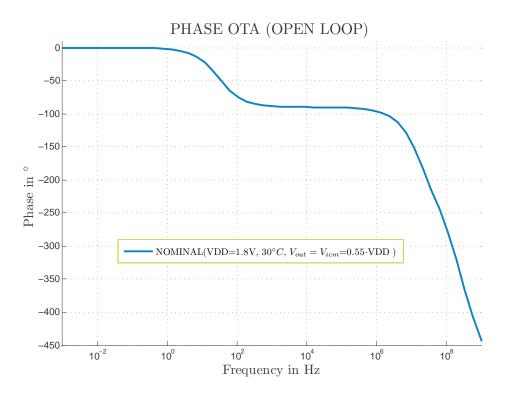

|   |      | 4.1.1 Calculations and sizing                                                      | 66 |

|   | 4.2  | Comparator                                                                         | 79 |

|   |      | 4.2.1 Calculations and sizing                                                      | 30 |

|   | 4.3  | Output driver                                                                      | 35 |

|   |      | 4.3.1 Calculations and sizing                                                      | 35 |

|   | 4.4  | Current bias cell                                                                  | 35 |

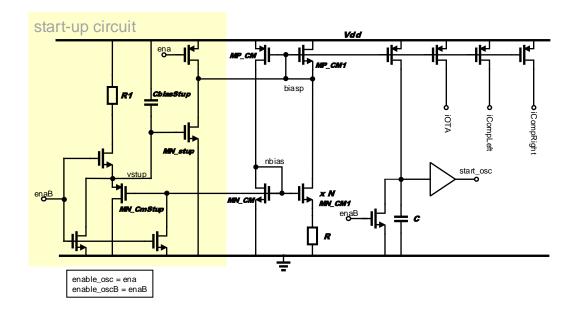

|   |      | 4.4.1 Start-up behavior                                                            | 37 |

|   |      | 4.4.2 Signal $start_{osc}$                                                         | 88 |

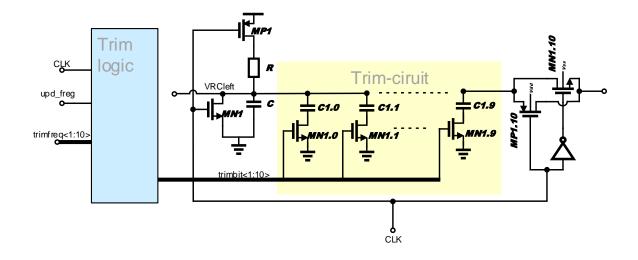

|   | 4.5  | Trim-circuit                                                                       | 90 |

|   |      | 4.5.1 Design aspects                                                               | 90 |

|   |      | 4.5.2 Calculations and sizing                                                      | 92 |

|   | 4.6  | RC-delay-cell                                                                      | 95 |

|   |      | 4.6.1 Design aspects of the RC-cell                                                | 96 |

|   | 4.7  | Resistive voltage divider                                                          | 97 |

|   |      | 4.7.1 Start-up behavior of the reference voltage                                   | 97 |

| 5 | Rel  | iability 9                                                                         | 99 |

|   | 5.1  | Charging resistor R                                                                | 99 |

|   |      |                                                                                    |    |

| 7 | Con            | clusio | n                                  | 111 |

|---|----------------|--------|------------------------------------|-----|

|   | 6.4            | Total  | frequency error                    | 108 |

|   | 6.3            | Aging  | and reliability analysis           | 107 |

|   | 6.2            | Functi | ional analysis                     | 107 |

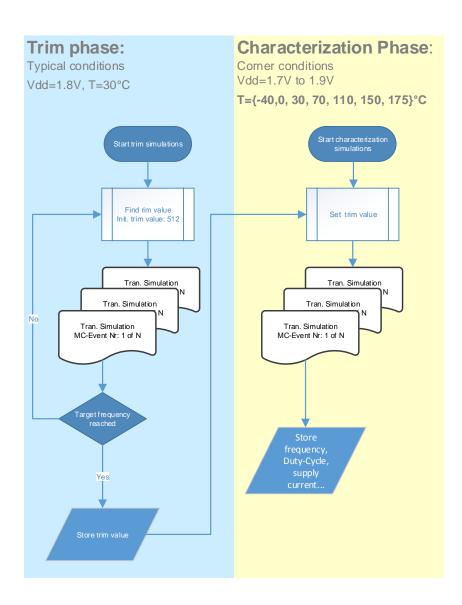

|   | 6.1            | Chara  | cterization over PVT, OCEAN-script | 103 |

| 6 | $\mathbf{Sim}$ | ulatio | n results                          | 103 |

|   | 5.3            | Electr | omigration                         | 101 |

|   |                | 5.2.4  | Unsilicided polysilicon            | 101 |

|   |                | 5.2.3  | METALxS                            | 100 |

|   |                | 5.2.2  | VIAx on METALxS                    | 100 |

|   |                | 5.2.1  | Contacts                           | 100 |

|   | 5.2            | CLK o  | output driver                      | 100 |

|   |                | 5.1.1  | Unsilicided polysilicon            | 99  |

# List of Figures

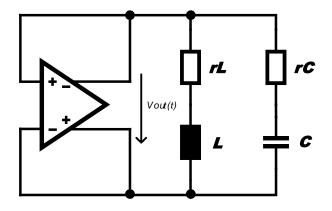

| 2-1  | Conventional LC-oscillator with output voltage $v_{out}(t)$                             | 27  |

|------|-----------------------------------------------------------------------------------------|-----|

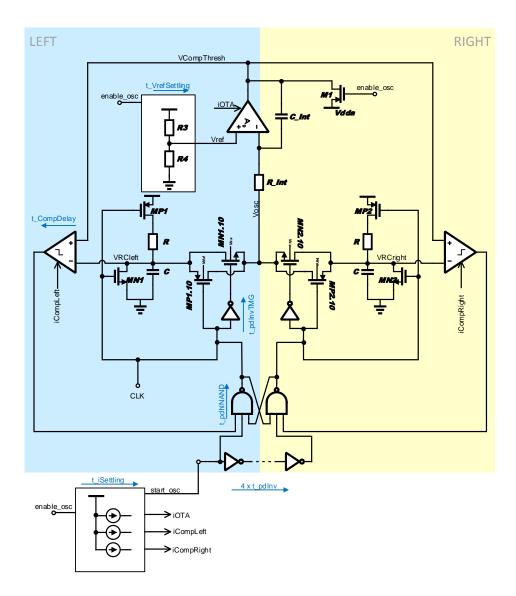

| 3-1  | RC-oscillator with voltage averaging feedback                                           | 39  |

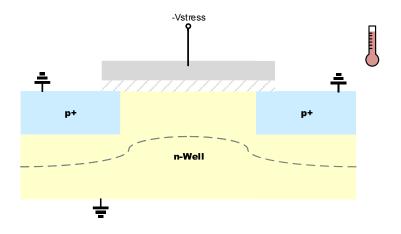

| 3-2  | NBTI stress of a PMOS                                                                   | 41  |

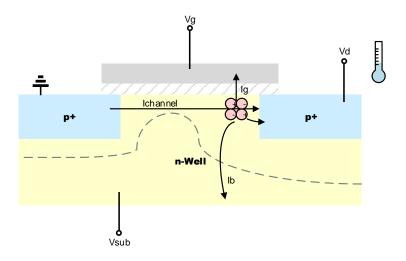

| 3-3  | Drain avalanche hot carrier injection (DAHC) in a PMOS                                  | 42  |

| 3-4  | Sensitivity of the period time to $\alpha$                                              | 57  |

| 4-1  | Current mirror OTA                                                                      | 66  |

| 4-2  | Gain of the OTA                                                                         | 71  |

| 4-3  | Phase of the OTA                                                                        | 72  |

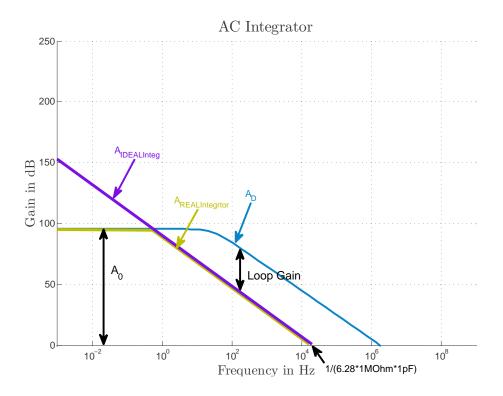

| 4-4  | AC behavior of the integrator and the differential amplification                        | 73  |

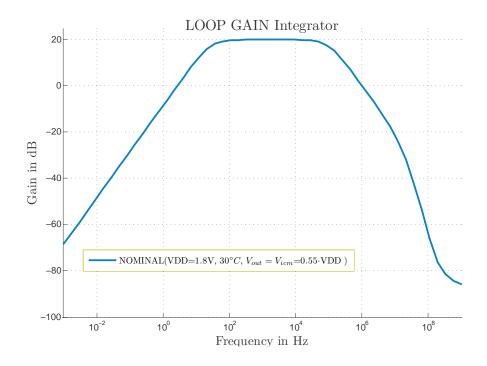

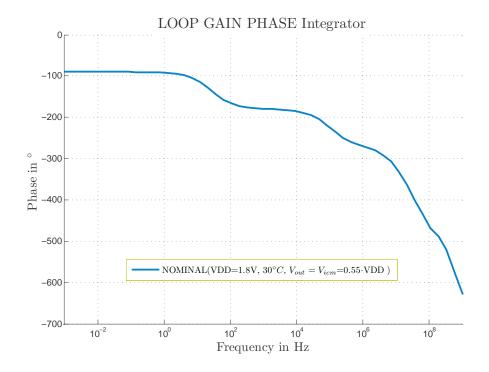

| 4-5  | Loop-gain setup                                                                         | 75  |

| 4-6  | Loop-gain of the integrator                                                             | 76  |

| 4-7  | Loop-gain phase of the integrator                                                       | 76  |

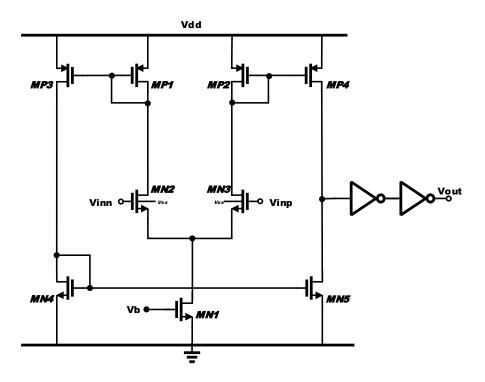

| 4-8  | Current mirror comparator                                                               | 80  |

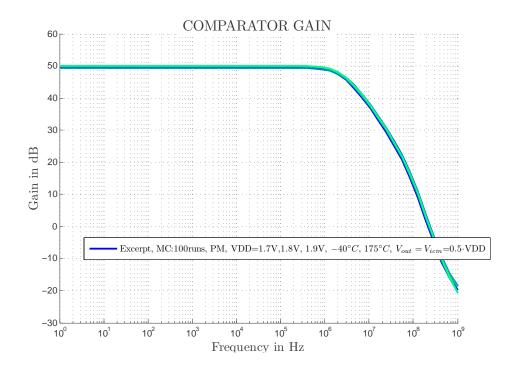

| 4-9  | Gain of the comparator                                                                  | 84  |

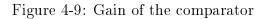

| 4-10 | Phase of the comparator                                                                 | 84  |

| 4-11 | Topology of the current bias cell                                                       | 86  |

| 4-12 | Trim-circuit                                                                            | 92  |

| 6-1  | Simplified OCEAN simulation sequence                                                    | 105 |

| 6-2  | Oscillator $\pm 6\sigma$ frequency stability over PVT variations $\ldots \ldots \ldots$ | 109 |

## List of Tables

| 1.1 | Oscillator target specification            | 23  |

|-----|--------------------------------------------|-----|

| 2.1 | State-of-the-art oscillator overview [50]  | 33  |

| 4.1 | OTA-integrator specification table 1 of 2  | 77  |

| 4.2 | OTA-integrator specification table 2 of 2  | 78  |

| 7.1 | Oscillator simulation results and features | 114 |

## List of Abbreviations

| RC    | Resistor-Capacitor                                |

|-------|---------------------------------------------------|

| Ρντ   | Process-Voltage-Temperature                       |

| CMOS  | Complementary Metal Oxide Semiconductor           |

| ABCD  | Advanced Bipolar CMOS DMOS                        |

| SOI   | Silicon On Insulator                              |

| NXP   | Next eXPerience                                   |

| ΟΤΑ   | Operational Transconductance Amplifier            |

| USB   | Universal Serial Bus                              |

| GPS   | Global Positioning System                         |

| XO    | Xtal (crystal) Oscillator                         |

| VCXO  | Voltage Compensated Xtal (crystal) Oscillator     |

| тсхо  | Temperature Compensated Xtal (crystal) Oscillator |

| 0CX0  | Oven Controlled Xtal (crystal) Oscillator         |

| MEMS  | Micro Electro Mechanical Systems                  |

| LC    | Inductor-Capacitor                                |

| PLL   | Phase Locked Loop                                 |

| CPU   | Central Processing Unit                           |

| FOM   | Figure Of Merit                                   |

| NAND  | Negated AND                                       |

| RS-FF | Reset Set Flip Flop                               |

| ні    | High                                              |

|       |                                                   |

#### LO Low

- **PMOS** P-type Metal Oxide Semiconductor

- NMOS N-type Metal Oxide Semiconductor

- **MOS** Metal Oxide Semiconductor

- **BTI** Bias Temperature Instability

- **NBTI** Negative Bias Temperature Instability

- **PBTI** Positive Bias Temperature Instability

- **CHE** Channel Hot-Electron

- SGHE Secondarily Generated Hot-Electron

- **SHE** Substrate Hot-Electron

- PD Power Down

- **BW** Band width

- **GBW** Gain Band Width

- **PM** Phase Margin

- ICM Input Common Mode

- **AC** Alternate Current

- **Gm** Transconductance

- **PSRR** Power Supply Rejection Ratio

- **CMRR** Common Mode Rejection Ratio

- **LSB** Least Significant Bit

- CLK Clock

- **TMG** Transmission Gate

- $TCR_1$  Temperature Coefficient of Resistance,  $1^{st}$  order

- $TCR_2$  Temperature Coefficient of Resistance,  $2^{nd}$  order

- $TCC_1$  Temperature Coefficient of Capacitance,  $1^{st}$  order

- $TCF_1$  Temperature Coefficient of Frequency,  $1^{st}$  order

- $TCF_2$  Temperature Coefficient of Frequency,  $2^{nd}$  order

## Chapter 1

## Introduction

"Strictly speaking, an oscillator (from the latin verb, "oscillo," to swing) produces sinusoids. A clock has rectangular or square wave output." The terms have come to be used interchangeably and this thesis bends to that convention [56]. In an age of increasing integration, external frequency references are also becoming more and more integrated on a chip. The main reasons for the integration of frequency references are costs, area and reliability. The following chapter provides an overview of siliconbased frequency references. It studies various state-of-the-art implementations of silicon based frequency references in detail. However, the main aim of this chapter is a comparison of the frequency references currently available in the literature. Finally, a comparison between these references will be provided [28].

First, a word about frequency stability. The stability of a frequency reference is a measure of the amount of change in the output frequency as a function of environmental parameters. These include temperature, supply voltage, process tolerances, noise, etc. But the main factors which influence output frequency are variations in process, voltage and temperature (PVT). The indication of stability can be done in ppm (part per million) or percent [21] [3] [22] [33] [24]. The frequency stability tells us about the deviation of the output frequency  $\Delta f$  from the nominal frequency  $f_0$ caused by environmental parameters [28].

$$f_{error} (\%) = \frac{\Delta f}{f_0} 10^2 \tag{1.1}$$

$$f_{error}(ppm) = \frac{\Delta f}{f_0} 10^6 \tag{1.2}$$

It should be noted that  $f_{error}$  is only meaningful if information about the environmental parameters is given.

#### Environmental parameters are:

- The measurement set-up: Temperature range, supply voltage range, trim, number of samples reported, standard deviation...

- Simulation set-up: Temperature range, supply voltage range, trim, corner, Monte-Carlo, standard deviation...

Frequency references are present in almost any electronic device. Therefore, it is understandable that, depending on the application of the device, different levels of accuracy are required. For instance, in some microcontroller applications, stable references ranging from 0.01% (100ppm) to 1% (10000ppm) [10] are needed, while USB 2.0 needs a clock accuracy of around 500ppm [11]. In wireless communication channels, much higher accuracies are required for the operation. For example, in mobile handset application, frequency references should have an accuracy of up to 2.5ppm [12], while a GPS receiver or mobile base station system requires an accuracy of sub ppm [28] [22] [2].

Now some words about quartz oscillators, as they are one of the reasons for the integration of frequency references. Crystal oscillators have been the only means of production of stable frequencies in the last decades. Their advantages are simple and include their low temperature dependence and "relatively low" cost with a small form factor. Therefore, they also have a dominant share in the frequency control market (more than 90%, equivalent to more than 4.5 billion U.S. dollars). To get a brief overview of some of the quartz oscillator technologies available on the market, some of them are listed below with the corresponding accuracy [28] [22].

- Non compensated (XO) and voltage compensated (VCXO) quartz oscillators achieve stability in the range of 20ppm to 100ppm.

- Temperature compensated (TCXO) quartz oscillators achieve stability in the range of 0.1ppm to 5ppm.

- Oven controlled (OCXO) quartz oscillators achieve stability in the range of 1ppb (parts per billion).

On the other hand, quartz oscillators also have some drawbacks. One of these drawbacks is the amount of space required on the circuit board when a particular number of frequency sources are required by the system. Another drawback is their sensitivity to mechanical shock and vibration. As a consequence, any mechanical stress, acceleration or vibration leads to frequency changes [22]. This series of drawbacks is what drives the search for integrated frequency references with similar frequency stability. Such references are made of silicon, which is why they are also referred to as silicon-based frequency references [35].

### 1.1 Motivation and target specification

In the modern world of communication RC-oscillators gain more and more on influence. Due to the developing of modern CMOS processes, passive elements such as resistors and capacitors can be produced with a low spread. This allows a further reliable process integration of external components. The necessary frequency stability, such as within 1% can be thoroughly achieved with some constraints (temperature range, voltage range, multi point trim) and more or less sophisticated concepts. This results in a considerable variety of application for RC-oscillators. The biggest challenge of these concepts consists mostly of achieving very good frequency stability at low power and a small area. As mentioned above, the future request for RC-oscillators is to achieve a similar frequency stability of quartz oscillators. This desire is triggered from many advantages of the integrated RC-oscillators.

#### These advantages are:

- Very good to integrate

- Very fast start-up times

- Suitable for low power applications

- Small area

- Trimable

- Require no external components

- Less costs compared to crystal oscillator

- Less susceptible to mechanical shock and vibrations

In large systems more than one system clocks are usually necessary to provide clocks for different sub systems. Depending on the operating mode of the system different clocks are also necessary. For instance, in sleep mode a low power oscillator will be used, but during the transmitting of signals, an RC- or crystal oscillator has to be used. It is also conceivable that an RC-oscillator is only used for the start-up phase until the crystal oscillator frequency is settled. A fast RC-oscillator for wake-up, could load the application code from the flash before the crystal oscillator is prepared. For these requirements, it is clear that this is not feasible with external crystal oscillators due to a long start-up time, space and cost reasons. However, disadvantages result due to the process variations of integrated passive components. To be able to use these oscillator technologies useful as a time source, usually a frequency trim has to be performed. Due to the above mentioned application aspects NXP decided to design an oscillator with a low PVT variation.

| 1.1.1 | Target | specification | of the | oscillator |

|-------|--------|---------------|--------|------------|

|-------|--------|---------------|--------|------------|

| Specification                    | Data                                                                       |

|----------------------------------|----------------------------------------------------------------------------|

| Principle of operation           | Best should be chosen                                                      |

| Frequency range in MHz           | 16                                                                         |

| Supply voltage in Volt           | 1.7 to 1.9                                                                 |

| Temperature range in $^{\circ}C$ | -40 to 150, up to 175 functional behavior                                  |

| Supply current in $\mu A$        | < 200                                                                      |

| Process                          | $0.14 \mu m$ SOI ABCD9-Power                                               |

| Accuracy in $\%$                 | $\pm 0.5$ over $\pm 6\sigma$ , PVT and trimmed                             |

| Area in $mm^2$                   | < 0.1                                                                      |

| Power-down mode                  | yes                                                                        |

| Duty-cycle in $\%$               | 45 to 55                                                                   |

| Settling time in $\mu s$         | < 250                                                                      |

| Settling behavior                | spike free                                                                 |

| Trim                             | yes                                                                        |

| Trim behavior                    | The frequency change due to the<br>trim signal has to be spike free        |

| Clock output                     | Enable/disable possibility with a spike free behavior                      |

| Start-up behavior                | From a low frequency with no frequence overshoot higher than $16MHz + 5\%$ |

## Chapter 2

## **Oscillator** topologies

In the following sections, several silicon-based frequency references are examined for their advantages and disadvantages.

### 2.1 MEMS-oscillators

Quartz resonators are excited by an electrical oscillating circuit. The oscillation is due to the piezoelectric properties of the quartz. But these piezoelectric properties cannot be integrated on silicon. Therefore, a lot of effort was spent on the research and development of silicon MEMS (Micro Electro Mechanical Systems) oscillators, which, like LC-oscillators, also have self-oscillation properties. In contrast, RC-oscillators have no self-oscillation properties. Thus, they always need additional components such as comparators or Schmitt-triggers to maintain their oscillation. The main aim of the extensive research surrounding the MEMS-oscillators was the replacement of expensive external crystals [31]. MEMS-resonators are structures with sizes in the micrometer to nanometer range which can be excited electrostatically, electromagnetically or piezoelectrically [51] [55]. Their frequency ranges from a few kHz up to one/several MHz with quality factors of 50000 up to 300000 which are comparable to quartz oscillators. The quality factor of the resonator determines the stability of the frequency reference and is equal to the ratio between the resonance frequency and the bandwidth of the LC-circuit. For MEMS-resonators, the shape and geometry determines this factor. This frequency stability is comparable with that of quartz oscillators. However, the jitter (phase noise) performance for mobile applications is still too low in MEMS technologies. For a better jitter performance with low noise and a high quality factor, LC-oscillators are a good alternative to MEMS-oscillators [51] [45]. Due to the special manufacturing process, it is not possible to manufacture MEMS structures and electronic circuits on the same die. That is also one of the biggest drawbacks of this technology [55] [30]. Furthermore, a big challenge in this technology is ensuring long term frequency stability with a protection against vibration, shock sensitivity and temperature drift [30]. However due to their very small dimensions and very low weight, MEMS-resonators have a better shock resistance than quartz crystals [20]. Compared to quartz oscillators, MEMS-oscillators are more area efficient and, due to mass production, more cost effective. Commercially available MEMS frequency references manufactured by Discera use the technique of combining a MEMS-resonator with a PLL [12]. The lower limit for the frequency stability is about 50ppm, at supply voltages from 1.8V to 3.3V. The output frequencies lie between 1-150MHz and the supply current is about 3mA.

## 2.2 LC-oscillators

As previously mentioned, LC-oscillators can be manufactured on silicon. These oscillators have various advantages and disadvantages compared to quartz or MEMSoscillators. Depending on the requirements, LC-oscillators can be preferred over quartz oscillators. They are mostly used in phase locked loops (PLLs) as voltage controlled oscillators. Due to their better phase noise properties, LC-oscillators are also used in RF applications. They have two energy storing elements, L and C, which therefore allow a free oscillation to be generated. As in other oscillator topologies, their frequency stability across a range of temperatures, voltages and process variations has to be considered. The output frequency is usually a function of temperature with a negative concave temperature coefficient whose sensitivity increases at high temperatures, see equation 2.2 [34]. With a positive linear dependency of the resistance  $r_L$  of the inductance on temperature, the LC-oscillator exhibits a negative temperature coefficient with a large quadratic frequency variation across temperatures [47]. The resistive losses of the coil limits the possible temperature range from  $20^{\circ}C$  to  $70^{\circ}C$ . Another disadvantage is the sensitivity of the output frequency due to conductive materials and eddy currents in the vicinity of the oscillator. Considering the many process and temperature dependent variables, one single point temperature trim is not practical for a definite temperature response as too many unknown variables can still influence the temperature response. For a well defined temperature response, a trim of the temperature coefficients of the frequency is necessary, but this causes an increase in production costs. The frequency  $\omega$  of an LC-oscillator is defined as per equation 2.1.

$$\omega = \omega_0 \sqrt{\frac{1 - \frac{r_L^2 C}{L}}{1 - \frac{r_C^2 C}{L}}} = \frac{1}{\sqrt{LC}} \sqrt{\frac{1 - \frac{r_L^2 C}{L}}{1 - \frac{r_C^2 C}{L}}}$$

(2.1)

$$f_{TC} = \frac{\partial \omega}{\partial T} \frac{1}{\omega} \approx -\frac{Cr_L^2}{L} \frac{\omega_0^2}{\omega^2} \frac{\partial r_L}{\partial T}$$

(2.2)

Figure 2-1: Conventional LC-oscillator with output voltage  $v_{out}(t)$

## 2.3 RC-harmonic oscillator

This type of oscillator uses resistors and capacitors to generate an oscillating signal. As known from integrated circuits, these passive elements have a large variation around their nominal value. This variation is in the order of 10 to 20 percent. Due to this large dependency on the absolute values and on temperature, an accurate prediction of the frequency without trimming is not possible. However, RC-oscillators have some advantages which make them very interesting for industrial applications. They can be used as a low-power, sleep or CPU oscillator. In these applications, a high accuracy is usually not necessary. Secondly, they require only a fraction of the power (micro-watts) and area compared to LC, MEMS or quartz oscillators. A stateof-the-art RC-oscillator can reach a frequency stability of up to 1% by trimming and temperature compensation. However, this depends on some details such as supply voltage range or temperature range. Harmonic RC-oscillators operate in a frequency range from one kHz to a few MHz. The output signal of an RC-oscillator depends on the topology of the oscillator. We can distinguish between clock RC-oscillators and harmonic RC-oscillators. Harmonic oscillators have a sinusoidal output voltage whereas clock oscillators have a rectangular one. A commonly known type of harmonic RC-oscillator is the Wien-Bridge-oscillator [15]. This oscillator combines an RCnetwork with an amplifier. The RC-network basically combines a high pass filter with a low pass filter, producing a very selective second-order frequency dependent band pass filter. At the resonant frequency, the reactance of the circuits equals its resistance R as the phase shift between the input and output equals zero degrees. The magnitude of the output voltage is at its maximum and is therefore equal to one third  $\frac{1}{3}$  of the input voltage. So if there is an amplification by 3, then the circuit oscillates [15]. In the first order, the frequency stability of the oscillator is determined by the process and temperature stability of the passive elements R and C. Other nonideal effects which can lead to additional inaccuracies in the output frequency include the finite gain, output impedance and the phase shift introduced by the amplifier. To mitigate these effects, a fully differential and modified Wien-Bridge-oscillator is proposed in [58] [44].

### 2.4 Relaxation-oscillators

Another type of RC-oscillator is a relaxation-oscillator. The oscillator is called relaxation-oscillator due to the relaxation time  $\tau = RC$  of the RC-network. This topology produces a digital (square wave) output signal also called clock [25]. Its output frequency lies between a few hundreds kHz to tens of MHz. Relaxation-oscillators are often used primarily because of their low power consumption and CMOS compatibility. These properties make them attractive for battery-powered applications such as wake-up timers or implantable biomedical systems [43] [26] [7]. Like in harmonic RC-oscillators, the time-giving element is a RC-network. This results again in the main disadvantages discussed above [43] [7]. By means of temperature compensation and trimming, a frequency stability of 2% [7] [26] [7] can realistically be obtained. The conventional relaxation-oscillator has the disadvantage that its comparator delay influences the frequency. For an exact description of the operation of conventional relaxation-oscillators please refer to the literature in [50]. However, this delay is subject to strong variations due to PVT. This leads to an additional error due the variation of the comparator delay. Various approaches are suggested in the literature in order to minimize this error. One obvious possible approach is to minimize the variation of the comparator delay is to increase the power of the comparator. This is usually not possible because this cannot be reconciled with the requirement of a lowpower oscillator. As part of the literature research, some relaxation-oscillators were investigated. However, not all of them are represented in the table 2.1 at the end of the chapter. The relaxation-oscillator in paper [63] was chosen for the implementation due to its close match of the requirements laid down by NXP. This oscillator will be discussed in detail in the following chapters. However some details are noted here. The oscillator has a novel voltage averaging feedback which has the big advantage that oscillation depends only on the RC-product. So its frequency is independent of the comparator delay. Therefore, it is possible to provide the comparator with lower power because the delay variation can be compensated. This meets the requirements for low power and frequency stability precisely.

### 2.5 Ring-oscillators

Another class of clock oscillators are ring-oscillators. They are often used as voltagecontrolled oscillators in jitter sensitive applications. Examples of such applications include PLLs or clock recovery circuits. An advantage of ring-oscillators is the high achievable frequency and the easy CMOS integration. There are a variety of topologies (also cross-coupled oscillators) which are explained in detail in [32]. The simplest topology of a ring-oscillator consists of a cascade of inverters with an odd number. However, ring-oscillators can be accomplished with analog differential delay stages too. This topology has the advantage that the frequency can be controlled with the output swing of the differential pair. Thus, for instance, the frequency variation can be partially compensated. More details on this implementation can be found in [6] and [29]. An analytic and exact calculation of the frequency for representatives of ring-oscillators is not straight forward. There are two analyses which are relevant to the calculation of the frequency. Firstly, a small signal analysis for the start-up behavior, and secondly, a large signal analysis for the settled case. In summary, the loop gain of a negative feedback circuit has to satisfy two conditions:

$$|H(j\omega_0)| \ge 1 \text{ and } \angle H(j\omega_0) = 180^\circ, \tag{2.3}$$

then the circuit may oscillate at  $\omega_0$ . These two conditions are called the Barkhausen Criteria. For a detailed description of the calculation of the frequency see [49].

As noted above two considerations (small and large signal analysis) are necessary. However, the results of the two considerations do not necessarily match. The reason of the frequency mismatch is conceivable. For ring-oscillators, the amplitude grows very rapidly, leading to a saturation phenomenon which results in the limitation of the maximum amplitude. This leads to non-linearities which can be treated only by a large-signal analysis. A large signal analysis for the propagation delay does not necessarily match the small-signal analysis, since in this case the output resistance and capacitance in the trip point are used whereas the propagation delay is calculated by non-linear currents and capacitances. It should be noted that, if the small signal loop gain is greater than one, then the circuit must spend also enough time in saturation (higher gain than in the triode region) so that the average loop gain is still equal to one. The trip point of an inverter is the point where  $v_{in} = v_{out}$  [49].

## 2.6 Conclusion and design choice

As mentioned in chapter 1, frequency stability can only be compared between publications if the data on the measurement or simulation set-up are known. For instance, 200 measurements of a published oscillator cannot be compared with two measurements of another published oscillator. The same applies to the simulation results. Although if a Monte-Carlo analysis was performed, it is still mostly unknown which parameters were varied by the Monte-Carlo analysis. In RC-oscillators for example, the temperature coefficient of a resistor (TCR) has to be changed since it is dependent on the doping concentration [46] [57]. A statement about the frequency spread is simply not meaningful if there is no variation on the temperature coefficient of a resistor. A comparison between the topologies can therefore only be made based on a rough estimation. The most interesting requirements for integrated oscillators are area, power consumption, frequency stability, jitter and the temperature range. Due to the two die solution, MEMS-oscillators need the largest surface of all integrated oscillators. In other words, a MEMS-oscillator is not CMOS compatible because it cannot be manufactured with a conventional CMOS circuit on a chip. This big disadvantage leads to higher packaging and production costs, as well as an increase in complexity. Its power consumption is similar to the LC-oscillator, and thus larger than in other topologies. However, MEMS and LC-oscillators are the only solutions to achieve better than 0.1% accuracy at a reasonable jitter level. For integrated circuits, the LC-oscillator provides the best performance across process and temperature variations. However, LC-oscillators need more area and power than all other oscillators. A further disadvantage of LC-oscillators is their limited temperature range. For less precise frequency stability requirements, RC, Ring, mobility or relaxationoscillators may offer interesting advantages. These oscillators can reach a frequency stability of up to 1%, depending on the topology. The great advantages of these oscillators are the small required area and the low power consumption ( $\mu Watt$  range). This makes them very interesting for low power applications. A very short summary of these studies can be found in the table 2.1 at the end of the chapter. Because of area and cost requirements, LC and MEMS-oscillator cannot be chosen for the design. RC-oscillators match the requirements of NXP very well. As seen in table 2.1 the relaxation-oscillator [63] has a good figure of merit as well as a conclusive design. Therefore this oscillator was chosen for the further design. This oscillator will be discussed in the following chapters in detail. For further information on the specification see chapter 1.1 "Motivation and target specification".

#### Figure of merit

A figure of merit (FOM) [48] can be defined as follows:

$$FOM = \frac{\Delta\omega}{\omega_{T_0}\Delta T} \frac{ppm}{\circ C}$$

(2.4)

Where  $\Delta \omega$  is the frequency deviation across the temperature range  $\Delta T$ , and  $\omega_{T_0}$  is the nominal frequency at  $T_0$ . This FOM addresses the frequency temperature coefficient.

| Table 2.1: 5                               | Table 2.1: State-of-the-art oscillator overview         [50] | erview [50]   |                |               |

|--------------------------------------------|--------------------------------------------------------------|---------------|----------------|---------------|

| Reference number                           | [63]                                                         | [29]          | [37]           | [52]          |

| Principle of operation                     | Relaxation with feedback                                     | Ring          | ГС             | RC-harmonic   |

| Frequency range in MHz                     | 14                                                           | 10            | 24             | 9             |

| Supply voltage in Volt                     | 1.7 to 1.9                                                   | 1.2 to 3      | 1.8            | 1.2           |

| Temperature range in $^\circ\mathrm{C}$    | -40 to 125                                                   | -20 to 100    | 0 to 70        | 0 to 120      |

| Supply current or power consumption        | $25\mu A$                                                    | $80\mu A$     | $4\mathrm{mW}$ | $66\mu A$     |

| Process in $\mu m$                         | 0.18                                                         | 0.18          | 0.13           | 0.065         |

| Accuracy in ppm                            | $\pm 3500$                                                   | $\pm 4500$    | $\pm 300$      | <b>±9000</b>  |

| Voltage coefficient in $ppm/V$             | 8000                                                         | 2500          | not available  | not available |

| Temperature coefficient in $ppm/^{\circ}C$ | $\pm 11.51$                                                  | $\pm 33.33$   | $\pm 8.6$      | 土86           |

| Area in $mm^2$                             | 0.04                                                         | 0.22          | 0.8            | 0.03          |

| Number of samples reported                 | 1                                                            | not available | commercial     | 9             |

| Figure of merit (FOM)                      | 21.2                                                         | 32.5          | 4.3            | 75            |

## Chapter 3

## Theoretical design considerations

### 3.1 Start-up and oscillation mechanism

The start-up behavior should be well defined and known. According to the specification (see chapter 1.1) of the start-up, the frequency has to settle within  $250\mu$ s from a low frequency to the higher target frequency. An overshoot of the frequency should be avoided as subsequent blocks could cause a system failure due to higher frequencies. Second, the default trim value for the very first start-up has to be chosen so that the frequency is always less than 16MHz + 5%. This specification can only be achieved through a well-defined starting procedure of the individual blocks and a large enough phase margin of the active filter.

# The main building blocks which have an influence on the start-up process are:

- The resistive voltage divider (reference voltage settling behavior)

- The current bias cell (current settling behavior)

- The delay elements (inverters chain) between the NANDs

- The active filter (sets the comparator threshold)

The resistor voltage divider and the current bias cell are very important, because the OTA and the comparator need a constant and well defined bias current for op-

eration. Only then, the OTA and comparator can work properly. Furthermore, the resistive voltage divider has a buffer capacitor and parasitic capacitances depending on the size of the resistors. That changes the start-up behavior in such a way, that the voltage at the reference node is not immediately present due to an RC-charging behavior. Therefore, we must now distinguish between two start signals, the externally applied  $enable_{osc}$  and the delayed internally generated  $start_{osc}$ . The external  $enable_{osc}$ first enables the resistive voltage divider and the current bias-cell. After the correct bias current and reference voltage have settled, the bias cell block creates a  $start_{osc}$ signal which starts the oscillator immediately. If the reference voltage and the bias current are not settled at a positive  $start_{osc}$  signal, than the integrator would integrate to a smaller average voltage which could lead to a significant higher frequency during the starting phase. For further information on the current bias block see chapter 4.4. A further problem during the start-up can be a simultaneous set of the  $start_{osc}$  signal of the NANDs at the RS-FF. This can be prevented with a short propagation delay between the two NANDs. As with conventional relaxation oscillators, the level of the comparator threshold also has a big influence on the starting frequency. To avoid a high frequency in the start phase, the comparator threshold has to be set to a high voltage. In our case, this can be easily done by forcing the integrator capacitor to the supply voltage  $V_{dda}$ . For a detailed description of the transient profile of this voltage see chapter 3.1.1 and figure 3-1.

#### The following requirements are also necessary for a proper start-up:

- $t_{VrefSettling} < t_{iSettling}$

- $t_{pdhlNAND} < 4 \cdot t_{pdInv}$

- $V_{CompThresh_{t=0}} = V_{dda}$

The first two statements above have to be checked in all supply and temperature corners with a Monte-Carlo analysis, in order to determine a proper safety margin.

•  $t_{pdhlNAND} < 4 \cdot t_{pdInv}$  :

This requirement is necessary to ensure that only the left RC-cell is charged during the start-up. The worst case value for the difference delay  $4 \cdot t_{pdInv}$  –  $t_{pdhlNAND}$  is as aspect at  $V_{dda} = 1.9V$  and  $-40^{\circ}C$ . There is a safety margin of  $(\mu - 6 \cdot \sigma) = 545ps - 19ps \cdot 6 = 431ps$ , which is sufficient.

•  $t_{VrefSettling} < t_{iSettling}$ :

This requirement is necessary to ensure a safe start-up from a low frequency.  $t_{iSettling}$  is the time between a HI from  $enable_{osc}$  until  $start_{osc}$  becomes HI.  $t_{iSettlingMIN} = (\mu - 6 \cdot \sigma) = 15.67\mu s - 0.56\mu s \cdot 6 = 12.3\mu s$ . The current of the bias cell is settled up to 0.4% of its end value after this time.  $t_{VrefSettlingMAX} = (\mu + 6 \cdot \sigma) = 9.16\mu s + 0.46\mu s \cdot 6 = 11.9\mu s$ .  $t_{VrefSettlingMAX}$  is the maximum time for a 0.05% settling of the reference voltage. Therefore, the requirement  $t_{VrefSettling} < t_{iSettling}$  is also satisfied. Note: These are very stable assumptions, because the  $t_{VrefSettling}$  has its worst case at 1.7V and  $-40^{\circ}C$  and  $t_{iSettling}$  at 1.9V and  $-40^{\circ}C$

#### 3.1.1 Start-up sequence

- 1. Let us assume that a start signal  $enable_{osc}$  is applied to the oscillator

- 2. The resistive voltage divider and the current bias cell will be enabled immediately

- 3. After the bias current is settled the  $start_{osc}$  signal goes to HI

- If  $t_{pdhlNAND} < 4 \cdot t_{pdhlInverter}$  then the right NAND will remain in the same state as before until the comparator switches to LO

- 4. The left NAND will switch to LO and the load capacitor of the left RC-cell will be charged

- $V_{CompThresh}$  is at this time forced to the supply voltage  $(V_{dda})$ . If a voltage is applied to the active filter, the  $V_{CompThrehs}$  voltage rises short-term above  $V_{dda}$ , due to a bootstrap effect! However, due to the parasitic diode of the PMOS, in the output stage, the voltage is limited to  $V_{dda} + v_{diode}$ . Stress check of the comparator input differential pair:

$Vdda+v_{diode} < V_{gs,Nmos,MAX}+V_{bs,Nmos}$ . Where  $V_{gs,Nmos,MAX} = 2.5$ V. So for a correctly biased comparator, there is no danger for the input differential pair due to the short-term stress.

- Due to the rising voltage  $V_{RCleft}$  at load capacitor of the left RC-cell, the negative input  $V_{inn}$  at the active filter also rises.

- If  $V_{inn}$  rises above  $V_{inp} = V_{ref}$ , then the OTA discharges its integrator capacitor  $C_{int}$  and  $V_{CompThresh}$  decreases.

- 5.  $V_{CompThresh}$  decreases due to the discharging of the OTA

- 6. If  $V_{CompThresh} < V_{RCleft}$  then the comparator switches to LO

- 7. The left NAND will therefore switch to HI and the right NAND to LO

- 8. Therefore, the right RC-cell begins to load the capacitor whereas the left RC-cell will be discharged

- 9. When  $V_{RCright} > V_{CompThresh}$  the compactor switches to LO again and the oscillation mechanism begins at step 7 with the other NAND

- So the waveforms  $V_{RCright}$ ,  $V_{RCleft}$  are transmitted alternately to the active filter

- The oscillator settles in to its target frequency if the average voltage of  $V_{RCright} + V_{RCleft} = V_{osc}$  is equal to  $V_{ref}$ .

Nevertheless, there are more requirements for a proper operation of the oscillator.

- The inverter to the transmission gate has to have a shorter propagation delay than the NAND. Otherwise both sides are shortened  $t_{pdhlNAND} > t_{pdhlInvTMG}$ .

- When neglecting parasitic effects, the comparator delay has to be greater than twice the propagation delay of the NANDs. This condition is easy to achieve at a frequency of 16MHz.

Figure 3-1: RC-oscillator with voltage averaging feedback

# 3.2 Power-down mode

A power-down mode is a necessary criterion to decrease the power consumption during unneeded phases. Due to aging effects of MOS transistors in power-down mode, a biasing of source, drain, gate and bulk at different voltage levels has to be avoided. Some precautions have to be taken to avoid an adverse shift in parameters due to this asymmetric bias. This shift in parameters can lead, for instance, to a higher offset or an higher offset drift, and therefore to a bad long-term performance. The long-term frequency stability is mainly influenced by aging of the circuit, whereas short-term frequency stability (jitter, phase noise) is influenced by thermal or  $\frac{1}{f}$  noise.

#### MOS transistor aging effects include:

- Negative bias temperature instability (NBTI) of a PMOS

- Positive bias temperature instability (PBTI) of a NMOS

- Hot carrier injection

#### 3.2.1 Bias temperature instability

Bias temperature instability (BTI) is a degradation effect in MOS transistors which causes parameter shifts when a high gate bias with respect to well, source, or drain is applied at relatively high temperatures. Depending on the sign of the gate bias with respect to well, source, or drain, the BTI is usually referred to as a negative BTI (NBTI) or a positive BTI (PBTI). PBTI of an NMOS is far less common than NBTI of a PMOS because PMOSs almost always operate with a negative gate to source voltage (NBTI) [40] [53]. See figure 3.2.1.

#### The typical setup for a NBTI stress of a PMOS is as follows:

- High temperature,  $100^{\circ}C$  to  $200^{\circ}C$

- The gate is negatively biased, whereas source and drain and substrate are grounded. Therefore the transistor is conductive,  $V_{DS} \approx 0V$

The electrical field over the gate oxide in this setup causes damage to the gate oxide and at the oxide-silicon interface. The parameter most affected is the threshold

Figure 3-2: NBTI stress of a PMOS

Fig. 3.2.1 shows the set-up for a NBTI stress. The source, drain, and substrate are grounded whereas the gate is negatively biased. These conditions are applied at higher temperatures and for a certain period of time. Due to the symmetry of source and drain no channel hot carriers are generated [53].

voltage  $V_T$  (increase in  $V_T$ , resulting in a slower transistor). As mentioned above, modes which are susceptible to BTI are the power-down mode or a mode with an asymmetrical bias of the transistors.

## Susceptible circuit parts include:

- The matched differential pair

- Voltage dividers with transistors

- Voltage comparators

To prevent lifetime reduction due to BTI, it is important to avoid asymmetrical stress of the MOS transistors in matched pair configurations. Therefore, it is better, if possible, to always use NMOS matched configurations. In power-down mode, PMOS transistors should always remain switched off [40]. This generally requires a gate

Figure 3-3: Drain avalanche hot carrier injection (DAHC) in a PMOS

Fig. 3-3 shows the set-up for a DAHC stress. Stress conditions:  $V_{gs} < V_{ds}$ . Hot carriers lead to generating electron-hole pairs. Hot electrons and hot holes are injected into the dielectric. Furthermore some of the carriers form a bulk current [16].

bias respective to the well so that the transistor is actively closed.

## **3.2.2** Hot carrier injection

Hot carrier injection is a reliability issue due to "hot carriers" that attain a very high kinetic energy from being accelerated by a high electric field. These energetic carriers can be injected into normally forbidden regions of the device, such as the gate dielectric, where they can get trapped or cause interface states to be generated. These defects in the dielectric lead to shifts in the threshold voltage  $V_T$  and transconductance degradation in MOS devices. To prevent lifetime reduction due to hot carrier injection, some design modifications can be made. These include, for example, a larger channel length, a doubled diffusion of source and drain or a graded drain junction. Four injection mechanisms can be distinguished when it comes to hot carrier injection into the dielectric [16].

- Channel hot-electron (CHE) injection  $V_{gs} \approx V_{ds}$

- Drain avalanche hot-carrier (DAHC) injection  $V_{gs} < V_{ds}$

- Secondarily generated hot-electron (SGHE) injection

- Substrate hot-electron (SHE) injection

For further information about the different conditions see [16]. In general, due to a higher  $V_{DS}$ , hot carriers can be injected into the dielectric, therefore, a higher  $R_{on}$  (low  $V_{GS}$ ) leads to an high electric field  $\implies$  high  $V_{DS}$ . For instance: The stress conditions with high  $V_{DS}$  and lower  $V_{GS}$  are called the drain avalanche hot-carrier (DAHC) injection see figure 3-3.

#### 3.2.3 Design considerations

The power-down mode (PD-mode) is a possible start scenario for the oscillator. For start-up, some voltage nodes have to be forced to a certain voltage in order to ensure that there is no overshoot of the frequency during start-up. Thus, the PBTI specifications of the comparator differential pair cannot be met because the comparator threshold has to be forced to  $V_{dda}$ . In order to meet the condition again, a transmission gate has to separate  $V_{inp}$  from  $V_{dda}$ . This problem does not occur for the OTA differential pair in the power-down mode because the reference voltage divider is switched off and thus  $V_{inn}$  can be easily connected to ground.  $V_{inp}$  of the OTA is also connected to ground so the PBTI condition is satisfied. Secondly, the integrator capacitor can be forced to  $V_{dda}$  without a problem so that a start with a low frequency is ensured. To minimize power consumption in power-down mode, low leakage transistors have sometimes been used in logic gates.

# 3.3 Frequency error due to a supply ripple

As observed in simulations, it makes a significant difference to the frequency when the supply voltage source is no longer assumed to be ideal. A ripple in the supply voltage can be caused by a high current load due to switching components and the finite internal resistance of the voltage regulator.

#### Solutions include:

- Optimizing of the current in switching components

- Buffer capacitors at peak current components

- Separate supply domains for analog and digital supply voltages

- A low-impedance voltage regulator

- A low-impedance layout

The frequency error caused by a ripple in the supply voltage arises because of the functional concept of an oscillator. The circuit concept tries to keep the average charge constant. So seen from a system point of view the RC-product behaves like a time depending RC-product.

#### This can be seen in the following derivation:

$$V_{ref} = \frac{1}{\tilde{T}} \int_0^{\tilde{T}} V_{osc} dt \qquad (3.1)$$

$$V_{osc} = v_c \quad for \dots t = \{0 \to \tilde{T}\} \quad (3.2)$$

where,

$$\tilde{T} = T/2$$

(3.3)

$$v_c = \int_0^t \frac{i_c(\tilde{t})}{C} d\tilde{t} = \frac{1}{C} \cdot Q(t)$$

(3.4)

$$V_{ref} = \frac{1}{\tilde{T}} \int_0^{\tilde{T}} v_c \, dt = \frac{1}{\tilde{T}} \int_0^{\tilde{T}} \int_0^t \frac{i_c(\tilde{t})}{C} \, d\tilde{t} \, dt = \frac{1}{C} \underbrace{\frac{1}{\tilde{T}} \int_0^{\tilde{T}} Q(t) \, dt}_{\text{average charge}} \tag{3.5}$$

# 3.4 Study of frequency spread determining factors

The frequency is based on an RC-product, so its very important which resistors and capacitors are chosen in order to achieve an accurate frequency across temperature or voltage variations. Thus, a study of the process and its devices is necessary to determine the depending voltage and temperature coefficients of the devices. As mentioned before, the period time is proportional to the RC-product. This means, that any spread of the temperature coefficient of the RC-product leads to a spread of the temperature behavior of the frequency.

# The main factors leading to instability in the frequency across temperatures include:

- The offset voltage drift of the OTA

- Spread in the reference voltage temperature coefficient

- The differential offset voltage drift in comparators

- The spread in the temperature coefficient of the RC-product

Beside these points, the strong spread of the temperature coefficients of the polyresistor is the limiting factor for the mass production of precisely integrated RCoscillators. Because of this, it is absolutely necessary to implement a spread of temperature coefficients in simulation models. Otherwise, we cannot draw a useful conclusion about a behavior with real process variations. A compensation for this spread is only possible through a trimming process across two or more temperatures. Because of the fact that this comes with long testing times and therefore with high testing costs, such trimming processes are not useful.

### 3.4.1 Charge resistor R

Because of the problems laid out above, we can only choose an  $N^+$  poly-resistor as a charging resistor. This resistor has the following advantages and disadvantages over other resistors:

• High temperature range:  $-40^{\circ}C$  to  $150^{\circ}C$

Thus poly-resistor can be used for automotive applications without any restrictions

- Very low leakage currents

- Temperature coefficients are very low for poly-resistors

- Self-heating N<sup>+</sup> poly: Beware, the poly-resistor has self-heating (since it is on STI-oxide) ⇒ Self-heating active-N<sup>+</sup>: No issue

- Voltage dependency is very low

- Sheet resistance is low compared to others

As known from the literature [36], the spread of  $TCR_1$  and  $TCR_2$  takes place due to different doping concentrations within the process variations. The resistors have a very low temperature dependency. Therefore, the temperature coefficient  $TCR_1$ can easily flip sign and is clearly a function of resistor width. As a consequence, the temperature behavior can change. For the thermal behavior of a resistor it should be kept in mind that a resistor can be split up into several resistive components:  $R = R_{contact} + R_{silicided} + R_{bulk} + R_{interface} \cdot \frac{W_0}{W}$ . Every one of these resistors has its own temperature coefficient. However, total TCR is dominated by the TCR value of  $R_{bulk}$  and  $R_{interface}$  [57].

### 3.4.2 Charge capacitor C

The capacitor in combination with the resistor is what determines period time. Thus, an appropriate choice of capacitor is also incredibly important. For this reason, we can only consider a fringe capacitor, because it possesses very small voltage and temperature dependence. The metal fringe capacitor is based on the capacitance between parallel metal lines (optionally connected with vias) and separated by the intra level dielectric. The capacitor is made of two inter-digitated combs at each metal level, which are stacked and aligned on the METAL1, METAL2, METAL3, METAL4 and METAL5 levels. A bus connects the fingers of both combs at each level. The capacitor is used without shielding because of the parasitic capacitance of the shield. Due to the insufficient capacitance-to-area ratio, the capacitance value could be increased at the fingers through vias. This option was not chosen due to possible reliability problems and the ensuing demands on the voltage screening circuitry.

# 3.5 Maximum frequency spread across temperatures

In order to estimate the real performance of the oscillator, the maximum frequency deviation in the trimmed state should be evaluated. Analytically, this calculation is not useful via an error calculation, because the variation in reference voltage is expressed with a complex superfunction and the large temperature range calls for at least a Taylor-approximation of the second order. This is why an estimation of the maximum frequency spread across temperatures was carried out via MATLAB (R). To do this, the spread of temperature coefficients was used in equation 3.43 and evaluated across temperatures. The result of this analysis possesses a frequency spread over temperature of  $\approx \pm 1.1\%$  in frequency.

## 3.6 Influence of the offset of the OTA

Ideally, the output of the operation amplifier should be at zero volts when the inputs are grounded. In practice, a small differential voltage must be applied to the inputs to force the output to zero. This is known as the input offset voltage  $V_{OS}$ . The input offset voltage is modeled as a voltage source  $V_{OS}$ , switched in series with the inverting or non-inverting input terminal of the operation amplifier [11].

See the following literature: Gray and Meyer [17], and Dostal [13] for more details concerning  $V_{OS}$  and the  $V_{OS}$  drift over temperature.

Typical CMOS operation amplifiers have offset voltages of around  $200\mu V$  to  $10000\mu V$  and offset voltage drifts of  $0.4\frac{\mu V}{K}$  to  $10\frac{\mu V}{K}$ , respectively [23].

#### 3.6.1 Frequency changes due to offset voltage

Because the offset voltage can be switched in series to the non-inverting input like a voltage source, a change in offset voltage is equivalent to a change in the reference voltage  $V_{ref}$  of the oscillator. Therefore, the frequency sensitivity is equivalent to: 186.1 $\frac{\%}{V} = 0.1861 \frac{\%}{mV}$ . For further information see chapter 3.8.1. As with a reference voltage offset, the static offset voltage can easily be compensated for during the trimming process. It is more difficult to compensate for the offset voltage drift. An offset voltage drift can only be compensated for with a multi-point trimming process. However, such trimming processes are very costly and therefore not usable. See also chapter 6.3, concerning the aging effects of the offset voltage. The design criteria for the input-pair area were specified according to the maximum offset voltage drift. Frequency errors due to the offset voltage drift should reach at most  $\pm 0.1\%$ .

This results in a maximum offset voltage drift of:

$$\pm 0.1\% = 0.1861 \frac{\%}{mV} \cdot \pm V_{OS} \tag{3.6}$$

$$\pm TC_{V_{OS}} \cdot \Delta T = \pm V_{OS} \tag{3.7}$$

$$\frac{\pm 0.1\%}{0.1861\frac{\%}{mV} \cdot 190^{\circ}C} = \pm TC_{V_{OS}} = \pm 2.8\frac{\mu V}{K}$$

(3.8)

$V_{OS} \ldots$  Offset voltage

$TC_{V_{OS}}$ ... Temperature coefficient of the offset voltage

$\Delta T \dots$  Temperature range

# 3.7 Influence of the comparator offset voltage

As mentioned in chapter 3.6, the offset voltage also displays temperature-dependent behavior. The offset voltage of the comparators is an uncritical factor for our oscillator. However, we need to distinguish two separate cases:

- Both comparators possess the same offset voltage and the same offset voltage drift.

- The offset voltage and the offset voltage drift are different in the two comparators.

The first case is insignificant because the offset voltage and the offset voltage drift are the same for both comparators. In the functional concept of the oscillator, this acts as an additional comparator delay, which is compensated for wholly through the circuitry. The second case is more critical. In this case, the duty-cycle of the clock frequency changes. Furthermore, a change in frequency takes place because assuming differential drift behavior in the offset voltages. In that case the integrated voltages  $V_{RCleft}$  and  $V_{RCright}$  have different areas. Therefore, differential drift behavior in offset voltage can only be compensated for by circuitry on average. That means, the specification value to be determined is the differential offset voltage drift of the comparators, since this causes a duty-cycle variation and a change in frequency. **Note:** The frequency change due the the static offset voltage and the mismatch in the RC-products are compensated due to the trim procedure in the test phase.

#### 3.7.1 Duty-cycle variation due to mismatch

The symmetry of an oscillating clock voltage is defined by the duty-cycle. This parameter is determined by differential offset voltage, differential offset voltage drift of the comparators and mismatch of the RC-product. Therefore its necessary to specify the maximum differential offset voltage drift and the mismatch. From these results, the required offset voltage behavior and the required mismatch can be achieved by adding to the area. However, the proposed oscillator can achieve a good accuracy for the following reasons. Passive devices as the charge resistor R and the charge capacitor C are well matched in CMOS processes. As discussed before, a limiting factor is the mismatch of differential pairs of comparators. However, this is not a critical issue because a reasonable design will keep the mismatch small, which results in duty-cycle degradation by less than 1% which is negligible for the application [63]. The duty-cycle D is defined as:  $D = \frac{T_{ON}}{T} = \frac{T_{ON}}{T_{ON+TOFF}} = \frac{1}{1+\frac{T_{OFF}}{T_{ON}}}$

#### Passive duty-cycle variation

Because period time results from the two RC-charging curves ( $V_{RCleft}$  and  $V_{RCright}$ ), we can assume that  $T_{ON}$  and  $T_{OFF}$  are proportional to the two RC-products. The mismatch of fringe capacitors is much lower than that of poly-silicon resistors. Therefore, it can be said that the whole passive mismatch is dominated by the poly-silicon resistors [63]. From the mismatch parameters of the resistor, we can deduce (see data sheet [39]):

$$6 \cdot \sigma \left(\frac{R_{\Delta}}{\bar{R}}\right) = 0.15 \tag{3.9}$$

$$6 \cdot \sigma \left(\frac{C_{\Delta}}{\bar{C}}\right) = \text{negligible, see [4]}$$

(3.10)

$$T_{ON} \propto R_{right}C_{right}$$

(3.11)

$$C_{ON} \propto R_{right}C_{right}$$

(3.11)

$$T_{OFF} \propto R_{left} C_{left}$$

(3.12)

$$D_{min} = \frac{1}{1 + \frac{R_{left}C_{left}\cdot 1.15}{R_{right}C_{right}}} = \frac{1}{1 + \frac{1.15}{1}} = 0.465$$

(3.13)

$$D_{max} = \frac{1}{1 + \frac{R_{left}C_{left}}{R_{right}C_{right} \cdot 1.15}} = \frac{1}{1 + \frac{1}{1.15}} = 0.534$$

(3.14)

Where  $R_{left}C_{left}$  and  $R_{right}C_{right}$  are assumed as a ideal RC. Assuming a symmetrical distribution, this signifies a duty-cycle variation of  $\pm 3.5\%$ .

#### Active duty-cycle variation due to $\Delta V_{os}$ of the comparators

A static differential offset voltage of the two comparators leads, as mentioned before, to a duty-cycle variation, because the threshold of the comparator changes. The maximum offset voltage variation can be calculated as follows.

Assuming  $t_{CompDelay}=0$ s, maximum duty-cycle variation of  $\pm 1\%$ , and the period time T changes due to the duty-cycle variation:

$$t = \frac{T}{2} = t_{th}$$

(3.15)

$$V_{RCleft}(t) = V_{CompThresh} = V dd \left(1 - e^{\frac{-t_{th}}{RC}}\right)$$

(3.16)

$$V_{RCright}(t) = V_{RCleft}(t) + V_{OS} = V dd \left(1 - e^{\frac{-(t_{th} + t_{OS})}{RC}}\right)$$

(3.17)

$$D = \frac{T_{ON} + t_{OS}}{T} \tag{3.18}$$

$$t_{OS} = D \cdot T - T_{ON} \tag{3.19}$$

$$V_{OS}(D) = V_{RCright} - V_{RCleft} = V dd \cdot e^{\frac{-t_{th}}{RC}} \left(1 - e^{\frac{-(D \cdot T - T_{ON})}{RC}}\right)$$

(3.20)

So if we assume a duty-cycle of D=0.5  $\pm 1\%$  with Vdd=1.8V, T=62.5ns and

$T_{ON} = \frac{T}{2}$  than the  $\Delta V_{OS}$  has to be less then 11mV.

As the formulas make apparent, the variation of duty-cycle is also a function of the comparator threshold because the threshold time  $t_{th}$  (in our case  $t_{th} = T/2$  with  $t_{CompDelay} = 0s$ ) is still in the equation 3.20.

# 3.8 Period time equation and sensitivity analyses

In order to derive a frequency equation, the oscillating voltage node  $V_{osc}$  at the active filter has to be considered. As described in the section "Start-up and oscillation mechanism", the oscillating RC-voltage  $V_{RCleft}$  and  $V_{RCright}$  are alternately applied to the active filter. Due to the large time constant of the active filter, an averaging of this signal takes place. That means,  $V_{osc} = V_{RCleft} + V_{RCright}$  is virtually shortened in a low frequency domain defined by the time constant and the amplification of the integrator (active filter), see equation 3.23 [10].

#### The derivation is as follows:

Assume a constant gain-bandwidth product.

$$1 \cdot f_{A=1,CL} = f_{3dB} \cdot A_0 \tag{3.21}$$

$$f_{A=1,CL} = \frac{1}{2\pi R_{int}C_{int}} \longrightarrow |A(s=j2\pi f_{A=1,CL})| = 1$$

(3.22)

$$f_{3dB} = \frac{1}{2\pi R_{int}C_{int}A_0}$$

(3.23)

- $f_{A=1,CL}$ ... Unity frequency closed loop

- $A_0 \ldots$  DC-gain of the integrator

- $f_{3dB}$ ... Cut-off frequency of the integrator

- A(s)... Frequency response of the integrator

The integrator controls the average value of  $V_{osc}$ , that it corresponds exactly to that of  $V_{ref}$ , see equation 3.24. That is, the oscillator behaves like a voltage controlled oscillator, controlled by the output voltage  $V_{CompThresh}$  of the active filter. Assuming an ideal amplifier,  $R \ll R_{int}$  and  $\tilde{T} = \frac{T}{2}$ , an equation can be derived as follows.

$$V_{ref} = \frac{1}{\tilde{T}} \int_0^{\tilde{T}} V_{osc} dt \qquad (3.24)$$

$V_{osc}$  is the voltage at the charging capacitor C,

$$V_{ref} = \frac{1}{\tilde{T}} \int_0^{\tilde{T}} V_{dda} \left( 1 - e^{\frac{-t}{RC}} \right) dt$$

(3.25)

Now the limits of the integral are used,

$$V_{ref} = \frac{V_{dda}}{\tilde{T}} \left( \tilde{T} - \left( RC - RC \, e^{\frac{-\tilde{T}}{RC}} \right) \right) \tag{3.26}$$

Separation of the T dep. equations,

$$\frac{\left(1 - \frac{V_{ref}}{V_{dda}}\right)\tilde{T}}{RC} = 1 - e^{\frac{-\tilde{T}}{RC}}$$

(3.27)

$$\alpha = \frac{V_{ref}}{V_{dda}} \tag{3.28}$$