Dipl.-Ing. Ralph Peter Weissnegger, BSc

### Design and Verification Process for Safety-Critical Embedded Systems in the Automotive Domain

### **DOCTORAL THESIS**

to achieve the university degree of

Doktor der technischen Wissenschaft

submitted to

### Graz University of Technology

Supervisor

Univ.-Prof. Dipl.-Inform. Dr.sc.ETH Kay Römer

Institute of Technical Informatics

Advisor Ass.Prof. Dipl.-Ing. Dr.techn. Christian Steger

### AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present doctoral thesis.

Date

Signature

# Acknowledgments

This thesis has been carried out at the Institute of Technical Informatics at the Graz University of Technology, in cooperation with the industrial partner CISC Semiconductor GmbH. I would like to thank CISC, especially Dr. Markus Pistauer, for making my PhD study possible and for letting me participate in very interesting industrial projects. I would like to thank my supervisor Prof. Kay Uwe Römer for being open for discussions and for excellently supporting the official and organizational part of my PhD study. Furthermore, my thanks go to Dr. Damian Dalton who kindly agreed to serve as a second adviser for my thesis. In particular, I would like to express my gratitude to my mentor Ass.-Prof. Dr. Christian Steger. He not only managed the organizational framework, made great journeys to interesting conferences possible, gave me a lot of freedom regarding my research topics, and helped me to produce the scientific work, but he also supported me spiritually and morally. I also want to thank my students Markus Schuß and Martin Schachner for their great work and support during the project. Additionally, I would like to thank my colleagues who made my work days easier and more enjoyable.

Finally, I would like to thank my family for their lifelong support and their tolerance and encouragement during my whole studies. They always pointed me in the right direction, made life easier through helpful discussions and showed me what's really important in life. Another big shout-out goes out to my friends and former flatmates, which have always been there for me, for all the amazing (sport-) trips, journeys, come2gethers, ... ...resulting in unforgettable memories.

> Graz, May, 2017 Ralph Weissnegger

### Abstract

The modern automotive market is heading towards fully automated self-driving cars. Following this evolution, the number of new assistance features for ensuring safe and reliable operations is rising. The sensing and controlling of these systems is the work of the highly distributed and connected electronic control units (ECU) and it is no surprise that up to 100 of these microcontrollers are integrated in the car of today. Moreover, these systems must be developed in compliance with various automotive standards to ensure dependability such as the ISO26262 (functional safety for road vehicles). Thus the design and verification of electric/electronic systems is becoming increasingly complex. Current tools and design flows hit the limits of complexity and are therefore not capable to efficiently address software and hardware design and optimization in a joint way. Furthermore, the technological, organizational and design gap in today's flows are not covered by current methods and tools. The increasing effort in system design verification through dynamically changing design makes the development very cost intensive and SoC integration unaffordable for many applications. This situation is even getting worse as the number of extra-functional properties, such as safety and security, and their importance, is increasing. To overcome these issues in the design and verification of safety-critical systems, we developed novel verification methodologies, embedded in a complete design process named SaVeSoC (Safety Aware Virtual Prototype Generation and Evaluation of a System on Chip). The SaVeSoC process defines a design methodology especially for safety-critical systems and is based on a standardized modeling language for real-time and embedded systems (UML/MARTE). A model-based approach eases the communication between different stakeholders, provides different views and serves as a central storage of information. By applying simulation-based verification including virtual prototyping, quantified reliability analysis and hardware evaluation on a seamless design process, we were able to speed-up the verification and to reduce the tools involved; resulting in completeness, correctness and consistency of the entire system. The whole design process, including the novel verification methodologies, has been implemented in the design and verification framework SHARC (Simulation and Verification of Hierarchical Embedded Microelectronic Systems) and applied to an industrial use-case of a battery management system (BMS). The complete approach has been evaluated by responsible design experts for safety-critical development and verification.

### Zusammenfassung

Der moderne Automobilmarkt bewegt sich hin in Richtung selbstfahrende vollautomatisierte Fahrzeuge. Aufgrund dieser Entwicklung steigt die Anzahl neuer Fahrerassistenzsysteme um ein sicheres und zuverlässiges Verhalten, zu garantieren. Da die Kundenanforderungen an Assistenzsystemen enorm steigen, ist es auch keine Überraschung, dass bis zu 100 elektronischer Steuergeräte (ECUs) in heutigen Autos integriert sind. Darüber hinaus müssen diese Systeme auch hinsichtlich der Anforderungen verschiedenster Automobilstandards wie dem Sicherheitsstandard für funktionelle Sicherheit bei Straßenfahrzeugen (ISO26262) erfüllt und entwickelt werden, um die Zuverlässigkeit zu gewährleisten. Aufgrund dieser Tatsachen wird das Entwickeln und Verifizieren von elektrischen/elektronischen Systemen immer komplexer. Aktuelle Werkzeuge und Entwicklungsprozesse stoßen an die Grenzen der Komplexität und sind daher nicht in der Lage, Software- und Hardware-Design und dessen Optimierung in einer gemeinsamen Weise effizient zu adressieren. Darüber hinaus sind die technologischen, organisatorischen und Entwicklungslücken in heutigen Prozessen durch aktuelle Methoden und Werkzeuge nicht abgedeckt. Eine Abnahme der Komplexität ist nicht in Sicht, da die Anzahl der außer-funktionalen Eigenschaften, wie Safety und Security, und deren Bedeutung, zunimmt. Um die Barrieren im Design von sicherheitskritischen Systemen und dessen Verifikation zu überwinden, entwickelten wir neuartige Verifikationsmethoden, die zudem in einem kompletten Designprozess namens SaVeSoC (Safety Aware Virtual Prototype Generation und Evaluation eines Systems on Chip) eingebettet sind. Der SaVeSoC-Prozess definiert eine Designmethodik speziell für sicherheitskritische Systeme und basiert auf standardisierten Modellierungssprachen für Echtzeit- und eingebettete Systeme (UML/MARTE). Durch das Anwenden simulationsbasierter Verifikation einschließlich virtuellem Prototyping, quantifizierter Zuverlässigkeitsanalyse und Hardware-Evaluierung in einem durchgehenden Designprozess, erreichten wir eine Beschleunigung der Verifikation und die Reduzierung der beteiligten Werkzeuge. Das Anwenden dieses Ansatzes führt zu Vollständigkeit, Korrektheit und Konsistenz des gesamten Systems. Der gesamte Designprozess, einschließlich der neuartigen Verifikationsmethoden, wurde im Design- und Verifikations-Framework SHARC (Simulation and Verification of Hierarchical Embedded Microelectronic Systems) implementiert und auf einen industriellen Anwendungsfall eines Batteriemanagementsystems (BMS) angewendet. Der komplette Ansatz wurde von verantwortlichen Designexperten für sicherheitskritische Entwicklung und Verifikation bewertet.

### **Executive Summary**

Over the past decades, we have been experiencing an increasing amount of electric/electronic (E/E) systems in the automotive domain. Today, we even speak about the electrification in the automotive field; thus we are heading towards fully electric cars which even speed up the growth in E/E systems. A modern car has up to 100 embedded Electronic Control Unit (ECU) [18] right now, and the number is even rising when we think about the emerging need for new assistance features in cars which help us to facilitate the vision towards the last stage of autonomous driving levels, stage 5. This stage refers to a fully autonomous system where the performance of a vehicle equals the experience of an adult human driver. This will be a major challenge for future vehicle development. The complex assistance features cannot properly work if these systems do not have a strong interaction (in-vehicle communication) and also inter-dependencies between them. Nowadays, we go even beyond the internal border of a car body for communication with a complex environment. For advanced driver features, modern cars have to communicate with each other (V2V - vehicle to vehicle), with the infrastructure (V2I - vehicle to infrastructure), but also with the cloud (vehicle2cloud) and other complex IoT devices (V2X). In the near future, this will enable a growth of new applications in the field of SmartCities and SmartMobility. This, in turn, raises also the amount of software in today's cars, which can lead up to a total of 150 million lines of code, which is vastly more than a Boeing 787 jet airliner [30]. Testing and verification of the software, hardware and complete systems in early stages is a bigger challenge in today's development. It raises the complexity level in the design, development and verification of complex systems and imposes an enormous effort for engineers in developing their applications. To fully test an autonomous car, it is predicted that a theoretical test track would need a length up to 88 times to the sun and back [66]. This utopistic distance could only be reached employing advanced simulation methodologies. Moreover, these systems must fulfill conformance to different automotive standards to guarantee dependability. In terms of safety, these systems must fulfill standards such as ISO26262 (functional safety for road vehicles), [42]. Since this standard is now treated as state of the art in court (2011), OEMs and their suppliers are required to develop and test their systems towards the recommended measures and methods. ISO 26262 is the functional safety standard for safety-critical systems in road vehicles. This standard addresses possible hazards caused by malfunctioning behavior of safety-related systems. It also provides an automotive safety lifecycle that covers safety aspects throughout the whole design and development process of modern products and systems. Depending on the Automotive Safety Integrity Level (ASIL) the system must be developed and tested according to different recommended measures and methods (e.g. FMEA, FTA, simulation, virtual prototyping) and must achieve a high level of reliability (e.g. low failure rates in hardware evaluation). Current design tools and flows, especially regarding safety-critical systems, hit the limits of complexity and therefore are not capable to efficiently address software and hardware design in a joint way. Moreover, the technological, organizational and design gap between the different abstraction levels that exists in today's development processes are not covered by current methods and tools. Besides the complexity and heterogeneity, also different kinds of requirements and constraints associated with the design of embedded systems must be taken into account. Extra-functional properties such as timing performance, power consumption or reliability are only partially addressed by disjoint special flows. The number of tools involved to cover all these properties is rising, thus leading to a complex toolchain where important information is distributed over several disjoint tools and organizations. Information transfer between these tools leads to inconsistency, incorrectness and incompleteness of the entire design. The increasing effort in system design verification through dynamically changing design makes the development very cost intensive and SoC integration unaffordable for many applications. This situation is even getting worse as the number of extra-functional properties, such as safety and security, and their importance, is increasing. Furthermore, the expectations towards system reliability are also significantly increasing or even become stringent in applications such as automotive or transportation. A further demand for more features (X-by-wire) and improved functionality (ADAS, autonomous driving) increases the complexity of future systems dramatically. Without advanced methods and tools, the effort in tackling these issues leads to an increase in development costs and time, thus missing the time-to-market window.

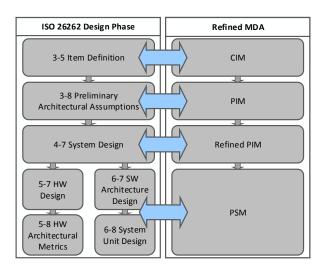

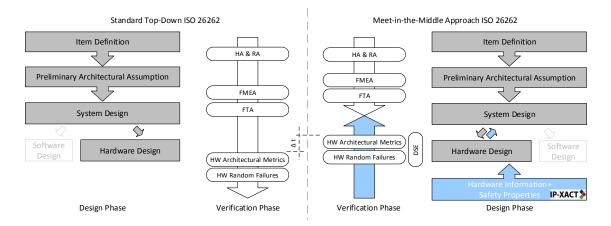

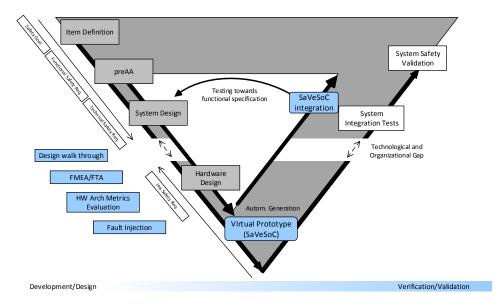

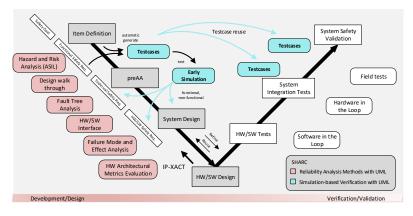

To overcome these issues in the design and verification of safety-critical systems, we developed novel verification techniques, embedded in a complete design process named SaVeSoC (Safety Aware Virtual Prototype Generation and Evaluation of a System on Chip). The SaVeSoC process defines a design methodology especially for safety-critical systems. This methodology is based on a standardized modeling language for real-time and embedded systems and is derived from the Unified Modeling Language (UML) standard. The name of this modeling language is MARTE and relies on the Model Driven Architecture (MDA) design layers. Since these layers lacked a proper definition, our contribution was to introduce an additional layer where safety aspects in the design can be seamlessly defined. By using structural and behavioral diagrams in combination with MARTE, important properties, such as timing behavior of safe states, but also resource management for several applications running on one ECU can be described analyzed. Furthermore, we show how different reliability analysis such as FMEA or FTA can be applied to the model-based approach throughout the design process. For the specification of the detailed hardware, we used a standard, which is very well known in the industry, named IP-XACT.

By connecting the structural system level components to executable models, we are able to describe the behavior of the system in a more sophisticated way. This has been done by defining a mapping between MARTE and SystemC. Since these two approaches share the same philosophy to start from a first system design down to a detailed hardware and software description, it was convenient to combine these two languages. The advantage of this approach is that no information must be transferred to other tools and the UML files retain as a single source of information. Furthermore, the configuration and parametrization of the simulation can be done using the defined MARTE properties.

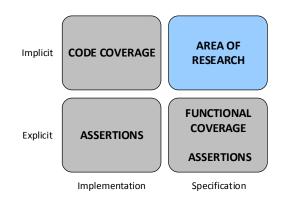

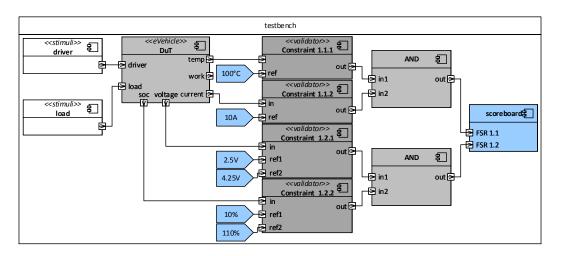

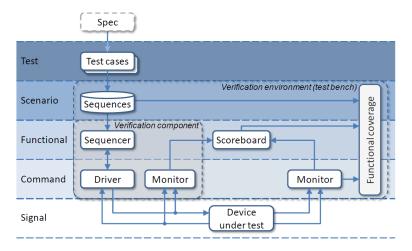

To increase and go beyond the level of functional coverage, we developed a methodology to automatically derive test benches from (safety-) requirements and the functional specification. These test benches can be reused throughout the whole development process. The (safety-) requirements have been defined in an extension for the UML2 profile named SysML. This approach has the advantage of automatically testing the design under various environmental conditions and in different design configurations.

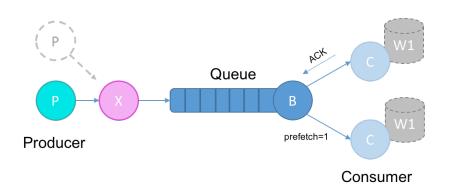

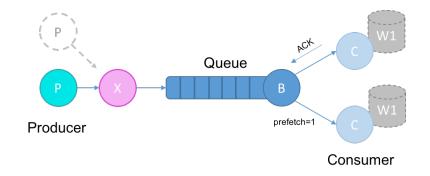

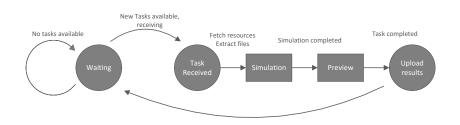

Since this approach leads to a significantly high amount of simulation tasks, we developed a new method and defined a layered architecture pattern for the distribution of independent simulation tasks to a cloud-based environment. This leads up to near linear speed-up in the coverage process. Results from the system verification can directly be used for the hardware (safety-) requirements and hardware platform design.

The detailed hardware specification, derived from our simulation experiments, can now be evaluated regarding single-point, latent and random hardware faults. This evaluation is mandatory in ISO26262 to verify the reliability of safety-critical hardware. By reusing safety properties and combining this approach with a standardized hardware description, we achieved to evaluate the hardware in earlier phases of development. Moreover, we could decrease the time for evaluating safety-critical hardware based on model-driven design.

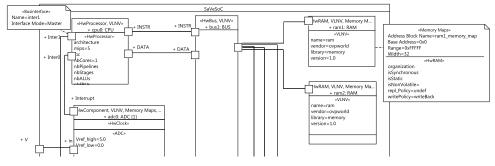

Using the same modeling language for the hardware description, we achieved to generate a first (safety aware) virtual prototype by reusing hardware components from an open library. This approach enables to test critical software much earlier in the design process by generating different hardware platforms on the fly. Thus software can be tested under different hardware configurations. Furthermore, our approach allows for a seamless integration into the functional specification of the system design by automatically generating proper interfaces, in order to verify its functionality.

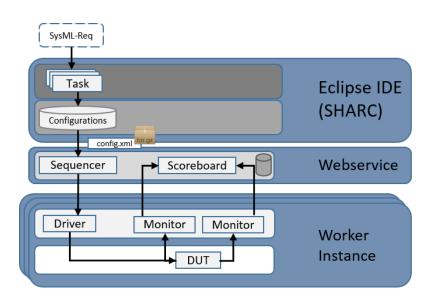

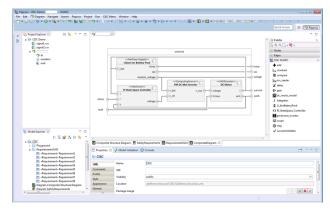

The whole design process, including the novel methodologies, has been implemented in the design and verification framework Simulation and Verification of Hierarchical Embedded Microelectronic Systems (SHARC). This framework is based on Eclipse and the UML editor Papyrus. By using our Eclipse plugins, every Papyrus editor is capable of verifying safety-critical embedded systems in line with the requirements of the functional safety standard ISO26262.

The complete approach has been evaluated by responsible design experts for safetycritical development and verification. The evaluation has been done regarding time (design effort), quality of the design, and verification coverage. Furthermore, we present the results of the OpenES design flow evaluation, to show the overall benefits of the newly developed approaches.

# Contents

| 1 | Intr | oduction                                        | 1 |

|---|------|-------------------------------------------------|---|

|   | 1.1  | Thesis Background                               | 3 |

|   | 1.2  | Problem Statement                               | 3 |

|   | 1.3  | Contributions                                   | 6 |

|   | 1.4  | Organization of the Thesis                      | 7 |

| 2 | Bac  | kground                                         | 9 |

|   | 2.1  | Functional Safety                               | 9 |

|   |      | 2.1.1 System Life Cycle                         | 9 |

|   |      | 2.1.2 Safety Life Cycle                         | 1 |

|   |      | 2.1.3 Stakeholder Analysis                      | 1 |

|   | 2.2  | Model-driven Engineering                        | 3 |

|   |      | 2.2.1 Design Languages                          | 5 |

|   |      | 2.2.2 Virtual Prototyping                       | 9 |

|   |      | 2.2.3 Design Frameworks                         | 1 |

|   | 2.3  | Related European Projects                       | 1 |

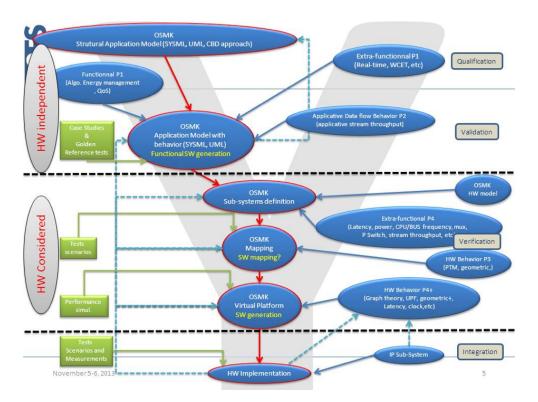

|   |      | 2.3.1 OpenES                                    | 1 |

|   |      | 2.3.2 eRamp                                     | 2 |

| 3 | Rela | ated Work 2                                     | 3 |

|   | 3.1  | Design of Safety-Critical Systems               | 3 |

|   | 3.2  | Hardware Evaluation in the ISO26262 Context     | 6 |

|   | 3.3  | Simulation and Virtual Prototyping 2            | 7 |

| 4 | SaV  | /eSoC Methodology 3                             | 1 |

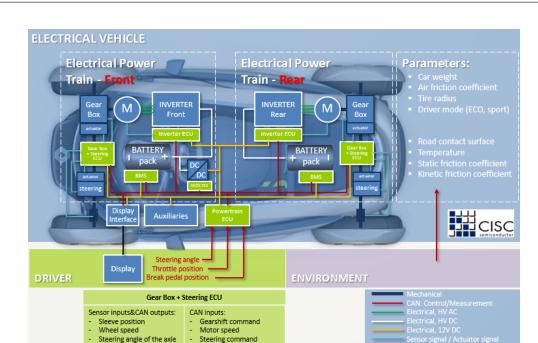

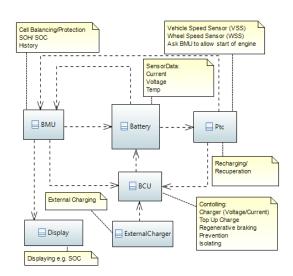

|   | 4.1  | Use Case                                        | 1 |

|   | 4.2  | Safety-Critical Embedded System Design          | 3 |

|   |      | 4.2.1 Functional Specification                  | 3 |

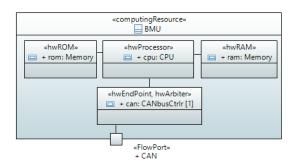

|   |      | 4.2.2 Hardware Design                           | 6 |

|   | 4.3  | Evaluation/Verification of the Design           | 8 |

|   |      | 4.3.1 Simulation-based Verification             |   |

|   |      | 4.3.2 Evaluation of the Hardware Architecture   |   |

|   |      | 4.3.3 Reuse of Safety Artifacts in Hardware IPs | 8 |

#### Design Process for Safety-Critical Embedded Systems in the Automotive Domain

| <ul> <li>4.4.1 Safety Aware Virtual Prototype</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |   | 49 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---|----|

| <ul> <li>5 SaVeSoC Implementation</li> <li>5.1 SHARC Framework</li> <li>5.1.1 System Component Library</li> <li>5.1.2 SysCore</li> <li>5.2 SHARC IDE</li> <li>5.3 Distributed Simulation Environment</li> <li>5.3 Distributed Simulation Environment</li> <li>6 SaVeSoC Evaluation</li> <li>6.1 Evaluation of the advanced OpenES Design Flow</li> <li>6.1.1 Definition of metrics</li> <li>6.2 Evaluation of the SaVeSoC Design Flow</li> <li>7 Conclusions</li> <li>7.1 Summary and Conclusion</li> <li>7.2 Future Work</li> <li>7.2.1 Fault Injection on TLM Level</li> </ul> |  |   | 49 |

| <ul> <li>5.1 SHARC Framework</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  | • | 51 |

| <ul> <li>5.1.1 System Component Library</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |   | 55 |

| <ul> <li>5.1.2 SysCore</li> <li>5.2 SHARC IDE</li> <li>5.3 Distributed Simulation Environment</li> <li>6 SaVeSoC Evaluation</li> <li>6.1 Evaluation of the advanced OpenES Design Flow</li> <li>6.1.1 Definition of metrics</li> <li>6.2 Evaluation of the SaVeSoC Design Flow</li> <li>6.2 Evaluation of the SaVeSoC Design Flow</li> <li>7 Conclusions</li> <li>7.1 Summary and Conclusion</li> <li>7.2 Future Work</li> <li>7.2.1 Fault Injection on TLM Level</li> </ul>                                                                                                     |  |   | 55 |

| <ul> <li>5.1.2 SysCore</li> <li>5.2 SHARC IDE</li> <li>5.3 Distributed Simulation Environment</li> <li>6 SaVeSoC Evaluation</li> <li>6.1 Evaluation of the advanced OpenES Design Flow</li> <li>6.1.1 Definition of metrics</li> <li>6.2 Evaluation of the SaVeSoC Design Flow</li> <li>6.2 Evaluation of the SaVeSoC Design Flow</li> <li>7 Conclusions</li> <li>7.1 Summary and Conclusion</li> <li>7.2 Future Work</li> <li>7.2.1 Fault Injection on TLM Level</li> </ul>                                                                                                     |  |   | 55 |

| <ul> <li>5.3 Distributed Simulation Environment</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |   |    |

| <ul> <li>5.3 Distributed Simulation Environment</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |   |    |

| <ul> <li>6.1 Evaluation of the advanced OpenES Design Flow</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |   |    |

| <ul> <li>6.1.1 Definition of metrics</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |   | 65 |

| <ul> <li>6.1.1 Definition of metrics</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |   | 65 |

| 7 Conclusions           7.1 Summary and Conclusion           7.2 Future Work           7.2.1 Fault Injection on TLM Level                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |   |    |

| 7.1       Summary and Conclusion         7.2       Future Work         7.2.1       Fault Injection on TLM Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |   | 69 |

| 7.2Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |   | 73 |

| 7.2Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |   | 73 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |   |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |   | 74 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  | • | 74 |

| 8 Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |   | 75 |

| 3ibliography 153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |   |    |

# List of Figures

| 1.1  | Overview of thesis contributions                             | 6  |

|------|--------------------------------------------------------------|----|

| 2.1  | Requirements, design and test phases in ISO26262             | 12 |

| 2.2  | T-shaped professionals                                       | 13 |

| 2.3  | 4+1 view model                                               | 15 |

| 2.4  | UML/MARTE levels of granularity                              | 17 |

| 2.5  | Comparison of UML and DSL languages                          | 18 |

| 2.6  | Implicit/explicit coverage                                   | 20 |

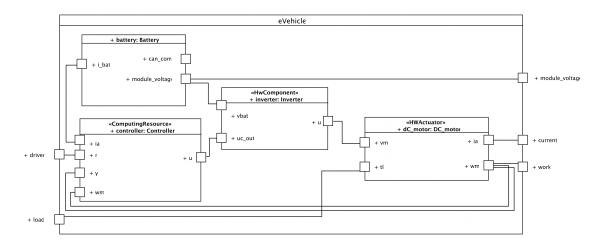

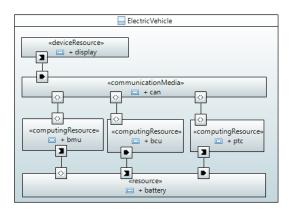

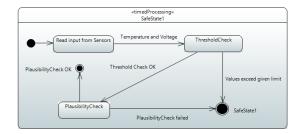

| 4.1  | Electric vehicle use case                                    | 32 |

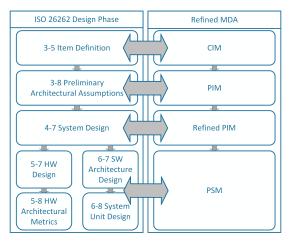

| 4.2  | Mapping approach between the ISO26262 and the MDA            | 34 |

| 4.3  | Item definition of ISO26262 with UML models                  | 35 |

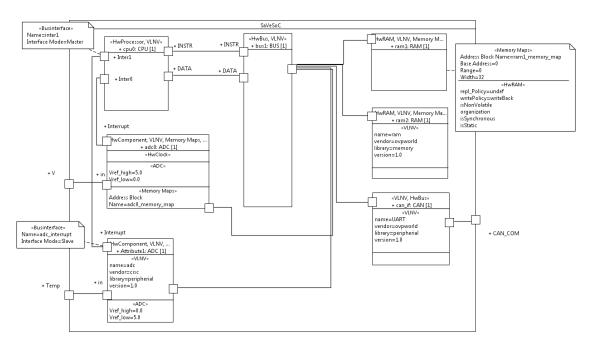

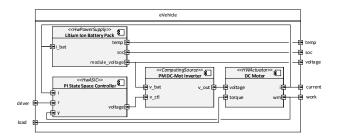

| 4.4  | SaVeSoC hardware platform                                    | 37 |

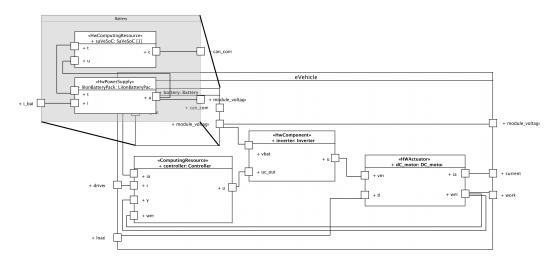

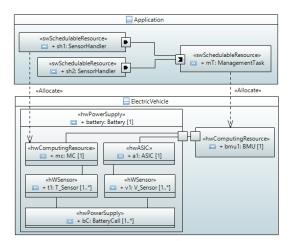

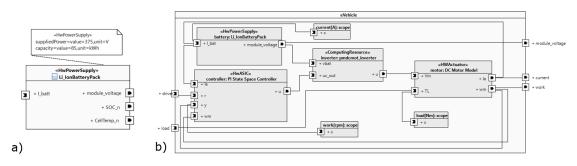

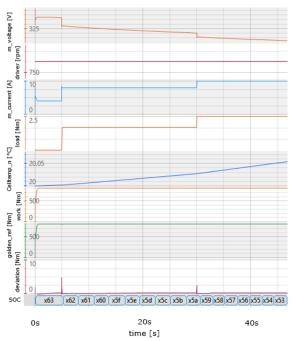

| 4.5  | Electric vehicle use case in MARTE                           | 38 |

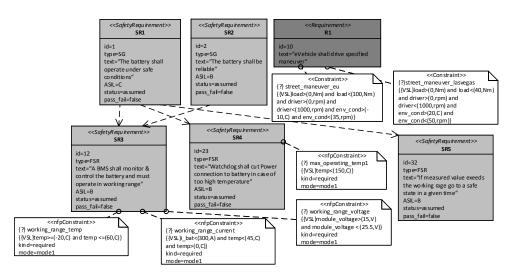

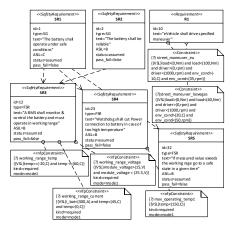

| 4.6  | Requirements and constraints pattern                         | 39 |

| 4.7  | Requirements and constraints definition                      | 40 |

| 4.8  | Safety requirements and constraints                          | 41 |

| 4.9  | UVM testbench generation                                     | 42 |

|      | UVM in a cloud-based approach                                | 43 |

|      | Simple worker queue from the enterprise integration patterns | 44 |

|      | Meet-in-the-middle approach                                  | 46 |

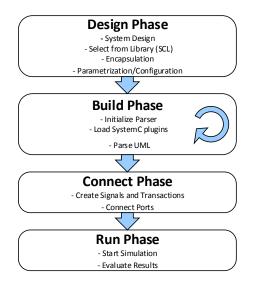

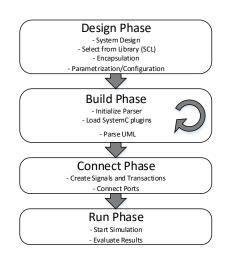

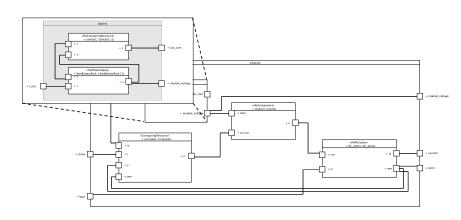

|      | SaVeSoC process                                              | 52 |

|      | SaVeSoC integration                                          | 53 |

| 4.15 | Communication channel                                        | 54 |

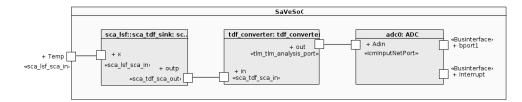

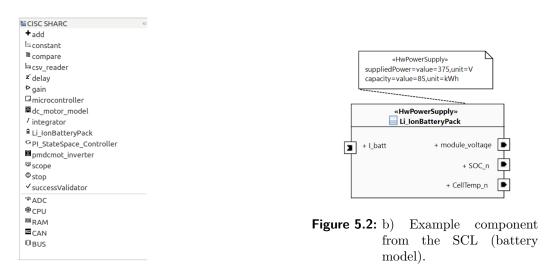

| 5.1  | System Component Library (SCL)                               | 56 |

| 5.2  | Component from the SCL                                       | 56 |

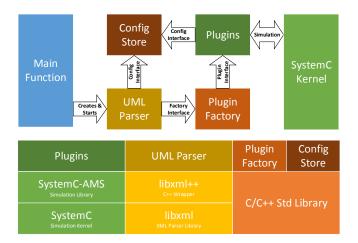

| 5.3  | Parser methodology for executable SystemC models             | 57 |

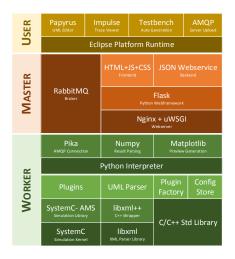

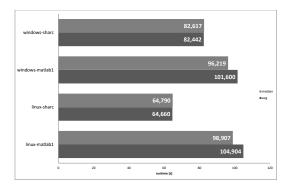

| 5.4  | SHARC framework                                              | 60 |

| 5.5  | Software stack of SHARC                                      | 61 |

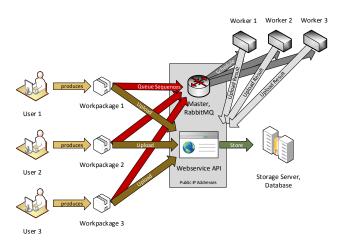

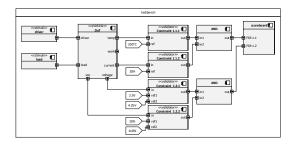

| 5.6  | Distributed simulation environment                           | 62 |

| 5.7  | Distributed simulation environment concept                   | 63 |

| 6.1  | OpenES collaboration matrix                                  | 66 |

| 6.2  | OpenES Design Flow                                           | 67 |

XVII

| 8.1 Overview of thesis contributions |  |

|--------------------------------------|--|

|--------------------------------------|--|

# List of Tables

| 2.1 | Risk graph according to ISO26262                                                                      | 10 |

|-----|-------------------------------------------------------------------------------------------------------|----|

| 4.1 | Architectural Metrics - evaluates whether the hardware achieves a certain ASIL, according to ISO26262 | 46 |

|     | Metrics definition and final savings                                                                  |    |

# List of Abbreviations

- **ADC** Analog Digital Converter.

- **ASIL** Automotive Safety Integrity Level.

- **AUTOSAR** Automotive Open Systems Architecture.

- **BMS** Battery Management System.

- **CAN** Controller Area Network.

- **CDV** Coverage Driven Verification.

- **CIM** Computational Independent Model.

- **CPU** Central Processing Unit.

- **CRV** Constraint Random Verification.

- **DSL** Domain Specific Language.

- **DUT** Design Under Test.

- **ECU** Electronic Control Unit.

- **ESL** Electronic System Level.

- **FEV** Fully Electric Vehicle.

- **FIFO** First In First Out.

- **IC** Integrated Circuit.

- **IP** Intellectual Property.

- $\ensuremath{\mathsf{ISS}}$  Instruction Set Simulator.

- **LSF** Linear Signal Flow.

- **MDA** Model Driven Architecture.

- **MDE** Model Driven Engineering.

- **MPSoC** MultiProcessor System on Chip.

- **OMG** Object Management Group.

- **OpenES** Open ESL Technologies for Next Generation Embedded Systems.

- **OVP** Open Virtual Platform.

- **PCB** Printed Circuit Board.

- **PIM** Platform Independent Model.

- **preAA** preliminary Architectural Assumption.

- **PSM** Platform Specific Model.

- **QEMU** Quick Emulator.

- **RTL** Register Transfer Level.

- SaaS Software as a Service.

- **SaVeSoC** Safety Aware Virtual Prototyp Generation and Evaluation of a System on Chip.

- SCL System Component Library.

- SHARC Simulation and Verification of Hierarchical Embedded Microelectronic Systems.

- **SiP** System in Package.

- **SoC** System-on-a-Chip.

- **SR** Safety Requirement.

- **SyAD** System Architecture Designer.

- **TCL** Tool Command Language.

- **TDF** Timed Data Format.

- **TLM** Transaction Level Modeling.

XXII

- **UML** Unified Modeling Language.

- ${\sf UVM}\,$  Universal Verification Methodology.

- **VLNV** Vendor Library Name Version.

- **VP** Virtual Prototype.

- $\ensuremath{\mathsf{VSL}}$  Value Specification Language.

# **1** Introduction

In the world of today, the amount of embedded electric/electronic (E/E) systems in various domains is increasing to a very great extent. When we think about the complexity of the past few years, it is apparent that new applications have emerged in which systems are not only interacting with each other but also have impact on the physical world, the so-called cyber-physical systems. Depending on their application, they must fulfill different requirements ranging from timing constraints, performance behavior, low power consumption, thermal or even working capability under different environmental conditions. The point here is, we live in a world where cyber-physical systems are ubiquitous. They have an impact on our daily lives and the malfunction of these systems can lead to severe damage or injury to people. We must thus ensure the dependability of these systems.

This is even more obvious when we turn to the automotive domain. It can be observed that there is a shift towards fully E/E systems resulting from the trend towards electric vehicles. In fact, a car is now more or less a smartphone on wheels. The sensing and controlling is the work of the highly distributed electronic control units (ECU), and it is no surprise, that through all these new features in cars, more than 100 of these microcontrollers [18] are currently integrated in a modern car. This situation also has an impact on the amount of software in cars today, which can total 150 million lines of code [30]. The communication between these ECUs even extends beyond the border of a car body. For complex assistance features, cars have to communicate with each other (V2V ) and also the infrastructure must be involved in the computation (V2I). Although, the goal and motivation in the development of a car stayed the same. The aim is to develop better, more reliable and safe products which reduce the number of deadly accidents. But the industry is facing new problems through the emergence of many new (assistance-) features that are also influencing each other. In turn, this raises the complexity level in the design, development and verification of complex systems and imposes an enormous effort for engineers in developing their applications. In terms of safety, these systems must fulfill standards such as ISO26262 (functional safety for road vehicles), [42]. Since this standard is now treated as state of the art in court, OEMs and their suppliers are required to develop and test their systems towards the recommended measures and methods. It is no longer sufficient to test single hardware or software components, the functionality of the whole system must be verified.

With the aim to increase the level of abstraction and automation, the Model Driven Engineering (MDE) approach has found its way into the development of systems and software. MDE has the benefit of being more flexible towards platform and staff changes, of reducing development and maintenance costs, increasing quality and moreover faster development cycles. However, this approach still faces some major challenges when thinking about tooling support. Compared to the landscape of programming languages MDE tools are weak. Due to the fact that developers are more into coding than modeling the acceptance of MDE approaches is still low. Furthermore, using MDE in bigger projects can lead to badly formed models, when using a too general purpose language or having too many domain-specific languages for modeling. Some modeling languages only cover a part of the development cycle, which means that companies have to invest effort and costs to support the rest of the life-cycle [12].

When we discuss the design of a system, a single modeling language immediately springs to mind, the Unified Modeling Language (UML), [35]. Having its roots in the software domain, UML paved the way and established a model-based thinking in various engineering domains, far across the borders of conventional software design. Since UML comes with several extensions such as MARTE [63], SysML [62] or EAST-ADL [26], engineers from different domains can use the full potential of an object-oriented approach. MARTE was introduced to overcome the enormous complexity issues in the design of real-time and embedded systems. It provides capabilities to model hardware, software as well as system design and provides the representation of timing, resource and performance behavior. Furthermore, UML/MARTE is already used for several reliability analysis techniques. Moreover, many semiconductor companies and suppliers are relying on this modeling language and it is used by several European projects such as the Open ESL Technologies for Next Generation Embedded Systems (OpenES) [16]. OpenES is a European initiative to fill the gaps in today's design flows and to develop common solutions to stay competitive on the world market.

Since today's state of the art car of today exists not only in one single version but rather in several hundreds of variants all with different features, each of which must be exhaustively tested to fulfill the standards. Millions of test kilometers must be driven to ensure the reliability of a car and it is neither economic nor safe to test them in a real environment [56]. Simulation plays an ever increasing and important role in the verification of the modern car. The virtual environment can easily be modified and the car can be represented in its different variations resulting in an economic advantage. Simulations can be done in early development phases, where the detailed implementation of a function is still undecided and based on platform-specific models where the hardware and software are explicitly defined (virtual prototype). Applied verification methods and tests can be monitored, reproduced and rerun every time. Another advantage of simulation is that it cannot only be run day and night but also massively in parallel. A specification and simulation language, which shares the same philosophy as the UML/MARTE approach, is SystemC [3]. Like UML, it shares the Model Driven Architecture (MDA) approach, starting from a higher-level system design (computational independent), down to hardware and software design.

In this work we present a novel design and development flow for a safety aware virtual

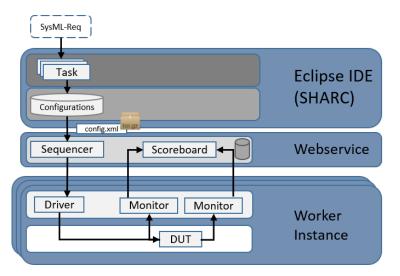

prototype. This design flow conforms to the ISO26262 standard and meets all its requirements to produce a reliable product in the end. The whole system, from a first functional specification down to hardware design, is specified by standardized modeling languages. Before the virtual prototype is generated from the hardware specification, several reliability analysis methods are applied and executed on this specification. This allows an early evaluation of the hardware design regarding safety before testing the prototype in simulation. Furthermore, we show the integration of the generated virtual prototype into the system design, to verify its functionality and interfaces. The whole methodology is available through the developed design and verification framework named SHARC (Simulation and Verification of Hierarchical Embedded Microelectronic Systems), [19].

#### 1.1 Thesis Background

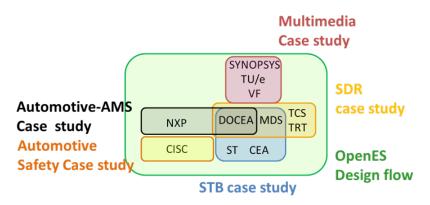

This thesis was carried out in cooperation with the industrial partner CISC Semiconductor GmbH. CISC is an international company within the field of automotive and RFID based in Klagenfurt, Graz (Austria) and Mountain View, California (US). In the automotive domain, their expertise lies in supporting the development process by enhanced verification methodologies and tools. This includes system integration of automotive systems through the support of simulation, virtual prototyping or HW/SW co-simulation. Being involved in joint R&D activities with all major European car manufactures and its suppliers in the area of microelectronic systems, CISC is driving new activities to handle the increased system complexity by their simulation-based system design methodology and wide spread system know-how. This expertise is also honored by various international standardization bodies, to which CISC is continuously contributing. Thanks to their organizational independence CISC can easily adapt to customer needs and offer project-specific tailoring and scaling of development processes and to adapt to project-dependent requirements. Furthermore, this thesis has profited from the influence of two major European projects, OpenES [16] and eRamp [31]. The TU Graz and CISC Semiconductor closely cooperated with well-known companies in the field of semiconductors. This includes partners from universities, research organizations (RTO) and industry such as ST, NXP, Infineon, CEA-List or Verimag.

#### 1.2 Problem Statement

This thesis aims at improving the model-based development and verification of embedded automotive safety-critical systems from a first initial system design down to hardware and software implementation. To gain a good understanding of the problems and complications that can occur during the development process, a fundamental factor is to get a comprehensive overview of the related work in this domain.

To cope with the high complexity in the integration of advanced embedded systems, the use of advanced methods and design tools is more relevant than ever. Besides the complexity and heterogeneity, different kinds of constraints and requirements associated with the design of embedded systems must be taken into account. These systems combine ever increasing complex software with complex hardware components (Intellectual Property (IP), Integrated Circuit (IC), System-on-a-Chip (SoC), System in Package (SiP), Printed Circuit Board (PCB)) and their design is confronted with the following issues:

- Current tools and flows hit the limits of complexity and therefore are not capable to efficiently address software and hardware design and optimization in a joint way.

- Increasing design effort makes SoC integration not affordable for many applications.

- The technological, organizational and design gap between different abstraction levels in today's development processes is not covered by current methods and tools.

- Extra-functional properties like timing performance, power consumption or reliability are only partially addressed by disjoint special flows. Inconsistency, inefficient design iterations, incorrectness, incompleteness and finally sub-optimal results are the consequences.

- Increased effort in system design verification through dynamically changing design.

- The number of tools involved in today's design flow is rising, thus leading to a complex tool-chain where important information is distributed over several disjoint tools and organizations.

- Exchange of information between simulation-based verification and reliability analysis throughout the whole development process, which are both highly required by the ISO26262 standard.

- Manual steps in the design and verification process without tool support.

This situation is even getting worse as the number of extra-functional properties such as safety or security and their importance is increasing. Furthermore, the expectations on system reliability are also significantly increasing or even become stringent in automotive or transportation applications. A further demand for more features (X-by-wire) and improved functionality (ADAS, autonomous driving) increases the complexity of future systems dramatically. Without advanced methods and tools, the effort in tackling these issues leads to an increase in development costs and time, and thus to missing the time-to-market window.

In the aim to verify complex and heterogeneous systems, a simulation-based approach is an effective way to gain more insights on the behavior of the whole system This is also stated and highly recommended by the functional safety standard ISO26262 for higher safety levels. Since these systems can have several different configurations depending on their purpose and are affected by a fast changing environment, they must exhaustively be tested towards their specific requirements. For fast and safe ramp of these devices, full coverage of parameter variation in simulation is, therefore, a primary success factor. Moreover, these systems are composed of highly heterogeneous subsystems on different abstraction levels, e.g. digital, analog, mechanical or software, which has an impact on the complexity and demands to combine different simulators in one framework. Due to this, simulation of complex systems can lead to a greater challenge in terms of managing complexity, hardware resources, simulation time (days or even months) and the amount of data produced. Moreover, a seamless integration of a virtual prototype into the upper layer of the system level specification and thus closing the design and verification gap is still an open issue in today's development.

Another issue is the fragmentation of the information to be captured at several levels of abstraction. Today, top-level specification is usually described in natural languages, which can lead to ambiguities or diverging interpretations between several teams involved in the design process such as system, software, hardware or verification teams. This effect is reinforced through additional effort in the development of safety-critical systems. Since model-based approaches are not yet common in the automotive industry, new design methods and tools must be introduced and are essential to avoid redundancy of information and ensure consistency all over the design process.

Therefore, this thesis aims at solving the main research questions by targeting the following goals:

- A seamless design process which helps to close technological, organizational and design gaps across abstraction levels in today's development of embedded automotive systems regarding functional safety.

- Development and integration of novel, model-based reliability analysis techniques and simulation-based verification in the proposed design process.

Besides the stated primary goals of this thesis, the following secondary goals are targeted:

- Reduction of the number of tools involved in the design process, thus to provice high traceability across design, requirements, tests and results which lead to high consistency, correctness, and completeness of models.

- Reducing manual steps, by introducing novel automation techniques throughout the development process.

#### 1.3 Contributions

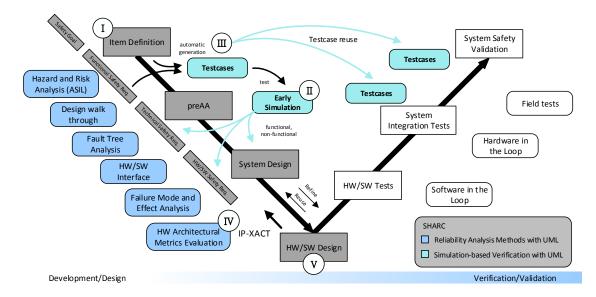

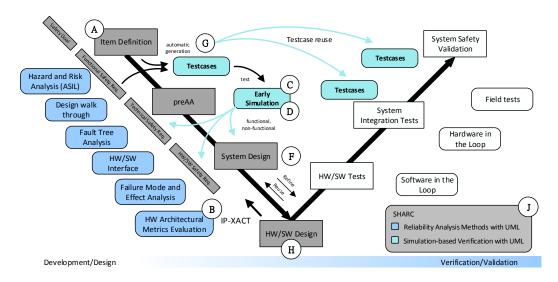

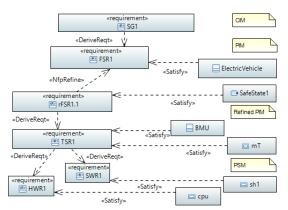

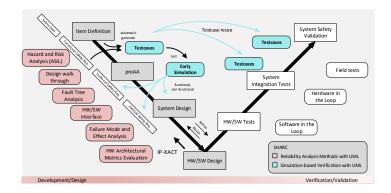

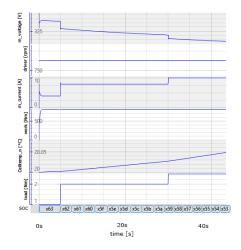

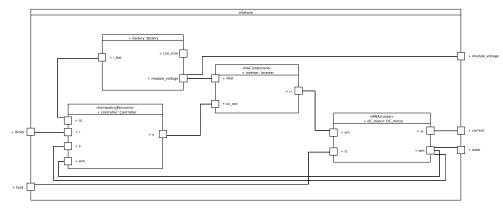

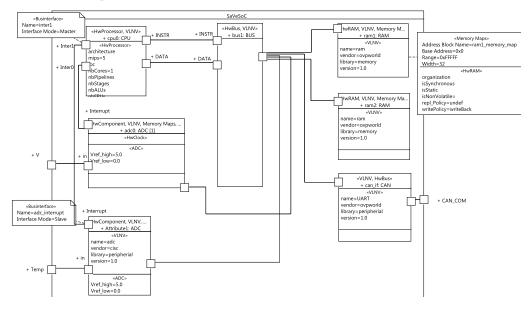

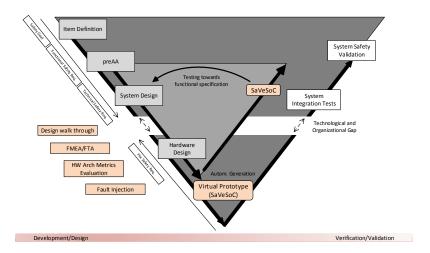

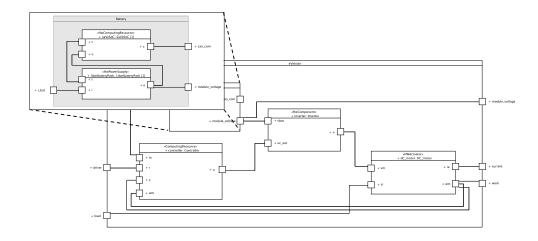

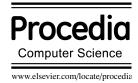

The overall scientific contributions of this thesis are presented in Fig.1.1. It shows an industrial V-model with safety extensions as it is specified in the functional safety standard ISO26262, better known as safety lifecycle. The contributions are listed in a numerical format, regarding their chronological appearance in the development cycle. Throughout this thesis we will demonstrate our proposed solutions by an industrial use case of a Battery Management System (BMS) provided by CISC Semiconductor GmbH. The use case illustrates a simplified version of the real application; it does neither represent an exhaustive nor a commercially-sensitive project and shall only provide evidence of the proposed solutions. First (I), we propose a novel design method for safety-critical systems, based on standardized modeling languages. With the help of an additional layer in the MDA, a gap in the design could be closed, and a seamless flow could be achieved. This design flow includes structural but moreover behavioral models, which describe safety aspects within the focus on ISO26262. Furthermore, this thesis emphasizes different reliability analysis techniques, which can be applied on these models throughout the development process. In

Figure 1.1: Overview of the contributions of this thesis that include techniques and tools that are applied during development to enhance the safety and reliability of the complete system.

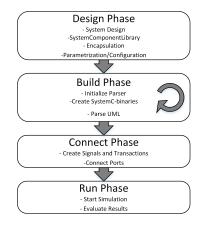

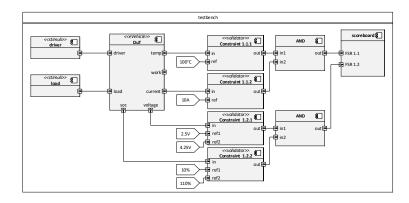

(II), we describe how these structural models can be connected to executable models for behavioral simulation on system level and how to provide a seamless integration into the design flow. This includes the definition of interfaces for analog and digital simulation but also specification and configuration of the whole system. Contribution to (III) addresses the definition of safety requirements and constraints in a machine-readable and semiformal structure. From this definition, testbenches for the verification of system safety requirements are automatically generated. This includes the verification of the system under different environment conditions and in different configurations to raise the level of functional coverage. To speed-up the coverage process, these independent simulation runs are distributed to a cloud-based environment. Results from the system verification can be directly used for the hardware platform design. The configuration and evaluation of the hardware platform regarding hardware faults is described in (IV). How this configuration leads to the automatic generation of a first virtual prototype will be explained in (V). Moreover, we show the seamless (back-)integration of the generated virtual prototype into the system design (functional specification) by using the novel methodologies implemented as a complete verification framework. This approach guarantees consistency, correctness and completeness within the overall system design and specified functionality.

### 1.4 Organization of the Thesis

The rest of this thesis is organized as follows. Chapter 3 discusses existing work in the area of design of safety-critical systems, design flows and virtual prototyping. Then, a novel design flow approach based on standardized modeling languages which includes design, evaluation, verification and integration of safety-critical systems is presented in Chapter 4. Chapter 5 describes how the methodologies have been implemented in the design and verification framework SHARC. Chapter 6 gives insights about the evaluation of the developed OpenES design flow and the specific SaVeSoC design flow. Finally, Chapter 7 concludes this thesis by summarizing the obtained results beyond the state of the art, and by providing hints on future research directions.

# 2 Background

This chapter provides definitions of key terms and a brief introduction to the background related to this thesis.

#### 2.1 Functional Safety

ISO26262 is the functional safety standard for safety-critical systems in road vehicles. This standard addresses possible hazards caused by malfunctioning behavior of safetyrelated systems. It also provides an automotive safety life cycle that covers safety aspects throughout the whole design and development process of modern products and systems. In the first phase, the concept phase (Part 3), the to-be-developed item is defined. The item definition describes the boundaries and interfaces as well as assumptions about systems or arrays of systems, to which functional safety is applied. After performing a hazard and risk analysis on the item to identify and categorize the hazards, the safety goals are derived, and the corresponding Automotive Safety Integrity Levels (ASIL) are determined (2.1). The ASIL specify the item's necessary safety requirements to avoid unreasonable risk due to malfunction. The ASIL is determined by three impact factors: severity (S0-S3), probability (E0-E4) and controllability (C0-C3). This results in four ASIL levels (A to D), where ASIL A is the lowest and ASIL D the highest level. The class quality management (QM) denotes no safety requirements to comply with ISO 26262. Following the determination, the product is developed using recommended methods and measures according to its ASIL.

After determination, the product is developed with recommended methods and measures according to its ASIL. The derived functional safety concept contains safety measures, including the safety mechanisms to be implemented in the item's architectural elements and these are specified in the functional safety requirements. After defining the functional safety requirements, the technical requirements, including those for the hardware and software, are derived. This, in turn, results in a safety case, to show that the system is acceptably safe. The safety case is used to collect and present evidence and to support safety claims and arguments.

#### 2.1.1 System Life Cycle

To more fully understand the safety life cycle and its concept we have to start with the definition of the global product/system life cycle. In integrated engineering, the produc-

| Severity Class   Probability Class   Controllabi |    |    | lity Class |    |

|--------------------------------------------------|----|----|------------|----|

|                                                  |    | C1 | C2         | C3 |

|                                                  | E1 | QM | QM         | QM |

| S1                                               | E2 | QM | QM         | QM |

| 51                                               | E3 | QM | QM         | А  |

|                                                  | E4 | QM | А          | В  |

|                                                  | E1 | QM | QM         | QM |

| S2                                               | E2 | QM | QM         | А  |

| 52                                               | E3 | QM | Α          | В  |

|                                                  | E4 | A  | В          | С  |

| S3                                               | E1 | QM | QM         | А  |

|                                                  | E2 | QM | А          | В  |

|                                                  | E3 | A  | В          | В  |

|                                                  | E4 | В  | С          | D  |

Table 2.1: Risk graph according to ISO26262.

t/system life cycle comprises all phases that the product/system goes through from the idea to its end-of-life and revival. This includes the different phases in a closed loop from design, manufacturing, distribution, customization, the end-of-life and revival.

The safety life cycle is embedded in the product/system life cycle and is explicitly focusing on the safety aspects and issues regarding functional safety. Its emphasis is on the activities during the concept phase (Part 3), product development (Part 4-system, Part 5-hardware and Part 6-software), production, operation, service and decommissioning (Part 7). Part 1 and 2, as well as 8 to 10 are not part of the safety life cycle but supporting it for completeness.

The industrial V-model is a graphical representation of the system life cycle. It is an extension to the tradional waterfall model, where the process follows a sequential flow, while the V-model is a simultaneous process. It helps to ensure that the results to be provided are complete and have the desired quality. Instead of the waterfall model, results can be tested during development of the system. By applying standardized processes, effort concerning development, production, operation, and maintenance can be estimated and controlled over the entire project. Furthermore, it helps to gain a common understanding and improves the communication between all stakeholders. The V-model gives an overview of the main activities to be performed and results that have to be produced during development, from the decomposition of requirements (left side) to integration of parts and their validation (right side). However, validation can be applied on the left side as well. This brings us to the difference between validation (are we building the right thing?) and verification (are we building the thing right?). According to the PMBOK guide (Project Management Body of Knowledge) [1], these two terms are defined as:

- "Validation. The assurance that a product, service, or system meets the needs of the customer and other identified stakeholders. It often involves acceptance and suitability with external customers. Contrast with verification."

- "Verification. The evaluation of whether or not a product, service, or system complies with a regulation, requirement, specification, or imposed condition. It is often an internal process. Contrast with validation."

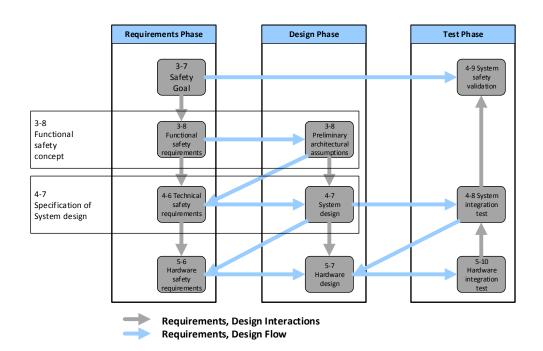

#### 2.1.2 Safety Life Cycle

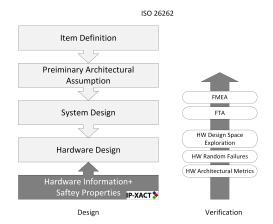

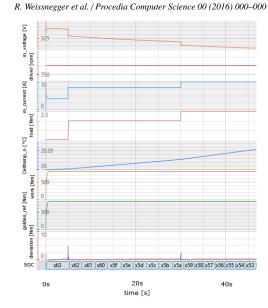

The safety life cycle can also be represented as a V-model of the system life cycle with some minor adaption to the functional safety standard. The engineering processes have been organized in such a way that each process on the left side has a corresponding testing task on the right side. The overall V-model includes two smaller V-models, which handle the hardware and software development processes. The V-model follows a requirementdriven approach which means that design and tests are derived from requirements. Each system requirement must be traceable to one or more design elements, tests, and vice versa. In the ISO26262 they are separated in phases, where each activity in the standard has dependencies between either the requirements, the design or the test phase (Fig.2.1). These phases are arranged vertical, and each activity can be derived from the upper-level indifferent phases, e.g., the hardware safety requirements are derived from the technical safety requirements and also depend on the inputs from system design. We will discuss a more illustrative example in 4.2.

#### 2.1.3 Stakeholder Analysis

The functional safety manager is responsible for coordinating and integrating all activities during the life cycle. Furthermore, he coordinates the different stakeholders, which take part in the whole life cycle. The definition of the stakeholder is "holding a stake," which means that everyone who has an interest in and can influence the process in a positive or negative way should be considered. A stakeholder analysis can give important inputs on who are the essential stakeholders regarding size (influence), distance (communication) and quality (relationship). Essential stakeholders in the context of the product life cycle are, e.g., clients, end users, customers, suppliers, design engineers (system, hardware, software), quality engineers, distributors, marketing, security engineers and safety engineers. In traditional product cycles, engineers are often decoupled from production or other departments, which can directly affect the development and design of a product/system. In modern, integrated design, all actors that are holding a stake in the product cycle should actively take part in the development process. This bi-directional relationship between designers and other stakeholders helps to achieve integrated design and to bring important properties such as safety or security into the product.

Figure 2.1: Relationship between the software, requirements and test phases in ISO26262.

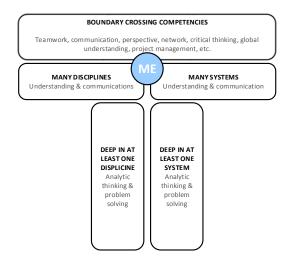

This discussion brings us to another important topic in today's design teams, the differentiation between I- and T-shaped people. The I-shaped professionals are people who have a deep insight in one field of expertise (thinking narrow and tide). They are highly versed in a specific area and learn from drilling more deeply into a particular field. Tshaped people have broader skills and knowledge and learn by different perspectives from different specialties. The vertical bar of the T describes the expertise of professionals in a certain field. The horizontal bar depicts the ability to think and collaborate across various disciplines and systems. T-shaped people not only have in-depth knowledge, but they also share empathy and enthusiasm for other people's expertise. According to [85], they have the competencies and soft skills to cross boarders in terms of teamwork, communication, perspective, networks, critical thinking, global understanding or project management across one or many disciplines and systems. Although T-shaped people are important in today's development and design, this should not raise the impression that others are less important; both types are essential in modern organizations. It is the competence to communicate and collaborate across different areas of expertise and to share information competently with non-experts. From the academic perspective, Information and Computer Engineering (ICE) [34], former Telematics at the Technical University of Graz (TU Graz), can be seen as a place where T-shaped people are formed. Besides the education in computer science including different and diverse disciplines such as mathematics, electrical engineering, informatics or telecommunication, also extra-functional properties such as information security or safety are well embedded in the curriculum. Furthermore, the integration of soft skills in project management, team building, customer perspective or law, are the basis of a T-shaped professional. Several other shapes are mentioned nowadays in literature, such as hyphen-shaped, pi-shaped, H-shaped or V-shaped but are out of the scope of this thesis.

Figure 2.2: The T-shaped professional.

If we project this view on functional safety, it is important that safety managers and engineers understand problems regarding hardware or software development and vice versa, engineers understand problems from the functional safety perspective. This forms, in the end, a Y-shaped professional, who combines two separate areas of expertise (which should naturally overlap) into one. In a modern, integrated design these people are key to integrate system/product properties such as functional safety.

A way to support this process and step towards achieving the goal of an integrated design is the model-based concept. It helps to communicate between several disciplines and to gather a common understanding of problems in the design. All in all, this is an important step towards a safe and reliable product, which also leads to faster time-to-market and reduction of development costs and product recalls.

## 2.2 Model-driven Engineering

In the aim to increase the level of abstraction and automation the MDE approach has found its way into the development of systems and software. One of the most popular MDE approaches is MDA, developed by the Object Management Group (OMG) standardization body. The MDA approach was driven by the diversity of systems, programming languages and frameworks in order to address interoperability and compatibility issues. As it is stated in the standard in the MDA Guide Version 1.0.1 from the OMG [57]: "In the ideal sense, computing should be viewed by the users as "my" world, with no artificial barriers of the operating system, hardware architecture, network compatibility, or application incompatibility. Given the continued, and growing, diversity of systems, this will never be achieved by forcing all software development to be based on a single operating system, programming language, instruction set architecture, application server framework or any other choice. There are simply too many platforms in existence, and too many conflicting implementation requirements, to ever agree on a single choice in any of these fields."

Conclusion: "We must agree to coexist by translation, by agreeing on models and how to translate between them."

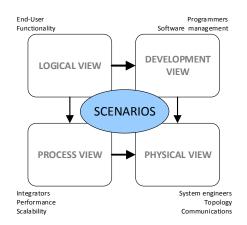

Organization of specialized people in projects of a certain size requires a lot of effort. Therefore, it is becoming increasingly important that stakeholders from different domains, e.g., hardware, software, system design but also safety and security engineers can efficiently work together. Particularly in the verification of safety-critical systems, safety managers and specialists need an entire view of the system that includes all domains involved in the system design. Such a design, expressed in an architectural description, supports the understanding of the system's essence and key properties regarding its behavior, composition and evolution. This, in turn, can bring to light concerns regarding feasibility, maintainability, and utility of the system. To overcome the issues with different stakeholders involved in the design process, [45] defined that an architecture description can have one or more architecture views. A view helps to address the various concerns held by the system's stakeholders. According to [43]: "A view is governed by its viewpoint: the viewpoint establishes the conventions for constructing, interpreting and analyzing the view to address concerns framed by that viewpoint. Viewpoint conventions can include languages, notations, model kinds, design rules, and/or modeling methods, analysis techniques and other operations on views.

One well-known viewpoint model is the "4+1" by [46]. This model allows to separately address the concerns of the various stakeholders of the architecture, as well as functional and extra-functional requirements. To capture large and challenging architectures, they propose a model consisting of logical view, process view, physical view and development flow. The logical view includes the used objects in the design. The process view captures the concurrency and synchronization aspects. The physical view describes the software to hardware mapping, whereas the development view depicts the static organization of the software in its development environment. These four views are organized around a fifth view, which represents the use cases or scenarios. The "4+1" view model described a rather generic approach, where other notations, tools or design methods can be used. For our purpose, we will focus on the unified modeling language standard (UML), which provides us with different diagrams to describe our system from different point of views.

Figure 2.3: The 4+1 view model according to [46].

## 2.2.1 Design Languages

### UML

UML is one modeling standard by the OMG [75]. It is a graphical representation for specification and documentation of software and other systems. With UML it is feasible to model application structure, behavior, architecture and also business processes and data structures. It delivers a complete view of the system, its individual components and the interactions between them. UML also declares how the system is expected to be used (special focus on system level use cases) providing different types of structural and behavioral diagrams. Another advantage is a common formalism to ease the exchange of information between stakeholders involved in the design and avoiding multiple captures of the same information. Although UML has advantages in capturing system level use cases and specifying system and software design, it lacks a proper definition for hardware design and non-functional properties such as timing, performance or thermal behavior. Extensions have been developed to overcome these issues.

#### SysML

SysML is an extension to UML2 and is a graphical modeling language for describing complex systems in system engineering. It supports the specification, analysis, verification and validation of a broad range of systems. It provides extensions to diagrams for describing behavioral and structural properties in UML2. Also, it has two additional diagrams (requirement, parametric) for requirements engineering and performance analysis. SysML is smaller and easier to learn than UML. One of the advantages of SysML is the mechanism to capture performance and quantitative information. It provides a good allocation of requirements to components, but it is inaccurate and provides no extra-functional properties.

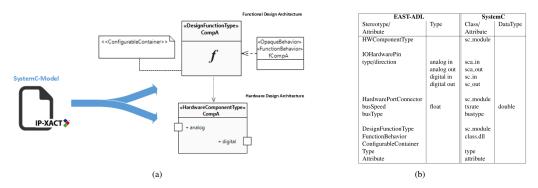

#### EAST-ADL

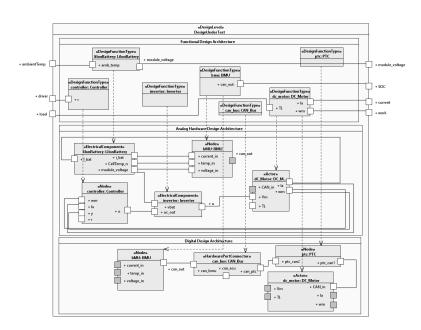

One modeling language that has established itself in the automotive domain is EAST-ADL. It allows capturing detailed automotive electric and electronic systems on five layers of abstraction, each with a clear separation of concerns: Vehicle, Analysis, Design, Implementation and Operational Level. Besides structural aspects, this modeling language allows the expression of behavior, requirements, verification and validation. The highest level is the Vehicle Level that describes electronic features to allow integration of product variability. The Analysis Level includes the Functional Analysis Architecture (FAA), which allows an abstract functional representation of the architecture (what the system shall do), in relation to the features from the Vehicle Level. The Design Level allows the decomposition of models in the FAA to Functional Design Architecture (FDA) models and Hardware Design Architecture (HDA) models. Within these models the functional representation of the architecture can be allocated onto the hardware platforms. The applications are represented by *DesignFunctionTypes* with annotated behavior and configurations. The hardware components are modeled by Sensors, Nodes (ECUs), Actuators and HardwarePortConnector (Buses) and more. They are interconnected by IOHardware-Pins or CommunicationHardwarePin and wired by HardwareConnectors. The last two layers (Implementation, Operational) are the realization of the implementation in Automotive Open Systems Architecture (AUTOSAR). Therefore, the models on these levels are compliant with the AUTOSAR specification. The behavior of components on all these levels is not explicitly addressed in EAST-ADL. It can be either expressed by behavioral diagrams (state machines, activity diagram) or externally in tools like Matlab.

EAST-ADL as automotive modeling language also addresses parts of the functional safety standard ISO2626, which was one of the outcomes of international projects like ATESST[10] and MEANAD[53]. This enables the language for safety analysis like Fault Tree (FTA) or Failure Mode and Effect Analysis (FMEA), but also for defining safety requirements and achieving high traceability of models and behavioral diagrams. Furthermore, this language provides means to describe validation and verification activities by VVCases. Since EAST-ADL is included in an Eclipse UML2 Editor called Papyrus [28], complex systems can be designed without licensing costs.

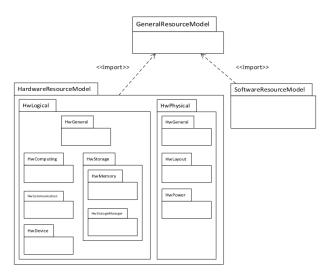

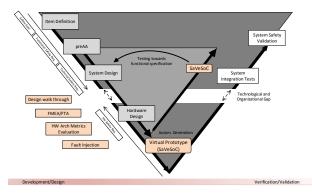

#### MARTE

MARTE is defined as a profile in UML2 and provides additional mechanisms for modeling real-time systems, which are missing in UML. Thanks to the UML extension mechanism, the software resource model (SRM) and hardware resource model (HRM) profiles extend UML2 with concepts for software and hardware. The purpose of the SRM package is to design software of real-time and embedded applications. It consists of the SW ResourceCore, which provides the basic software resource concept. The HRM is an extension to UML and serves as a description of existing and for the conception of new hardware platforms. These descriptions can be made of different levels of granularity. The HRM is grouping most hardware concepts under a hierarchical taxonomy. It is composed of a logical view (HwLogical) that classifies hardware resources depending on their functional behavior and a physical view (HwPhysical) that focuses on the physical nature. The HWLogical model provides a classification for different hardware entities such as computing, storage or communication. This includes stereotypes like HwASIC, HwProcessor, HwBus, HwDevice or HwMemory. All the stereotypes defined in the HRM package are organized under a tree of inheritances (Fig. 2.4 from more generic stereotypes. This has the advantage that if no stereotype suits to model a used hardware component, a more generic stereotype may fit instead. As an example, a HwSensor inherits the properties from HwI/O and is furthermore a specialization of Hw Device. In contrast, the HW-Physical package contains stereotypes as physical components. They describe their shape, size, and position within the platform, power consumption or other physical properties.

Figure 2.4: MARTE levels of granularity.

#### Domain specific language

A Domain Specific Language (DSL), or application specific language is a formal language, which is used to describe a problem in a specific domain (e.g., avionics, financial services) and eases the interaction between human and computer. This language needs a specific design and implementation for a certain domain where it is supposed to be used. In the development of a DSL, the target is to achieve a high degree of specificity of a problem.

This concept shall ensure that everything in the target domain can be described, and everything surrounding this domain is negligible. Thus, a domain specific language can lead to an excess of highly specialized language concepts that is difficult to learn and cumbersome to use [77].

#### **Evaluation of Design Languages**

To determine which design language is the most efficient to describe a complete safetycritical system in an automotive environment, we evaluated the before mentioned design languages regarding six important aspects (Figure 2.5):

- Standardization (interoperability with other tools)

- Level of abstraction (defined in the language)

- Application (software architecture)

- Hardware platform (architecture)

- Extra-functional properties (supports e.g., timing behavior)

- Requirements (supports definition of requirements)

|                             | DSL      | UML               | SysML        | EAST-ADL     | MARTE |   |

|-----------------------------|----------|-------------------|--------------|--------------|-------|---|

| Standardized                | 8        | Ø                 | Ø            | Ø            | Ø     | _ |