Inge Siegl, BSc.

# Capacitive Charge Pump based Low Power Pipeline ADC

# MASTER'S THESIS

to achieve the university degree of

Diplom-Ingenieurin

Master's degree programme: Electrical Engineering

submitted to

# Graz University of Technology

Supervisor

Ass.Prof. Dipl.-Ing. Dr.techn. Peter Söser

Institute of Electronics

# AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present master's thesis.

Date

Signature

# Abstract

This thesis investigates the low power design for pipelined analog-to-digital converters. The focus is on the multiplying-digital-to-analog converter (MDAC) block, whereof various switched capacitor based principles are presented. It aims to avoid power hungry operational amplifiers which are common in these state of the art solutions. The research question was, whether this is possible while maintaining a high enough gain accuracy for operation without digital calibration. The most important contribution is a new topology which uses only one sampling capacitor per channel. Therefore, the proposed circuit is characterised by a less complex design and requires less area on chip. Additionally, it reaches a better gain accuracy for equally sized sampling capacitors. Simulation results are provided to confirm these statements. The thesis concludes with a discussion of trade-offs between the different presented design approaches.

# Kurzfassung

Diese Arbeit untersucht das Design von leistungsarmen *pipeline* analog-zu-digital Umsetzern. Der Fokus liegt dabei auf dem *multiplying-digital-to-analog converter* (MDAC) Block, wovon verschiedene *switched capacitor* basierte Topologien vorgestellt werden. Das Ziel war leistungshungrige Operationsverstärker, welche in bekannten Lösungen häufig Verwendung finden, zu umgehen. Die Frage war, in wie weit dies möglich ist, wenn trotzdem die Verstärkungsgenauigkeit gewahrt bleiben soll, um eine Funktion ohne digitale Kalibrierung zu ermöglichen. Die wichtigste Errungenschaft ist eine neue Topologie, welche nur eine sampling Kapazität pro Kanal aufweist. Die vorgestellte Schaltung ist daher weniger komplex und braucht weniger Platz am Chip. Darüber hinaus erreicht sie bei gleich großen Kapazitätswerten eine bessere Verstärkungsgenauigkeit. Entsprechende Simulationsergebnisse werden bereitgestellt, um diese Behauptungen zu belegen. Die Arbeit schließt mit einer Diskussion der Kompromisse der unterschiedlichen vorgestellten Methoden. This thesis was carried out at the Institute of Electronics

in cooperation with ams AG

and is dedicated to my two grandmas, who never quite knew what I was studying, but were still proud of me.

# Thanks

On the technical side I want to thank:

Andrzej Gajdardziew, first of all for the topic, which got me hooked on. But more importantly for the numerous inspiring discussions, never killing an idea and his amazing gift to explain.

Mario Manninger, who kept the project alive and made sure that its outcome will hopefully be of use for the ams AG, which was a sponsor of this project.

Peter Söser, for his guidance and providing me a great freedom in the realization of this thesis. Thanks also goes to John Thompson, who was helping me along with good old-style pen and paper analysis; to Peter Speer, who contributed with his layout skills, but also to Pietro Cipriano, Andreas Haller, Anneliese Moser, Beatriz Olleta, Sudhakar Singamala, Christian Wunderl and Christian Zangl who made coming to work simply more pleasurable.

Further, I want to thank my sister and my mother for their motivation and support. As well as my dad for bringing me in touch with the world of electronics at an early age which was probably why I later even considered studying it.

Finally, a big tribute goes to Andreas Daniel Sinnhofer, who did not only support and encourage me throughout my time at university, but also had to stand me when I was physical at home but my mind still at work.

# Contents

| Abstract |       |         |                                                |    |  |  |  |  |

|----------|-------|---------|------------------------------------------------|----|--|--|--|--|

| 1.       | Intro | ductio  | n                                              | 1  |  |  |  |  |

|          | 1.1.  | Structu | are                                            | 2  |  |  |  |  |

| 2.       | Moti  | vation  |                                                | 3  |  |  |  |  |

|          | 2.1.  | Area a  | nd Power Consumption                           | 3  |  |  |  |  |

| ١.       | Fur   | ndame   | entals                                         | 4  |  |  |  |  |

| 3.       | Anal  | og-to-l | Digital Conversion                             | 5  |  |  |  |  |

|          | 3.1.  | Ideal ( | Characteristics                                | 6  |  |  |  |  |

|          | 3.2.  | Error 1 | Measures of Actual ADCs                        | 6  |  |  |  |  |

|          |       | 3.2.1.  | Static Errors                                  | 6  |  |  |  |  |

|          |       |         | 3.2.1.1. Offset Error                          | 8  |  |  |  |  |

|          |       |         | 3.2.1.2. Gain Error                            | 8  |  |  |  |  |

|          |       |         | 3.2.1.3. Integral Non Linearity - INL          | 8  |  |  |  |  |

|          |       |         | 3.2.1.4. Differential Non Linearity - DNL      | 8  |  |  |  |  |

|          |       |         | 3.2.1.5. Missing Codes and Monotony Errors     | 8  |  |  |  |  |

|          |       | 3.2.2.  | Dynamic Errors                                 | 8  |  |  |  |  |

|          |       |         | 3.2.2.1. Signal-to-Noise Ratio - SNR           | 9  |  |  |  |  |

|          |       |         | 3.2.2.2. Signal-to-Noise and Distortion Ratio  | 10 |  |  |  |  |

|          |       |         | 3.2.2.3. Effective Number of Bits - ENOB       | 10 |  |  |  |  |

|          |       |         | 3.2.2.4. Total Harmonic Distortion - THD       | 10 |  |  |  |  |

|          |       |         | 3.2.2.5. Spurious Free Dynamic Range - SFDR    | 10 |  |  |  |  |

|          |       |         | 3.2.2.6. Effective Resolution Bandwidth - ERBW | 11 |  |  |  |  |

|          |       | 3.2.3.  | Figure of Merit - FOM                          | 11 |  |  |  |  |

| 4.       |       | Topol   | -                                              | 12 |  |  |  |  |

|          | 4.1.  | Direct  | ADCs                                           | 12 |  |  |  |  |

|          |       | 4.1.1.  | Comparator                                     | 12 |  |  |  |  |

|          |       | 4.1.2.  | Flash Converter                                | 12 |  |  |  |  |

|          |       | 4.1.3.  | Successive Approximation Register ADC          | 14 |  |  |  |  |

|          |       | 4.1.4.  | Algorithmic ADC                                | 15 |  |  |  |  |

|          |       |         | 4.1.4.1. Cyclic ADC                            | 16 |  |  |  |  |

|          |       |         | 4.1.4.2. Pipelined ADC                         | 16 |  |  |  |  |

#### Contents

| 4.2.1. Sigma-Delta-Converter.       18         4.3. Time Interleaved ADCs.       18         4.4. Range of Operation       18         5. Pipelined ADC Design       19         5.1. Accuracy Requirements       19         5.2. Stage Scaling       22         5.3. Comparator Offset and Redundancy       22         5.4. 1.5-bit Differential Stage Realisations       25         5.5. Concepts for MDAC Realisation       25         5.5. Concepts for MDAC Realisation       27         5.5.3. C+C Charge Pump       27         5.5.3.1. Shortcommings       27         5.5.3.1. Charge Pump .       27         5.5.3.1. Shortcommings       27         6.1. Charge Pumps .       30         6.2. Capacitor Arithmetic       30         6.3. Resistor Approximation       31         6.4.1. Capacitors       32         6.4.2.1. Transmission Gate       32         6.5.2. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.3.2. Constant $V_{CS$                                   |    | 4.2.                        | Indirect ADCs                             | 17 |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------|-------------------------------------------|----|--|--|

| 4.3. Time Interleaved ADCs       18         4.4. Range of Operation       18         4.4. Range of Operation       18         5. Pipelined ADC Design       19         5.1. Accuracy Requirements       19         5.1.1. Stage Error       22         5.2. Stage Scaling       22         5.3. Comparator Offset and Redundancy       22         5.4. 1.5-bit Differential Stage Realisations       25         5.5. Concepts for MDAC Realisation       25         5.5. Concepts for MDAC Realisation       27         5.5.1. Charge Transfer Technique QT       27         5.5.2. Delta Charge Flow Technique $\delta Q$ 27         5.5.3. C+C Charge Pump       27         5.5.3. Sortchemmings       27         6. Switched Capacitor Basics       30         6.1. Charge Pumps       30         6.2. Capacitor Arithmetic       30         6.3. Resistor Approximation       31         6.4.1.1. Capacitor Parasitics       32         6.4.2. Switched       Capacitor Crutits in Pipelined ADC Design         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.3. Dummy Switch       38                                        |    |                             | 4.2.1. Sigma-Delta-Converter              | 18 |  |  |

| 5. Pipelined ADC Design       19         5.1. Accuracy Requirements       19         5.1.1. Stage Error       22         5.2. Stage Scaling       22         5.3. Comparator Offset and Redundancy       22         5.4. 1.5-bit Differential Stage Realisation       25         5.5. Concepts for MDAC Realisation       25         5.5. Concepts for MDAC Realisation       27         5.5.2. Delta Charge Flow Technique $\delta Q$ 27         5.5.3. C+C Charge Pump       27         5.5.3. Shortcommings       27         6. Switched Capacitor Basics       30         6.1. Charge Pumps       30         6.2. Capacitor Approximation       31         6.4. Components       31         6.4.1. Capacitors       32         6.4.2. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.3. Dummy Switch       38         11. Findings       39         7. Improvements for the C+C Charge Pump M                                     |    | 4.3.                        |                                           | 18 |  |  |

| 5. Pipelined ADC Design       19         5.1. Accuracy Requirements       19         5.1.1. Stage Error       22         5.2. Stage Scaling       22         5.3. Comparator Offset and Redundancy       22         5.4. 1.5-bit Differential Stage Realisation       25         5.5. Concepts for MDAC Realisation       25         5.5. Concepts for MDAC Realisation       27         5.5.2. Delta Charge Flow Technique $\delta Q$ 27         5.5.3. C+C Charge Pump       27         5.5.3. Shortcommings       27         6. Switched Capacitor Basics       30         6.1. Charge Pumps       30         6.2. Capacitor Approximation       31         6.4. Components       31         6.4.1. Capacitors       32         6.4.2. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.3. Dummy Switch       38         11. Findings       39         7. Improvements for the C+C Charge Pump M                                     |    | 4.4.                        | Range of Operation                        | 18 |  |  |

| 5.1. Accuracy Requirements       19         5.1. Stage Error       22         5.2. Stage Scaling       22         5.3. Comparator Offset and Redundancy       22         5.4. 1.5-bit Differential Stage Realisations       25         5.5. Concepts for MDAC Realisation       25         5.5. Concepts for MDAC Realisation       27         5.5.1. Charge Transfer Technique $QT$ 27         5.5.3. C+C Charge Pump       27         5.5.3. C-C Charge Pump       27         5.5.3. C-C Charge Pump       30         6.1. Charge Pumps       30         6.2. Capacitor Basics       30         6.1. Charge Pumps       30         6.2. Capacitor Arithmetic       30         6.3. Resistor Approximation       31         6.4.1. Capacitors       31         6.4.1. Capacitor Parasitics       32         6.4.2. Switches       32         6.5.3. Witched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3.3. Dummy Switch       38<                                                   |    |                             |                                           |    |  |  |

| 5.1.1. Štage Error       22         5.2. Stage Scaling       22         5.3. Comparator Offset and Redundancy       22         5.4. 1.5-bit Differential Stage Realisations       25         5.5. Concepts for MDAC Realisation       25         5.5.1. Charge Transfer Technique $QT$ 27         5.5.2. Delta Charge Flow Technique $\delta Q$ 27         5.5.3. C+C Charge Pump       27         5.5.3. C+C Charge Pump       27         5.5.3. C+C Charge Pump       30         6.1. Charge Pumps       30         6.2. Capacitor Basics       30         6.3. Resistor Approximation       31         6.4.1. Capacitors       31         6.4.2. Components       32         6.4.2. Switched Capacitor Parasitics       32         6.4.2. Switches       32         6.4.2. Switches       32         6.5.3. Settling Error       33         6.5.4.4.1. Transmission Gate       33         6.5.3. Sottling Error       33         6.5.4.2. Noise Considerations       33         6.5.3.3. Dottom Plate Sampling       38         6.5.3.4. Constant $V_{CS}$ Sampling       38         6.5.3.3. Dummy Switch       38         11. Fundings       39                                                                   | 5. | Pipe                        | elined ADC Design                         | 19 |  |  |

| 5.2. Stage Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 5.1.                        | Accuracy Requirements                     | 19 |  |  |

| 5.3. Comparator Offset and Redundancy       22         5.4. 1.5-bit Differential Stage Realisations       25         5.5. Concepts for MDAC Realisation       25         5.5.1. Charge Transfer Technique $QT$ 27         5.5.2. Delta Charge Flow Technique $\delta Q$ 27         5.5.3.1. Shortcommings       27         5.5.3.1. Shortcommings       27         5.5.3.1. Shortcommings       27         5.5.3.1. Shortcommings       27         6.1. Charge Pumps       30         6.2. Capacitor Basics       30         6.1. Charge Pumps       30         6.2. Capacitor Arithmetic       30         6.3. Resistor Approximation       31         6.4.1. Capacitors       31         6.4.1. Capacitor Parasitics       32         6.4.2. Switches       32         6.4.2.1. Transmission Gate       32         6.5.3. Settling Error       33         6.5.3. Charge Injection       34         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{CS}$ Sampling       38         6.5.3.3. Dummy Switch       38         6.5.3.3. Dummy Switch       38         6.5.3.3. Dummy Switch       38         6.5.3.3. Dummy Switch       38                                                          |    |                             | 5.1.1. Stage Error                        | 22 |  |  |

| 5.4.       1.5-bit Differential Stage Realisations       25         5.5.       Concepts for MDAC Realisation       25         5.5.1.       Charge Transfer Technique $QT$ 27         5.5.2.       Delta Charge Flow Technique $\delta Q$ 27         5.5.3.       C+C Charge Pump       27         5.5.3.       Shortcommings       27         5.5.3.       C+C Charge Pump       27         5.5.3.       Shortcommings       27         6.       Switched Capacitor Basics       30         6.1.       Charge Pumps       30         6.2.       Capacitor Arithmetic       30         6.3.       Resistor Approximation       31         6.4.       Components       31         6.4.1.       Capacitor Parasitics       32         6.4.2.       Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.4.2.       Noise Considerations       33         6.5.3.       Stitim Pipelined ADC Design       33         6.5.3.       Charge Injection       34         6.5.3.1.       Bottom Plate Sampling       38         6.5.3.2.       Constant $V_{CS}$ Sampling       38         6.5.3.3.       Dummy Switch       38 <th></th> <th>5.2.</th> <th>Stage Scaling</th> <th>22</th>                    |    | 5.2.                        | Stage Scaling                             | 22 |  |  |

| 5.4.       1.5-bit Differential Stage Realisations       25         5.5.       Concepts for MDAC Realisation       25         5.5.1.       Charge Transfer Technique $QT$ 27         5.5.2.       Delta Charge Flow Technique $\delta Q$ 27         5.5.3.       C+C Charge Pump       27         5.5.3.       Shortcommings       27         5.5.3.       C+C Charge Pump       27         5.5.3.       Shortcommings       27         6.       Switched Capacitor Basics       30         6.1.       Charge Pumps       30         6.2.       Capacitor Arithmetic       30         6.3.       Resistor Approximation       31         6.4.       Components       31         6.4.1.       Capacitor Parasitics       32         6.4.2.       Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.4.2.       Noise Considerations       33         6.5.3.       Stitim Pipelined ADC Design       33         6.5.3.       Charge Injection       34         6.5.3.1.       Bottom Plate Sampling       38         6.5.3.2.       Constant $V_{CS}$ Sampling       38         6.5.3.3.       Dummy Switch       38 <th></th> <th>5.3.</th> <th>Comparator Offset and Redundancy</th> <th>22</th> |    | 5.3.                        | Comparator Offset and Redundancy          | 22 |  |  |

| 5.5. Concepts for MDAC Realisation       25         5.5.1. Charge Transfer Technique $QT$ 27         5.5.2. Delta Charge Flow Technique $\delta Q$ 27         5.5.3. C+C Charge Pump       27         5.5.3. I. Shortcommings       27         6. Switched Capacitor Basics       30         6.1. Charge Pumps       30         6.2. Capacitor Arithmetic       30         6.3. Resistor Approximation       31         6.4. Components       31         6.4.1. Capacitors       31         6.4.1. Capacitor Parasitics       32         6.4.2. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3. Constant $V_{CS}$ Sampling       38         6.5.3. Dummy Switch       38         6.5.3.3. Dummy Switch       38         6.5.3.3. For Analysis       45         8.3. Error Analysis       45         8.3. Charge Injection       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45 <th></th> <th>5.4.</th> <th></th> <th>25</th>          |    | 5.4.                        |                                           | 25 |  |  |

| 5.5.1. Charge Transfer Technique $QT$ 27         5.5.2. Delta Charge Flow Technique $\delta Q$ 27         5.5.3. C+C Charge Pump       27         5.5.3. C+C Charge Pump       27         5.5.3.1. Shortcommings       27         6. Switched Capacitor Basics       30         6.1. Charge Pumps       30         6.2. Capacitor Arithmetic       30         6.3. Resistor Approximation       31         6.4. Components       31         6.4.1. Capacitor Parasitics       32         6.4.2. Switches       32         6.4.2.1. Transmission Gate       32         6.4.2.1. Transmission Gate       33         6.5.2. Noise Considerations       33         6.5.3. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.4. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38         6.5.3.3. Dummy Switch       38         6.5.3.3. Dummy Switch       42         8.1. Functional Description       42                                            |    | <u> </u>                    |                                           |    |  |  |

| 5.5.2. Delta Charge Flow Technique $\delta Q$ 27         5.5.3. C+C Charge Pump       27         5.5.3.1. Shortcommings       27         6. Switched Capacitor Basics       30         6.1. Charge Pumps       30         6.2. Capacitor Arithmetic       30         6.3. Resistor Approximation       31         6.4. Components       31         6.4.1. Capacitors       31         6.4.2. Switches       32         6.4.2. Switches       32         6.4.2.1. Transmission Gate       32         6.5.2. Noise Considerations       33         6.5.3. Settling Error       33         6.5.4.5. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38         6.5.3.3. Dummy Switch       38         6.5.3.3. Dummy Switch       34         8.1. Functional Description       42         8.1. Functional Description       42         8.3. Error Analysis       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection <th></th> <th>5</th> <th>*</th> <th>-</th>                                 |    | 5                           | *                                         | -  |  |  |

| 5:5.3. C+C Charge Pump       27         5:5.3.1. Shortcommings       27         6. Switched Capacitor Basics       30         6.1. Charge Pumps       30         6.2. Capacitor Arithmetic       30         6.3. Resistor Approximation       31         6.4. Components       31         6.4.1. Capacitors       31         6.4.2. Switches       32         6.4.2. Switches       32         6.4.2. Switches       32         6.4.2. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38 <b>11. Findings 39</b> 7. Improvements for the C+C Charge Pump MDAC       40         8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45                                                                                                              |    |                             |                                           | -  |  |  |

| 5.5.3.1.       Shortcommings       27         6.       Switched Capacitor Basics       30         6.1.       Charge Pumps       30         6.2.       Capacitor Arithmetic       30         6.3.       Resistor Approximation       31         6.4.       Components       31         6.4.1.       Capacitor Parasitics       32         6.4.1.1.       Capacitor Parasitics       32         6.4.2.       Switches       32         6.4.2.       Switches       32         6.4.2.       Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1.       Settling Error       33         6.5.2.       Noise Considerations       33         6.5.3.       Charge Injection       34         6.5.3.       Charge Injection       34         6.5.3.1.       Bottom Plate Sampling       37         6.5.3.2.       Constant $V_{GS}$ Sampling       38         6.5.3.3.       Dummy Switch       38         11.       Findings       39         7.       Improvements for the C+C Charge Pump MDAC       40         8.       Differential Gain MDAC       42         8       Functional Description                                                                                                      |    |                             |                                           | -  |  |  |

| 6. Switched Capacitor Basics       30         6.1. Charge Pumps       30         6.2. Capacitor Arithmetic       30         6.3. Resistor Approximation       31         6.4. Components       31         6.4. Components       31         6.4. Components       31         6.4. Components       31         6.4.1. Capacitors       32         6.4.1. Capacitor Parasitics       32         6.4.2. Switches       32         6.4.2. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38         11. Findings       39         7. Improvements for the C+C Charge Pump MDAC       40         8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45                                                                                                                                      |    |                             |                                           | -  |  |  |

| 6.1. Charge Pumps       30         6.2. Capacitor Arithmetic       30         6.3. Resistor Approximation       31         6.4. Components       31         6.4. Components       31         6.4.1. Capacitors       31         6.4.2. Switches       32         6.4.2. Switches       32         6.4.2. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38 <b>11. Findings 39 7. Improvements for the C+C Charge Pump MDAC 40 8. Differential Gain MDAC</b> 42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                |    |                             | 5.5.3.1. Shoreoninings                    | 27 |  |  |

| 6.1. Charge Pumps       30         6.2. Capacitor Arithmetic       30         6.3. Resistor Approximation       31         6.4. Components       31         6.4. Components       31         6.4.1. Capacitors       31         6.4.2. Switches       32         6.4.2. Switches       32         6.4.2. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38 <b>11. Findings 39 7. Improvements for the C+C Charge Pump MDAC 40 8. Differential Gain MDAC</b> 42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                | 6. | Swit                        | ched Capacitor Basics                     | 30 |  |  |

| 6.2. Capacitor Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |                             |                                           | 30 |  |  |

| 6.3. Resistor Approximation       31         6.4. Components       31         6.4.1. Capacitors       31         6.4.1.1. Capacitor Parasitics       32         6.4.1.1. Capacitor Parasitics       32         6.4.2.1. Transmission Gate       32         6.4.2.1. Transmission Gate       32         6.5. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38         11. Findings       39         7. Improvements for the C+C Charge Pump MDAC       40         8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                            |    |                             |                                           | -  |  |  |

| 6.4. Components       31         6.4.1. Capacitors       31         6.4.1.1. Capacitor Parasitics       32         6.4.2. Switches       32         6.4.2.1. Transmission Gate       32         6.4.2.1. Transmission Gate       32         6.4.2.1. Transmission Gate       32         6.4.2.1. Transmission Gate       32         6.5. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38         11. Findings       39         7. Improvements for the C+C Charge Pump MDAC       40         8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                      |    |                             |                                           | -  |  |  |

| 6.4.1. Capacitors       31         6.4.1.1. Capacitor Parasitics       32         6.4.2. Switches       32         6.4.2.1. Transmission Gate       32         6.4.2.1. Transmission Gate       32         6.5. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38 <b>11. Findings 39 7. Improvements for the C+C Charge Pump MDAC</b> 40 <b>8. Differential Gain MDAC</b> 42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                           |    |                             |                                           | 0  |  |  |

| 6.4.1.1.       Capacitor Parasitics       32         6.4.2.       Switches       32         6.4.2.       Switches       32         6.4.2.1.       Transmission Gate       32         6.5.2.       Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1.       Settling Error       33         6.5.2.       Noise Considerations       33         6.5.3.       Charge Injection       34         6.5.3.1.       Bottom Plate Sampling       37         6.5.3.2.       Constant $V_{GS}$ Sampling       38         6.5.3.3.       Dummy Switch       38         11.       Findings       39         7.       Improvements for the C+C Charge Pump MDAC       40         8.       Differential Gain MDAC       42         8.1.       Functional Description       42         8.2.       Advantages       45         8.3.1.       Charge Injection       45         8.3.1.       Charge Injection       45                                                                                                                                                                                                                                                                                           |    | 0.4.                        |                                           | 0  |  |  |

| 6.4.2. Switches       32         6.4.2.1. Transmission Gate       32         6.5.2. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38         7. Improvements for the C+C Charge Pump MDAC       40         8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |                             | · A                                       | 0  |  |  |

| 6.4.2.1.       Transmission Gate       32         6.5.       Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1.       Settling Error       33         6.5.2.       Noise Considerations       33         6.5.3.       Charge Injection       34         6.5.3.1.       Bottom Plate Sampling       37         6.5.3.2.       Constant $V_{GS}$ Sampling       38         6.5.3.3.       Dummy Switch       38         6.5.3.3.       Dummy Switch       38         7.       Improvements for the C+C Charge Pump MDAC       40         8.       Differential Gain MDAC       42         8.1.       Functional Description       42         8.2.       Advantages       45         8.3.1.       Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                             |                                           | 0  |  |  |

| 6.5. Switched Capacitor Circuits in Pipelined ADC Design       33         6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3. Charge Injection       34         6.5.3. Charge Injection       37         6.5.3. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38         6.5.3.3. Dummy Switch       38         7. Improvements for the C+C Charge Pump MDAC       40         8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |                             |                                           | -  |  |  |

| 6.5.1. Settling Error       33         6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38 <b>II. Findings 39 7. Improvements for the C+C Charge Pump MDAC</b> 40 <b>8. Differential Gain MDAC</b> 42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | <u> </u>                    |                                           |    |  |  |

| 6.5.2. Noise Considerations       33         6.5.3. Charge Injection       34         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38 <b>II. Findings 39 7. Improvements for the C+C Charge Pump MDAC</b> 40 <b>8. Differential Gain MDAC</b> 42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45         8.3.1. Differential Distribution       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 6.5.                        |                                           |    |  |  |

| 6.5.3. Charge Injection       34         6.5.3.1. Bottom Plate Sampling       37         6.5.3.2. Constant $V_{GS}$ Sampling       38         6.5.3.3. Dummy Switch       38 <b>II. Findings</b> 39 <b>7. Improvements for the C+C Charge Pump MDAC</b> 40 <b>8. Differential Gain MDAC</b> 42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |                             |                                           |    |  |  |

| 6.5.3.1.       Bottom Plate Sampling       37         6.5.3.2.       Constant $V_{GS}$ Sampling       38         6.5.3.3.       Dummy Switch       38 <b>II. Findings 39 7. Improvements for the C+C Charge Pump MDAC 40 8. Differential Gain MDAC 42</b> 8.1.       Functional Description       42         8.2.       Advantages       45         8.3.       Error Analysis       45         8.3.1.       Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |                             |                                           |    |  |  |

| 6.5.3.2.       Constant V <sub>GS</sub> Sampling       38         6.5.3.3.       Dummy Switch       38         II. Findings       39         7.       Improvements for the C+C Charge Pump MDAC       40         8.       Differential Gain MDAC       42         8.1.       Functional Description       42         8.2.       Advantages       45         8.3.       Error Analysis       45         8.3.1.       Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |                             |                                           |    |  |  |

| 6.5.3.3. Dummy Switch       38         II. Findings       39         7. Improvements for the C+C Charge Pump MDAC       40         8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                             |                                           |    |  |  |

| II. Findings       39         7. Improvements for the C+C Charge Pump MDAC       40         8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |                             |                                           | 38 |  |  |

| 7. Improvements for the C+C Charge Pump MDAC       40         8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |                             | 6.5.3.3. Dummy Switch                     | 38 |  |  |

| 7. Improvements for the C+C Charge Pump MDAC       40         8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |                             |                                           |    |  |  |

| 7. Improvements for the C+C Charge Pump MDAC       40         8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | с:,                         | adings                                    | 20 |  |  |

| 8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | FII                         | luligs                                    | 29 |  |  |

| 8. Differential Gain MDAC       42         8.1. Functional Description       42         8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7. | Imp                         | rovements for the C+C Charge Pump MDAC    | 40 |  |  |

| 8.1. Functional Description428.2. Advantages458.3. Error Analysis458.3.1. Charge Injection45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |                             |                                           |    |  |  |

| 8.2. Advantages       45         8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8. | Diff                        | erential Gain MDAC                        | 42 |  |  |

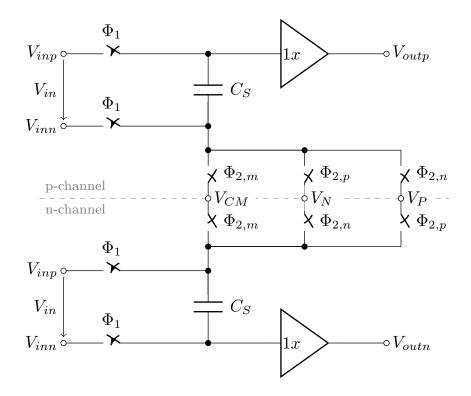

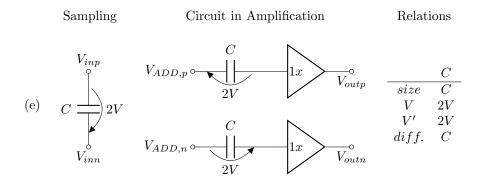

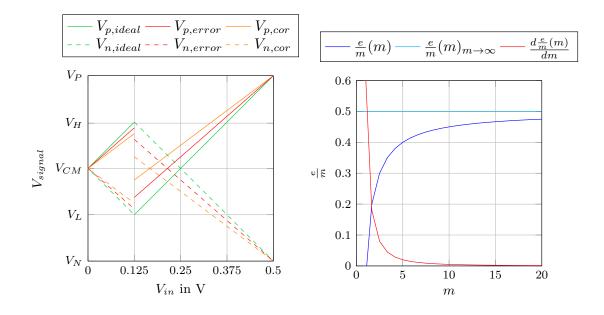

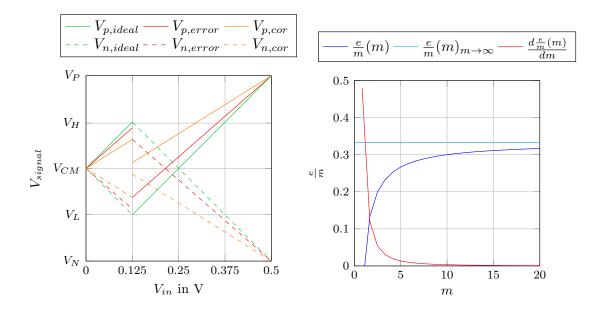

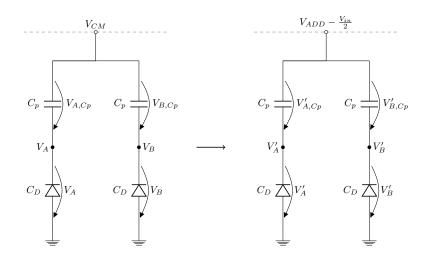

| 8.3. Error Analysis       45         8.3.1. Charge Injection       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 8.1. Functional Description |                                           |    |  |  |

| 8.3.1. Charge Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 8.2.                        | Advantages                                | 45 |  |  |

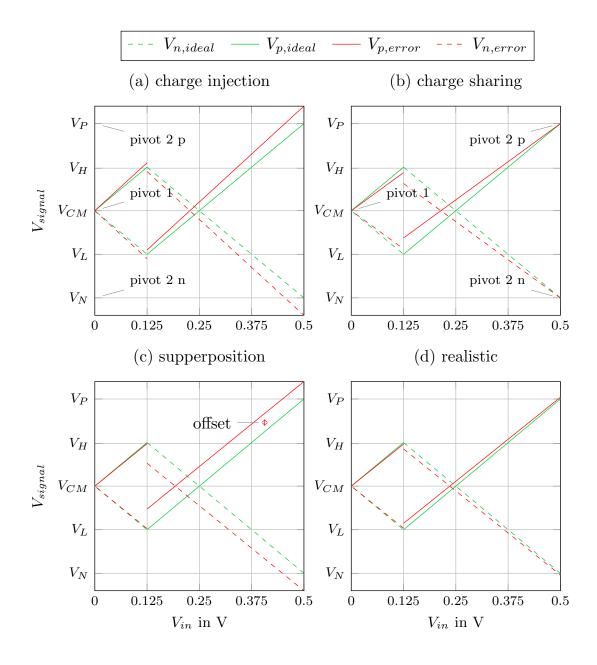

| 8.3.1. Charge Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 8.3.                        | Error Analysis                            | 45 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                             | 8.3.1. Charge Injection                   |    |  |  |

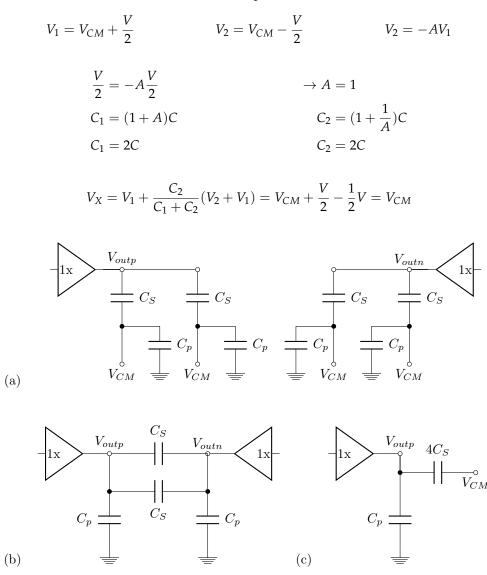

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                             | 8.3.2. Voltage Divider at the Output Node | 47 |  |  |

#### Contents

|     | 8.3.3. Capacitor Mismatch                                        | 47 |

|-----|------------------------------------------------------------------|----|

|     | 8.3.4. Current Mismatch between Channels                         | 48 |

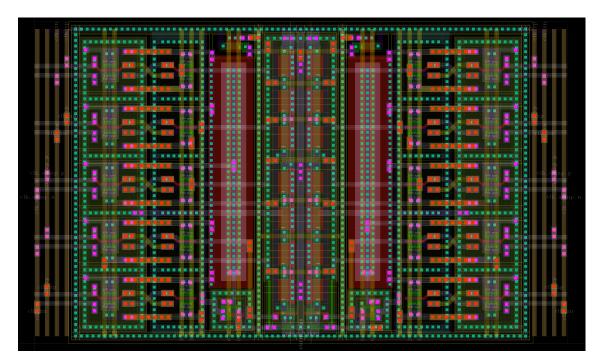

|     | 8.4. Dimensioning and Design                                     | 48 |

|     | 8.4.1. Capacitor and Switch Sizes                                |    |

|     | 8.4.2. Stage Scaling - Unity Gain Cell                           |    |

|     | 8.4.3. Buffer Design                                             | -  |

|     | 8.5. Conclusion                                                  |    |

| 9.  | Error Compensations                                              | 52 |

|     | 9.1. Analog Error Correction                                     | 52 |

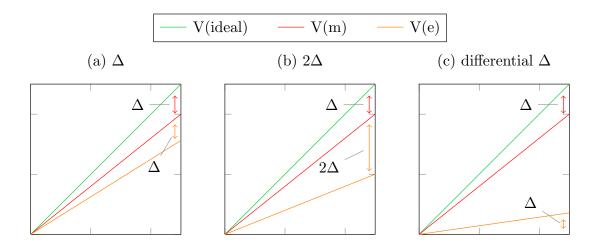

|     | 9.1.0.1. $\Delta$ Emending Path                                  | 53 |

|     | 9.1.0.2. $2\Delta$ Emending Path                                 | 54 |

|     | 9.1.0.3. Differential $\Delta$                                   | 55 |

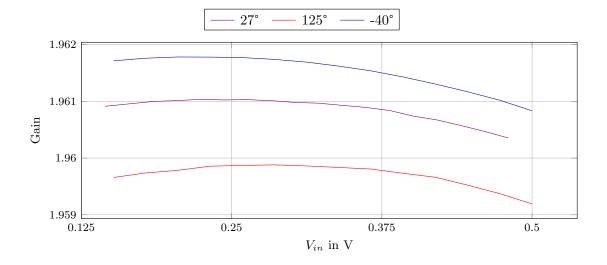

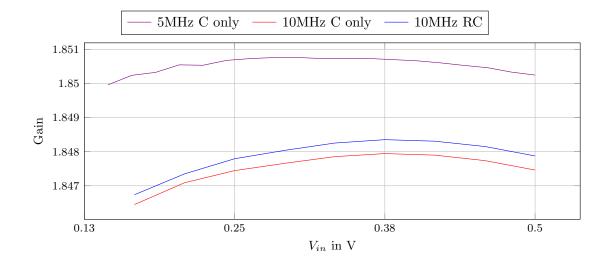

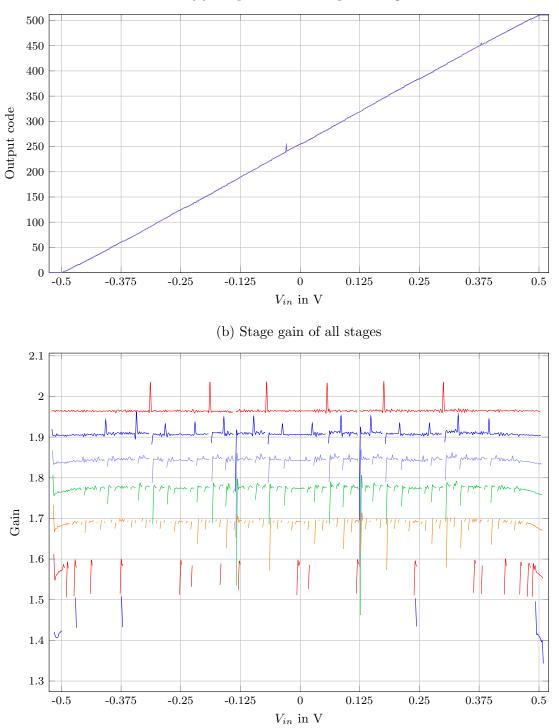

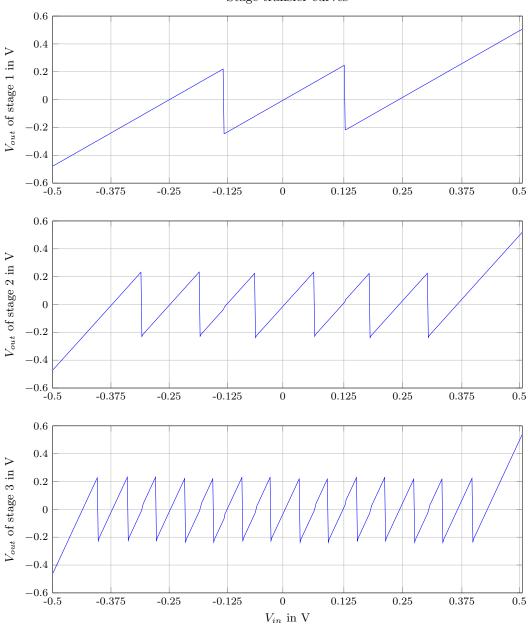

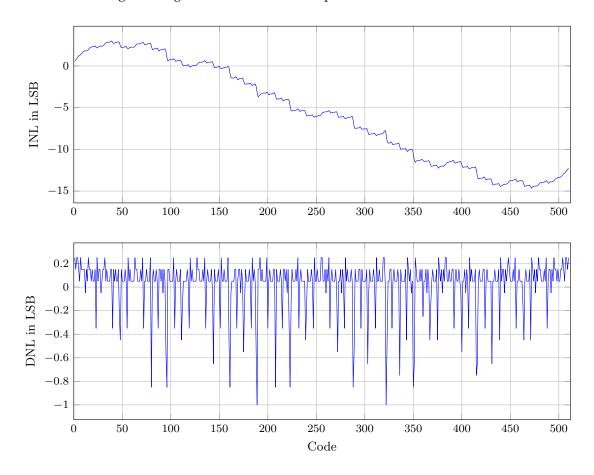

| 10  | Results                                                          | 57 |

|     | 10.1. Comparison between Different Gain Stages                   | 57 |

|     | 10.1.1. Gain as a Function of Load Capacitance                   | 58 |

|     | 10.2. Unity Gain Cell                                            | 61 |

|     | 10.3. ADC Performance                                            | 63 |

|     | 10.3.1. INL and DNL                                              | 66 |

|     | 10.4. Related Work - Performance Summary                         | 66 |

| 11  | Conclusion                                                       | 68 |

|     | 11.1. Future Work                                                | 68 |

| Α.  | Mathematical Derivations                                         | 70 |

|     | A.1. Setting the Potential of the Bottom Plate Capacitance       | -  |

|     | A.2. The Impact of Capacitor Sizes on a Capacitive Voltage Adder | -  |

|     | A.3. Effective Capacitance                                       |    |

|     | A.3.1. Calculating the Error Using the Charges                   |    |

|     | A.3.2. Calculating the Equivalent Capacitance Value              |    |

|     | A.4. Emending Proportionality Factor                             | 74 |

| Bil | liography                                                        | 76 |

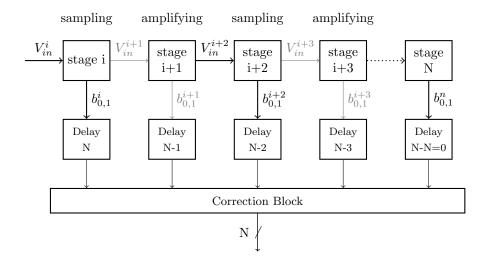

# 1. Introduction

A main goal in the design of consumer products has always been to improve their performance in regards of their primary function and purpose. Yet taking a look at recent developments the challenge is more and more to provide devices able to act in a clever way on their own.

A good example for this clever way of operation are digital cameras equipped with rotary sensors. They are able to save the rotation with which a picture has been taken. This functionality has nothing to do with the basic function of taking high resolution pictures. However, it is convenient for the user when pictures are already rotated correctly when loaded to a PC. Other examples are noise cancellation in head-phones or alert and assistance systems in cars. Robotics and autonomous driving, which are in the focus of research at the moment, carry this idea to the extreme, where devices are meant to operate and take complex decisions with minimal input from the user.

What all these use cases have in common is that devices adjust their behaviour to the circumstances. In order to be responsive to the environment you have to be able to sense it. Since signal processing is almost always done in the digital domain each sensor requires an analog-to-digital converter (ADC). According to this trend the number of ADCs per device can be expected to grow.

The desire to transform analog signals into the digital domain arises from the computational power available there. It turned out that digital signal processing can be done much cheaper than its analog counterpart. As the performance development of ADCs is lacking behind the one of digital circuitry [33] there is need to work on ADC concepts to prevent it of becoming the bottleneck of system performance.

For mobile devices like phones, tablets and smart-watches, but also mobile robots power consumption is essential [18]. However, it also turns out to be an issue for devices where basically enough power is at hand [11]. The reason are packaging costs which diminish when power dissipation and the heating accompanied with it, can be reduced [4]. This explains why power dissipation is a crucial factor in ADC design.

1. Introduction

# 1.1. Structure

The motivation and underlying problem of this thesis is discussed in chapter 2.

Then the first part gives an overview on the fundamentals of the field. The 3<sup>rd</sup> chapter addresses the used terminology and characteristics of ADC converters and further introduces the non-idealities of an actual ADC. The 4<sup>th</sup> chapter gives an overview over the basic principles of analog-to-digital conversion and explains the concepts on a common-sense level. Chapter 5 focuses on the pipelined ADC topology, pointing out state of the art approaches and known pitfalls for the design. In chapter 6 some basics design guidelines for switched capacitor circuits are presented.

In the second part new ideas and concepts are discussed. Chapter 7 presents a way to improve the function of the prior art discussed in chapter 5.5.3. A new topology to implement the desired function is introduced in chapter 8. The 9<sup>th</sup> chapter introduces some ideas for further improvement on a theoretical level. All simulation results comparing and discussing performance are collected in chapter 10. Finally, a conclusion and outlook can be found in chapter 11 where the results of this work are discussed and summarized.

Mathematical derivations for statements made throughout the other chapters are carried out in detail in the appendix A to keep the comprehensibility.

# 2. Motivation

Pipelined ADCs took over to dominate the area of moderate resolution and conversion speed [25]. Yet they face the problem of high power consumption due to the large number of operational amplifiers (OP-amps).

Different attempts were made to minimize total power consumption of the OP-amps which are part of each stage. There is potential to save power by switching off the OP-amp during idle times. However, since they show long start up times this measure is not suitable for higher frequencies [9]. Likewise, one OP-amp could be used for two stages. Additional switches, long transmission lines and missing resetting are drawbacks of this approach. Another concept tries to reduce the number of stages and with it the number of OP-amps by using multi-bit stages. This shifts the problem to the complexity of the sub-ADC and the sub-digital-to-analog converter (DAC).

Since the main contributor of power consumption is the OP-amp, the simplest solution would be to avoid them at all. This was done by Ahmed in [2] where a charge pump is used to create the gain and a simple source follower to forward the signal. The proposed architecture used digital calibration to overcome circuit imperfections.

The question of this thesis was whether this idea of passive gain creation could be adapted for the use in an existing design, which exactly suffered from too high power consumption. The goal was to find ways to improve the given topology to hopefully make it work without digital calibration. This should lead to a simpler and more efficient design.

### 2.1. Area and Power Consumption

For system design and production costs the area occupied by a certain topology is a crucial factor. On the one hand costs per chip shrink if more chips can be placed on one wafer. In addition, the size of the chip increases the risk of defects and further may reduce the yield which lowers the profit [12, p.155]. Above all the aim is therefore a small design.

While area has mainly negative effects on the chip manufacturer, power consumption has an even wider impact. Packaging costs can be reduced for low power consumption because of less thermal requirements [4]. Additionally, power consumption has an influence on performance even during operation. Finding the right topology for the given requirements is therefore a tricky task considering the great variety of existing designs in today's literature.

# Part I.

# **Fundamentals**

An analog signal is continuous in time and can reach an infinite amount of possible values. To represent such a signal in a digital system, which has finite possible states and is working at a certain clock rate, it has to be limited by its values in time and amplitude. Otherwise the digital side could never keep track with the real world neither have a chance to represent it. The block performing this task is called analog-to-digital converter (ADC).

Digitalisation in the time domain means that the input is only observed at certain time steps. This process is referred to as sampling. Values between the sampling steps are simply neglected. According to the sampling theorem [30] the original signal can be reconstructed when the sampling frequency is more than twice of the highest signal frequency.

In case that an ADC needs more than one clock cycle to finish the conversion a sample-and-hold (S&H) block is needed. This block samples the input and charges a capacitor to store the value so that it can be provided as constant throughout the conversion process.

To reach a finite amount of states we specify the full scale range (FSR) between the lowest  $V_N$  and highest  $V_P$  allowed input. The process of digitalisation can than be described as mapping this range to a number of codes (n) with the length of N bits. With more bits the number of possible codes rises and the mapping becomes finer and finer. Therefore, the number of bits is indicating the resolution of an ADC.

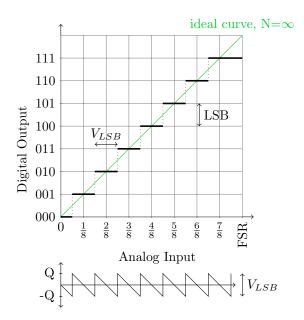

The mapping process is also apparent in the transfer curve which is shown in Figure 3.2 (a) for an ideal 3 bit ADC. The quantisation step ( $V_{LSB}$ ) as defined in Equation 3.3, is describing the size of one step on the analog side. All voltages within that step will be represented by the same code. For higher resolution the steps become smaller and the stair case function is converging towards a straight line. This ideal conversion curve is marked in green in the diagrams. The difference between this ideal curve to the transfer curve of an ideal 3 bit ADC is called quantisation error (Q). It can be interpreted as an information loss and its characteristic is shown below the transfer curve. The mathematical relations between the discussed parameters are given in Equation 3.1 to 3.4.

$$FSR = V_P - V_N \tag{3.1}$$

$$n = 2^N \tag{3.2}$$

$$V_{LSB} = \frac{FSR}{n} = \frac{FSR}{2^N}$$

(3.3)

$$|Q_{max}| = \frac{V_{LSB}}{2} = \frac{FSR}{2^{N+1}}$$

(3.4)

Figure 3.1.: Transfer curve of an ideal 3 bit ADC with resulting quantization error.

## 3.1. Ideal Characteristics

Accordingly, an ideal ADC is fully specified by the following parameters:

- **FSR** Or  $V_P$  and  $V_N$  respectively, defines the input range the ADC is able to process.

- **N** the Stated Number of Bits, hence the number of bits of a generated output code. Together with the FSR it determines the resolution.

- $\mathbf{f}_{samp}$  the sampling frequency, directly implies that the time for conversion is given as  $\frac{1}{f_{samp}}$ . Further, it limits the frequency of the input for which the converter can be used as a Nyquist converter to avoid aliasing to  $\frac{f_{samp}}{2}$ .

# 3.2. Error Measures of Actual ADCs

The width and location of the steps on the analog side can differ from the ideal curve because of errors in the conversion process in an actual ADC. For the characterisation of actual ADCs certain errors have been defined [28].

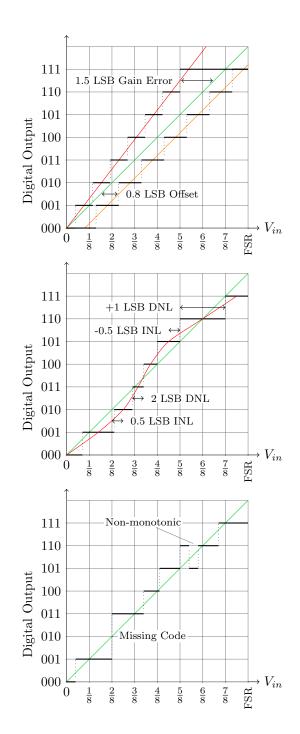

## 3.2.1. Static Errors

Static errors occur even for a constant input signal which has to be digitised. They are caused by non-ideal circuit behaviour due to component mismatch, temperature dependences or process variation. As a first requirement the input must not change more than  $\frac{1}{2}V_{LSB}$  during the time of the conversion. Otherwise at the moment when the result is present at the output it will not correspond to the ADCs current input. The now discussed errors are all marked in Figure 3.2 for a better understanding.

Figure 3.2.: Ideal and non-ideal ADC transfer curves showing the influence of different errors.

#### 3.2.1.1. Offset Error

The offset error describes the difference of the origin of the transfer curve from the ideal value of  $\frac{1}{2}V_{LSB}$ . Accordingly, the whole curve is shifted parallel which allows to correct this error externally simply by adding or subtracting the known offset from the digital values.

#### 3.2.1.2. Gain Error

A gain error is present if the slope of the transfer curve deviates form its ideal value. For an unipolar ADC it is measured as the distance between ideal and actual position of the last transition and usually given in parts of least significant bit (LSB) or percent of the FSR. For a bipolar ADC a negative and a positive gain error is equivalently given as the distance from the first and the last jump to their ideal positions. As this error is affecting all values in the same amount it can be eliminated afterwards by multiplying the digital values with the right correction factor.

#### 3.2.1.3. Integral Non Linearity - INL

An integral non-linearity (INL) error is present when the midpoint of the steps of the transfer curve are not placed on a straight line. Therefore this error is often referred to as *Linearity error*. It can not be corrected in the digitised values.

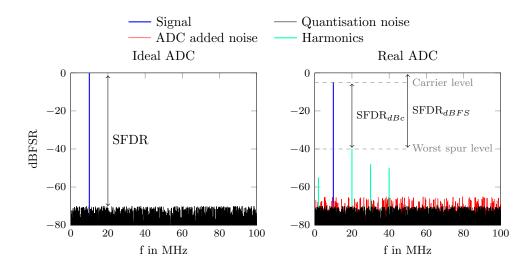

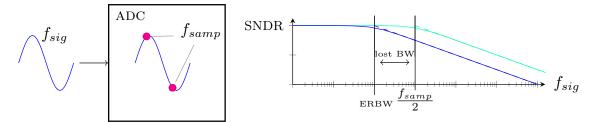

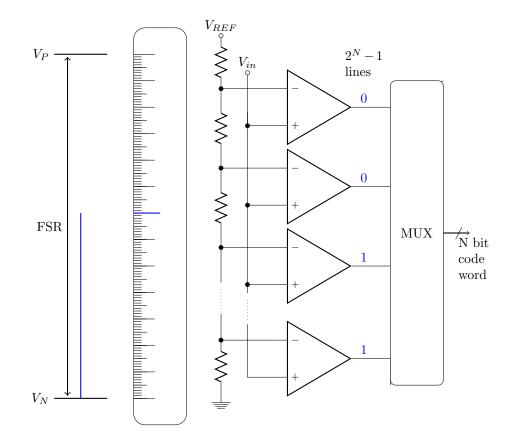

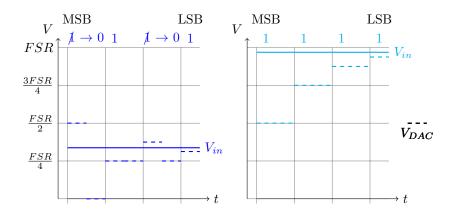

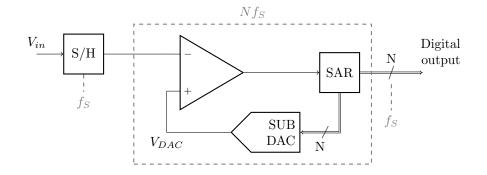

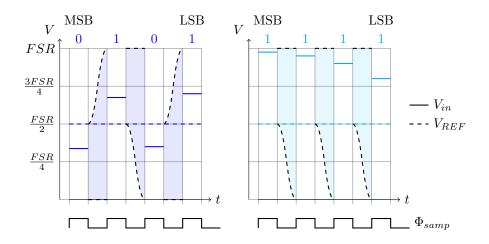

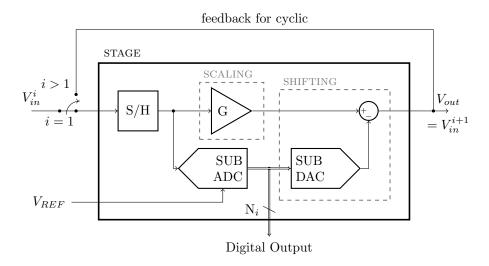

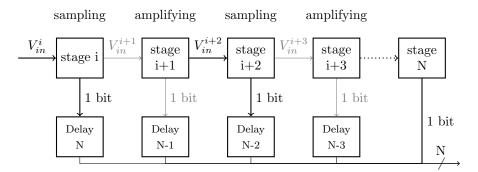

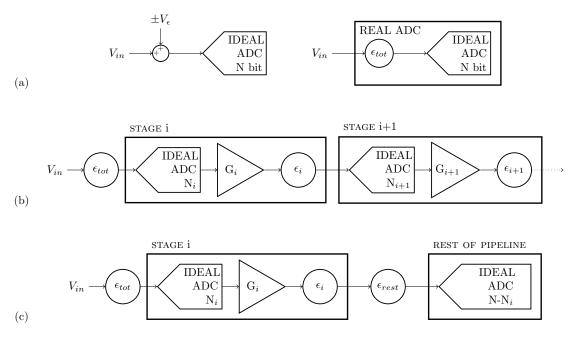

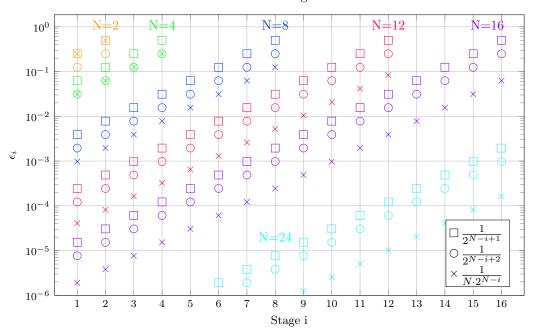

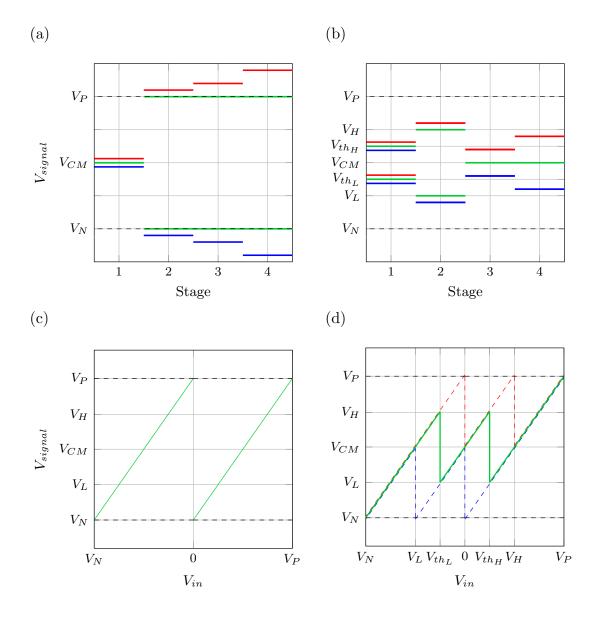

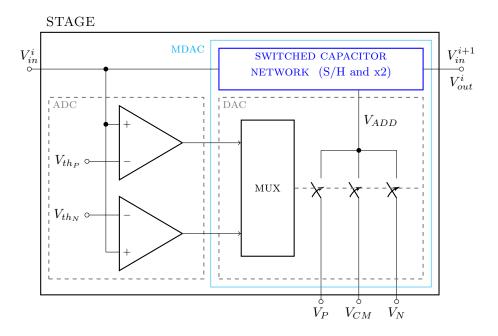

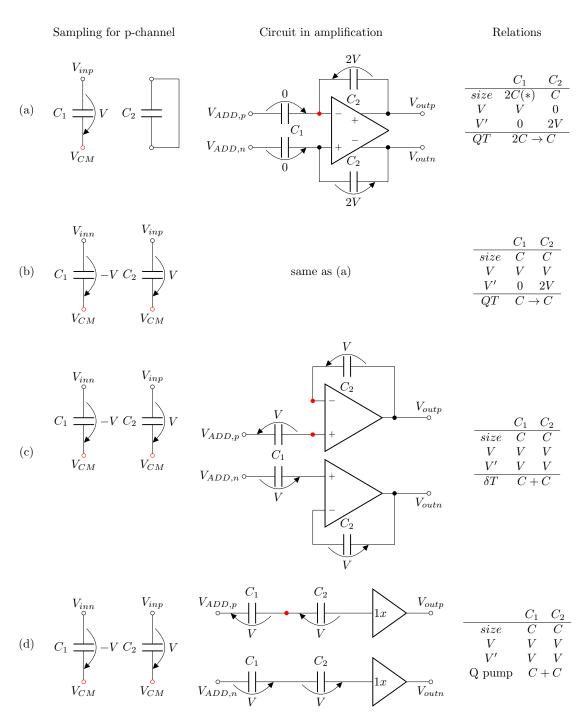

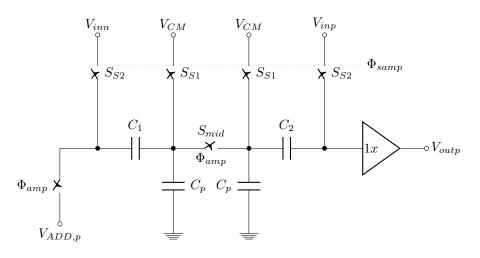

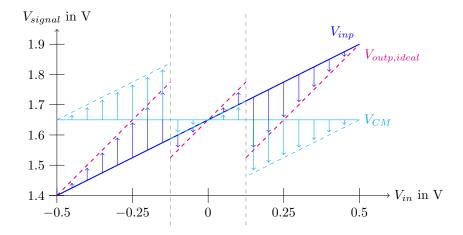

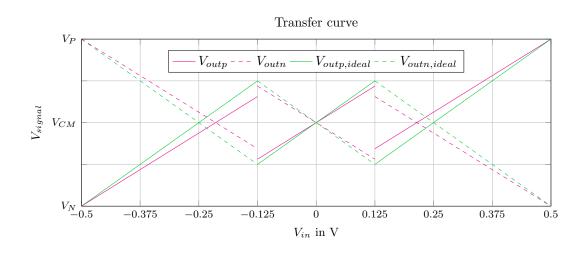

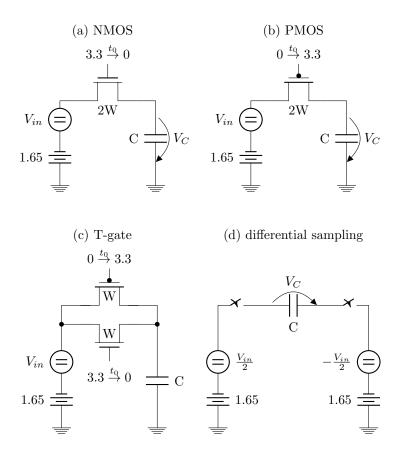

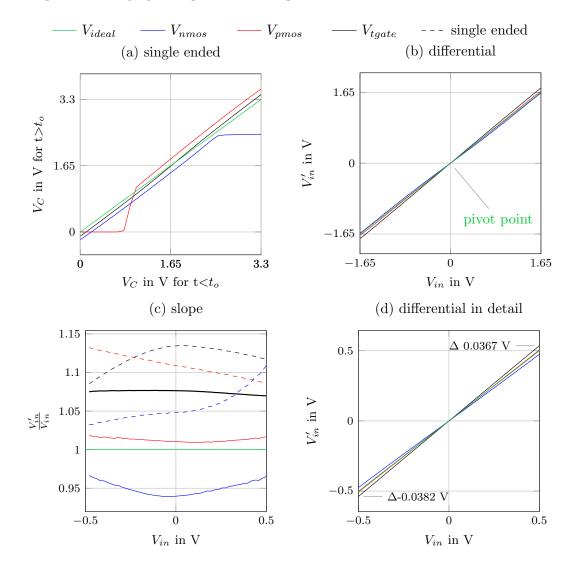

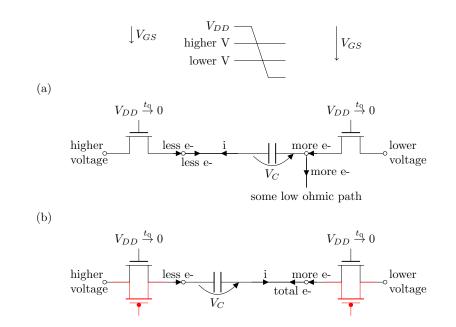

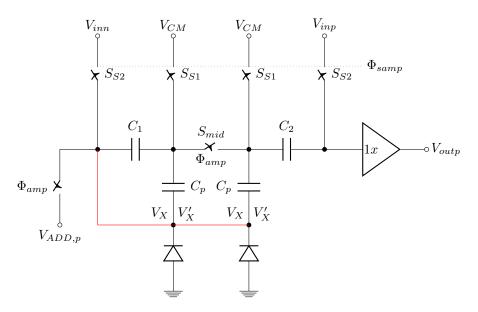

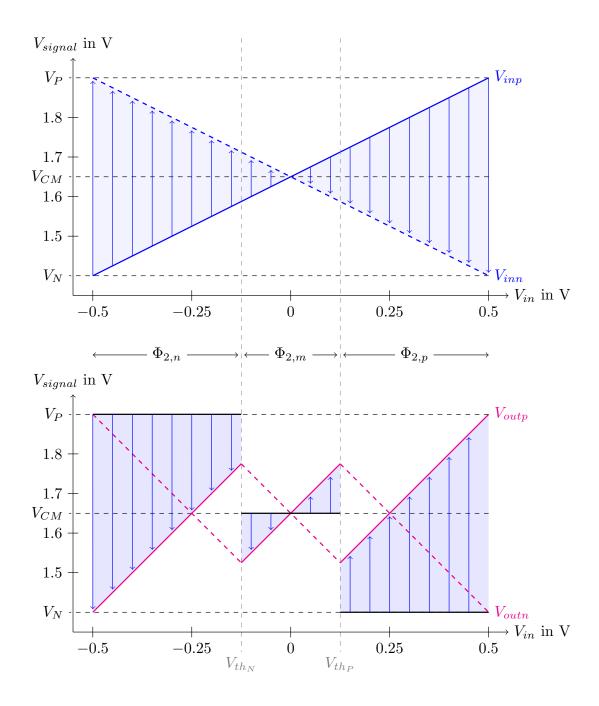

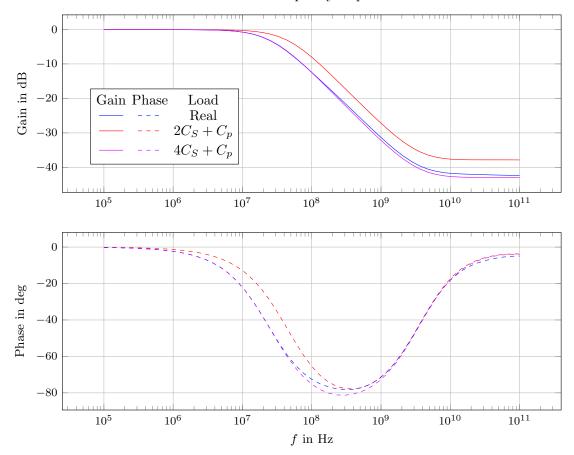

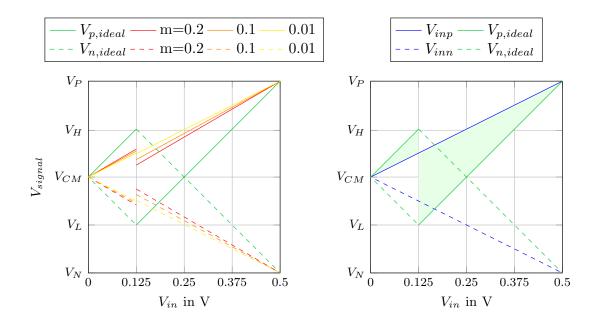

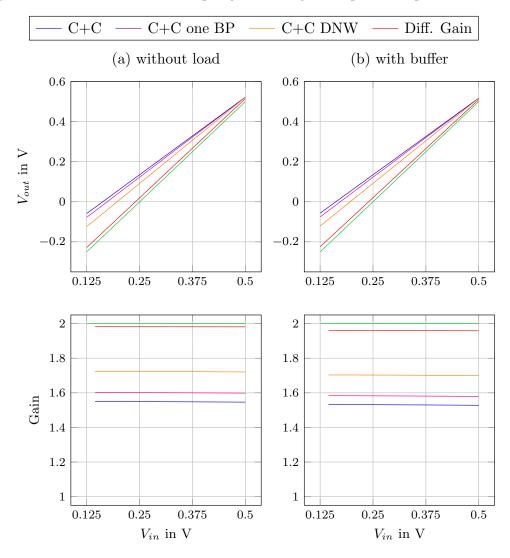

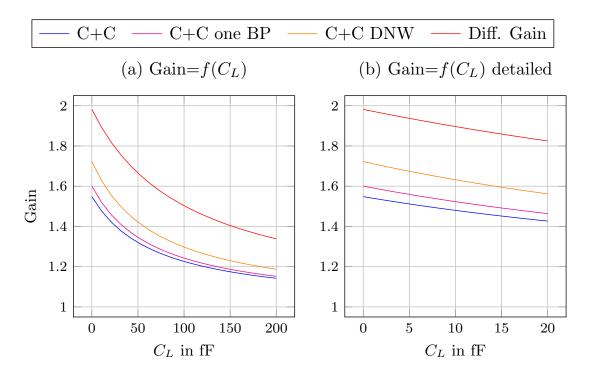

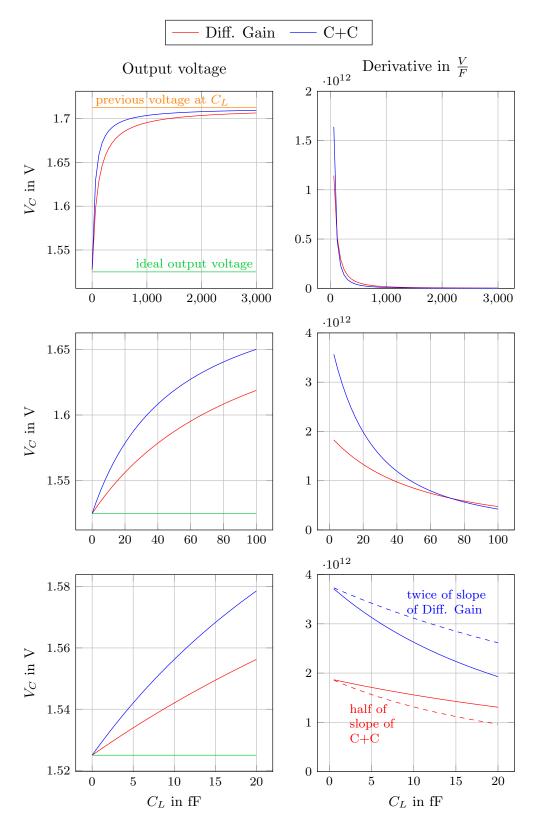

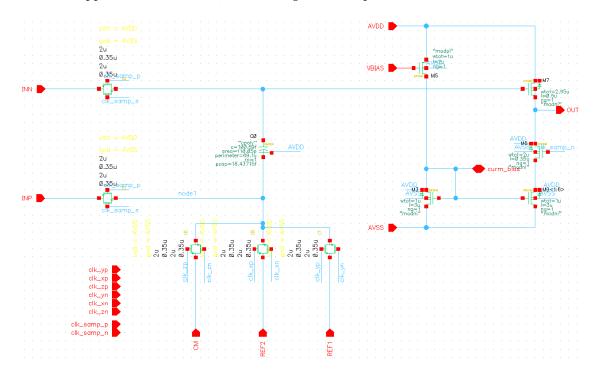

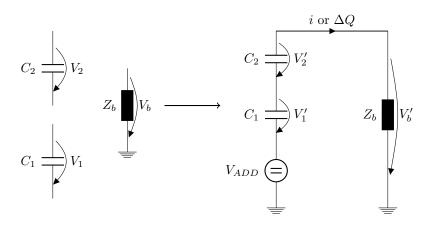

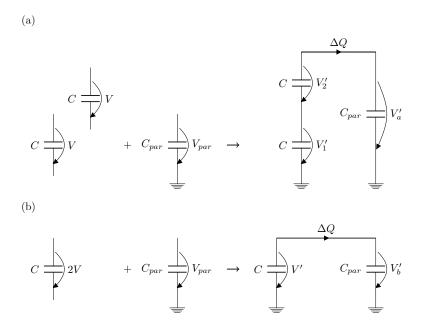

#### 3.2.1.4. Differential Non Linearity - DNL