Linear Temporal Logic - in Theory and Industry

by

Karin Greimel

A PhD Thesis Presented to the Faculty of Computer Science in Partial Fulfillment of the Requirements for the PhD Degree

Assessors

Prof. Roderick Bloem (Graz University of Technology, Austria) Prof. Werner Damm (Universität Oldenburg, Germany)

June 2016

Institute for Applied Information Processing and Communications (IAIK) Faculty of Computer Science Graz University of Technology, Austria

## Abstract

Linear Temporal Logic specifications can be used for synthesis and formal verification of reactive systems.

For Linear Temporal Logic synthesis a Linear Temporal Logic specification is given as input and the output is a reactive system satisfying the specification. The specifications we consider are guarantees that need to be satisfied by the system if the inputs to the system satisfy a set of assumptions. In classic Linear Temporal Logic synthesis the system is allowed to behave arbitrarily if the assumptions are not satisfied. We argue that the system should be robust, it should try to satisfy the guarantees as well as possible even if the assumptions are not satisfied. We define two different notions of robustness, one for safety and one for liveness properties. In both cases a system is robust if a small number of violations of the assumptions lead to a small number of violations of the guarantees. For both, safety and liveness, we show how to verify and synthesize robust systems. Our work on synthesis of robust systems leads to new game theoretic results. For the synthesis of robust systems from safety specifications we define and solve ratio games. For the synthesis of robust systems from liveness specifications we develop a faster algorithm to solve Generalized Reactivity games.

For formal verification a Linear Temporal Logic specification and a reactive system are given as input and the output is a proof showing that the system satisfies the specification. We show how to use model checking, a formal verification technique, to verify specifications of smart cards. The proposed approach satisfies the Common Criteria Certification requirements for high Evaluation Assurance Levels. Common Criteria is a security certification scheme widely used in the smart card industry. Especially for e-government and banking products such as electronic passports, credit/debit cards, etc., high assurance of the security is of great importance. We give two case studies of security policy models using model checking. For the first case study we model a security IC. The model enabled the first Evaluation Assurance Level 6 certification within the German certification scheme. For the second case study we model the Java Card applet firewall. The model uncovered contradictions in the security requirements that have been overlooked for several years. We propose to integrate the formal verification method into the product design process by using UML statecharts as input to the model checker. UML is commonly known by engineers and thus allows a project to maximize the benefits of formal methods in the product design process.

## Acknowledgements

I would like to thank my supervisor Roderick Bloem for introducing me to the field of formal methods, particularly for introducing me to the research community. I learned a lot about logic, automata, game theory and related topics but also how to conduct and present research. I am looking forward to learning a lot more and fruitful cooperation in the future.

I am grateful for all the fun and instructive times with my colleagues at the university. Special thanks go to Barbara Jobstmann, who has been a role model for me since I started working on my diploma thesis and who made me feel very welcome during my stay in Lausanne where we started working on synthesizing robust systems. I very much enjoyed working together. I would also like to thank Krishnendu Chatterjee for his contribution to the game theoretic part of synthesizing robust systems for liveness specifications. My thanks also go to all the colleagues at the institute, but mostly to Georg Hofferek and Robert Könighofer who are forthcoming and helpful and always open for discussions.

I would not have been able to finish my thesis without the support from people at NXP, thanks to Martin Schaffer, Christoph Herbst, Ernst Haselsteiner, Johannes Loinig, Hans-Gerd Albertsen and many others. I am also indebted to people outside NXP. Gerd Beuster initiated our work on security policy modeling and provided a first model. I got great technical support from Fraunhofer on COSIDE, especially from Norman Seßler. My thanks also go to Franz Röck for a first version of the Java Card OS firewall model. I hope for many more years of working together.

The work of my thesis was funded by Graz University of Technology, NXP Semiconductors, the European Commission with the projects COCONUT (FP7-2007-IST-1-217069) and DIAMOND (FP7-2009-IST-4-248613), and the Austrian Research Promotion Agency (FFG) with the project NewP@ss.

Last but not least I would like to thank my family for being there for me at all times; most important Wolfgang Aigner.

Big thanks to all who encouraged and supported me,

Karin Greimel Graz, June 2016

# Table of Contents

| Abstract                                             |                                 |                                                                                                                 |                                                                                                                                                                                                                                                          |                                                                                                                                                                        |  |  |  |  |   |                    |                    |  |            |

|------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|---|--------------------|--------------------|--|------------|

| Acknowledgements                                     |                                 |                                                                                                                 |                                                                                                                                                                                                                                                          |                                                                                                                                                                        |  |  |  |  |   |                    |                    |  |            |

| List of Tables i<br>List of Figures :<br>Glossary xi |                                 |                                                                                                                 |                                                                                                                                                                                                                                                          |                                                                                                                                                                        |  |  |  |  |   |                    |                    |  |            |

|                                                      |                                 |                                                                                                                 |                                                                                                                                                                                                                                                          |                                                                                                                                                                        |  |  |  |  | A | crony              | $\mathbf{ms}$      |  | xv         |

|                                                      |                                 |                                                                                                                 |                                                                                                                                                                                                                                                          |                                                                                                                                                                        |  |  |  |  | 1 | <b>Intr</b><br>1.1 | oductio<br>Outline |  | $f 1 \\ 3$ |

| 2                                                    | <b>Sym</b><br>2.1<br>2.2<br>2.3 | Problem<br>Contrib<br>Prelimi<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.6<br>Safety<br>2.4.1<br>2.4.2 | ng Robust Systems         n Statement         pution         naries         Systems         Acceptance Conditions         Automata         Specifications         Games and Strategies         Synthesis         Defining Robustness         Ratio Games | <b>5</b><br>6<br>7<br>7<br>8<br>9<br>11<br>13<br>13<br>14<br>18                                                                                                        |  |  |  |  |   |                    |                    |  |            |

|                                                      | 2.5<br>2.6                      | 2.5.1<br>2.5.2<br>2.5.3<br>2.5.4<br>Related                                                                     | Verifying and Synthesizing Robust Systems                                                                                                                                                                                                                | $21 \\ 26 \\ 28 \\ 30 \\ 33 \\ 35 \\ 36 \\ 22 \\ 36 \\ 22 \\ 36 \\ 36 \\ 36 \\ 30 \\ 35 \\ 36 \\ 36 \\ 30 \\ 30 \\ 35 \\ 36 \\ 30 \\ 30 \\ 30 \\ 30 \\ 30 \\ 30 \\ 30$ |  |  |  |  |   |                    |                    |  |            |

|                                                      |                                 |                                                                                                                 | Continuity                                                                                                                                                                                                                                               | $\frac{36}{37}$                                                                                                                                                        |  |  |  |  |   |                    |                    |  |            |

|    |                  | 2.6.3   | Controllers                                   | . 38 |  |  |  |  |  |

|----|------------------|---------|-----------------------------------------------|------|--|--|--|--|--|

|    |                  | 2.6.4   | Games                                         |      |  |  |  |  |  |

|    |                  | 2.6.5   | Robustness Specifications                     | . 41 |  |  |  |  |  |

|    |                  | 2.6.6   | Environment Assumptions                       | . 42 |  |  |  |  |  |

|    |                  | 2.6.7   | Extensions                                    | . 42 |  |  |  |  |  |

|    | 2.7              | Conclu  | usions                                        |      |  |  |  |  |  |

| 3  | Sec              | urity F | Policy Modeling for Smart Cards               | 45   |  |  |  |  |  |

|    | 3.1              | Proble  | em Statement                                  | . 45 |  |  |  |  |  |

|    | 3.2              | Contri  | ibution                                       | . 47 |  |  |  |  |  |

|    | 3.3              | Prelim  | ninaries                                      | . 48 |  |  |  |  |  |

|    |                  | 3.3.1   | Smart Cards                                   |      |  |  |  |  |  |

|    |                  | 3.3.2   | Common Criteria                               | . 51 |  |  |  |  |  |

|    |                  | 3.3.3   | Model Checking                                |      |  |  |  |  |  |

|    |                  | 3.3.4   | Unified Modeling Language Statechart Diagrams |      |  |  |  |  |  |

|    | 3.4              | Model   | ing Smart Cards                               |      |  |  |  |  |  |

|    |                  | 3.4.1   | Modeling Approach                             |      |  |  |  |  |  |

|    |                  | 3.4.2   | Common Criteria Requirements                  |      |  |  |  |  |  |

|    |                  | 3.4.3   | Case Study - Security IC                      |      |  |  |  |  |  |

|    |                  | 3.4.4   | Case Study - Java Card System                 |      |  |  |  |  |  |

|    | 3.5              | Model   | ing using UML Statecharts                     |      |  |  |  |  |  |

|    |                  | 3.5.1   | Integration into the Design Process           |      |  |  |  |  |  |

|    |                  | 3.5.2   | Level of Abstraction                          |      |  |  |  |  |  |

|    |                  | 3.5.3   | Example                                       |      |  |  |  |  |  |

|    | 3.6              | Relate  | ed Work                                       |      |  |  |  |  |  |

|    | 0.0              | 3.6.1   | Common Criteria                               |      |  |  |  |  |  |

|    |                  | 3.6.2   | Model Checking                                |      |  |  |  |  |  |

|    |                  | 3.6.3   | Model Driven Engineering                      |      |  |  |  |  |  |

|    |                  | 3.6.4   | Formal Verification of UML Statecharts        |      |  |  |  |  |  |

|    | 3.7              | 0.0     | usions                                        |      |  |  |  |  |  |

| 4  | Con              | clusio  | ns                                            | 97   |  |  |  |  |  |

| Δ  | Iav              | a Card  | Properties                                    | 99   |  |  |  |  |  |

|    |                  |         | -                                             | 59   |  |  |  |  |  |

| Bi | Bibliography 11  |         |                                               |      |  |  |  |  |  |

| Aι | Author Index 129 |         |                                               |      |  |  |  |  |  |

## List of Tables

| 3.1 | Certified Products by Assurance Level and Certification Date, |    |

|-----|---------------------------------------------------------------|----|

|     | source: https://www.commoncriteriaportal.org/products/stats/. | 46 |

| 3.2 | Target of Evaluation Modes Description (excerpt)              | 64 |

| 3.3 | Operations (excerpt)                                          | 65 |

|     | Input Variables                                               | 70 |

| 3.5 | Bytecodes                                                     | 71 |

| 3.6 | inputSharing                                                  | 71 |

| 3.7 | inputJCREop                                                   | 72 |

| 3.8 | inputCurrentlyActiveContext                                   | 72 |

| 3.9 | Internal Variables                                            | 73 |

# List of Figures

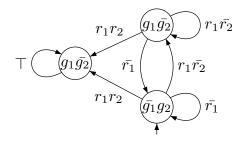

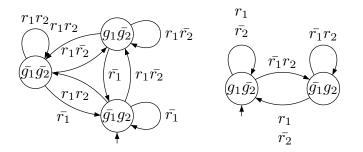

| 2.1  | Automata for $A = G(\neg(r_1 \land r_2))$ and $G_i = G(r_i \to X g_i) \ldots \ldots$ | 16 |

|------|--------------------------------------------------------------------------------------|----|

| 2.2  | Cost automata $C_A$ , $C_{G_i}$ , and $C'_{G_i}$ counting violations of A and $G_i$  | 17 |

| 2.3  | Automatically constructed system for $A \to (G_1 \land G_2 \land G_3)$               | 17 |

| 2.4  | A 2-robust and a 1-robust system                                                     | 18 |

| 2.5  | Automata $A_1$ and $A_2$ for calculating realizability and strict real-              |    |

|      | izability. <sup>1</sup>                                                              | 24 |

| 2.6  | Game graph for 3SAT formula                                                          | 32 |

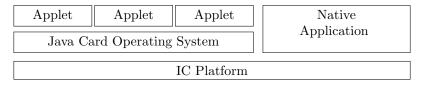

| 3.1  | Architecture of a smart card                                                         | 49 |

| 3.2  | Components of a Typical Security Integrated Circuit (IC)                             | 50 |

| 3.3  | Documentation Refinement in the Assurance Class Development                          | 54 |

| 3.4  | Evaluation Assurance Summary, source [38]                                            | 55 |

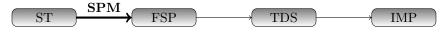

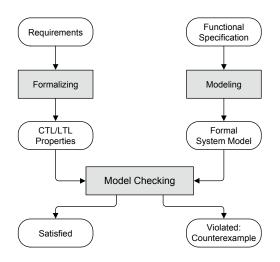

| 3.5  | Process of Model Checking for Functional Specifications                              | 60 |

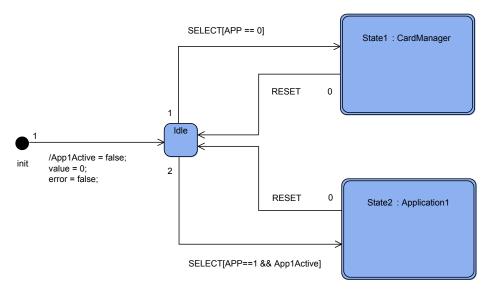

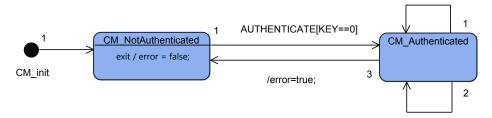

| 3.6  | Model of the Java Card Firewall                                                      | 69 |

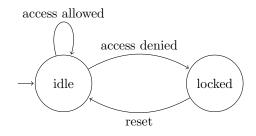

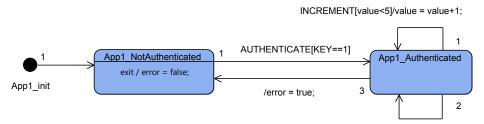

| 3.7  | Access Control Policy Overview state diagram                                         | 83 |

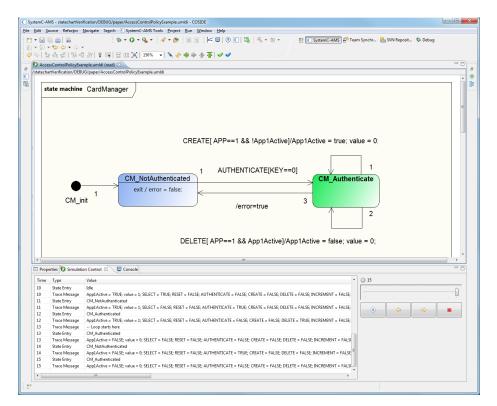

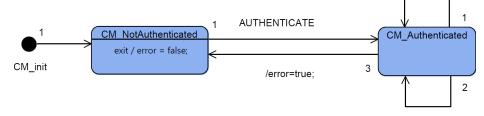

| 3.8  | Access Control Policy Card Manager state diagram                                     | 83 |

| 3.9  | Access Control Policy Application 1 state diagram                                    | 83 |

| 3.10 | Visualization of counter example                                                     | 86 |

| 3.11 | Access Control Policy Card Manager state diagram without key                         |    |

|      | check                                                                                | 87 |

## Glossary

applet An application running on a Java Card OS. 49, 50, 63, 68, 91

Bundesamt für Sicherheit in der Informationstechnik Common Criteria certification body. 47, 51

Common Criteria Security certification scheme. 2, 3, 45, 47, 48, 51, 52, 59, 60, 73, 78–80, 88–92, 94, 95

**Evaluation Assurance Level** Assurance level of a Common Criteria certification. 2, 3, 45, 47, 54, 61–63, 88–91, 95

**flash** A programmable non volatile memory. 49, 50 **Functional Specification** The functional specification of the product under evaluation. 53, 54, 59, 60, 62, 63, 68, 90

Java Card OS An operating system that allows to run applications written in Java on a smart card. v, 49–51, 63, 68

**Protection Profile** Template for a Security Target for a Common Criteria certification. 48, 51, 53, 54, 72, 74, 77, 78

Security Function Policy Set of Security Functional Requirements that define a policy. 74, 75, 77

Security Functional Requirement Security requirement stated in the Security Target for a Common Criteria certification. 52, 59–63, 65, 68, 73–75, 78, 89

**Security Policy Model** Formal model of security policies for Common Criteria certification. 2, 3, 45, 47, 48, 52–54, 59, 60, 63, 68, 88–90, 94, 95

**Security Target** Common Criteria document describing the Target of Evaluation and listing the Security Functional Requirements. 51–54, 59–61, 63, 65, 67, 89

smart card An Integrated Circuit with memory and applications, for example a credit card. xi, 2–4, 48, 49, 51, 56, 59, 68, 79–81, 92, 93

**Special Function Register** Register in an Integrated Circuit used to configure the circuit. 61

statechart A graphical representation of a finite state machine, part of UML. 2–4, 48, 56–59, 61, 63, 78, 79, 82, 88, 95

Target of Evaluation Product under evaluation. ix, 51-54, 62-64, 67, 89

**Target of Evaluation Design** Design description of the product under evaluation. 53, 54

**Target of Evaluation Security Functionality** Description of the security functionality of the product under evaluation. 51–53, 62, 74, 75, 77

**Target of Evaluation Security Functionality Interface** Interface description of the security functionality of the product under evaluation. 53, 63

waterfall model The waterfall model is a sequential design process, used in software development processes, in which progress is seen as flowing steadily downwards (like a waterfall) through the phases of conception, initiation, analysis, design, construction, testing, production, and maintenance.. 53

## Acronyms

**AIS** Application Notes and Interpretation of the Scheme. 63 **API** Application Programming Interface. 50

CASE Computer Aided Software Engineering. 89

CNF Conjunctive Normal Form. 31

CPU Central Processing Unit. 49, 50, 64

CTL Computation Tree Logic. 9, 10, 56, 57, 62, 63, 77, 82, 95

**DCB objective** Disjunctions of Conjunctions of Büchi objectives. 30–33 **DNF** Disjunctive Normal Form. 31

**EEPROM** Electrically Erasable Programmable Read Only Memory. 49, 50

**FSM** Finite State Machine. 56, 57, 59, 61, 63

**GR(1)** Generalized Reactivity(1). 1, 3, 7, 11, 13, 27, 30, 33, 35, 39, 42, 43 **GUI** Graphical User Interface. 94

IC Integrated Circuit. xi, 45, 47–51, 54, 59, 61, 63–65, 68, 88, 95 ICAO International Civil Aviation Organization. 50 ISM Interactive State Machine. 89 IT Information Technology. 45, 52

**JCRE** Java Card Runtime Environment. 50, 68, 69, 71, 73, 76, 90 **JCVM** Java Card Virtual Machine. 50, 69, 70, 89, 90

LTL Linear Temporal Logic. 1, 2, 9, 10, 37, 41, 43, 56, 57, 62, 63, 82, 95, 97, 98

MMU Memory Management Unit. 3, 49, 50, 61, 64, 65, 67 MSCC Maximal Strongly Connected Component. 32, 33

RAM Random Access Memory. 49, 50ROM Read Only Memory. 49, 50RTL Register Transfer Level. 1, 2

**UML** Unified Modeling Language. 2–4, 48, 56–58, 61, 63, 78, 79, 88, 90, 93–95, 97

# Introduction

Linear Temporal Logic (LTL) is a formal language which was introduced by Pnueli in [120] for specifying and verifying the correctness of reactive systems. Reactive systems are continuously running systems that react to a given input. Examples are operating systems, controllers, and protocols. Correctness for such systems can not be defined in terms of the input-output relation at the end of the computation but are defined in terms of the input-output relation during computation. Temporal logic provides the means to define the correct input-output relation during computation; it allows to define sets of computation sequences.

A formal specification language can be used in the design of reactive systems in different ways. From an automation perspective LTL synthesis [47] is the most attractive application. The user provides a formal specification and the synthesis tool generates a system that satisfies the specification. Instead of writing Register Transfer Level (RTL) code the designer only needs to provide an LTL specification. Since the system is constructed from the specification it is correct by construction, assuming that the synthesis tool works correctly. Unfortunately LTL synthesis is a very complex problem, it is 2EXPTIME-complete [125]. The complexity issue can be circumvented by either considering small problems as in program repair [96] or by considering a subset of LTL such as Generalized Reactivity(1) (GR(1))[119]. Apart from the complexity issue, at the current state of the art, the applicability of LTL synthesis for larger systems is also difficult because writing a good specification is not an easy task. The specification must be complete but should not over-constrain the system. Additionally we want the synthesized systems to not only satisfy the specification but to also have properties like minimum size, maximum speed, robustness and many more depending on the application field. Although LTL synthesis has been theoretically solved for many

years there is still a lot of research necessary before it can be applied in an industrial setting.

In contrast to LTL synthesis, LTL verification has found its way into industry in some application fields. The most common formal verification technique is model checking [50]. A model checker is a tool that takes a model and a specification as input and returns **true** if the model satisfies the specification and **false** otherwise. In this context a model is a finite state machine. A finite state machine can have different representations. Examples are hardware description languages such as Verilog and VHDL, proprietary model checking languages such as NuSMV and AIGER, or graphical representations such as Unified Modeling Language (UML) statecharts. A model checker gives a mathematical proof that the model satisfies the specification. In contrast to testing methods, which test a finite number of execution paths, a model checker shows that every execution path in the model satisfies the specification. In the semiconductor industry model checking is usually applied to RTL code on module level to verify parts of safety or security critical products. Formally verifying a large system at RTL level is usually too expensive since LTL model checking is in PSPACE [130].

The main advantage of having a formal specification independent of its usage is that it gives a clear and unambiguous documentation of the design intent. Specifications are often given in natural language, which is easier to understand than a formal language but also easier to misinterpret. A formal language leaves no room for interpretation, therefore it is a good addition to a natural language specification.

Formal methods in general aim at providing more rigorous methods in system design. They allow to find errors and contradictions in the specification early in the design process. With the increasing complexity of todays systems it becomes impossible to design a correct system without the help of such rigorous methods. Unfortunately formal methods are quite expensive in terms of expertise, time and computing power. Thus they are usually only applied to security or safety critical systems, where the costs of a failure of the system exceeds the costs of applying more rigorous design methods. Examples can be found in the automotive, aviation, space, and smart card industry. These industries often have to comply with standards or certification schemes which at some point require a formal specification and/or proof for security or safety critical parts of a product. An example of a security certification scheme which is widely accepted in the smart card industry is Common Criteria [36]. Common Criteria provides different Evaluation Assurance Levels. Higher Evaluation Assurance Levels require more formal evidence from the developer.

The contribution of this thesis is twofold. One part advances the field of LTL synthesis. The other part introduces new methods for Security Policy Models for high assurance level Common Criteria certifications. A short introduction to each is given below.

The first part of this thesis deals with the problem of *synthesizing robust systems*. There are many correct solutions for every LTL synthesis problem. Many different systems can realize a set of specifications, but the system we want

to synthesize should not only be correct but also be robust. We propose to define robustness for such systems and to synthesize robust systems that are resilient to errors. We consider GR(1) specifications, where the system has to satisfy a set of guarantees if the environment satisfies a set of assumptions. A system is robust if small deviations from the assumed environment behavior only leads to small deviations in the guaranteed system behavior. There exist different ways of measuring deviations from expected behavior. We propose two different measures for two different types of properties, namely safety and liveness generalized reactivity properties. Safety robustness specifications are based on counting each error of the environment and the system. A system is more robust if the ratio between environment errors and system errors is smaller. We define ratio games to solve the synthesis problem for safety robustness specifications. We also show how to solve the verification problem for safety robustness specifications. Liveness robustness specifications are based on counting the number of violated assumptions and guarantees. A system is more robust if less guarantees are violated. We develop a new game theoretic algorithm to solve the synthesis problem for liveness robustness specifications. We also show how to solve the verification problem for liveness robustness specifications.

The second part of this thesis deals with security policy modeling for smart cards. For high level Common Criteria certifications a Security Policy Model is required. A Security Policy Model is a formal model of the security policies of a security product such as a smart card. We show how such a Security Policy Model can be realized with a model checker and describe two case studies. For the first case study we model the access control policy of the Memory Management Unit (MMU) of the NXP P60 Secure Smart Card Controller which was used for the Evaluation Assurance Level 6 certification of the product. It was the first certification in the German scheme that reached Evaluation Assurance Level 6. For the second case study we model the access control policy of the Java Card firewall. The formal verification of the Java Card firewall requirements uncovers contradictions. The case study demonstrates that without formal analysis contradictions can stay undetected in a requirements specification for several years. We also show how the implementation of a Security Policy Model can be integrated into an industrial design process using UML statecharts as modeling language.

The first part is a contribution to basic research of possible future synthesis methods. It is based on logic, complexity theory, automata theory, and game theory. The second part is a contribution to current industry methods and processes. It is based on formal methods, certification standards, and industry requirements. This thesis gives deep insights into the theoretical background of formal methods but also shows how to apply formal methods in an industrial setting.

## 1.1 Outline

The thesis is presented in two main parts.

The first part given in Chapter 2 deals with the synthesis of robust systems. Starting with the problem statement in Section 2.1 and the description of the contribution in Section 2.2. Section 2.3 gives the necessary definitions for the subsequent sections. Section 2.4 presents a robustness definition for safety specifications and describes a solution to the corresponding verification and synthesis problem. Section 2.5 presents a robustness definition for liveness specifications and describes the solution of the corresponding verification and synthesis problem. Related work is given in Section 2.6 and the conclusions are given in Section 2.7.

The second part given in Chapter 3 deals with security policy models for smart cards. Starting with the problem statement in Section 3.1 and the description of the contribution in Section 3.2, Section 3.3 gives the necessary definitions for the subsequent sections. Section 3.4 describes the proposed security policy modeling approach and gives two case studies which describe security policy models for smart cards. Section 3.5 shows how security policy modeling can be integrated into the design process of a smart card by using UML statecharts. Related work is given in Section 3.6 and the conclusions are given in Section 3.7.

Chapter 4 gives an overall conclusion of the work.

# Synthesizing Robust Systems

# This chapter describes our work on synthesizing robust systems. It includes the

## 2.1 Problem Statement

work of two publications: [27] and [22].

Current verification and synthesis approaches consider the functional correctness of a system as a Boolean question: either the specification is fulfilled, or it is not. This approach is unsatisfactory in many situations [23]. In particular, many specifications consist of environment assumptions and system guarantees. For such specifications, the classical approach does not impose any restrictions on the behavior of the system when the environment assumptions are *not* fulfilled. We argue that (1) desirable systems act in some "reasonable" way, even if the environment does not always fulfill the assumptions and (2) it is an undue burden on the user to specify the proper behavior of the system for each and every environment behavior. Desirable systems should fulfill a natural "graceful degradation" property in the sense that the system should fulfill the guarantees as well as it can, given any behavior of the environment.

Suppose that a system is required to accept up to 1000 requests per second and to respond to each request within 0.1 seconds. What should the system do when request number 1001 arrives? There are several options, including terminating the system, dropping the extra request, or delaying a response. Clearly, all of these approaches satisfy the specification, but some are better than others. (Cf. [56].) Thus, a system should not only be correct, it should also be *robust*, meaning that it "behaves 'reasonably', even in circumstances that were not anticipated in the requirements specification [...]" [79].

## 2.2 Contribution

We define robustness for safety properties and for liveness properties of the form  $A \to G$ , where A is an environment assumption and G is a system guarantee. For both safety and liveness properties we show how to verify and synthesize a robust system.

Let us first discuss the difference between safety and liveness properties. Here we only give an informal explanation and a small example, for a more detailed discussion refer to [4]. Safety properties stipulate that "bad things" do not happen. For example consider the controller of a traffic light. A possible safety property could be: "Exactly one light must always be on". In contrast, liveness properties stipulate that "good things" do happen eventually. Considering the controller of a traffic light again, a possible liveness property could be: "Eventually the green light must be on". The fundamental difference in verification and synthesis is that for safety properties it is always (at any point in time) possible to determine whether the property has been violated or not but for liveness properties this is not possible. Consider the traffic light again, as long as only one light is on at a time the above safety property is satisfied, but as soon as no light is on or more than one light is on the above safety property is not satisfied anymore. Now imagine the red light is on, currently we can not decide if the above liveness property is violated or not. Because of this intrinsic difference between safety and liveness properties we define two different notions of robustness.

#### Safety

For safety we define robustness as the ratio between the possible errors of the environment and the resulting errors of the system. For safety specifications we can define a measure to count how often/badly an assumption or a guarantee is violated. An environment error corresponds to a violation of an assumption and a system error corresponds to a violation of a guarantee. A system is robust if finitely many environment errors never lead to infinitely many system errors, it is k-robust if the ratio of environment errors to system errors is always smaller than or equal to k.

We give a solution to the verification problem and the synthesis problem for (k-)robust systems. The synthesis problem is solved through a novel type of games, we call ratio games. An optimal robust system corresponds to the winning strategy of a ratio game, where the system minimizes the ratio of system errors to environment errors. We show that ratio games have optimal positional strategies and show how to calculate an optimal positional strategy in pseudopolynomial time.

#### Liveness

For liveness the notion of robustness that we suggest aims to maximize the number of guarantees that are fulfilled for any number of assumptions that may be violated. Note that for liveness properties we can not count how often a property is violated but only how many properties are violated.

We give different examples of robustness measures for Generalized Reactivity(1) (GR(1)) properties and show that they can all be reduced to Generalized Reactivity formulas. We show how to verify such formulas and how to synthesize them to robust systems. For synthesis we develop a novel game-theoretic algorithm that is faster than Zielonka's, although it does produce strategies with larger memory. Our algorithm can also be used for the synthesis of GR(1) properties, in which case it outperforms the algorithm of [119] when the state space of the specification is larger than the number of assumptions and guarantees.

### 2.3 Preliminaries

We discuss the verification and synthesis of reactive systems. The language of a reactive system consists of infinite words. For a word  $w = w_1 \dots$ , let  $|w| \in \mathbb{N} \cup \{\infty\}$  be the length of the word, let  $w[..i] = w_1 \dots w_i$  be the prefix of length *i*, and let  $w[i..] = w_i w_{i+1} \dots$  be the suffix starting at position *i*. We denote the set of all finite (infinite) words over the alphabet *A* by  $A^*$  ( $A^{\omega}$ ).

#### 2.3.1 Systems

We consider systems with a set of input signals I and a set of output signals O. We define  $AP = I \cup O$ . We use the signals as atomic propositions in the specifications defined below. Our input alphabet is thus  $\Sigma_I = 2^I$ , the output alphabet is  $\Sigma_O = 2^O$ , and we define  $\Sigma = 2^{AP}$ .

#### Moore machines

We use Moore machines to represent systems. A Moore machine with input alphabet  $\Sigma_I$  and output alphabet  $\Sigma_O$  is a tuple  $M = (Q, q_0, \delta, \lambda)$ , where Q is the set of states,  $q_0 \in Q$  is the initial state,  $\delta : Q \times \Sigma_I \to Q$  is the transition function, and  $\lambda : Q \to \Sigma_O$  is the output function. In each state, the Moore machine outputs a letter in  $\Sigma_O$ , then reads a letters in  $\Sigma_I$ , and moves to the next state. The run of M on a sequence  $x = x_0 x_1 \ldots \in \Sigma_I^{\omega}$  is a sequence  $\rho_0 \rho_1 \ldots \in Q^{\omega}$ , where  $\rho_0 = q_0$  and  $\rho_{i+1} = \delta(\rho_i, x_i)$ . The corresponding word is  $\lambda(\rho) = w_0 w_1 \ldots \in \Sigma^{\omega}$ , where  $w_i = \lambda(\rho_i) \cup x_i$ . The language of M,  $L(M) \subseteq \Sigma^{\omega}$ , consists of the words corresponding to the runs of M. We define  $L^*(M) = L(M) \cap \Sigma^*$ .

#### 2.3.2 Acceptance Conditions

The specifications we use are automata and we synthesize a system that realizes a given specification using games. Both automata and games can have the following acceptance conditions.

Let Q be a set of states, an *acceptance condition* is a predicate Acc :  $Q^{\omega} \to \mathbb{B}$ , mapping infinite runs to true or false (accepting and not accepting, or winning and losing, respectively). The *safety acceptance condition* is Acc( $\rho$ ) = true iff  $\rho$  never leaves  $F \subseteq Q$ , the set of safe states. The Büchi acceptance condition is  $\operatorname{Acc}(\rho) = \operatorname{true} \operatorname{iff} \inf(\rho) \cap F \neq \emptyset$ , where  $F \subseteq Q$  is the set of accepting states and  $\inf(\rho)$  is the set of elements that occur infinitely often in  $\rho$ . We abbreviate the Büchi condition as  $\mathcal{B}(F)$ . A Generalized Reactivity acceptance condition is a predicate  $\bigwedge_{l=1}^{k} (\bigwedge_{i=1}^{m_l} \mathcal{B}(A_{l,i}) \to \bigwedge_{i=1}^{n_l} \mathcal{B}(G_{l,i}))$ , where  $A_{l,i} \subseteq Q$  are assumptions and  $G_{l,i} \subseteq Q$  are guarantees. To simplify notation, we will assume that the  $m_l$ are all equal to some constant m, and similarly for  $n_l$  and n. The acceptance condition is a GR(1) acceptance condition if k = 1, it is a generalized Büchi acceptance condition if k = 1 and m = 0, it is a Streett acceptance condition with k pairs if m = n = 1.

#### 2.3.3 Automata

A deterministic *automaton* over the alphabet  $\Sigma$  is a tuple  $A = (Q, q_0, \delta)$ , where Q is a finite set of states,  $q_0 \in Q$  is the initial state, and  $\delta : Q \times \Sigma \to Q$  is the transition function.

A run of an automaton A on a word  $w = w_0 w_1 \ldots \in \Sigma^* \cup \Sigma^\omega$  is the longest sequence  $\rho(w) = \rho_0 \rho_1 \ldots \in Q^* \cup Q^\omega$  such that  $\rho_0 = q_0$ , and  $\rho_{i+1} = \delta(\rho_i, w_i)$ . An automaton accepts a word if its run is accepting (see below). We call the set L(A) of infinite words accepted by A the language of A.

The product automaton  $A = A_1 \times A_2$  of two automata is defined as usual.

#### Safety automaton

A safety automaton  $A = (Q, q_0, \delta, F)$  is a complete deterministic automaton  $(Q, q_0, \delta)$  together with a set  $F \subseteq Q$  of accepting states such that there are no edges from non-accepting to accepting states. An infinite run is accepting if it never leaves F. See Section 2.3.2 for a formal definition of the safety acceptance condition.

#### Büchi automaton

A Büchi automaton  $A = (Q, q_0, \delta, F)$  is an automaton with a Büchi condition with accepting state set F. An infinite run is *accepting* if a state in F is visited infinitely often. See Section 2.3.2 for a formal definition of the Büchi acceptance condition.

#### Single and Double Cost Automata

A single (double) cost automaton over the alphabet  $\Sigma$  is a tuple  $C = (Q, q_0, \delta, c)$ consisting of a complete deterministic automaton  $(Q, q_0, \delta)$  and a cost function  $c: Q \times \Sigma \to \mathbb{N}$  ( $c: Q \times \Sigma \to \mathbb{N} \times \mathbb{N}$ , respectively) that associates to each transition a value in  $\mathbb{N}$  ( $\mathbb{N} \times \mathbb{N}$ , resp.) called *cost*. In a double cost automaton, we use  $c_s$  and  $c_e$  to refer to the cost function of the first and the second component, respectively. The maximal cost is the smallest  $W \in \mathbb{N} \ \forall q \in Q, \sigma \in \Sigma : c(q, \sigma) \leq$ W ( $c_e(q, \sigma), c_s(q, \sigma) \leq W$ ). The cost of a word  $w \in \Sigma^* \cup A^{\omega}$ , denoted by C(w), is the sum  $\sum_{i=0}^{|W|} c(\rho(w)_i, w_i)$ , For double cost automata, we use  $C_e(w)$  and  $C_s(w)$  to refer to the first and second component, respectively, of the cost of the word w.

The sum of two cost automata  $A_1 = (Q_1, q_{01}, \delta_1, c_1)$  and  $A_2 = (Q_2, q_{02}, \delta_2, c_2)$ is the cost automaton  $A = A_1 + A_2 = (Q, q_0, \delta, c)$ , where A is the product of the automata  $A_1$  and  $A_2$  with costs  $c = c_1 + c_2$ , i.e.,  $c((q_1, q_2), \sigma) = c_1(q_1, \sigma) + c_2(q_2, \sigma)$ . The product of two single cost automata  $A_1 = (Q_1, q_{01}, \delta_1, c_1)$  and  $A_2 = (Q_2, q_{02}, \delta_2, c_2)$  is a double cost automaton  $A = A_1 \times A_2 = (Q, q_0, \delta, c)$ , where A is the product of the automata  $A_1$  and  $A_2$  with costs  $c = (c_1, c_2)$ , i.e.,  $c((q_1, q_2), \sigma) = (c_1(q_1, \sigma), c_2(q_2, \sigma))$ .

#### 2.3.4 Specifications

We use safety automata for safety specifications and Büchi automata for liveness specifications. In our examples, we also show Linear Temporal Logic (LTL) formulas describing the discussed properties. Furthermore we use LTL and Computation Tree Logic (CTL) specifications in Chapter 3 for model checking.

#### **Temporal Logic**

Temporal Logic is used to describe the behavior of reactive systems. LTL was introduced by Pnueli in [120] and CTL was introduced by Ben-Ari in [15] to describe properties of infinite computations where the specification of an end state is not possible. We will give a short introduction to the syntax and semantics of LTL future formulas. For further reading we recommend [106].

The syntax of an LTL formula over a set of atomic propositions AP is defined as follows.

- 1. Every atomic proposition p in AP is an LTL formula,

- 2. if f and g are LTL formulas then  $\neg f$  and  $f \land g$  are LTL formulas, and

- 3. if f and g are LTL formulas then X f and  $f \cup g$  are LTL formulas.

The operators used in the definition are denoted as the elementary operators. Other connectives can be seen as abbreviations:  $f \lor g = \neg(\neg f \land \neg g), f \to g = \neg f \lor g, f \leftrightarrow g = (f \land g) \lor (\neg f \land \neg g), \mathsf{F} f = \mathsf{true} \,\mathsf{U} \,f, \text{ and } \mathsf{G} \,f = \neg \,\mathsf{F} \neg f.$

The semantics of an LTL formula over a set of atomic propositions P are recursively defined over infinite words over the alphabet  $2^{AP}$ .

- 1. Atomic Propositions:

- $p \in AP : w[i..] \models p \text{ iff } p \in w_i.$

- 2. Boolean Operators:

- $w[i..] \models \neg f$  iff not  $w[i..] \models f$ , and

- $w[i..] \models f \land g$  iff  $w[i..] \models f$  and  $w[i..] \models g$ .

3. Temporal Operators:

- $w[i..] \models \mathsf{X} f$  iff  $w[i+1..] \models f$ , and

- $w[i..] \models f \cup g$  iff  $\exists j \ge i : w[j..] \models g$  and  $\forall k, i \le k < j : w[k..] \models f$ .

We refer to X as the next operator and to U as the until operator. The semantics of the operators always (G) and eventually (F) can be derived from the semantics of the elementary operators.

- $w[i..] \models \mathsf{G} f$  iff  $\forall j \ge i : w[j..] \models f$ , and

- $w[i..] \models \mathsf{F} f$  iff  $\exists j \ge i : w[j..] \models f$ .

A word w satisfies the formula f if  $w \models f$ . A Moore machine M satisfies or realizes an LTL formula f  $(M \models f)$  if all possible words of the Moore Machine satisfy the formula.

The syntax of an CTL formula over a set of atomic propositions AP is defined as follows.

- 1. Every atomic proposition p in AP is an CTL formula,

- 2. if f and g are CTL formulas then  $\neg f$  and  $f \wedge g$  are CTL formulas, and

- 3. if f and g are CTL formulas then  $\mathsf{AX} f$ ,  $\mathsf{A}(f \cup g)$ , and  $\mathsf{E}(f \cup g)$  are CTL formulas.

The operators used in the definition are denoted as the elementary operators. Other connectives can be seen as abbreviations:  $f \lor g = \neg(\neg f \land \neg g), f \to g = \neg f \lor g$ ,  $\mathsf{EX} f = \neg \mathsf{AX} \neg f$ ,  $\mathsf{EF} f = \mathsf{E}(\mathsf{true} \,\mathsf{U} \,f)$ , and  $\mathsf{AG} f = \neg \mathsf{EF} \neg f$ .

The semantics of an CTL formula over a set of atomic propositions AP are recursively defined over the language of Moore Machines  $M = (Q, q_0, \delta, \lambda)$  with the alphabet  $2^{AP}$ . Let q be a state of M ( $q \in Q$ ) and let L(M, q) be the language of the Moore Machine with initial state q.

- 1. Atomic Propositions:

- $p \in AP : (M,q) \models p$  iff  $\exists w_0 w_1 \ldots \in L(M,q) : p \in w_0$ .

- 2. Boolean Operators:

- $(M,q) \models \neg f$  iff not  $(M,q) \models f$ , and

- $(M,q) \models f \land g$  iff  $(M,q) \models f$  and  $(M,q) \models g$ .

- 3. Temporal Operators:

- $(M,q) \models \mathsf{AX} f$  iff  $\forall$  runs  $qq_1 \dots$  of  $M : (M,q_1) \models f$ ,

- $(M,q) \models \mathsf{A}(f \cup g)$  iff  $\forall$  runs  $qq_1 \dots$  of  $M : \exists j \ge i : (M,q_j) \models g$  and  $\forall k, i \le k < j : (M,q_k) \models f$ , and

- $(M,q) \models \mathsf{E}(f \cup g)$  iff  $\exists$  a run  $qq_1 \dots$  of  $M : \exists j \ge i : (M,q_j) \models g$  and  $\forall k, i \le k < j : (M,q_k) \models f$ .

We refer to E as the exists operator and to A as the for all operator. The semantics of the operators EX, EF and AG can be derived from the semantics of the elementary operators.

- $(M,q) \models \mathsf{EX} f$  iff  $\exists$  a run  $qq_1 \dots$  of  $M : (M,q_1) \models f$ ,

- $(M,q) \models \mathsf{EF} f \text{ iff } \exists a \text{ run } qq_1 \dots \text{ of } M : \exists j : (M,q_j) \models f,$

- $(M,q) \models \mathsf{AG} f \text{ iff } \forall \text{ runs } qq_1 \dots \text{ of } M : \forall j : (M,q_j) \models f,$

#### Safety

Safety properties are properties stating that something bad will never happen or equally that we always stay in a safe state. In temporal logic these properties are usually defined using the G operator. We use safety automata to specify safety properties. Given a safety automaton A, we say the Moore machine M satisfies A, if  $L(M) \subseteq L(A)$ . We use cost automata to specify the cost of an error for robust systems satisfying a safety specification.

#### Liveness

Liveness properties are properties stating that eventually some property will hold. We look at a special subset of properties, which can include safety and liveness. The specifications we consider are GR(1) specifications. GR(1) specifications consist of two parts: assumptions and guarantees [119]. They specify the interaction between an environment (controlling the input variables  $\Sigma_I$ ) and a system (controlling the output variables  $\Sigma_O$ ). The specification states that the system must fulfill all guarantees whenever the environment fulfills all assumptions.

A GR(1) specification over the alphabet  $\Sigma$  consists of m Büchi automata  $A_1^a, \ldots, A_m^a$  for the environment assumptions and n Büchi automata  $A_1^g, \ldots, A_n^g$  for the system guarantees [119]. Let  $A^{GR(1)} = (Q, \delta, q_0, \operatorname{Acc})$  be the product of all automata  $A_i^a$  and  $A_i^g$ , where the state space is  $Q = Q_1^a \times \cdots \times Q_m^a \times Q_1^g \times \cdots \times Q_n^g$ , the transition function is  $\delta((q_1^a, \ldots, q_n^g), \sigma) = (\delta_1^a(q_1^a, \sigma), \ldots, \delta_n^g(q_n^g, \sigma))$ , and the initial state is  $q_0 = (q_{0,1}^a, \ldots, q_{0,n}^g)$ . Let  $J_i^a = \{(q_1^a, \ldots, q_n^g) \in Q \mid q_i^a \in F_i^a\}$  be the set of states that are accepting in  $A_i^a$ . Similarly, let  $J_i^g$  be the set of all states of  $A^{GR(1)}$  that are accepting in  $A_i^g$ . The acceptance condition Acc is a GR(1) condition with assumptions  $J_i^a$  and guarantees  $J_i^g$ .

Note that the size of the state space of the specification grows exponentially with the number of assumptions and guarantees (if the Büchi automata have more than 2 states), whereas m and n grow linearly.

A system realizes a GR(1) specification  $A^{GR(1)}$  if the language of the system is part of the language of  $A^{GR(1)}$ .

#### 2.3.5 Games and Strategies

A game graph is a finite directed graph  $G = (S, s_0, E)$  consisting of a set of states S, an initial state  $s_0 \in S$ , and a set of edges  $E \subseteq S \times S$  such that each state has

at least one outgoing edge. The states are partitioned into a set  $S_1$  of *Player-1* states and a set  $S_2$  of *Player-2* states. When the initial state is not relevant, we omit it and write (S, E). A play  $\rho = s_0 s_1 \ldots \in S^{\omega}$  is an infinite sequence of states such that for all  $i \geq 0$  we have  $(s_i, s_{i+1}) \in E$ . We denote the set of all plays by  $\Omega$ .

Given a game graph G = (S, E), a *(finite memory) strategy* for Player 1 is a tuple  $(\Gamma, \gamma_0, \pi)$ , where  $\Gamma$  is some (finite) set representing the memory,  $\gamma_0 \in \Gamma$ is the initial memory content, and  $\pi : S_1 \times \Gamma \to S \times \Gamma$  is a function mapping a Player-1 state *s* and a memory content to a successor state *s'* and an updated memory content such that  $(s, s') \in E$ . A Player-2 strategy is defined similarly. We denote by  $\Pi_1$  and  $\Pi_2$  the set of all possible Player-1 and Player-2 strategies, respectively. A strategy is *positional* if it depends only on the current state. We represent a positional strategy  $\pi$  for player *p* as a function from  $S_p$  to *S*. Let  $\rho((\Gamma_1, \gamma_{0,1}, \pi_1), (\Gamma_2, \gamma_{0,2}, \pi_2), s)$  denote the unique play starting at *s* when Player 1 plays according to the strategy  $(\Gamma_1, \gamma_{0,1}, \pi_1)$  and Player 2 plays according to  $(\Gamma_2, \gamma_{0,2}, \pi_2)$ .

A game is a game graph together with an objective. The game graph defines the possible actions of the players. The objective describes the goal for the players. Some games have a quantitative objective, for example mean payoff games. Other games have qualitative objective, namely that of winning. Generalized Reactivity games are games with quantitative objectives.

For quantitative objectives we define the value of a play, which is given by a value function  $v : \Omega \to \mathbb{R} \cup \{-\infty, \infty\}$ . The value of a state s under Player-1 strategy and Player-2 strategy, denoted by  $v((\Gamma_1, \gamma_{0,1}, \pi_1), (\Gamma_2, \gamma_{0,2}, \pi_2), s)$ , is the value of the play  $\rho((\Gamma_1, \gamma_{0,1}, \pi_1), (\Gamma_2, \gamma_{0,2}, \pi_2), s)$ .

We consider complementary objectives for the two players: Player 1 tries to minimize the value of a state and Player 2 tries to maximize it. (Note that the converse is more usual.) The Player-1 value of a state s under the strategy  $(\Gamma_1, \gamma_{0,1}, \pi_1)$  is  $\sup_{(\Gamma_2, \gamma_{0,2}, \pi_2) \in \Pi_2}(v((\Gamma_1, \gamma_{0,1}, \pi_1), (\Gamma_2, \gamma_{0,2}, \pi_2), s))$ , which is the value Player 1 can guarantee with his strategy independent of the strategy Player 2 plays. A strategy  $(\Gamma_1, \gamma_{0,1}, \pi_1)$  is optimal for Player 1 in state s if the Player-1 value of the state s under the strategy  $(\Gamma_1, \gamma_{0,1}, \pi_1)$  is minimal. The Player-2 value and Player-2 optimal strategies are defined correspondingly. The value of a state s denoted by v(s) is the Player-1 value of the play starting in s, in which both players play optimally.

A mean payoff game is described as a tuple  $((S, s_0, E), w)$ , where  $(S, s_0, E)$  is a game graph and  $w : E \to \mathbb{N}$  is a payoff function. The value function for a play  $\rho = s_0 s_1 \dots$  in a mean payoff game is  $v(\rho) = \limsup_{n \to \infty} \frac{1}{n} \sum_{i=0}^n w(e_i)$  with  $e_i = (s_i, s_{i+1})$ .

The objectives for games with qualitative objectives are acceptance conditions. Acceptance conditions are given in Section 2.3.2.

A Generalized Reactivity (GR) game is a tuple ((S, E), Acc), consisting of a game graph (S, E) and a Generalized Reactivity acceptance condition Acc. A play  $\rho$  is winning for Player 1 if it satisfies the objective of the game Acc( $\rho$ ) = true, otherwise it is winning for Player 2. A strategy  $\pi_1$  is winning for Player 1 if for

all strategies  $\pi_2$  of Player 2 the play  $\rho((\Gamma_1, \gamma_{0,1}, \pi_1), (\Gamma_2, \gamma_{0,2}, \pi_2), s_0)$  is winning. A game is winning for Player 1 (Player 2) if there exists a winning strategy for Player 1 (Player 2, resp.). A GR(1) game is a game with a GR(1) acceptance condition. A Streett game is a game with a Streett acceptance condition.

Given a game graph G, two objectives are equivalent if all plays in G have the same winner for both objectives. The objectives are *equivalent* if they are equivalent for any game graph.

#### 2.3.6 Synthesis

For synthesis we translate the specification into a game such that a winning strategy for the game corresponds to a Moore machine that satisfies the specification. In the following we describe how to translate automata into game graphs and GR(1) specifications into GR(1) games.

An automaton  $A = (Q, q_0, \delta)$  over the alphabet  $\Sigma$  can be translated into a game graph  $(S, s_0, E)$  as follows. We define the set of Player-1 states as  $S_1 = \{s_{(q,\sigma_i)} \mid q \in Q \text{ and } \sigma_i \in \Sigma_I\} \cup \{s_0\}$ . The Player-2 states  $S_2$  are given by the set  $S_2 = \{s_{(q,\sigma_o)} \mid q \in Q \text{ and } \sigma_o \in \Sigma_O\}$ . The set of game states is the set  $S = S_1 \cup S_2$ . Every state of the game (except for the initial state) represents a state of the automaton and an input or output label. Note that this corresponds to moving from a transition-labeled to a state-labeled system. Every outgoing transition of a state q in A is translated into two steps of the game: first, Player 1 chooses a letter  $\sigma_o$  from  $\Sigma_O$  by moving to the states  $s_{(q,\sigma_o)}$ , then Player 2 chooses a letter  $\sigma_i$  from  $\Sigma_I$  and moves according to the transition relation to a new state  $s_{(q',\sigma_i)}$  such that  $\delta(q, \sigma_o \cup \sigma_i) = q'$ . Formally, we have that  $E_1 = \{(s_{(q,\sigma_i)}, s_{(q,\sigma_o)}) \mid q \in Q, \sigma_o \in \Sigma_O, \text{ and } \sigma_I \in \Sigma_I\} \cup \{(s_0, s_{q_o,\sigma_o}) \mid \sigma_o \in \Sigma_O\},$  $E_2 = \{(s_{(q,\sigma_o)}, s_{(q',\sigma_I)}) \mid q, q' \in Q, \sigma_o \in \Sigma_O, \sigma_I \in \Sigma_I, \text{ and } \delta(q, \sigma_o \cup \sigma_i) = q'\}$ , and  $E = E_1 \cup E_2$ .

A GR(1) specification  $A^{GR(1)} = (Q, q_0, \delta, \operatorname{Acc})$  over the alphabet  $\Sigma$  with m environment assumptions and n system guarantees can be translated into a GR(1) game  $((S, s_0, E), ((A_1, \ldots, A_m), (G_1, \ldots, G_n)))$  as follows. The automaton  $(Q, q_0, \delta)$  is translated into the game graph  $(S, s_0, E)$  as described above. Let  $J_i^a$  and  $J_j^g$  be defined as described for GR(1) specifications, then the assumption sets are  $A_i = \{s_{(q,\sigma_o)} \mid q \in J_i^a\}$  and the guarantee sets are  $G_j = \{s_{(q,\sigma_o)} \mid q \in J_j^q\}$ .

## 2.4 Safety

This section proposes a formal notion of robustness through graceful degradation for discrete functional safety properties: A small error by the environment should induce only a small error by the system, where the error is defined quantitatively as part of the specification, for instance, as the number of failures. Given such a specification, we define a system to be robust if a finite environment error induces only a finite system error. As a more fine-grained measure of robustness, we define the notion of k-robustness, meaning that on average, the number of system failures is at most k times larger than the number of environment failures. We show that the synthesis question for robust systems can be solved in polynomial time as a one-pair Streett game and that the synthesis question for k-robust systems can be solved using *ratio games*. Ratio games are a novel type of graph games in which edges are labeled with a cost for each player, and the aim is to minimize the ratio of the sum of these costs. We show that ratio games are positional, that the associated decision problem is in NP  $\cap$  co-NP, and that they can be solved in pseudopolynomial time. They can be solved in polynomial time if the cost of a failure is assumed to be constant.

In the next subsection, we present our framework based on error functions, and define robustness and k-robustness. In Section 2.4.2, we introduce ratio games and show how to solve them. Section 2.4.3 shows how to use ratio games to construct correct and robust systems.

#### 2.4.1 Defining Robustness

In this section we introduce our notion of robustness based on error specifications. We show how error specifications relate to classical specifications and the notion of realizability. We conclude with an example.

**Definition 1.** An *error function* is a function  $d : \Sigma^* \cup \Sigma^\omega \to \mathbb{N} \cup \{\infty\}$ . The function is monotonically increasing in the sense that if w' is a prefix of w then  $d(w') \leq d(w)$ .

The error functions define a distance between allowed and observed behavior, for instance, by measuring the number of failures in some appropriate sense. Thus, d(w) = 0 indicates that w fulfills the specification, and a higher value indicates a more serious violation of the specification.

**Definition 2.** An *error specification* is a pair of error functions  $(d_e, d_s)$ .

Error specifications provide a measure of "badness" for both the environment behavior (using  $d_e$ ) and the system behavior (using  $d_s$ ) and form the specifications we use in the sequel. We assume that these specifications are provided by the user.

**Definition 3.** A Moore machine M realizes an error specification  $(d_e, d_s)$  if  $\forall w \in L(M) : d_e(w) = 0$  implies  $d_s(w) = 0$ .

Thus, an error specification induces a classical specification  $A \to G$ , where  $A = \{w \in \Sigma^{\omega} \mid d_e(w) = 0\}$  and  $G = \{w \in \Sigma^{\omega} \mid d_s(w) = 0\}$  are sets of infinite words.

The following notion is an alternative to realizability, forbidding the system to make mistakes before the environment does.

**Definition 4.** A Moore machine M strictly realizes an error specification  $(d_e, d_s)$  if  $\forall w \in L^*(M) : d_e(w[..|w| - 1]) = 0$  implies  $d_s(w) = 0$ . An error specification is strictly realizable if there exists a Moore machine that strictly realizes it.

**Example 1.** An example of a specification that is realizable but not strictly realizable is  $A_1 \wedge A_2 \rightarrow G_1 \wedge G_2$ , where x is an input, y is an output,  $A_1$  requires that x is always true (Gx),  $A_2$  says that x is initially equal to  $y \ (x \leftrightarrow y)$ ,  $G_1$  states that y is always true (Gy), and  $G_2$  states that x in the first step and y in the second step are different  $(x \nleftrightarrow (Xy))$ . All Moore machines that realize the specification start with setting y to false, which violates the guarantees but forces the environment to do the same<sup>1</sup>.

**Definition 5.** A Moore machine M is *robust* with respect to an error specification  $(d_e, d_s)$  if  $\forall w \in L(M) : d_e(w) \neq \infty$  implies  $d_s(w) \neq \infty$ .

This means that a robust system can recover from a finite environment error. Note that a system can be robust with respect to a specification that it does not realize if it contains a word with a finite system error but no environment error. Error specifications can forbid words by assigning infinite system costs. (In particular, this is possible when such specifications are given by double cost automata, as below.)

In order to calculate the quality of a robust system we want to calculate the largest system error for every environment error.

**Definition 6.** A Moore machine M is k-robust with respect to an error specification  $(d_e, d_s)$  if  $\exists d \in \mathbb{N} : \forall w \in L^*(M) : d_s(w) \leq k \cdot d_e(w) + d$ .

Obviously, every k-robust system is robust, regardless of k. Also, every robust system is k-robust for some finite k, see Theorem 6, i.e., for every finite Moore machine, the growth of the system error is either linear with respect to the environment error or unbounded. This motivates our choice of the robustness measure as a linear function. The definition of k-robustness allows us to rank Moore machines with respect to error specifications: A smaller k is better, it means that the system error increases slowly with the environment error. The constant d allows the system finitely many system failures independent of the environment error. In this work, we focus on the infinite behavior of a machine, and note that d can be bounded by the product of the size of the Moore machine and the maximal weight. We leave minimization of d to future work.

**Definition 7.** A Moore machine (k-)robustly (and strictly) realizes an error specification if it (strictly) realizes the specification and it is (k-)robust with respect to the specification.

In the remainder, we use double cost automata to define error specifications. The environment (system) error function associated with C maps each  $w \in \Sigma^* \cup \Sigma^\omega$  to its cost  $C_e(w)$  ( $C_s(w)$ , respectively). Note that a double cost automaton can be seen as the product of two single cost automata. We can construct an error specification from a set of cost automata  $C_{A_i}$  for the system and  $C_{G_i}$  for the environment. The error specification (a double cost automaton) is the product of the sum of all  $C_{A_i}$  and the sum of all  $C_{G_i}$ .

<sup>&</sup>lt;sup>1</sup>This specification is based on an example by Marco Roveri.

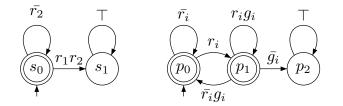

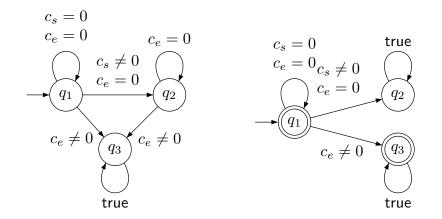

**Figure 2.1:** Automata for  $A = \mathsf{G}(\neg(r_1 \land r_2))$  and  $G_i = \mathsf{G}(r_i \to \mathsf{X} g_i)$

**Example 2.** Consider a system with two request signals  $r_1$  and  $r_2$  as inputs and two grant signals  $g_1$  and  $g_2$  as outputs. We want the system to respond to each request with a grant in the next step. Formally, we require that the system satisfies  $G_i = \mathsf{G}(r_i \to \mathsf{X} g_i)$  for  $i \in \{1, 2\}$ . The system should also guarantee that grants are mutually exclusive, i.e.,  $G_3 = \mathsf{G} \neg (g_1 \land g_2)$ . To avoid a contradicting specification, we assume that requests are also mutually exclusive, i.e.,  $A = \mathsf{G} \neg (r_1 \land r_2)$ . Figure 2.1 shows two safety automata, one for A and one for  $G_1$  and  $G_2$ . Note that we summarize labels on edges with Boolean expressions over  $r_i$  and  $g_i$ , where a horizontal alignment of two variables represents a conjunction and a vertical alignment of two variables represent a disjunction. We use a bar to denote negation and  $\top$  to denote true. States depicted with two cycles are accepting states. Note that the automaton for  $G_3$  is exactly the same as for A, where  $r_1$  and  $r_2$  are renamed to  $g_1$  and  $g_2$ , respectively.

Starting from the specification  $A \to (G_1 \wedge G_2 \wedge G_3)$ , we can define what it means for the system and the environment to fail. In particular, the environment violates assumption A if it raises  $r_1$  and  $r_2$  at the same time. This corresponds to taking the edge from  $s_0$  to  $s_1$ . The leftmost automaton  $C_A$  in Figure 2.2 is a cost automaton that counts every violation of the environment. Note that once the environment "pays" for taking the edge  $r_1r_2$ , we go back to the initial state, resetting the specification. Similarly, if the system violates Guarantee  $G_i$ by choosing to go from  $p_1$  to  $p_2$ , it also incurs cost 1 as shown in the second automaton  $C_{G_i}$  in Figure 2.2.

Note that it is up to the user to define the cost of a violation and the state in which to continue after the specification is violated. A reset or a skip are two natural alternatives. A reset corresponds to an edge to the initial state. For a skip, we simply add a self-loop. The rightmost automaton  $C'_{G_i}$  of Figure 2.2 is an alternative cost automaton for  $G_i$  with  $i \in \{1, 2\}$ , which uses a mixture of reset and skip. For the cost automaton  $C_{G_i}$ , the word  $(r_1, \bar{g_1})(r_1, \bar{g_1})^{\omega}$  has cost 1 whereas it has cost 2 for the cost automaton  $C'_{G_i}$ . For the second automaton, the cost corresponds to the number of unanswered requests.

The costs on the edges are given by the user. For instance, the user might consider a violation of the mutual-exclusion properties  $G_3$  more severe and associate with it a higher cost than a violation of the response properties  $G_1$  or  $G_2$ .

Given cost automata  $C_{G_1}$ ,  $C_{G_2}$ , and  $C_{G_3}$  that describe the cost and the

Figure 2.2: Cost automata  $C_A$ ,  $C_{G_i}$ , and  $C'_{G_i}$  counting violations of A and  $G_i$

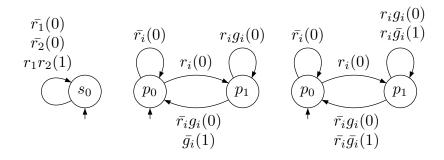

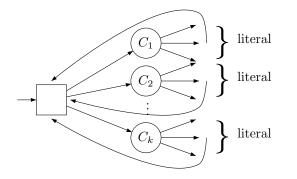

**Figure 2.3:** Automatically constructed system for  $A \to (G_1 \land G_2 \land G_3)$

behavior associated with a violation of the corresponding property, we can construct a cost automaton  $C_G = C_{G_1} + C_{G_2} + C_{G_3}$  for  $G = G_1 \wedge G_2 \wedge G_3$ . The automaton  $C_G$  defines the error function of the system. The cost automaton for the environment  $C_A$  specifies the error function of the environment. The product  $C = C_A \times C_G$  is the error specification.

Figure 2.3 shows a system M (synthesized with Lily [94]) for the specification  $A \to G$ . It is easy to see that M satisfies  $A \to G$ . As long as the environment satisfies A, which means that it does not provide  $r_1$  and  $r_2$  simultaneously, the system responds to each  $r_i$  with the corresponding  $g_i$  in the next step. However, M is not robust with respect to C: The input sequence  $i = (r_1 r_2)(\bar{r_1} r_2)^{\omega}$  has cost one, but the corresponding output  $o = (\bar{g_1}g_2)(g_1\bar{g_2})^{\omega}$  of the system has cost  $\infty$ .

Figure 2.4 shows two systems that are robust with respect to the error specification, for any word with finitely many environment errors the systems produce finitely many system errors. The first system in Figure 2.4 is 2-robust with respect to the error specification using  $C'_{G_i}$  whereas the second system in Figure 2.4 is 1-robust. For the input  $(r_1r_2)^{\omega}$  the output of the first Moore machine is  $(\bar{g_1}g_2)(\bar{g_1}\bar{g_2})^{\omega}$  and for the second it is  $(g_1\bar{g_2})^{\omega}$ .

Note that out of the three systems given above (which all satisfy  $A \to G$ ) the

Figure 2.4: A 2-robust and a 1-robust system

last system is the most robust one. In our opinion, it is also the one most likely to please the designer.

In Section 2.4.3 we show how to synthesize (strictly) realizing robust and k-robust systems from an error specification. We also show how these notions can be verified. The next section introduces Ratio games, which are crucial to our synthesis algorithms.

#### 2.4.2 Ratio Games

In this section we introduce ratio games, which we need to synthesize k-robust systems. Intuitively, a system is k-robust if the ratio of the system error to the environment error is smaller than or equal to k for every word of the system. An optimal strategy for Player 1 in a ratio game minimizes this ratio.

**Definition 8.** A ratio game<sup>2</sup> G is a tuple  $((S, s_0, E), w_1, w_2)$  consisting of a game graph  $(S, s_0, E)$  and two weight functions  $w_1, w_2 : E \to \mathbb{N}$  mapping edges to non-negative integer values. The value function for a play  $\rho = s_0 s_1 \ldots \in S^{\omega}$  is

$$v(\rho) = \lim_{m \to \infty} \limsup_{l \to \infty} \frac{\sum_{i=m}^{l} w_1(s_i, s_{i+1})}{1 + \sum_{i=m}^{l} w_2(s_i, s_{i+1})}$$

(2.1)

Ratio games are a generalization of mean payoff games. If  $w_2(e) = 1$  for all  $e \in E$ , then G is a mean payoff game. Note that the sequence of quotients for  $l \to \infty$  might diverge, which requires the use of lim sup or lim inf. We follow the definition of mean payoff games and take the lim sup. The outer-most limit ensures that only the infinite behavior is relevant as in the definition of k-robustness, i.e., if  $\sum_{i=0}^{\infty} w_1(e_i)$  is finite, then  $v(\rho) = 0$ . The addition of 1 in the denominator avoids division by zero. It does not influence the value of  $v(\rho)$ if  $\sum_{i=0}^{\infty} w_2(e_i)$  is infinite.

$<sup>^{2}</sup>$ Our graph-based ratio games should not be confused with those of [129], which represent games in a normal form, enumerating all strategies. We cannot use that representation to obtain a polynomial algorithm.

The maximal weight W in a ratio game  $((S, s_0, E), w_1, w_2)$  is defined by  $W = \max\{w_i(e) \mid e \in E, i \in \{1, 2\}\}$ . The set of possible values  $v(\rho)$  of a play  $\rho$ , where both players play positional strategies is  $V = \{0, \frac{1}{|S| \cdot W}, \dots, \frac{|S| \cdot W}{1}, \infty\}$ . Lemma 1 shows that ratio games have optimal positional strategies, which implies that it suffices to consider positional strategies and that the value of every state is in V.

#### Lemma 1. Ratio games have optimal positional strategies.

*Proof.* It suffices to show that the two one-player games  $(S_2 = \emptyset, \text{ respectively})$  $S_1 = \emptyset$  have optimal positional strategies [80]. Consider a game graph G with  $S_2 = \emptyset$ . Take in G a simple cycle with the minimum ratio r of all simple cycles. We show that the positional strategy  $\pi_1$  that goes to this simple cycle and stays within it forever is optimal. Note that the value  $v(\rho)$  of the play  $\rho$  induced by the strategy  $\pi_1$  is r, since the outer-most limit in Eq. 2.1 allows us to ignore a finite prefix of  $\rho$ .

If r = 0, the claim trivially holds. If  $r = \infty$ , then in any simple cycle the sum of the weights  $w_2$  is 0 and the sum of the weights  $w_1$  is strictly greater than 0. This implies that all edges e on cycles have weight  $w_2(e) = 0$  and in every cycle there is at least one edge e with  $w_1(e) > 0$ , and so any infinite play has ratio  $\infty$ .

For  $0 < r < \infty$ , let r be  $\frac{a}{b}$  for some integers a, b > 0 and let  $\rho'$  be an arbitrary play in the single player game. We decompose  $\rho'$  into a sequence of ratios  $\frac{a_1}{b_1}, \frac{a_2}{b_2} \dots$  by the following procedure (cf. [140]): we put the states of  $\rho'$ on a stack in the order of their appearance, once we encounter a state q that is already on the stack, we remove the sequence from the first to the second appearance of q and compute its ratio  $\frac{a_i}{b_i}$ . Note that the sum of the weights  $w_1$ and  $w_2$  in this cycle can be  $c_i$ -times larger than  $a_i$  and  $b_i$ , respectively, where  $c_i$  is some integer constant between 1 and  $W \cdot |S|$ . Note that the height of the stack is at most |S|. Due to the outer-most limit, we can ignore the part of  $\rho'$ that is always left on the stack in the computation of the value  $v(\rho')$ . Then,  $v(\rho') = \limsup_{l \to \infty} \frac{\sum_{i=1}^{l} c_i \cdot a_i}{1 + \sum_{i=1}^{l} c_i \cdot b_i}$  for some constants  $0 < c_i \le W \cdot |S|$ . Since the minimum simple-cycle ratio is  $\frac{a}{b}$ , we know that  $\frac{a_i}{b_i} \ge \frac{a}{b}$  for all i > 0 and the minimum simple-cycle ratio is  $\frac{a}{b}$ , we know that  $\frac{a_i}{b_i} \ge \frac{a}{b}$  for all i > 0 and together with the fact that  $c_i$ 's are positive integer constants, we know that  $v(\rho') \ge \limsup_{l \to \infty} \frac{\sum_{i=1}^{l} a}{1 + \sum_{i=1}^{l} b}$  and therefore  $v(\rho') \ge \frac{a}{b}$ . The proof for Player-2 games is analogous.

The decision problem of a ratio (mean payoff) game is, given a ratio r (mean payoff v) decide if the value of the game is at least r(v). The decision problem for mean payoff games is in NP  $\cap$  co-NP [140]. We show how the decision problem for ratio games can be reduced to the decision problem of mean payoff games. The reduction shows that the decision problem for ratio games is in NP  $\cap$  co-NP. We also use this reduction to calculate the values of the states in a ratio game. The reduction is similar to that used by Lawler [102] for the reduction of ratio graphs to the minimal mean cycle problem.

**Lemma 2.** Let  $G_R = ((S, s_0, E), w_1, w_2)$  be a ratio game with maximal weight W. Given a ratio  $\frac{a}{b}$  with  $0 \le a \le |S| \cdot W$  and  $0 < b \le |S| \cdot W$ , we can decide whether a state has value  $v = \frac{a}{b}$ ,  $v < \frac{a}{b}$ , or  $v > \frac{a}{b}$  in  $O(|S|^3 \cdot W^2 \cdot |E|)$  time.

*Proof.* We reduce the decision for the ratio game to a decision for the mean payoff game  $G_{\rm MP} = ((S, s_0, E), w)$  with payoff function  $w(e) = b \cdot w_1(e) - a \cdot w_2(e)$ . In the following, let  $v_{\rm R} (v_{\rm R}(\rho))$  be the value (of run  $\rho$ ) in  $G_{\rm R}$  and similarly for  $v_{\rm MP}$ .

We show that  $v_{\rm R} \leq \frac{a}{b}$  implies  $v_{\rm MP} \leq 0$  and  $v_{\rm R} \geq \frac{a}{b}$  implies  $v_{\rm MP} \geq 0$ . The decision whether  $v_{\rm MP} < 0$ ,  $v_{\rm MP} = 0$ , or  $v_{\rm MP} > 0$  can be made in  $O(|S|^2 \cdot W' \cdot |E|)$  time, where W' is the maximal weight in the mean payoff game [140]. We have  $W' \leq b \cdot W \leq |S| \cdot W^2$ , thus the decision for the ratio game can be made in  $O(|S|^3 \cdot W^2 \cdot |E|)$  time.

Suppose  $v_{\rm R} \leq \frac{a}{b}$ . We show that Player 1 can achieve a run of value at most 0 in  $G_{\rm MP}$  and thus  $v_{\rm MP} \leq 0$ . Let  $\pi_1$  be a positional optimal Player-1 strategy for  $G_{\rm R}$  and let  $\pi_2$  be a positional optimal strategy for Player 2 in  $G_{\rm MP}$ . Because both strategies are positional,  $\rho(s_0, \pi_1, \pi_2)$  consists of a stem and a simple cycle, say  $\rho = (e'_1, \ldots, e'_m) \cdot (e_1, \ldots, e_n)^{\omega}$ . Note that

$$v_{\rm R}(\rho) = \frac{\sum_{i=0}^{n} w_1(e_i)}{\sum_{i=0}^{n} w_2(e_i)} \text{ and } v_{\rm MP}(\rho) = \frac{b \sum_{i=0}^{n} w_1(e_i) - a \sum_{i=0}^{n} w_2(e_i)}{n}$$

Suppose  $\sum_{i=0}^{n} w_1(e_i) > 0$ , then, since  $v_{\rm R} \leq \frac{a}{b}$  and is thus finite, we have  $\sum_{i=0}^{n} w_2(e_i) > 0$ . It follows that

$$\frac{\sum_{i=0}^{n} w_1(e_i)}{\sum_{i=0}^{n} w_2(e_i)} \le \frac{a}{b} \text{ implies } \frac{b \sum_{i=0}^{n} w_1(e_i) - a \sum_{i=0}^{n} w_2(e_i)}{n} \le 0.$$

If  $\sum_{i=0}^{n} w_1(e_i) = 0$ , then

$$\frac{b\sum_{i=0}^{n} w_1(e_i) - a\sum_{i=0}^{n} w_2(e_i)}{n} = \frac{-(a\sum_{i=0}^{n} w_2(e_i))}{n} \le 0.$$

The proof that  $v_{\rm R} \geq \frac{a}{b}$  implies that  $v_{\rm MP} \geq 0$  is similar, using an optimal strategy for Player 2 in  $G_{\rm R}$ .

**Theorem 3.** Given a ratio game  $((S, E), w_1, w_2)$  with maximal weight W, the value for every  $s \in S$  can be computed in  $O(|S|^3 \cdot W^2 \cdot |E| \cdot \log(|S| \cdot W))$ .

*Proof.* We use the decision procedure from Lemma 2 to perform a binary search on the list of possible values  $V \setminus \{\infty\}$ . If the ratio is greater than  $|S| \cdot W$ , it is infinite. There are less than  $(|S| \cdot W)^2$  different ratios, thus we need at most  $2 \cdot \log(|S| \cdot W)$  calls to the decision procedure.

Given an algorithm to find the values of the game we can use the "group testing" technique from [140] to find optimal positional strategies.

**Theorem 4.** Given a ratio game  $((S, E), w_1, w_2)$  with maximal weight W, positional optimal strategies for both players can be found in  $O(|S|^4 \cdot \log(\frac{|E|}{|S|}) \cdot |E| \cdot \log(|S| \cdot W) \cdot W^2)$ .