# Low-Cost Side-Channel Analysis and Fault Analysis Setups and Their Application Targeting Secured ASICs

by

Thomas Korak

A PhD Thesis Presented to the Faculty of Computer Science in Partial Fulfillment of the Requirements for the PhD Degree

Assessors

Prof. Stefan Mangard (TU Graz, Austria) Prof. Tim Güneysu (University of Bremen, Germany)

October 2015

Institute for Applied Information Processing and Communications (IAIK) Faculty of Computer Science Graz University of Technology, Austria

### Abstract

Physical attacks aim at revealing secret data that is processed by an electronic device by observing side-channel information such as the power consumption or by intentionally injecting faults during a critical computation. A wide range of electronic devices is vulnerable to this kind of attack. However, literature published in this field often lacks clear statements whether the presented attacks can be performed by applying off-the-shelf, low-cost equipment or if specialized tools are required.

With this work we aim at demonstrating the power of measurement setups enabling physical attacks, built-up with off-the-shelf, low-cost equipment exclusively. Attacks which can be conducted with such setups pose a serious threat as they can be performed by a wide range of attackers. They are therefore more likely to lead to real-world exploits than attacks which require highly specialized equipment that is hard to obtain.

The main contribution consists in verifying the functionality of the low-cost setups by performing exemplary side-channel analysis (SCA) and fault analysis (FA) attacks. The attacked devices include chips providing authentication services for radio-frequency identification (RFID) systems, microcontrollers for sensor nodes, and application-specific integrated circuits (ASICs) implementing cryptographic algorithms. When targeting RFID systems, we show that keyrecovery attacks can be mounted at a distance of up to one meter with low-cost equipment, posing a serious threat for real-world systems. In addition, we are the first to present SCA-attack results targeting an SCA-protected, keyed KECCAK instance implemented on a taped-out ASIC. The results show that the proposed secret-sharing countermeasure applied on low-resource devices does not lead to a sufficient protection level when keeping in mind the immense overhead in terms of area and runtime. We further study the influence of setup parameters (laser pulse length, laser power, and laser focus) on the success of invasive, optical fault injections. The parameters have to be chosen with great care for a successful, reproducible fault injection. Our non-invasive, low-cost fault injection setup proved to be an effective tool for disturbing the correct operation of a wide range of microcontrollers frequently applied for sensor-node applications.

The results presented in this thesis clearly show that the power of low-cost setups for SCA attacks and FA attacks must not be underestimated. These attacks pose a serious threat for electronic devices executing security-relevant applications and have to be considered already in the early design phase.

## Acknowledgements

I would like to thank all people who supported me during the last years. Special thanks to all former and current colleagues at IAIK. It was always interesting to do joint research leading to this thesis and have some fruitful discussions during the coffee breaks. Special thanks to my former colleague Thomas Plos for his great support during my PhD start. I also want to thank my former group leader Jörn-Marc Schmidt and my current group leader Stefan Mangard for their support during the PhD thesis.

I would also like to thank all the coauthors and all the partners who have contributed in some way to my work.

I would also like to thank my assessors, Stefan Mangard and Tim Güneysu for their reviews and detailed comments leading to the final version of this thesis.

Finally and most importantly, I would like to thank my family and my friends for their great support during my studies. Especially my parents endorsed me in every situation, they always found the motivating words.

> Thomas Korak Graz, October 2015

# Table of Contents

| $\mathbf{A}$ | bstra                     | $\mathbf{ct}$                                          |                                               | iii                                                     |

|--------------|---------------------------|--------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------|

| A            | ckno                      | wledge                                                 | ements                                        | $\mathbf{v}$                                            |

| Li           | st of                     | Table                                                  | S                                             | xi                                                      |

| Li           | st of                     | Figur                                                  | es                                            | xiii                                                    |

| A            | crony                     | $\mathbf{yms}$                                         |                                               | xiv                                                     |

| 1            | <b>Intr</b><br>1.1<br>1.2 | roducti<br>Motiva<br>Contri<br>1.2.1<br>1.2.2<br>1.2.3 |                                               | $egin{array}{c} 1 \\ 2 \\ 4 \\ 5 \\ 6 \\ 7 \end{array}$ |

| <b>2</b>     | SCA                       | <b>A-A</b> tta                                         | cks Targeting Contactless Devices             | 9                                                       |

|              | 2.1                       | Introd                                                 | luction                                       | 10                                                      |

|              | 2.2                       | Prelin                                                 | ninaries                                      | 11                                                      |

|              |                           | 2.2.1                                                  | CRYPTA ASIC                                   | 11                                                      |

|              |                           | 2.2.2                                                  | Parasitic Load Modulation                     | 13                                                      |

|              |                           | 2.2.3                                                  | Resolution Optimization                       | 14                                                      |

|              |                           | 2.2.4                                                  | Analogue Demodulation Approach                | 16                                                      |

|              | 2.3                       | -                                                      | arison of Measurement Approaches              | 16                                                      |

|              |                           | 2.3.1                                                  | Measurement Setup                             | 17                                                      |

|              |                           | 2.3.2                                                  | Profiling for Resolution Optimization         | 18                                                      |

|              | ~ .                       | 2.3.3                                                  | Results of the Comparison                     | 18                                                      |

|              | 2.4                       |                                                        | te SCA Attacks                                | 20                                                      |

|              |                           | 2.4.1                                                  | Measurement Setup and Post Processing         | 21                                                      |

|              |                           | 2.4.2                                                  | Verification of the Parasitic Load Modulation | 23                                                      |

|              |                           | 2.4.3                                                  | Remote SCA-Attack Results                     | 24                                                      |

|              | 0 F                       | 2.4.4                                                  | Discussion of the Results                     | 26                                                      |

|              | 2.5                       |                                                        | proximity Measurements                        | $27 \\ 28$                                              |

|              |                           | $2.5.1 \\ 2.5.2$                                       | Comparison of ASIC and FPGA version           | 28<br>28                                                |

|              | 2.6                       |                                                        | ssion                                         | $\frac{20}{30}$                                         |

|              | 2.0                       | Discus                                                 |                                               | - <b>J</b> U                                            |

| 3 | $\mathbf{SC}$ | A-Attacks Targeting Sensor Nodes                                | 33 |

|---|---------------|-----------------------------------------------------------------|----|

|   | 3.1           | Introduction                                                    | 34 |

|   | 3.2           | Non-Invasive Location-dependent EM measurements                 | 36 |

|   |               | 3.2.1 Used Microcontroller                                      | 36 |

|   |               | 3.2.2 AES Implementations                                       | 37 |

|   |               | 3.2.3 Measurement Setup                                         | 37 |

|   |               | 3.2.4 Evaluation Metric                                         | 38 |

|   |               | 3.2.5 Location-Dependent SCA-Attack Results                     | 40 |

|   | 3.3           | Semi-Invasive High-Resolution EM Measurements                   | 41 |

|   |               | 3.3.1 <i>TAMPRES</i> ASIC Introduction                          | 42 |

|   |               | 3.3.2 Measurement Setup                                         | 43 |

|   | 3.4           | Semi-invasive SCA-Attack Results                                | 44 |

|   |               | 3.4.1 AES Hardware Module                                       | 44 |

|   |               | 3.4.2 LRPRF Hardware Module                                     | 47 |

|   | 3.5           | Discussion                                                      | 49 |

|   | ~~            |                                                                 |    |

| 4 |               | A Attacks Targeting a Crypto ASIC                               | 53 |

|   | 4.1           | Introduction                                                    | 54 |

|   | 4.2           | Preliminaries                                                   | 56 |

|   |               | 4.2.1 KECCAK                                                    | 56 |

|   |               | 4.2.2 SPONGEWRAP                                                | 57 |

|   | 4.0           | 4.2.3 Higher-order DPA Attacks                                  | 57 |

|   | 4.3           | The Attacked ASIC ZORRO                                         | 58 |

|   | 4.4           | SCA-Attack Setting                                              | 60 |

|   |               | 4.4.1 Evaluation Metric                                         | 62 |

|   |               | 4.4.2 Measurement Setup                                         | 63 |

|   | 4.5           | SCA-Attack Results                                              | 63 |

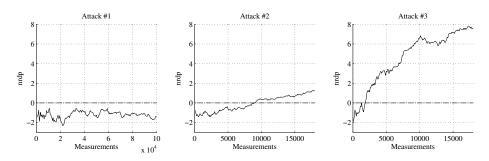

|   |               | 4.5.1 DPA Attacks Targeting ZORRO in NM                         | 63 |

|   |               | 4.5.2 HO-DPA Attacks Targeting ZORRO in MM                      | 63 |

|   |               | 4.5.3 DPA-Attacks Targeting ZORRO in HM                         | 65 |

|   |               | 4.5.4 Summary of Hiding and Masking Applied Independently .     | 65 |

|   | 1.0           | 4.5.5 Security Approximation for ZORRO in SMM                   | 66 |

|   | 4.6           | Discussion                                                      | 69 |

| 5 | No            | n-Invasive Fault Attacks                                        | 71 |

| 0 | 5.1           |                                                                 | 72 |

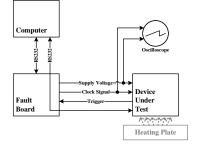

|   | 5.2           | Fault Injection Environment                                     | 74 |

|   | 0.2           | 5.2.1 Custom-made Fault Board                                   | 74 |

|   |               | 5.2.2 Extension Boards                                          | 75 |

|   |               | 5.2.3 Heating Equipment                                         | 78 |

|   | 5.3           | Experiment Description                                          | 78 |

|   | 0.0           | 5.3.1 Fault-Injection Impact on Different Microcontroller Plat- | 10 |

|   |               | forms                                                           | 79 |

|   |               | 5.3.2 Combination of Fault Injection Methods                    | 80 |

|   | 5.4           | Experiment Results                                              | 82 |

|   |               | · · · · · · · · · · · · · · · · · · ·                           |    |

|   |     | 5.4.1   | Fault-Injection Impact on Different Microcontroller Plat-<br>forms                                | 82  |

|---|-----|---------|---------------------------------------------------------------------------------------------------|-----|

|   |     | 5.4.2   | forms                                                                                             |     |

|   | 5.5 | 0       | ssion                                                                                             |     |

|   | 0.0 | Discus  | 551011                                                                                            | 91  |

| 6 | Sen |         | sive Fault Attacks                                                                                | 93  |

|   | 6.1 | Introd  | luction                                                                                           | 94  |

|   | 6.2 | Optica  | al Fault-Injection Attacks                                                                        | 95  |

|   |     | 6.2.1   | Influence of Light Irradiation on Memory Cells                                                    |     |

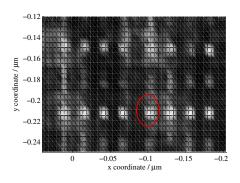

|   |     | 6.2.2   | Finding Optical Sensitive Spots                                                                   | 97  |

|   | 6.3 | Fault   | Injection Environment                                                                             |     |

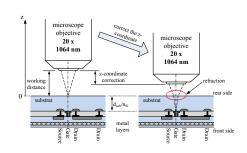

|   |     | 6.3.1   | Optical Equipment                                                                                 |     |

|   |     | 6.3.2   | Stepper Table                                                                                     | 99  |

|   |     | 6.3.3   | Oscilloscope and Control Computer                                                                 | 99  |

|   |     | 6.3.4   | Custom-made Fault Board                                                                           | 99  |

|   |     | 6.3.5   | Devices Under Test (DUT)                                                                          | 100 |

|   | 6.4 | Exper   | iment Description                                                                                 | 100 |

|   |     | 6.4.1   | Front-side Experiments                                                                            | 100 |

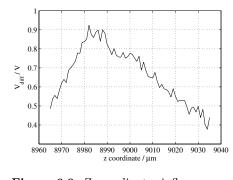

|   |     | 6.4.2   | Rear-side Experiments                                                                             | 101 |

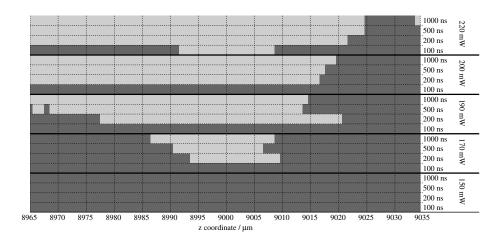

|   | 6.5 | Exper   | iment Results                                                                                     | 102 |

|   |     | 6.5.1   | Front-side Experiments                                                                            | 102 |

|   |     | 6.5.2   | Rear-side Experiments                                                                             | 104 |

|   | 6.6 | Discus  | ssion                                                                                             | 107 |

| 7 | Act | ive Re  | elay Attacks                                                                                      | 109 |

|   | 7.1 | Introd  | luction $\ldots$ | 110 |

|   | 7.2 | Prelin  | ninaries                                                                                          | 111 |

|   |     | 7.2.1   | The ISO/IEC 14443 Timing Constraints                                                              | 111 |

|   |     | 7.2.2   | Relay using NFC-Enabled Smart Phones                                                              | 112 |

|   |     | 7.2.3   | Relay using Custom Proxy/Mole                                                                     |     |

|   |     | 7.2.4   | Related Work                                                                                      | 114 |

|   |     | 7.2.5   | Terminology                                                                                       |     |

|   | 7.3 | Attacl  | k Scenarios and Used Setups                                                                       | 116 |

|   |     | 7.3.1   | Relaying an AES Authentication Process                                                            | 116 |

|   |     | 7.3.2   | The "Phones-in-the-middle" Attack                                                                 | 117 |

|   |     | 7.3.3   | A Custom Relay Proxy                                                                              | 119 |

|   | 7.4 | Result  | ūs                                                                                                | 121 |

|   |     | 7.4.1   | "Phones-in-the-middle"                                                                            | 121 |

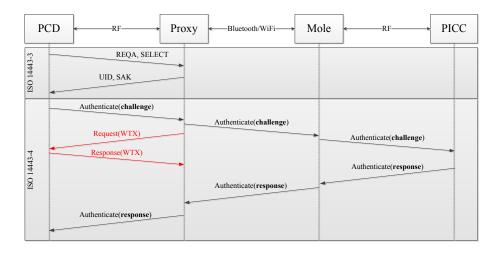

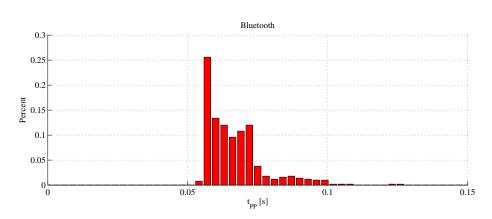

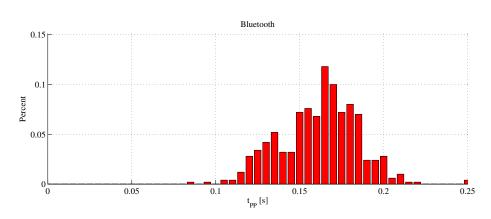

|   |     | 7.4.2   | Bluetooth vs. WLAN                                                                                | 123 |

|   |     | 7.4.3   | Custom Relay Proxy                                                                                | 124 |

|   | 7.5 | Concl   | usion                                                                                             | 125 |

| 8 | Con | nclusio | ns                                                                                                | 127 |

| 9 | Abo | out the | e Author                                                                                          | 131 |

Bibliography

$\mathbf{135}$

# List of Tables

| 2.1 | Analogue demodulation circuit: Input voltage and correlation val- |     |

|-----|-------------------------------------------------------------------|-----|

|     | ues                                                               | 20  |

| 2.2 | Relation: $U_{pp}$ and angle for $d = 30  cm$ .                   | 23  |

| 2.3 | SCA-attack results for the analyzed distances                     | 27  |

| 3.1 | Localized EM measurements, DPA results                            | 42  |

| 3.2 | Nr of measurements for SCA on TAMPRES AES                         | 45  |

| 4.1 | DPA attack results: ZORRO                                         | 65  |

| 4.2 | ZORRO countermeasure comparison                                   | 66  |

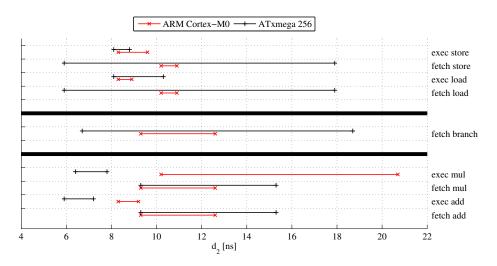

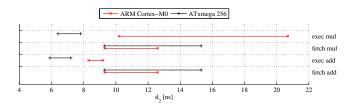

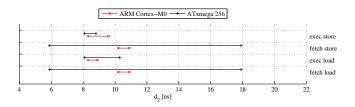

| 5.1 | Examined instructions                                             | 79  |

| 5.2 | Parameter set for fault injection.                                | 82  |

| 7.1 | Overview of different relay-attack setups.                        | 115 |

| 7.2 | Comparison Bluetooth and WiFi as relay channel.                   | 123 |

| 7.3 | Results of custom-made proxy.                                     | 125 |

# List of Figures

| 2.1  | Architecture of the evaluated chip.                                                              | 12 |

|------|--------------------------------------------------------------------------------------------------|----|

| 2.2  | The development board with the evaluated chip                                                    | 12 |

| 2.3  | The CRYPTA ASIC-chip.                                                                            | 13 |

| 2.4  | IAIK demotag                                                                                     | 13 |

| 2.5  | Inductive coupling between reader and tag antenna                                                | 15 |

| 2.6  | Resolution enhancement of EM measurements                                                        | 15 |

| 2.7  | Analogue demodulation circuit.                                                                   | 16 |

| 2.8  | Profiling for resolution optimization.                                                           | 17 |

| 2.9  | Relation: correlation and window positions.                                                      | 19 |

| 2.10 | Comparison of the measurement approaches                                                         | 20 |

| 2.11 | Remote SCA attacks - measurement setup                                                           | 21 |

| 2.12 | Internal authenticate sequence.                                                                  | 21 |

| 2.13 | Measurement setup 100 cm.                                                                        | 22 |

| 2.14 | $U_{pp} = f(d).$                                                                                 | 23 |

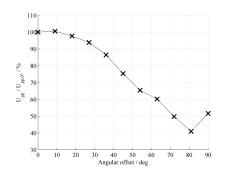

| 2.15 | $U_{pp} = f(angular  offset). \dots \dots$ | 23 |

| 2.16 | DPA-attack result with opened chip housing                                                       | 24 |

| 2.17 | DPA-attack result with closed chip housing.                                                      | 24 |

| 2.18 | Relation: Correlation and window size.                                                           | 25 |

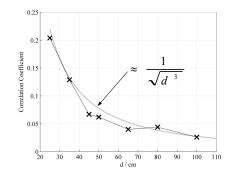

| 2.19 | Relation: Correlation and distance.                                                              | 25 |

| 2.20 | DPA attack results                                                                               | 29 |

| 3.1  | The attacked microcontroller.                                                                    | 37 |

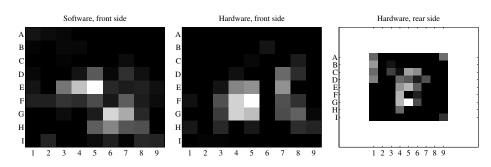

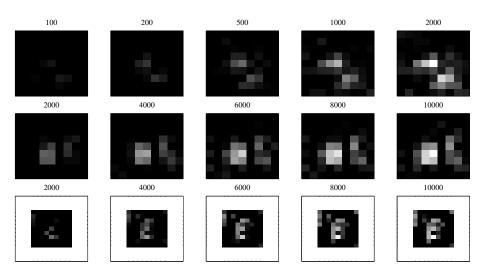

| 3.2  | EM leakage landscapes                                                                            | 40 |

| 3.3  | EM leakage evolution                                                                             | 41 |

| 3.4  | TAMPRES ASIC architecture                                                                        | 43 |

| 3.5  | High-resolution EM measurement setup.                                                            | 44 |

| 3.6  | AES hardware module location.                                                                    | 45 |

| 3.7  | Power Model Profiling                                                                            | 46 |

| 3.8  | AES SBox characterization                                                                        | 47 |

| 3.9  | LRPRF Sbox characterization                                                                      | 50 |

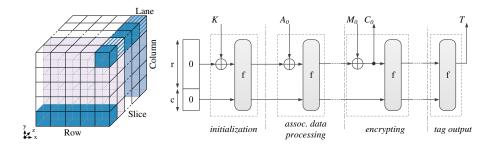

| 4.1  | Keccak state                                                                                     | 56 |

| 4.2  | The SpongeWrap construction.                                                                     | 56 |

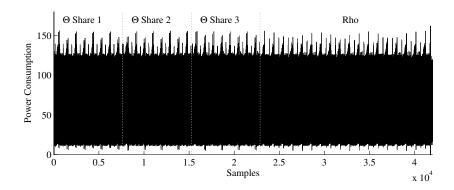

| 4.3  | Power trace MM-3                                                                                 | 64 |

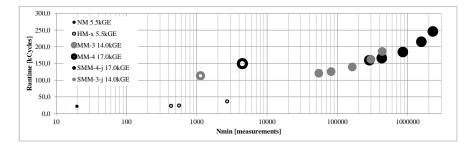

| 4.4  | Runtime/ $N_{min}$ comparison of ZORRO                                                           | 68 |

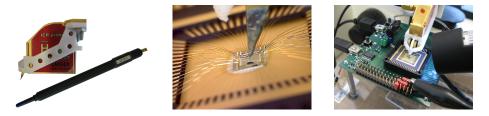

| 5.1  | Parts of the fault-injection setup.                            | 74  |

|------|----------------------------------------------------------------|-----|

| 5.2  | Block diagram of the fault-injection setup.                    | 74  |

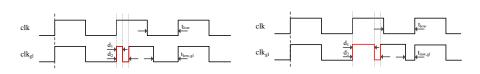

| 5.3  | Clock-glitch generation - small $d_1$                          | 75  |

| 5.4  | Clock-glitch generation - large $d_1$                          | 75  |

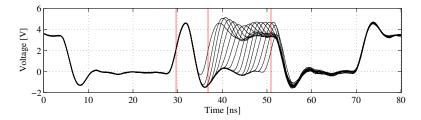

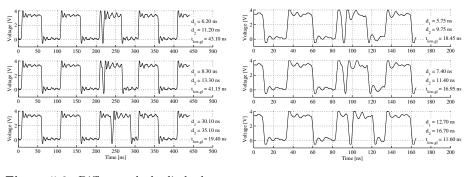

| 5.5  | Clock signals: $8ns \ge d_2 \ge 22ns$                          | 76  |

| 5.6  | Experimental setup.                                            | 76  |

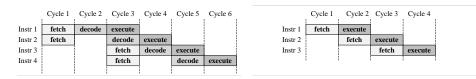

| 5.7  | ARM Cortex-M0 instruction execution procedure                  | 77  |

| 5.8  | ATxmega 256 instruction execution procedure.                   | 77  |

| 5.9  | Different clock-glitch shapes for 10 MHz.                      | 81  |

| 5.10 | Different clock-glitch shapes for 20 MHz.                      | 81  |

| 5.11 | Result summary non-invasive fault injection                    | 83  |

| 5.12 | Clock glitch and underpowering.                                | 88  |

| 5.13 | Faults generated for add R16, R5, $f_{clk} = 10MHz$            | 89  |

| 5.14 | Faults generated for add R16,R5, $f_{clk} = 20MHz$ .           | 89  |

| 5.15 | A simple synchronous circuit.                                  | 90  |

| 5.16 | Timing diagram.                                                | 90  |

| 0.10 |                                                                | 00  |

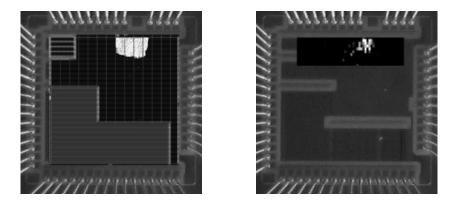

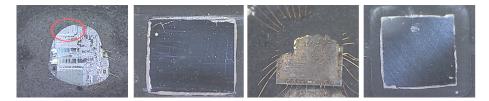

| 6.1  | Exposed microcontrollers.                                      | 95  |

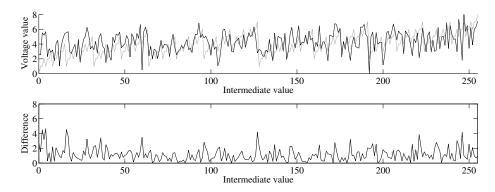

| 6.2  | Architecture of an SRAM cell                                   | 96  |

| 6.3  | Voltage measurements                                           | 96  |

| 6.4  | Schematic of the laser diode driver circuit.                   | 98  |

| 6.5  | Optical fault injection setup                                  | 100 |

| 6.6  | Z-coordinate correction.                                       | 100 |

| 6.7  | Parameter influence, PIC 16F84 front side                      | 103 |

| 6.8  | Laser sensitivity scan, PIC 16F84 front side.                  | 104 |

| 6.9  | Z-coordinate influence, PIC 16F84 front side                   | 104 |

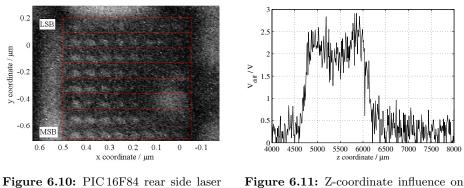

| 6.10 | Laser sensitivity scan, PIC 16F84 rear side.                   | 105 |

| 6.11 | Z-coordinate influence, PIC 16F84 rear side.                   | 105 |

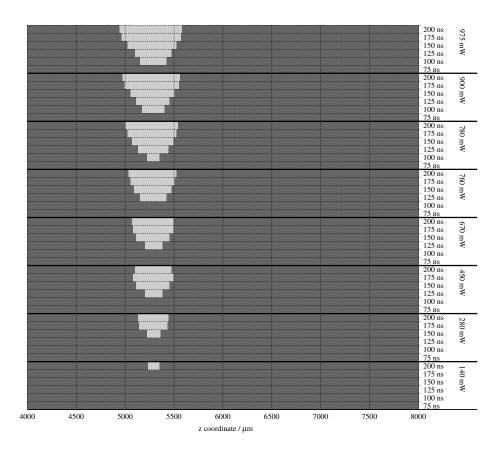

| 6.12 | Parameter influence, PIC 16F84 rear side                       | 106 |

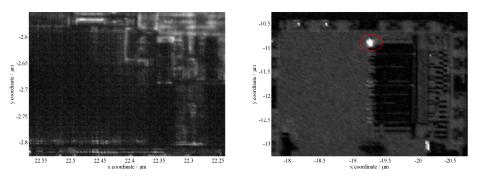

| 6.13 | ATmega 162/v front side laser sensitivity plot                 | 107 |

| 6.14 | ATmega 162/v rear side laser sensitivity plot.                 | 107 |

|      |                                                                |     |

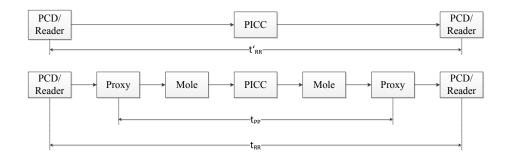

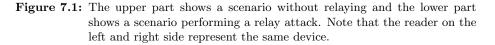

| 7.1  | Communication without and with relay attack.                   | 116 |

| 7.2  | Relay communication flow during an AES authentication process. | 118 |

| 7.3  | The custom made proxy                                          | 120 |

| 7.4  | Result: Smart phone and Bluetooth as relay channel             | 122 |

| 7.5  | Result: Smart phone and WiFi as relay channel                  | 122 |

| 7.6  | Comparison: Two vs. three smart phones                         | 123 |

| 7.7  | Result using custom-made proxy.                                | 124 |

# Acronyms

| AE                     | Authenticated Encryption                  |

|------------------------|-------------------------------------------|

| AES                    | Advanced Encryption Standard              |

| AFE                    | Analog Front-End                          |

| AP                     | Access Point                              |

| APDU                   | Application Protocol Data Unit            |

| API                    | Application Programming Interface         |

| ASIC                   | Application-Specific Integrated Circuit   |

| CAESAR                 | Competition for Authenticated Encryption: |

|                        | Security, Applicability, and Robustness   |

| CED                    | Concurrent Error Detection                |

| CEMA                   | Correlation Electromagnetic Analysis      |

| CMOS                   | Complementary Metal-Oxide Semiconductor   |

| CPA                    | Correlation Power Analysis                |

| CPU                    | Central Processing Unit                   |

| CRC                    | Cyclic Redundancy Check                   |

| CRYPTA                 | Cryptographically Protected Tag           |

| DCM                    | Digital Clock Manager                     |

| DEMA                   | Differential Electromagnetic Analysis     |

| DES                    | Data Encryption Standard                  |

| DPA                    | Differential Power Analysis               |

| DST                    | Digital Signature Transponder             |

| DUT                    | Device Under Test                         |

| ECC                    | Elliptic Curve Cryptography               |

| $\mathbf{E}\mathbf{M}$ | Electromagnetic                           |

| FA                     | Fault Analysis                            |

| FDT                    | Frame Delay Time                          |

| FET                    | Field-Effect Transistor                   |

| FWT                    | Frame Waiting Time                        |

| FIB                    | Focused Ion Beam                          |

| FPGA                   | Field-Programmable Gate Array             |

| GE                     | Gate Equivalent                           |

| HDL                    | Hardware Description Language             |

| $_{ m HF}$             | High Frequency                            |

| IC                     | Integrated Circuit                        |

| IV                     | Intermediate Value                        |

| IoT                    | Internet of Things                        |

|                        | Ŭ                                         |

| ISO                  | international Organization for Standardization |

|----------------------|------------------------------------------------|

| LIVA                 | Light-Induced Voltage Alteration               |

| LSB                  | Least Significant Bit                          |

| LSI                  | Large Scale Integration                        |

| LRPRF                | Leakage-Resilient Pseudo-Random Function       |

| MAC                  | Message Authentication Code                    |

| MCU                  | Microcontroller Unit                           |

| MSB                  | Most Significant Bit                           |

| NIST                 | National Institute of Standards and Technology |

| NFC                  | Near-Field Communication                       |

| nrdp                 | Nearest-Rival Distinguishing Power             |

| PCB                  | Printed Circuit Board                          |

| PCD                  | Proximity Coupling Device                      |

| PICC                 | Proximity Integrated Circuit Card              |

| PTV                  | Process, Temperature, and Voltage              |

| RAM                  | Random-Access Memory                           |

| $\mathbf{RF}$        | Radio Frequency                                |

| RFID                 | Radio-Frequency Identification                 |

| RSA                  | Rivest, Shamir, and Adleman                    |

| SCA                  | Side-Channel Analysis                          |

| SHA                  | Secure Hash Algorithm                          |

| $\operatorname{SNR}$ | Signal-to-Noise Ratio                          |

| SRAM                 | Static Random-Access Memory                    |

| TAMPRES              | Tamper Resistant Sensor Nodes                  |

| TI                   | Texas Instruments                              |

| UART                 | Universal Asynchronous Receiver Transmitter    |

| UHF                  | Ultra-High Frequency                           |

| UID                  | Used Identification                            |

| USB                  | Universal Serial Bus                           |

| UV                   | Ultraviolet                                    |

| WSN                  | Wireless Sensor Network                        |

| WTX                  | Waiting Time Extension                         |

# Introduction

The amount of data shared and transmitted between mobile devices has grown rapidly during the last decade. It is a fact that the majority of digital media consumption now takes place on mobile devices. Since 2014 the number of mobile Internet users exceeds the number of the traditional desktop Internet users and the gap is likely to grow in future [29]. Also other new technologies like Radio Frequency Identification (RFID) systems, contactless smartcards based on Near-Field Communication (NFC), or wireless sensor nodes distributing their measurement data, contribute to the growth of transmitted data. Besides the convenience, the trend to mobile Internet usage and the penetration of new technologies in our everyday life also poses several challenges. One of these challenges is the secure handling of data. The majority of data is sent over insecure channels allowing non-authorized parties to eavesdrop, modify, or redirect a communication of potentially confidential data. In order to prevent this, sender and receiver of confidential data have to put security measures in place. The goal of these measures is to provide confidentiality, integrity and authenticity of the transmitted data. A wide range of cryptosystems are available to realize these properties. Following Kerckhoffs's principle, all information of the cryptosystem is typically public knowledge and only the key is kept secret by the communication partners. So a main asset in cryptosystems is the secrecy of the private key. Hence an attacker should not be able to gain information about the private key used during a communication. To ensure this, different attacks have to be considered during the design and in particular the implementation of a cryptosystem. In fact, attacks often target weaknesses in the implementation of cryptographic algorithms and can be grouped into logical and physical attacks.

Logical attacks assume that an attacker can use the existing communication interface of a device to mount an attack. Software vulnerabilities, security APIs, or test and debug interfaces can be used for performing logical attacks [25, 88]. A wide range of logical attacks can also be mounted remotely.

If an attacker has physical access to the attacked device for some time, physical attacks become feasible. The goal of a physical attack is to reveal the secret key or other relevant, secret information, by observing and measuring side-channel information during the execution of the cryptographic algorithm. These side-channel information can for example be the power consumption, the electromagnetic emanation, or the timing behavior. Whenever the side-channel information is correlated with some secret values processed inside the device, we speak of exploitable leakage of secret information through the side channel. Examples are key-dependent power consumption or key-dependent runtime of the algorithm. In this case an analysis of the side-channel measurements allows to extract the value of the secret key or narrow down the search space for a brute-force attack. In addition to passively measuring side-channel information, the physical access also allows to actively manipulate the device to force erroneous computations. Analyzing the erroneous output allows to gain additional knowledge about internal data. This knowledge about internal data can assist in revealing the secret key. Active manipulations can be achieved in a non-invasive, semi-invasive, or invasive manner. In non-invasive scenarios, no modification of the attacked device is required, examples are tampering with the ambient temperature or the clock signal. Semi-invasive and invasive scenarios require a modification of the attacked device. This modification often consists of a decapsulation step to access the chip die. Semi-invasive attacks do not contact or modify the inner chip structure (e.g., optical fault injections). Invasive attacks require contact or modification of the inner chip structure what can be done with probing cards or focused ion-beam (FIB) stations. Publications in the past 15 years have shown that the full range of electronic devices can be vulnerable to physical attacks. Examples are notebooks [45], smart phones [133], smart cards [91], and contactless chip cards based on the radio-frequency identification (RFID) and near-field communication (NFC) technology [106].

#### 1.1 Motivation

In general, physical attacks are always successful if an attacker is equipped with sufficient resources (money, time, expertise, ...). In practice, the main goal is to make attacks so hard that the effort exceeds the profit for the attack. As a result, attacks requiring only a limited amount of resources have to be considered. Many attacks published in the past lack the clear statement regarding the applicability in case of a budget-limited attacker (One exception is e.g. [65]). In this work we present a wide range of low-cost setups enabling physical attacks to showcase the power of budget-limited attackers. We target different devices, all exposed to physical attacks due to their fields of application. Among these devices are RFID and NFC tags, microcontrollers for sensor nodes, and application-specific integrated circuits (ASICs) implementing state-of-the-art cryptographic algorithms. The fact if a setup can be categorized as low-cost depends on sev-

eral factors. The first and most important factor is that all parts required for the setup are off-the-shelf parts and can be bought by everybody. For some custom-made equipment no mass market exists, leading to limited availability and high costs, what leads to the second factor. The price of all devices included in the setup represents the second factor. It is influenced by the budget of the attacker. We upper-bound the equipment costs with 40000 EUR. The value of  $40\,000\,\mathrm{EUR}$  has been chosen because this value reflects the maximum costs for the equipment we have used during our research. The devices with the biggest influence on the costs are a high-end oscilloscope ('LeCroy WP 725 Zi', approx. 20000 EUR), a fully-automated three axes stepper table ('Marzhauser SCAN 75x50', approx. 15000 EUR), and a microscope ('Zeiss AxioScope 40A', approx. 5000 EUR). Note that not all attacks presented in this thesis require all the previously mentioned equipment. For most measurements, e.g. a cheaper oscilloscope ('PicoScope 6404c', approx. 5000 EUR) is sufficient. Therefore the value of 40 000 EUR is only given as an upper bound. The costs for most of the attacks presented in this thesis are significantly below that bound.

Next we want to shortly discuss two factors, which significantly influence the equipment costs for physical attacks. These factors are the type of physical attack and the countermeasures implemented on the attacked device to make it harder for an attacker to succeed with a physical attack.

1. **Type of physical attack:** The first factor affecting the equipment costs is the type of the physical attack. Physical attacks can be classified into *side-channel analysis (SCA) attacks* and *fault analysis (FA) attacks* on the highest level.

SCA attacks are passive, which means that they only observe the device while performing the cryptographic computation under normal conditions. Popular side-channels are the power consumption, the electromagnetic (EM) emanation or the timing behavior. The required equipment and its costs depend on the properties of the device. The amount of leakage incorporated in the measurements dictates the required performance of the measurement devices, e.g. the oscilloscope. In case of EM attacks, the measurement location and resolution also influence the equipment cost. High-resolution measurements typically increase the success probability for the attack, but also require more expensive and specialized EM probes. Timing measurements can typically be performed with lower effort. The runtime of a cryptographic algorithm on most devices can be measured by observing the power consumption, the EM emanation, the communication interface, or some external pins.

FA attacks, on the other hand, actively influence the operating conditions of the attacked device to force some erroneous behavior. Popular means for causing errors in non-invasive FA scenarios are modifications of the clock frequency, the power supply or the temperature. Semi-invasive fault attacks require modifications of the attacked device, e.g. decapsulation to access the inner structure. In contrast to invasive fault attacks, semi-invasive fault attacks do not require direct contact to the inner structure. Optical attacks using laser beams can be categorized as semi-invasive attacks. Microprobing can be categorized as invasive attack. Both, the equipment costs and also the power of the attack increase from non-invasive to invasive.

2. Implemented countermeasures: Next to the type of the attack, also the implemented countermeasures on the targeted device can have a significant influence on the costs of the required equipment. Here we have to differ between countermeasures against SCA attacks and FA attacks.

Hiding and masking techniques are popular countermeasures to harden devices against SCA attacks [86]. Successful SCA attacks targeting devices secured by one of the aforementioned countermeasures typically require a significantly higher amount of measurements compared to their unprotected counterpart. Next to that, the observation time for every single measurement increases in many cases because of the longer runtime of the algorithm caused by the countermeasure. To handle this increased effort the measurement setup can be improved by using e.g. oscilloscopes providing higher performance.

To harden a device against fault attacks, Concurrent Error Detection (CED) schemes have been developed. An overview of the most-common CED schemes is given in [148]. CED can be realized by performing the critical calculation twice and the final result is only returned if the results of both calculations are identical. The two calculations can be performed in parallel (hardware redundancy) or one after the other (time redundancy). If the targeted device is protected by a CED scheme, one option for a successful FA attack is to inject a similar fault twice. This requirement has a significant impact on the required equipment. In case of optical fault injections, one might require two accurately positionable laser beams. This requirement significantly increases the equipment costs. If such an equipment is not available, safe-error attacks [149] are a second option for conducting successful FA attacks targeting devices protected by a CED scheme.

Other countermeasures apply sensor-based approaches (e.g. light sensors or active shields for detecting decapsulation). However, these countermeasures are out of the scope of this thesis.

#### **1.2** Contributions and Outline

Most SCA attacks and FA attacks reported in literature put the focus on the results achieved when attacking a specific algorithm. A discussion of the equipment required for performing the attack is often missing. In this thesis we address this issue by presenting low-cost measurement setups for preforming a wide range of SCA and FA attacks. All the setups exclusively use off-the-shelf

parts and their applicability has been verified by exemplary attacks. We looked at low-cost in three different settings: power/EM, fault, and relay attacks.

#### 1.2.1 Low-Cost Power and EM Attacks

In the context of EM SCA in the RFID domain we have investigated one prototype chip for RFID applications named CRYPTA. This chip integrates one hardware AES module with two countermeasures. These countermeasures are the random insertion of dummy rounds and shuffling. For verifying the locationdependent EM leakage, we have chosen an ATxmega 256 microcontroller. Here we compare the EM side-channel leakage of one software AES implementation with the leakage of the integrated hardware AES module. Both implementations do not include protection mechanisms against side-channel attacks. For performing high-resolution EM measurements we target a prototype chip named TAMPRES ASIC. Experiments with this chip include the analysis of the AES hardware implementation and the analysis of the LRPRF<sup>1</sup> implementation. The AES module has no SCA countermeasures integrated. Parallel processing and a limitation in the number of different plaintexts are the mechanisms to provide side-channel security for the LRPRF module. For low-cost power analysis we target an authenticated encryption algorithm based on the KECCAK-f permutation. This algorithm is implemented on a prototype ASIC and two countermeasures to harden the chip against SCA attacks are integrated. These countermeasures are hiding and secret sharing. The main contributions regarding low-cost power and EM measurement setups can be summarized as follows:

• We propose a novel measurement approach for measuring EM side-channel information of contactless RFID and NFC systems, named resolution op-timization.

This approach is presented in Chapter 2. Results of SCA attacks targeting a prototype ASIC for RFID applications show that the resolution optimization performs better compared to an existing approach if the distance between measurement antenna and attacked device exceeds 8 cm.

• The novel approach, the resolution optimization, is used to mount remote SCA attacks.

These remote SCA attacks are discussed in Chapter 2 and they allow to measure exploitable side-channel information up to a distance of 1 meter. We show this by successfully revealing the secret key used in a cryptographic protocol implemented on the prototype ASIC for RFID applications. Parts of these results were presented at COSADE 2012 [80], at CT-RSA 2013 [78], and at ARES 2013 [81].

• We study the spatial EM leakage of a hardware and a software AES implementations on microcontrollers.

$<sup>^1{\</sup>rm Leakage}\mbox{-}{\rm resilient}$  pseudo-random function.

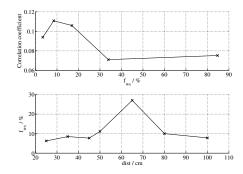

In Chapter 3, results achieved with spatial EM measurements are discussed. The chapter consists of two main contributions. First, we examine the spatial EM leakage of a software AES implementation and the hardware AES module integrated on an off-the-shelf microcontroller. Next to that we study high-resolution EM measurements for evaluating an AES and a LRPRF hardware module integrated on a prototype ASIC, respectively. The results can assist in finding the correct order of key-byte values. Results of this chapter have been published at FPS 2013 [73] and in Deliverable 5.2 of the TAMPRES project [74].

• We present first practical DPA attacks targeting a keyed KECCAK instance implemented on a taped-out ASIC.

Results of these attacks are presented in Chapter 4. We show that the frequently proposed secret-sharing countermeasure for sponge-based algorithms does not lead to the expected security gain if applied on low-resource implementations. We verify this by applying a cryptographic ASIC named ZORRO. This ASIC implements an AE algorithm based on KECCAK. Power measurements captured with a low-cost measurement setup are used for the SCA experiments. Parts of this chapter have been published at COSADE 2015 [97].

#### 1.2.2 Low-Cost Fault Injection

In the context of non-invasive fault injections, we target three different microcontroller types, all well-suited for usage in sensor nodes. These selection includes one ATmega 162/v, one ATxmega 256, and one ARM Cortex-M0. We do not target a specific cryptographic implementation during our investigations. The focus is put on the vulnerability of selected instructions to the fault injections. For studying semi-invasive fault injection, the target devices are one ATmega 162/v and one PIC 16F84 microcontroller. Here we study the influence of injection parameters on the ability to inject faults in volatile memory. The main contributions regarding low-cost fault-injection setups can be summarized as follows:

• We developed, improved, and applied a low-cost, FPGA-based fault board.

This fault-board is used in Chapter 5 to tamper with the clock signal and the supply voltage for performing FA attacks targeting microcontrollers. In Chapter 6 we apply the fault-board for controlling the laser pulses in optical fault scenarios.

• We improve an existing optical fault-injection setup.

The improvements consist in using high-power, pulsed laser diodes which allow front-side and rear-side attacks. Additionally, we use a specialized laser-diode mount to fix the diodes on top of a microscope. This allows to easily exchange the laser diodes. Using the fully-automated stepper table it is possible to perform laser scans of the whole chip area of the device under test.

• We are among the first to study the effects of similar fault injections on two different microcontroller platforms.

In Chapter 5, we apply non-invasive fault injections and study their impact on two different microcontroller platforms. Also the effectiveness of a combination of fault-injection methods is investigated. The results of these evaluations have been presented at FDTC 2014 [75, 77] and in the 10<sup>th</sup> volume of IEEE Transactions on Information Forensics and Security [87].

• We discuss the most-important parameters influencing the success of optical fault injections.

This evaluations can be found in Chapter 6. It turned out that the main parameters are the focus of the laser beam, the laser power and the laser pulse length. For the experiments we have applied a low-cost fault injection setup. This setup allows optical attacks from the front side and the rear side. The results have been presented at FPS 2014 [72].

#### 1.2.3 Low-Cost Relay Attacks

The main contributions regarding low-cost relay-attack setups can be summarized as follows:

• Introducing low-cost relay attacks applying two NFC-enabled smart phones.

With the relay setup presented in Chapter 7 relay distances of up to 110 meters can be reached by applying two/three NFC-enabled smart phones without the usage of a public network.

• We reveal and discuss limitations which arise when using smart phones for relay attacks.

A UID, which cannot be modified and limited access to low-level commands are two limitations. By replacing one smart phone by a low-cost, custommade proxy device, most of the revealed limitations can be circumvented.

• We compare the two most relevant relay channels, Bluetooth and WLAN.

By performing exemplary relay attacks we evaluate the performance of the two relay channels regarding relay distance and speed.

• We discuss improvements when using the custom-made proxy device.

These improvements include the cloning of the victim's UID, extending the relay time, modifying commands, and adding or skipping specific commands. The results relating to relay attacks have been presented at IEEE RFID 2014 [76].

# SCA-Attacks Targeting Contactless Devices

This chapter presents side-channel measurement setups and the corresponding results targeting devices operating in the RFID and NFC domain. This means, the devices, which will be referred to as tags in the following, typically do not have an integrated power supply. The required energy is delivered contactlessly via the EM field generated by a reader device. Power measurements are only possible on prototype devices or with significant modifications of the circuit. Therefore, real-world attacks take advantage of the electromagnetic (EM) emanation of the device in order to extract side-channel information. A prototype RFID-tag chip named *CRYPTA* served as target for the side-channel experiments performed in this chapter. The results presented in this chapter have been published in [78, 80, 81] and the main contributions can be summarized as follows.

#### Contribution

- Comparison of two measurement approaches for RFID/NFC scenarios with the parameter measurement distance.

- Remote SCA attacks proving that exploitable leakage can be measured at distances up to one meter with low-cost equipment.

- Introduction of the term "parasitic load modulation" and verification of the existence.

- Comparison of the amount of exploitable leakage of the ASIC version of *CRYPTA* and its functional-equivalent FPGA prototype.

• Investigation of the effectiveness of the SCA countermeasures implemented on *CRYPTA*.

This chapter is structured as follows. Section 2.1 gives an introduction to the RFID domain and discusses relevant related work. Preliminary information required for the rest of the chapter is given in Section 2.2. The results for the comparison of two measurement approaches are presented in Section 2.3. Remote SCA attacks and their application are presented in Section 2.4. In Section 2.5 close-proximity measurements are performed in order to compare the exploitable leakage of the *CRYPTA* ASIC with the leakage from an FPGA prototype. In the course of this comparison also the countermeasures on the *CRYPTA* ASIC are evaluated. Section 2.6 concludes the chapter with a short discussion.

#### 2.1 Introduction

Radio-frequency identification (RFID) technology has gained a lot of attention during the last decade and is used in many applications like ticketing, supplychain management, electronic passports, access-control systems, immobilizers, and payment systems. The relevance of this technology is underlined by the integration of RFID functionality into the latest generation of smart phones, using so-called near-field communication (NFC). With this widespread use of RFID technology, new applications like the future Internet of Things (IoT) will arise where security plays an important role. When integrating security to RFID systems, not only the selected cryptographic algorithms have to be secure, but also their implementation has to be protected against attacks such as side-channel analysis.

An RFID system consists of a reader (e.g. a smart phone) and a tag that communicate contactlessly by means of a radio frequency (RF) field. The tag is a small microchip attached to an antenna. Passive tags also receive their power supply from the RF field, which limits the available power budget of the tags. Especially passive tags that can be produced at low cost can be used in applications like the future IoT, where tags have to be competitive in price. In order to keep the price low, tags have to be produced in high volume and with smallest possible chip size. A very limited power budget together with smallest chip size make the integration of cryptographic security to RFID tags challenging.

Recent incidents like the reverse engineering of the CRYPTO 1 algorithm in Mifare tags [101], the breaking of the Digital Signature Transponder (DST) [27], or the attacks on the Hitag 2 cipher [34] and the KeeLoq remote entry system [36] have emphasized the need for integrating strong cryptographic security to RFID tags. A lot of effort has been made by the research community to bring strong security to resource-constrained RFID tags. Well-known examples are symmetric-key schemes like the Advanced Encryption Standard (AES) [39, 49, 94] and PRESENT [110], or public-key schemes like Elliptic Curve Cryptography (ECC) [11, 14, 51, 143] and NTRU [53].

Applying a strong cryptographic algorithm alone is not enough. Also the implementation of the algorithm has to be protected against SCA attacks. There is a large number of published articles about DPA attacks on contact-based devices, but only a handful of them about attacks on RFID devices. Hutter *et al.* [54, 55] have presented several DPA attacks on high-frequency (HF) RFID prototype devices. Oren and Shamir [105] have inspected the EM emissions of ultra-high frequency (UHF) tags to deduce the secret kill password. Kasper *et al.* [65] and Oswald [106] have successfully applied SCA attacks on a contactless smart card that computes Triple DES (3DES). The authors have applied an analogue demodulation circuit in order to improve the measurements, i.e. to filter out the interfering reader field.

As a main contribution in this chapter, we present measurement setups which do not require a demodulation circuit. A comparison of the performance of our setup with the one presented in [65] reveals that especially for larger distances between measurement probe and attacked device, our approach is advantageous. It is shown that with this measurement setup, exploitable side-channel information can be measured at distances up to one meter. This is mainly achieved by applying a self-made measurement antenna customized for our needs. A relation between measurement distance and attack effort is derived in theory and approved by practical results. An AES implementation on a prototype RFID-tag chip named *CRYPTA* served as target for the experiments. Although *CRYPTA* has countermeasures against SCA attacks integrated, they were disabled for the experiments.

As a further contribution a comparison in terms of exploitable side-channel leakage of the taped-out *CRYPTA* ASIC and a functional equivalent FPGA prototype was performed. In the course of these experiments, where EM traces were measured at close proximity, the effectiveness of the SCA countermeasures were examined.

#### 2.2 Preliminaries

In this section preliminary information required for the rest of the chapter is given. First, the investigated RFID-tag chip, the *CRYPTA* ASIC and its functional-equivalent FPGA prototype are introduced. Next, an introduction to *parasitic load modulation* is given. The parasitic load modulation describes how side-channel information of RFID chips is modulated on the reader signal. Finally, the two measurement approaches, which are compared are introduced. The first approach, the *analogue demodulation approach*, has been proposed by Kasper *et al.* in [65]. The second approach has been developed by us and we refer to it as *resolution optimization*.

#### 2.2.1 CRYPTA ASIC

In the following paragraph, an introduction to the CRYPTA chip is given. First the focus is put on the ASIC realization of CRYPTA followed by its FPGA-

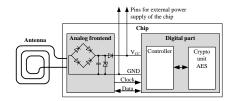

Figure 2.1: Architecture of the evaluated chip.

Figure 2.2: The development board with the evaluated chip.

prototype version.

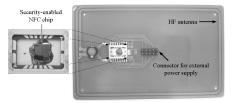

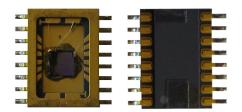

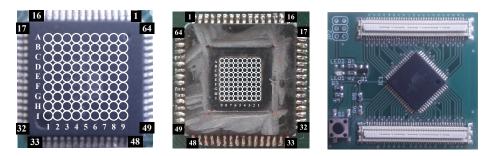

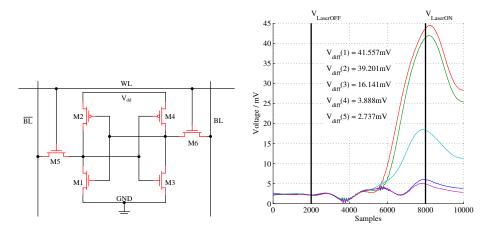

The *CRYPTA*-ASIC chip is mounted in a prototype metal package which is open on top as depicted in Figure 2.3. If the two package pins are connected to an antenna, it behaves like a normal contactless chip card and can communicate with a reader device. *CRYPTA* operates in the HF frequency range of 13.56 MHz and the communication protocol is implemented according to the ISO 14443A standard [60]. The chip consists of two main parts as depicted in the architecture overview in Figure 2.1: the analog front-end (AFE) and the digital part. The antenna is connected to the AFE that provides the power supply and the clock signal to the digital part. The digital part is responsible for processing the commands to communicate with the reader. This part also contains a crypto unit with an AES implementation supporting the key length of 128 bits to provide symmetric-key cryptography. The AES part is implemented as special-purpose hardware to meet the most important requirements for RFID-tag chips: low power consumption and small chip area.

In order to increase the resistance against SCA attacks, the AES implementation has two countermeasures integrated: the insertion of dummy rounds and shuffling. The chip processes in total 25 rounds during an AES encryption/decryption. Ten rounds relate to the real computation of AES and fifteen rounds are dummy rounds that process random data. The dummy rounds are randomly inserted before the first and after the last real AES round. With shuffling, the processing order of the bytes of the state is randomized. As the AES state consists of sixteen bytes every byte can be processed at sixteen different points in time. In a typical DPA-attack scenario it is important to know at which point in time a specific byte of the state is processed. Because of that fact shuffling increases the attack complexity. It is important to mention that *CRYPTA* allows to switch off the countermeasures. This option is advantageous for several of our investigations.

Figure 2.2 depicts the ASIC chip mounted on a development board that contains an antenna with four windings. The board also allows to power the chip with an external power supply. If an external power supply with a voltage of at least 3.3 V is connected, the chip does not use the power supply extracted from the reader field. This allows to measure the power consumption of the chip with a resistor in the ground line.

In addition to the ASIC-chip version we also use an FPGA-prototype version

Figure 2.3: The CRYPTA ASIC-chip.

Figure 2.4: The IAIK demotag consisting of the FPGA (top) and the main board (bottom).

of *CRYPTA* for the evaluation. This FPGA-prototype version is based on the IAIK demotag which consists of two parts. The first part is the FPGA (XILINX Spartan-3) itself, which implements the digital part of *CRYPTA*. The second part is the so-called main board, which consists of the analog front-end and the antenna. The IAIK demotag is depicted in Figure 2.4. For a reader device, the FPGA-prototype tag appears like a regular, passive RFID tag. It uses an external power supply but the reader field is used for communication and for extracting the clock signal. We used the FPGA-prototype version to show that the DPA-attack results achieved with this device are comparable with the results from the ASIC-chip versions. Therefore, one output pin was used as trigger pin to signalize, when the AES encryption starts. One advantage of the FPGA-prototype version is that small modifications can be integrated and tested with low effort. The FPGA prototype further gives the ability to correct bugs detected on the real chip and evaluate the effects of the modification and chip developers can test the implementation before manufacturing the ASIC chip.

#### 2.2.2 Parasitic Load Modulation

For remote SCA attacks we present an approach that requires neither the separation of the tag chip from its antenna nor the application of special analog preprocessing circuits. In contrast to close-proximity measurements we exploit the strong reader field as a carrier of the weak data-dependent information emitted by the tag for the remote SCA-attack scenarios. As we assume that most of the data-dependent information is amplitude modulated on the reader signal, it is sufficient to measure only the peaks of the reader signal. This simple measurement concept was originally used for analyzing the emissions of UHF tags [109]. In this work we show that this concept is also suitable for gathering the data-dependent emissions of RFID/NFC tags operating in the HF range, even at greater distances.

NFC and HF RFID systems are inductively coupled. This means that the antennas of reader and tag are loosely coupled and act like an air-core transformer [40], which is illustrated in Figure 2.5. Applying an alternating voltage at the reader antenna ( $U_{Reader}$ ) results in a magnetic field that itself induces

an alternating voltage at the tag antenna ( $U_{Tag}$ ). The voltage at the tag is not only used for data transmission from the reader to the tag (i.e., by modulating the reader field in step with the data), but also to provide the power supply for passive tags. Data transmission from the tag to the reader is done by so-called load modulation, where an impedance  $Z_{Mod}$  is switched in step with the data. Switching the impedance  $Z_{Mod}$  changes also the overall impedance of the tag  $Z_{Tag}$ , which in turn results in changes in the magnetic field and in detectable voltage variations at the reader antenna.

However, not only the intended load modulation influences the magnetic field, but also changes in the power consumption of the tag chip. As the power consumption directly relates to the chip's effective impedance  $Z_{Chip}$ , the overall impedance of the tag is changed as well. In that way data-dependent information present in the power consumption of the tag chip is modulated on the reader field. We call this effect *parasitic load modulation*, according to a similar effect named *parasitic backscatter* that was observed by Oren and Shamir for tags operating in the UHF range [105]. In the following, we use this *parasitic load modulation* for conducting remote SCA attacks targeting the *CRYPTA* tag.

It is not obvious that remote attacks are applicable on HF tags. First, HF tags are inductively coupled and operate in the near field where RF signals are attenuated with  $1/d^3$  (with *d* being the distance). UHF tags on the other hand operate in the far field, where RF signals are only attenuated with 1/d. Moreover, the *parasitic backscatter* observed by Oren and Shamir does not influence the reader field, rather it relates to independent electromagnetic waves emitted by the tag antenna. Consequently, a favorable placement of the measurement antenna is possible that allows to gather mainly the signal emitted by the tag antenna. However, this is not possible when measuring the *parasitic load modulation* of a tag, as it is directly modulated on the strong reader field.

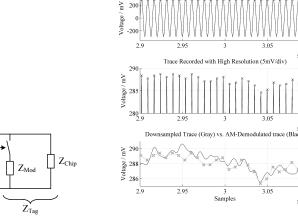

#### 2.2.3 Resolution Optimization

A special recording technique has been applied which does not require the application of any analog preprocessing circuits. Due to parasitic load modulation, recording only the peaks of the reader signal should be sufficient and further increase the resolution of the measurement. The upper plot in Figure 2.6 shows one trace where the whole amplitude is recorded and the lower plot shows the same trace zoomed into the peaks. For this approach it is also sufficient to store only the maximum value per period, where the period equals  $\frac{1}{13.56MHz} = 73.75ns$ . The following experiment shows that this method is similar to an analog demodulation followed by a lowpass filtering. For this experiment we have applied these two steps on the trace from the top plot of Figure 2.6. The two steps were performed in MATLAB<sup>®</sup>. Using the build-in function amdemod we demodulated the trace. Afterwards a lowpass filter was applied on the demodulated trace using the function filtfilt with a cut-off frequency  $f_{co} = 15 MHz$ . The comparison plot at the bottom of Figure 2.6 clearly depicts that there are only small deviations in the results of the two approaches. It turned out that except of the downsampling step no other preprocessing steps (e.g., alignment, filterInductive

coupling

Reader

antenna

Figure 2.5: Basic principle of inductive coupling between reader and tag antenna.

Data

$U_{\text{Tag}}$

Tag

antenna

Figure 2.6: Resolution enhancement of EM measurements.

Trace Recorded with Low Resolution (100mV/div)

3.05

x 10

x 10<sup>4</sup>

ing) are required in order to perform successful DPA attacks. For enhancing the resolution of the measurements, the voltage-scaling setting voltage per division (V/div) of the oscilloscope has been used. With increasing resolution also the number of different voltage values increases. As a result of only measuring the peaks of the signal the voltage values are fine grained what increases the efficiency of the DPA attack.

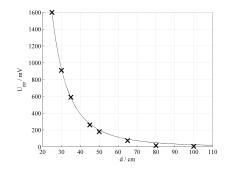

In the following, we define a factor  $f_{ws}$ , which brings the V/div setting of the oscilloscope and the peak-to-peak voltage  $U_{pp}$  of the EM signal in relation. This factor can be interpreted as window size on the voltage axis, describing the percentage of the signal being recorded with the current settings ( $N_{div}$  equals the number of divisions of the used oscilloscope on the voltage axis):

$$f_{ws} = \frac{V/div \cdot N_{div}}{U_{pp}} \cdot 100 \,[\%] \tag{2.1}$$

Besides the window size, the window position is the second parameter which has to be considered when using the resolution optimization approach. This parameter is set using the voltage offset setting of the oscilloscope and defines the part of the signal actually recorded. Both parameters, size and position of the recording window need to be found during a profiling phase. It is comparable to finding the correct time interval for successfully mounting a DPA attack.

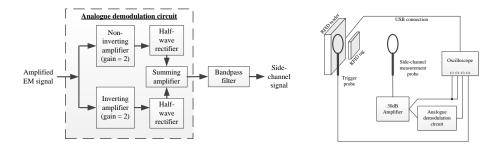

Figure 2.7: Analogue demodulation circuit (left) and setup used for comparing two measurement approaches (right).

#### 2.2.4 Analogue Demodulation Approach

In the following the analogue demodulation approach as published in [65] is explained. In a first step, the leakage model is established according to Equation 2.2.

$$s(t) = (P_{const} + p(t)) \cdot \cos(\omega_{reader} \cdot t)$$

(2.2)

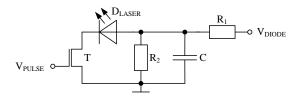

s(t) denotes the reader signal, which can be measured by an adversary. It is amplitude modulated with a constant part of the power consumption  $P_{const}$  and a time-varying part p(t). This time variations can be caused by the execution of different operations on the tag or by executing a similar operation on different values. Furthermore,  $\omega_{reader} = 2\pi \cdot f_{reader}$  with  $f_{reader} = 13.56$  MHz being the carrier frequency. p(t) includes the relevant side-channel information to carry out side-channel attacks. Typically  $P_{const} >> |p(t)|$ , this fact makes it a crucial task to filter the exploitable side-channel information out of s(t). The authors of [65] propose to use an analogue demodulation circuit to perform this task. A block diagram of an exemplary analogue demodulation circuit is depicted in the left part of Figure 2.7. In a first step, the EM signal measured with the EM probe is split up into two parts. Both parts are then amplified, one with a gain equal 2 and one with a gain equal -2. Next, the negative signal parts are removed using half-wave rectifiers. In a last step, both signals are summed up again and the result can already be used as side-channel signal. To further improve the measurement process, a bandpass filer can be applied to suppress the DC part of the demodulated signal on the one hand and high frequencies carrying no information on the other hand.

#### 2.3 Comparison of Measurement Approaches

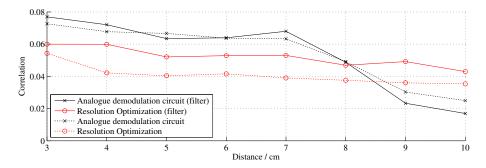

In the following section the results of the comparison of the two previously introduced measurement approaches are discussed. By performing experiments with measurement distances between 3 cm and 10 cm the influence of the measurement distance on the two approaches has been studied. It figured out that the

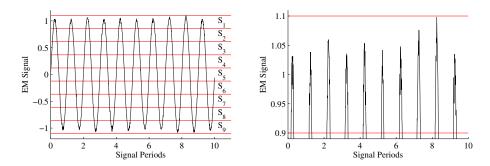

Figure 2.8: Measurement of the full EM signal (left) and improved resolution by only measuring the peaks of the signal (right).

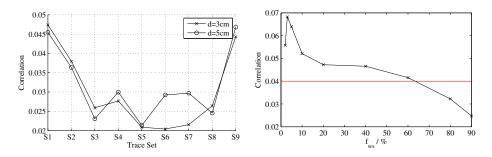

resolution optimization approach is advantageous for measurements at distances exceeding 8 cm. The results of this approach can further be improved by applying a moving-average filter on the measured traces. The same filter applied on the measurements from the analogue demodulation circuit did not further improve the results compared to unfiltered measurements. A disadvantage of the resolution optimization is the requirement for a profiling step in order to find the best parameters for window size and position. Before the achieved results are discussed in detail, the measurement setup is introduced.

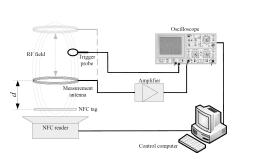

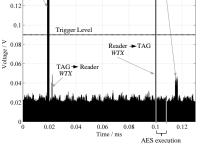

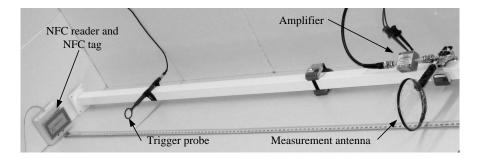

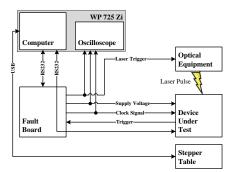

#### 2.3.1 Measurement Setup

A schematic view of the measurement setup is depicted in Figure 2.7 on the right. The measurements are controlled by a 'LeCroy WP 725 Zi' oscilloscope. This device is not only used for measuring the side-channel information, but it also establishes the communication with the RFID tag. The communication consists of a simple command triggering an AES encryption on the RFID tag. The CRYPTA chip was used as device under test. A trigger probe (model 'LFR 400' from 'Langer EMV Technik') placed in close proximity to the reader provided the trigger information. For measuring the side-channel signal, a self-made loop antenna with  $N_{ant} = 5$  windings and a diameter  $d_{ant} = 8$  cm has been applied. Different values for  $N_{ant}$  as well as for  $d_{ant}$  have been investigated, but the best results have been achieved with the values mentioned above. Experiments using a second LFR 400 EM probe revealed that the diameter of this probe  $(2.5 \,\mathrm{cm})$  is too small for meaningful measurements at higher distances. The signal measured with the self-made antenna has been amplified with a 30 dB amplifier. The output of the amplifier is directly connected to two inputs of the oscilloscope and to the input of the analogue demodulation circuit. With the third channel of the oscilloscope the output signal of the analogue demodulation circuit is captured. Capturing the amplified EM signal twice allows to evaluate two different oscilloscope settings (voltage/division, offset) in parallel.

#### 2.3.2 Profiling for Resolution Optimization

In contrast to the amplitude demodulation approach, the resolution optimization as applied for the remote SCA attacks requires an initial profiling phase. Results of this profiling phase are the optimal **window position** (adjusted by the *voltage offset* setting of the oscilloscope) and the **window size** (set by the *voltage/division* setting of the oscilloscope).

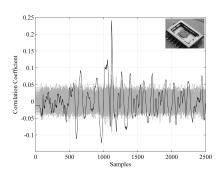

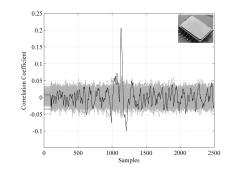

In order to find the best-fitting window position, the following approach is applied. In a first step, the peak-to-peak value of the EM signal  $U_{pp}$  is split into M equally-sized segments  $S_1 \ldots S_M$ . Using the voltage offset and the voltage/division setting of the oscilloscope allows to select each segment separately for recording. The left plot in Figure 2.8 depicts one recorded EM signal measuring the whole amplitude. Furthermore, the M = 9 trace segments  $S_1$  to  $S_9$  are marked. For the right plot of Figure 2.8 the settings of the oscilloscope were modified in order to measure segment  $S_1$ . For each segment, N = 20000measurements were recorded each including one AES execution. The same set of input values for the AES were used for all segments and the key was fixed and known for all the experiments. After the measurement process, a DPA attack was performed on each segment  $S_i, i = 1 \dots M$  separately, leading to a maximum correlation coefficient for the correct key hypothesis  $\rho_{max,i}$  for each segment. The segment containing most side-channel information is found by evaluating  $S_m | m = argmax(\rho_{max,i})$ . Evaluations at two different distances between reader and measurement antenna both yield segments  $S_1$  and  $S_9$  as the best window positions. Results are depicted in Figure 2.9. Concluding this experiment, most of the exploitable side-channel leakage for the specific device appears in the peaks of the signal.

In order to find the best-matching value for  $f_{ws}$ , i.e. the value maximizing the amount of leakage in the measurements, the following approach is used. For a fixed distance between measurement antenna and tag of 3 cm, M = 9 trace sets containing 20 000 traces were recorded for  $f_{ws}$  settings between 2% and 90% by choosing the appropriate *voltage/division* setting on the oscilloscope. The window position for all window sizes was chosen to include the positive peaks of the EM signal according to the outcome of the previous experiment. DPA attacks were performed using each trace set separately, leading to a maximum correlation coefficient for the correct key hypothesis  $\rho_{max,i}$  for  $i = 1 \dots M$ . The best  $f_{ws}$  value equals the setting which maximizes the correlation value. The result of this experiment is depicted in the right plot of Figure 2.9. The maximum correlation coefficient values for the analyzed  $f_{ws}$  settings are shown.  $f_{ws} = 3\%$ turns out to lead to the best results. It might be intuitive to use the smallestpossible value for  $f_{ws}$  but results show that this is not the case. We conclude that too small values for  $f_{ws}$  chop parts of the trace containing exploitable leakage.

#### 2.3.3 Results of the Comparison

After the proper settings for window position and window size for the resolution optimization approach have been found, the comparison between the two mea-

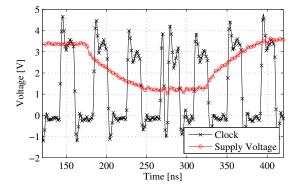

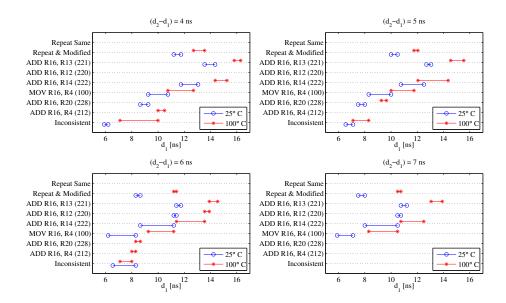

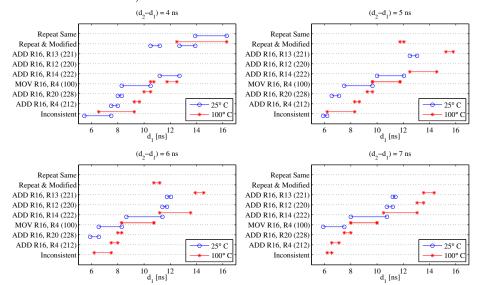

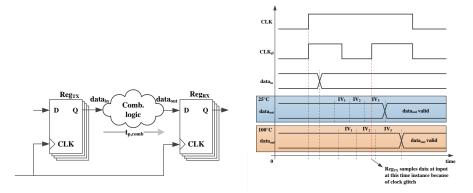

Figure 2.9: Correlation coefficients for the correct key hypothesis for different window positions (left). Correlation coefficient as a function of the window size  $f_{ws}$  (right).