#### AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present doctoral thesis.

Date

Signature

#### ACKNOWLEDGEMENTS

I would like to take the opportunity to thank a number of people who gave me personal and technical guidance throughout the last years. Without this enduring support I wouldn't have made it up to this point of finally writing this acknowledgement.

First of all, I'd like to thank my Prof. Dr. W. Bösch for giving me the opportunity to work on such an interesting realm as the design of broadband high power GaN PAs. Thank you for giving me the freedom to focus on topics of my choice in-depth, which are/were technically for me of great interest.

Also, a special thanks goes to my supervisor Dr. R. Quay at the Fraunhofer IAF in Freiburg for supporting me and pushing me through all various kinds of issues and problems, which I experienced during my PhD. Thank you for reviewing my papers and my "lengthy" thesis, for introducing me to the world of on-wafer measurements and for giving me moral and emotional support during tough times.

I really appreciate the enormous technical experience of F. van Raay, who provided constructive feedback, inventive solutions and ideas in situations when I got stuck. Thanks to all IAF employees, who were involved in the processing and measurement of my MMIC designs. Especially, I'm indebted to T. Maier and R. Lozar for conducting all of the on-wafer small-signal and large-signal measurements at the IAF, which were unfortunately not always "standard" measurements.

Furthermore, many thanks to G. Kahmen for arranging the PhD cooperation between the TU Graz and Rohde & Schwarz GmbH & Co.KG. Doing the PhD at R&S in Munich gave me the great possibility to work scientifically in an industrial environment with many experienced colleagues, who were willing to share their knowledge in integrated circuit design and packaging. Due to all their expertise and discussions we had, I was finally able to cope with the challenging and demanding task of "closing the gap" between scientific and industrial requirements.

I am very grateful to my colleague T. Huber for spending hours of fruitful technical, scientifical as well as personal discussions with me. Sentences such as "...this can be easily computed by hand..." or "...a quick simulation should show the dependence..." often ended in days of additional work and with new upcoming problems. Although, the unintended "extended" work-frame often brought up new ideas and really helped to understand things in more detail. I'm looking forward to stick to these kind of discussions in our future work.

Also, special thanks to R. Schumann and I. Melczarsky for profound technical discussions on modeling, technology and ADS- & CST-simulation related topics.

Last but not least, I'm eternally grateful to my wife Anne for her patience and mental support, especially during times of emional stress and trouble over the last years. I really appreciate that you sacrificed a lot of our weekend time for the greater good of finishing this thesis. Thank you for always building me up and pushing me through tough times, when the next "crisis" was already looming.

#### ABSTRACT

The insatiable need for higher data rates in the communication market enforces communication systems in the long term to move up in frequency. In order to significantly boost channel capacities and therewith the net data throughput, frequencies in the higher microwave spectra need to be allocated in the future to provide sufficient bandwidth. This in turn makes even a greater demand on the measurement equipment to be able to build and test such communication systems in the first place. Especially power amplifiers (PAs) prove to be one of the key components in the transmitter chain of measurement instruments, since they mainly constitute the last performance bottleneck before the test signal is fed to the device under test (DUT).

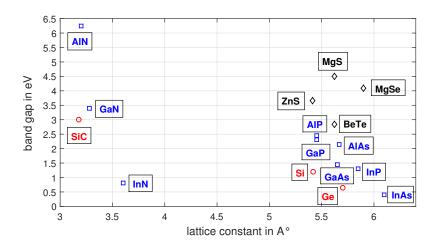

Ever since solid-state PAs based on GaAs semiconductor technology came up in the early 80's, nearly all of the high-end applications, such as mobile communications, radar systems, military equipment or measurement instruments, comprise GaAs PAs as performance enabler for achieving high power at high frequencies. With the advent of commercial available GaN on SiC technology in 2005, a new chapter in III-V semiconductor technology has been openend. Peak power densities in continuous-wave mode up to 40 W/mm have been reported for AlGaN/GaN HEMTs on SiC in [1]. Out of the roughly four times higher power densities of GaN compared to GaAs (p)HEMTs, most of the GaAs PAs are/will be nowadays replaced by their GaN competitor to boost the output power for the next application generations. In particular, the high output power per capacitance ratio of GaN technology allows for better matching of the HEMT's input and output to the typical 50  $\Omega$  environment at higher frequencies. This in turn enables the implementation of wideband PAs over multiple decades, which makes this technology so attractive for the application in measurement instruments.

This work focuses on the realization of multi-decade broadband PAs in a 0.25µm GaN technology, which are optimized for the use in measurement instruments, such as e.g. signal generators. The most promising PA topologies for wideband operation from DC up to several GHz are the resistive feedback PA (FBPA) and the traveling-wave PA (TWA) or distributed PA (DPA), respectively. Since not only the maximum output power but moreover also linearity and noise play a decisive role for the applicability of GaN PAs in measurement instruments, this work investigates adequate wideband on-chip linearization and noise reduction concepts for FBPAs and TWAs in detail, which further improve the linearity and noise compared to conventional FBPA and TWA designs.

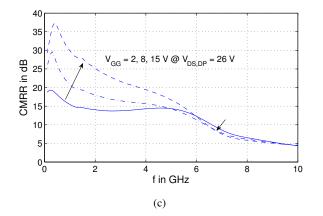

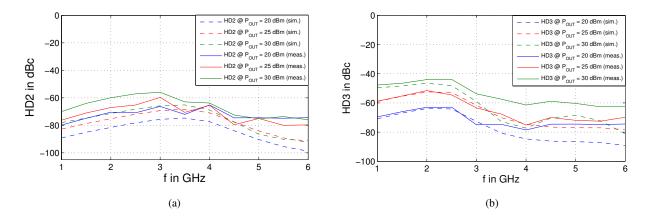

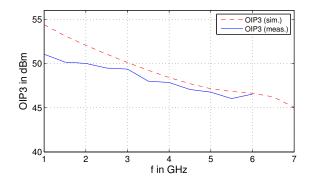

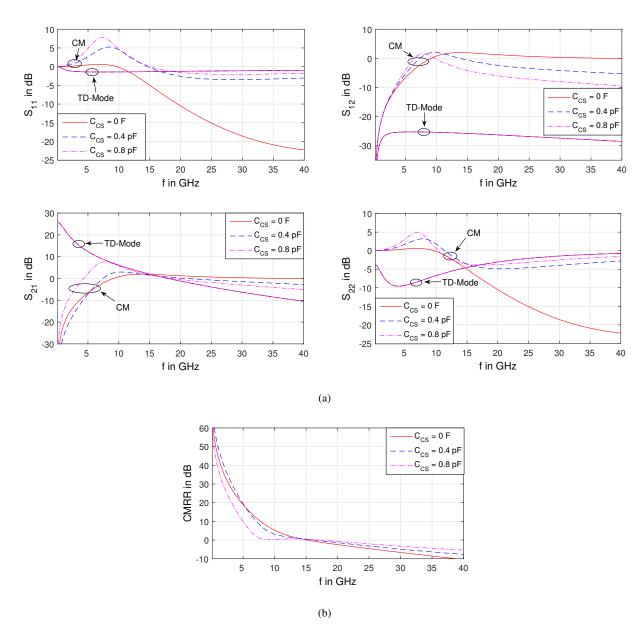

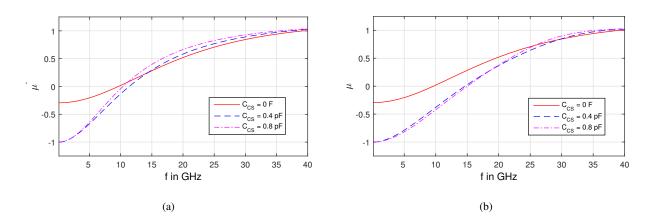

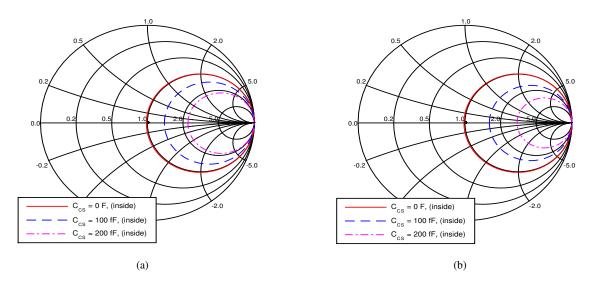

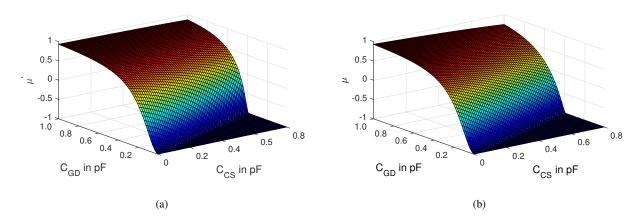

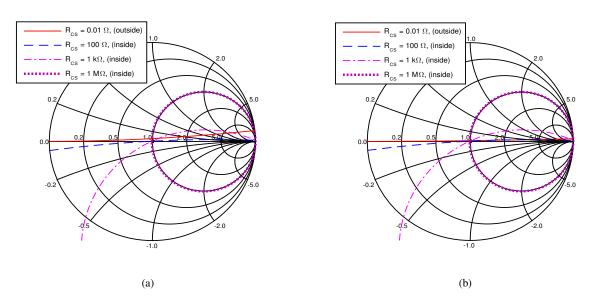

During the course of this work a DC-6 GHz FBPA was designed on the one hand in the conventional singleended way and on the other hand in a truly-differential approach (TD-FBPA) in order to improve the harmonic distortion (*HD*) by even-order nonlinearity cancellation. The final TD-FBPA design showed to improve the *HD2* by more than 25 dB and the overall *SFDR* by 10 dB compared to the single-ended FBPA design, resulting in a *SFDR* of -55 dBc at  $P_{OUT} = 25$  dBm. Moreover an *OIP3* at 1 GHz of 51 dBm and at 6 GHz of 46 dBm was measured for the TD-FBPA, which results in an improvement of more than 5 dB of the 3<sup>rd</sup> order intermodulation product, showing an outstanding linearity performance for a 4 Watt broadband FBPA in GaN technology. On top, the general small-signal stability of pseudo-differential (PD) and truly-differential (TD) amplifiers was analyzed, where the latter topology proved to be especially prone to CM-instabilities in GaN technology. Therefore, an analytical boundary condition for low frequency CM-stability dependent on the intrinsic HEMT parameters and the impedance environment was derived. The striking cause for the CM-instability in GaN technology was identified to be related to the small amount of feedback capacitance ( $C_{GD}$ ) compared to the input ( $C_{GS}$ ) and output ( $C_{DS}$ ) capacitances. Especially for a usually given impedance environment of  $Z_0 = 50 \ \Omega$ , the necessary ratio of  $C_{GD}$  to  $C_{GS}$  and  $C_{DS}$  for low frequency stability is more severe. With increasing  $Z_0$  and a higher transitfrequency ( $f_T$ ), which results from a smaller  $C_{GS}$  and/or a larger  $g_m$ , the requirements for the necessary capacitance ratios become more relaxed. Based on these theoretical findings, remedies for CM-stabilization in TDamplifiers, such as applying parallel feedback, omission of the gate-source field-plates or inductive compensation of the tail-current-source (TCS) capacitance, were deduced and verified by the DC-6 GHz TD-FBPA design.

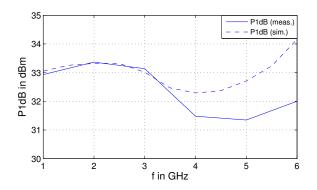

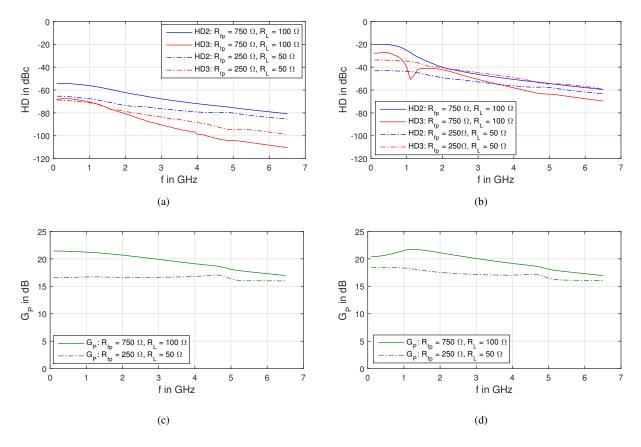

For a similar frequency range from DC-6.5 GHz, a linearized low-noise TWA (L<sup>2</sup>NTWA) design, which makes use of a diode predistortion concept for the first time in a distributed structure, was designed with the goal of achieving high linearity and low-noise performance at the same time in a 2 W PA class. By means of an external diode-tuning voltage, the even- and odd-order linearity can be traded off against each other up to a certain degree without degrading the gain or I/O-RL of the L<sup>2</sup>NTWA to a greater extent. The measurement of the assembled MMIC in package showed a flat gain of larger than 14 dB from 10 MHz up to almost 7 GHz, whereby the lower operational frequency was only limited by the values of the off-chip SMD components. Linearity measurements additionally revealed a high linearity with a maximum *SFDR* of -38 dBc at  $P_{OUT} = 25$  dBm and an *OIP*3 of larger than 42 dBm at its optimum diode-tuning voltage. A minimum *NF* of 1.8 dB at 2 GHz was measured for the nominal bias point of  $V_{DS} = 28$  V and  $I_{DS} = 200$  mA/mm. Together with a  $P_{1dB}$  of greater than 1 W over the whole band, the design classifies into the high power LNA class and is perfectly suited as a highly linear low-noise driver stage for their DC-6 GHz GaN FBPA or TD-FBPA counterparts.

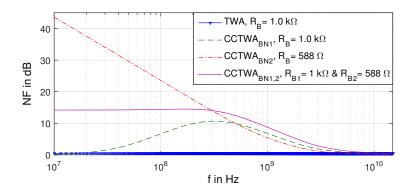

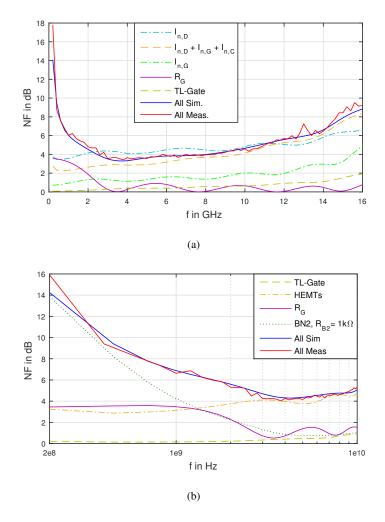

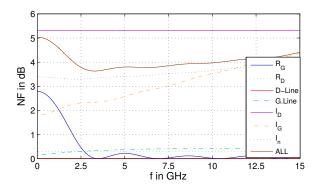

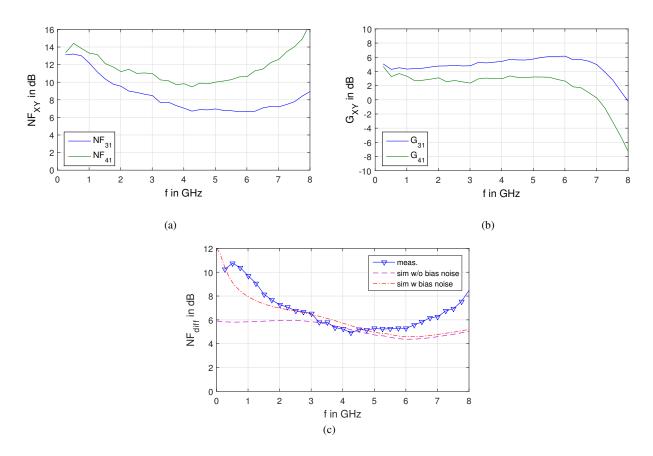

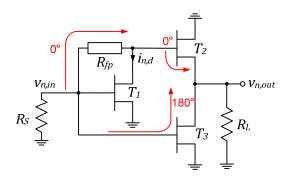

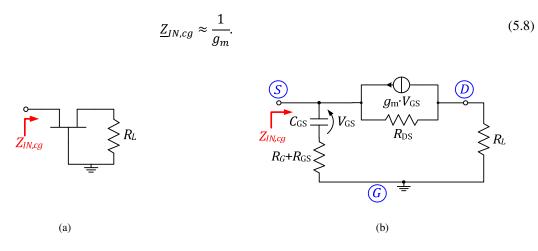

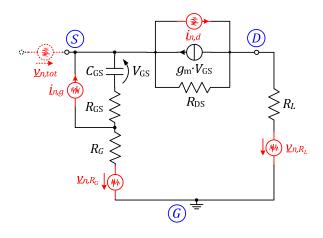

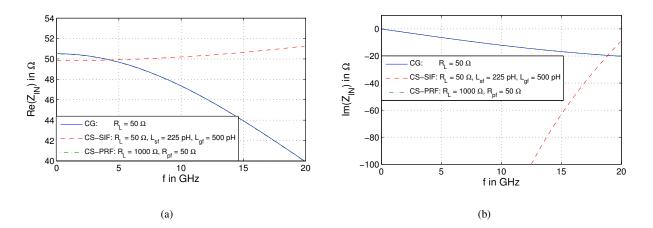

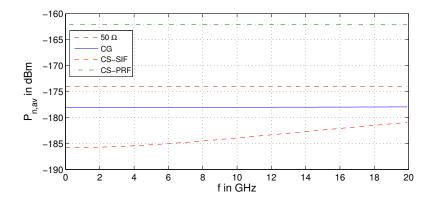

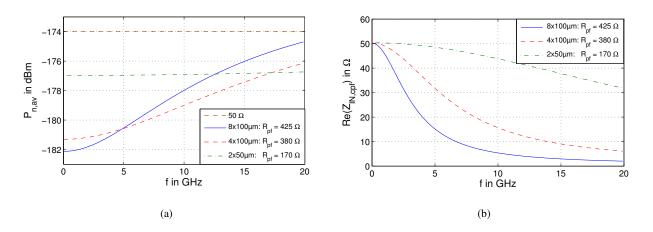

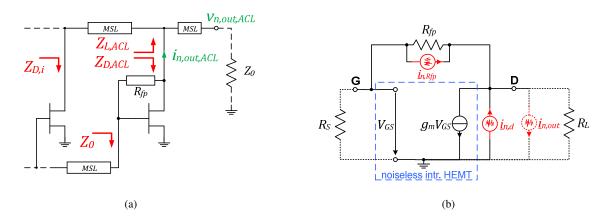

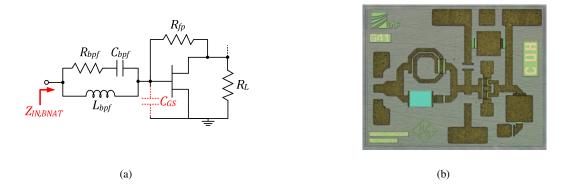

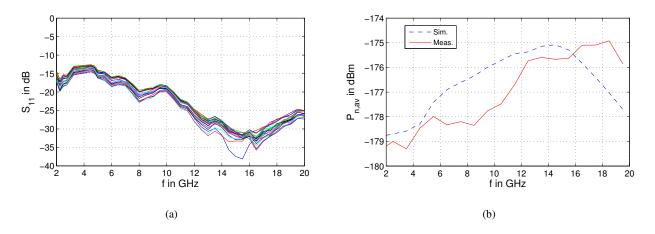

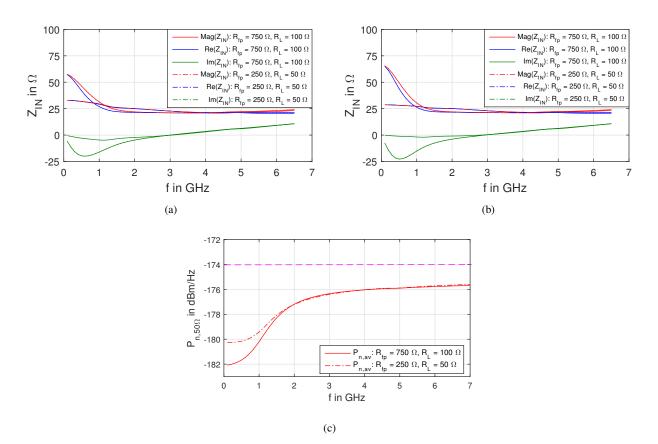

In terms of noise performance, conventional TWAs exhibit a significant increase in noise toward low frequencies, which makes this topology inappropriate for low frequency applications in measurement instruments. By means of a DC-15 GHz reference design, the steep increase in NF below 2 GHz was verified by measurements, after identifying all different noise contributors. The corresponding transfer functions to the output of all present noise sources were calculated mathematically and the contribution to the overall NF analytically evaluated. The largest low frequency noise contribution was identified to originate from the gate bias resistors, when capacitive gate-coupling is applied. If no capacitive gate-coupling is present, the gate-line termination resistor introduces the second largest amount of noise to the output due to the TWA's inherent reverse transfer function from the gate-termination to the output. In order to minimize this noise contribution, three distinct active cold load (ACL) concepts are reviewed and theoretically analyzed in order to find the best suited topology for TWAs. Out of the three different ACL concepts, the common-source topology with parallel resistive feedback (CS-PRF) proved to be the most suited one. Furthermore, among the two presented possibilities of terminating the gate-line with the CS-PRF ACL at either the last stage of the TWA or as substitution of the resistive load, the latter showed from the analysis to be the more promising solution with respect to the targeted gain and ORL of the TWA. Nevertheless, the analysis revealed that both methods are effective to minimize the low frequency noise. Based on the preceding analysis the more suited CS-PRF ACL concept was combined with an upstream RLC-filter to obtain a wider input match, which is also called "blue noise active termination" (BNAT) due to its shaped high frequency noise spectrum. The BNAT was first of all designed on a separate die to verify its general functionality by on-wafer measurements. After successful proof of concept the BNAT was attached to the L<sup>2</sup>NTWA design to investigate the degree of NF improvement compared to a resistive load. The NF measurements showed an improvement of 1.9 dB from 5.5 dB with resistive load down to 3.6 dB with BNAT.

### KURZFASSUNG

Die unstillbare Nachfrage nach höheren Datenraten im Kommunikationssektor zwingt langfristig Kommunikationssyteme bei höheren Frequenzen zu arbeiten. Um die Kanalkapazität und damit den Netto-Datendurchsatz zu steigern, müssen die Trägerfrequenzen in Zukunft immer weiter ins höhere Mikrowellenspektrum verschoben werden, um ausreichend Bandbreite zur Verfügung zu stellen. Dies wiederum stellt noch höhere technische Anforderungen an die Messinstrumente, damit derartig hochfrequente Kommunikationssysteme überhaupt gebaut und getestet werden können. Im Speziellen stellen breitbandige Leistungsverstärker eine der Schlüsselkomponenten in Sendesignalpfaden von Messinstrumenten dar, da diese als letzte aktive Komponente vor der Herausführung des Testsignals zum Messobjekt (DUT) maßgeblich die Signalintegrität beeinflussen.

Seit dem Aufkommen von GaAs Halbleitertechnologie in den 80er Jahren, beinhalten fast alle High-End Andwendungen, wie z. B. die Mobilkommunikation, Radarsysteme, Militärgeräte oder Messinstrumente, GaAs MMIC PAs um hohe Leistungen bei hohen Frequenzen zu realisieren. Mit der Etablierung kommerziell verfügbarer GaN auf SiC Technologie seit 2005 wurde ein neues Kapitel in der Geschichte der III-V Halbleitertechnologie geöffnet. Spitzenleistungsdichten im CW-Betrieb von bis zu 40 W/mm für AlGaN/GaN auf SiC wurden in [1] demonstriert. Aufgrund der ungefähr viermal höheren Leistungsdichte von GaN HEMTs im Vergleich zu GaAs HEMTs wird ein Großteil der GaAs PAs heutzutage durch die konkurrierende GaN Technologie ersetzt, um die Ausgangsleistung in Anwendungen für neuere Generationen zu steigern. Besonders das Verhältnis von Ausgangsleistung zu Kapazität ermöglicht bei höheren Frequenzen eine bessere Eingangs-/Ausgangsanpassung der GaN HEMTs in einem 50  $\Omega$  - System. Dies wiederum ermöglicht es breitbandige PAs über mehrere Dekaden zu realisieren, was diese Technologie so attraktiv für Anwendungen in Messinstrumenten macht. Diese Arbeit konzentriert sich daher auf die Realisierung von breitbandigen PAs über mehrere Frequenzdekaden in 0.25µm GaN Technologie, die für den Einsatz in Messinstrumenten, wie z. B. Signalgeneratoren (SG), optimiert sind. Für breitbandigen Betrieb von DC bis zu mehreren GHz sind die zwei vielversprechendsten PA Topologien zum Einen der resistive Rückkopplungsverstärker (FBPA) und zum Anderen der Wanderwellen (TWA) oder verteilte (DPA) PA. Da nicht nur die maximale Ausgangsleistung sondern auch die Linearität und das Rauschen eine entscheidende Rolle für die Eignung von GaN PAs in Messinstrumenten spielt, widmet sich diese Arbeit der detaillierten Untersuchung von geeigneten breitbandigen Linearisierungs- und Rauschminimierungskonzepten, welche die Linearitäts- und Rauscheigenschaften speziell von FBPAs und TWAs auf Chipebene verbessern.

Im Laufe dieser Arbeit wurde ein DC-6 GHz FBPA zum einen auf konventionelle unsymmetrische Weise (FBPA) und zum anderen in voll-differentieller Form (TD-FBPA) entworfen, um die harmonischen Verzerrung (*HD*) durch Auslöschung der geradzahligen Harmonischen zu verringern. Das finale Design des TD-FBPA zeigt im Vergleich zum unsymmetrischen FBPA dabei eine Verbesserung des *HD2* von 25 dB und der *SFDR* von 10 dB auf, was in einer *SFDR* von -55 dBc bei  $P_{OUT} = 25$  dBm resultiert. Darüber hinaus wurde ein *OIP3* bei 1 GHz von 51 dBm und bei 6 GHz von 46 dBm gemessen, was zu einer Verbesserung des Intermodulationsprodukts dritter Ordnung von mehr als 5 dB führt. Dies zeigt das herausragende Gesamtlinearitätsverhalten eines 4 Watt DC-6 GHz FBPAs. Zusätzlich wurde die Kleinsignalstabilität von pseudo-differentiellen (PD) und voll-differentiellen (TD) Verstärkern untersucht, wobei sich heraustellte, dass letztere Topologie speziell in GaN Technologie anfällig für Gleichtaktinstabilität in Abhängigkeit der intrinsischen HEMT Parameter und Umge-

bungsimpedanz hergeleitet. Als ausschlaggebendes Kriterium für die Gleichtaktinstabilität in GaN Technologie kann auf die kleine Rückkopplungskapazität ( $C_{GD}$ ) im Vergleich zur Eingangs- ( $C_{GS}$ ) und Ausgangskapazität ( $C_{DS}$ ) zurückgeführt werden. Speziell für die übliche Umgebungsimpedanz von  $Z_0 = 50 \Omega$  ist die niederfrequente Stabilitätsanforderung and das Verhältnis von  $C_{GD}$  zu  $C_{GS}$  und  $C_{DS}$  äußerst hoch. Mit steigendem  $Z_0$  und höheren Transitfrequenzen ( $f_T$ ), sprich kleinerem  $C_{GS}$  und größerem  $g_m$ , verringert sich die Anforderung an das notwendige Kapazitätsverhältnis. Basierend auf diesen theoretischen Erkenntnissen wurden Gegenmaßnahmen zur Gleichtaktstabilisierung abgeleitet, wie z. B. das Hinzufügen einer parallelen Rückkopplung, das Entfernen der Gate-Source Feldplatten oder durch eine induktive Kompensation der parasitären Kapazität der Versorgungsstromquelle und diese mit Hilfe des DC-6 GHz TD-FBPA Designs verifiziert.

Für einen ähnlichen Frequenzbereich von DC-6.5 GHz wurde ein linearisierter rauscharmer TWA (L<sup>2</sup>NTWA) mit integriertem Dioden-Vorverzerrungskonzept zum ersten Mal in einer verteilten Struktur entworfen, mit dem Ziel gleichzeitig hohe Linearität und geringes Rauschen in einem 2 W PA zu erzielen. Mit Hilfe einer externen Dioden-Abstimmspannung können die geraden als auch ungeraden Harmonischen bis zu einem bestimmten Grad gegeneinander abgewägt werden ohne die Verstärkung oder die Eingangs-/Ausgangsanpassung des L<sup>2</sup>NTWAs signifikant zu verschlechtern. Die Messungen des assemblierten gehäusten MMICs zeigen einen flachen Verstärkungsverlauf von größer 14 dB über einen Frequenzbereich von 10 MHz bis fast hoch zu 7 GHz, wobei die untere Grenzfrequenz lediglich von den Werten der externen SMD Komponenten bestimmt wird. Die Linearitätsmessungen haben zusätzlich gezeigt, dass eine hohe Linearität mit einem maximalen störungsfreien dynamischen Bereich (*SFDR*) von -38 dBc bei einer Ausgangsleistung von  $P_{OUT} = 25$  dBm und ein *OIP3* von größer als 42 dBm bei optimaler Dioden-Abstimmspannung erreicht wird. Messungen der Rauschzahl (*NF*) haben ein minimum von 1.8 dB bei 2 GHz für den nominalen Arbeitspunkt von  $V_{DS} = 28$  V and  $I_{DS} = 200$  mA/mm ergeben. In Kombination mit einem  $P_{1dB}$  von über 1 W über das komplette Frequenzband ordnet sich dieses Design in die Hochleistungs-LNA-Klasse ein und ist somit geeignet als hoch lineare und rauscharme Treiberstufe für den vorher erwähnten DC-6 GHz FBPA oder TD-FBPA.

Konventionelle TWAs weisen in der Regel einen erheblichen Anstieg des Rauschens zu niedrigen Frequenzen auf, was diese Verstärkertopologie in Bezug auf ihr Rauschverhalten für die niederfrequente Anwendung in Messgeräten ungeeignet macht. Mit Hilfe eines DC - 15 GHz Referenzdesigns wurde der steile Anstieg der NF unterhalb von 2 GHz messtechnisch verifiziert, nachdem alle Rauschquellen identifiziert wurden. Die zugehörigen Rauschübertragungsfunktionen zum Ausgang wurden jeweils mathematisch berechnet und der Beitrag zur gesamten NF analytisch bewertet. Der größte Anteil des niederfrequenten Rauschens stammt von den Gate-Vorspannwiderständen für den Fall, dass die Gates kapazitiv gekoppelt sind. Ist dies nicht der Fall, dann steuert der Gate-Leitungsabschlusswiderstand aufgrund des typischen Verlaufs der Rückwärtsübertragungsfunktion von der Abschlusslast zum Ausgang den zweitgrößten Rauschanteil bei niedrigen Frequenzen bei. Um diesen Rauschbeitrag zu minimieren wurden drei unterschiedliche rauscharme Lastkonzepte (ACL) untersucht und theoretisch analysiert, um die am besten geeignete Topologie für TWAs zu identifizieren. Von diesen drei ACL-Konzepten erwies sich die Common-Source Topologie mit paralleler Rückkopplung (CS-PRF) als äußerst geeignet. Dabei gibt es prinzipiell zwei verschiedene Ansätze, um die Gate-Leitung mittels der CS-PRF abzuschließen. Beim ersten Ansatz wird die letzte aktive Stufe im TWA ersetzt wohingegen beim zweiten Ansatz der resistive Gate-Leitungsabschlusswiderstand direkt ersetzt wird. Letztere Methode zeigt ausgehend von einer vereinfachten mathematischen Analyse, dass diese die vielversprechendere Lösung in Bezug auf die Verstärkung und die Ausgangsanpassung des TWAs ist. Dennoch sind beide Ansätze effektive Maßnahmen, um das niederfrequente Rauschen in TWAs zu minimieren. Basierend auf der vorhergehenden Analyse wurde das CS-PRF Konzept mit einem vorgeschalteten RLC-Filter kombiniert, um eine breitbandigere Eingangsanpassung des

TWAs zu ermöglichen. Diese Schaltung wird auch als "aktive blaue Rauschlast" (BNAT) bezeichnet, da ihr resultierender Rauschfrequenzgang in Analogie zum Lichtspektrum blauem Licht entspräche. Zur Verifizierung wurde die BNAT zunächst auf einem separaten Chip entworfen, um die generelle Funktionalität messtechnisch zu verifizieren. Nach erfolgreicher Überprüfung des Konzeptes wurde die BNAT als Gate-Leitungsabschlusslast zum bestehenden L<sup>2</sup>NTWA Design hinzugefügt, um den Grad der niederfrequenten *NF* Verbesserung im Vergleich zu einer resistiven Abschlusslast zu evaluieren. Die Rauschmessungen ergaben eine Verbesserung der *NF* um 1.9 dB von 5.5 dB mit resistiver Last auf 3.6 dB mit aktiver Rauschlast (BNAT).

# TABLE OF CONTENTS

| Abstract        |                                        |

|-----------------|----------------------------------------|

| Kurzfassung     | V                                      |

| Table of Conte  | ntsIX                                  |

| List of Figures |                                        |

| List of Tables. |                                        |

| List of Symbol  | sXIX                                   |

| Abbreviations   | XX                                     |

| CHAPTER 1       | Introduction                           |

| 1.1             | Motivation                             |

| 1.2             | Challenges and Questions               |

| 1.3             | "State-of-the-Art" Broadband GaN PAs   |

| 1.4             | Thesis Synopsis                        |

| CHAPTER 2       | GaN Technology and Modeling            |

| 2.1             | GaN Technology                         |

|                 | 2.1.1 AlGaN/GaN on SiC                 |

|                 | 2.1.2 HEMT Technology1                 |

|                 | 2.1.3 IAF GaN25 Technology             |

| 2.2             | Modeling of GaN HEMTs14                |

|                 | 2.2.1 Small-Signal Modeling            |

|                 | 2.2.2 Large-Signal Modeling            |

|                 | 2.2.3 Noise Modeling                   |

| CHAPTER 3       | Broadband Power Amplifiers             |

| 3.1             | Amplifier Classes                      |

| 3.2             | Matching                               |

|                 | 3.2.1 Small-Signal Matching            |

|                 | 3.2.2 Theory of Optimum Power Matching |

|                 | 3.2.3 Load-Line Matching in TWAs       |

| 3.3             | Feedback Power Amplifiers              |

|                 | 3.3.1 Transfer Characteristics         |

|                 | 3.3.2 Noise Analysis of FBPAs          |

|                 | 3.3.3 FBPA Design Criteria             |

|                 | 3.3.4 DC - 6 GHz Feedback PA Design    |

|           | 3.3.5 Performance Improvement Measures                                      | 68  |

|-----------|-----------------------------------------------------------------------------|-----|

|           | 3.3.6 Key Findings                                                          | 70  |

| 3.4       | Distributed Power Amplifiers                                                | 71  |

|           | 3.4.1 Transfer Characteristics                                              | 71  |

|           | 3.4.2 Capacitively Coupled TWA Biasing                                      | 74  |

|           | 3.4.3 Noise Analysis of TWAs                                                | 74  |

|           | 3.4.4 TWA Design Criteria                                                   | 89  |

|           | 3.4.5 DC – 15/20 GHz Traveling-Wave Amplifier Designs                       | 95  |

|           | 3.4.6 Performance Improvement Measures                                      | 101 |

|           | 3.4.7 Key Findings                                                          | 108 |

| CHAPTER 4 | Linearization Concepts                                                      | 111 |

| 4.1       | Linearity FoMs                                                              | 113 |

|           | 4.1.1 Harmonic Distortion                                                   | 113 |

|           | 4.1.2 Intermodulation Distortion                                            | 114 |

| 4.2       | GaN HEMT Nonlinearities                                                     | 119 |

|           | 4.2.1 Investigation of Channel-Current Nonlinearities                       | 121 |

|           | 4.2.2 Investigation of Gate-Source Capacitor Nonlinearities                 | 127 |

|           | 4.2.3 Key Findings                                                          | 130 |

| 4.3       | Parallel and Series Feedback Linearization                                  | 131 |

|           | 4.3.1 Linearity in Feedback Systems                                         | 131 |

|           | 4.3.2 Linearization in GaN FBPAs                                            | 133 |

|           | 4.3.3 Key Findings                                                          | 136 |

| 4.4       | Staggering Drain-Line Principle in TWAs                                     | 137 |

|           | 4.4.1 Harmonic Distortion                                                   | 137 |

|           | 4.4.2 Intermodulation.                                                      | 141 |

|           | 4.4.3 Key Findings                                                          | 143 |

| 4.5       | Derivative Superposition Method                                             | 144 |

|           | 4.5.1 General DSM Principle                                                 | 144 |

|           | 4.5.2 Evaluation of DSM for GaN                                             | 147 |

|           | 4.5.3 Key Findings                                                          | 151 |

| 4.6       | Nonlinear Diode Predistortion                                               | 152 |

|           | 4.6.1 Principle of Diode Predistortion                                      | 152 |

|           | 4.6.2 DC – 6.5 GHz Highly Linear Low Noise TWA Design                       | 155 |

|           | 4.6.3 Key Findings                                                          | 160 |

| 4.7       | Truly and Pseudo-Differential Linearization                                 | 161 |

|           | 4.7.1 Even-Order Harmonic Cancellation                                      |     |

|           | 4.7.2 Susceptibility to Phase & Amplitude Imbalances and Process Variations | 162 |

|           | 4.7.3 The Series Feedback Dilemma in TD-amplifiers                          |     |

|             |        | 4.7.4 DC-6 GHz Truly-Differential PA Design                     | 171 |

|-------------|--------|-----------------------------------------------------------------|-----|

|             |        | 4.7.5 Key Findings                                              |     |

|             | 4.8    | Conclusion                                                      | 184 |

| CHAPTER     | R 5    | Noise Reduction Schemes                                         | 187 |

| :           | 5.1    | Feedforward Noise Cancellation in FBPAs                         |     |

|             |        | 5.1.1 General FFNC Principle                                    |     |

|             |        | 5.1.2 FFNC in FBPAs.                                            |     |

|             |        | 5.1.3 Key Findings                                              | 190 |

| :           | 5.2    | Active Gate-Line Termination in TWAs                            | 191 |

|             |        | 5.2.1 Common-Gate ACL                                           | 191 |

|             |        | 5.2.2 Common-Source ACL with Series Inductive Feedback          | 193 |

|             |        | 5.2.3 Common-Source ACL with Parallel Resistive Feedback        | 195 |

|             |        | 5.2.4 Comparison of ACL Concepts                                | 197 |

|             |        | 5.2.5 ACL Termination as Last Stage in TWAs                     | 200 |

|             |        | 5.2.6 BNAT in DC-6.5 GHz Highly Linear Low Noise TWA            |     |

|             |        | 5.2.7 Key Findings                                              | 210 |

| :           | 5.3    | Conclusion                                                      | 212 |

| CHAPTER     | R 6    | Stability Investigation of Differential Amplifiers              | 215 |

|             | 6.1    | Theoretical Stability Investigation of an Unmatched TD-pair     | 215 |

|             |        | 6.1.1 Stability Dependence on the Current-Source Capacitance    | 218 |

|             |        | 6.1.2 Stability Dependence on the Current-Source Resistance     |     |

|             |        | 6.1.3 Stability Dependence on Intrinsic HEMT Parameters         | 221 |

|             | 6.2    | Stability Investigation of a DC – 6 GHz Truly-Differential FBPA | 224 |

|             | 6.3    | Conclusion                                                      |     |

| Final Conc  | lusio  | on and Outlook                                                  |     |

| List of Pub | olicat | ions                                                            | 233 |

| References  |        |                                                                 | 234 |

| Appendix A  | A      |                                                                 | 244 |

| Appendix I  | В      |                                                                 | 246 |

| Appendix (  | С      |                                                                 | 249 |

| Appendix I  | D      |                                                                 | 251 |

| Appendix I  | E      |                                                                 | 257 |

|             |        |                                                                 |     |

# LIST OF FIGURES

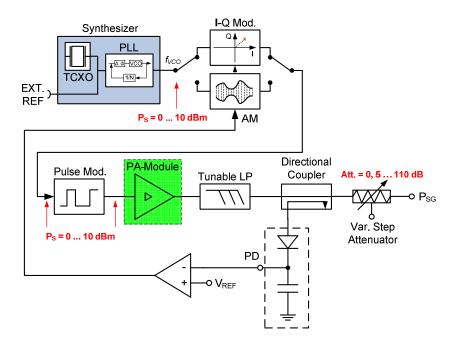

| Fig. 1-1: Typical component blocks of an analog/vector microwave signal generator                                                                                                                                       | 2      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

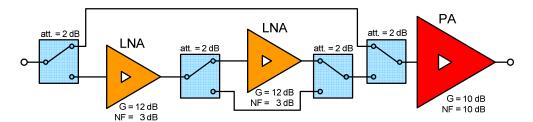

| Fig. 1-2: PA module of microwave signal generator with typical commercial MMICs                                                                                                                                         | 3      |

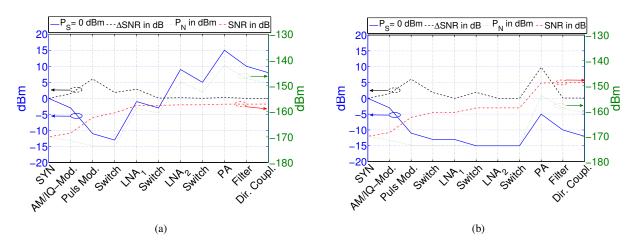

| Fig. 1-3: Power-levels in SG chain for <i>PS</i> = 0 dBm with (a) 2 LNAs + PA and (b) PA only                                                                                                                           | 4      |

| Fig. 2-1: Bandgap vs. lattice constant for different semiconductor materials ((□) III-V,(○) IV-IV,(◊) II-VI)                                                                                                            | 10     |

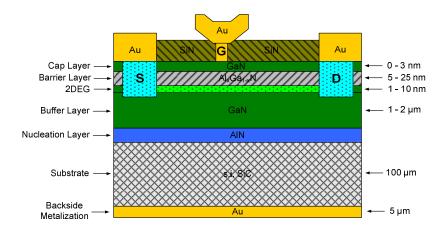

| Fig. 2-2: Cross-section of a AlGaN/GaN HEMT on SiC                                                                                                                                                                      | 11     |

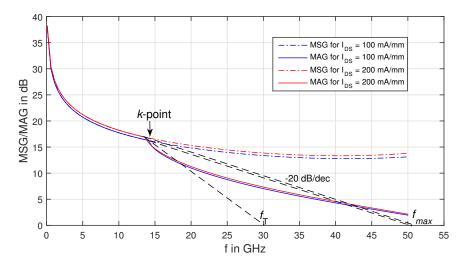

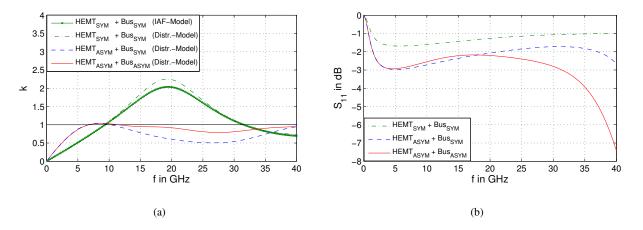

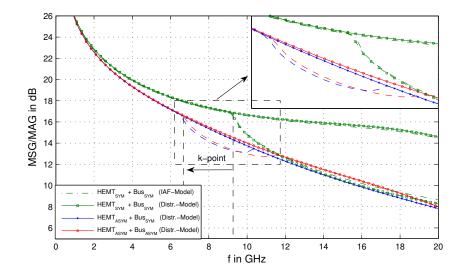

| Fig. 2-3: <i>MSG/MAG</i> vs. <i>f</i>                                                                                                                                                                                   | 12     |

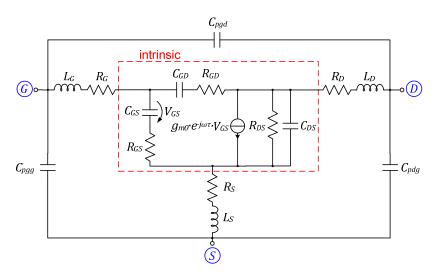

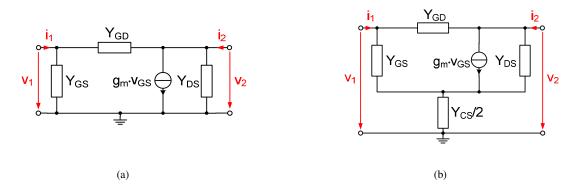

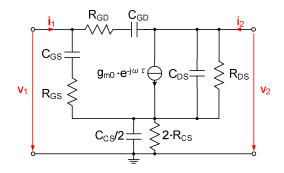

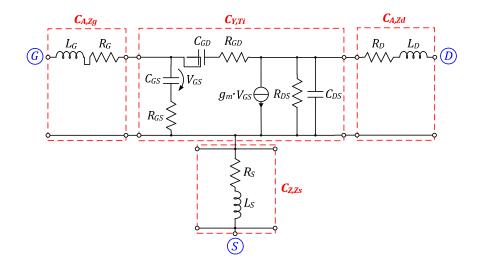

| Fig. 2-4: HEMT equivalent small-signal model with extrinsic parasitic shell                                                                                                                                             | 14     |

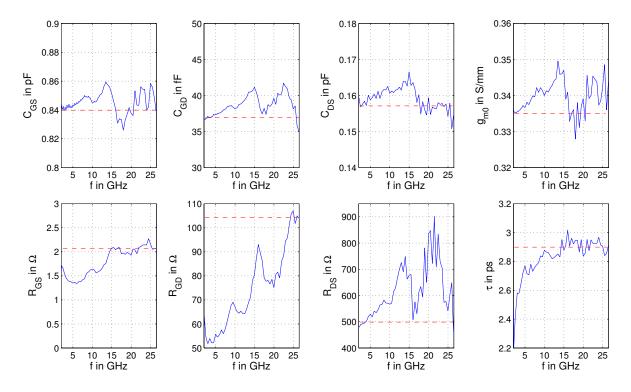

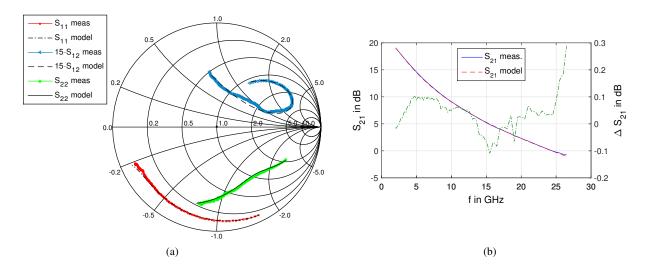

| Fig. 2-5: Extracted intrinsic HEMT model parameters of an 8×50µm HEMT in the frequency range from 2 GHz to 20 GHz at VDS = 28 V and IDS = 200 mA/mm                                                                     |        |

| Fig. 2-6: Measured and modelled (a) S11, 15. S12 and S21 and (b) S21 vs. frequency of a de-embedded 8×50µm HE                                                                                                           | EMT    |

| Fig. 2-7: Large-signal modeling classes                                                                                                                                                                                 |        |

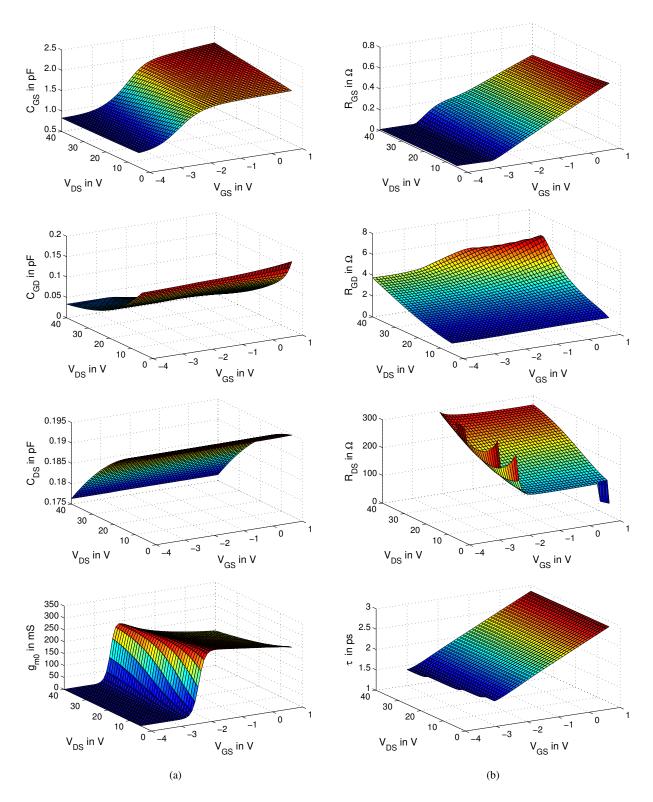

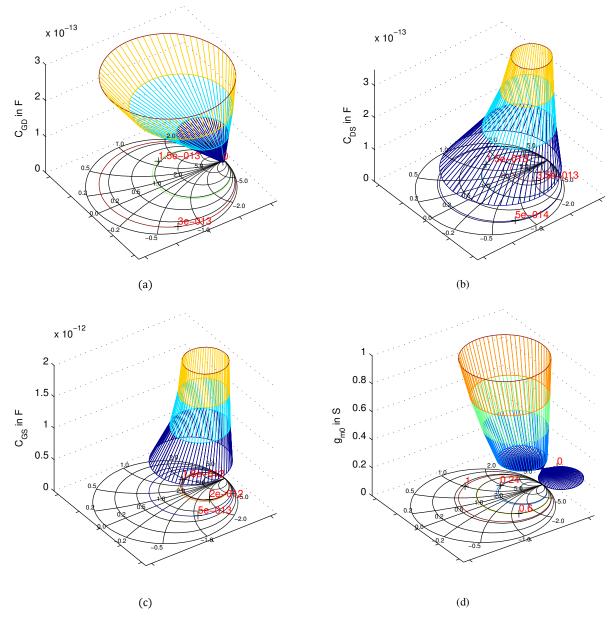

| Fig. 2-8: Intrinsic HEMT parameters dependent on VGS and VDS according to the IAF nonlinear state-space voltage-                                                                                                        |        |

| model for a 8×125µm GaN HEMT.                                                                                                                                                                                           | -      |

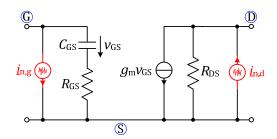

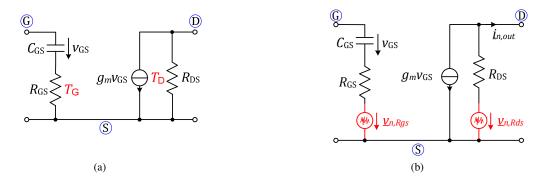

| Fig. 2-9: Schematic of Pucel's small-signal noise model                                                                                                                                                                 | 21     |

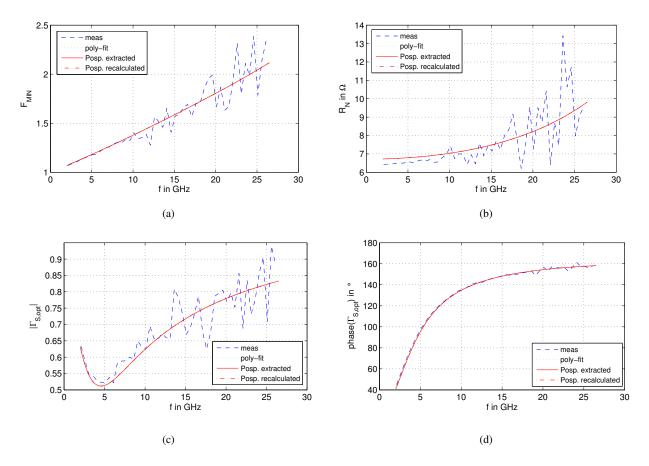

| Fig. 2-10: Schematic of Pospieszalski's small-signal noise model (a) with equivalent noise temperatures and (b) equiv<br>noise voltage sources                                                                          |        |

| Fig. 2-11: Schematic of Pospieszalski's small-signal noise model with corresponding noise voltage sources for the                                                                                                       |        |

| calculation of the equivalent input and output short circuit noise currents of Pucel's equivalent noise model                                                                                                           | 124    |

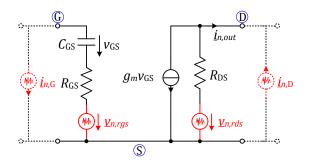

| Fig. 2-12: Equivalent noise parameters of (a) Pospieszalski's ( $TG = 297 \text{ K}$ , $TD \approx 6014 \text{ K}$ ) and (b) Pucel's ( $P = 0.9, R$ )                                                                   |        |

| Imc = 0.816) small-signal noise model from (2.26)-(2.30) for a 8×125µm low-noise device                                                                                                                                 |        |

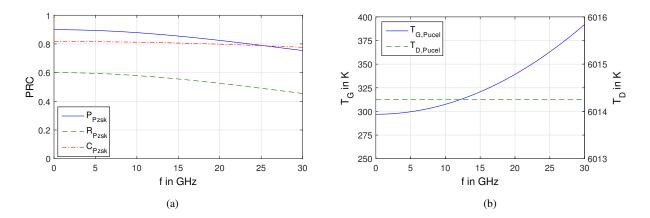

| Fig. 2-13: Measured and modelled noise parameters of a $8 \times 50 \mu$ m HEMT at VDS = 28 V and IDS = 200 mA/mm                                                                                                       |        |

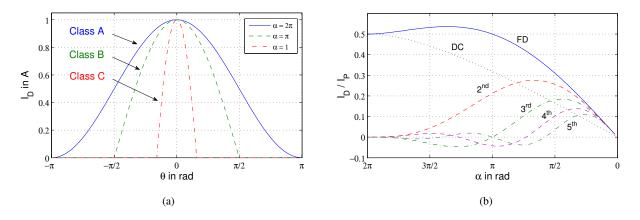

| Fig. 3-1: (a) $ID$ vs. $\theta$ in rad for the operational classes A,B and C and (b) normalized Fourier components of $In$ vs. the                                                                                      |        |

| conduction angle $\alpha$                                                                                                                                                                                               |        |

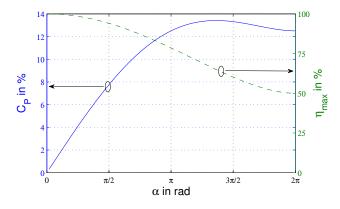

| Fig. 3-2: Normalized power capability <i>CP</i> and maximum effiency $\eta max$ vs. conduction angle $\alpha$                                                                                                           | 32     |

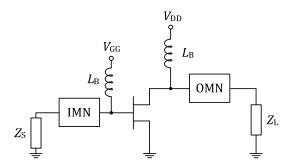

| Fig. 3-3: Schematic of common-source HEMT with input- and output matching networks                                                                                                                                      | 33     |

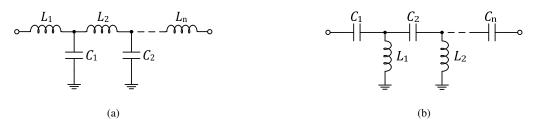

| Fig. 3-4: (a) LC-low pass and (b) CL-high pass matching network                                                                                                                                                         | 34     |

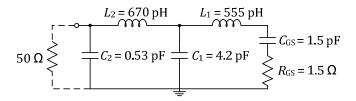

| Fig. 3-5: 2-stage LC-low pass matching for a $8 \times 125 \mu m$ HEMT input impedance to 50 $\Omega$ source impedance match                                                                                            | 35     |

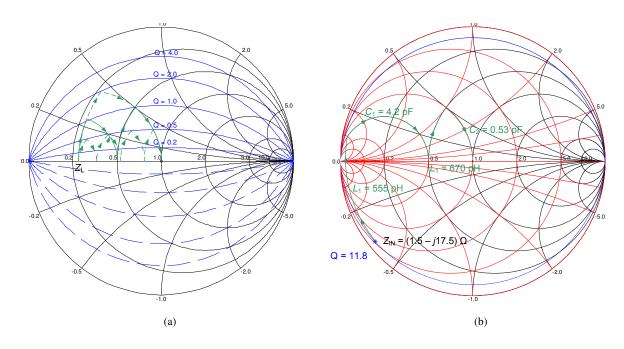

| Fig. 3-6: (a) constant <i>Q</i> -factor curves for <i>RLC</i> -networks with $Q < 0.5$ , 1 and 2 and (b) 2-stage <i>LC</i> input matching for a input match of a $8 \times 125 \mu$ m HEMT to 50 $\Omega$ at 6 GHz.     |        |

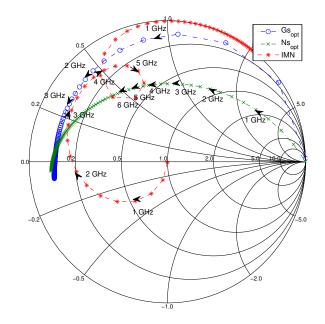

| Fig. 3-7: Source reflection circles for max. unilateral gain and optimum noise match for a low-noise 8×125um GaN H                                                                                                      |        |

| at VDS = 15 V and IDS = 200 mA/mm                                                                                                                                                                                       |        |

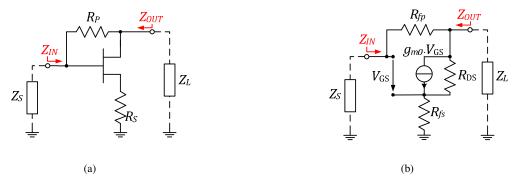

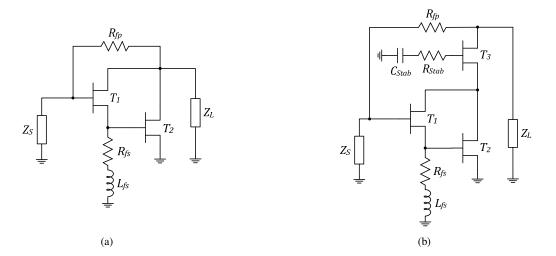

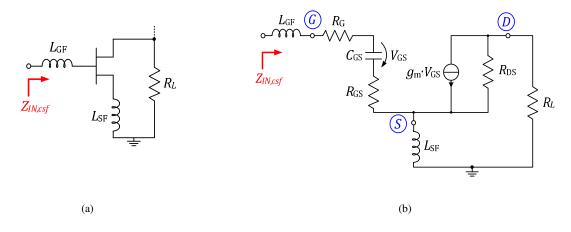

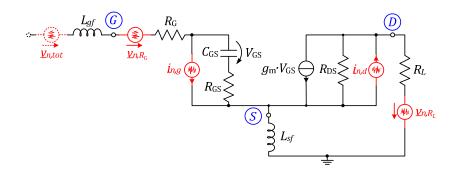

| Fig. 3-8: (a) CS-HEMT with parallel and series feedback and (b) simplified equivalent circuit for DC matching                                                                                                           |        |

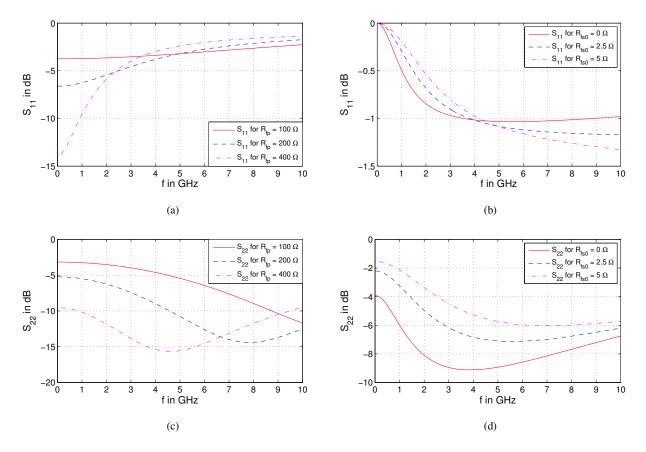

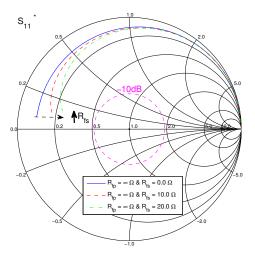

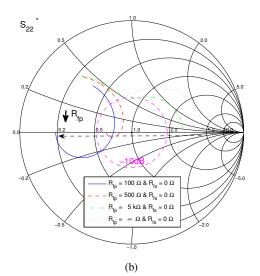

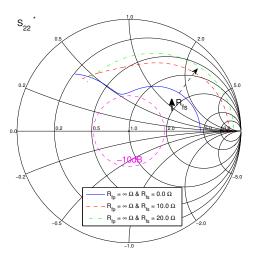

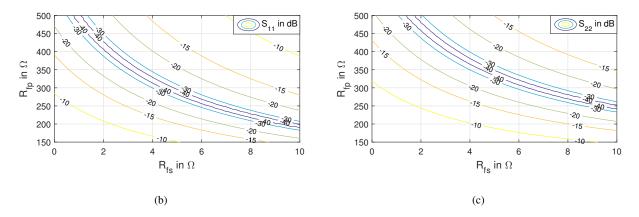

| Fig. 3-9: Simulated (a,b) S11 and (c,d) S22 of parallel ( <i>Rfp</i> ) (left) and series ( <i>Rfs</i> ) (right) resistive feedback matchin 8×125µm HEMT                                                                 | -      |

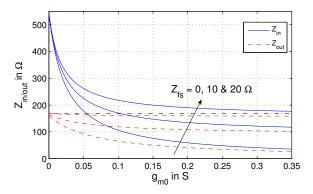

| Fig. 3-10: Calculated ZIN and ZOUT vs. $gm0$ of a 8×125um GaN HEMT with parallel and series feedback for $Zfp$                                                                                                          |        |

| $\Omega$ and $Zfs = 0,1020 \Omega$                                                                                                                                                                                      |        |

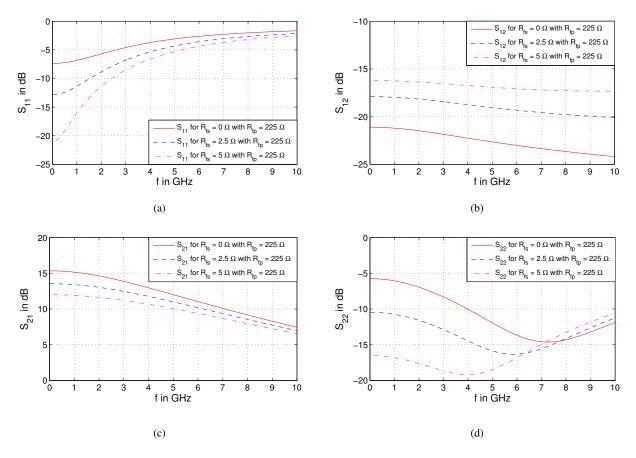

| Fig. 3-11: Simulated (a) S11, (b) S12, (c) S21 and (d) S22 for low frequency matching of a $8 \times 125 \mu m$ HEMT by mean parallel ( $Rfp = 225 \Omega$ ) and series ( $Rfs = 0, 2.5, 5 \Omega$ ) resistive feedback | ans of |

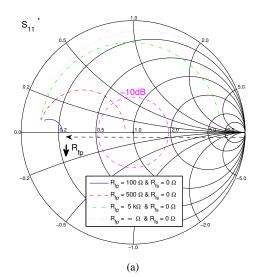

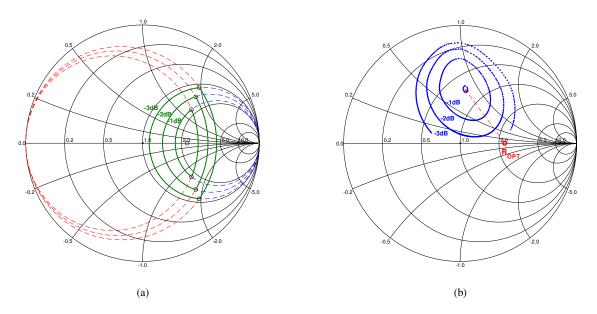

| Fig. 3-12: Simulated S11 * and S22 * trajectories of (a,b) only parallel ( $Rfp$ ), (c,d) only series ( $Rfs$ ) and (e,f) parallel                                                                                      |        |

| series resistive feedback matching of a $8 \times 125 \mu$ m HEMT in the frequency range from DC – 20 GHz                                                                                                               |        |

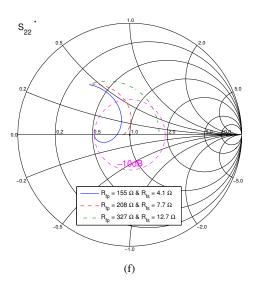

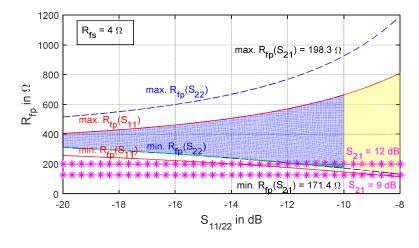

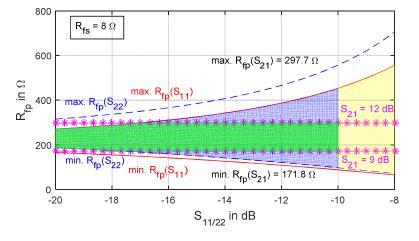

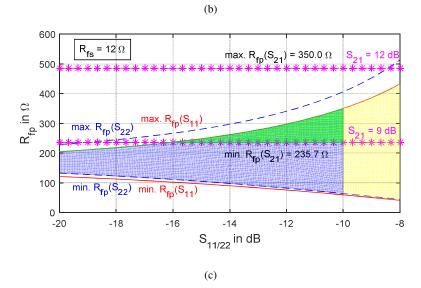

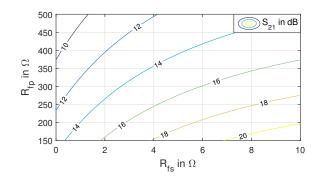

| Fig. 3-13: Calculated $Zfp$ vs. $S11/22$ of a 8×125µm GaN HEMT with parallel and series feedback for (a) $Zfs = 4 \Omega$                                                                                               |        |

| (b) $Zfs = 8 \Omega$ and (c) $Zfs = 12 \Omega$                                                                                                                                                                          |        |

| Fig. 3-14: Calculated (a) $S21$ , (b) $S11$ and (c) $S22$ of a $8 \times 125$ um GaN HEMT for different $Rfs$ and $Rfp$                                                                                                 |        |

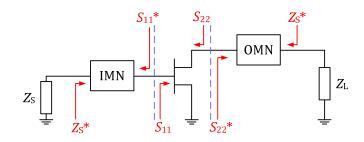

| Fig. 3-15: Schematic of a complex conjugate matched transistor to the source and load impedance ZS and ZL                                                                                                               |        |

| Fig. 3-16: (a) ideal <i>I-V</i> -curves of HEMT with optimum load-line and (b) simulated DC and pulsed isothermal <i>I-V</i> -cur                                                                                       |        |

| an $8 \times 125 \mu$ m GaN HEMT, including the recommended max. power dissipation hyperbola for <i>Pdiss</i> = 8 W                                                                                                     |        |

|                                                                                                                                                                                                                         | 45     |

| Fig. 3-17: Large-signal output matching for (a) series reactance and (b) parallel susceptance delivering constant output power to <i>RL</i> , <i>lo</i> and <i>RL</i> , <i>hi</i>                                                               | 46  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

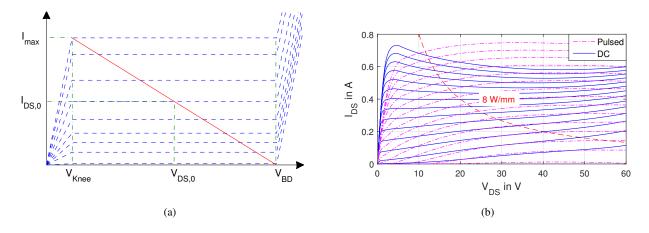

| Fig. 3-18: (a) Calculated ideal load-pull contours according to Fig. 3-17 and (b) simulated load-pull constours of a $8 \times 125 \mu m$ HEMT at $f = 6$ GHz and $Pin = 26$ dBm                                                                |     |

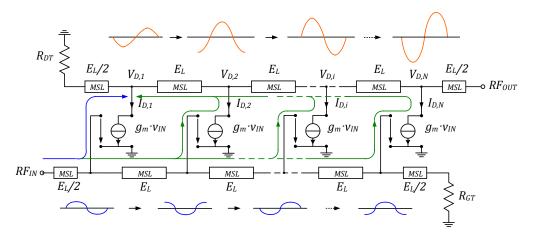

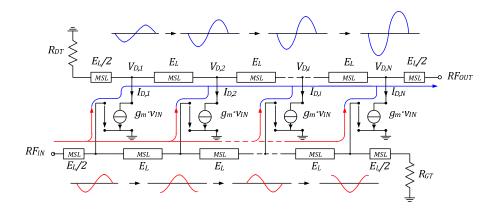

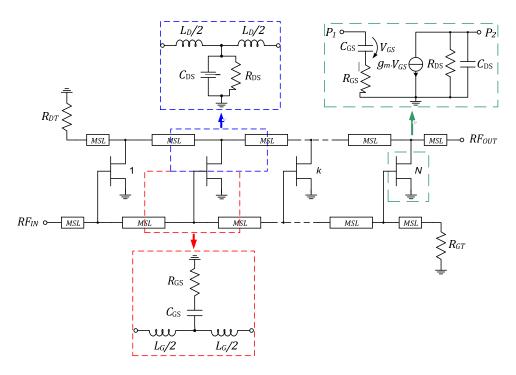

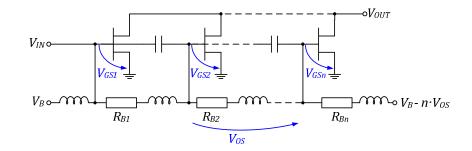

| Fig. 3-19: Simplified schematic of a <i>N</i> -stage UDPA                                                                                                                                                                                       |     |

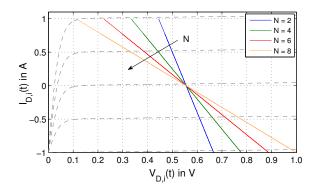

| Fig. 3-20: Normalized transistor load-lines in a UDPA for $N = 2,4,6 \& 8$ at $El = 0^{\circ}$                                                                                                                                                  |     |

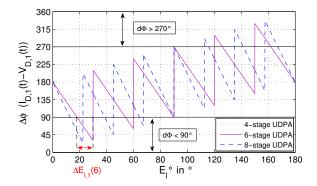

| Fig. 3-21: Phase difference at the drain terminal of the 1st gain-stage between current <i>ID</i> , $1(t)$ and voltage <i>VD</i> , $1(t)$ for 4, 6, 8.                                                                                          | N = |

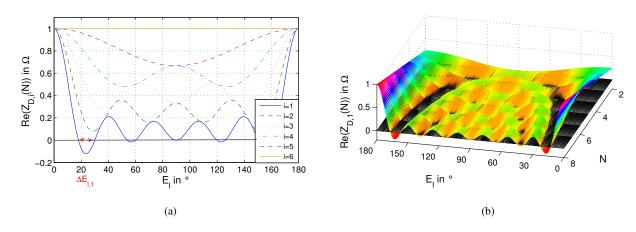

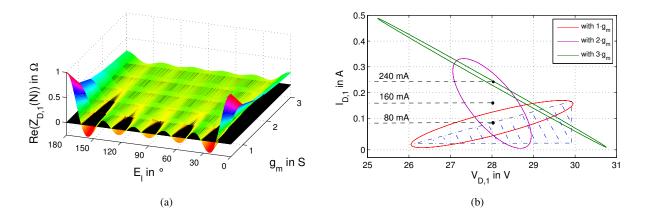

| Fig. 3-22: Normalized (a) $Re\{ZD, i(N)\}$ vs. El for $N = 6$ and $i = 1, 26$ and (b) $Re\{ZD, 1(N)\}$ vs. El and N for $ZL = 50$                                                                                                               | Ω ( |

| Fig. 3-23: (a) normalized $Re{ZD, 1(N)}$ vs. El & $gm$ for $N = 6$ and (b) load-lines of 1st transistor of the DC-15 GHz UDPA                                                                                                                   |     |

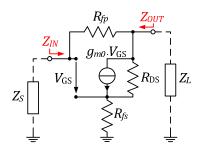

| Fig. 3-24: Equivalent circuit of FBPA with series and parallel resistive feedback at DC.                                                                                                                                                        | 53  |

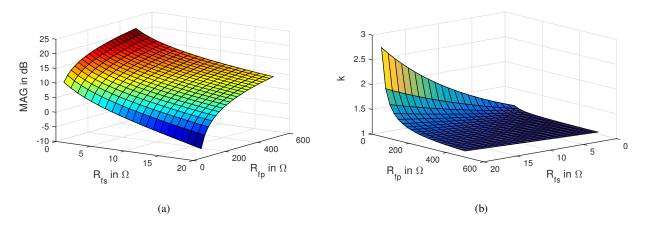

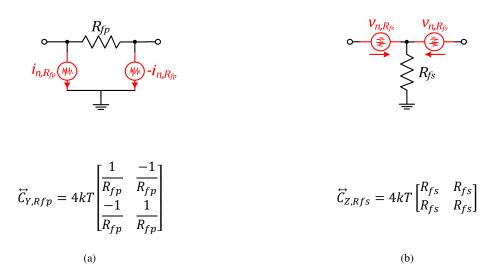

| Fig. 3-25: (a) MAG and (b) Rollett's stability factor k vs. Rfp and Rfs of a FBPA at DC with a 8×125um HEMT                                                                                                                                     | 54  |

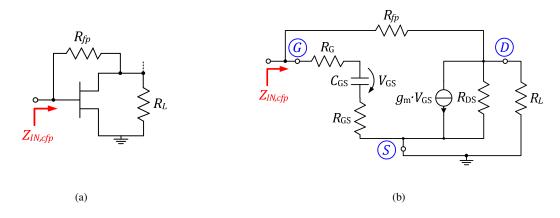

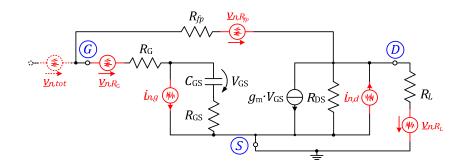

| Fig. 3-26: (a) parallel and (b) series resistive-feedback and its corresponding noise representation                                                                                                                                            | 56  |

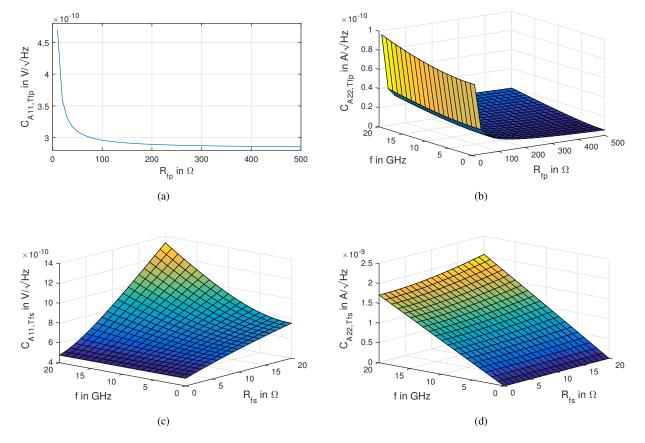

| Fig. 3-27: Dependency of (a) $CA11$ , $Tfp$ on $Rfp$ , (b) $CA22$ , $Tfp$ on $Rfp$ and $f$ , (c) $CA11$ , $Tfs$ on $Rfs$ and $f$ and (d) $CA22$ , $Tfs$ on $Rfs$ and $f$ for a $8 \times 125 \mu$ m HEMT                                        | 59  |

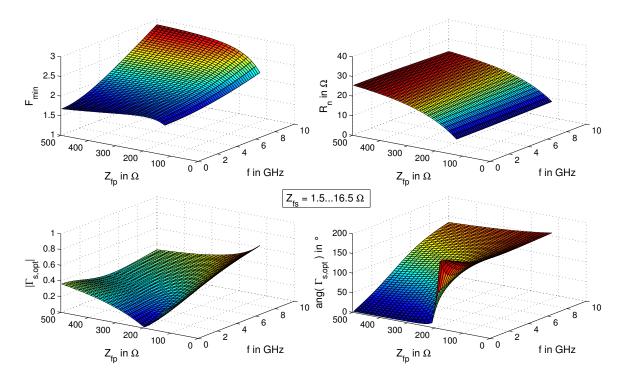

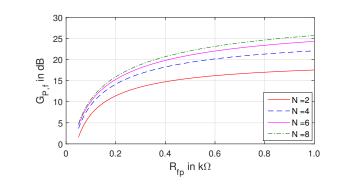

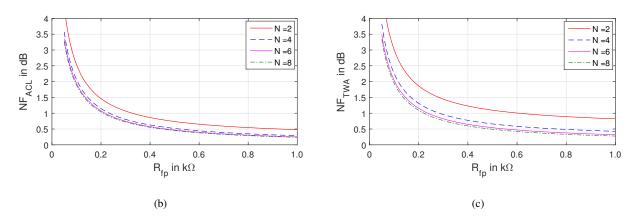

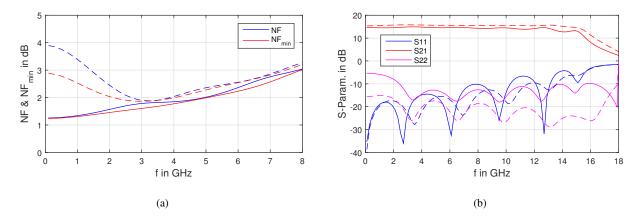

| Fig. 3-28: <i>Fmin</i> , <i>Rn</i> , $\Gamma s$ , <i>opt</i> and $\measuredangle \Gamma s$ , <i>opt</i> vs. <i>f</i> and vs. <i>Rfp</i> for S21= 10 dB ( <i>Rfs</i> = 1.516.5 $\Omega$ ) of an 8×125µm HE applying parallel and series feedback |     |

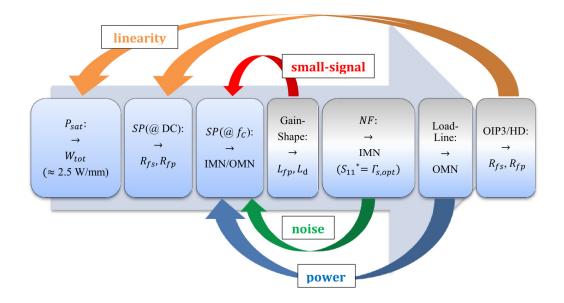

| Fig. 3-29: Flow-chart for FBPA design guidelines                                                                                                                                                                                                |     |

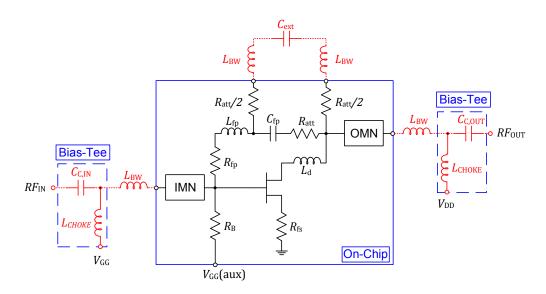

| Fig. 3-30: Schematic of FBPA applying series and parallel resistive feedback with off-chip low frequency extension                                                                                                                              |     |

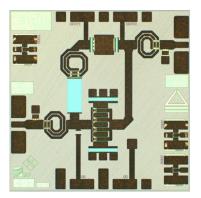

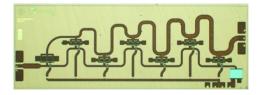

| Fig. 3-31: Photograph of DC-6 GHz Feedback MMICs (a) Futago_V1, (b) Futago_V2 and (c) Futago_V3                                                                                                                                                 |     |

| Fig. 3-32: Measured (a) S21 and (b) S11 and S22 of the DC-6 GHz FBPA "Futago_V3" in package at VDS = 28 V and = 200 mA/mm.                                                                                                                      |     |

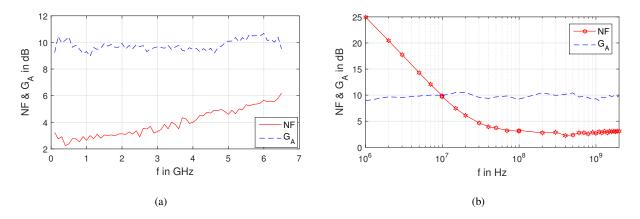

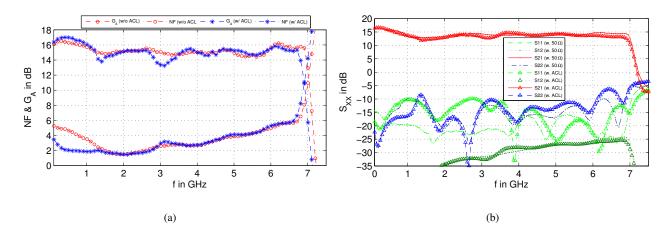

| Fig. 3-33: Measured <i>NF</i> and <i>GA</i> for (a) 1-6 GHz and (b) 10 MHz - 2 GHz of the DC-6 GHz FBPA "Futago_V3" in package at <i>V</i> DS = 28 V and <i>I</i> DS = 200 mA/mm                                                                | 66  |

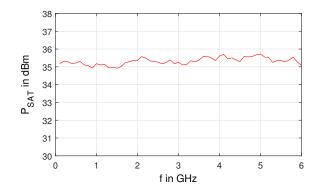

| Fig. 3-34: Measured <i>Psat</i> of the DC-6 GHz Feedback MMIC Futago_V3 in package at <i>V</i> DS = 28 V and <i>I</i> DS = 200 mA/mm.                                                                                                           | 67  |

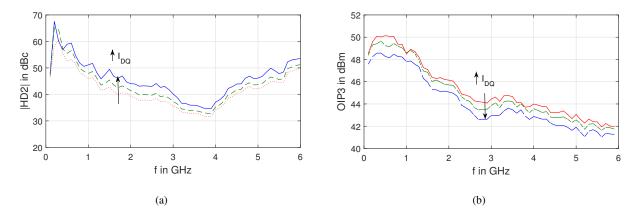

| Fig. 3-35: Measured (a) <i>HD</i> 2 at <i>Pout</i> = 25 dBm and (b) <i>OIP</i> 3 with $\Delta f$ = 5 MHz of the DC-6 GHz Feedback MMIC                                                                                                          |     |

| Futago_V3 in package for VDS = 28 V and IDS = 200, 225 & 250 mA/mm                                                                                                                                                                              | 67  |

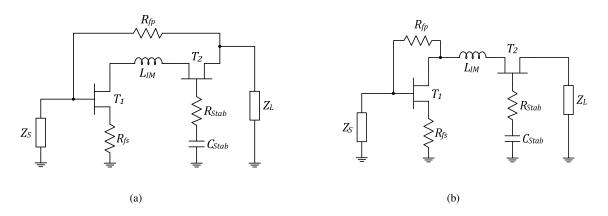

| Fig. 3-36: Schematic of Cascode FBPA with series and (a) parallel resistive feedback over CS-HEMT and (b) parallel resistive feedback over CS- and CG-HEMT                                                                                      | 68  |

| Fig. 3-37: Schematic of FBPA with (a) Darlington-stage and (b) Cascode Darlington-stage applying series and parallel resistive feedback.                                                                                                        |     |

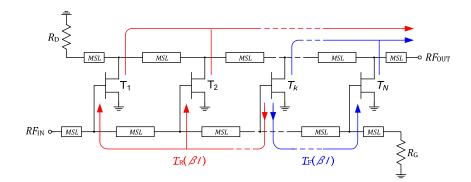

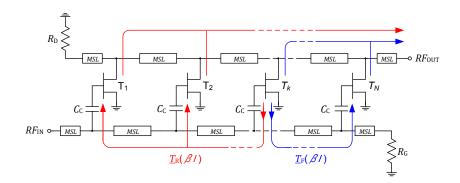

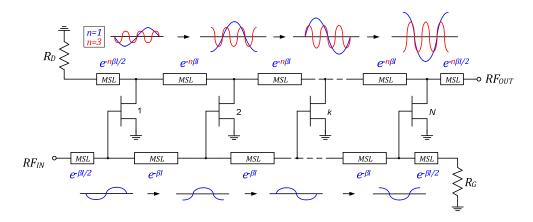

| Fig. 3-38: Conventional uniform TWA topology with voltage controlled current sources as active elements                                                                                                                                         |     |

| Fig. 3-39: Conventional uniform TWA topology (UDPA)                                                                                                                                                                                             |     |

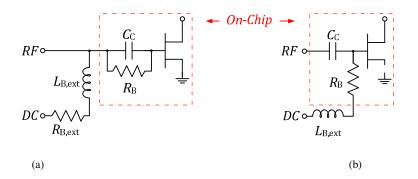

| Fig. 3-40: (a) parallel RC-biasing scheme and (b) separate biasing scheme for capacitively coupled TWA stages                                                                                                                                   |     |

| Fig. 3-41: Forward and reverse transfer functions $TF(\beta)$ and $TR(\beta)$ of a TWA                                                                                                                                                          | 76  |

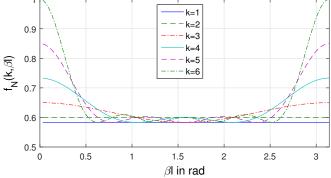

| Fig. 3-42: Normalized $fN(k,\beta l)$ vs. $\beta l$ for different k and $(N = 6)$ of TWA                                                                                                                                                        | 76  |

| Fig. 3-43: Forward and reverse transfer functions $TF(\beta l) \& TR(\beta l)$ in a CCTWA                                                                                                                                                       | 77  |

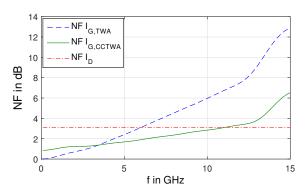

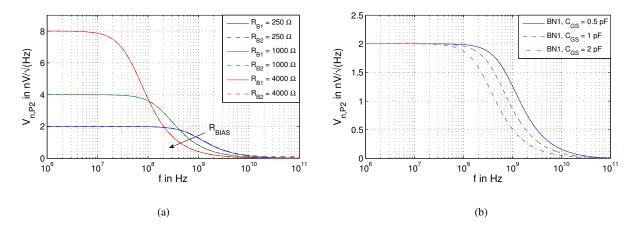

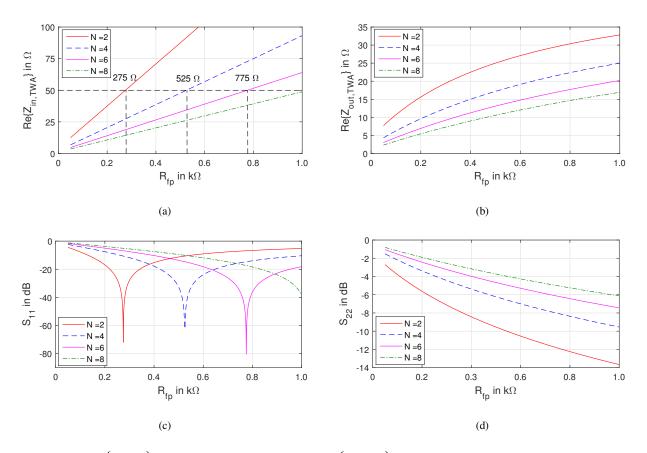

| Fig. 3-44: NF of induced-gate- and channel-noise for TWA & CCTWA with N = 6                                                                                                                                                                     | 79  |

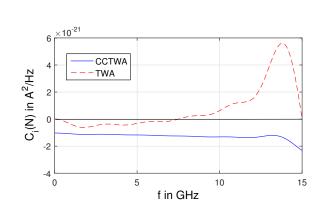

| Fig. 3-45: Simulated <i>Ci</i> vs. $f$ for a conventional TWA and a CCTWA with $N = 6$                                                                                                                                                          | 80  |

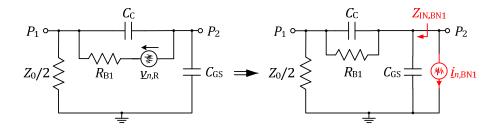

| Fig. 3-46: Equivalent noise representation for TWA's BN1 of Fig. 3-40 (a)                                                                                                                                                                       |     |

| Fig. 3-47: Equivalent noise representation for TWA's BN2 from Fig. 3-40 (b)                                                                                                                                                                     | 82  |

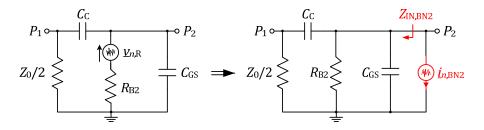

| Fig. 3-48: (a) noise voltage vs. $f$ at P2 for (a) BN1 and BN2 with $RB$ = 0.25, 1.0, 4.0 k $\Omega$ , $CGS$ = 0.5 pF, $CC$ = 0.25 pF, $Z$                                                                                                      |     |

| 50 $\Omega$ and (b) BN1 for CGS/CC sweep, $RB = 250 \Omega$ , $Z0 = 50 \Omega$ )                                                                                                                                                                |     |

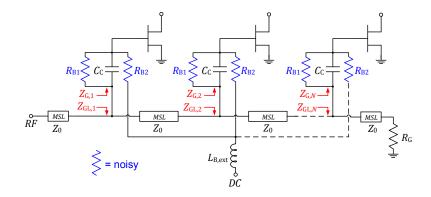

| Fig. 3-49: CCTWA with direct gate bias over RB1 and separate gate bias over RB2 with an external choke LB, ext                                                                                                                                  | 84  |

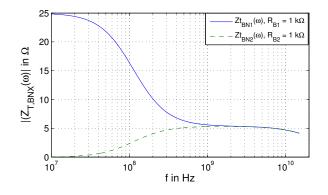

| Fig. 3-50: $ ZT, BNx(\omega) $ of BN1 and BN2                                                                                                                                                                                                   |     |

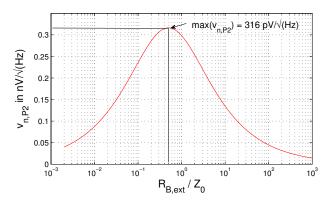

| Fig. 3-51: vn, P2 vs. RB, ext/Z0 of conventional biased TWA                                                                                                                                                                                     | 86  |

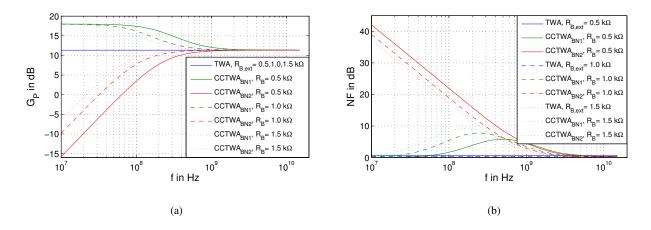

| Fig. 3-52: Computed (a) $GP$ and (b) $NF$ of conventional TWA and CCTWA with BN1 & BN2 ( $N = 6$ )                                                                                                                                              |     |

| Fig. 3-53: NF of TWA & CCTWA with BN1, BN2 and BN1+BN2                                                                                                                                                                                          | 89  |

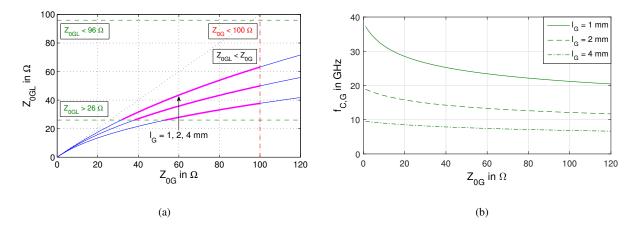

| Fig. 3-54: (a) loaded gate-line impedance $(Z0GL)$ vs. characteristic microstrip gate-line impedance $(Z0G)$ for different gate-line lengths $(lG)$ of 1,2 and 4 mm and (b) corresponding dependence of the gate-line cut-off frequency                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (fc, G) on ZOG $(CIN = 0.5  pF)$                                                                                                                                                                                                                                                                                                                                    |

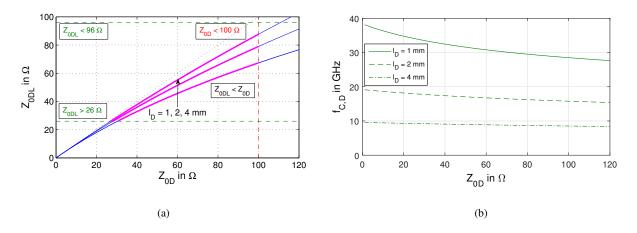

| <ul> <li>Fig. 3-55: (a) loaded drain-line impedance (Z0DL) vs. characteristic microstrip drain-line impedance (Z0D) for different drain-line lengths (<i>lD</i>) of 1,2 and 4 mm and (b) corresponding dependence of the drain-line cut-off frequency (<i>fc</i>, <i>D</i>) on Z0D (COUT = 0.1 pF)</li></ul>                                                        |

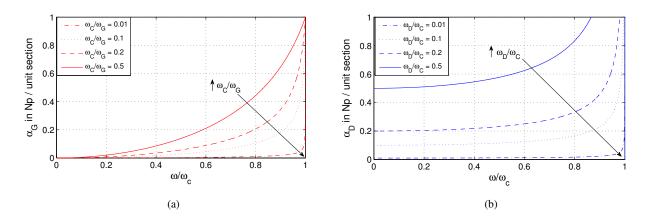

| Fig. 3-56: (a) gate-line attenuation $\alpha$ G and (b) drain-line attenuation $\alpha$ D vs. normalized frequency $\omega\omega c$                                                                                                                                                                                                                                 |

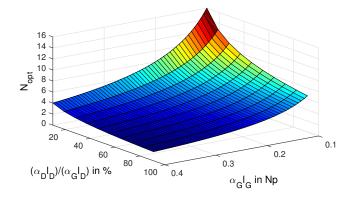

| Fig. 3-57: Calculated optimum number of stages Nopt dependent on gate- and drain-line attenuation                                                                                                                                                                                                                                                                   |

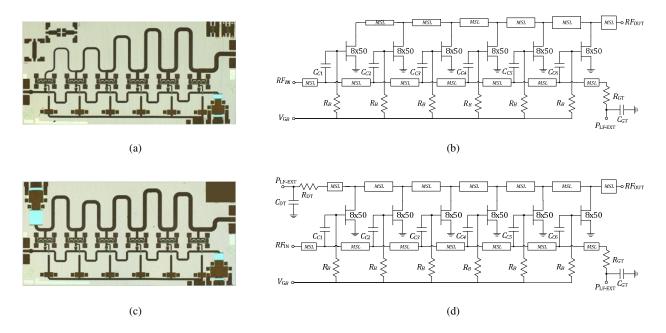

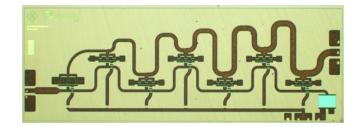

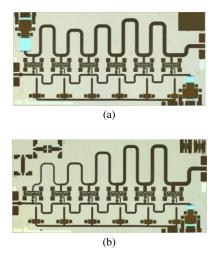

| Fig. 3-58: Photograph of the DC-15 GHz (a) nonuniform (Nasu) GaN TWA with schematic in (b) and (c) uniform GaN TWA (Unzen) with schematic in (d)                                                                                                                                                                                                                    |

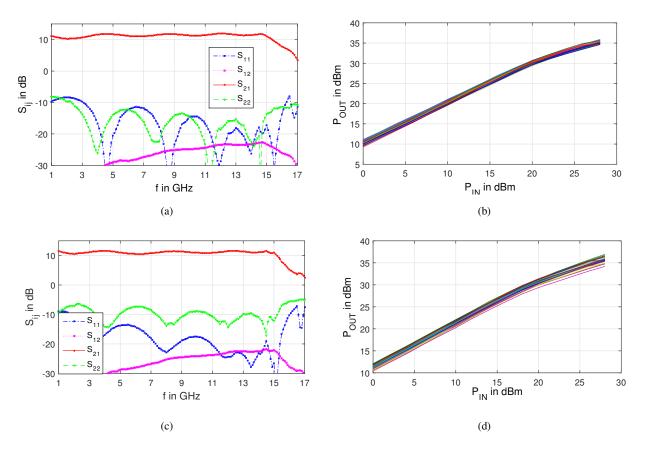

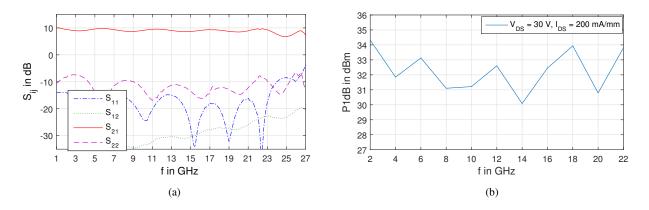

| Fig. 3-59: On-wafer measured (a) S-Parameter vs. f and (b) POUT vs. PIN of the DC-15 GHz uniform TWA (Unzen) and                                                                                                                                                                                                                                                    |

| (c) <i>S</i> -Parameter vs. <i>f</i> and (d) <i>POUT</i> vs. <i>PIN</i> of the DC-15 GHz nonuniform TWA (Nasu) for <i>V</i> DS = 28 V and <i>I</i> DS = 200 mA/mm                                                                                                                                                                                                   |

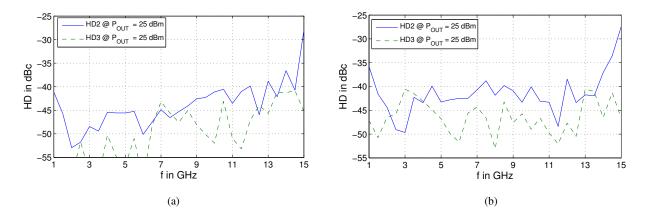

| Fig. 3-60: On-wafer measured <i>HD</i> @ <i>P</i> OUT = 25 dBm for (a) nonuniform (Nasu )and (b) uniform (Unzen) DC-15 GHz<br>TWA at <i>V</i> DS = 30 V and <i>I</i> DS = 200 mA/mm                                                                                                                                                                                 |

| Fig. 3-61: (a) photograph of DC-20 GHz TWA MMIC (Numazawa) and (b) corresponding schematic                                                                                                                                                                                                                                                                          |

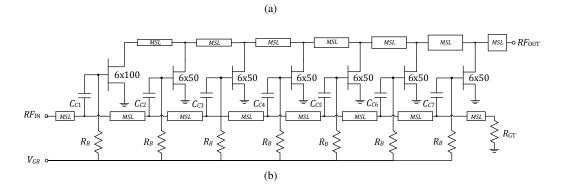

| Fig. 3-62: (a) Measured on-wafer S-parameters and (b) $P1dB$ of DC-20 GHz TWA (Namazuwa) at $VDS = 30$ V and $IDS = 200$ mA/mm                                                                                                                                                                                                                                      |

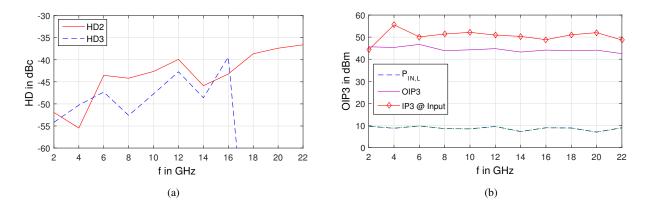

| Fig. 3-63: On-wafer measured (a) <i>HD</i> vs. $f @ POUT = 20 \text{ dBm}$ and (b) <i>OIP3</i> vs. $f$ with $\Delta f = 5 \text{ MHz}$ for <i>VDS</i> = 28 V and <i>IDS</i> = 200 mA/mm of DC-20 GHz TWA (Namazuwa)                                                                                                                                                 |

| Fig. 3-64: Comparison between measured & ADS back-fitted simulated NF of the DC-15 GHz TWA (Unzen) 100                                                                                                                                                                                                                                                              |

| Fig. 3-65: Calculated NF separated by its contributors in the ideal DC-15 GHz TWA (Unzen), assuming a constant gain of                                                                                                                                                                                                                                              |

| GP = 10  dB and an I/O- <i>RL</i> of 10 dB                                                                                                                                                                                                                                                                                                                          |

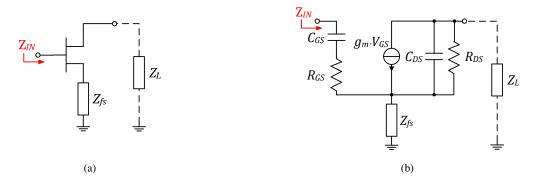

| Fig. 3-66: Schematic of HEMT (a) with series feedback impedance $Z_S$ (b) simplified equivalent small-signal circuit 102                                                                                                                                                                                                                                            |

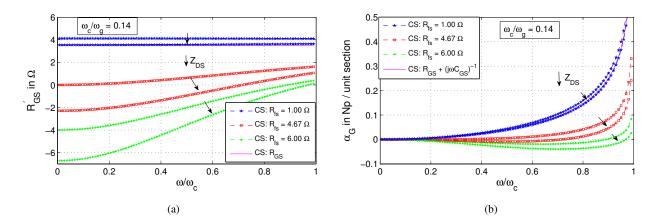

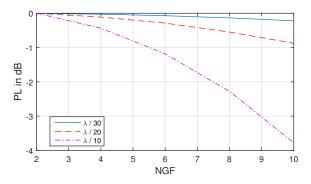

| Fig. 3-67: (a) Loss compensated RGS' and (b) corresponding gate-line attenuation $\alpha$ G for different Rfs of a CS-HEMT (WG = 0.3 mm) with Cfs = 5 · CGS = 2.25 pF for ZDS = $\infty$ and for CDS = 85 fF, RDS = 580 $\Omega$ , ZL = 50 $\Omega$ 103                                                                                                             |

| Fig. 3-68: Schematic of (a) Cascode configuration and (b) small-signal approximation of cascode for output impedance calculation                                                                                                                                                                                                                                    |

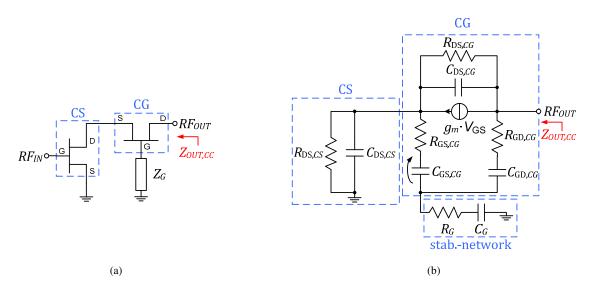

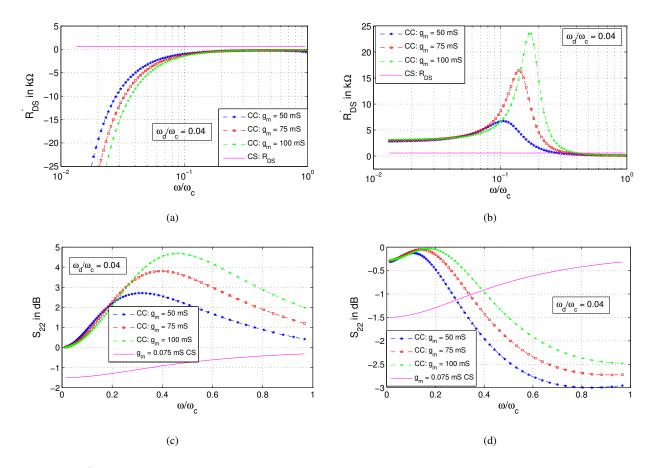

| Fig. 3-69: <i>RDS'</i> vs. $\omega\omega C$ of CG-HEMT (WG = 0.3 mm) for different <i>gm</i> values with (a) <i>YDS</i> , <i>CS</i> = <i>Y</i> GD, <i>CG</i> = 0 and <i>Y</i> G = $\infty$ and (b) <i>YDS</i> , <i>CS</i> = <i>YDS</i> , <i>CG</i> and <i>CG</i> = 0.26 pF, <i>RG</i> = 20 $\Omega$ . (c) and (d) show the corresponding <i>S</i> 22 of (a) and (b) |

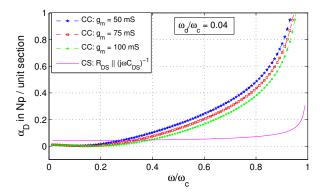

| Fig. 3-70: $\alpha D$ vs. $\omega \omega C$ of CC-HEMT (WG = 0.3 mm) for different $gm$ with YDS, $CS = YDS$ , $CG$ and $CG = 0.26$ pF, $RG = 20 \Omega$ .                                                                                                                                                                                                          |

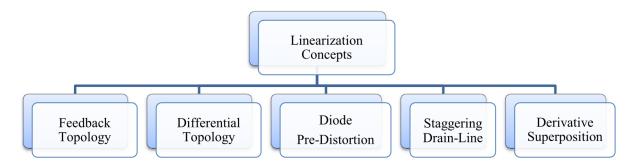

| Fig. 4-1: Proposed on-chip linearization concepts for FBPAs and TWAs                                                                                                                                                                                                                                                                                                |

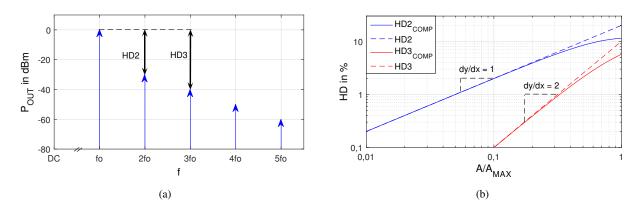

| Fig. 4-2: (a) CW-spectrum of a nonlinear PA and (b) HD2 & HD3 in percent vs. normalized input amplitude A 114                                                                                                                                                                                                                                                       |

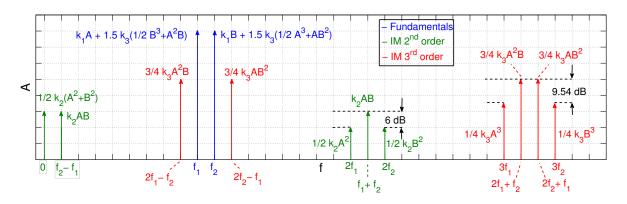

| Fig. 4-3: Two-tone IM spectrum with corresponding amplitude coefficients                                                                                                                                                                                                                                                                                            |

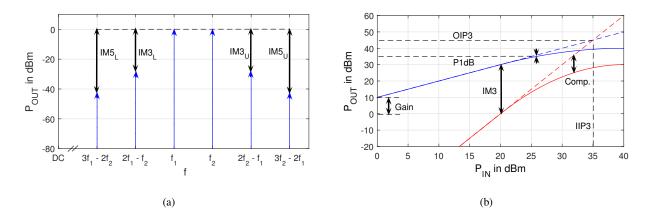

| Fig. 4-4: Two-tone intermodulation distortion of 3 <sup>rd</sup> and 5 <sup>th</sup> order ( <i>IM</i> 3 & <i>IM</i> 5) and (b) relationship between <i>OIP</i> 3 and <i>IIP</i> 3                                                                                                                                                                                  |

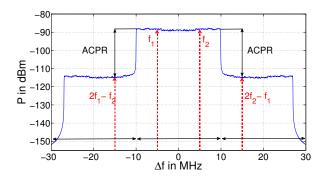

| Fig. 4-5: Typical LTE-spectrum with a BW of 20 MHz, distorted by the neighbor channel                                                                                                                                                                                                                                                                               |

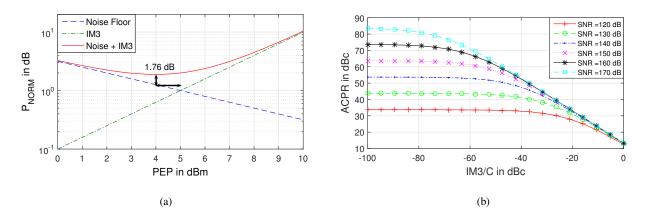

| Fig. 4-6: (a) ACPRnorm vs. PEP and (b) ACPR vs. IM3/C118                                                                                                                                                                                                                                                                                                            |

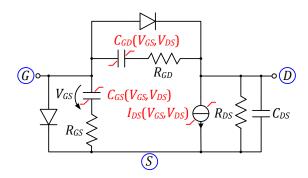

| Fig. 4-7: Intrinsic large-signal model of GaN HEMT with nonlinear drain-source channel current and capacitances 119                                                                                                                                                                                                                                                 |

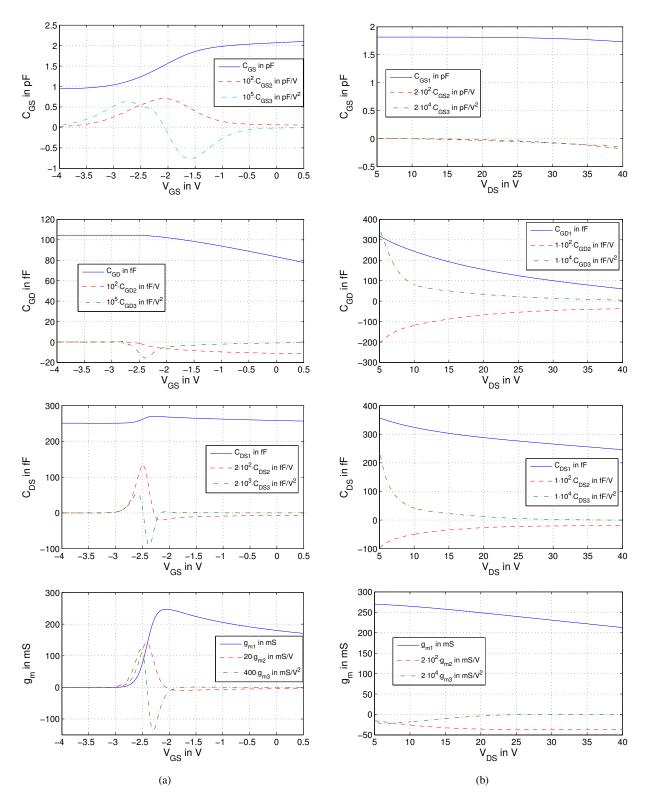

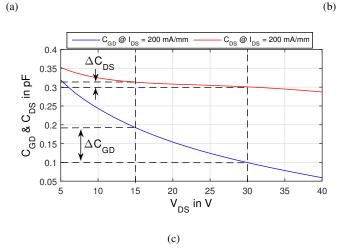

| Fig. 4-8: CGS, CGD, CDS and gm dependence (a) on VGS for VDS = 30 V and (b) on VDS for IDS = 200 mA/mm of a $8 \times 125 \mu m$ GaN HEMT                                                                                                                                                                                                                           |

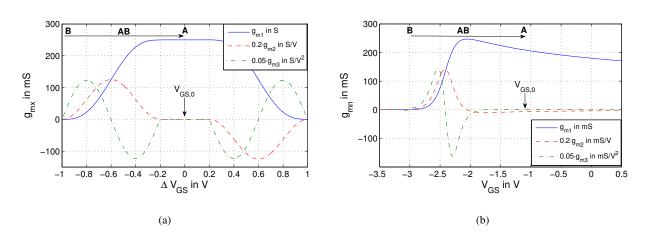

| Fig. 4-9: gm-curves of (a) idealized HEMT and (b) 8×125µm GaN HEMT LS-model; gm2 and gm3 are both multiplied                                                                                                                                                                                                                                                        |

| by a factor of 0.2 and 0.05, respectively                                                                                                                                                                                                                                                                                                                           |

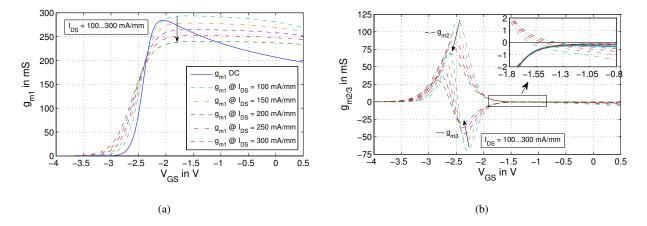

| Fig. 4-10: Transient RF- (a) $gm1$ and (b) $gm2/3$ vs. VGS for IDS = 100300 mA/mm of an $8 \times 125 \mu$ m GaN HEMT 122                                                                                                                                                                                                                                           |

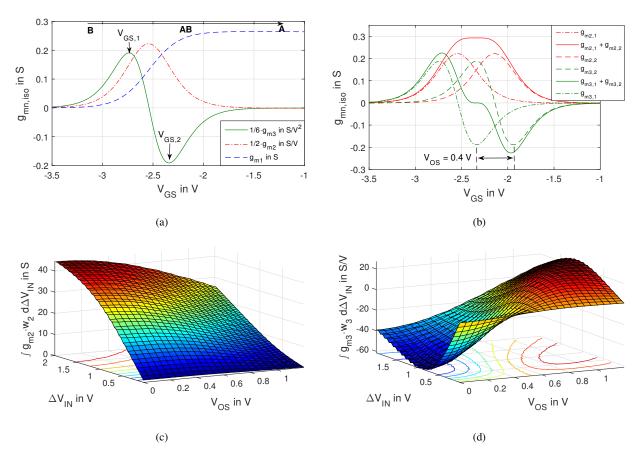

| Fig. 4-11: Integral of $g_{m2}$ - and $g_{m3}$ over $\Delta VIN$ plotted vs. $\Delta VIN$ and VGS0 for (a,c) an idealized HEMT and (b,d) $8 \times 125 \mu m$<br>GaN HEMT                                                                                                                                                                                           |

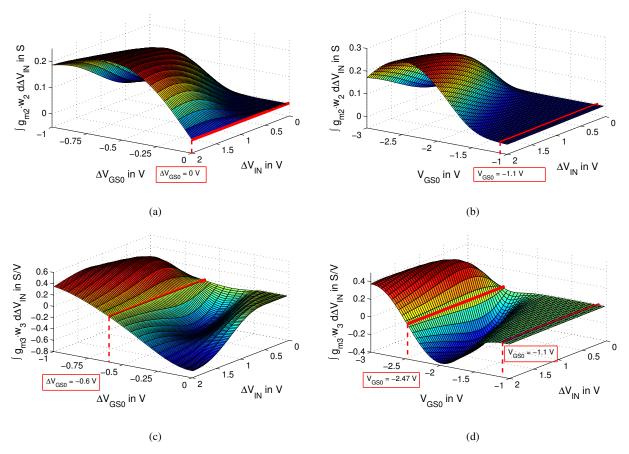

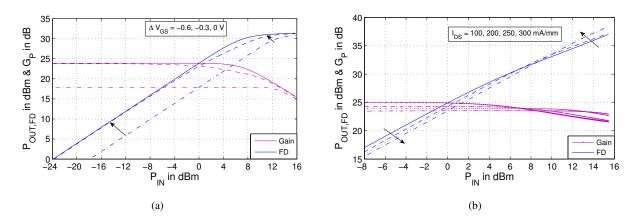

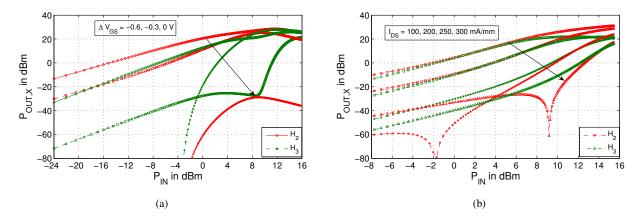

| Fig. 4-12: Calculated $P_{OUT,FD}$ & $GP$ vs. $PIN$ of (a) an idealized HEMT for $\Delta VGS = -0.60$ V and (b) $8 \times 125 \mu$ m GaN HEMT                                                                                                                                                                                                                       |

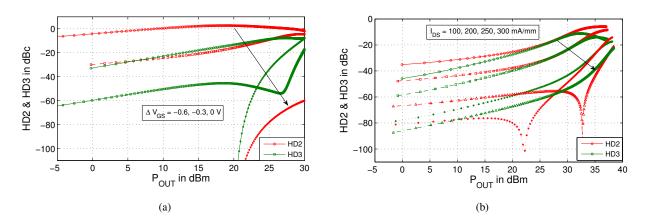

| Fig. 4-13: Calculated H2 & H3 in dBm vs. <i>PIN</i> of (a) an idealized HEMT for $\Delta VGS = -0.60$ V and (b) $8 \times 125 \mu$ m GaN HEMT                                                                                                                                                                                                                       |

| Fig. 4-14: | Calculated <i>HD2</i> and <i>HD3</i> vs. <i>POUT</i> of (a) an idealized HEMT for $\Delta VGS = -0.60$ V and (b) $8 \times 125 \mu$ m GaN HEMT.            |     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

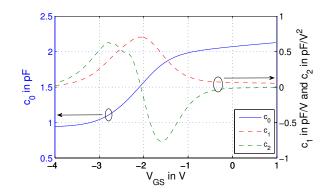

| Fig. 4-15: | CGS0 (c0) and its higher derivatives c1 and c2 versus VGS                                                                                                  | 128 |

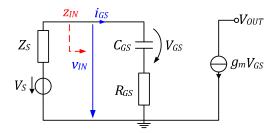

| Fig. 4-16: | Simplified HEMT schematic driven by a Thévenin source                                                                                                      | 129 |

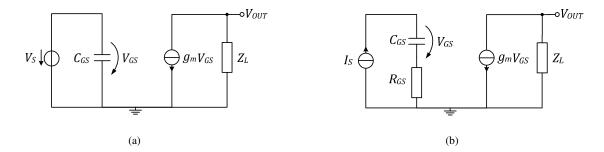

| Fig. 4-17: | (a) low frequency and (b) high frequency approximation of HEMT driven by a constant power source                                                           | 129 |

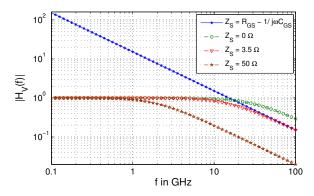

| Fig. 4-18: | Voltage transfer function $HV(\omega)$ vs. f for different source impedances ZS                                                                            | 130 |

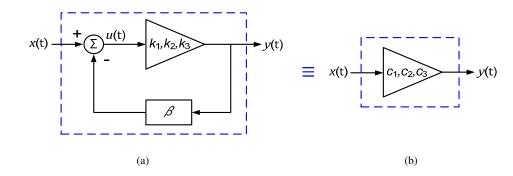

| Fig. 4-19: | (a) Nonlinear feedback system with distortion coefficients $kn$ and unilateral feedback $\beta$ and (b) its equivalent                                     |     |

|            | representation with converted distortion coefficients cn                                                                                                   | 131 |

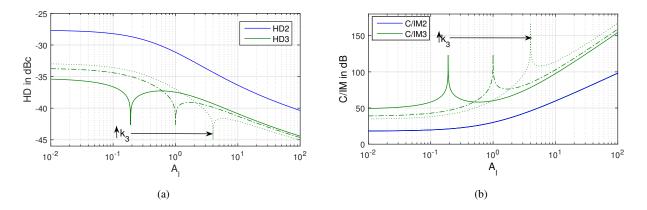

| Fig. 4-20: | (a) <i>HD</i> and (b) <i>C/IM</i> -ratio vs. <i>Al</i> of nonlinear feedback system with distortion coefficients $k1 = 1$ , $k2 = 1/8$ a                   | nd  |

|            | $k3 = 5 \cdot 10^{-3} / V^3$ (solid), $15.625 \cdot 10^{-3} / V^3$ (dashed-dotted), $25 \cdot 10^{-3} / V^3$ (dotted)                                      | 133 |

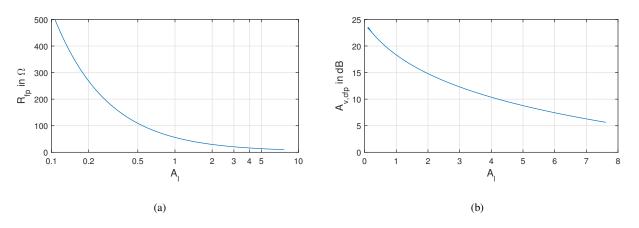

| Fig. 4-21: | (a) Loop gain Al vs. $Rfp$ and (b) closed-loop gain $Av, cfp$ vs. Al of parallel resistive FBPA for a $8 \times 125 \mu m$ HEMT                            | 134 |

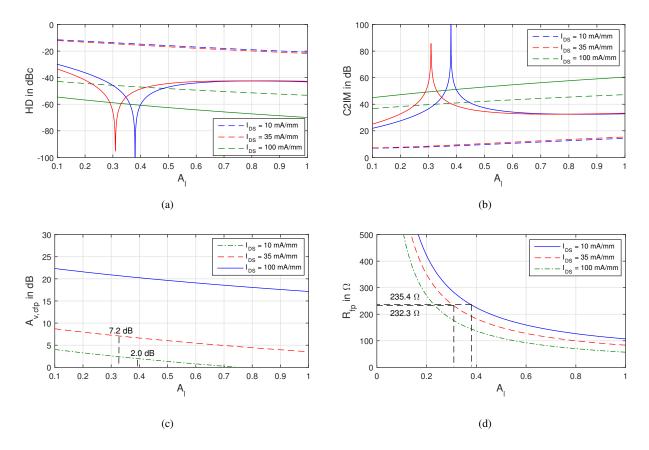

| Fig. 4-22: | (a) HD2 (dashed) & HD3 (solid) vs. Al, (b) C/IM2 (dashed) & C/IM3 (solid) vs. Al, (c) Av, cfp vs. Al and (                                                 | d)  |

| U          | Rfp vs. $Al$ of an 8×125µm FBPA with parallel resistive feedback for the distortion coefficients at $IDS = 10, 3$ and 100 mA/mm from                       | 35  |

| Fig 4-23.  | Sketch of the drain-line propagation difference between fundamental and 3 <sup>rd</sup> harmonic due to nonlinear                                          | 155 |

| 118 201    | transistors in a UDPA                                                                                                                                      | 137 |

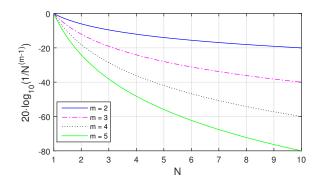

| Fig. 4-24: | Dependency of <i>HDm</i> vs. <i>N</i> in dB for equal gate- and drain-line phase coefficients                                                              |     |

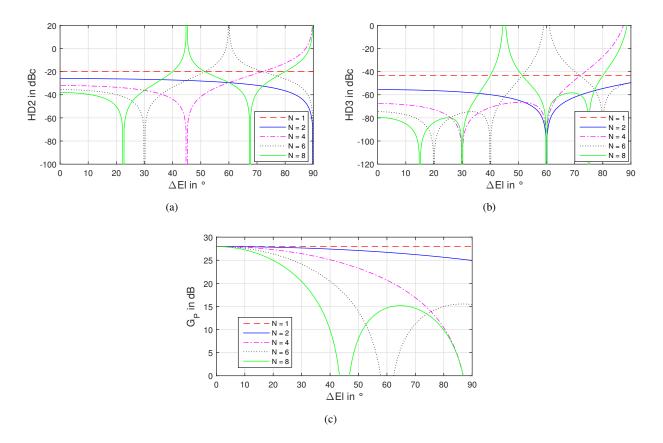

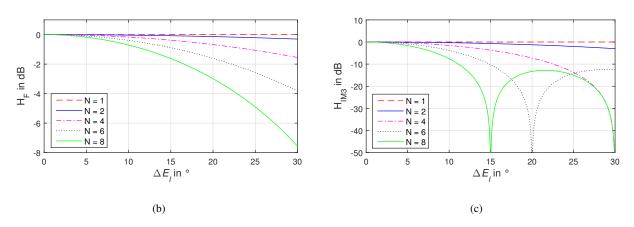

|            | (a) $HD2$ , (b) $HD3$ and (c) $GP$ of fundamental vs. $\Delta E1$ for different number of stages N in a UDPA                                               |     |

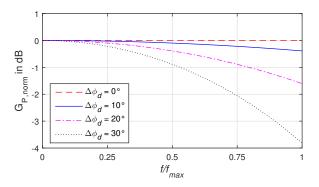

|            | Dependency of GP vs. $f/fmax$ in dB and $N = 6$ for a staggered drain-line with an additional phase offset $\Delta \Phi$                                   |     |

| 0          | at <i>fmax</i>                                                                                                                                             |     |

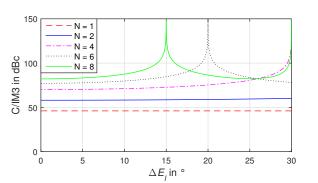

| Fig. 4-27: | (a) $C/IM3$ , (b) HF of the fundamental and (c) HIM3 of the intermodulation products vs. $\Delta El$ for different                                         |     |

| U          | number of stages N in a UDPA                                                                                                                               | 142 |

| Fig. 4-28: | Schematic of the derivative superposition method applied to HEMTs via resistive voltage division                                                           |     |

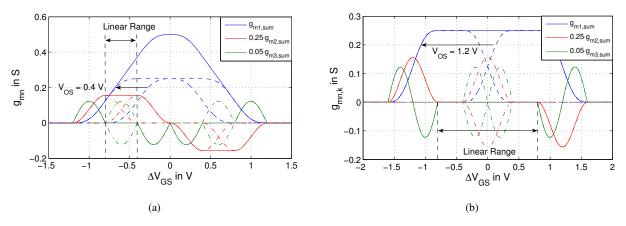

|            | gm-transfer characteristics of DSM applied to two HEMTs for (a) $VOS = 0.4$ V and (b) $VOS = 1.2$ V                                                        |     |

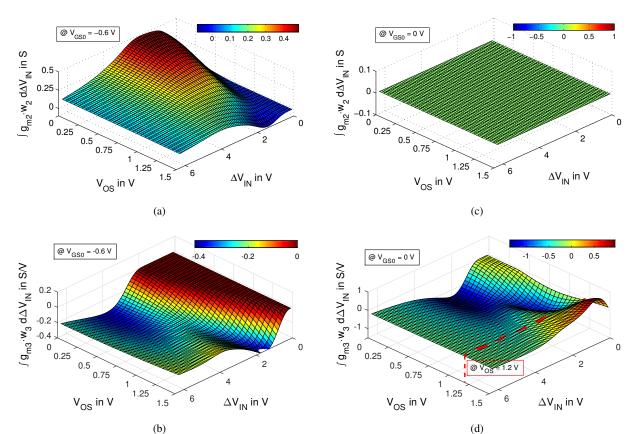

|            | Weighted integrals of (a) $gm2$ and (b) $gm3$ at $VGS0 = -0.6$ V and (c) $gm2$ and (d) $gm3$ at $VGS0 = 0$ V over                                          |     |

| -          | different input voltage swings $\Delta VIN$ and different offsets VOS of the DSM applied to two ideal HEMTs                                                | 145 |

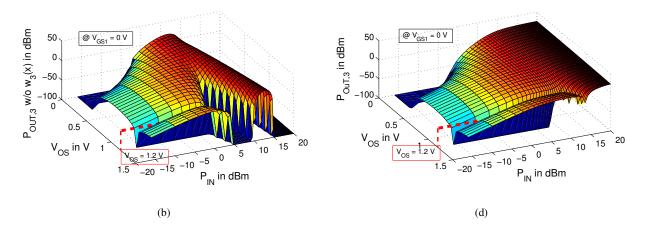

| Fig. 4-31: | <i>POUT</i> , 3 in dBm over <i>PIN</i> and <i>VOS</i> for <i>V</i> GS0 = 0 V in (a) w/o and (b) with weighting function $w3(x)$ of DSI for two ideal HEMTs |     |

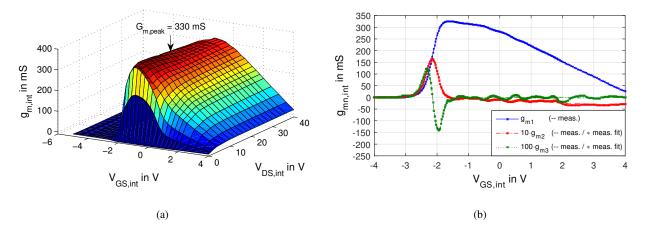

| Fig. 4-32: | Extrapolated measured isothermal intrinsic $gm$ -transfer characteristic of an 8×125µm GaN HEMT (a) vs. VG                                                 | S   |

| -          | and VDS (courtesy: IAF) and (b) vs. VGS for VDS = $30$ V including $gm2$ and $gm3$                                                                         | 147 |

| Fig. 4-33: | (a) isothermal gmn-curves, (b) sum of two isothermal gmn-curves with $VOS = 0.4$ V and integral of (c) gm2                                                 | 2   |

|            | and (d) $gm3$ over different input voltage swings $\Delta VIN$ and different offset voltages $VOS$ for the DSM with two                                    | vo  |

|            | 8×125µm HEMTs                                                                                                                                              | 148 |

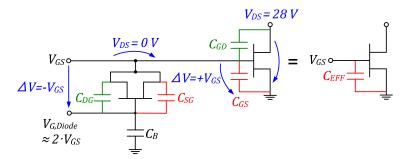

| Fig.4-34:  | simplified diode predistortion concept for CGS-nonlinearity cancellation                                                                                   | 152 |

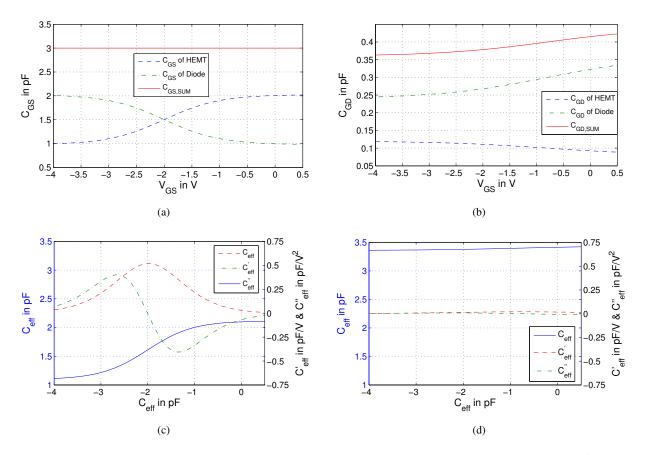

| Fig. 4-35: | Approximated (a) CGS and (b) CGD vs. VGS dependence of a predistorted $8 \times 125 \mu m$ HEMT. Ceff and its $1^{st}$                                     | and |

|            | $2^{nd}$ order derivatives vs. VGS of (c) the single $8 \times 125 \mu m$ HEMT and (d) the predistorted $8 \times 125 \mu m$ HEMT                          | 153 |

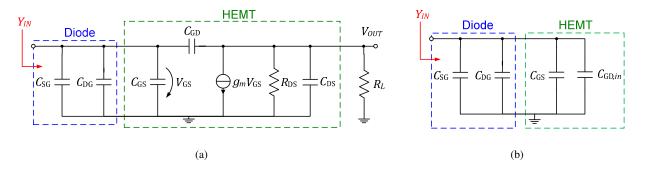

| Fig. 4-36: | (a) Equivalent small-signal circuit for diode predisortion plus HEMT and (b) equivalent Miller effect                                                      |     |

|            | representation                                                                                                                                             |     |

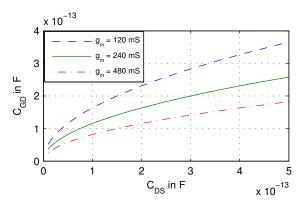

| Fig. 4-37: | Calculated Ceff of the 8×125µm predistorted HEMT for different RDS and CDS values                                                                          | 154 |

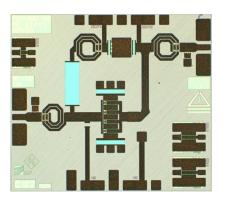

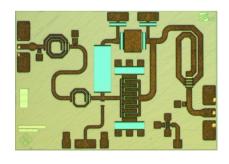

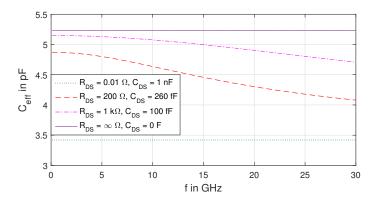

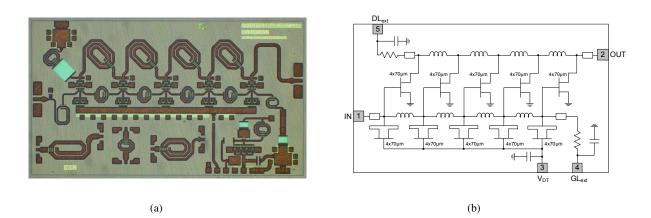

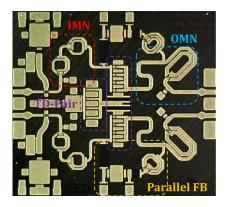

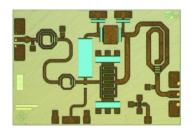

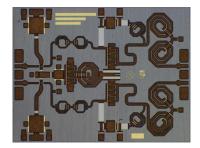

| Fig. 4-38: | (a) Photograph and (b) corresponding schematic of the DC-6.5 GHz highly linear low-noise TWA MMIC ("Latukan")                                              | 155 |

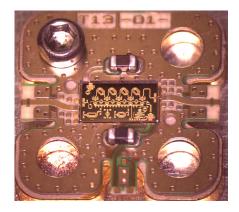

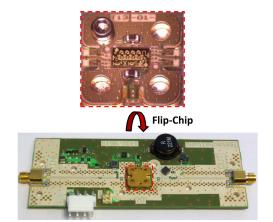

| Fig. 4-39: | (a) photograph of the packaged DC-6.5 GHz L2NTWA ("Latukan") including SMD capacitors for low frequence                                                    | ncy |

|            | extensions on gate- and drain-line and (b) flip-chip assembly in RO4350 test board including on-board bias-te                                              | ees |

|            |                                                                                                                                                            |     |

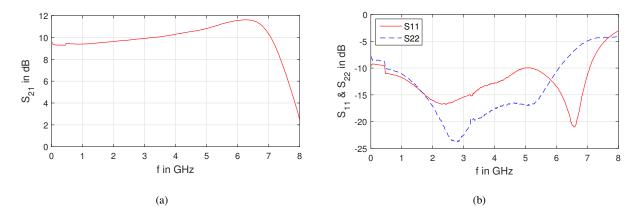

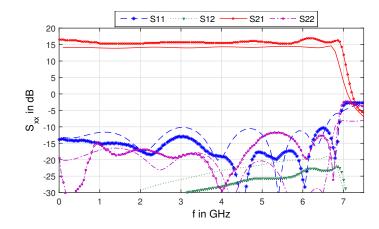

| -          | Simulated & measured S-parameters of L <sup>2</sup> NTWA ("Latukan") from 10 MHz - 7.5 GHz in package                                                      |     |

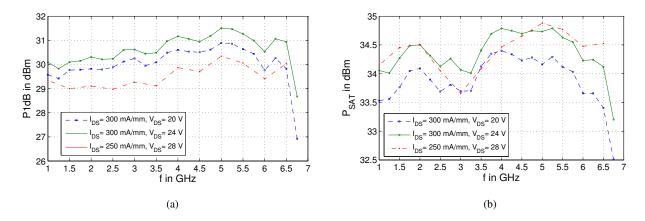

| Fig. 4-41: | Measured (a) P1dB and (b) Psat of DC-6.5 GHz L <sup>2</sup> NTWA ("Latukan") in package for different VDS and ID                                           |     |

|            | $VDT = 2.5 \cdot VGS$                                                                                                                                      |     |

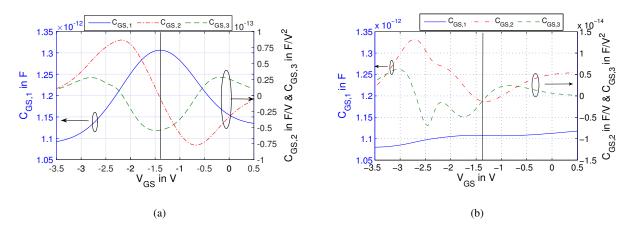

| Fig. 4-42: | $CGS1_1$ , $CGS2$ and $CGS3$ of a 4×70µm as diode plus a 4×70µm common-source HEMT vs. $VGS$ for (a) $V_{DT} = -$                                          |     |

|            | V and (b) $V_{DT} = -4.9$ V (@ $V_{DS} = 28$ V)                                                                                                            | 158 |

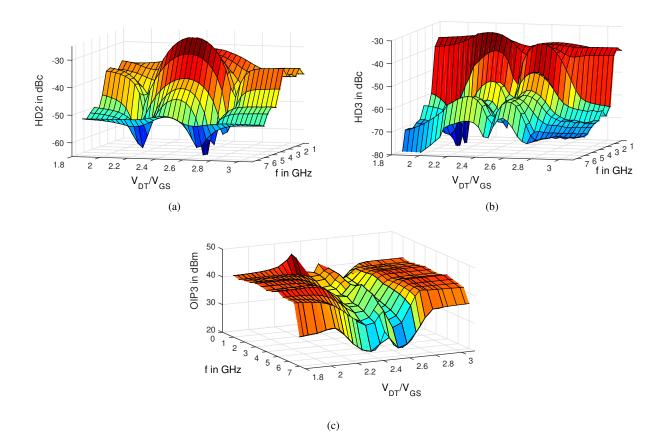

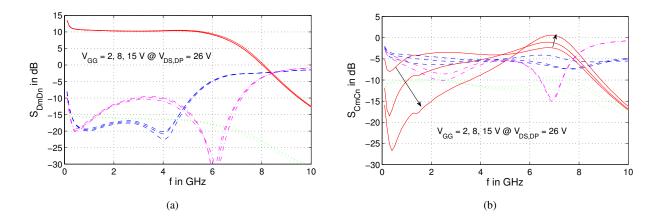

| Fig. 4-43: | Measured (a) <i>HD</i> 2, (b) <i>HD</i> 3 at <i>POUT</i> = 25 dBm and (c) <i>OIP</i> 3 at $\Delta f$ = 10 MHz vs. $f$ and vs. <i>VDT/VGS</i> of            |     |

|            | L <sup>2</sup> NTWA ("Latukan") from 1-6.5 GHz in package (VDS = 28 V and IDS = 250 mA/mm)                                                                 | 159 |

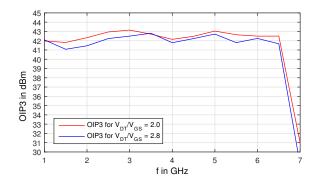

| Fig. 4-44: Measured <i>OIP</i> 3 with $\Delta f = 10$ MHz vs. $f$ for <i>VDT/V</i> GS = 2.0 & 2.8 of the L <sup>2</sup> NTWA ("Latukan") from 1-6.5 GHz in package                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

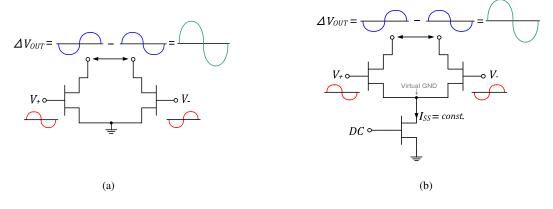

| Fig. 4-45: Schematic of (a) pseudo-differential (PD) and (b) truly-differential (TD) amplifier                                                                                                                            |

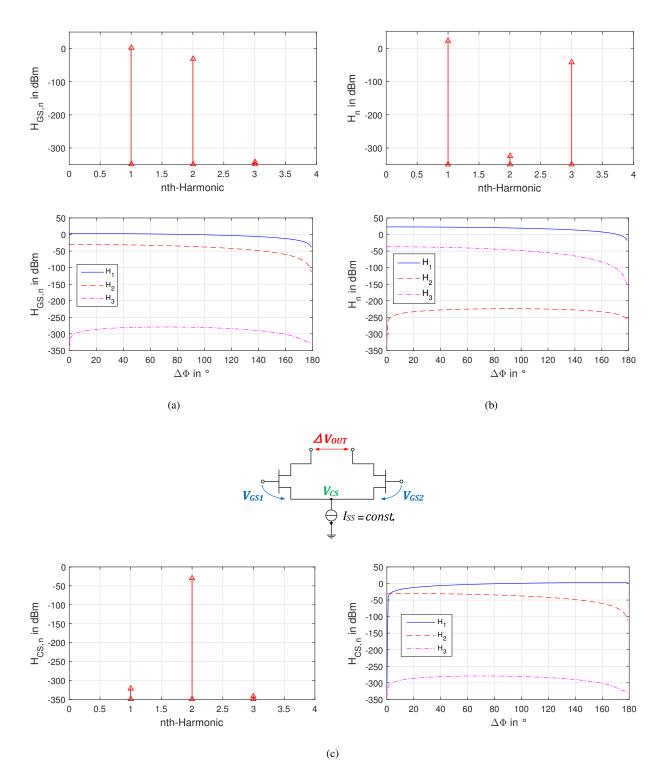

| Fig. 4-46: Simulated output spectral components at $\Delta \phi = 0$ and corresponding dependence on $\Delta \phi$ of (a) VGS, (b) $\Delta VOUT$                                                                          |

| and (c) VCS of an ideal TD-pair comprising $2^{rd}$ order nonlinear transistors with coefficients $gm1 = 0.1$ , $gm2 =$                                                                                                   |

| 0.01 (gm3 = 0) and an ideal TCS                                                                                                                                                                                           |

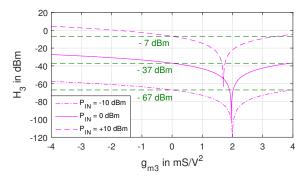

| Fig. 4-47: Simulated 3 <sup>rd</sup> harmonic (H3) vs. $gm3$ at $PIN = -10, 010$ dBm and $\Delta \phi = 0$ of an ideal TD-pair with ideal TCS $(gm1 = 0.1, gm2 = 0.01)$                                                   |

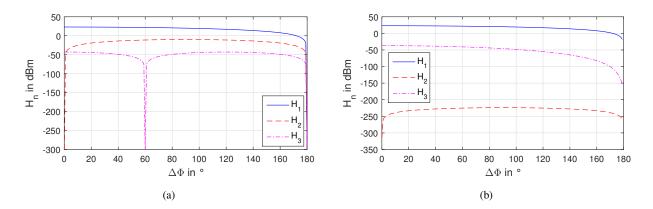

| Fig. 4-48: Simulated/Computed spectral output components (H1, H2, H3) in dBm vs. $\Delta \phi$ of an ideal (a) PD-pair and (b)<br>TD-pair with ideal TCS for $PIN = 0$ dBm ( $gm1 = 0.1$ , $gm2 = 0.01$ , $gm3 = 0.001$ ) |

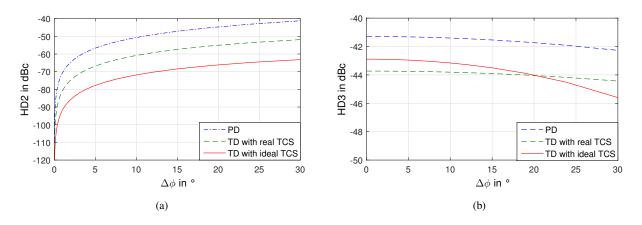

| Fig. 4-49: Simulated (a) HD2 vs. $\Delta \phi$ and (b) HD3 vs. $\Delta \phi$ at Pout= 20 dBm for $f = 6$ GHz of an unmatched 6×50µm PD-                                                                                   |

| pair, 6×50µm TD-pair with 6×50µm TCS and a 6×50µm TD-pair with ideal current source                                                                                                                                       |

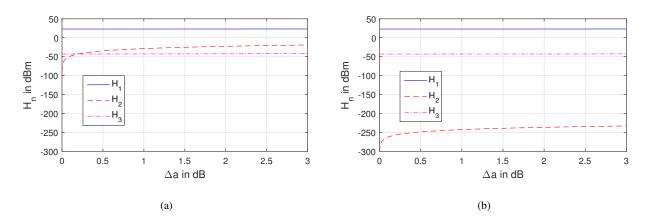

| Fig. 4-50: Simulated/Computed spectral output components ( $H1, H2, H3$ ) in dBm vs. $\Delta a$ in dB of an ideal (a) PD-pair and                                                                                         |

| (b) TD-pair with ideal TCS for $PIN = 0$ dBm ( $gm1 = 0.1$ , $gm2 = 0.01$ , $gm3 = 0.001$ )                                                                                                                               |

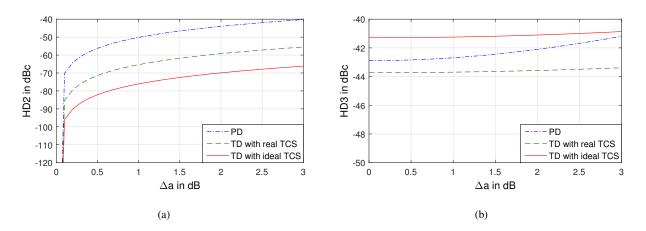

| Fig. 4-51: Simulated (a) HD2 vs. $\Delta a$ and (b) HD3 vs. $\Delta a$ at Pout= 20 dBm for $f = 6$ GHz of an unmatched $6 \times 50 \mu$ m PD-                                                                            |

| pair, 6×50µm TD-pair with 6×50µm TCS and a 6×50µm TD-pair with ideal current source                                                                                                                                       |

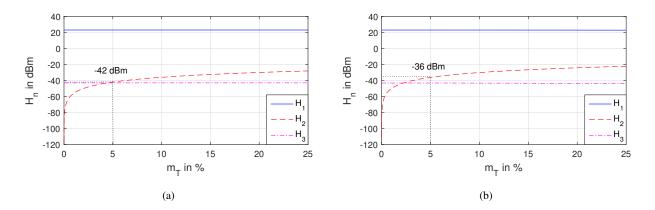

| Fig. 4-52: Simulated/Computed spectral output components (H1, H2, H3) in dBm vs. mT in % of an ideal (a) PD-pair and                                                                                                      |

| (b) TD-pair with ideal TCS ( $gm1 = 0.1, gm2 = 0.01, gm3 = 0.001$ )                                                                                                                                                       |

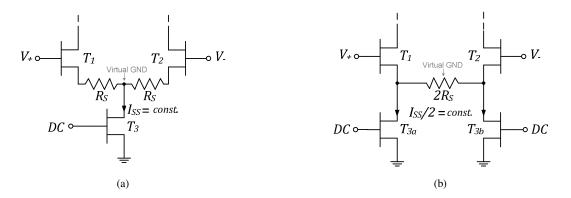

| Fig. 4-53: TD-pair with series feedback and (a) common current source and (b) split current source                                                                                                                        |

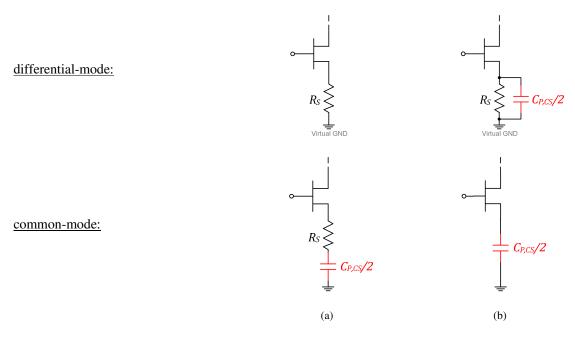

| Fig. 4-54: Equivalent half-section of single- and double-current source solution of TD-pair for differential- and common-                                                                                                 |

| mode from (a) Fig. 4-53 (a) and (b) Fig. 4-53 (b)                                                                                                                                                                         |

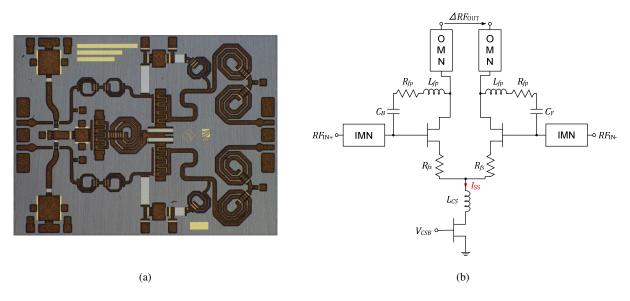

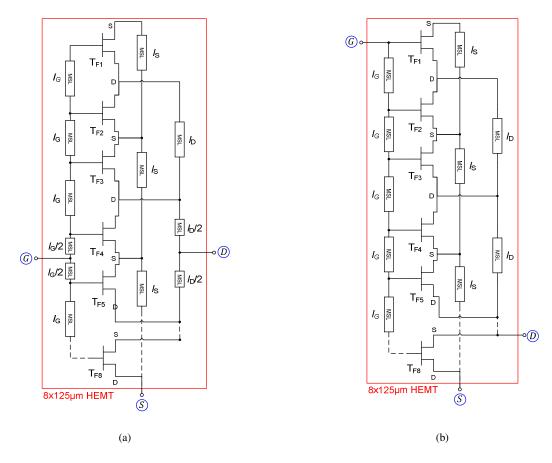

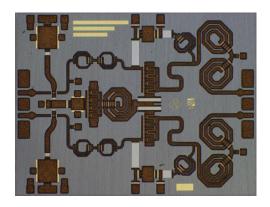

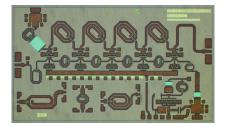

| Fig. 4-55: Photograph of DC-6 GHz truly-differential FBPA (a) "Trafalgar V2" and (b) corresponding simplified general schematic                                                                                           |

| Fig. 4-56: (a) S21, (b) CMRR, (c) $\mu'$ and (d) $\mu$ for different inductive compensation values of the parasitic capacitance                                                                                           |

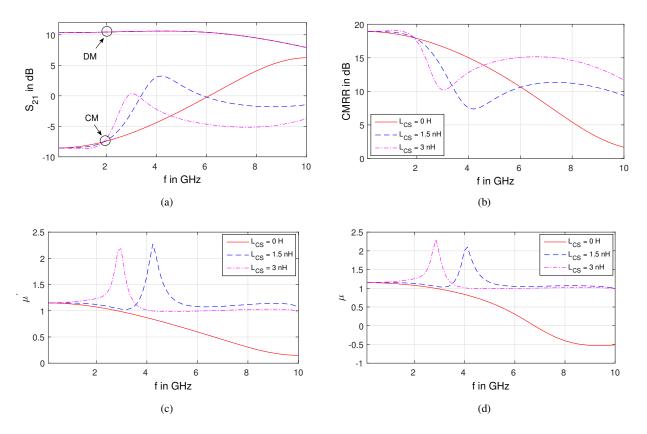

| towards ground of the TCS-HEMT 172                                                                                                                                                                                        |

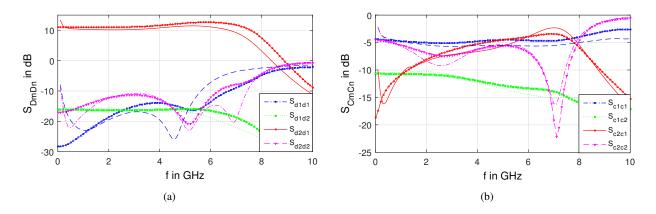

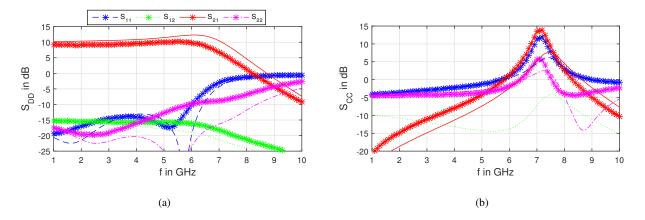

| Fig. 4-57: Simulated (markers) & on-wafer measured (lines) (a) SDD vs. f and (b) SCC vs. f of DC-6 GHz TD-FBPA                                                                                                            |

| ("Trafalgar V2") for $VDD = 38$ V, $VGG = 6$ V and $ISS = 100$ mA/mm                                                                                                                                                      |

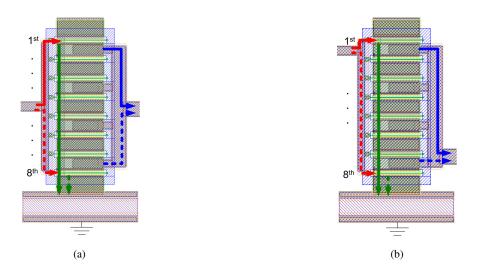

| Fig. 4-58: Layout of (a) symmetric gate/drain-bus connection (SBS) and (b) asymmetric gate/drain-bus connection (ABS)                                                                                                     |

| of an asymmetric source-terminated 8×125µm, as applied in the DC-6 GHz TD-FBPA ("Trafalgar V2") 173                                                                                                                       |

| Fig. 4-59: Schematic of (a) symmetric gate/drain-bus connection and (b) asymmetric gate/drain-bus connection of the                                                                                                       |

| asymmetric source-terminated $8 \times 125 \mu m$ from Fig. 4-58                                                                                                                                                          |

| 8×125um HEMT in comparison to a 8×125um HEMT with SBS and symmetric source-termination                                                                                                                                    |

| Fig. 4-61: Simulated $MSG/MAG$ vs. f of SBS and ABS for an asymmetric source-terminated $8 \times 125$ un HEMT in                                                                                                         |

| comparison to a 8×125um HEMT with SBS and symmetric source-termination                                                                                                                                                    |