# Transceiver design for contactless desktop reader supporting MODE1 and MODE2 of ISO/IEC 18000-3

Diploma Thesis

at

Graz University of Technology

submitted by

Selma Školjić

Institute for Broadband Communication Graz University of Technology A 8010 Graz, Austria

in cooperation with

Ao.Univ.-Prof. Dipl.-Ing. Dr. Erich Leitgeb Dipl.-Ing. Peter Pirc (Infineon Graz)

Graz, June 2010

### Abstract

The goal of this project was to create a contactless desktop reader for ISO/IEC 18000-3 supporting MODE1 and MODE2. The reader consists of an analog front-end and a microcontroller. The microcontroller programming was the main aim of this diploma thesis.

To achieve this, initial theoretical research was conducted, emphasizing the basics of an RFID system and the magnetic field, as well as the two supporting MODEs of the ISO/IEC 18000-3. The ARM based microcontrollers are also investigated. Based on this research, different algorithms were developed and tested. Ultimately, tests were run on the analog front-end and microcontroller functioning together and results were presented.

The first part of this document is a short introduction to RFID systems in general. The parts of RFID systems are explained and the RFID systems classification is given. Also, there is a short introduction to coding and modulation techniques. The next chapter gives us an overview of the ISO/IEC 18000-3. Since MODE1 is compatible with the ISO/IEC 15693, this chapter will cover this standard, also. In next chapter, the coding techniques for both modes are explained. Decoding techniques are described next. Finally the conclusions are presented.

Keywords: RFID, ISO/IEC 18000-3, Vicinity, Phase Jitter Modulation, Reader

### Kurzfassung

Ziel dieses Projekts war es, einen kontaktlosen Desktop Leser für den Standard ISO/IEC 18000-3 zu entwickeln, welcher MODE1 and MODE2 unterstützen würde. Der Leser setzt sich aus einer analogen Eingangstufe und einem Microcontroller zusammen, wobei letzterer das Hauptthema dieser Diplomarbeit ist.

Um das genannte Vorhaben zu realisieren, musste zuerst der theoretische Aspekt untersucht werden. Dabei wurde beim theoretischen Zugang von den Grundlagen des RFID Systems und des Magnetfeldes bis zu den zwei unterstützten MODEs des ISO/IEC 18000-3 Standards, alles abgedect. Die ARM Microcontrollers sind, auch, untersucht geworden. Anhand dieser Untersuchungen wurden verschiedene Algorithmen entwickelt und getestet. Als Abschluss wurden Tests in Bezug auf die gemeinsame Funktionsweise der analogen Eingangstufe und des Microcontrollers durchgeführt und die Ergebnisse präsentiert.

Der erste Teil des Dokuments beinhaltet eine kurze allgemeine Einführung zu RFID Systemen, wobei einzelne Bestandteile der Systeme und die Klassifikation der Systeme angeführt werden. Des weiteren wird eine Einführung zu den Kodier- und Modulationstechniken gegeben. Das nächste Kapitel bietet einen Überblick über den Standard ISO/IEC 18000-3. Da MODE1 mit dem Standard ISO/IEC 15693 kompatibel ist, wird dieser Standard ebenfalls behandelt werden. Im darauf folgenden Kapitel werden die Kodiertechniken beider Modi erläutert. Es folgen die Dekodiertechniken und abschließend die Präsentation der Schlussbetrachtungen/Ergebnisse.

Schlüsselwörter: RFID, ISO/IEC 18000-3, Vicinity, Phase Jitter Modulation, Reader

### **Statutory declaration**

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

Graz, ..... Signature .....

### Eidesstattliche Erklärung

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe.

Graz, am ..... Unterschrift .....

### Acknowledgements

I would like to express my gratitude to Infineon Technologies Austria AG, for providing me the opportunity to write my diploma thesis in such a highly professional environment and in such fantastic working atmosphere. Among all my colleagues I am in particular indebted to Peter Pirc, my project manager and Christian Pontesegger for his support on the digital design. On the academic side, I would like to thank Prof. Erich Leitgeb for being my helpful mentor.

Last but not least, I would like to thank my parents for their emotional and financial support throughout my studies.

Selma Školjić Graz, Austria, 2010

# Contents

| Contents         |                   |          |                                |      |  |  |  |

|------------------|-------------------|----------|--------------------------------|------|--|--|--|

| Li               | List of Figures x |          |                                |      |  |  |  |

| List of Tables x |                   |          |                                |      |  |  |  |

| G                | lossar            | y        |                                | xiii |  |  |  |

| 1                | Introduction      |          |                                |      |  |  |  |

| 2                | Ove               | rview of | f RFID technology              | 3    |  |  |  |

|                  | 2.1               | Typica   | l RFID components              | 3    |  |  |  |

|                  |                   | 2.1.1    | Transponder                    | 4    |  |  |  |

|                  |                   | 2.1.2    | Reader                         | 4    |  |  |  |

|                  | 2.2               | Classif  | fication of RFID systems       | 5    |  |  |  |

|                  |                   | 2.2.1    | Operating frequency            | 5    |  |  |  |

|                  |                   | 2.2.2    | Range                          | 5    |  |  |  |

|                  | 2.3               | Physic   | al fundamentals of RFID        | 6    |  |  |  |

|                  |                   | 2.3.1    | The magnetic field             | 6    |  |  |  |

|                  |                   | 2.3.2    | The alternating magnetic field | 9    |  |  |  |

|                  | 2.4               | Coding   | g and modulation               | 10   |  |  |  |

|                  |                   | 2.4.1    | Coding                         | 11   |  |  |  |

|                  |                   |          | 2.4.1.1 Non-return to zero     | 11   |  |  |  |

|                  |                   |          | 2.4.1.2 Manchester code        | 12   |  |  |  |

|                  |                   |          | 2.4.1.3 Unipolar RZ coding     | 12   |  |  |  |

|   |     |         | 2.4.1.4    | Miller coding                                  | 13 |

|---|-----|---------|------------|------------------------------------------------|----|

|   |     |         | 2.4.1.5    | Pulse-pause coding                             | 13 |

|   |     | 2.4.2   | Digital n  | nodulation                                     | 14 |

|   |     |         | 2.4.2.1    | Amplitude shift keying                         | 14 |

|   |     |         | 2.4.2.2    | Frequency shift keying                         | 15 |

|   |     |         | 2.4.2.3    | Phase shift keying                             | 16 |

| 3 | ISO | /IEC 18 | 000-3      |                                                | 17 |

|   | 3.1 | ISO/IE  | EC 18000-2 | 3 MODE1                                        | 18 |

|   |     | 3.1.1   | ISO/IEC    | 15693 Part 1                                   | 18 |

|   |     | 3.1.2   | ISO/IEC    | 15693 Part 2                                   | 18 |

|   |     |         | 3.1.2.1    | Communications signal interface VCD to VICC    | 19 |

|   |     |         | 3.1.2.2    | Communications signal interface VICC to VCD    | 21 |

|   |     | 3.1.3   | ISO/IEC    | 15693 Part 3                                   | 24 |

|   |     |         | 3.1.3.1    | VICC data elements                             | 24 |

|   |     |         | 3.1.3.2    | Request and response format                    | 24 |

|   |     |         | 3.1.3.3    | VICC states                                    | 25 |

|   |     |         | 3.1.3.4    | Anticollision                                  | 26 |

|   | 3.2 | ISO/IE  | EC 18000-2 | 3 MODE2                                        | 29 |

|   |     | 3.2.1   | Commur     | nications signal interface interrogator to tag | 29 |

|   |     |         | 3.2.1.1    | Phase jitter modulation                        | 29 |

|   |     |         | 3.2.1.2    | Data rate and data coding                      | 30 |

|   |     |         | 3.2.1.3    | Interrogator to tag frames                     | 30 |

|   |     | 3.2.2   | Commur     | nications signal interface tag to interrogator | 31 |

|   |     |         | 3.2.2.1    | Data rate and data coding                      | 32 |

|   |     |         | 3.2.2.2    | Tag to interrogator frames                     | 32 |

|   |     | 3.2.3   | Commar     | d format                                       | 33 |

|   |     | 3.2.4   | Tag reply  | format and tag states                          | 34 |

|   |     | 3.2.5   | Collision  |                                                | 35 |

| 4 | Cod  | ing of t | he coded baseband                               | 37 |

|---|------|----------|-------------------------------------------------|----|

|   | 4.1  | MODE     | E decision                                      | 37 |

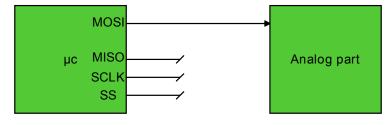

|   | 4.2  | Serial   | peripheral interface                            | 38 |

|   | 4.3  | Coding   | g techniques for the STR71x microcontroller     | 39 |

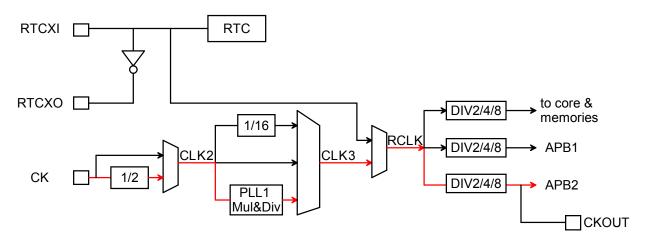

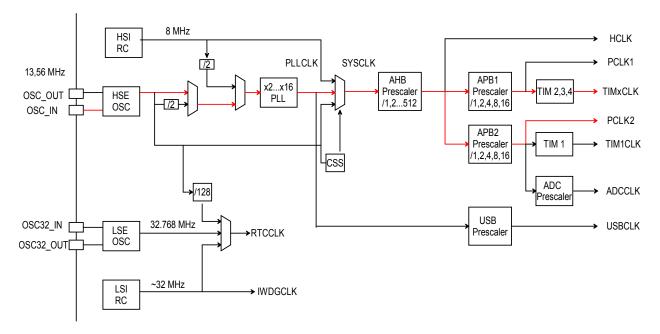

|   |      | 4.3.1    | Clock configuration                             | 39 |

|   |      | 4.3.2    | SPI configuration                               | 40 |

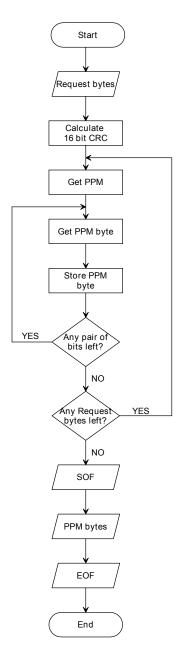

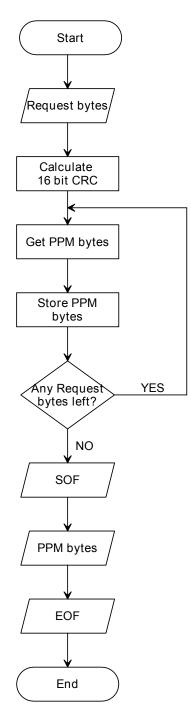

|   |      | 4.3.3    | MODE1 transmission                              | 41 |

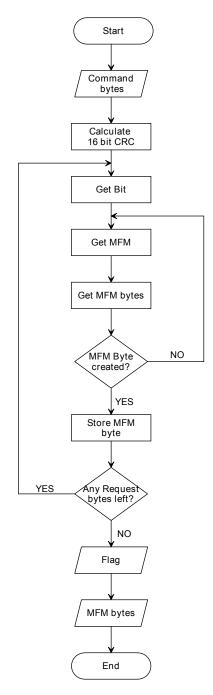

|   |      | 4.3.4    | MODE2 transmission                              | 43 |

|   | 4.4  | Coding   | g techniques for the STM32Fx microcontroller    | 45 |

|   |      | 4.4.1    | Clock and SPI configuration                     | 45 |

|   |      | 4.4.2    | MODE1 transmission                              | 47 |

|   |      | 4.4.3    | MODE2 transmission                              | 49 |

| 5 | Dece | oding of | f the coded baseband                            | 51 |

|   | 5.1  | Decod    | ing techniques for the STR71x microcontroller   | 51 |

|   |      | 5.1.1    | MODE1 decoding                                  | 51 |

|   |      | 5.1.2    | MODE2 decoding                                  | 53 |

|   | 5.2  | Decod    | ing techniques for the STM32Fx microcontroller  | 56 |

|   |      | 5.2.1    | MODE1 decoding                                  | 56 |

|   |      | 5.2.2    | MODE2 decoding                                  | 60 |

| 6 | Rea  | der imp  | lementation                                     | 63 |

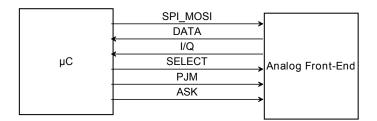

|   | 6.1  | Interfa  | ce between microcontroller and analog front-end | 63 |

|   | 6.2  | User in  | nterface commands                               | 64 |

|   |      | 6.2.1    | User interface command set for MODE1            | 64 |

|   |      | 6.2.2    | User interface command set for MODE2            | 64 |

| 7 | Con  | clusion  |                                                 | 66 |

| A | Cycl | lic redu | ndancy check MODE1                              | 68 |

|   | A.1  | 16 bit   | CRC detection                                   | 68 |

|   | A.2  | 16 bit   | CRC calculation example                         | 68 |

| B  | Cyclic redundancy check MODE2 |                                |    |  |  |

|----|-------------------------------|--------------------------------|----|--|--|

|    | <b>B</b> .1                   | 32 bit CRC detection           | 70 |  |  |

|    | B.2                           | 32 bit CRC calculation example | 70 |  |  |

| Bi | bliogr                        | aphy                           | 73 |  |  |

# List of Figures

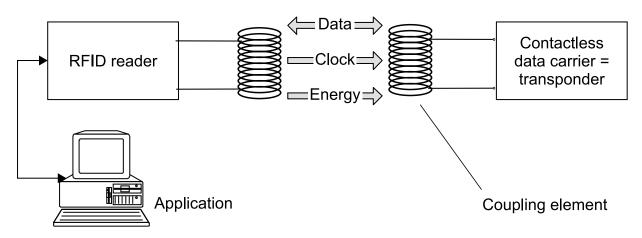

| 2.1  | Basic RFID system (adapted from [2])                                                 | 3  |

|------|--------------------------------------------------------------------------------------|----|

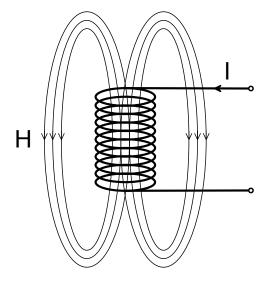

| 2.2  | Magnetic field of a current-carrying cylindrical coil (adapted from [2])             | 7  |

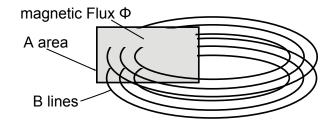

| 2.3  | Relation between magnetic flux $\Phi$ and magnetic flux density B (adapted from [2]) | 7  |

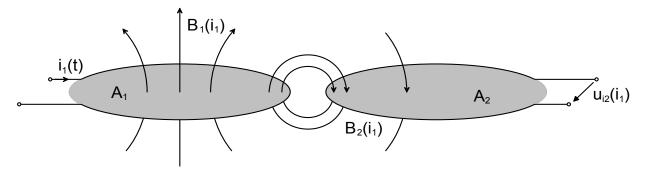

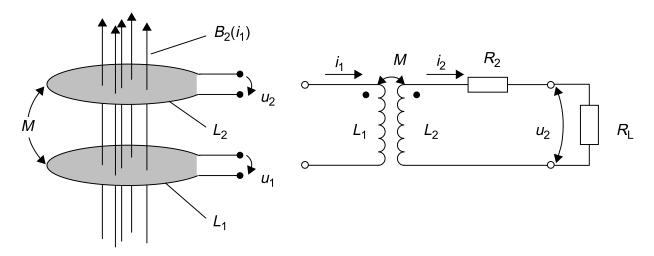

| 2.4  | Mutual induction (adapted from [2])                                                  | 8  |

| 2.5  | Transformer coupling (adapted from [2])                                              | 10 |

| 2.6  | The communication system (adapted from [2])                                          | 11 |

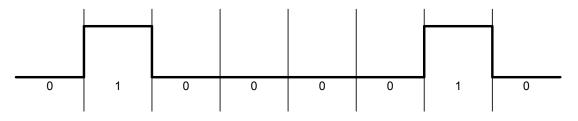

| 2.7  | Non-return to zero for binary string 01000010                                        | 11 |

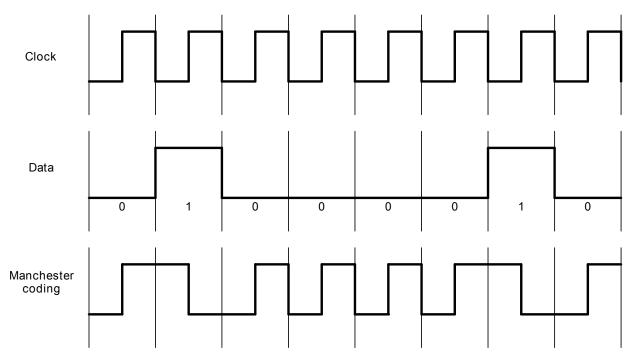

| 2.8  | Manchester coding for binary string 01000010                                         | 12 |

| 2.9  | Unipolar RZ for binary string 11100010                                               | 13 |

| 2.10 | Miller coding (a) and Modified Miller coding (b) of binary 01000010                  | 13 |

| 2.11 | Pulse-pause of binary 01010011                                                       | 14 |

| 2.12 | Generation of a 100% ASK modulation (adapted from [2])                               | 15 |

| 2.13 | Generation of binary FSK modulation (adapted from [2])                               | 15 |

| 2.14 | Generation of binary PSK modulation (adapted from [2])                               | 16 |

| 3.1  | 1 out of 256 coding mode VCD to VICC (adapted from [7])                              | 19 |

| 3.2  | Start of frame of the 1 out of 256 coding mode VCD to VICC (adapted from [7])        | 19 |

| 3.3  | End of frame for either mode VCD to VICC (adapted from [7])                          | 20 |

| 3.4  | 1 out of 4 coding mode VCD to VICC (adapted from [7])                                | 20 |

| 3.5  | 1 out of 4 coding example                                                            | 21 |

| 3.6  | Start of frame of the 1 out of 4 mode VCD to VICC (adapted from [7])                 | 21 |

| 3.7  | Logic 0 when using one subcarrier VICC to VCD [7]                                    | 22 |

| 3.8  | Logic 1 when using one subcarrier VICC to VCD [7]                                    | 22 |

|      |                                                                                      |    |

| 3.9                                                                                         | Start of frame when using one subcarrier VICC to VCD [7]                 | 22                                                                                 |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 3.10                                                                                        | End of frame when using one subcarrier VICC to VCD [7]                   | 22                                                                                 |

| 3.11                                                                                        | Logic 0 when using two subcarriers VICC to VCD [7]                       | 23                                                                                 |

| 3.12                                                                                        | Logic 1 when using two subcarriers VICC to VCD [7]                       | 23                                                                                 |

| 3.13                                                                                        | Start of frame when using two subcarriers VCD to VICC (adapted from [7]) | 23                                                                                 |

| 3.14                                                                                        | End of frame when using two subcarriers VCD to VICC (adapted from [7])   | 24                                                                                 |

| 3.15                                                                                        | VICC state transition diagram [6]                                        | 26                                                                                 |

| 3.16                                                                                        | Description of a possible anticollision sequence in MODE1 [6]            | 28                                                                                 |

| 3.17                                                                                        | PJM waveform[8]                                                          | 29                                                                                 |

| 3.18                                                                                        | Command MFM encoding of binary 00110101                                  | 30                                                                                 |

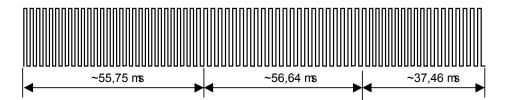

| 3.19                                                                                        | Two possible command flags (Interrogator to tag)[8]                      | 31                                                                                 |

| 3.20                                                                                        | Reply MFM encoding of binary 00110101                                    | 32                                                                                 |

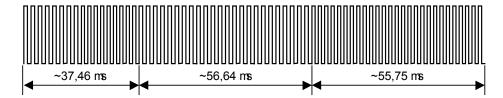

| 3.21                                                                                        | Two possible command flags (Tag to interrogator)[8]                      | 32                                                                                 |

| 3.22                                                                                        | Tag state diagram [8]                                                    | 35                                                                                 |

| 3.23                                                                                        | Anticollision management sequence in MODE2                               | 36                                                                                 |

| 4.1                                                                                         | SPI pins                                                                 | 38                                                                                 |

| 4.2                                                                                         | Clock tree of the STR71x (adapted from [10])                             | 39                                                                                 |

| 4.3                                                                                         | SPI pin usage                                                            | 40                                                                                 |

| 4.4                                                                                         | Flowchart MODE1 coding technique for the STR71x                          | 41                                                                                 |

| 4.5                                                                                         | Making of PPM Bytes for the STR71x MODE1                                 | 42                                                                                 |

|                                                                                             |                                                                          |                                                                                    |

| 4.6                                                                                         | MODE1 Start of frame                                                     | 43                                                                                 |

| 4.6<br>4.7                                                                                  |                                                                          |                                                                                    |

|                                                                                             | MODE1 Start of frame                                                     | 43                                                                                 |

| 4.7                                                                                         | MODE1 Start of frame                                                     | 43<br>43                                                                           |

| 4.7<br>4.8<br>4.9                                                                           | MODE1 Start of frame                                                     | 43<br>43<br>44                                                                     |

| 4.7<br>4.8<br>4.9<br>4.10                                                                   | MODE1 Start of frame                                                     | 43<br>43<br>44<br>45                                                               |

| <ol> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> <li>4.11</li> </ol>               | MODE1 Start of frame                                                     | 43<br>43<br>44<br>45<br>46                                                         |

| <ol> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> </ol> | MODE1 Start of frame                                                     | <ul> <li>43</li> <li>43</li> <li>44</li> <li>45</li> <li>46</li> <li>47</li> </ul> |

| 5.2 | Example of vicinity periods of binary 1                | 53 |

|-----|--------------------------------------------------------|----|

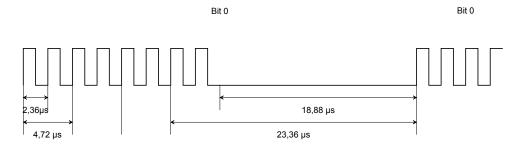

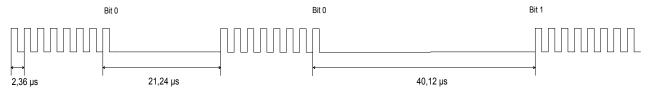

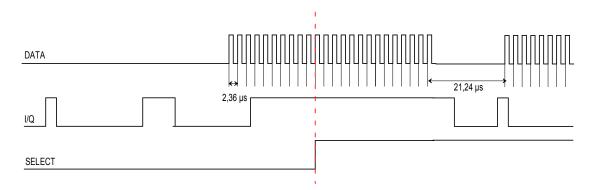

| 5.3 | MODE2 possible reply sequence                          | 53 |

| 5.4 | MODE2 reply flag                                       | 54 |

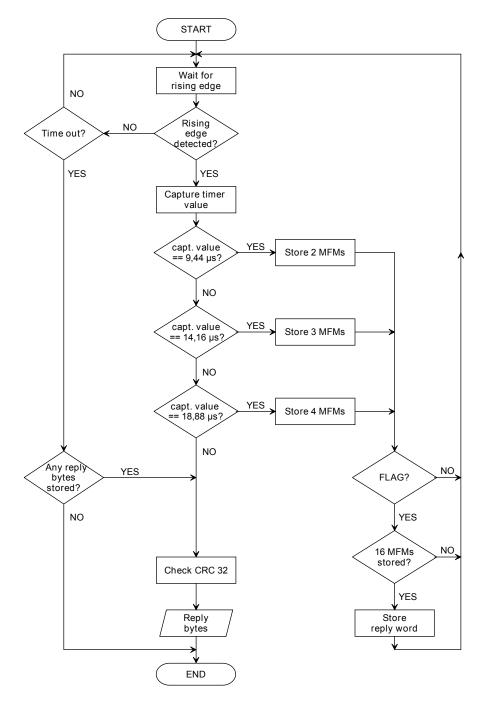

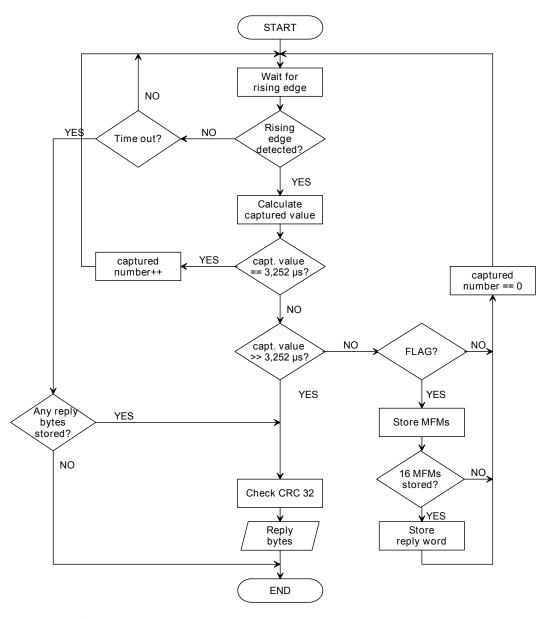

| 5.5 | Flowchart MODE2 decoding technique for the STR71x      | 55 |

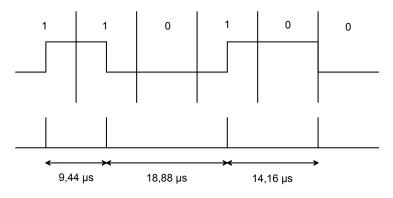

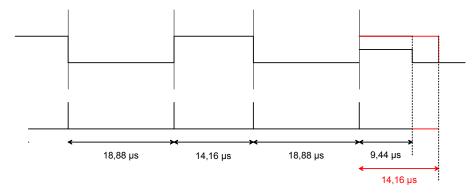

| 5.6 | Example of MODE1 periods of binary 001                 | 56 |

| 5.7 | MODE1 SOF detecting and demodulator channel decision   | 57 |

| 5.8 | Flowchart MODE1 decoding technique for the STM32x      | 59 |

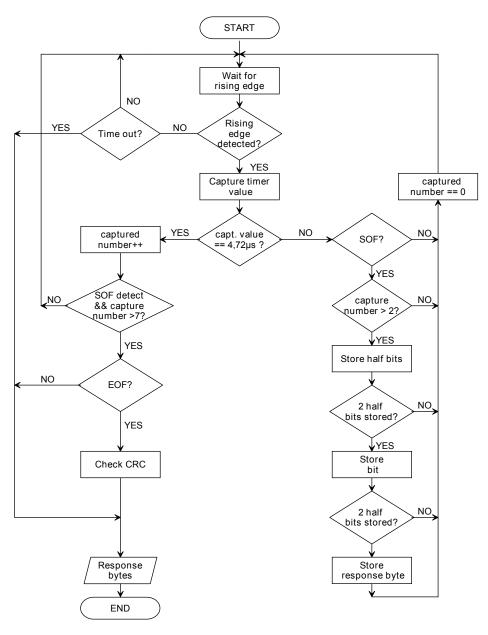

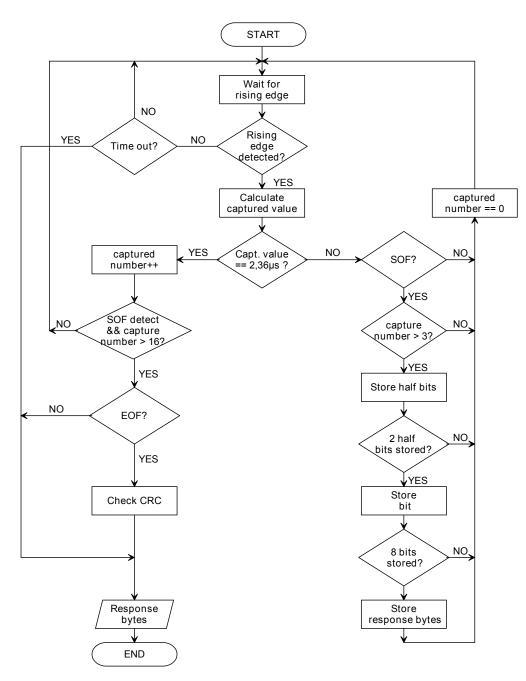

| 5.9 | Flowchart MODE2 decoding technique for the STM32x      | 62 |

| 6.1 | Interface between microcontroller and analog front-end | 63 |

# List of Tables

| 3.1         | Channel frequencies and division ratios(adapted from [8])                | 31 |

|-------------|--------------------------------------------------------------------------|----|

| 3.2         | Command fields(adapted from [8])                                         | 33 |

| 3.3         | Valid command format for group read and specific write(adapted from [8]) | 34 |

| 3.4         | Reply fields(adapted from [8])                                           | 34 |

| 4.1         | Signals for modulation type detection                                    | 37 |

| 5.1         | MFM bits detection MODE2 for the STR71x                                  | 54 |

| 5.2         | Creation of half bits for MODE1 STM32x                                   | 58 |

| A.1         | CRC 16 definition (adapted from [6])                                     | 68 |

| A.2         | Example of CRC16 calculation                                             | 69 |

| <b>B</b> .1 | CRC 32 definition (adapted from [8])                                     | 70 |

| B.2         | Example of CRC32 calculation (adapted from [8])                          | 71 |

# Glossary

| AFI   | Application Family Identifier               |

|-------|---------------------------------------------|

| APB   | Advanced Peripheral Buss                    |

| ARM   | Advanced RISC Machine                       |

| ASK   | Amplitude Shift Keying                      |

| BPSK  | Binary Phase Shift Keying                   |

| СРНА  | Clock Phase                                 |

| CPOL  | Clock Polarity                              |

| CRC   | Cyclic Redundancy Check                     |

| DSFID | Data Storage Format Identifier              |

| EOF   | End Of Frame                                |

| FIFO  | First In, First Out                         |

| FSK   | Frequency Shift Keying                      |

| FTDMA | Frequency and Time Division Multiple Access |

| HF    | High Frequency                              |

| HSE   | High Speed External                         |

| HSI   | High Speed Internal                         |

| IC    | Integrated Circuit                          |

| IEC  | International Electrotechnical Commission      |

|------|------------------------------------------------|

| ISO  | International Organization for Standardization |

| JTC  | Joint Technical Committee                      |

| LSB  | Last Significant Bit                           |

| LSE  | Low Speed External                             |

| LSI  | Low Speed Internal                             |

| MFM  | Modified Frequency Modulation                  |

| MISO | Master In Slave Out                            |

| MOSI | Master Out Slave In                            |

| MSB  | Most Significant Bit                           |

| NRZ  | Non-Return to Zero                             |

| PJM  | Phase Jitter Modulation                        |

| PPM  | Pulse Position Modulation                      |

| PSK  | Phase Shift Keying                             |

| RFU  | Reserved for Future Use                        |

| RZ   | Return to Zero                                 |

| SOF  | Start Of Frame                                 |

| SPI  | Serial Peripheral Interface                    |

| UID  | Unique Identifier                              |

| VCD  | Vicinity Coupling Devices                      |

| VICC | Vicinity Integrated Circuit Card               |

## 1. Introduction

*Radio Frequency Identification* (RFID) is a technology for identifying objects using a radio frequency signal. This technique is part of automatic identification procedures (auto-ID) and at first was intended as a replacement for bar codes. But the range of application of RFID systems increased enormously and it quickly became more then just a better version of bar codes. Today, RFID systems have become a part of our every day life. They are most commonly used as antitheft devices in shops. Further fields of application lie in e.g. ticket services for public transport, car and automotive industry, animal tracing, pharmaceuticals and medical industry, e-passports, etc. This particular type of RFID systems are more related to a chip card than to bar codes. The data is stored on an electronic carrier while the energy support and data exchange is contactless.

A typical RFID system consists of a reader (also called interrogator) and one or more transponders (tags). The transponder can be attached to any object or animal that needs to be identified. The reader emits an electromagnetic field which is used for data transmission. If the tag is *passive*, then the electromagnetic field of a reader is also used for energy supply.

Since the applications for RFID systems are getting more and more complex, the demands on tags are also growing. First of all, the tags memory capacity is growing. Automatically, the data transfer time becomes longer, making data transfer speed another very important factor in RFID systems development. The next important step in RFID systems development is reading and writing data to multiple tags within field. This diploma thesis particularly focuses on RFID systems defined in ISO/IEC 18000-3, which are generally based on a multiple tags in field communication.

The ISO/IEC 18000-3 MODE1 is compatible with ISO/IEC 15693. The tags based on this standard are also called *vicinity* tags. They are used for asset tracking, inventory tracking, document tracking, parking management and supply chain integration.

The ISO/IEC 18000-3 MODE2 covers the phase jitter modulation (PJM) technology which is 10 times faster than other HF technologies. PJM tags are designed for applications where many

#### CHAPTER 1. INTRODUCTION

tags are stacked together such as documents management, gamings, medicine, pharmaceuticals and jewelry. In documents management, for instance, it is possible to detect all documents with tags even if they are stacked together without separation, e.g. in shelves.

The aim of this diploma thesis was to create a low cost reader that would support MODE1 and MODE2 of ISO/IEC 18000-3. The analog front end of a reader is coverd by Eva-Maria Hanzl as part of her diploma thesis "Analog Front End for a Contactless Desktop Reader supporting ASK and PSK modulation techniques". This diploma thesis focuses on programming of a microcontroller embedded in a analog front-end. First, the microcontroller codes the reader command and sends it to the analog front-end, which modulates it and emits a modulated signal via antenna. After tag response on the command, the load modulated signal is demodulated by the analog demodulator. Then the microcontroller has to demodulate the subcarrier and decode the data.

The first part of this document is a short introduction to RFID systems in general (2). The parts of RFID systems reader and transponder are explained. The RFID systems classification is given based on operating frequency and range. Also, there is a short introduction to coding and modulation techniques which are most commonly used in RFID systems. The next chapter will provide an overview of the ISO/IEC 18000-3 (3). Therein, the communication signal interface between reader and transponder and other way around will be explained. In addition, the command and reply format are introduced. Since MODE1 is compatible with the ISO/IEC 15693, this chapter will cover this standard as well. In Chapter 3, the coding techniques for both modes are explained and, also, the microcontroller configuration. Decoding techniques are described in Chapter 4. Finally the conclusions are presented in Chapter 6.

## 2. Overview of RFID technology

The following chapter presents a short overview of the RFID technology. In order to properly understand the way a transceiver works, basic knowledge of RFID technology is essential. The following sections are according to [2].

### 2.1 Typical RFID components

Every RFID system consists of a minimum of two components: a *transceiver* and a *transponder*. The transponder or tag is attached to an object and can be seen as a data-carrying device. A transceiver or reader is able to read data from tag. Depending on its field of application, a reader can also write data onto a transponder.

Figure 2.1: Basic RFID system (adapted from [2])

#### CHAPTER 2. OVERVIEW OF RFID TECHNOLOGY

#### 2.1.1 Transponder

There are many types and forms of transponders, but they can altogether be divided into three major groups:

- **Low-end systems** have a memory size of a few bytes. With these systems, memory can only be read. The most prominent example for this system are the 1-Bit-Transponders, which are only used to detect whether an object is or is not within reader field. These systems have no anticollision algorithm.

- **Mid-range systems** are more complex and have a larger memory size (up to 100 kbytes). Memory can be read and written. They have anticollision algorithms, which makes it possible to place more than one transponder in the reader field.

- **High-end systems** have the largest memory size and are equipped with a microprocessor. This enables them to process more complex commands.

Depending on their power supply, mid-range and high-end systems can be classified into *active* and *passive* transponders. Active transponders have an internal power supply consisting of batteries or solar cells. Passive transponders, on the other hand, obtain their energy from the reader field. Both types have their advantages and disadvantages. An active transponder can be read at large distances, but it can not function without a battery, so the lifetime is limited. Such transponders are usually larger and more expensive. Passive transponders are significantly less expensive, much smaller and last longer. One of the major disadvantages here is, however, that passive transponders can only be read from short distance.

All of the above mentioned types of transponders come in different sizes and shapes, depending on their type of application. Some of the usual transponder shapes include: disks, cylinders, cards, keyfobs, smart labels etc.

### 2.1.2 Reader

The reader controls the communication process of RFID systems. Elements of a reader such as this include: a transmitter and receiver, a control unit and a coupling device. The reader generates an electric, magnetic or electromagnetic field, which supplies transponders with power and transmits data and commands. Besides the basic functions like power supply and data control, the reader should be able to preforming more complex tasks such as: anticollision, authentication and data encryption.

### 2.2 Classification of RFID systems

There are many ways to classify RFID systems based on their characteristics. The following subsections shall discuss only those who are most important and most relevant for this diploma thesis.

### 2.2.1 Operating frequency

As previously mentioned, the reader generates an electromagnetic field. The frequency of this field is called *operating frequency* of the RFID system. All RFID systems operate in following frequency bands:

- Low Frequency [LF] range from 30 kHz to 300 kHz

- High Frequency [HF] range from 3 MHz to 30 MHz

- Ultra High Frequency [UHF] range from 300 MHz to 3 GHz

### 2.2.2 Range

The area size that is covered by a reader where transponders can be identified is called range. There are three categories of RFID systems based on their range: close coupling systems, remote coupling systems and long range coupling systems.

Some of the main characteristics of *close coupling* systems are:

- range is less then one centimeter

- coupling is based on electric and magnetic energy

- frequency values lie between DC and 30 MHz

- As example door locking systems

*Remote coupling* systems have following characteristics:

- range is up to one meter

- coupling is mostly based on magnetic energy

#### CHAPTER 2. OVERVIEW OF RFID TECHNOLOGY

- frequency values lie between 135 kHz and 13.56 MHz

- As example contactless smart cards

And finally the long range coupling systems can be recognized by the following characteristics:

- range can reach to a meter and beyond

- coupling is based on electromagnetic waves. They operate like conventional radio systems

- frequency values lie between 890 MHz and 930 MHz or 2.45 GHz

- Used for logistics

### 2.3 Physical fundamentals of RFID

As already mentioned in the previous section, inductive coupling is a common type of remote coupling. Some of the most common types in recent years have been various kinds of inductively coupled tags, including tags that follow the ISO/IEC 15693 standard for vicinity-coupled smart cards [5]. As the ISO/IEC 18000-3 tags also are inductively coupled tags, the next subsection will explain the basics of a magnetic field.

### 2.3.1 The magnetic field

The magnetic field is produced by all moving charges. It can be described by a *magnetic field strength* H vector, which depends on the amplitude of the current. Conductors are mostly loop-shaped. If there is more than one loop stacked together, we have a short cylindrical coil and the H is equal to:

$$H = N \frac{I}{2\pi r} \tag{2.1}$$

N represents the number of loops while r stands for radius. The maximum strength is concentrated in the center of the coil. Increasing the current or the number of the loops would also increase the strength of the magnetic field.

Figure 2.2: Magnetic field of a current-carrying cylindrical coil (adapted from [2])

The *Magnetic flux*  $\Phi$  and the *magnetic flux density* B, also represent the physical measures for describing the magnetic field

$$\Phi = \int_{A} \mathbf{B} \cdot d\mathbf{A} \tag{2.2}$$

Formula 2.2 shows that  $\Phi$  is calculated by determining the total number of streamlines of a magnetic field that pass through a specified area A. B denotes the number of flux lines by a certain area. If B is constant, the formula can be simplified as follows:

$$\Phi = |\mathbf{B}| \cdot A = B \cdot A. \tag{2.3}$$

Figure 2.3: Relation between magnetic flux  $\Phi$  and magnetic flux density B (adapted from [2])

$\Phi$  and therefore B depend on the material present in the magnetic field. The property of the material relevant for the magnetic field is called magnetic conductivity  $\mu$ . According to that,  $\Phi$

and B can be calculated as follows:

$$\Phi = B \cdot A = \mu_0 \mu_r \mathbf{H} A = \mu \mathbf{H} A \tag{2.4}$$

$\begin{array}{ll} \mu_0 & \dots & \text{magnetic field constant} \ (\mu_0 = 4\pi \cdot 10^{-7} \, \text{Vs}/\text{Am}) \\ \mu_r & \dots & \text{relative permeability of the material} \ (\mu_{r,air} = 1) \end{array}$

The quotient of the magnetic flux generated and the current flowing are called *inductance* L. L is a measure for how much flux can be created by a certain current. There are two types of inductance called self-induction and mutual-induction. Self-induction happens when an electromotive force and a voltage are induced in the same circuit in which the current and flux are changing.

$$L = \frac{N\Phi}{I} = \frac{N\mu HA}{I} \tag{2.5}$$

If an electromotive force and a voltage are induced into one circuit as a result of current and flux changing in another circuit, than we are talking about mutual-induction (see Figure 2.4).

Figure 2.4: Mutual induction (adapted from [2])

Two conductor loops are placed next to each other. Current  $I_1$  flows through loop 1 and consequently, a magnetic flux  $\Phi_1(I_1)$  occurs. This loop is called *exciting*. A part of this flux penetrates the remote conductor loop 2, which is called *adjacent*, and this flux is defined as  $\Phi_2(I_1)$ . The relation between these two flux is called mutual-induction and is described in formula 2.6:

$$M_{21} = \frac{\Phi_2(I_1)}{I_1} \tag{2.6}$$

#### CHAPTER 2. OVERVIEW OF RFID TECHNOLOGY

Actually, it is entirely irrelevant which loop is exciting and which one is adjacent, since  $M_{21}=M_{12}=M$ .

The coupling flux depends on the dimensions and geometry of both conductor loops and their position to each other. The *coupling factor* k is used to provide qualitative information about magnetic coupling, independently from geometric dimensions.

$$k = \frac{M}{\sqrt{L_1 \cdot L_2}} \tag{2.7}$$

The value of k can be between 0 (completely decoupled) and 1 (perfectly coupled).

### 2.3.2 The alternating magnetic field

While the previous subsection was a short introduction of a static magnetic field, this subsection will provide a short overview of an alternating magnetic field.

Change of magnetic flux  $\Phi$  generates an electric field. Electromagnetic waves will be produced by an alternating electric, magnetic field, if vacuum is present as a medium. If there is an open conductor loop present, induction voltage  $u_i$  (see formula 2.8) will be generated at the end of the loop.

$$u_i = -\frac{d\Phi(t)}{dt} \tag{2.8}$$

If there are two open conductors loops and one is generating an alternating magnetic field while the other is affected by it, energy can be transferred. This type of coupling is called transformer coupling and is used to supply passive transponders with power. Figure 2.5 depicts this principle. In exciting loop L1, current  $I_1$  flows as result of voltage  $u_1$ . An alternating magnetic field is generated and it penetrates  $L_2$ . As a result, voltage  $u_2$  is induced. This means that an alternating current in one loop can induce an alternating voltage in another loop within near filed. The right part of the figure shows a circuit for the transformer setup. The left part shows a real system, where resistors are present.

Figure 2.5: Transformer coupling (adapted from [2])

$R_2$  ... resistance of the loop windings

$R_L$  ... resistance applied to the loop

### 2.4 Coding and modulation

The main aim of this diploma thesis was to design coding and decoding techniques for the ISO/IEC 18000-3. Therefore, this section provides an in-depth analysis of coding techniques used in RFID and, also, a short overview on digital modulation.

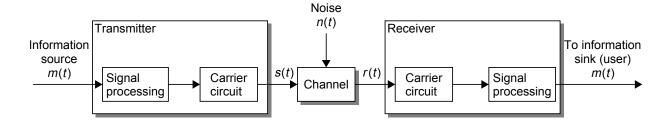

Data transfer between reader and transponder can be divided into three major sections (see Figure 2.6):

- signal coding (signal processing) and the modulator (carrier circuit/analog front end) in the reader (transmitter)

- the transmission medium (channel)

- signal decoding (signal processing) and the demodulator (carrier circuit) in the transponder (receiver)

The modulator acts as an interface to the actual communication medium and often involves functions such as frequency conversion, amplification, and antenna-like transducers. The channel encoder is a discrete-input/discrete-output device whose usual purpose is seen in providing some error-correction capability for the system [21].

Figure 2.6: The communication system (adapted from [2])

### 2.4.1 Coding

The term signal coding actually stands for optimizing a signal (data baseband) according to the characteristics of the transmission channel (medium magnetic field). This procedure provides protection against interference and collision.

The following subsections will discuss some of the most commonly used line codes in RFID systems.

#### 2.4.1.1 Non-return to zero

Non-return to zero (NRZ) is the simplest line code. In this code, a binary 1 is represented as a high signal and binary 0 as a low signal. Usually, NRZ is used with PSK or FSK modulation. The biggest problem with this line code occurs when confronted with a large number of bits of the same value. It is very hard to detect boundaries of the received bits at the receiver. Figure 2.7 shows NRZ for binary string 01000010.

Figure 2.7: Non-return to zero for binary string 01000010

#### CHAPTER 2. OVERVIEW OF RFID TECHNOLOGY

#### 2.4.1.2 Manchester code

The Manchester coding uses a negative transition in the middle of bit 1 and a positive transition in the middle of bit 0. The transitions of this type of coding are synchronized with the clock (see Figure 2.8). This way, sender and receiver are easy to synchronize, making the code applicable for a large series of bits carrying the same value.

The Manchester coding is used by ISO/IEC 18000-3 MODE1 for data transmission from vicinity-card to vicinity coupling device (see Section 3.1).

Figure 2.8: Manchester coding for binary string 01000010

#### 2.4.1.3 Unipolar RZ coding

RZ means return to zero. This means that at some point of a bit interval, the signal returns to a point that is either high or low. During the first half bit period, binary 1 is represented by a high signal. Binary 0 is the same as in NRZ, and therefore low. The problem of a long string of 1-es is solved, but this technique is still problematic when it comes to detecting boundaries of the received long string of 0-s. Figure 2.9 depicts unipolar RZ for binary string 11100010.

Figure 2.9: Unipolar RZ for binary string 11100010

#### 2.4.1.4 Miller coding

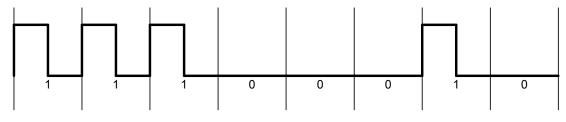

The Miller coding means that bit '1' is going to have a state change at the middle of a bit interval and a bit '0' at the beginning of a bit interval. If bit '0' follows bit '1', no state change will occur. This coding is also known as *modified frequency modulation*(MFM) and is used by ISO/IEC 18000-3 MODE2 for data transmission (see Section 3.2).

Besides the standard Miller code, there is, also, a modified Miller code where every transition is replaced by a negative pulse. This variant is often used in RFID. The pulse is very short, allowing a continuous power supply from reader to transponder during data transmission. Figure 2.10 shows an example for binary string 01000010 in both Miller coding (a) and modified Miller coding (b).

Figure 2.10: Miller coding (a) and Modified Miller coding (b) of binary 01000010

### 2.4.1.5 Pulse-pause coding

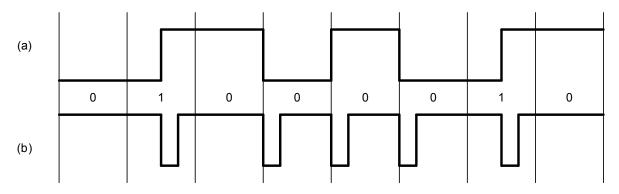

Pulse-pause coding is a very simple coding type. Here, binary 1 represents a pause of duration t and binary 0 the pause of duration 2t. Just like in modified Miller coding, the pulse durations here are very short. Therefore, it is possible to provide continuous power supply for the transponder. An example of pulse-pause coding is shown in figure 2.11.

Figure 2.11: Pulse-pause of binary 01010011

### 2.4.2 Digital modulation

Digital modulation is the transformation of a digital signal into waveforms that are compatible with a transmission medium (channel). There are three types of modulation: amplitude shift keying (ASK), frequency shift keying (FSK) and phase shift keying (PSK).

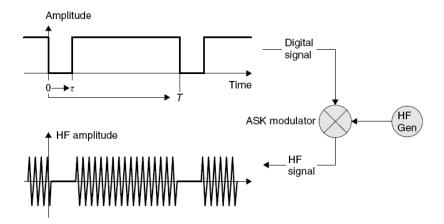

#### 2.4.2.1 Amplitude shift keying

Amplitude shift keying is used in ISO/IEC 18000-3 MODE1. This particular type of keying sends digital data over analog carriers by changing the amplitude of a wave in time with the data stream. The amplitude of the carrier signal is switched according to the baseband signal. The analytic expression for ASK is:

$$s(t) = A(t) \cdot \cos(\omega_0 t + \varphi_0) \tag{2.9}$$

A(t) represents the baseband information and  $\cos(\omega_0 t + \varphi_0)$  represents the carrier. A binary ASK can be characterized by the *modulation index m* (see formula 2.10) which is a measure for the ratio of the amplitude levels.

$$m = \frac{\hat{u}_{HI} - \hat{u}_{LO}}{\hat{u}_{HI} + \hat{u}_{LO}} \cdot 100\%$$

(2.10)

The modulation index ranges from 0, meaning no modulation, to 100%, meaning that one amplitude state is zero. MODE1 of ISO/IEC 18000-3 uses two modulation indexes, 10% and 100%.

ASK can actually be described as a multiplication of an unipolar digital baseband signal and a high-frequency, sinusoidal carrier signal as shown in figure 2.12.

Figure 2.12: Generation of a 100% ASK modulation (adapted from [2])

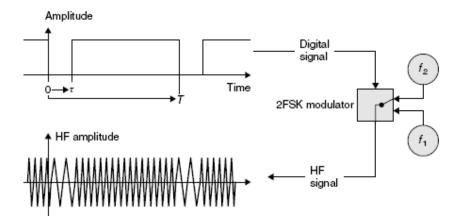

#### 2.4.2.2 Frequency shift keying

Frequency shift keying sends changes through the frequency of the wave. The analytic expression for FSK modulation is:

$$s(t) = A \cdot \cos\left(\omega_0(t) t + \varphi_0\right) \tag{2.11}$$

$\omega_0(t) t$  represents the frequency that changes. The simplest FSK is a binary FSK, which means using a couple of discrete frequencies to transmit binary information. Figure 2.13 depicts the generation of a binary FSK.

Figure 2.13: Generation of binary FSK modulation (adapted from [2])

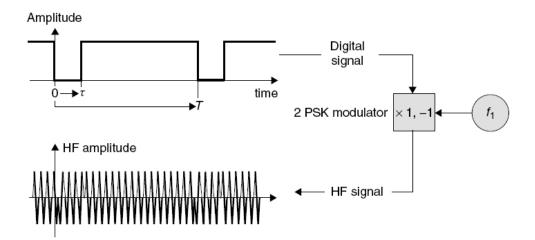

#### 2.4.2.3 Phase shift keying

Phase shift keying means that the phase of a carrier signal is modulated. Mathematically, PSK can be described as follows:

$$s(t) = A \cdot \cos(\omega_0 t + \varphi_0(t)) \tag{2.12}$$

$\varphi_0(t)$  represents the phase that changes. The simplest PSK is a binary PSK (BPSK). The binary states '1' and '0' are converted into corresponding phase states, in this case 0° and 180°. Mathematically, a binary PSK is the same as a multiplication of the carrier oscillation by 1 and -1. The generation of this type of modulation is shown in figure 2.14.

Figure 2.14: Generation of binary PSK modulation (adapted from [2])

Communication between the tag and the reader by ISO/IEC 18000-3 MODE2 takes place by using BPSK. Communication between reader and tag takes place by using *phase jitter modulation PJM*. PJM will be explained in further detail in chapter 3 (see section 3.2.1.1).

## 3. ISO/IEC 18000-3

The *International Organization for Standardization* (ISO) and the *International Electrotechnical Commission* (IEC) are the worlds largest publisher of international standards. The members of ISO or IEC are national bodies that participate in the development of international standards. ISO and IEC have technical committees which deal with particular fields of technical activity, and collaborate with each other due to mutual interest.

ISO/IEC JTC1 is a joint technical committee of ISO and IEC in the field of information technology. The ISO/IEC 18000 *Radio frequency identification for item management* has been developed by this committee. The main goal of this protocol is to use the same protocols for all frequencies, where possible. This way, the problems of migrating from one frequency to another would be minimized, just like the costs for software and implementation. This standard consists of 7 parts:

- Part 1: Reference architecture and definition of parameters to be standardized

- Part 2: Parameters for air interface communications below 135 kHz

- Part 3: Parameters for air interface communications at 13.56 MHz

- Part 4: Parameters for air interface communications at 2.4 GHz

- Part 5: Parameters for air interface communications at 5.8 GHz (withdrawn)

- Part 6: Parameters for air interface communications at 860 MHz to 960 MHz

- Part 7: Parameters for air interface communications at 433 MHz

This diploma thesis focuses on the ISO/IEC 18000-3. It has three MODES of operation. MODE1 is compliant with ISO/IEC 15693, which will be described in the next section 3.1. MODE2 is completely defined in section 3.2. MODE3 is a high speed interface with two options.

Option 1 is ASK based, option 2 is PJM based. Since MODE3 is not included in this diploma thesis it will not be described. Though all of the above modes are not interoperable, they are also non-interfering.

### 3.1 ISO/IEC 18000-3 MODE1

Since the ISO/IEC 18000-3 MODE1 is compatible with ISO/IEC 15693, the following subsections will cover this standard.

ISO/IEC 15693 forms a part of a series of International Standards that specify a contactless smart card. The standard consists of four parts. The first three parts are: *Part 1 - Physical characteristics*, *Part 2 - Air interface and initialization* and *Part 3 - Anticollision and transmission protocol* shall be described in the next sections.

Part 4 - Extended command set and security features will not be described since it is not an integral part of this diploma thesis.

### 3.1.1 ISO/IEC 15693 Part 1

This part describes the physical characteristics of a transponder. In this standard, the transponder is referred to as *Vicinity integrated circuit card* (VICC). A card of the card type ID-1 into which integrated circuit(s) and coupling means have been placed and in which communication to such integrated circuit(s) is done by inductive coupling in the vicinity of a coupling device. The reader that provides power and control for data transmission is referred to as *vicinity coupling device* (VCD).

### 3.1.2 ISO/IEC 15693 Part 2

The second part of ISO/IEC 15693 defines the power and data transfer between VICC and VCD. The VCD produces a magnetic field. The frequency of the field is  $13.56 \text{ MHz} \pm 7 \text{ kHz}$ . The field strength should lie between 150 mA/m and 5 A/m. Whenever power is received by the card, it is able to respond to incoming commands from the VCD.

#### 3.1.2.1 Communications signal interface VCD to VICC

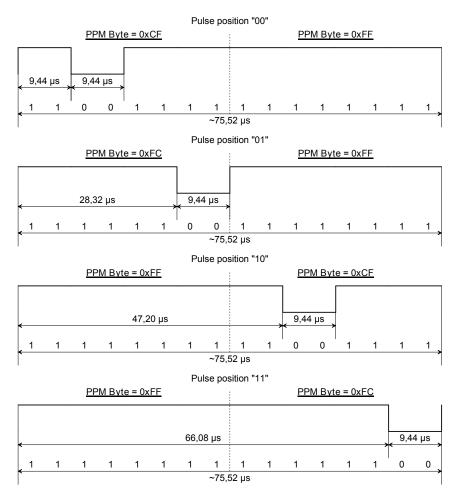

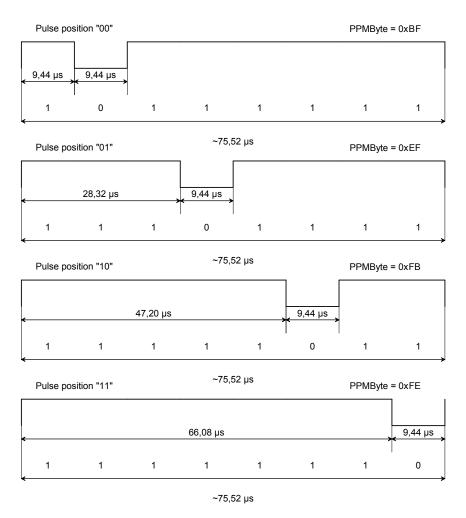

ASK is a modulation principle used in communication between the VCD and the VICC. The modulation index can be either 10% or 100% (see section 2.4.2.1). The VCD decides which one is to be used. Data coding will be implemented using pulse position mode. The VICC supports two data coding modes: *1 out of 256* and *1 out of 4*. Since this thesis is focusing on a low-cost transceiver, only the 1 out of 4 mode will be used.

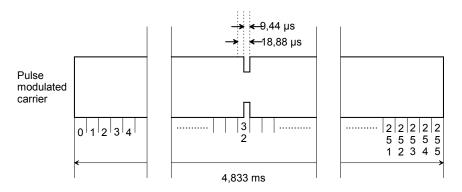

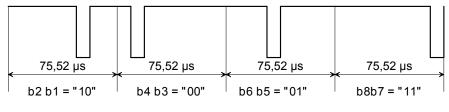

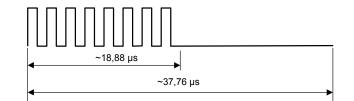

#### 1 out of 256 coding mode

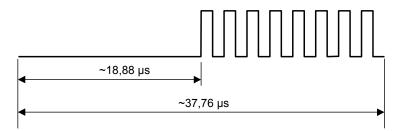

In this coding technique the one byte value is represented by the position of one pause. The value of the byte is determined by the position of the pause. One pause has a length of 18.88  $\mu$ s  $(256/f_c)$  which gives us a byte length of 4.833 ms. The next figure depicts this pulse position modulation technique for byte '20'  $((20)_h = (32)_h)$  sent by the VCD to the VICC.

Figure 3.1: 1 out of 256 coding mode VCD to VICC (adapted from [7])

Data framing is used at the beginning and at the end of every command. These data frames represent code violations. They are used to make synchronization and independence of protocol easier. Figure 3.2 depicts the SOF for this coding technique.

Figure 3.2: Start of frame of the 1 out of 256 coding mode VCD to VICC (adapted from [7])

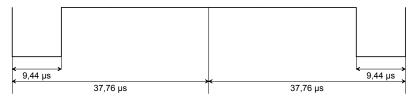

The EOF is described in the next figure. It is the same for both coding modes.

Figure 3.3: End of frame for either mode VCD to VICC (adapted from [7])

### 1 out of 4 coding mode

Figure 3.4 depicts the 1 out of 4 pulse position technique and coding.

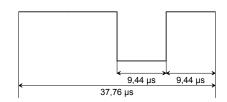

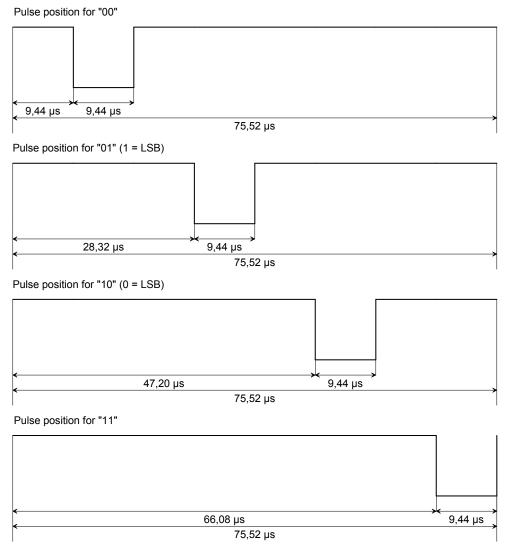

Figure 3.4: 1 out of 4 coding mode VCD to VICC (adapted from [7])

Two bits are coded as the position of a 9.44  $\mu$ s pause in a 75.52  $\mu$ s symbol time, providing a bit rate of 26.48 kbits/s. The least significant bits are being transmitted first. Figure 3.5 shows a transmission example of byte 'D2' ( $(D2)_h = (11010010)_b$ ). First, the LSB pair '10' is being transmitted.

Figure 3.5: 1 out of 4 coding example

Figure 3.6 depicts the SOF of the 1 out of 4 data coding mode. As already mentioned, the EOF is the same as in the previous mode (see figure 3.3).

Figure 3.6: Start of frame of the 1 out of 4 mode VCD to VICC (adapted from [7])

#### 3.1.2.2 Communications signal interface VICC to VCD

One or two subcarriers may be used as selected by the VCD. The VICC supports both modes. In order to keep the transceiver simple, only one subcarrier will be used in this diploma thesis.

#### Bit representation and coding when using one subcarrier

The frequency of the subcarrier load modulation will be  $f_c/32 = 423.75$  kHz. Data shall be encoded using Manchester coding. Logic 0 starts with 8 pulses of  $f_c/32$  (423.75 kHz), followed by unmodulated time  $256/f_c$  (18.88  $\mu$ s). Logic 1 works the other way round, as to be seen in figures 3.7 and 3.8.

Figure 3.7: Logic 0 when using one subcarrier VICC to VCD [7]

Figure 3.8: Logic 1 when using one subcarrier VICC to VCD [7]

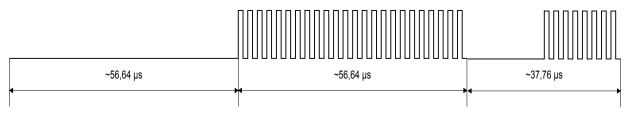

Just like the commands, responses also include data framing. The data frames represent code violations. When using one subcarrier, a start of frame comprises of three parts (see figure 3.9). First, there is an unmodulated time of minimum  $768/f_c$  (56.64 µs), followed by 24 pulses of  $f_c/32$  (423.75 kHz) and a logic 1 at the end.

Figure 3.9: Start of frame when using one subcarrier VICC to VCD [7]

The end of a frame also comprises of three parts (see figure 3.10). At the beginning, there is a logic 0, followed by 24 pulses of  $f_c/32$  (423.75 kHz) and after that an unmodulated time of minimum  $768/f_c$  (56.64  $\mu$ s).

Figure 3.10: End of frame when using one subcarrier VICC to VCD [7]

### CHAPTER 3. ISO/IEC 18000-3

### Bit representation and coding when using two subcarriers

Using two subcarriers logic 0 starts, also, with 8 pulses of  $f_c/32$  (423.75 kHz) and is then followed by 9 pulses of  $f_c/28$  (484.28 kHz).

Figure 3.11: Logic 0 when using two subcarriers VICC to VCD [7]

Logic 1 starts with 9 pulses of  $f_c/28$  and ends with 8 pulses of  $f_c/32$ .

Figure 3.12: Logic 1 when using two subcarriers VICC to VCD [7]

Similar as in one carrier, SOF and EOF also have tree parts. SOF starts with 27 pulses of  $f_c/32$  (423.75 kHz), followed by 24 pulses of  $f_c/32$  (423.75 kHz) and at the end, logic 1 (see figure 3.13). Parts of EOF are: logic 0, 24 pulses of  $f_c/32$  (423.75 kHz) and 27 pulses of  $f_c/32$  (423.75 kHz), as depicted in figure 3.14.

Figure 3.13: Start of frame when using two subcarriers VCD to VICC (adapted from [7])

Figure 3.14: End of frame when using two subcarriers VCD to VICC (adapted from [7])

# 3.1.3 ISO/IEC 15693 Part 3

This part describes the anticollision and transmission protocols. Furthermore, it discusses topics such as protocol, commands and other parameters required to initialize communication between a VICC and a VCD. Besides anticollision, the optional means for an easier and more efficient selection of one out of several cards based on their application criteria is described.

### 3.1.3.1 VICC data elements

All VICCs have a *unique identifier* UID. The UID is used to address each VICC individually and is set by the IC manufacturer. The 8 MSB bits are 'E0', followed by a 8 bits IC manufacturer code and a unique serial number of 48 bits. Another part of VICC data is the application family identifier (AFI). AFI is used to extract from all VICCs present in reader field only the VICCs that are needed for application chosen by VCD. AFI is programed and locked by VCD commands. Not all VICCs support AFI. If AFI is not supported by a VICC, it will ignore all requests that have AFI value.

The way data is structured in the VICC memory may, also, be programmed and locked by the VCD commands. This is called a data storage format identifier (DSFID). VICC memory is organized in blocks. Up to 256 blocks can be addressed and block size can average up to 256 bits.

### 3.1.3.2 Request and response format

The transmission protocol defines data exchange between VCD and VICC and vice versa. It is based on the so called *reader talks first* concept which means that the VICC can only transmit after receiving a valid command from the VCD. Each VCD request and VICC response are contained in a frame (SOF and EOF). The VCD sends a request consisting of flags, command code, mandatory and optional parameter fields, application data fields and CRC. The VICC response consists of: flags, mandatory and optional parameter fields depending on command, application

### CHAPTER 3. ISO/IEC 18000-3

#### data fields and CRC.

**Flags** specify which actions should be preformed by VICC (request flags) or have been preformed (response flags) and which corresponding fields are present. Using flags the VCD specifies: whether one or two subcarriers will be used, which data rate will be used and whether all or only the one VICC in field shall respond.

**The command code** is only present within a request. There are four types of commands. The *Mandatory commands* are supported by all VICCs. The command codes range from '01' to '0F'. Then there are *Optional commands* whit a code range from '20' to '9F'. The VICCs may support them, though not compulsory. The *Custom commands* are manufacturer specific functions and range from 'A0' to 'DF'. Last but not least, there are *Proprietary commands* that are used for tests and programming of system information. Their range lies between 'E0' and 'FF'.

Mandatory and optional parameters fields are parts of a request or a reply that depend on the command sent by the VCD. If for instance, the VCD sends an inventory command during the anticollision sequence, the command may have a *mask length* and *mask value* block. Mask value keeps the value of right received bytes and mask length has the length of the mask. Only those VICCs whose UID starts with these bytes are going to respond. AFI and DSFID fields are, also, optional parameters for requests.

**Application data** depends, also, on a command that is sent by the VCD. For example if the VCD sends a write command, it has to contain the number of blocks which will be written on and the data that needs to be written on the VICC.

**CRC** is a technique used for detecting errors in digital data transmission. A *Checksum*, meaning a particular number of check bits, is added to the message being transmitted. The receiver can determine whether or not the check bits agree with the data. Appendix A gives an example along with a description of the CRC detection method.

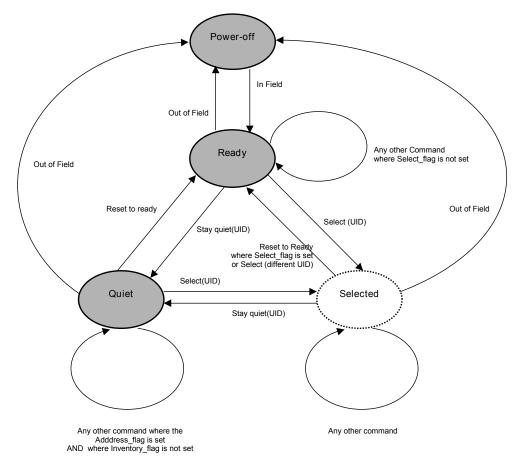

### 3.1.3.3 VICC states

Depending on VCD commands, the VICC can be in four different states. Figure 3.15 shows these VICC states. The *Power-off* state is a mandatory state where the VICC can not be activated by the VCD. Another mandatory state is *Ready*. The VICC is in ready state when activated by a VCD and can process any request if the *Select-flag* is not set. *Quiet* state means that the VICC can process any request where the *Address-flag* is set and the *Inventory-flag* is not. *Select* state is the only optional state where the VICC shall process only requests with the *Select-flag* set.

Figure 3.15: VICC state transition diagram [6]

### 3.1.3.4 Anticollision

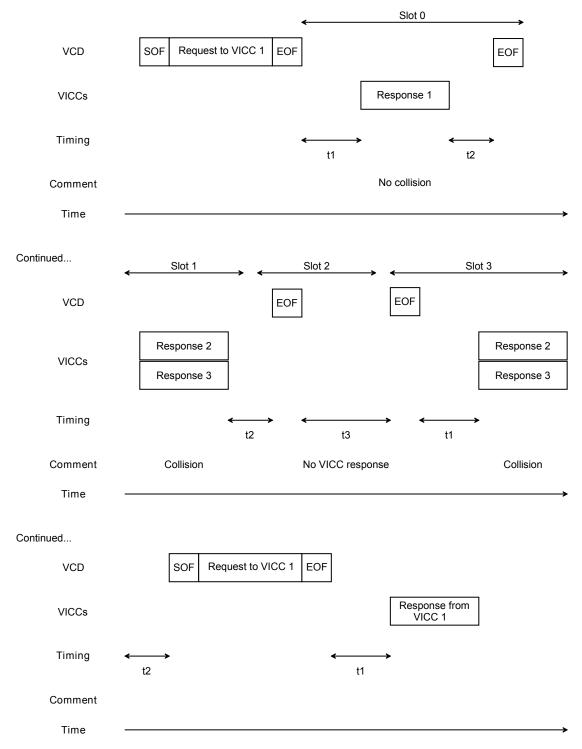

An anticollision sequence is needed whenever multiple VICCs are present within the VCD field. The VCD sends an inventory command in which it sets the number of slots. The number of slots can be either 16 or 1. The slots start immediately after EOF and VCD switch to another slot by sending an EOF. If two or more VICC sends their response during one slot, the VCD detects this and remembers collision. It then switches to another slot. If there is no VICC response in one slot, the VCD will switch to another slot. The VCD can either interrupt the anticollision sequence, or continue until the last slot, before sending request to the one VICC that was able to respond without collision.

In order to avoid simultaneous transmission of both VCD and VICC, the following timing specifications are defined:

1. VICC waiting time before transmitting response after reception of an EOF from the VCD

The VICC shall wait  $t_1$  time after receiving EOF of the VCD command, before sending a response. If the VICC detects a carrier modulation during this time, it should reset its timer and wait for further time period  $t_1$ . The minimal value is 318.6  $\mu$ s, the nominal value is 320.9  $\mu$ s and the maximum is 323.3  $\mu$ s.

2. VICC modulation ignore time after reception of an EOF from the VCD

During time  $t_{mit}$ , VICCs shall ignore any received 10% modulation after detection of valid command EOF. The minimum value is 323.3  $\mu$ s+  $t_{nrt}$ .  $t_{nrt}$  represents the nominal response time of a VICC.

3. VCD waiting time before sending a subsequent request

When the VCD has received a VICC response, it shall wait  $t_2$  time before sending a subsequent request. The minimum value here is 309.2  $\mu$ s.

4. VCD waiting time before switching to the next slot during an inventory process

If the VCD starts to receive one or more VICC responses, it shall wait until the reception of response is complete, then wait for  $t_2$  and afterwards send EOF to switch to another slot. If the VCD receives no response, than it shall wait  $t_3$  before switching to the next slot. When using 100% modulation the minimum value of  $t_3$  is 323.3  $\mu$ s +  $t_{sof}$  (time for a VICC to transmit an SOF). If 10% is used, then  $t_{3_{min}}$  is 323.3  $\mu$ s +  $t_{nrt}$  (nominal response time of a VICC).

The next figure depicts a possible anticollision sequence.

### CHAPTER 3. ISO/IEC 18000-3

Figure 3.16: Description of a possible anticollision sequence in MODE1 [6]

# 3.2 ISO/IEC 18000-3 MODE2

MODE2 is not interoperable with any other MODE described in this standard. It is also not interfering with any other MODE. This system is also based on the *reader talk first* technique. The frequency of the field is  $13.56 \text{ MHz} \pm 7 \text{ kHz}$ .

## 3.2.1 Communications signal interface interrogator to tag

Interrogator commands are transmitted by Phase Jitter Modulation (PJM). PJM is a new modulation method and ISO/IEC 18000-3 is the only RFID systems standard that does not use amplitude modulation for communication.

### 3.2.1.1 Phase jitter modulation

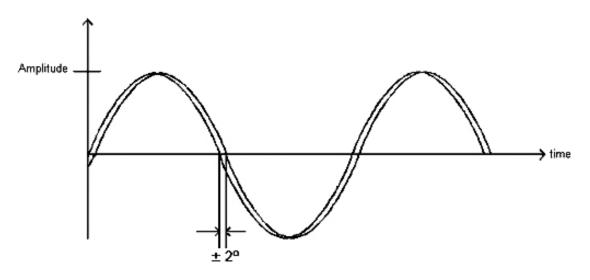

PJM can be described as variation of phase shift keying (PSK) (see section 2.4.2.3). Data transmission is done by using small phase shifts (between  $\pm$  1.0 ° and  $\pm$  2.0 °) of the interrogator field. The PJM signal can be considered as the sum of an unmodulated carrier signal and a data modulated quadrature carrier signal, which is attenuated and filtered [20]. Figure 3.17 depicts a PJM waveform.

Figure 3.17: PJM waveform[8]

PJM has many advantages over the previously applied methods. Some of the most important

are:

- There is no reduction in power transfer to tag.

- Sideband levels are independent of data rate.

- The bandwidth of the PJM signal does not exceed the original modulated data bandwidth.

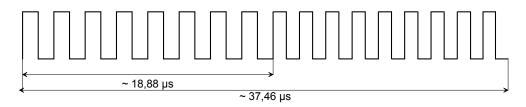

### 3.2.1.2 Data rate and data coding

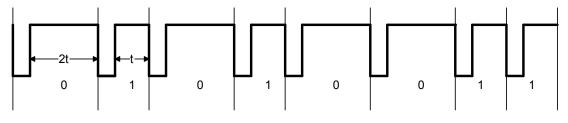

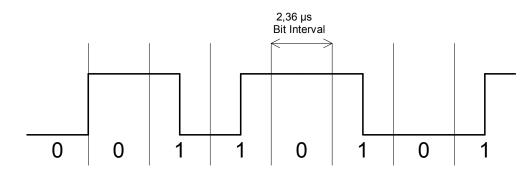

The command data rate is 423.75 kbit/s ( $f_c/32$ ). The bit interval is 2.36  $\mu$ s. The *Modified Frequency Modulation* (MFM) is used as the encoding method. MFM or Miller coding is described in section 2.4.1.4. The next figure (3.18) depicts a command MFM encoding and timing of binary 00110101.

Figure 3.18: Command MFM encoding of binary 00110101

### 3.2.1.3 Interrogator to tag frames

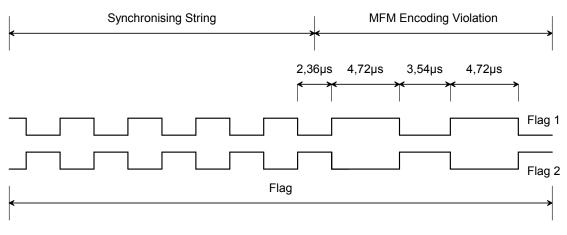

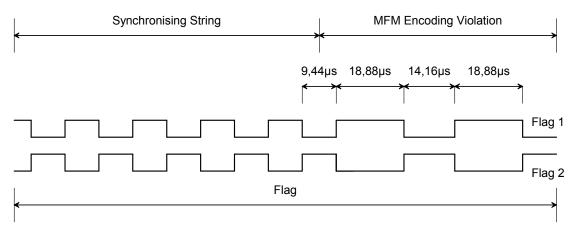

In this MODE, frames are called flags. The command flag defines the start of a command and the bit interval timings. Flags consist of three parts. The first part contains 9 bits of valid MFM data. Second comes a MFM encoding violation. The encoding violation is not present in normal data. It has three parts: a 2 bit interval ( $4.72 \mu s$ ), a 1.5 bit interval ( $3.54 \mu s$ ) and at the end, another 2 bit interval. Eventually, a bit '0' defines end of a flag. Two possible flags are depicted in figure 3.19.

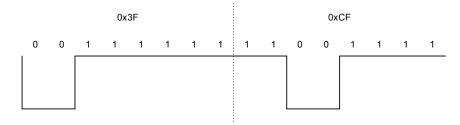

Figure 3.19: Two possible command flags (Interrogator to tag)[8]

## 3.2.2 Communications signal interface tag to interrogator

This MODE uses the same coding technique for replies and commands (MFM). There are 8 selectable modulated subcarriers which tags may use. Tags randomly select a channel to reply on. Table 3.1 shows possible channel frequencies and division ratios.

| Channel | Frequency [kHz] | Division ratio |  |

|---------|-----------------|----------------|--|

| Α       | 969             | 14             |  |

| В       | 1233            | 11             |  |

| С       | 1507            | 9              |  |

| D       | 1808            | 7.5            |  |

| E       | 2086            | 6.5            |  |

| F       | 2465            | 5.5            |  |

| G       | 2712            | 5              |  |

| Н       | 3013            | 4.5            |  |

Table 3.1: Channel frequencies and division ratios(adapted from [8])

Since the aim of this diploma thesis is to come up with a *low-cost* transceiver, the interrogator is a single channel one, meaning that tags can only reply on one channel. For this kind of interrogators, Channel G is considered to be the most suitable, although we have chosen channel B, since it is a slower one.

The modulation type is BPSK, which is also the simplest form of PSK. It uses two phases separated by  $180^{\circ}$ .

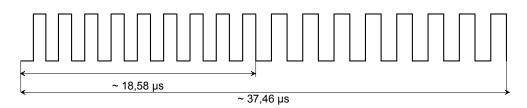

### 3.2.2.1 Data rate and data coding

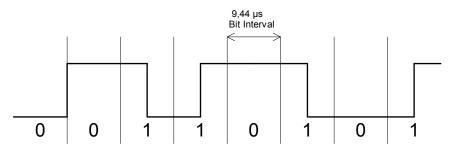

The replies are MFM encoded (see section 2.4.1.4). The only difference is that the data rate is set to 105.9375 kbit/s  $\approx$  106 kbit/s and the bit interval is now 9.44  $\mu$ s. An example of reply MFM encoding of binary string 00110101 is shown in figure 3.20

Figure 3.20: Reply MFM encoding of binary 00110101

### 3.2.2.2 Tag to interrogator frames

A flag comprises of the same three parts as an interrogator to tag flag (see section 3.2.1.3), with the exception that the period of bit interval is four times longer. Figure 3.21 depicts two possible flags.

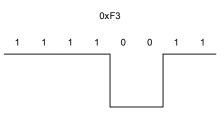

Figure 3.21: Two possible command flags (Tag to interrogator)[8]

## 3.2.3 Command format

The fields of a valid command are shown in table 3.2. All fields are transmitted following the *least significant bit first* principle.

| Code | Field                        | Bits | Comment                                                                                 |

|------|------------------------------|------|-----------------------------------------------------------------------------------------|

| F    | Flag                         | 16   | MFM violation sequence                                                                  |

| Cd   | Command                      | 16   | command field                                                                           |

| Cn   | Command number               | 16   | command number field                                                                    |

| SS   | Specific identifier          | 32   | used to communicate with an individual tag                                              |

| G    | Application group identifier | 16   | used to communicate with tags from the same appli-<br>cation group                      |

| С    | Conditional identifier       | 16   | used to communicate with tags that meet a conditional test                              |

| PPP  | Password                     | 48   | used to restrict writes to tag memory. It shall only be<br>provided if required by tag. |

| R    | Read address and length      | 16   | 8 bit address and 8 bit length fields for memory read                                   |

| W    | Write address and length     | 16   | 8 bit address and 8 bit length fields for memory write                                  |

| Ra   | Read address                 | 16   | 16 bit address field for memory read                                                    |

| Rl   | Read length                  | 16   | 16 bit length field for memory read                                                     |

| Wa   | Write address                | 16   | 16 bit address field for memory write                                                   |

| Wl   | Write length                 | 16   | 16 bit length field for memory write                                                    |

| D    | Write data                   | 16   | data to be written to the tag                                                           |

| С    | CRC                          | 16   | validation CRC                                                                          |

Table 3.2: Command fields(adapted from [8])

Depending on the type of command the interrogator sends, different fields shall be used. Table 3.3 shows the format for *group read* and *specific write* commands.

| Command type   | Start fields | Identifier fields | Address&length fields | Data | CRC |

|----------------|--------------|-------------------|-----------------------|------|-----|

| group read     | F [Cd] Cn    | G Ci              | [R] or [Ra Rl]        |      | C   |

| specific write | F [Cd] Cn    | SS [PPP]          | [W] or [Wa Wl]        | D    | С   |

Table 3.3: Valid command format for group read and specific write(adapted from [8])

## 3.2.4 Tag reply format and tag states

The reply fields are shown in table 3.4. They are also transmitted based on the *least significant bit first* principle.

| Code | Field                        | Bits | Comment                                                                         |

|------|------------------------------|------|---------------------------------------------------------------------------------|

| F    | Flag                         | 16   | MFM violation sequence                                                          |

| Н    | Hardcode                     | 16   | if tag includes hardcode then all hardcode data is sent in replies              |

| Т    | Time stamp                   | 16   | is set equal to the command number included in first valid interrogator command |

| L    | Lock pointer                 | 16   | identifier field                                                                |

| М    | Manufacturing code           | 16   | identifier field                                                                |

| SS   | Specific identifier          | 32   | identifier field                                                                |

| G    | Application group identifier | 16   | identifier field                                                                |

| Ci   | Conditional identifier       | 16   | identifier field                                                                |

| Co   | Configuration word           | 16   | identifier field                                                                |

| D    | Read data                    | 16   | data request by a valid command                                                 |

| CC   | CRC                          | 32   | validation CRC                                                                  |

### Table 3.4: Reply fields(adapted from [8])

For the MODE2 reply, the 32 bit CRC mode is used. Appendix B gives a method explanation and an example of CRC32.

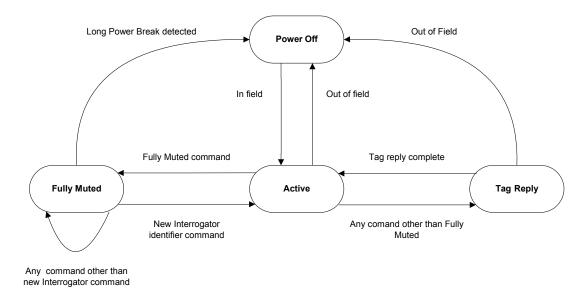

Just like VICCs, the PJM tags can also be in four different states (see section 3.22). The first state is *Power off.* Whenever a tag is in this state, it can not be activated by the interrogator. There is no field. The next state is *Active*. The tag is activated by the interrogator and it can

### CHAPTER 3. ISO/IEC 18000-3

process any command. Once the tag has received a valid interrogator command, it switches to *Tag Reply* state. After the tag reply is complete it goes back to active state. Receiving a fully muted command brings tag into *Fully Muted* state. The tag remains in this state until receiving a new valid identifier command. Any other command will be ignored.

Figure 3.22: Tag state diagram [8]

Every tag can detect an interrogator's field power breaks that last longer than 5  $\mu$ s. Breaks between 5  $\mu$ s and 10  $\mu$ s are called *short power breaks*, where after the tag will initialize and wait for a command. If the break lies between 10  $\mu$ s and 50 ms then the tag will exit fully muted state. This type of break is called *long power break*.

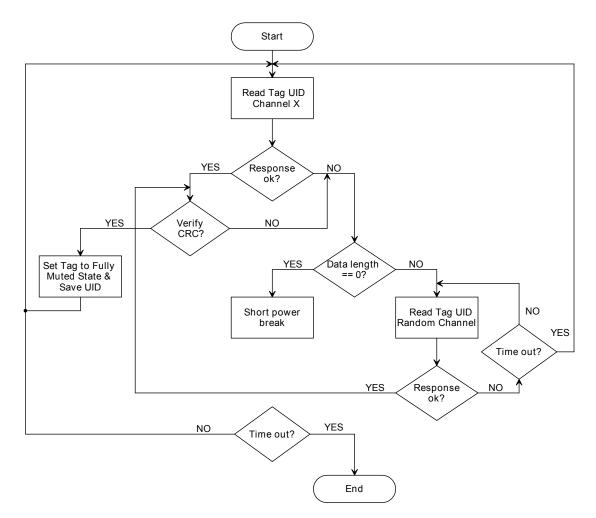

### 3.2.5 Collision management

One of the most important advantages of the ISO/IEC 18000-3 is that it allows to detect a large number of tags. To make that possible, a combination of Frequency and Time Division Multiple Access (FTDMA) is used. Tags reply to a command on a randomly selected channel. For each command, the tag will select another channel. In order to detect a large number of tags, the interrogator can temporarily mute tags, once they have been identified, so they do not reply. The next figure depicts an anticollision management sequence.

The interrogator sends a read UID command for just one channel. After receiving a tag reply, the interrogator checks CRC. If CRC is correct, the interrogator sends another command. If CRC

Figure 3.23: Anticollision management sequence in MODE2

is invalid, the data length will be checked. If there is no data (data length = 0) the interrogator makes a short power break and then sends the command again. Because of the short power break, the tags will be reinitialized, though the ones in fully muted state will not change their state. If there is data and CRC is not right, a collision has occurred. Multiply tags replied on same channel. In this case, the reader sends a read UID command for a random channel. This command will be sent for so long, until a interrogator receives a tag reply. After that, the CRC verification is run again and the same sequence starts over. The interrogator keeps repeating this sequence until all tags in field are muted and all UIDs are stored.

# 4. Coding of the coded baseband signal for ISO/IEC 18000-3

This chapter presents the practical realisation of the project. As already mentioned, the aim of this diploma thesis was to develop a contactless desktop reader supporting MODE1 and MODE2 of ISO/IEC 18000-3. In the beginning, the microcontroller of the STR71x family from ST Microelectonics was used on the reader board and Integrated Development Environment. As the decoding technique on this microcontroller did not lead to the desired results, it was replaced by a STM32Fx Cortex M3 family microcontroller. In the next sections, the coding technique for both microcontorllers will be explained.

# 4.1 MODE decision

Before a command can be sent to a tag, the modulator needs to know which MODE will be used in use. There are three possibilities: for MODE1 10% or 100% ASK and PJM for MODE2. This is done by using two output signals (PJM and ASK pins). Depending on these two signal values, the modulator detects which mode is going to be used. The next table shows pin values and their matching modulation.

| PJM pin | ASK pin | Selected Modulation |

|---------|---------|---------------------|

| low     | low     | 100% ASK            |

| low     | high    | 10% ASK             |

| high    | low     | PJM                 |

| high    | high    | RFU                 |

Table 4.1: Signals for modulation type detection

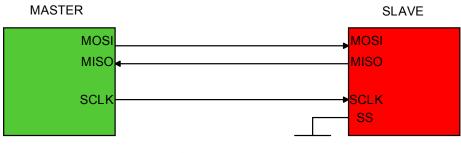

# 4.2 Serial peripheral interface

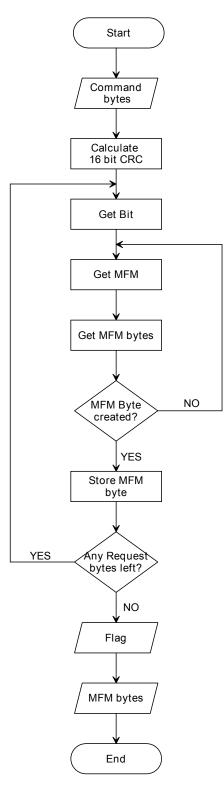

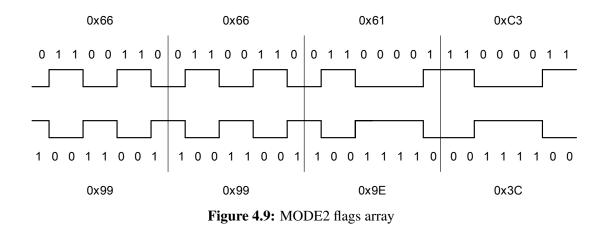

In both cases, the buffered SPI was used. Choosing this communications interface gave us the possibility of a 8- or 16-bit transfer frame format selection, two 10-word depth (16-bit) FIFOs buffer, an internal clock prescaler and up to 18 MHz speed. In this section, the basics of the buffered SPI architecture will be explained.