## A highly linear amplifier chain for a delta-sigma analogue-to-digital converter

Diploma thesis

by

### Gerhard Martin Landauer

Submitted to the Faculty of Electrical and Information Engineering in partial fulfilment of the requirements for the degree

Diplom-Ingenieur

of the Electrical Engineering diploma programme

$\operatorname{at}$

Graz University of Technology

Supervisors:

Graz University of Technology: Dr. Mario Auer

Lille University of Science and Technology: Prof. Nathalie Rolland

Graz, October 2010

### Statutory declaration

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

date and  $\operatorname{signature}$

#### Abstract

In this diploma thesis, which has been made during a stay abroad at Lille University of Science and Technology, an amplifier chain is developed. This chain is operated differentially and has a voltage gain of 40 dB, high linearity and low group delay. It serves as a building block of a high-performance delta-sigma analogue-to-digital converter, which will be used in a radar application.

The main focus of this work is the high requirements of the amplifiers concerning the low limit for signal degradations due to nonlinear distortion. Based on a survey of existing literature, possible bipolar differential amplifier topologies are described. Notably, their linearity properties and eventual distortion compensation mechanisms are analysed. The topologies, which are most adapted to the given problem, are designed with the Cadence's Virtuoso Platform software package in combination with Agilent's GoldenGate simulator. A SiGe topology of Infineon is used for this schematic design process.

Afterwards, the performance of the designed circuits is analysed. The single amplifier stages, as well as the overall amplifier chain, are regarded with the help of nominal and statistical simulations to finally determine their conformance to the desired specifications.

#### Kurzfassung

Im Rahmen dieser Diplomarbeit, die während eines Auslandsaufenthaltes an der Université des Sciences et Technologies de Lille durchgeführt wurde, wird eine Verstärkerkette entwickelt. Diese Kette wird differenziell betrieben und weist eine Spannungsverstärkung von 40 dB, hohe Linearität sowie eine niedrige Gruppenlaufzeit auf. Sie dient als einer der Grundblöcke eines hochperformanten Delta-Sigma Analog-Digital-Umsetzers, der wiederum in einem Radargerät zur Anwendung kommen wird.

Ein Hauptaugenmerk dieser Arbeit liegt auf den hohen Anforderungen an die einzelnen Verstärkerstufen sowie die gesamte Verstärkerkette hinsichtlich des niedrigen Limits für Signalverzerrungen durch nichtlineare Effekte. Basierend auf einer intensiven Literaturrecherche werden mögliche bipolare differentielle Verstärkertopologien beschrieben und insbesondere ihre Linearitätseigenschaften und eventuellen Mechanismen zur Störungskompensation beleuchtet. Die Topologien, die die gegebene Problemstellung am besten zu erfüllen geeignet sind, werden anschließend mit Cadence' Softwarepaket Virtuoso Platform in Kombination mit Aglient's GoldenGate-Simulator entworfen. Hierzu steht eine SiGe-Technologie von Infineon zur Verfügung.

Die Leistungsfähigkeit der entwickelten Schaltungen wird anschließend analysiert. Hierzu werden sowohl die einzelnen Verstärkerstufen, als auch die gesamte Verstärkerkette, nominellen und statistischen Analysen unterzogen, um letztendlich ihre Konformität zu den gegebenen Spezifikationen feststellen zu können.

#### Résumé

Ce mémoire de maîtrise était effectuée pendant un stage à l'étranger, à l'Université des Sciences et Technologies de Lille. Le sujet de ce stage était le développement d'une chaîne d'amplificateurs. Cette chaîne est opérée de manière différentielle. Elle a un gain en tension de 40 dB, une linéarité élevée et un petit temps de groupe. Elle fait partie d'un convertisseur delta-sigma, qui lui-même sera utilisé dans une application radar.

Une attention particulière de ce travail a été portée aux différents étages ainsi qu'à la chaîne complète afin d'ètudier des limites de distorsion non-linéaire. Basées sur une recherche bibliographique, différentes topologies d'amplificateurs sont analysées. Les schémas des topologies les plus adaptées au problème sont ensuite développés en utilisant le logiciel Virtuoso Platform de Cadence en combinaison avec le moteur de simulation GoldenGate de Agilent. Une technologie SiGe de Infineon est à disposition pour le design. La performance des circuits est analysée. Les étages et toute la chaîne sont regardés avec l'aide d'une étude nominale et une étude statistique, pour finalement pouvoir constater leur conformité aux spécifications. To my parents, for their moral and financial support throughout my studies.

# Contents

| 1        | Intr           | Introduction 1                                                      |  |  |  |  |  |  |

|----------|----------------|---------------------------------------------------------------------|--|--|--|--|--|--|

|          | 1.1            | Motivation and objectives of this work                              |  |  |  |  |  |  |

|          | 1.2            | $ m System$ overview $\ldots$ $\ldots$ $\ldots$ $\ldots$ $2$        |  |  |  |  |  |  |

|          | 1.3            | Desired specifications                                              |  |  |  |  |  |  |

|          |                | 1.3.1 Variables used to describe the specifications                 |  |  |  |  |  |  |

|          |                | 1.3.2 Exact definition of the specifications                        |  |  |  |  |  |  |

| <b>2</b> | Diff           | offerential amplifier topologies 7                                  |  |  |  |  |  |  |

|          | 2.1            | Advantages of differential structures                               |  |  |  |  |  |  |

|          |                | 2.1.1 Gain and common-mode rejection ratio                          |  |  |  |  |  |  |

|          |                | 2.1.2 Suppression of even-order harmonics                           |  |  |  |  |  |  |

|          | 2.2            | Fixed-gain topologies                                               |  |  |  |  |  |  |

|          |                | 2.2.1 Basic emitter-coupled pair                                    |  |  |  |  |  |  |

|          |                | 2.2.2 Emitter-coupled pair with emitter degeneration                |  |  |  |  |  |  |

|          |                | 2.2.3 Emitter-coupled pair with diode-connected load                |  |  |  |  |  |  |

|          |                | 2.2.4 Compensated cascode                                           |  |  |  |  |  |  |

|          |                | 2.2.5 Cherry-Hooper                                                 |  |  |  |  |  |  |

|          |                | 2.2.6 Miki                                                          |  |  |  |  |  |  |

|          |                | 2.2.7 Cross-coupled differential pair                               |  |  |  |  |  |  |

|          |                | 2.2.8 Multi-tanh principle                                          |  |  |  |  |  |  |

|          | 2.3            | Variable-gain topologies                                            |  |  |  |  |  |  |

|          |                | 2.3.1 Gilbert cell                                                  |  |  |  |  |  |  |

|          |                | 2.3.2 Quarter-Square Multiplier                                     |  |  |  |  |  |  |

|          | 2.4            | Equivalence of emitter degeneration topologies                      |  |  |  |  |  |  |

|          | 2.5            |                                                                     |  |  |  |  |  |  |

|          | 2.6            | Selection of the most appropriate amplifier topologies              |  |  |  |  |  |  |

|          |                | 2.6.1 Fixed-gain topologies                                         |  |  |  |  |  |  |

|          |                | 2.6.2 Variable gain topology                                        |  |  |  |  |  |  |

| 3        | $\mathbf{Sch}$ | nematic design of the amplifier stages 42                           |  |  |  |  |  |  |

|          | 3.1            | Circuit components provided by the Infineon B7HF200 SiGe technology |  |  |  |  |  |  |

|          |                | $3.1.1$ Transistors $\ldots$ $\ldots$ $43$                          |  |  |  |  |  |  |

|          |                | 3.1.2 Resistors                                                     |  |  |  |  |  |  |

|          |                | 3.1.3 Capacitors                                                    |  |  |  |  |  |  |

|          | 3.2            | Transistor biasing for low non-linear distortion                    |  |  |  |  |  |  |

|          | 3.3            | Emitter follower                                                    |  |  |  |  |  |  |

|          | 3.4            | Fixed-gain amplifiers                                               |  |  |  |  |  |  |

|          | 0              | 3.4.1 Emitter-coupled pair with diode-connected load                |  |  |  |  |  |  |

|          |                | 3.4.2 Compensated cascode                                           |  |  |  |  |  |  |

|          | 3.5            | Variable-gain amplifier                                             |  |  |  |  |  |  |

|          | 0.0            | 3.5.1         Gilbert cell         60                               |  |  |  |  |  |  |

|          |                |                                                                     |  |  |  |  |  |  |

| 4                         | Per            | ormance analysis of the amplifier stages                                                    | 66                |  |  |  |  |  |

|---------------------------|----------------|---------------------------------------------------------------------------------------------|-------------------|--|--|--|--|--|

|                           | 4.1            | Simulation methods                                                                          | . 66              |  |  |  |  |  |

|                           |                | 4.1.1 Simulation engine                                                                     | . 66              |  |  |  |  |  |

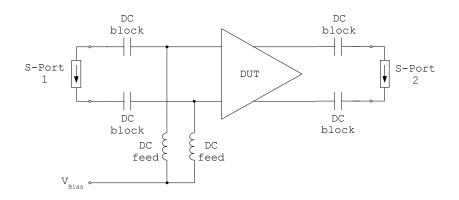

|                           |                | 4.1.2 Biasing, load impedance, input and output voltage                                     | . 67              |  |  |  |  |  |

|                           |                | 4.1.3 Simulation variables                                                                  |                   |  |  |  |  |  |

|                           | 4.2            | Fixed-gain amplifiers                                                                       |                   |  |  |  |  |  |

|                           |                | 4.2.1 Nominal simulation                                                                    |                   |  |  |  |  |  |

|                           |                | 4.2.2 Statistical simulation                                                                |                   |  |  |  |  |  |

|                           |                | 4.2.3 Performance analysis summary                                                          |                   |  |  |  |  |  |

|                           |                | 4.2.4 Specification conformity of the fixed-gain amplifier topologies and final selection . |                   |  |  |  |  |  |

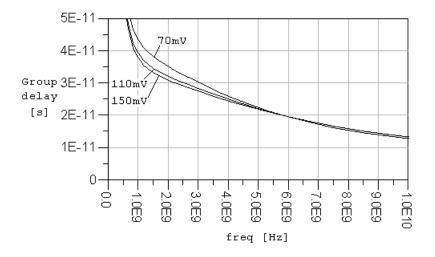

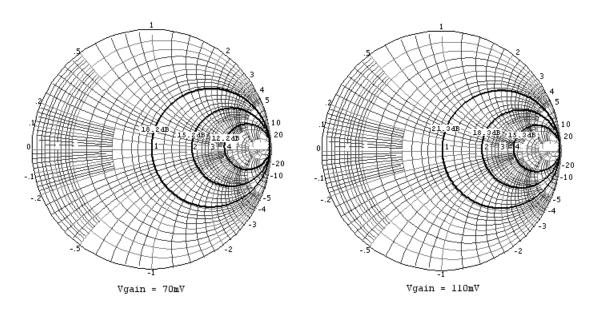

|                           | 4.3            | Variable-gain amplifier                                                                     |                   |  |  |  |  |  |

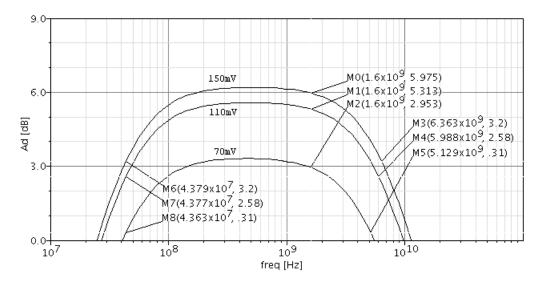

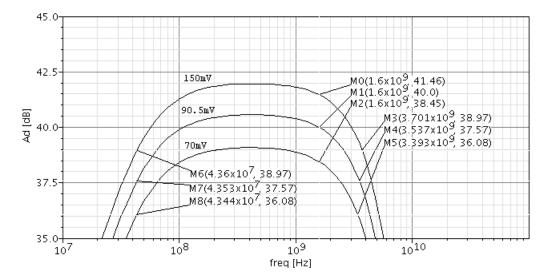

|                           | ч.0            | 4.3.1 Nominal simulation                                                                    |                   |  |  |  |  |  |

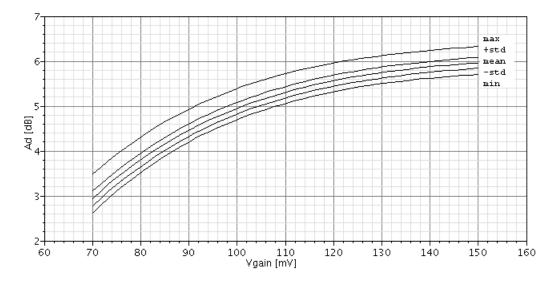

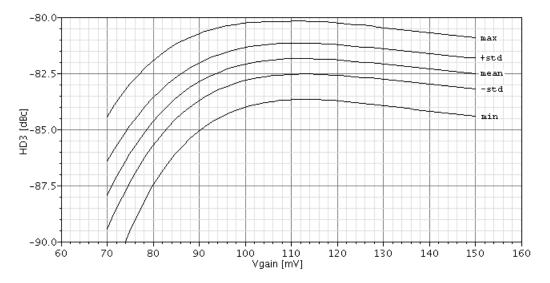

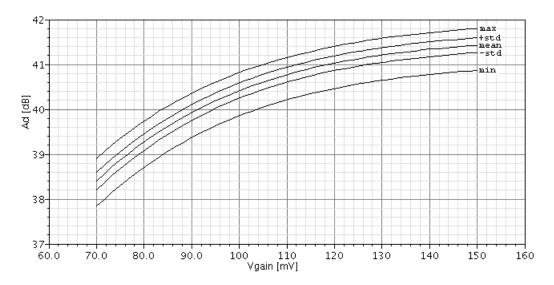

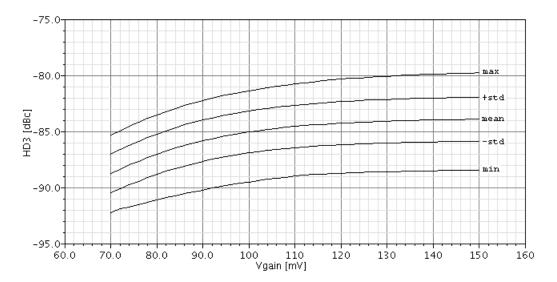

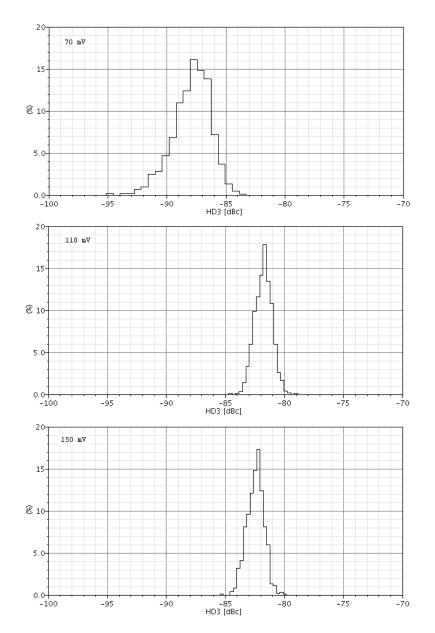

|                           |                | 4.3.2 Statistical simulation                                                                |                   |  |  |  |  |  |

|                           |                | 4.3.3 Performance analysis summary                                                          |                   |  |  |  |  |  |

|                           |                | 4.3.4 Specification conformity of the variable-gain amplifier                               |                   |  |  |  |  |  |

|                           |                | 4.5.4 Specification comornity of the variable-gain amplifier                                | . 79              |  |  |  |  |  |

| <b>5</b>                  | The            | overall amplifier chain                                                                     | 80                |  |  |  |  |  |

|                           | 5.1            | Topology of the overall amplifier chain                                                     | . 80              |  |  |  |  |  |

|                           | 5.2            | Analysis of the filter-less amplifier chain's performance                                   |                   |  |  |  |  |  |

|                           |                | 5.2.1 Nominal values                                                                        |                   |  |  |  |  |  |

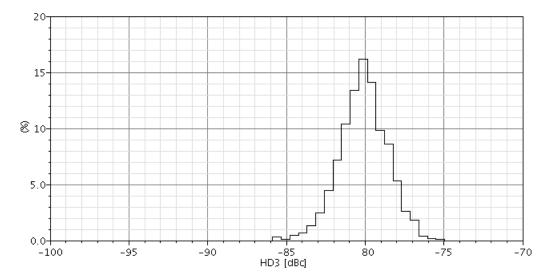

|                           |                | 5.2.2 Statistical analysis                                                                  |                   |  |  |  |  |  |

|                           |                | 5.2.3 Performance analysis summary                                                          |                   |  |  |  |  |  |

|                           |                | 5.2.4 Specification conformity of the amplifier chain                                       |                   |  |  |  |  |  |

|                           |                | · · · ·                                                                                     |                   |  |  |  |  |  |

| 6                         |                | Conclusion and extensions                                                                   |                   |  |  |  |  |  |

|                           | 6.1            | Conclusion                                                                                  |                   |  |  |  |  |  |

|                           | 6.2            | Future research steps                                                                       | . 89              |  |  |  |  |  |

| в                         | blio           | raphy                                                                                       | 90                |  |  |  |  |  |

| <b>D</b> .                | 301105         | apny .                                                                                      | 00                |  |  |  |  |  |

| $\mathbf{A}_{\mathbf{i}}$ | ppen           | lices                                                                                       | 94                |  |  |  |  |  |

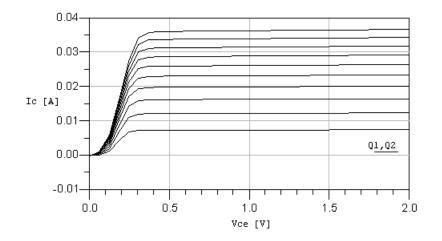

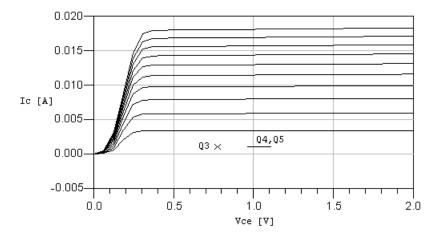

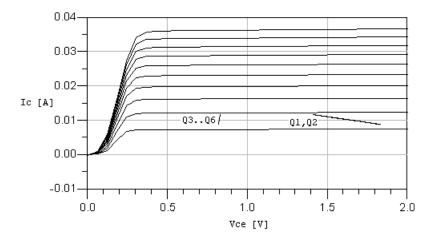

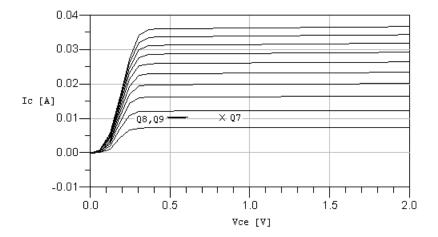

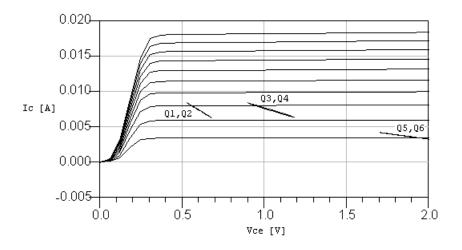

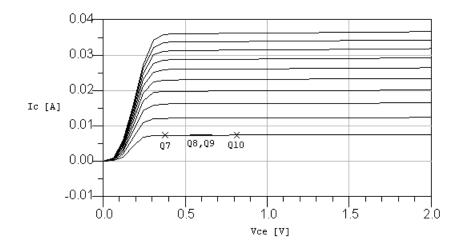

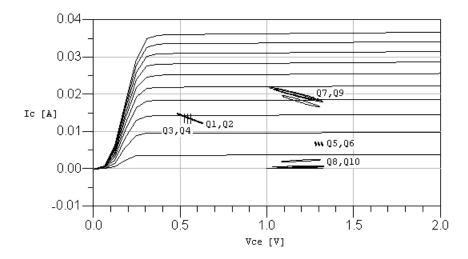

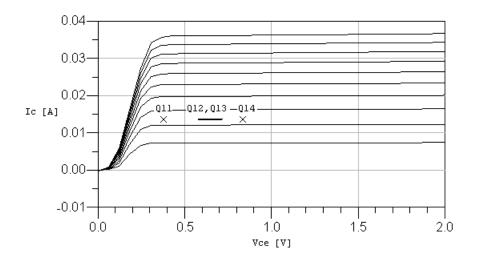

| ٨                         | Tra            | Fransistor output characteristics                                                           |                   |  |  |  |  |  |

| А                         |                | Emitter follower                                                                            | <b>94</b><br>. 95 |  |  |  |  |  |

|                           | A.1<br>A.2     | Emitter-coupled pair with diode-connected load                                              |                   |  |  |  |  |  |

|                           | A.2<br>A.3     | Compensated cascode                                                                         |                   |  |  |  |  |  |

|                           |                |                                                                                             |                   |  |  |  |  |  |

|                           | A.4            | Gilbert cell                                                                                | . 98              |  |  |  |  |  |

| в                         | $\mathbf{Sim}$ | lation results for the amplifier stages                                                     | 99                |  |  |  |  |  |

|                           |                | Fixed-gain amplifiers                                                                       | . 100             |  |  |  |  |  |

|                           |                | B.1.1 Nominal simulation results                                                            |                   |  |  |  |  |  |

|                           |                | B.1.2 Statistical variation of the third-order distortion                                   |                   |  |  |  |  |  |

|                           | B.2            | Variable-gain amplifier                                                                     |                   |  |  |  |  |  |

|                           | ~              | B.2.1 Nominal simulation results                                                            |                   |  |  |  |  |  |

|                           |                | B.2.2 Statistical variation of the third-order distortion                                   |                   |  |  |  |  |  |

|                           |                |                                                                                             |                   |  |  |  |  |  |

| $\mathbf{C}$              |                | lation results for the overall amplifier chain                                              | 105               |  |  |  |  |  |

|                           |                | Nominal simulation results                                                                  |                   |  |  |  |  |  |

|                           | C.2            | Statistical variation of the third-order distortion                                         | . 107             |  |  |  |  |  |

## Chapter 1

## Introduction

## 1.1 Motivation and objectives of this work

This thesis describes the design and simulation of a highly linear fully-differential broadband amplifier chain, which forms part of a bandpass delta-sigma analogue-to-digital converter. The work of this thesis was performed during a stay abroad at Lille University of Science and Technology, France.

The foundation for this work was laid by an internationally active semiconductor company, which develops a high-end analogue-to-digital converter based on the delta-sigma concept. The main operating figures of this data converter are an effective number of bits (ENOB) equal to 9 bit and a conversion rate of 500 MSa/s. Its conversion speed and accuracy allow the converter to be used in a next-generation radar application.

The semiconductor company contracted the IRCICA research institute of the University of Lille, to develop one part of the converter, an amplifier chain. This choice was motivated by the expertise, which IRCICA already holds in the field of high-speed data converters. An example of former research activities at the institute is a 7 bit 40 GSa/s analogue-to-digital converter, which records transient events with a length of 5 ns [1, 2]. This project gave basic ideas of how to conceive the amplifiers of this work.

The amplifier chain to be designed for the converter is operated differentially. It consists of several individual differential amplifier stages, with one stage having variable gain. The chain needs to have high gain, very low non-linear distortion and a low noise figure. Low group delay is another crucial requirement and implies high bandwidth. Not many differential amplifier topologies are capable of fulfilling all these requirements at the same time, in particular high linearity is difficult to achieve. Therefore, an analysis of topologies with low signal distortion in addition to an analysis of standard amplifier topologies is one major part of this thesis and performed in Chapter 2, whereby an emphasis is put on the circuit functionalities concerning linearity. Appropriate fixed-gain and variable-gain amplifier types, which fit most accurately to the given problem, are identified.

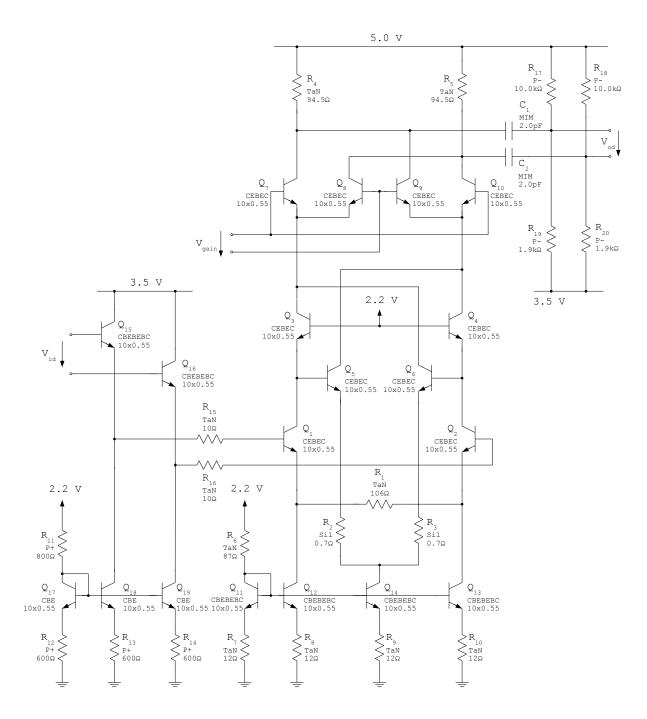

The second major part of this thesis is the schematic design and simulation of the amplifiers and the overall amplifier chain. In Chapter 3, the schematics for the amplifiers chosen in the preceding chapter are designed. The used software package is Cadence's Virtuoso Platform in combination with Agilent's GoldenGate RFIC simulation engine. The circuits are implemented using Infineon's fast B7HF200 200 GHz SiGe technology. Afterwards, the single amplifier stages and the overall amplifier chain are simulated in detail in Chapters 4 and 5. With the help of these simulations their compliance to the given specifications is finally verified.

Having designed and simulated the amplifier chain within the framework of this thesis, the proposed circuits will undergo an extensive stability analysis and will be laid out in future design steps. Then they will be integrated into the overall delta-sigma converter system and implemented as a monolithic microwave integrated circuit (MMIC).

### 1.2 System overview

Before the requirements of the amplifier chain are described in more detail, the principle of the bandpass delta-sigma analogue-to-digital converter [3] is regarded to have an overview of the system, into which the amplifier chain of this work is included.

The converter contains an analogue-to-digital converter (ADC) and a digital-to-analogue converter (DAC) as subsystems, both with 7 bit resolution. However, the overall delta-sigma ADC has an ENOB of 9 bit and not 7 bit. This resolution enhancement of 2 bit is due to the delta-sigma principle, realised by high oversampling of the signal of interest by the internal ADC and a loop structure with noise-shaping properties.

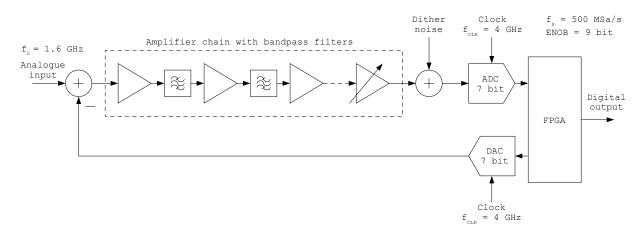

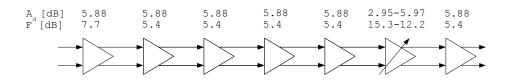

Figure 1.1: Block diagram of the delta-sigma analogue-to-digital converter. The amplifier chain is in the forward path of the converter's control loop. It consists of several fixed-gain amplifiers, a variable-gain amplifier and bandpass filters.

#### Functional principle of the overall converter system

The name bandpass sigma-delta-converter reveals that the input signal is not provided in the baseband. Its spectrum is concentrated around an intermediate frequency  $f_0$  of 1.6 GHz. This signal constellation is the result of a preceding receiver structure with downconversion of the received HF radar signal to this intermediate frequency. At the input of the converter, an error signal is built by subtracting the last conversion result from the input signal. This error signal is amplified by the highly linear chain and modified by its bandpass filters. Dither noise is added to prevent the circuit from generating idle tones, i.e. output oscillations occurring at low input signal levels. Next, the signal with 200 MHz bandwidth is sampled with a rate of 4 GSa/s by the 7 bit-ADC. Thus, the sampling rate is much higher than the signal bandwidth. Shannon's sampling theorem of the necessity of sampling the signal with a frequency of at least twice its bandwidth to avoid information loss is more than fulfilled due to this oversampling. The sampled data is reconverted to an analog signal and fed back to the subtractor circuit to build a new error signal, but is also fed to a decimation filter and a downconversion mixer, implemented on a field-programmable gate array (FPGA), and provided as a digital baseband signal at the output of the overall converter.

Normally the quantisation noise resulting from a conversion from the analogue to the digital domain has a white spectrum. The feedback loop of a delta-sigma converter with a bandpass loop filter, combined with oversampling, yields a noise power spectral density with the noise power concentrated at frequencies far away from  $f_0$ . This procedure is called noise-shaping. The signal band sustains less degradation due to noise and the signal-to-noise ratio (SNR) is increased compared to classical converters. This lower quantisation noise is reflected in a higher ENOB of the overall delta-sigma converter, gaining 2 bit of resolution in the case of the converter of this work.

#### Amplifier chain requirements

In order to be able to ideally operate the delta-sigma converter, several demands are made on the amplifier chain:

• Linearity:

The resolution enhancement of the converter is based on the high spurious-free dynamic range <sup>1</sup> (SFDR) after the nose-shaping process of the converter loop. Performance degradation due to non-linearities of the amplifier chain has to be avoided, as additional spectral components due to these non-linearities decrease the SFDR and consequently also the converter's resolution. To avoid this problem, the linearity requirements on the amplifier chain are stringent and the most challenging problem to be solved by this thesis.

• Gain:

An optimal use of the input range of the internal 7 bit-ADC requires a certain amplifier chain gain.

• Speed:

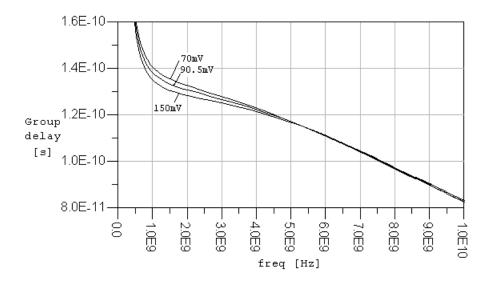

The 250 ns sampling time of the 7 bit-ADC requires a delta-sigma converter's control loop, which only introduces a short delay. Hence, the group delay of the amplifier chain, which forms part of the loop, must stay below certain limits. Thus, the group delay at the operating frequency 1.6 GHz is another major amplifier chain constraint apart from linearity and noise requirements.

Group delay is inherently linked to bandwidth. The required low group delay implies high bandwidth of the amplifiers.

• Noise:

The need for low noise is given due to the need for a low SFDR of the converter. Degrading the SFDR because of high noise levels would lead to a decrease in resolution.

• Output impedance magnitude:

The amplifiers' output impedances must have certain values to guarantee correct adaptation and operation of the bandpass filters.

$<sup>^{1}</sup>$  The spurious-free dynamic range is defined as the ratio between the ADC's input signal and the strongest signal distortion at its output, be it the noise floor or additional spectral components due to non-linear effects.

## **1.3** Desired specifications

In this section the requirements on the amplifiers and the overall amplifier chain are described according to the specification sheets obtained by the contracting semiconductor company.

#### **1.3.1** Variables used to describe the specifications

• Third-order harmonic distortion HD<sub>3</sub>

The linearity of the circuits is characterised by the third-order harmonic distortion, i.e. the ratio between the voltage magnitude  $|V_{out_3}|$  of the third harmonic at 4.8 GHz and the voltage magnitude  $|V_{out_1}|$  of the 1.6 GHz fundamental wave of the output signal.

$$HD_3 = \left| \frac{\mathbf{V}_{\text{out}_3}}{\mathbf{V}_{\text{out}_1}} \right| \tag{1.1}$$

• Voltage gain A<sub>d</sub>

Throughout this work the gain is defined as the ratio between the signals' voltage magnitudes at the output and input of an amplifier or the amplifier chain, whereby only their fundamental frequency of 1.6 GHz is considered. Due to the differential principle of operation of the amplifiers and the amplifier chain, the gain of primary interest is the differential voltage gain  $A_d$ .

$$A_d = \left| \frac{\mathbf{V}_{\text{out}_1}}{\mathbf{V}_{\text{in}_1}} \right| \tag{1.2}$$

• Group delay  $\tau_{\rm g}$

The group delay of a network is obtained by differentiating the angular frequency  $\omega$  by the phase shift  $\phi$  between the input and output of the network.

$$\tau_g = -\frac{\partial\phi}{\partial\omega} \tag{1.3}$$

• Bandwidth B

The standard 3 dB-bandwidth is used as the bandwidth measure.

• Output impedance magnitude |Z<sub>out</sub>|

As the imaginary part of the output impedance is virtually non existent, the output impedance is regarded by taking its magnitude value.

### **1.3.2** Exact definition of the specifications

The desired specifications are classified in two groups according to their priority. The first group is formed by necessary requirements, which must be complied with. Desirable requirements build the second group. It is aimed for their exact fulfilment, but small deviations from the given limits are acceptable. This prioritisation gives enough flexibility for a research project's design process, for which the linearity and speed requirements are high.

| Amplifier stage specification |                               |                 |  |  |

|-------------------------------|-------------------------------|-----------------|--|--|

| Necessary requirements        |                               |                 |  |  |

| $HD_3$                        | < -8                          | 80 dBc          |  |  |

| Desirable requirements        |                               |                 |  |  |

|                               | fixed gain                    | variable gain   |  |  |

| $A_d$                         | $6 \text{ or } 9 \mathrm{dB}$ | $3 \dots 6  dB$ |  |  |

| В                             | $\geq 10  \mathrm{GHz}$       |                 |  |  |

| $	au_g$                       | $\tau_g \leq 20 \mathrm{ps}$  |                 |  |  |

| $ Z_{out} $ 200 $\Omega$      |                               |                 |  |  |

Table 1.1: Desired specification for the amplifier stages

| Amplifier chain specification |                      |  |  |  |

|-------------------------------|----------------------|--|--|--|

| Necessary requirements        |                      |  |  |  |

| $HD_3$                        | $< -80 \mathrm{dBc}$ |  |  |  |

| $A_d$                         | $40\mathrm{dB}$      |  |  |  |

| $	au_g$                       | $< 180\mathrm{ps}$   |  |  |  |

| $\bar{F}$                     | $< 10  \mathrm{dB}$  |  |  |  |

Table 1.2: Desired specification for the overall amplifier chain

All specification values are defined for 27 °C room temperature conditions. However, values at low and high temperatures should not differ strongly from the given specification, and are also regarded in the analyses of Chapters 4 and 5 to study temperature influence on the circuit behaviour.

The amplifier chain specification is defined for a chain without added bandpass filters.

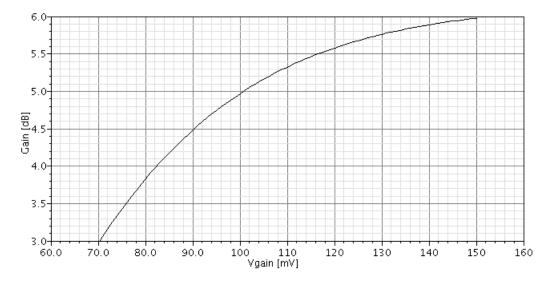

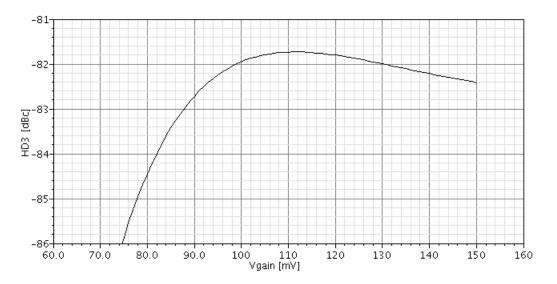

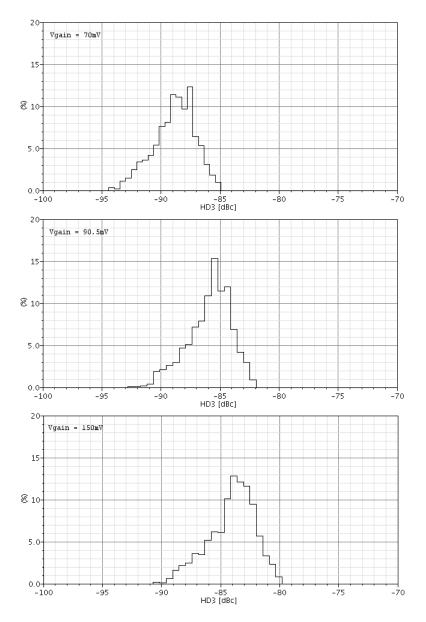

The third-order harmonic distortion values of the amplifier stages and the overall amplifier chain have to be smaller than  $-80 \,\mathrm{dBc}$  for the whole output voltage range, especially for the maximum output voltage of  $500 \,\mathrm{mV_{pp}}$ . To have some linearity margin, the maximum output voltage is chosen as  $600 \,\mathrm{mV_{pp}}$  throughout this thesis. In the case of variable gain, the HD<sub>3</sub> criterion must be met for all possible gain values. If performance degradations due to statistical variations of the circuit components are considered, the number of complying circuits has to be at least 99%.

The voltage gain of the fixed-gain amplifier stages must be equal to 6 or 9 dB, so that eventually two 9 dB-stages could be used instead of three 6 dB-stages. Small gain deviations are tolerated, since the variable gain amplifier with its gain from 3 to 6 dB can compensate for these variations to a certain extent. However, the voltage gain of the overall amplifier chain has to be exactly 40 dB, also under consideration of statistical circuit variations.

Single amplifier stages should have a group delay in the order of 20 ps and a bandwidth of at least 10 GHz in order to easily obtain a group delay smaller than 180 ps for the overall filter-less amplifier chain.

The amplifier chain's noise figure must be less than 10 dB. At least the first stages of the chain need to have a noise figure considerably lower than 10 dB, to be able to fulfil this 10 dB-condition for the overall amplifier chain. As the noise figure of an amplifier is dependent on the signal source's output impedance, the source impedances also have to be defined along with the noise figure of the overall amplifier chain has to be considered for this source impedance. The source impedances for the single amplifier stages are  $100 \Omega$  for the first stage, and  $200 \Omega$  for all following stages.

The differential output impedances of all amplifiers of the chain should be equal to  $200 \Omega$ . Due to resistor tolerances, this is only possible within the limits given by the component tolerances of the used technology.

Power consumption is only of secondary importance. Experience shows that the amplifier chain should not consume more than about 1 W of power.

## Chapter 2

## Differential amplifier topologies

One of the main tasks of this work was to find amplifiers, which are capable of fulfilling all the needed specifications, most notably the linearity limit of a third-order harmonic distortion of  $HD_3 < -80$  dBc. Before looking at the different topologies, the main advantages of differential amplifiers, common-mode rejection and suppression of even-order harmonics, are described. Then the basic emitter-coupled differential pair is analysed. The emitter-coupled pair is the basis for all the more sophisticated differential amplifiers, so importance is attached to its analysis, even if it is not usable for this work. All fixed gain topologies are regarded concerning their mechanisms of distortion correction, if existent, and the resulting linearity properties. Possible major drawbacks, which contradict their use in the amplifier chain, are indicated. The linearity analysis in analytical form is only done for the basic emitter-coupled pair, for all other topologies one relies on numerical simulations, because either closed form solutions for  $HD_3$  do not exist, or their derivation would be too elaborate. To the authors best knowledge, there exist only two possible solutions for the variable gain amplifiers, so the choice of the best variable-gain solution is more easily made than for the fixed gain amplifiers. Finally, the properties of all amplifiers are summarised and the most appropriate topologies are chosen.

## 2.1 Advantages of differential structures

The main property of differential amplifiers is that a differential input signal is amplified and accessible at the output, whereas common-mode input signals are completely suppressed in the case of an ideal circuit and have no influence on the output. Many advantages result from the capability of rejecting commonmode input signals. Reduction of common-mode input distortion, reduction of noise, the suppression of even-order harmonics and insensitivity to temperature changes make the differential topology the first choice in the case of low-distortion design. Furthermore the possibility of directly connecting the output of a stage to the input of the next stage requires no additional coupling elements between the stages of amplifier cascades. Because of all these advantages the differential amplifier is an omnipresent element in analogue circuit design. For the amplifier chain of this work only differential topologies are chosen.

#### 2.1.1 Gain and common-mode rejection ratio

The input signals, the gain and the measure common-mode rejection ratio (CMRR) are mathematically defined [4]. The CMRR is an important classification figure of the rejection of common-mode input signals of differential amplifiers and should ideally be infinitely high to strongly reduce distortions.

The differential-mode and common-mode input voltages of an amplifier are equal to

$$V_{id} = V_{in}^{+} - V_{in}^{-} \tag{2.1}$$

$$V_{ic} = \frac{V_{in}^+ + V_{in}^-}{2} \tag{2.2}$$

The differential gain is defined as the amplification factor of a differential input voltage, if the DC input level is kept constant.

$$A_d = \left. \frac{\partial V_{od}}{\partial V_{id}} \right|_{V_{ic}=0} \tag{2.4}$$

Its counterpart is the undesired but due to non-ideal components not completely avoidable commonmode gain. It can be obtained by exciting both inputs equally. The resulting change of the output voltage gives

$$A_c = \left. \frac{\partial V_{od}}{\partial V_{ic}} \right|_{V_{id}=0} \tag{2.5}$$

Now the ratio between common- and differential-mode gain is taken to calculate the CMRR as

$$CMRR = \frac{A_d}{A_c} \tag{2.6}$$

As already mentioned, a high CMRR means low-distortion behaviour of the circuit. Firstly, long leads feeding the input of the amplifier can sustain distortion. If the distortion affects both leads the same way, it can be seen as a change of the DC input level and is thus rejected. Because of the small distances between successive amplifier stages on the MMIC a strong diminution of influences of common-mode distortion can be expected. Secondly, temperature changes, acting on the transistor properties of the symmetrical structure of a differential amplifier in the same way, can be considered as a common-mode excitation of the input of the next stage. Therefore, differential structures are more robust against temperature variations. Thirdly, presumed that a single current source biases the amplifier's differential pair, the noise caused by this current source is also rejected for the same reason, notably the common-mode rejection of the next amplifier stage. Finally, one other important consequence of high CMRR is that successive stages can be connected directly without interstage coupling components. If the DC output level of one stage lies within the region of operation of the following input stage, no decoupling capacitances and no additional biasing circuits have to be used.

#### 2.1.2 Suppression of even-order harmonics

Balanced circuits like differential amplifiers suppress even-order harmonics of a sinusoidal input signal. The spectral components at even-order frequency multiples, generated by non-linearities, do therefore not exist at the output of an ideal amplifier, excited by a single-tone signal at its input. This behaviour can be explained by looking at the power series of the output signals of the two branches of a differential pair [5]. Assuming a completely symmetrical topology, the coefficients of the power series, which describe the non-linear behaviour, are identical for both branches. Only the sign of the input voltage differs, as the inputs are excited differentially.

$$V_o^+ = \frac{k_0}{2} + \frac{k_1}{2} \cdot V_{id} + \frac{k_2}{2} \cdot V_{id}^2 + \frac{k_3}{2} \cdot V_{id}^3 + \frac{k_4}{2} \cdot V_{id}^4 + \dots$$

(2.7)

$$V_o^- = \frac{k_0}{2} + \frac{k_1}{2} \cdot (-V_{id}) + \frac{k_2}{2} \cdot (-V_{id})^2 + \frac{k_3}{2} \cdot (-V_{id})^3 + \frac{k_4}{2} \cdot (-V_{id})^4 + \dots$$

(2.8)

Raising the input voltages to their respective powers and building the difference of the output voltages of the two amplifier branches leads to the following expression for the differential output voltage.

$$V_{od} = V_o^+ - V_o^- = k_1 \cdot V_{id} + k_3 \cdot V_{id}^3 + k_5 \cdot V_{id}^5 + \dots$$

(2.9)

The input voltage is assumed sinusoidal.

$$V_{id} = a \cdot \sin\left(\omega \cdot t\right) \tag{2.10}$$

If a sine function is exponentiated by an odd integer, the new function consists of a sum of sine functions with odd-order multiples of the fundamental frequency, as can be proven by calculating the Fourier series of the exponentiation result. Therefore the output contains the following frequency components.

$$V_{od} = a_1 \cdot \sin(\omega \cdot t) + a_3 \cdot \sin(3\omega \cdot t) + a_5 \cdot \sin(5\omega \cdot t) + \dots$$

(2.11)

In the ideal case the ratio between the even harmonics and the fundamental frequency is equal to zero, they do not exist. Due to mismatches of the amplifier components and resulting asymmetry of the two branches, they are not completely suppressed, but normally they are small enough to be expected below the odd-order harmonics. The HD<sub>2</sub> value is lower than the HD<sub>3</sub> value, and as both even- and odd harmonics strongly decrease with increasing order, all harmonic distortion levels from order four upwards can normally be ignored. So the only prominent single-tone distortion measure in weakly nonlinear circuits is the HD<sub>3</sub> measure.

### 2.2 Fixed-gain topologies

All the differential amplifier topologies with constant gain, which have been found during the bibliographical research and which show promise to be used for this work, are mentioned in this section. The basic emitter-coupled pair is analysed as a theoretical example. The same pair with additional emitter-degeneration resistors is still a simple, but much more linear topology. If diodes are added to the emitter-degenerated differential pair, the distortion gets even lower. Another promising architecture is the compensated cascode amplifier, which has included a correction amplifier to lower distortion. The same is the case for an amplifier topology reported by Miki. To complete the list of candidates for the amplifier chain, the fast Cherry-Hooper circuit, the cross-coupled differential pair and the multi-tanh principle are analysed.

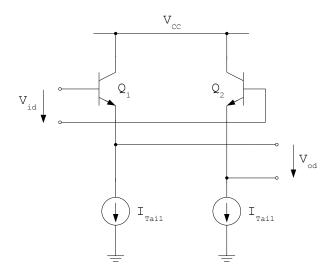

#### 2.2.1 Basic emitter-coupled pair

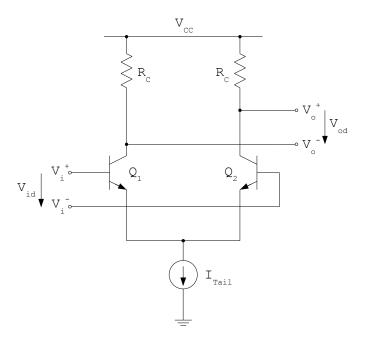

The emitter-coupled pair in its most simple configuration [6, 4] consists of two identical transistors  $Q_1$  and  $Q_2$  with their emitters connected together (Figure 2.1). The shared emitter node is biased by a current source with ideally infinitely high output impedance. The input voltages at the bases of the transistors are converted to output collector currents, which cause a voltage drop-off at the collector load resistances, and the difference between these voltages represents the output voltage of the amplifier.

#### DC transfer characteristics and gain

The collector current of a bipolar transistor, using the standard large signal relations for the forward-active region and neglecting the Early-effect, can be expressed by the diode-law equation.

$$I_c = I_S \cdot \exp\left(\frac{V_{be}}{V_T}\right) \tag{2.12}$$

Building the ratio between the two collector currents of the pair under assumption of identical transistors and therefore identical saturation currents  $I_S$  results in

$$\frac{I_{c1}}{I_{c2}} = \exp\left(\frac{V_{id}}{V_T}\right) \tag{2.13}$$

With application of Kirchhoff's current law at the emitter node we find that

$$I_{Tail} = \frac{I_{c1} + I_{c2}}{\alpha_F}$$

(2.14)

The combination of equations 2.13 and 2.14 leads to expressions for both collector currents.

$$I_{c1} = \frac{\alpha_F \cdot I_{Tail}}{1 + \exp\left(\frac{-V_{id}}{V_T}\right)}$$

(2.15)

$$I_{c2} = \frac{\alpha_F \cdot I_{Tail}}{1 + \exp\left(\frac{V_{id}}{V_T}\right)} \tag{2.16}$$

The differential output voltage is calculated by

$$V_{od} = (V_{CC} - I_{c1} \cdot R_C) - (V_{CC} - I_{c2} \cdot R_C)$$

(2.17)

By using the mathematical relation between the hyperbolic tangent and the exponential function we can finally express the DC characteristics of the emitter-coupled pair as

$$V_{od} = I_{Tail} \alpha_F R_C \tanh\left(-\frac{V_{id}}{2V_T}\right)$$

(2.18)

Thus the combination of the exponential transconductance characteristics of the two transistors leads to a hyperbolic tangent relation between the input and the output of the classical emitter-coupled pair. This is only valid for low-frequency signals, without consideration of parasitic capacitances, and under negligence of other second order effects.

The differential gain of the pair is only dependent on the biasing current, the common-base current gain and the collector resistance. At low input signals it is equal to

$$A_d = \left. \frac{\partial V_{od}}{\partial V_{id}} \right|_{V_{id} \ll} = -\frac{I_{Tail} \alpha_F R_C}{2V_T} \tag{2.19}$$

With the simple differential pair high gain is achievable at low signal levels. For instance,  $I_{Tail} = 20 \text{ mA}$ ,  $\alpha_F = 0.99$  and  $R_C = 100 \Omega$  give a differential voltage gain of  $A_d = 31.6 \text{ dB}$ .

#### Harmonic distortion

The analytic description of the DC characteristics can be used to calculate the second- and third-order harmonic distortions  $HD_2$  and  $HD_3$  by developing it into a power series.

$$V_{od} = k_1 V_{id} + k_2 V_{id}^2 + k_3 V_{id}^3 + k_4 V_{id}^4 + k_5 V_{id}^5 + \dots =$$

(2.20)

$$= I_{Tail} \alpha_F R_C \cdot \left( -\frac{V_{id}}{2V_T} + \frac{V_{id}^3}{24V_T^3} + \frac{V_{id}^5}{240V_t^5} + \dots \right)$$

(2.21)

Knowing the relations between the  $n^{th}$ -order nonlinearity coefficients  $k_n$  and the  $n^{th}$ -order harmonic distortions HD<sub>n</sub> [7], the harmonic distortions of order two and three are given as

$$HD_2 = \frac{1}{2} \left| \frac{k_2}{k_1} \right| = 0 \tag{2.22}$$

$$HD_3 = \frac{1}{4} \left| \frac{k_3}{k_1} \right| = \frac{1}{48} \frac{\hat{V}^2}{V_T^2}$$

(2.23)

There exists no distortion of order two, as can be expected for a perfectly symmetrical differential amplifier, for which only odd-order distortion has to be considered.

The distortion of order three limits the maximum input voltage. The amplifier specifications only allow a  $HD_3$  of less than  $-80 \, dBc$ . With the help of the relation derived before, the maximum input voltage can be determined as approximately  $3.60 \, mV_{pp}$ .

In the analysis of weakly nonlinear behaviour of the bipolar emitter-coupled pairs done in [7], the relation between device mismatch and second-order distortion is derived. Assuming device mismatch of the transistors, their transconductances are not equal any more. The mismatch between the load resistors is considered as negligible, so due to simplifications the second-order harmonic is only expressed as a function of the difference  $\Delta g_m$  between the transconductances. Using elaborate calculations with Volterra series, the second-order harmonic distortion becomes approximately

$$HD_2 = \frac{1}{8} \cdot \frac{\Delta g_m}{g_m} \cdot \frac{\dot{V}}{V_T}$$

(2.24)

If the transconductance mismatch  $\Delta g_m$  between the two transistors of an emitter-coupled differential pair is known, the HD<sub>2</sub> value can easily be calculated. Normally HD<sub>3</sub> is larger than HD<sub>2</sub>.

#### Common-mode rejection ratio

The CMRR is only equal to zero, if the tail current source is assumed to be ideal. If the source has a finite output resistance  $R_{Tail}$ , the emitter-coupled pair can be seen as two common-emitter amplifiers with emitter degeneration resistances of  $2R_{Tail}$ , as it is done by Gray [6]. For this approach of calculating the differential and common-mode gain of the emitter-coupled pair, the Equations 2.4 and 2.5 give

$$A_d = -g_m R_C \tag{2.25}$$

$$A_c = -\frac{g_m R_C}{1 + 2g_m R_{Tail}} \tag{2.26}$$

Building the ratio between those two gains as given by equation 2.6, yields

$$CMRR = 1 + 2g_m R_{Tail} \tag{2.27}$$

The quality of the current source is therefore the determining factor of CMRR. A standard current source should be favoured over a tail resistor, which would be a simpler but worse performing solution. A more complex current source with higher output resistance, like the cascode current source, would increase CMRR at the cost of higher circuit complexity. So a trade-off has to be made between common-mode rejection and complexity of the current source.

#### Summary

It can be concluded, that the input voltage limit of 3.6 mV is two decades too low to give the simple emitter-coupled pair a perspective to be practically used for this work. It is impossible to achieve at least moderately linear behaviour with input voltages higher than some millivolts. Under consideration of other non-linearity sources than the low-frequency input-output relation, the voltage limit is expected to be even lower. The simple differential pair shall therefore only be seen as a theoretical basis for more complex topologies. Because of its simple design, it serves only as an example to show the basic properties of differential pairs in an analytical way.

Figure 2.1: Scheme of the basic emitter-coupled pair

#### 2.2.2 Emitter-coupled pair with emitter degeneration

If emitter degeneration resistors are added to the emitter nodes of the transistors, negative feedback is established. If the base-emitter voltage  $V_{be}$  of a transistor is increased, the current through its emitter is also increased according to the transconductance of the transistor. This increase of current, however, leads to a higher voltage drop-off at the emitter degeneration resistor, which counteracts the original  $V_{be}$  voltage increase. Due to the feedback, the linearity of the circuit is substantially higher than without emitter degeneration, whereas the voltage gain decreases with rising degeneration.

This amplifier topology is not just a theoretical example like the simple emitter-coupled pair, it is by contrast used in a vast number of electronic circuits. An example for an application using an emitter-coupled pair with emitter degeneration is a 50 GHz wideband amplifier for fibre-optic communications presented by Agarwal et al. [8], who use two of these amplifiers in an amplifier chain. Perndl et al. [9] also work with this topology and presented another broadband amplifier chain based on amplifiers with emitter degeneration.

Even if this topology still does not have a great complexity, there exists no explicit solution for its low frequency input-output relation. Therefore it is impossible to develop a power series out of the DC characteristics, to analytically express the harmonic distortion for instance. Nevertheless, the voltage gain of the circuit can approximately be expressed by accepting simplifications, and the  $HD_3$  distortion can be evaluated with numerical methods.

#### DC transfer characteristics and gain

The differential input voltage between the bases of the transistors is equal to

$$V_{id} = V_{be1} + I_{c1}R_E - V_{be2} - I_{c2}R_E \tag{2.28}$$

The equations 2.15 and 2.16, which describe the collector currents of a simple emitter-coupled pair, are modified by adding the influence of the voltage drop-offs described by Equation 2.28. This gives the transcendental equations for the collector currents as

$$I_{c1} = \frac{\alpha_F \cdot I_{Tail}}{1 + \exp\left(\frac{-V_{id} - \left(I_{Tail} - \frac{2I_{c1}}{\alpha_F}\right)R_E}{V_T}\right)}$$

(2.29)

$$I_{c2} = \frac{\alpha_F \cdot I_{Tail}}{1 + \exp\left(\frac{V_{id} + \left(I_{Tail} - \frac{2I_{c2}}{\alpha_F}\right)R_E}{V_T}\right)}$$

(2.30)

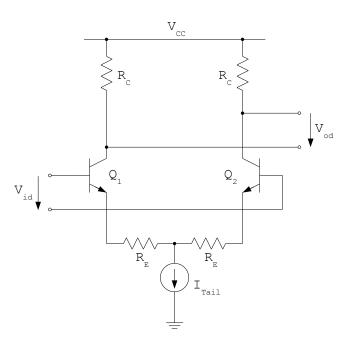

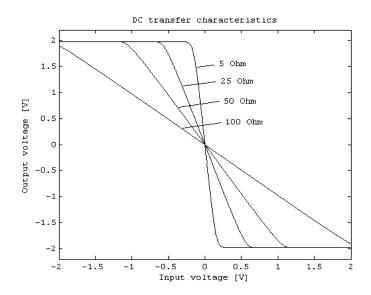

These equations are numerically solved to obtain the DC transfer characteristic of the amplifier. Realistic numerical values are chosen for the tail current source  $I_{Tail}$ , the collector resistance  $R_C$  and the common-base current gain  $\alpha_F$ . Different values are assigned to the emitter degeneration resistance to demonstrate its impact on gain and linearity range. The relations obtained between input and output are shown in Figure 2.3 for different degrees of degeneration.

The gain of the emitter-coupled pair with emitter degeneration can be estimated by taking Equation 2.28 and assuming that the base-emitter voltages  $V_{be1}$  and  $V_{be2}$  are equal [4]. With this approach the collector currents are given as

$$I_{c1} \approx \frac{I_{Tail}}{2\alpha_F} + \frac{V_{id}}{2R_E} \tag{2.31}$$

$$I_{c2} \approx \frac{I_{Tail}}{2\alpha_F} - \frac{V_{id}}{2R_E} \tag{2.32}$$

(2.33)

Using 2.17 gives the differential output voltage

$$V_{od} \approx -\frac{R_C}{R_E} \cdot V_{in} \tag{2.34}$$

The differential voltage gain in the linear region is approximately equal to the ratio between the collector and the emitter degeneration resistance.

$$A_d \approx -\frac{R_C}{R_E} \tag{2.35}$$

#### Harmonic distortion

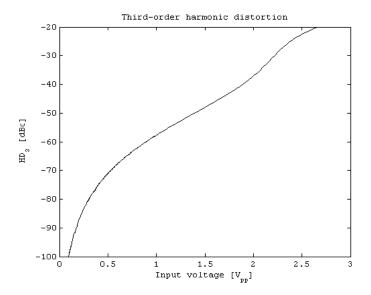

The third-order harmonic distortion is numerically calculated by applying an input sine wave to the DC transfer function of the amplifier. The resulting slightly distorted output signal is transformed into the frequency domain, where the HD<sub>3</sub> value can easily be obtained (Figure 2.4). The third-order harmonic distortion for an amplifier with a voltage gain of  $A_d = 2$  reaches the -80 dBc limit at an input voltage of about  $302 \text{ mV}_{pp}$ , which is a substantial improvement compared to the simple differential amplifier.

#### Summary

It can be concluded, that the emitter-coupled pair with emitter degeneration resistors is able to obtain high linearity without unacceptably decreasing the gain by using too high degeneration resistors. According to the numerical simulation for a voltage gain of about two, the third-order harmonic distortion at 300 mV is approximately equal to the limit of  $HD_3 = -80 \, dBc$ . However, the numerical simulation does not consider other non-linearities, which exist without doubt, so the real voltage limit is below the calculated one.

Figure 2.2: Scheme of the emitter-coupled pair with emitter degeneration

Figure 2.3: Plot of the DC input-output characteristics for an emitter-coupled pair with emitter degeneration resistances, calculated with MATLAB. The circuit is biased by a  $I_{Tail}$  current of 20 mA, the common-base current gain is chosen as  $\alpha_F = 0.99$  and the collector resistance  $R_C$  is equal to 100  $\Omega$ . To show the influence of the emitter degeneration resistance,  $R_E$  values of 5, 25, 50 and 100  $\Omega$  are applied. Increasing the emitter degeneration resistance leads to an extension of the linear region, but also to a decrease of voltage gain.

Figure 2.4: Plot of the third-order harmonic distortion HD<sub>3</sub> vs. input voltage for an emitter-coupled pair with emitter degeneration resistors, calculated with MATLAB. The emitter degeneration resistance is chosen as  $R_E = 45 \Omega$  to obtain a voltage gain of  $A_d = 2$ , otherwise the same conditions as for Figure 2.3 apply. HD<sub>3</sub> is equal to -80 dBc at an input voltage of about  $302 \text{ mV}_{pp}$ .

#### 2.2.3 Emitter-coupled pair with diode-connected load

Despite emitter degeneration, the emitter-coupled pair with emitter degeneration resistors still lacks sufficient linearity, even if the region of operation is already improved by this measure. The main reason for the non-linearity is that the base-emitter voltages  $V_{be1}$  and  $V_{be2}$  do not change by same amounts when changing the differential input voltage. Thus, the effective emitter degeneration resistances on the two sides of the differential pair are not identical. This results in a non-constant mismatch of the circuit, which varies as a function of the input voltage, and which is the principal source of distortions. This distortion can be compensated by adding diodes in series to the collector resistors [10].

#### Linearisation method

The effective emitter degeneration resistance  $\hat{R}_E$  is composed of the degeneration resistor  $R_E$ , the differential emitter resistance  $r_e$ , the input signal source resistance  $R_S$  and the base spreading resistance  $R_{BB}$ , divided by the forward current gain, as well as a bulk resistor  $R_E$  conn for the emitter connection.

$$\tilde{R}_E = R_E + R_E_{conn} + \frac{R_S + R_{BB'}}{\beta_F + 1} + r_e$$

(2.36)

By assuming an input-independent forward current gain  $\beta_F$ , the influence of the resistances located on the base side of the transistor can be assumed to be constant, and can therefore be combined with the emitter connection resistance to a constant  $R_A$ . Hence, the effective emitter degeneration resistance can be presented as

$$\tilde{R}_E = R_E + R_A + r_e \tag{2.37}$$

The differential emitter resistance  $r_e$  is dependent on the current flow through the transistor, and is therefore the only value, which is dependent of the input voltage. Its value is calculated by differentiating the diode law relationship.

$$I = I_S \cdot \exp\left(\frac{V}{V_T}\right) \tag{2.38}$$

$$\frac{dI}{dV} = \frac{1}{V_T} I_S \cdot \exp\left(\frac{V}{V_T}\right) = \frac{I}{V_T}$$

(2.39)

$$r_e = \frac{dV}{dI} = \frac{V_T}{I} \tag{2.40}$$

Applying a differential input voltage to the circuit causes a change in voltage drop-off of  $\pm \frac{V_{id}}{2}$  across the two effective emitter degeneration resistances  $\tilde{R}_{e1}$  and  $\tilde{R}_{e2}$ . This increases the current through one path by  $\Delta I$ , and decreases it by the same amount through the other path of the differential pair, yielding two different emitter currents and therefore two unequal differential emitter resistances

$$r_{e1} = \frac{V_T}{\frac{I_{Tail}}{2} + \Delta I} \tag{2.41}$$

$$r_{e2} = \frac{V_T}{\frac{I_{Tail}}{2} - \Delta I} \tag{2.42}$$

The current change  $\Delta I$  is calculated by dividing the voltage change  $V_{id}$  through the sum of the effective emitter degeneration resistors.

$$\Delta I = \frac{V_{id}}{\tilde{R}_{E1} + \tilde{R}_{E2}} \tag{2.43}$$

The sum  $\tilde{R}_{E1} + \tilde{R}_{E2}$  should ideally be constant to have a constant relation between  $\Delta I$  and  $V_{id}$ , but it is a function of  $V_{id}$  and therefore the relation between differential input voltage and differential emitter current is not constant.

$$\tilde{R}_{E1} + \tilde{R}_{E2} = 2R_E + 2R_A + r_{e1} + r_{r2} =$$

(2.44)

$$= 2R_E + 2R_A + V_T \cdot \frac{I_{Tail}}{\left(\frac{I_{Tail}}{2}\right)^2 - \left(\frac{V_{id}}{\tilde{R}_{E1} + \tilde{R}_{E2}}\right)^2}$$

(2.45)

The circuit can be linearised by adding n diodes to the collector resistances of the circuit. To obtain the same component properties for the diodes and the principal transistors  $Q_1$  and  $Q_2$  of the pair, the diodes should be built of transistor with the same dimensions as  $Q_1$  and  $Q_2$ . When diodes are added, the collector resistor value  $R_C$  has to be n times the value of the emitter degeneration resistor  $R_E$  to obtain the optimal compensation of non-linearity.

$$R_C = nR_E \tag{2.46}$$

Assuming the simplification  $\alpha_{\rm F} = 1$  and neglecting different values for the source resistance  $R_{\rm S}$ , the effective collector resistances, which include the resistors and the diodes, are equal to

$$\tilde{R}_{C1} = n\tilde{R}_{E1} = R_C + nR_A + nr_{e1} \tag{2.47}$$

$$R_{C2} = nR_{E2} = R_C + nR_A + nr_{e2} \tag{2.48}$$

The voltage gain obtained by this configuration is

$$A_d = \frac{V_{od}}{V_{id}} = \frac{\Delta I \cdot \left(\tilde{R}_{C1} + \tilde{R}_{C2}\right)}{\Delta I \cdot \left(\tilde{R}_{E1} + \tilde{R}_{E2}\right)} = n$$

(2.49)

To obtain the best linearity performance, the ratio between emitter and collector resistance needs to correspond with the number of diodes n. The voltage gain then is also equal to n. It can only have integer values, which may be a limitation in some applications.

If additional non-linearity sources did not exist and the simplifications taken had no influence, the circuit would be perfectly linear, always preconditioned that the input voltage is low enough to avoid clipping. Nevertheless, even under real conditions the circuit shows very high linearity.

Figure 2.5: Scheme of the emitter-coupled pair with diode-connected load

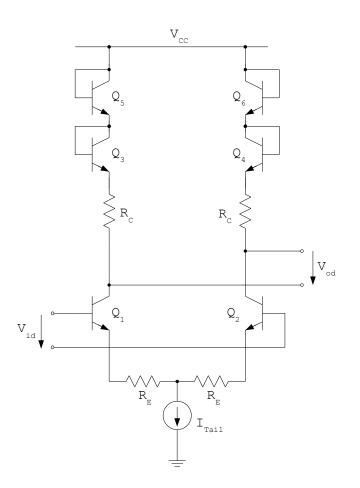

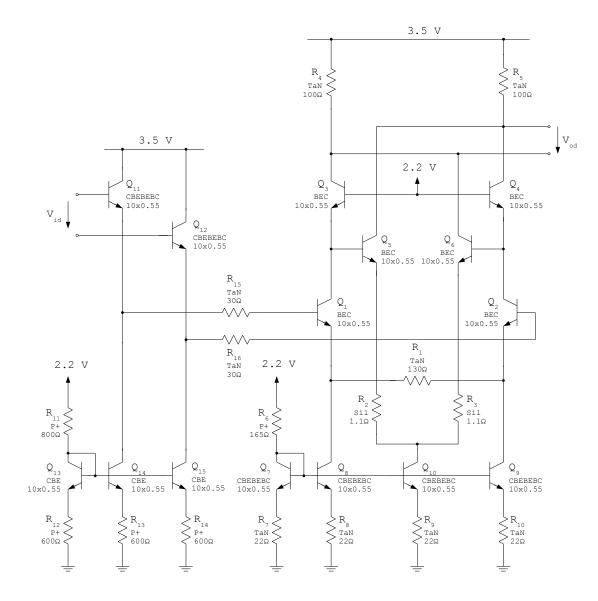

#### 2.2.4 Compensated cascode

The compensated cascode is a highly linear topology, presented by Quinn [11]. It is based on the simple cascode technology, improved by a compensation amplifier, which corrects the main non-linear effect of the cascode.

#### Cascode principle

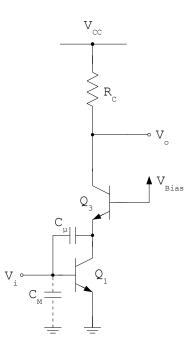

The simple cascode configuration is a common-emitter common-base amplifier, as shown in Figure 2.6. The collector of the common-emitter transistor  $Q_1$  is connected to the emitter of the common-base transistor  $Q_3$ . The base of the common-base transistor is biased at a fixed voltage level, thus the collector node of the common-emitter transistor is also fixed at a virtually constant voltage level, apart from small variations of the base-emitter voltage of  $Q_3$ . As the collector voltage of  $Q_1$  is kept constant, the Early-Effect due to base-width modulation is avoided for this transistor, which leads to a reduction of non-linearity caused by this effect [12]. The ratio between the emitter and the collector current of  $Q_1$  is nearly constant, thus the overall transconductance of the cascode amplifier is more linear, due to reduction of base-width modulation, than the transconductance of a simple common-emitter stage.

Figure 2.6: Cascode principle

Another positive effect of the cascode configuration is the increase of bandwidth. A simple commonemitter stage sustains bandwidth degradation because of the Miller effect. Seen from the input side of the common-emitter amplifier, the effect of the parasitic base-collector capacitance  $C_{\mu}$  is multiplied by a factor nearly proportional to the voltage gain A, obtaining an increased input capacitance  $C_M$ .

$$C_M = C_\mu \cdot (1 + |A|) \tag{2.50}$$

The collector of the common-emitter transistor of the cascode topology is kept at a constant level, thus the Miller capacitance is strongly reduced to  $C_M \approx 2C_{\mu}$ . The common-base transistor is biased at a constant base voltage level, a priori avoiding the Miller effect. The result of the decrease of the Miller effect is an increase of bandwidth.

#### Linearisation method

The main source of non-linearity for emitter-coupled pairs with emitter degeneration resistors, which are based on the cascode topology, is the same as for the other emitter-coupled pairs presented. The base-emitter voltages of the principal transistors  $Q_1$  and  $Q_2$  do not have the same value, if the currents flowing through them are not equal due to a differential input voltage. The undesired difference  $\Delta V_{be} =$  $\Delta V_{be1} - \Delta V_{be2}$  between the emitters of the two common-emitter transistors  $Q_1$  and  $Q_2$  also exists as a nearly identical replica  $\Delta V'_{be} = \Delta V_{be3} - \Delta V_{be4}$  between the emitters of the common-base transistors  $Q_3$ and  $Q_4$ . This replica is sensed by another emitter-coupled pair  $Q_5$ - $Q_6$  with emitter degeneration, which builds the compensation amplifier with a certain transconductance  $G_m$ . The sensed error signal  $\Delta V'_{be}$ is amplified and the error currents at the outputs of the compensation amplifier are subtracted from the inaccurate output currents of the cascode amplifier. The non-linearity caused by the systematic  $\Delta V_{be}$ error is nearly completely compensated, if an appropriate value for  $G_m$  is chosen.

The differential output current  $\Delta I_o$  can be expressed by

$$\Delta I_o = \frac{V_{id}}{2R_E} - \frac{V_{be}}{R_E} + V_{be'} \cdot G_M \tag{2.51}$$

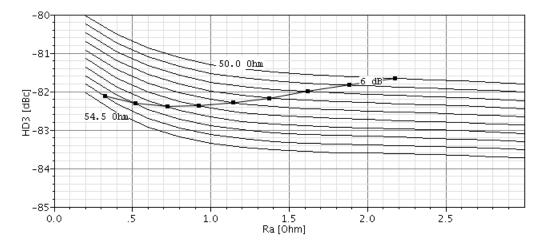

Thus, compensation is achieved, if the compensation amplifier transconductance  $G_M$  is equal to the conductance value  $R_E^{-1}$  of the emitter degeneration resistors of the principal differential pair.  $G_M$  is determined by the emitter degeneration resistors  $R_A$  of the correction amplifier.  $R_A$  is therefore the variable, which has to be optimised to obtain a maximum of linearity.

After compensation there are still several systematic error sources. Sensing  $\Delta V_{be}$ , and not  $\Delta V_{be}$  is one of them. Moreover, the compensation amplifier itself is non-linear, but as the error signal is small, its non-linearity does not have a big impact. It also has finite bandwidth, causing lower non-linearity compensation at higher frequencies.

The disadvantages of the compensated cascode are an increased number of components and therefore increased noise, the need for a biasing voltage and two current sources, as well as the need for high supply voltage as with the current sources and the cascode there are at least three transistors connected in series. Nevertheless, the advantages of this topology outweigh the problems. A high gain, determined by the emitter degeneration resistors  $R_E$ , can be achieved by at the same time staying highly linear.

Figure 2.7: Scheme of the compensated cascode

#### 2.2.5 Cherry-Hooper

This differential amplifier topology has a high gain-bandwidth product. Its functional principle, developed by Cherry and Hooper [13], is a strong impedance mismatch between successive amplifier stages, which acts as a decoupling mechanism and provides high bandwidth. Nowadays Cherry-Hooper amplifiers are widely used in high speed applications like amplifiers in fibre-optic systems. For instance, Baeyens et al. [14] proposed a 40 Gbit/s limiting amplifier chain with three Cherry-Hooper amplifiers, and Choudhury et al. [15] presented a 50 GHz bandwidth amplifier chain with four amplifiers.

A Cherry-Hooper amplifier consists of two stages, each one of them with feedback. A first transadmittance stage ( $Q_1$  and  $Q_2$ ) with optional series feedback in form of emitter degeneration resistors  $R_{E1}$ converts the differential input voltage into an output current. This stage has high input and output impedance and is terminated by a stage with low input impedance, to obtain sufficient impedance mismatch. So the transadmittance stage is followed by a transimpedance stage, built by the transistors  $Q_3$ and  $Q_4$ , which has low input and output impedance, and needs to be driven by a current source, which is the case as it is connected to the transadmittance stage. The shunt feedback of the second stage is realised by feedback-resistors  $R_F$  and the emitter followers  $Q_5$  and  $Q_6$ . Due to the low output impedance of the transimpedance stage, the load impedance of the overall Cherry-Hooper amplifier should be high. As a modification, the resistors  $R_2$  have been added by Greshishchev and Schvan [16], to increase the voltage gain of the circuit.

The DC characteristics of the amplifier, which are derived in [17] for an amplifier without emitter degeneration, show several sources of non-linearity. The voltage at the output of the transadmittance stage respective of the input of the transimpedance stage is given by

$$V_2 - V_1 \approx R_1 I_{Tail2} \cdot \tanh\left(\frac{V_2 - V_1}{2V_T}\right) + R_F I_{Tail1} \cdot \tanh\left(\frac{-V_{id}}{2V_T}\right) + V_{be6}\left(V_{id}\right) - V_{be5}\left(V_{id}\right)$$

(2.52)

The first term represents the shunt feedback of the transimpedance stage, the second term the input voltage as it would be amplified, if only the transadmittance stage itself would exist. Both terms contain the hyperbolic tangent function, which creates odd-order harmonics as it has been described for the simple emitter-coupled pair. An additional disturbance factor is the non-linear relation between the base-emitter voltages and the collector currents of the feedback emitter-followers  $Q_5$  and  $Q_6$ .

The solution for  $V_2 - V_1$  has to be found numerically. Subsequently, the overall output voltage can be calculated by a hyperbolic tangent relation.

$$V_{od} \approx (R_1 + R_2) I_{Tail2} \cdot \tanh\left(\frac{V_2 - V_1}{2V_T}\right)$$

$$(2.53)$$

The focus of the widely used Cherry-Hooper amplifier definitely lies on bandwidth, it is not optimised for linearity. For sufficient linearity additional external feedback would be necessary, which substantially lowers gain and bandwidth and counteracts the advantages of this topology.

Figure 2.8: Scheme of the Cherry-Hooper differential amplifier

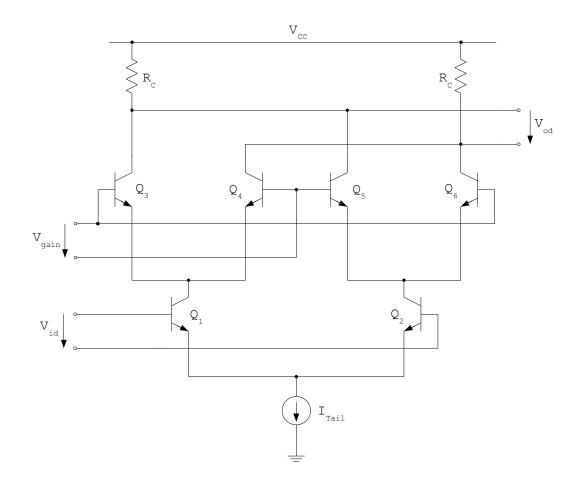

#### 2.2.6 Miki

This is another topology based on the differential pair with emitter degeneration and linearisation by correcting the  $\Delta V_{be}$  distortion. It was first presented by Miki et al., who used it as a signal buffer in a broadband analogue-to-digital converter [18].

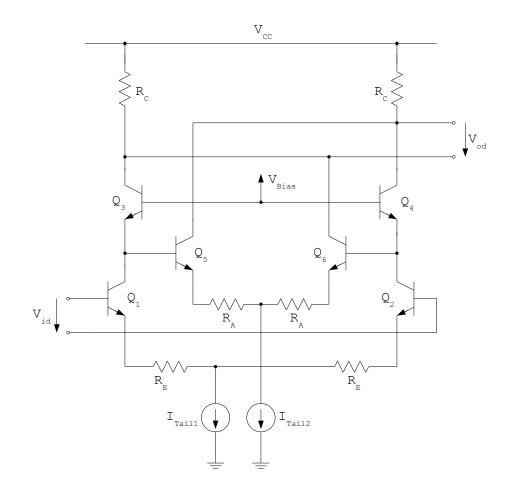

The Miki configuration consists of two differential pairs with emitter degeneration (Figure 2.9). The inner differential pair  $Q_1$ - $Q_2$  acts as the gain section of the amplifier. The second differential pair  $Q_3$ - $Q_4$  creates replicas of the collector currents of the first differential pair. These currents create approximately the same  $\Delta V_{be}$  distortions at the emitter followers  $Q_5$  and  $Q_6$ , which counteract the nonlinear behaviour of the first differential pair  $Q_1$ - $Q_2$ .

For a given configuration of  $R_{E1}$  and  $R_1$ , the outer differential pair  $Q_5$ - $Q_6$  needs an appropriate value of resistor  $R_{E2}$  to minimise distortions. The following derivation shows the functionality of the linearisation of this topology, as well as defining the ideal choice of  $R_{E2}$ .

#### Linearisation method

Using the diode-law equation and neglecting the Early-effect, the base-emitter voltages of the transistors  $Q_1$  and  $Q_2$  of the inner differential pair as functions of their collector currents are equal to

$$V_{be1} = V_T \cdot \ln\left(\frac{I_{Tail1} + \Delta I}{I_S}\right) = V_{be} + \Delta V_{be1}$$

(2.54)

$$V_{be2} = V_T \cdot \ln\left(\frac{I_{Tail1} - \Delta I}{I_S}\right) = V_{be} + \Delta V_{be2}$$

(2.55)

The current change  $\Delta I$  caused by the differential input voltage  $V_{id}$  is

$$\Delta I_1 = \frac{V_{id} - \Delta V_{be1} + \Delta V_{be2}}{2R_{E1}} \tag{2.56}$$

The differential voltage  $V_{12}$  between the collectors of  $Q_1$  and  $Q_2$  can be calculated by

$$V_{12} = -2\Delta I_1 \cdot R_C = -\frac{R_C}{R_{E1}} \cdot (V_{id} - \Delta V_{be1} + \Delta V_{be2})$$

(2.57)

Considering the unequal voltage drop-offs  $V_{be5}$  and  $V_{be6}$  at the emitter followers  $Q_5$  and  $Q_6$ , the differential output voltage is equal to

$$V_{od} = -\frac{R_C}{R_{E1}} \cdot V_{id} + \frac{R_C}{R_{E1}} \cdot \Delta V_{be1} - \Delta V_{be5} + \frac{R_C}{R_{E1}} \cdot \Delta V_{be2} - \Delta V_{be6}$$

(2.58)

Compensation is reached, when the base-emitter voltage changes of the emitter followers  $Q_5$  and  $Q_6$  exactly counteract the amplified base-emitter voltage changes of  $Q_1$  and  $Q_2$ .

$$\frac{R_C}{R_{E1}} \cdot \Delta V_{be1} = \Delta V_{be5} \tag{2.59}$$

$$\frac{R_C}{R_{E1}} \cdot \Delta V_{be2} = \Delta V_{be6} \tag{2.60}$$

The development of  $V_{be}$  into a power series

$$V_{be} = V_T \cdot \ln\left(\frac{I_{Tail} + \Delta I}{I_S}\right) = V_T \cdot \left(\ln\left(\frac{I_{Tail}}{I_S}\right) + \frac{\Delta I}{I_S} + \frac{\Delta I^2}{2I_S^2} + \frac{\Delta I^3}{3I_S^3} + \dots\right)$$

(2.61)

shows, that  $\Delta V_{\rm be}$  can be linearly approximated by

$$\Delta V_{be} \approx V_T \cdot \frac{\Delta I}{I_S} \tag{2.62}$$

Due to symmetry, only one of the Equations 2.59 and 2.60 has to be considered and can be expressed as

$$\frac{R_C}{R_{E1}} \cdot V_T \cdot \frac{\Delta I_1}{I_S} = V_T \cdot \frac{\Delta I_2}{I_S} \tag{2.63}$$

The current change  $\Delta I_2$  in the outer differential pair has to be greater by the factor  $\frac{R_C}{R_{E1}}$  than the current change  $\Delta I_1$  in the inner pair. This factor is equal to the differential voltage gain  $A_d$ . As the same input voltage is applied to the outer and the inner pair, this can be reached by choosing the degeneration resistor  $R_{E2}$  as

$$R_{E2} = \frac{R_{E1}}{R_C} \cdot R_{E1} = \frac{1}{A_d} \cdot R_{E1} \tag{2.64}$$

Applying this value for  $R_{E2}$  leads to the compensation of non-linearity.

In summary, the amplifier topology presented by Miki et al. has high linearity due to the compensation and a gain, which can be chosen by the resistances  $R_{E1}$  and  $R_{C}$ .

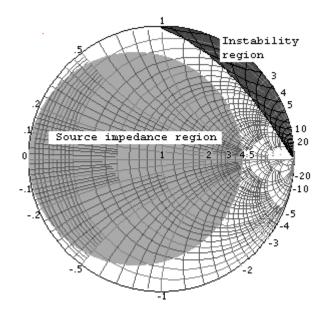

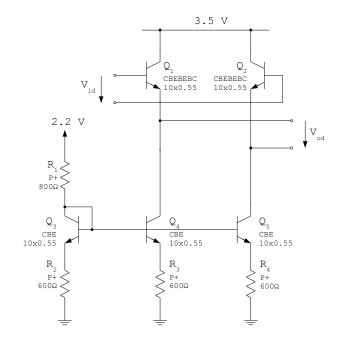

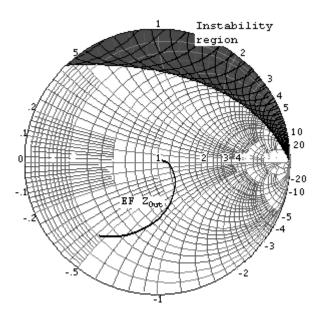

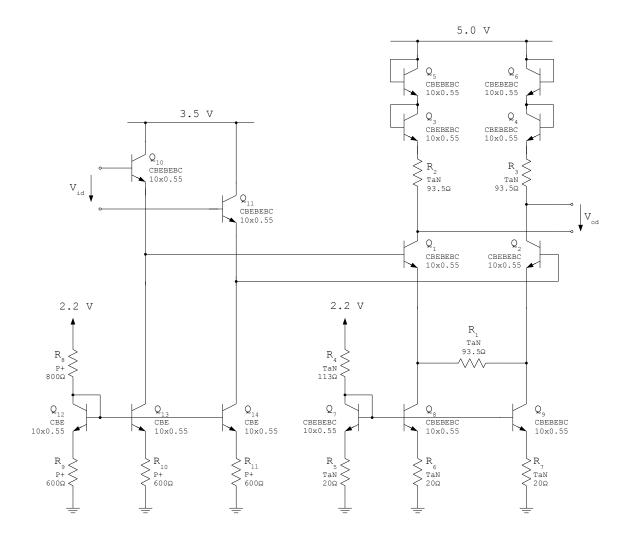

#### **Output** resistance

Despite these advantages, this topology has a major drawback. Its output is formed by an emitter follower, thus it has low impedance. The output impedance cannot freely be defined according to the given specifications, meaning it cannot be adapted to the following filter stage. In addition, an emitter follower at the output of an amplifier stage leads to stability problems, if the input buffer of the succeeding amplifier stage is also built by an emitter follower.

Figure 2.9: Scheme of the Miki topology

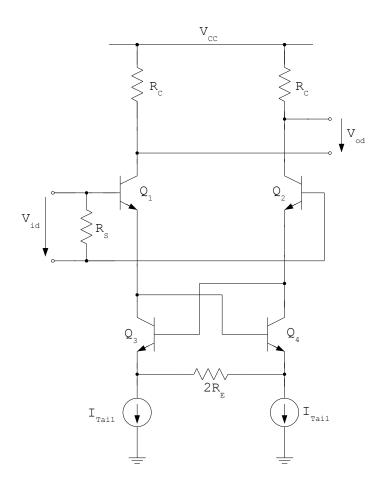

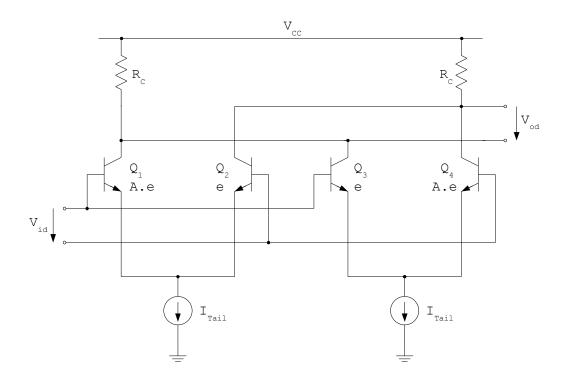

#### 2.2.7 Cross-coupled differential pair

Figure 2.10 depicts a cross coupled differential pair. It is built of four transistors. The principal transistors  $Q_1$  and  $Q_2$  of the differential pair amplify the input signal. The correction transistors  $Q_3$  and  $Q_4$  have their bases cross-connected to the emitters of the principal transistors of the respective other path of the pair. The emitter degeneration resistor defines the voltage gain of the circuit. The first publication of this topology, also referred to as differential quartet, has been made by Pookaiyaudom et al. [19].

Like the emitter-coupled pair with diode-connected load or the compensated cascode, this circuit compensates the principal non-linearity of differential pairs, i.e. the non-linear relation between the collector current  $I_c$  and the base-emitter voltage  $V_{be}$  of the transistors. In the following description of the circuit's functionality, a common-base current gain  $\alpha_F = 1$  is assumed, therefore no base currents have to be considered. However, this simplification is not needed if a base current compensation circuit is applied to the cross-coupled differential pair, as it is also proposed by Pookaiyaudom as an optional improvement of the topology.

#### Linearisation method

In the first path of the differential amplifier, the same current  $I_{Tail} + \Delta I$  flows through the transistors  $Q_1$  and  $Q_3$ , assuming that, as mentioned above, the base currents are negligible. The current through the second path, and therefore through transistors  $Q_2$  and  $Q_4$ , is equal to  $I_{Tail} - \Delta I$ . The base-emitter voltages of transistors  $Q_1$  and  $Q_3$  are of the same value  $V_{be1}$ , when second order effects like base-width modulation are neglected and only a dependency on the collector current is presumed. The base-emitter voltages of the other two transistors are equal to  $V_{be2}$ . Due to cross-coupling, the voltage sums across the series-connections  $Q_1$ - $Q_4$  and  $Q_2$ - $Q_3$  are the same. Thus, the voltage at the emitter degeneration resistor is an exact replica of the differential input voltage, leading to a constant relation between the current through the resistor and the input voltage, and compensation is reached.

If base spreading resistances as well as emitter bulk and contact resistances are small, the transconductance  $G_M$  of the circuit is approximately defined by the reciprocal value of the resistance  $2R_E$  and is virtually constant over a large range of operation. The voltage gain of the overall circuit is

$$V_d = G_M \cdot 2R_C = \frac{R_C}{R_E} \tag{2.65}$$

#### **Stability issues**

The circuit has a major disadvantage. It uses positive feedback and it has a negative input resistance, which means that it is only conditionally stable. To stabilise the circuit, at the input a small positive resistor  $R_S$  has to be put in parallel to the large negative input resistance to obtain an overall resistance nearly equal to the additional small positive resistor, which stabilises the circuit. The absolute value of the negative input resistance decreases with rising frequency, so a capacitor is needed in parallel to the small resistor, to assure stabilisation over the whole frequency range. This stabilisation leads to a undesired low input impedance of the circuit.

Because of the stability concerns and the resulting low input impedance, this approach was not pursued further.

Figure 2.10: Scheme of the cross-coupled differential pair

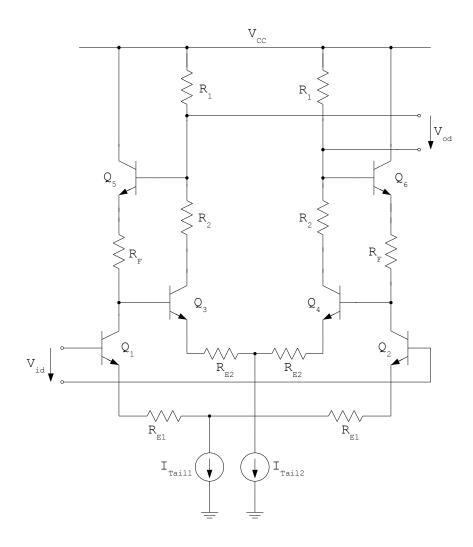

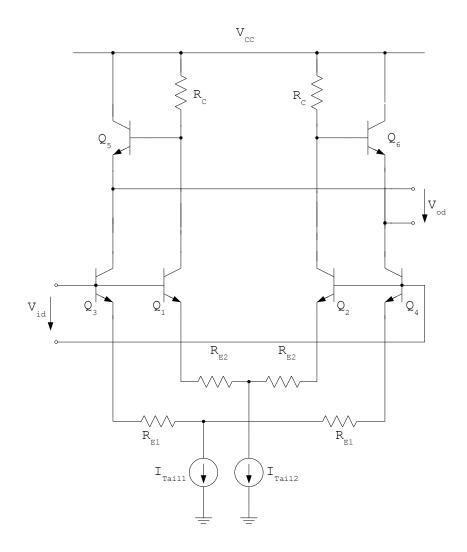

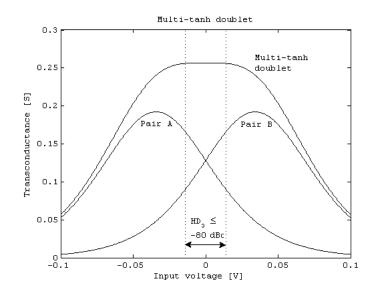

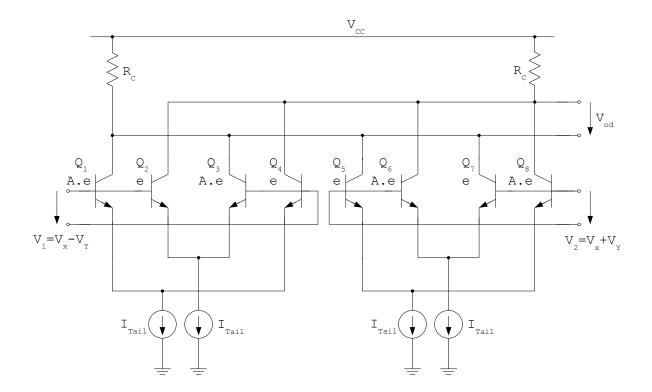

#### 2.2.8 Multi-tanh principle

Multi-tanh cells [20] are groups of emitter-coupled differential pairs with their inputs and outputs connected in parallel. The individual hyperbolic tangent DC characteristics are separated along the input voltage range and added together. The sum of the individual characteristics builds a more linear overall circuit. Multi-tanh cells of order n consist of n differential pairs with n tanh-functions, all with different offsets. Each of the differential pairs is fed by an individual biasing current stemming from one of the n tail current sources.

The overall output current is obtained by summing the individual characteristics.

$$\Delta I_o = \sum_{j=1}^n I_j \cdot \tanh\left(\frac{V_{id} - V_{off_j}}{2V_T}\right)$$

(2.66)

Differentiation yields the transconductance G<sub>m</sub> of the overall circuit.

$$G_m = \sum_{j=1}^n \frac{I_j}{2V_T} \cdot \operatorname{sech}^2\left(\frac{V_{id} - V_{off_j}}{2V_T}\right)$$

(2.67)

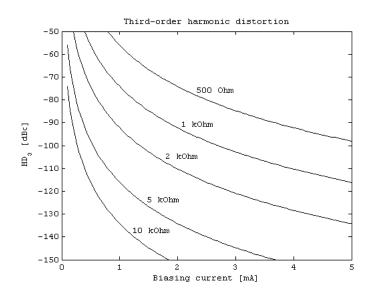

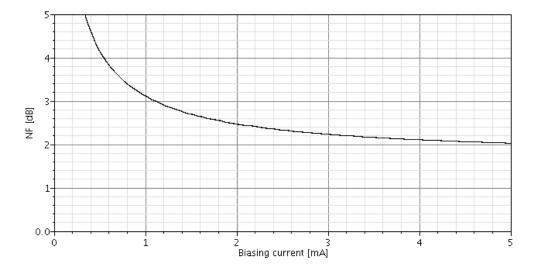

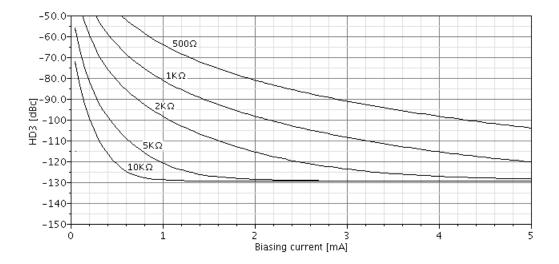

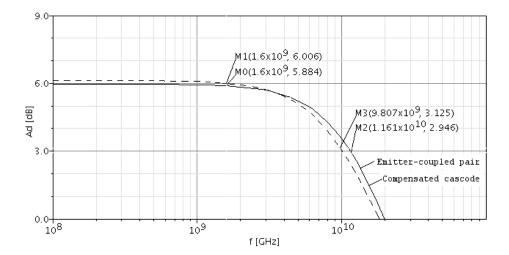

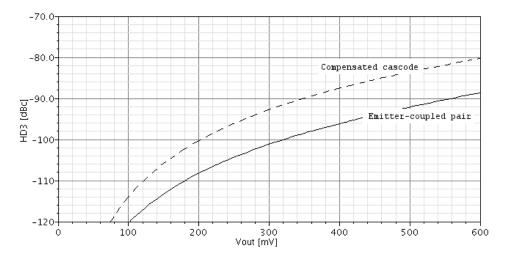

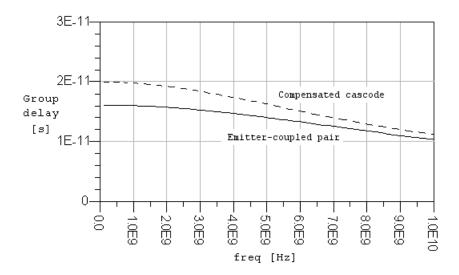

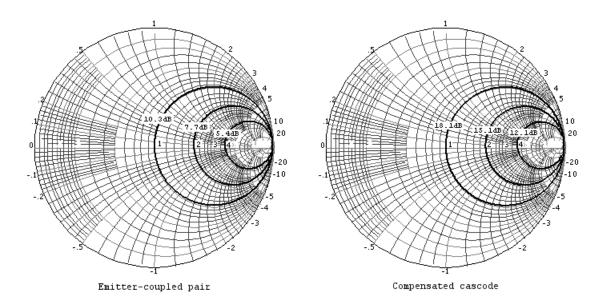

There are several ways of creating the offset of the tanh function. All of them are based on unbalancing the differential pairs. For cells with low order n the most simple method is the one of using unequal emitter areas of the two transistors of a pair. The emitter-area ratios and biasing currents of the pairs of the several stages of a multi-tanh cell have to be optimised to obtain a maximum of linearity. Offset voltages can also be introduced by connecting the bases of the different transistors by resistors. The resistors are also connected to current-sources, which cause the offset-voltage drop-offs across them. The emitter-area and offset-resistor methods can also be combined, which is useful for higher-order multi-tanh cells, which would otherwise need high emitter-area ratios to obtain the wanted shifts of the tanh-characteristics. To make the circuits more robust against emitter-area mismatches, slightly deviant tail currents or varying ohmic resistances at the accesses to the nodes of the transistors, emitter degeneration resistors can be added to the differential pairs.