# Design of a Bandwidth Calibration Unit for a PLL

Alexander Wolf

Submitted as thesis to attain the academic degree "Dipl.-Ing." at the

Graz University of Technology

# Institute for Electronics

Supervisor: Dipl.-Ing. Dr. techn. Mario Auer

Graz, October 2010

# Abstract

The bandwidth of a phase locked loop (PLL) influences its characteristics greatly, e.g. the phase noise performance or the maximum possible data rate for a modulator. The open loop gain is an important factor which determines the bandwidth, and therefore also the small signal gain of the voltage controlled oscillator (VCO), which can vary greatly over different operating points. To guarantee the fulfillment of all specifications, parts of the circuit have to be overdesigned, which wastes chip area and power. This diploma thesis presents a bandwidth calibration concept based on a time to digital converter (TDC), which allows the bandwidth to stabilize over different conditions, and therefore the amount of overdesign can be reduced. The functionality of the concept is shown with a transient simulation, and a short introduction to the topic time-to-digital conversion is given.

# Kurzfassung

Die Bandbreite einer Phasenregelschleife beeinflusst ihre Eigenschaften stark, z.B. das Phasenrauschen, oder die maximal mögliche Datenrate bei einem Modulator. Die Schleifenverstärkung der offenen Schleife hat einen großen Einfluss auf die Bandbreite, und deshalb auch die Kleinsignalverstärkung des spannungsgesteuerten Oszillators, welche stark über verschiedene Betriebspunkte variiert. Um die Erfüllung aller Spezifikationen garantieren zu können, müssen Teile der Schaltung überdimensioniert werden. Dies bedeutet einen erhöhten Verbrauch an Fläche und Leistung. Diese Diplomarbeit stellt ein, auf einem Zeitquantisierer basierendes, Konzept vor, mit dessen Hilfe die Bandbreite über die verschiedenen Konditionen stabilisiert werden kann, und somit verringert sich der notwendige Grad an Überdimensionierung. Die Funktionalität wird in einer Transienten-Simulation demonstriert, und es wird eine kurze Einleitung in die Thematik der Zeitquantisierung gegeben.

# Acknowledgements

I would like to thank my supervisor Dipl.-Ing. Dr. techn. Mario Auer for his kind help and motivation, and for being the mouthpiece towards the Graz University of Technology. I also want to thank him very much for his help regarding the text itself.

I also would like to express my appreciation especially to my external supervisor Dipl.-Ing. Martin Flatscher at the Infineon Technologies Austria AG Design Center Graz, for the uncountable hours he spent, giving me more insight into the fascinating world of micro electronics, for his patience, his questions and remarks which lead to a better end result, and also for his guidance.

I also want to thank Infineon Technologies Austria AG which made this diploma thesis possible, and all the great and kind people which work there, who have always made me felt very welcome.

# Contents

| 1 | Introduction 1          |                               |                                     |    |  |  |  |  |

|---|-------------------------|-------------------------------|-------------------------------------|----|--|--|--|--|

|   | 1.1                     | Aim of                        | f this thesis                       | 1  |  |  |  |  |

|   | 1.2                     |                               | ation                               | 2  |  |  |  |  |

|   | 1.3                     | Conce                         | ept based on TDC                    | 4  |  |  |  |  |

| 2 | Phase-locked-Loop (PLL) |                               |                                     |    |  |  |  |  |

|   | 2.1                     |                               | of use                              | 8  |  |  |  |  |

|   | 2.2                     | Archite                       | ecture                              | 9  |  |  |  |  |

|   | 2.3                     |                               | onents                              | 9  |  |  |  |  |

|   |                         | 2.3.1                         | Voltage Controlled Oscillator (VCO) | 9  |  |  |  |  |

|   |                         | 2.3.2                         | Phase Detector                      | 12 |  |  |  |  |

|   |                         | 2.3.3                         | Loop Filter                         | 19 |  |  |  |  |

|   |                         | 2.3.4                         | Feedback Divider                    | 26 |  |  |  |  |

|   | 2.4                     | Opera                         | tion                                | 28 |  |  |  |  |

|   | 2.5                     | Model                         |                                     | 30 |  |  |  |  |

|   |                         | 2.5.1                         | Phase Model                         | 30 |  |  |  |  |

|   |                         | 2.5.2                         | Voltage Model                       | 35 |  |  |  |  |

|   |                         | 2.5.3                         |                                     | 36 |  |  |  |  |

| _ |                         |                               |                                     |    |  |  |  |  |

| 3 |                         | Fime-to-digital Conversion 39 |                                     |    |  |  |  |  |

|   | 3.1                     |                               | Al Applications                     | 39 |  |  |  |  |

|   | 3.2                     |                               | ods                                 | 39 |  |  |  |  |

|   |                         | 3.2.1                         | Analog Time Stretching              | 39 |  |  |  |  |

|   |                         | 3.2.2                         | Time to Voltage Conversion          | 40 |  |  |  |  |

|   |                         | 3.2.3                         | Tapped Delay Line                   | 40 |  |  |  |  |

|   |                         | 3.2.4                         | Pseudo-Differential Delay Line      | 41 |  |  |  |  |

|   |                         | 3.2.5                         | Vernier Delay Line                  | 42 |  |  |  |  |

|   |                         | 3.2.6                         | Vernier Oscillators                 | 43 |  |  |  |  |

|   |                         | 3.2.7                         | Pulse Shrinking                     | 43 |  |  |  |  |

|   |                         | 3.2.8                         | Ring Oscillator                     | 44 |  |  |  |  |

|   | 3.3                     | Impler                        | mentation                           | 44 |  |  |  |  |

|   |                         | 3.3.1                         | Interpolator                        | 45 |  |  |  |  |

|   |                         | 3.3.2                         | Coarse Counters                     | 52 |  |  |  |  |

|   |                         | 3.3.3                         | Output Calculation                  | 58 |  |  |  |  |

|   | 3.4                     | Simula                        | ation                               | 62 |  |  |  |  |

| 4 | Ban          | dwidth         | Calibration of a Phase Locked Loop (PLL)         | 64  |  |  |

|---|--------------|----------------|--------------------------------------------------|-----|--|--|

|   | 4.1          | Princip        | ple                                              | 64  |  |  |

|   |              | 4.1.1          | TDC as Observer                                  | 66  |  |  |

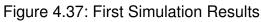

|   |              | 4.1.2          | Stimulus Generation                              | 68  |  |  |

|   |              | 4.1.3          | Procedure                                        | 78  |  |  |

|   |              | 4.1.4          | Measurand Approximation                          | 85  |  |  |

|   | 4.2          | Implementation |                                                  |     |  |  |

|   |              | 4.2.1          | System Overview                                  | 91  |  |  |

|   |              | 4.2.2          | TDC Converter                                    | 91  |  |  |

|   |              | 4.2.3          | DC Cancelling                                    | 92  |  |  |

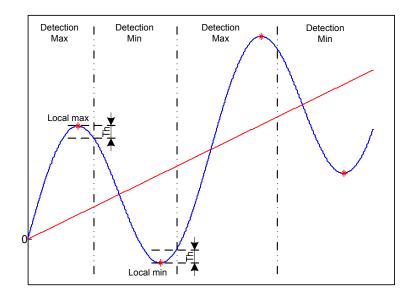

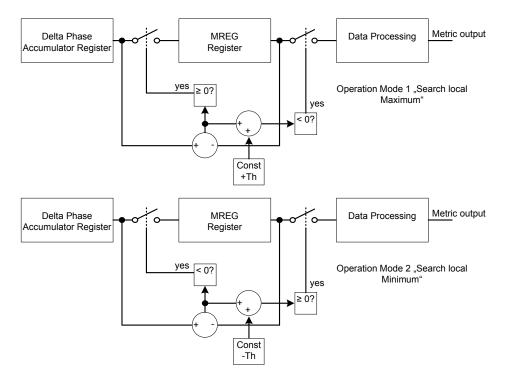

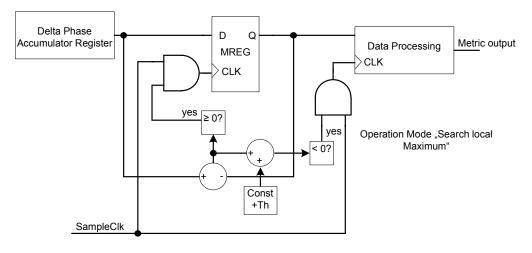

|   |              | 4.2.4          | Sample Point in Time Detector                    | 94  |  |  |

|   |              | 4.2.5          | Phase Deviation Processing                       | 95  |  |  |

|   | 4.3          | Other          | Measurement Techniques                           | 100 |  |  |

|   |              | 4.3.1          | Bandwidth Measurement based on Crossover Time    | 100 |  |  |

|   |              | 4.3.2          | Bandwidth Measurement based on Natural Frequency | 100 |  |  |

|   |              | 4.3.3          | Phase Transfer Function Measurement              | 100 |  |  |

|   |              | 4.3.4          | Jitter Transfer Function Measurement             | 101 |  |  |

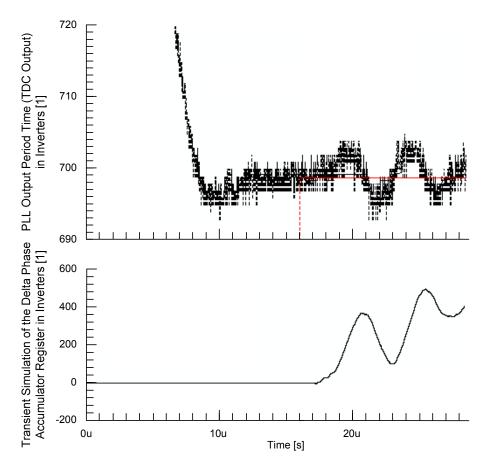

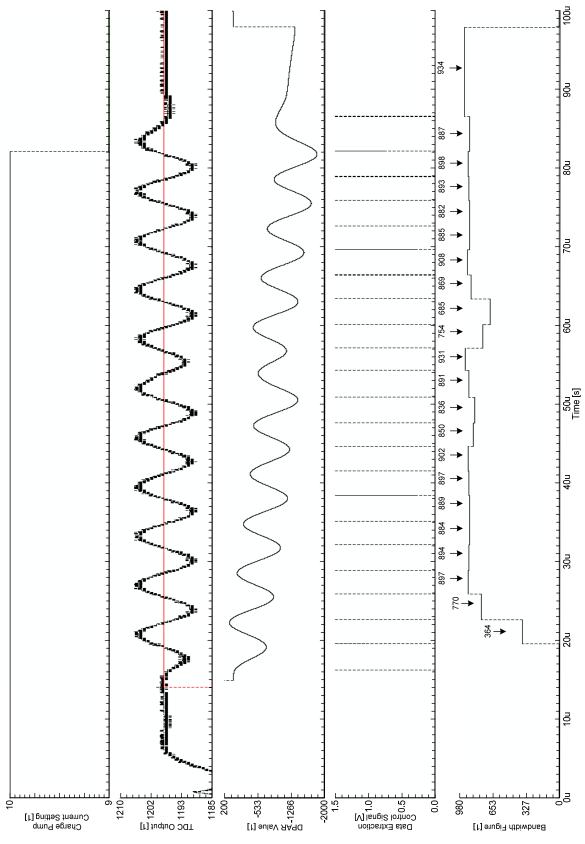

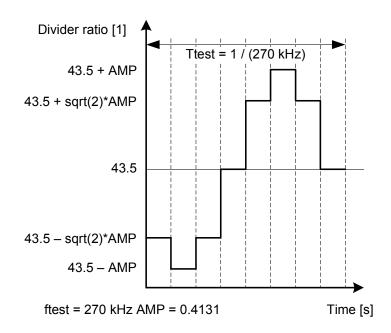

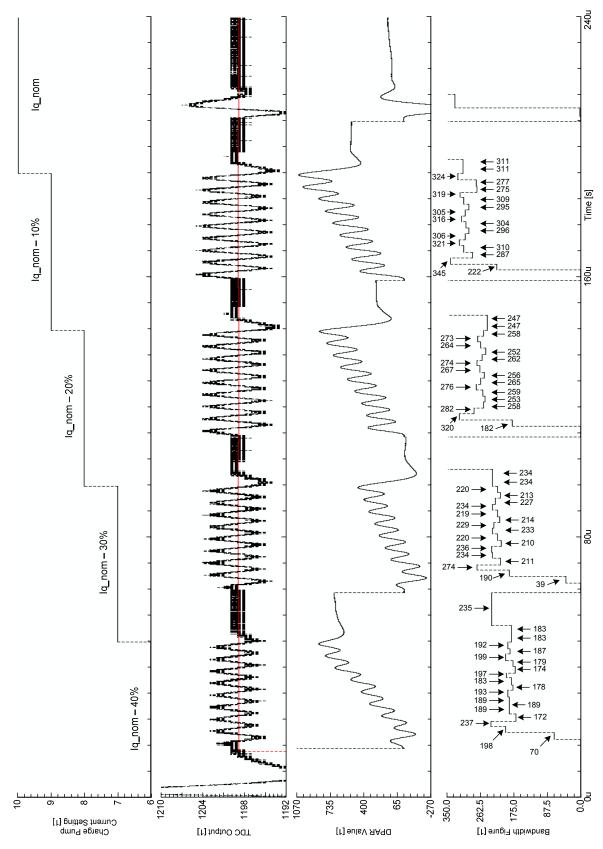

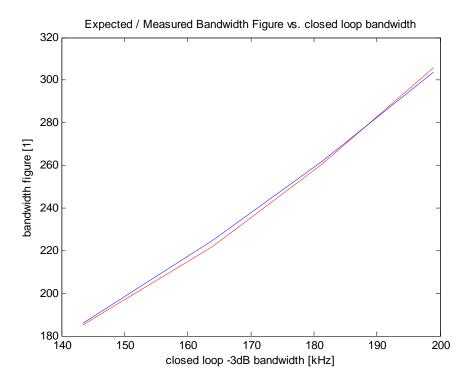

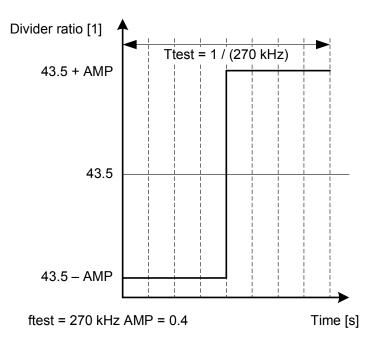

|   | 4.4          | Result         | ts                                               | 102 |  |  |

| 5 | o Conclusion |                |                                                  |     |  |  |

# **1** Introduction

## 1.1 Aim of this thesis

- The aim of this thesis is to find a concept for the measurement of the PLL closed-loop bandwidth, which then, if necessary, allows a calibration of the bandwidth. If the bandwidth is stabilized, then chip area and power dissipation will be saved. The final concept introduced in this thesis is able to determine the absolute value of the closed-loop transfer function at different frequencies, and therefore delivers the bandwidth. Furthermore, if the bandwidth calibration is only needed, then the *test* frequency can be fixed, simplifying the concept even more. Then the concept delivers a value which is proportional to the bandwidth.

- The concept found in this thesis is based on a time-to-digital converter. This

allows the implementation of two additional features. The first feature is

the ring oscillator in the TDC core, which can be used as a second on-chip

frequency source, enabling the transceiver to receive its own transmitted

data. This loopback functionality allows additional tests to be carried out.

The second feature is a time-to-digital converter at the PLL output, which

can be used to measure the output period time jitter.

- This thesis also proposes a concept for the time-to-digital converter. The TDC core consists of a ring oscillator, to allow it to be used as a second frequency source. Allong with the TDC core, the prescaler and the coarse counter, all other components are normal digital logic blocks, and therefore easy to implement. The resulting TDC concept allows a typical maximum measurement time interval of 33 *ns*.

## 1.2 Motivation

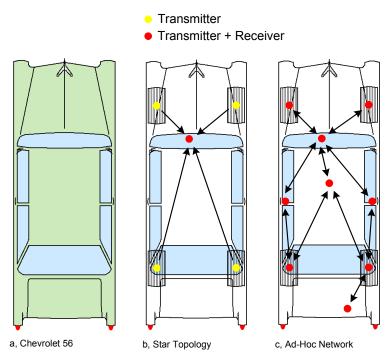

The demand for analog integrated circuits which utilize a transmitter or a receiver is growing every year. In a modern car, an increasing amount of wireless technology can be found. One example are tire pressure sensors. Different topologies (Figure 1.1) can be used to connect these wireless devices.

Figure 1.1: Two Wireless Network Topologies

An Ad-Hoc network topology has the advantage that between all nodes a physical connection does not have to be possible, and if the distance for a direct communication is too great then the message can be forwarded by other nodes. This increases reliability, and the bridgeable distance. The downside is that now at least the central nodes have to be transceivers, and this does increase the complexity.

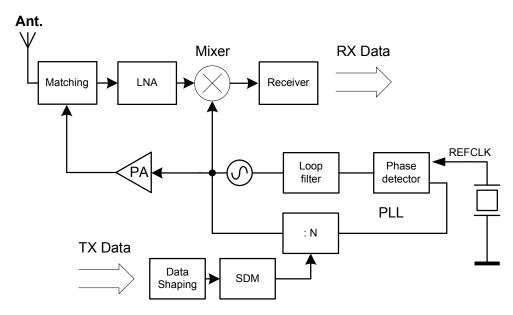

A transceiver structure which is presented in Figure 1.2 utilizes a phase locked loop as a frequency synthesizer for generation of the carrier, the modulator, a power amplifier, an antenna, a mixer for the receive path, and the receiver block itself. The output frequency generated by the phase locked loop is digitally settable, and stabilized by the crystal oscillator.

The modulator shapes the carrier signal in dependence of the current data input

Figure 1.2: Basic Transceiver Architecture

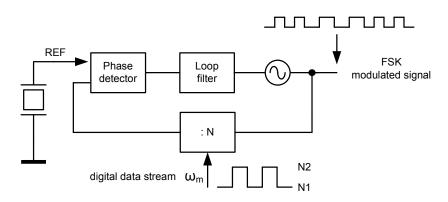

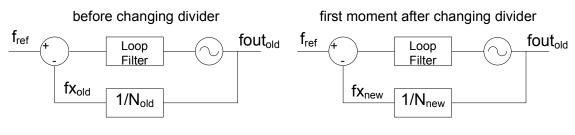

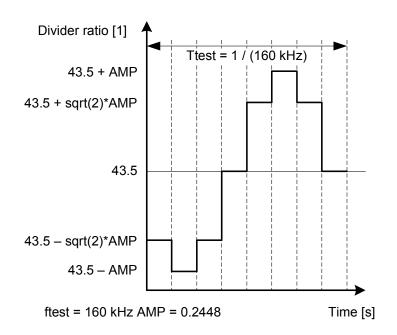

bit. Which signal parameter is altered depends on the used modulation method. If the frequency of the transmission is changed between defined values according to the data signal level, then this is called frequency shift keying (FSK). It can be easily implemented by changing the feedback divider setting of the phase locked loop (1.3) according to the data stream [1].

Figure 1.3: Frequency Shift Keying (FSK)

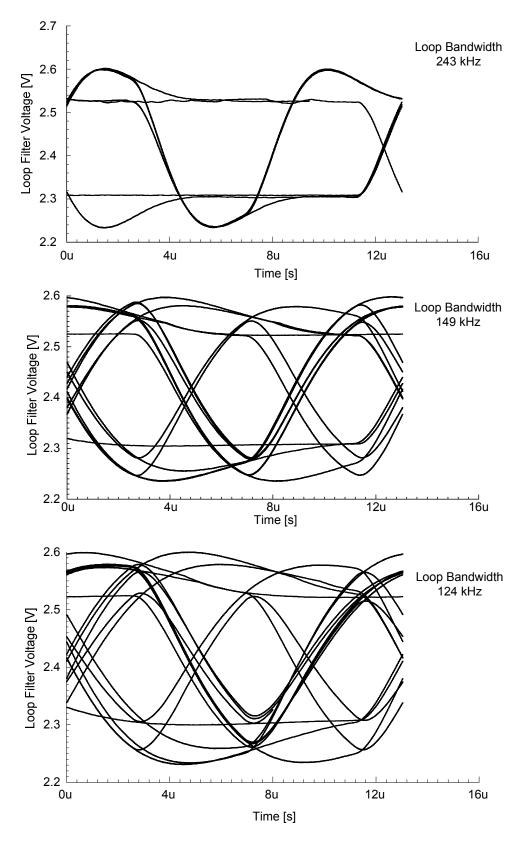

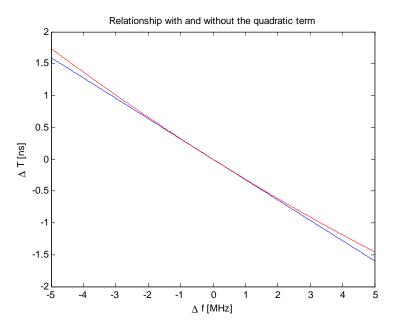

For this modulation, the closed-loop bandwidth of the PLL must be set according to the data rate of the transmission. If it is too low then the shape of the modulated output signal is increasilly falsified (Figure 1.4), and the quality of the transmission decreases. The closed loop bandwidth depends on many parameters, which have a statistic nature or are not constant. For example the small signal gain of the voltage controlled oscillator can change its value by 100 percent over different samples or different operating points. Hence it follows that the bandwidth will also not be fixed, but can vary greatly. That means the PLL must be designed to provide enough bandwidth for the specified data rate also in the worst case scenario.

If the PLL bandwidth is overdesigned to guarantee the function in the worst case scenario, it gets increasingly difficult to obtain a low enough PLL output signal phase noise, and this specification has again be meet. To be sure that the phase noise specification is fulfilled, again overdesign could be needed. This again wastes area and power.

An on-chip closed loop bandwidth measurement circuit would allow the correction of an initial deviation from the specified value. The correction of a wrong loop gain can be done with a variation of the charge pump current. For example if the VCO gain is to small, then the charge pump current is increased to cancel this effect. This stabilizes the closed loop bandwidth of the PLL, and as a result much overdesign is not needed anymore, therefore some area and power could be saved.

## 1.3 Concept based on TDC

Two additional applications are possible if the built-in-self-calibration concept is based on a time-to-digital converter which utilizes a ring-oscillator.

# Built-in-self-test (BIST) for a Period-Time-Jitter Measurement of the PLL on-Chip

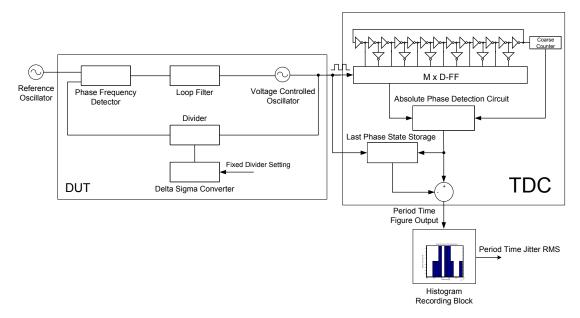

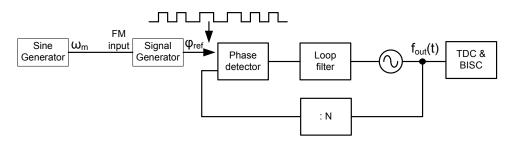

The time-to-digital converter at the output of the phase locked loop can be used to measure the period time of a lot of periods of the PLL output signal. If a histogram is made on-chip from this data, then the period-time-jitter can be measured [2]. The structure of such a test can be seen in Figure 1.5. This would allow to benchmark the phase noise performance of the phase locked loop in a fast an easy manner.

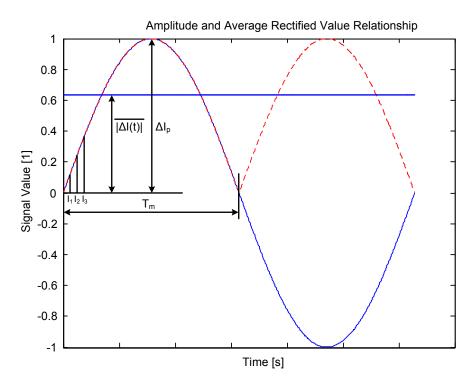

Figure 1.4: Loop bandwidth impact on a FSK modulation ( $230 \ kHz$ ), if the loop bandwidth is too small then the output signal quality worsens

Figure 1.5: Period Time Jitter Measurement, a time-to-digital converter will allow to measure the period time jitter at the PLL output

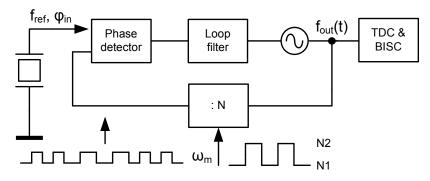

#### Second Frequency Source on-Chip

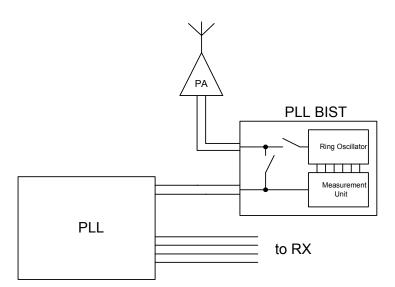

The TDC core ring oscillator could be used as a second frequency source (Figure 1.6). If the inverters in the ring are built tuneable, then the output frequency can also be set in a specific range. To make a coarse selection of the output frequency the following method could be used in combination with the on-chip PLL:

- Set the PLL to the new wanted output frequency of the ring oscillator

- The output word of the time-to-digital converter is used to tune the ring oscillator

- If the output word is bigger than twice the number of inverters in the ring, then its output frequency is to high. Via tuning of the ring supply voltage the propagation delay of the inverters is increased.

- If the output word is smaller than twice the number of inverters in the ring then the output frequency is to low. Again tuning is done.

- If the output word is exactly twice the number of inverters then the second output frequency is tuned to the current output frequency of the phase

#### Figure 1.6: Second frequency source. This source will allow an additional loopback mode

locked loop. Now the PLL output can be disconnected from the TDC input, and the ring oscillator serves as a second frequency source.

Two independently setable frequency sources on-chip would allow a transceiver to receive its own transmissions. Normally this would not be possible, if only one frequency source is integrated, and the second frequency can not be derived from the first frequency source. As an example this would allow loopback tests.

# 2 Phase-locked-Loop (PLL)

# 2.1 Fields of use

Phase-Locked-Loops are used in many different applications. These include [3]:

- Frequency synthesis: Clock signals or carriers must have a stable frequency like a crystal oscillator provides, but the output frequency must also often be digitally settable. A phase-locked-loop offers both: stabilized by a crystal oscillator, and a digitally settable output frequency.

- Clock recovery [4]: Many new data communication standards use a serial transmission scheme for the data path, with the drawback that the data clock from the transmitter is now missing at the receiver, and has to be restored first from the data stream. This can be done with a PLL. As long as the time interval between subsequent signal edges in the received data stream are short enough, the PLL restores the clock which was used for sending the data.

- Usage of a PLL for de-skewing: When using more parallel high frequency signal data paths for a data transmission, not every path is exactly as long as the others in the electrical sense. At the receiver all of the different data paths are not delayed by the same time, and sampling without insuring this can yield to wrong received data. On a complex and high frequency board, e.g. a computer mainboard skewing is an important topic, and a phaselocked-loop can be used to ensure that all the data paths are delayed the same amount of time.

- Jitter and noise reduction: The output signal which is constructed with the help of the PLL circuit follows the input signal frequency deviation over time, and so the wanted signal is conserved. But because of the finite bandwidth

of the phase-locked-loop the new output signal cannot follow very fast deviations of the input signal, thus the jitter and noise of the input signal can be filtered out using the PLL.

• Modulation and demodulation in various applications [1]

# 2.2 Architecture

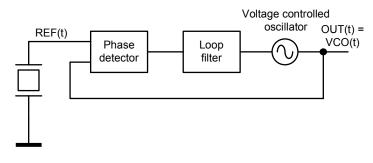

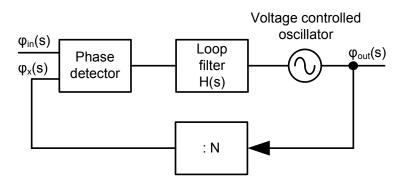

A basic architecture of a PLL is shown in Figure 2.1:

Figure 2.1: Basic PLL Architecture [3]

An important part of the phase-locked-loop is the voltage controlled oscillator (VCO), which generates an output signal with a frequency that is controlled by a voltage at the control input. The second basic block is the phase detector, which compares the input signal from the reference oscillator with the current output signal of the VCO. In many cases, the reference signal comes from a crystal oscillator.

# 2.3 Components

### 2.3.1 Voltage Controlled Oscillator (VCO)

#### **Ring Oscillator**

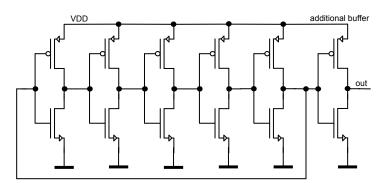

The voltage controlled oscillator is often realised in form of a ring or an LC oscillator [3]. A ring oscillator is very small, but normally does not offer a comparable high *Q*-factor as the LC oscillator. Therefore the ring oscillator generally has a higher phase noise at the output as a comparable LC oscillator [5]. Also ring oscillators tend to have a bad power supply rejection ratio (PSRR) which means fluctuations on the supply voltage will translate to changes in the output frequency. A single-ended ring oscillator structure is shown in Figure 2.2.

Figure 2.2: Single-ended Ring Oscillator

A single-ended ring oscillator consists of a chain of an uneven number of inverters [6]. The last inverter output is fed back into the input of the first one. No stable operating point can be found in this circuit. The output frequency can be found with [6]:

$$f_{out} = \frac{1}{2 \cdot M \cdot t_d} \tag{2.1}$$

where M denotes the number of inverters in the chain, and  $t_d$  is the typical propagation delay of a single inverter. This equation acts on the assumption that the propagation delay of a high-to-low transistion equals exactly the delay for a low-tohigh transition [7]. For a standard inverter used in a digital circuit this is normally not the case.

For tuning the single-ended ring oscillator firstly the amount of capacity on every output node can be controlled in dependence of the control voltage. For example a varactor could be used as a variable capacitance, but a drawback is the increased power dissipation for smaller output frequencies. The second possibility is to tune the supply voltage of the ring oscillator core. The third realisation of a VCO uses a steered supply current for either the whole oscillator core, or for every single stage. The advantage of these methods is that for a smaller output frequency the supply current drops.

#### **LC** Oscillator

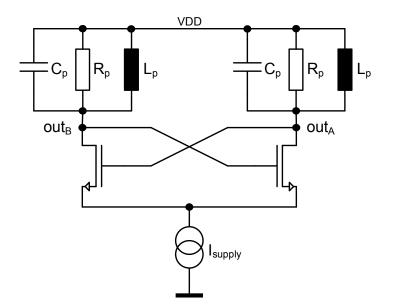

A basic element of any LC oscilator is a resonance tank formed by an inductor L and a capacitor C. This kind of oscillator offers a good jitter and phase noise performance, but needs normally a lot of space for the implementation of the inductor. Also there is parasitic coupling from the inductor to the surrounding circuits. An often used differential circuit is shown in Figure 2.3 [3].

Figure 2.3: Differential LC Oscillator

Two resonance tanks are the load for the two transistors, and if the overall gain is high enough then noise in the circuit is amplified continually, and the oscillation starts. In the steady state condition the tail current  $I_{supply}$  is switched periodically between the two sides [3].

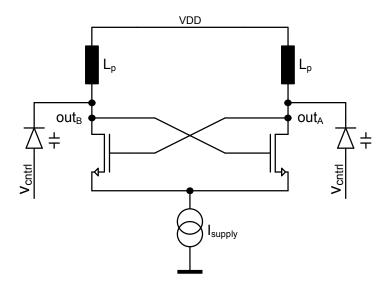

To make this oscillator tunable (Figure 2.4) [3] one can change the value of the inductor or the capacitance. The inductor is fixed by its physical layout, and therefore the capacitance has to be controlled, e.g. with a varactor device, which changes its capacitance with the voltage across its terminals.

Figure 2.4: Differential Voltage Controlled LC Oscillator [3]

#### 2.3.2 Phase Detector

#### **Analog Multiplier**

Analog multipliers are often realised in the form of a gilbert cell or as a fourquadrant multiplier. They allow very high frequency operation, and are often used with sinusoidal or near sinusoidal input signals.

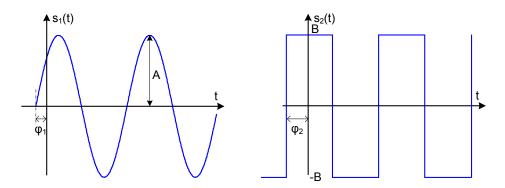

Example for a reference signal [4]:

$$s_1(t) = A \cdot \sin(\omega_1 \cdot t + \varphi_1) \tag{2.2}$$

The feedback signal from the divider can also be rectangular (fourier series):

$$s_{2}(t) = B \cdot \left[\frac{4}{\pi} \cdot \cos(\omega_{2} \cdot t + \varphi_{2}) + \frac{4}{3 \cdot \pi} \cdot \cos(3 \cdot \omega_{2} \cdot t + \varphi_{2}) + \frac{4}{5 \cdot \pi} \cdot \cos(5 \cdot \omega_{2} \cdot t + \varphi_{2}) + \ldots\right]$$

(2.3)

These two input signals are also shown in Figure 2.5. These signals are now multiplied together, to form the output signal. If the loop is in the locked state then the frequency of both input signals is equal.

Figure 2.5: Possible Input Signals [4]

$$s_{out}(t) = s_1(t) \cdot s_2(t) = A \cdot B \cdot sin(\omega_1 \cdot t + \varphi_1)$$

$$\cdot \left[\frac{4}{\pi} \cdot cos(\omega_2 \cdot t + \varphi_2) + \frac{4}{3 \cdot \pi} \cdot cos(3 \cdot \omega_2 \cdot t + \varphi_2) + \frac{4}{5 \cdot \pi} \cdot cos(5 \cdot \omega_2 \cdot t + \varphi_2) + \ldots\right] \quad (2.4)$$

Further simplification with

$$sin(x) \cdot cos(y) = \frac{1}{2} \cdot [sin(x-y) + sin(x+y)]$$

(2.5)

$$s_{out}(t) = A \cdot B \cdot \frac{4}{2 \cdot \pi} \cdot \left[ sin(\omega_1 \cdot t + \varphi_1 - \omega_2 \cdot t - \varphi_2) + sin(\omega_1 \cdot t + \varphi_1 + \omega_2 \cdot t + \varphi_2) \right. \\ \left. + \frac{1}{3} \cdot sin(3 \cdot \omega_1 \cdot t + \varphi_1 - 3 \cdot \omega_2 \cdot t - \varphi_2) \right. \\ \left. + \frac{1}{3} \cdot sin(3 \cdot \omega_1 \cdot t + \varphi_1 + 3 \cdot \omega_2 \cdot t + \varphi_2) + \ldots \right]$$

(2.6)

$$s_{out}(t) = A \cdot B \cdot \frac{4}{2 \cdot \pi} \cdot \left[ sin(\varphi_1 - \varphi_2) + sin(2 \cdot \omega_1 \cdot t + \varphi_1 + \varphi_2) + \frac{1}{3} \cdot sin(\varphi_1 - \varphi_2) + \frac{1}{3} \cdot sin(6 \cdot \omega_1 \cdot t + \varphi_1 + \varphi_2) + \ldots \right]$$

(2.7)

The first DC term in the brackets is the term we wanted to obtain with the analog

multiplier. It carries the information about the phase error. All other high frequency terms in the brackets are unwanted, and therefore are filtered out in the loop filter.

$$s_{out}(t) = A \cdot B \cdot \frac{2}{\pi} \cdot [sin(\varphi_1 - \varphi_2) + ...] = A \cdot B \cdot \frac{2}{\pi} \cdot [sin(\varphi_{error}) + ...]$$

(2.8)

If we set

$$Kpd = A \cdot B \cdot \frac{2}{\pi} \tag{2.9}$$

the so called phase detector gain can be introduced [4]. Also the high frequency terms are now left out. The detector output can be written in a new form:

$$s_{out}(t) \simeq Kpd \cdot [sin(\varphi_{error})]$$

(2.10)

If the value of  $\varphi_{error}$  is very small, the sin function can be further approximated, so we can get the linear model of the phase locked loop.

$$s_{out}(t) \simeq Kpd \cdot \varphi_{error}$$

(2.11)

This output signal of the analog multiplier is now used to control the voltage controlled oscillator after it has passed the loop filter.

XOR Gate

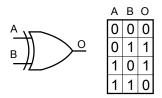

Figure 2.6: XOR Gate

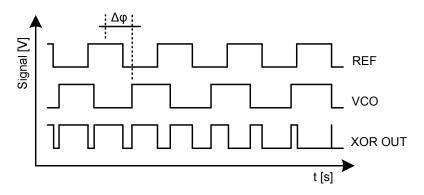

A single XOR gate can be used as a phase detector [4, 3] (Figure 2.6). It

outputs a waveform whose width of the output pulses are proportional to the difference of the phases of both input signals (=phase error), as can be seen in Figure 2.7. A low pass filter creates the mean value from the output signal, and the filtered DC voltage is proportional to the phase error. An attribute of the XOR gate is the creation of pulses on both the rising and falling edges.

Figure 2.7: XOR Phase Detector Time Behaviour

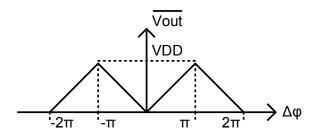

A drawback of the XOR gate is that it can only handle small phase errors, because its transfer function is ambiguous for a phase error bigger than  $\pm \pi$ . The transfer function is illustrated in Figure 2.8.

Figure 2.8: XOR Linear Transfer Function [3]

#### **JK Flip Flop**

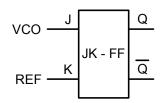

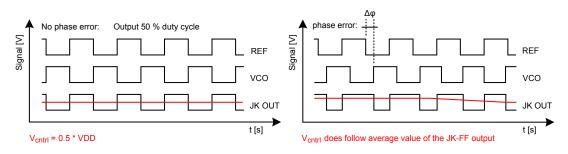

A second possibility for a phase detector is the usage of a JK flip flop [4] (Figure 2.9). In this case the phase detector is sensitive on the rising edge of both of the input signals. The falling edges of the signals do not play a role in this type of PD.

With zero phase error the two input signals have opposite phase alignments. The rising edge of the reference signal sets the flip flop output to high, and the

Figure 2.9: JK Flip Flop Phase Detector

next rising edge from the VCO output sets the output back to low. That means with zero phase error, the output signal from the phase detector has a duty cycle of 50 percent, and the average DC output voltage is half the supply voltage. If a small phase error is introduced, e.g. the voltage controlled oscillator falls behind the reference phase, then the duty cycle starts to grow above 0.5, because the logical high level time of the output is now longer than the low level time, and so the average DC output voltage starts also to rise. This increases the VCO output frequency, and the phase error is minimized again. Figure 2.10 illustrates the operation.

Figure 2.10: JK FF Phase Detector Time Behaviour

The transfer function can be seen in Figure 2.11, which describes the average output voltage as a function of the input phase error. This function is again ambiguous outside the region  $\pm \pi$ .

#### PFD, Phase Frequency Detector + Charge Pump

A modern and frequently used detector is the phase frequency detector (PFD) [3]. It offers advantages in comparison to the other phase detectors, especially when both input frequencies are not equal, and the loop is in an unlocked state. The other phase detectors can not work well, if the phase error gets to big, because of their ambiguous behaviour for large phase errors. The phase frequency detector

Figure 2.11: JK FF Transfer Function [4]

not only can compare the phase alignment, but it also has the ability to compare both of the input frequencies together (frequency detector), which helps to find lock easily.

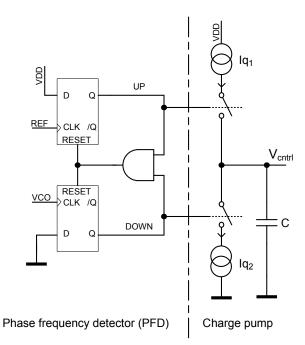

A typical PFD and charge pump circuit can be seen in Figure 2.12 [4, 3, 1].

Figure 2.12: Phase Frequency Detector and Charge Pump Architecture [3]

The circuit is sensing edges at the signal inputs, e.g. rising edges. The PFD circuit has an internal state which can be changed when input signal edges are arriving. With the two digital inputs four different states are possible, but one of the states (UP = high, DOWN = high) is prevented with the use of an additional AND gate which resets both flip flops when this state is arising. The possible

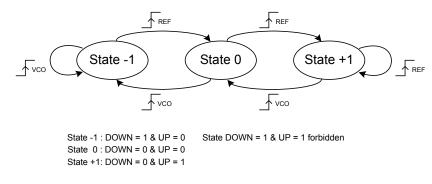

states are shown in Figure 2.13.

Figure 2.13: PFD State Diagram [8]

**Frequency Detector** We assume the loop is not locked, and the reference frequency is much higher than the divided output frequency, and so more rising edges are sensed by the PFD on the REF input before a rising edge on the VCO input occurs. With every rising edge on REF, the state is increased from -1 to 0, from 0 to +1 and so on. If we reach state +1 every additional edge also yields state +1. State +1 does also mean the UP output is activated (logical high), the switch in the UP branch of the charge pump is closed, and so the capacitor is charged by a constant current  $Iq_1$ , and therefore its voltage is rising. This increases the output frequency of the VCO until the point where both input frequencies of the PFD are almost identical (Figure 2.14) [3].

As the difference between both frequencies gets smaller and smaller less rising edges on the REF input are sensed before a rising edge on the VCO input occurs, and so the probability to reach state +1 gets smaller and smaller, while the probability for state 0 rises. For almost identical frequencies, the state is periodically changed between state 0 and state +1. In this way the frequency detector functionality stops, because the frequencies are identical, and the phase frequency detector will work as a phase detector.

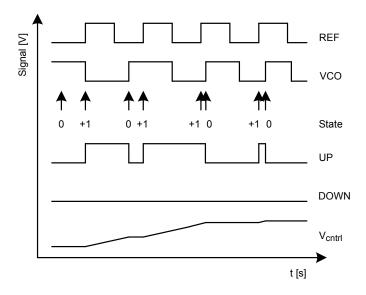

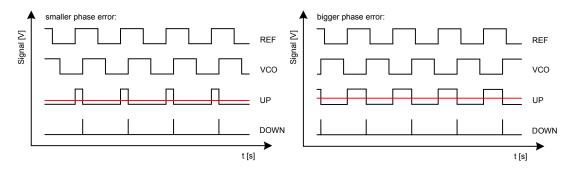

**Phase Detector** If both input frequencies are equal the PFD does phase detection (Figure 2.15) [3]. If for example on the REF input a rising edge is sensed, then the UP output is activated until a rising edge on the VCO input is found, which then sets the second flip flop output to high. The AND gate detects the two activated outputs, and resets both flip flops. The time between the two rising

Figure 2.14: PFD Frequency Detector Time Behaviour

edges on the inputs determines the duty cycle of the switching signals UP/DOWN to the current sources, which are then charging or discharging the capacitor. The phase difference (=phase error) determines the output voltage after the loop filter.

Figure 2.15: PFD Phase Detector Time Behaviour

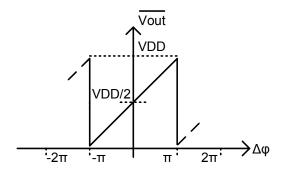

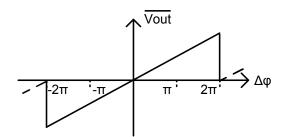

The average loop filter DC output voltage as a function of the input phase error can be seen in Figure 2.16. The well-defined area of the transfer function is for the PFD  $\pm 2 \cdot \pi$  [3].

#### 2.3.3 Loop Filter

The loop filter filters out high frequency signal parts from the phase detector output signal, and creates the DC average voltage for the VCO control input. The loop filter and its parameters have a huge impact on the PLL behaviour.

Figure 2.16: PFD Transfer Function

#### Very Basic PD + no Filter

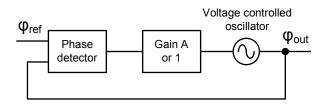

A phase locked loop with an order of one is only possible without a loop filter, or if the loop filter is frequency independent [8]. So the loop filter transfer function equals H(s) = A. The setup is shown in Figure 2.17.

Figure 2.17: Order One Phase Locked Loop

The open loop transfer function is:

$$G(s) = \frac{Kpd \cdot Kvco \cdot A}{s} \tag{2.12}$$

The closed loop transfer function is:

$$T(s) = \frac{\varphi_{out}(s)}{\varphi_{ref}(s)} = \frac{G(s)}{1 + G(s)}$$

(2.13)

$$T(s) = \frac{Kpd \cdot Kvco \cdot A}{s + Kpd \cdot Kvco \cdot A}$$

(2.14)

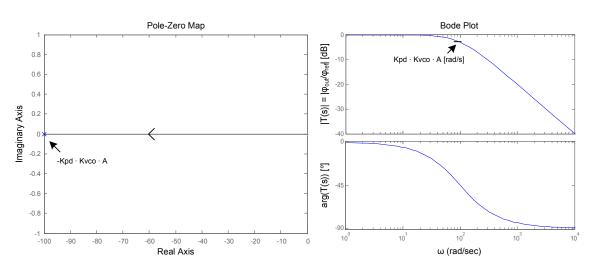

The highest occurring power of s in the closed loop transfer function denominator is one, and so is the order. Often A(s) equals 1, and so the gain remaining in the open loop transfer function is Kpd and Kvco. If the loop is closed, the only pole moves from its zero position to the new position [8]

$$p1 = -Kpd \cdot Kvco \cdot A \tag{2.15}$$

Figure 2.18: Order One PLL Bode Plot and s-Plane [8]

The closed phase locked loop has the -3dB bandwidth of  $Kpd \cdot Kvco \cdot A [rad/s]$ , and behaves like a low pass filter, as can be seen in 2.18.

#### Very Basic PD + RC Lowpass Filter (Lag)

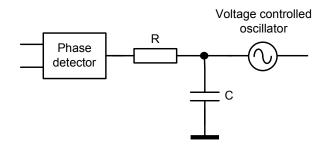

The loop filter consists of a resistor R and a capacitance C [8]. The phase detector in this case is a simple XOR or a JK flip flop type. The only integrator in the loop is the voltage controller oscillator, and so the loop will be of type I, but also of order 2. The circuit is illustrated in Figure 2.19.

Figure 2.19: RC Lowpass Loop Filter

The loop filter transfer function is

$$H(s) = \frac{1}{1 + s \cdot R \cdot C} \tag{2.16}$$

With the gain of the phase detector and the voltage controlled oscillator one can find the whole open loop transfer function:

$$G(s) = \frac{Kpd \cdot Kvco}{(1 + s \cdot R \cdot C) \cdot s}$$

(2.17)

The second order of *s* under the fraction comes from the integrating behavior of the voltage controlled oscillator in the phase model. To get the closed loop transfer function we calculate

$$T(s) = \frac{G(s)}{1 + G(s)}$$

(2.18)

$$T(s) = \frac{Kpd \cdot Kvco}{(1 + s \cdot R \cdot C) \cdot s \cdot (1 + \frac{Kpd \cdot Kvco}{(1 + s \cdot R \cdot C) \cdot s})}$$

(2.19)

$$T(s) = \frac{Kpd \cdot Kvco}{Kpd \cdot kvco + (1 + s \cdot R \cdot C) \cdot s}$$

(2.20)

$$T(s) = \frac{Kpd \cdot Kvco}{s^2 \cdot RC + s + Kpd \cdot Kvco}$$

(2.21)

The highest occurring power of *s* in the closed loop transfer function denominator is two, and so this loop is second order. Using an often used equation form in the control theory this equation can be rewritten as [3]:

$$T(s) = \frac{\omega_n^2}{s^2 + 2 \cdot \zeta \cdot \omega_n \cdot s + \omega_n^2}$$

(2.22)

with

$$\omega_n = \sqrt{\frac{1}{R \cdot C} \cdot Kpd \cdot Kvco}$$

(2.23)

$$\zeta = \frac{1}{2} \cdot \sqrt{\frac{1}{R \cdot C \cdot Kpd \cdot Kvco}}$$

(2.24)

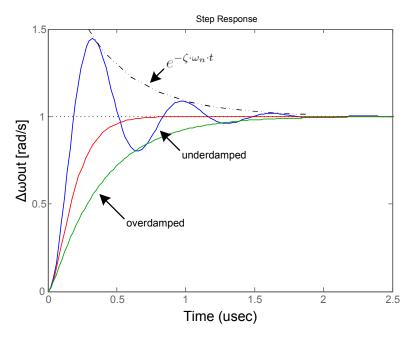

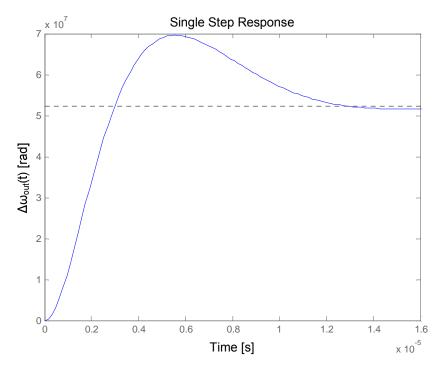

Expression  $\omega_n$  is called natural frequency, and  $\zeta$  is the damping ratio. Depending on these two parameters, the behaviour of the phase locked loop changes completely. If  $\zeta > 1$  then the system is overdamped, which means the transient response of the loop has the form of two exponentials, and no overshooting occurs. Otherwise if  $\zeta < 1$  then the system is called underdamped, and overshooting occurs, but the loop transponse will be very fast [3]. So with these two parameters a trade between settling speed and overshooting can be done. Two different example frequency step reponses with different damping ratios of the loop are shown in Figure 2.20.

Figure 2.20: Possible Frequency Step Responses [3]

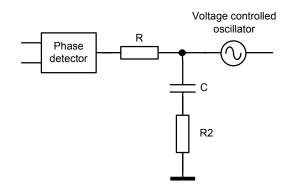

#### Very Basic PD + Lead-Lag Filter

An additional resistor in the lowpass filter adds a zero to the transfer function, and with it the behaviour of the loop can be further changed [8]. The expanded loop filter is shown in Figure 2.21.

Figure 2.21: Additional Zero implemented (Lead-Lag Filter)

The new transfer function is

$$H(s) = \frac{1 + s \cdot C \cdot R2}{1 + s \cdot C(R + R2)}$$

(2.25)

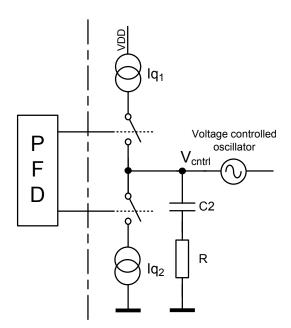

#### PFD + a single capacitor and an optional resistor

For a type two PLL, two integrators are needed in the open loop so the loop filter must also contain an integrator. In the case of a voltage output phase detector an additional integrator is only possible with an active filter [8], which means more power dissipation. If a phase detector with a charge pump (=current output) is used, a single capacitor at the output delivers an additional integrator [3], and so with a passive filter, a type two PLL is possible.

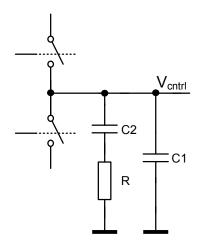

If the capacitance  $C_2$  in Figure 2.22 is inserted, and R has a value of zero, then the filter has the transfer function of an integrator, and we have realized a type two PLL. But two integrators in a control system without additional corrective actions are unstable [3]. To obtain stability only a resistor R is needed in series to the capacitor, and it creates an additional zero in the transfer function. Its position can be set, so that we get enough phase margin at the gain crossover frequency to make the loop stable.

A drawback of this resistor is that every current impulse into or from the filter creates a voltage ripple at the loop filter output, which then translates to a ripple in the VCO output frequency [3]. A little change to the filter can attenuate this effect as presented in Figure 2.23. A part of the old capacitance C2 from the last filter variant is now put into a new capacitor C1. In this way less ripple is produced, because in the first moment of a new current pulse into or from the

Figure 2.22: Simple Loop Filter (with Integrator)

filter this current can pass capacitor C1, and does not introduce a troublesome voltage at R.

Figure 2.23: Improved Voltage Ripple Performance

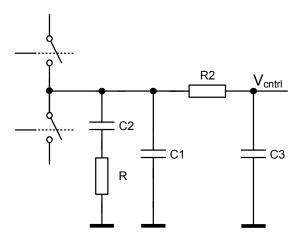

#### PFD + 3rd Order Loop Filter

The order can be increased again by adding a low pass filter to Figure 2.23. The result is shown in Figure 2.24 [1]. This loop filter is used in this diploma thesis, and so its transfer function should also be presented here.

Figure 2.24: 3rd Order Loop Filter

The following equations can be found in [1]:

$$H(s) = \frac{1 + s \cdot R \cdot C2}{s \cdot (A2 \cdot s^2 + A1 \cdot s \cdot A0)}$$

(2.26)

with

$$A0 = C1 + C2 + C3 \tag{2.27}$$

$$A1 = C2 \cdot R \cdot (C1 + C3) + C3 \cdot R2 \cdot (C1 + C2)$$

(2.28)

$$A2 = C1 \cdot C2 \cdot C3 \cdot R \cdot R2 \tag{2.29}$$

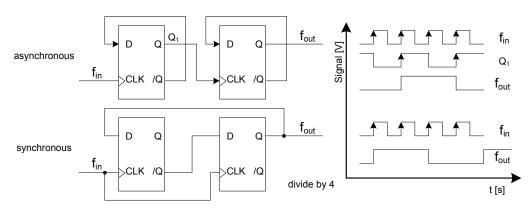

#### 2.3.4 Feedback Divider

#### Division by an integer value

It is sufficient for many applications if the output frequency can be set in integer multiples of the reference frequency, and this can be achieved with a frequency divider N in the feedback path [3, 1]. If the reference frequency is not small enough to achieve the needed output frequency resolution, a fractional PLL can be used instead. An integer PLL has the advantage that it is less complex.

Frequency division is often achieved with flip flops in toggle configuration, if the division factor is fixed, and the frequency can be divided by a factor of  $2^{b}$ , where

*b* equals the number of devices. A implementation which can be synchronious or asynchronious is seen in Figure 2.25.

Figure 2.25: Fixed Frequency Divider

Should the output frequency be digitally programmable often binary counters are used. It counts every time a rising or a falling edge occurs. After  $b = 2^n - r$  input signal edges it overflows, where *n* is the number of bits of the counter, and *r* is the value which is reloaded to the counter after every overflow. So the frequency is divided by a factor of *b*. In comparision to binary counters a flip flop divider saves power and area, and so they are used as a prescaler in front of programmable binary counters.

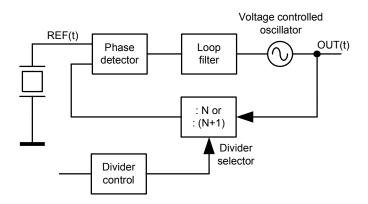

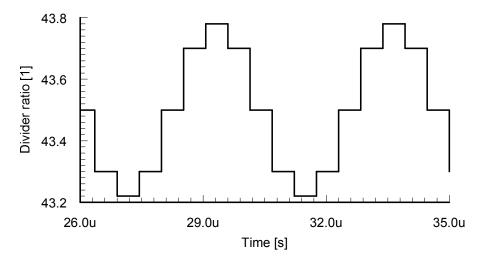

#### Delta-sigma fractional-N phase locked loop

If the frequency resolution of a integer PLL is not enough, a fractional-N phase locked loop (Figure 2.26) can be used, which allows the multiplication of the reference frequency with a configurable rational number [1]. Its feedback divider can divide the output frequency by N or by N + 1, and the active divider setting is changed over time. For example, 9 periods of the input reference signal the output frequency is divided by 300 (=N), and then one period it is divided by 301 (=N+1). The average of the divider settings is  $(9 \cdot 300 + 1 \cdot 301)/10 = 300.1$ . So the output frequency is  $300.1 \cdot fref$ . The loop filter filters out the higher frequencies which are generated at the output of the PDF because of the switching action.

A downside of a fractional-N PLL is that the periodic change of the divider does generate fractional spurs, which increases the noise inside the phase locked loop [1].

Figure 2.26: Fractional-N PLL Architecture

If the divider setting of a fractional-N PLL is not changed periodically, but is controlled by a delta-sigma converter, therefore set in a random manner, the problem with the fractional spurs can be improved. The noise at the PFD output is moved to higher frequencies, and so the lowpass loop filter can filter out more of it. So the delta-sigma converter helps to improve the performance [1].

# 2.4 Operation

Figure 2.27: Typical PLL Time Behaviour

The function of a phase locked loop should be described based on an example which is shown in Figure 2.27. If for example the output signals phase does lead in time in comparison to the reference signal, then the phase detector decreases the VCO control voltage, and with it also the output frequency a little bit. This small frequency drop is enough to allow the phase of the reference signal to catch up,

and the phase error gets smaller with time. While the error decreases, the VCO slowly speeds up. At some point a phase error of zero would be reached, but it is most likely that the loop will not respond fast enough to this zero phase error, and will overdo the correction of the initial error.

Now the reference signals phase is leading, and the phase detector has to speed up the VCO until the phase of both signals is equal again. Some time later the loop will reach a stable operating condition where both signals have the same phase state, or are only misaligned by a phase error which is constant over time, and this is called the "locked state". From then on the loop will try to follow slower phase changes of the reference signal with the phase of the output signal.

### 2.5 Models

#### 2.5.1 Phase Model

In the locked state the phase detector behaves like a linear block, because the phase error never grows above the boundaries where the phase detector transfer function gets ambiguous, thus there is a linear relationship between the phase error and the output of the phase detector [4].

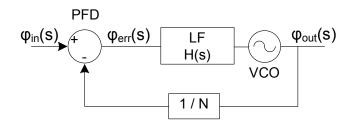

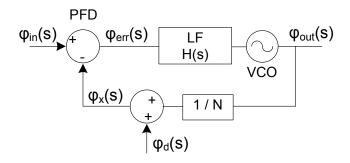

This linear relationship allows to describe the PLL and its behaviour in a phase model [9]. A basic model is shown in Figure 2.28. Instead of using a voltage or current of a real signal inside the PLL, the phase of all signals is used as the information parameter. At the PLL input, the phase of the reference signal is injected and at the output the phase of the output signal can be derived.

The advantage of such a simplified model is that the phase model delivers the time response of a PLL, which we are interested in, without doing a very time and resource consuming transient simulation of the whole circuit in the time domain [9]. We do not get the value of all the voltages and currents inside the circuit over time from this model.

Figure 2.28: Linear PLL Phase Model [3]

#### **Building Blocks**

**Phase Detector** Because our model is in the phase space, the modelling of the phase detector can be simply done as a subtracter, which calculates the phase difference between both inputs 2.29 [3]. The so called gain of the phase detector (=Kpd) describes how steep the relationship between the phase error and the average VCO input voltage is (Figure 2.30).

Figure 2.29: Phase Detector Model

The output of the phase detector can be calculated with:

Figure 2.30: Phase Detector Transfer Function [3]

**Loop Filter** The output signal from the phase detector is translated into the input control voltage of the VCO by the loop filter [3]. Figure 2.31 shows the loop filter.

Figure 2.31: Loop Filter Model

The transfer function of the loop filter is:

$$H(s) = \frac{Y(s)}{X(s)} \tag{2.31}$$

with Y(s)...output signal, X(s)...input signal

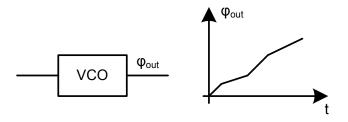

**Voltage Controlled Oscillator** The output frequency is controlled by the control voltage at the input of the VCO, and in the ideal case this relationship is perfectly

linear. To get the phase of the output signal for the phase model we use the following equation:

$$\varphi(t) = \int_0^t \omega(\tau) \, d\tau \tag{2.32}$$

To derive the phase of the output signal we integrate over the output frequency  $\omega(\tau)$  of the VCO [3]. So in the phase model the VCO is working as an integrator, and the relationship between the input control voltage and the frequency deviation of the output frequency is called the gain of the VCO (=Kvco [ $\frac{Hz}{V}$ ]). See Figure 2.32 for details.

Figure 2.32: Voltage Controlled Oscillator Model

Transfer function of a VCO [3, 9]:

$$H_{vco}(s) = \frac{\varphi_{out}(s)}{v_{cntrl}} = \frac{Kvco}{s}$$

(2.33)

with  $v_{cntrl}$ ...input control voltage signal of the VCO

**Frequency Divider** To find the model for a divider with a division factor of N in the phase space, we can use equation 2.5.1. If we divide the frequency through a constant value N over time, this constant value can be prescind from the integral, and the phase of this signal is divided by the same value.

$$\varphi(t) = \int_0^t \frac{\omega(\tau)}{N} d\tau = \frac{1}{N} \cdot \int_0^t \omega(\tau) d\tau$$

(2.34)

The model for a feedback divider is therefore (Figure 2.33)

$$H_{Divider}(s) = \frac{\varphi_{out(s)}}{\varphi_{in(s)}} = \frac{1}{N}$$

(2.35)

$\phi_{in}$  : N  $\phi_{out} = \phi_{in} / N$

Figure 2.33: Frequency Divider Model

**Reference Oscillator** Because we need to feed the phase of the reference signal into the phase detector, we firstly have to do a frequency-to-phase space conversion as we did with the VCO. So we integrate the frequency.

#### **PLL Characterization**

Order of a PLL

The order of a PLL is found with the highest occurring power of the variable *s* in the closed loop transfer function denominator of the phase-locked loop [8].

• Type of a PLL

The PLL type is found by the number of integrators in the open loop transfer function [8]. Because every VCO is itself an integrator in the phase model, all PLL types are at least one.

#### **Transfer Functions**

The open loop transfer function G(s) is

$$G(s) = \frac{Kpd \cdot Kvco \cdot H(s)}{s}$$

(2.36)

For calculation of the output response of the loop to an input signal variation, the closed loop transfer function is important. It tells us how the phase at the ouput

node of the loop responds to a phase signal at the reference input of the loop. The closed loop transfer function is derived from the open loop transfer function.

$$T(s) = \frac{G(s)}{1 + \frac{G(s)}{N}} = \frac{\varphi_{out}(s)}{\varphi_{in}(s)}$$

(2.37)

$$T(s) = \frac{Kpd \cdot Kvco \cdot H(s)}{s \cdot (1 + \frac{Kpd \cdot Kvco \cdot H(s)}{s \cdot N})} = \frac{Kpd \cdot Kvco \cdot H(s)}{s + \frac{Kpd \cdot Kvco \cdot H(s)}{N}}$$

(2.38)

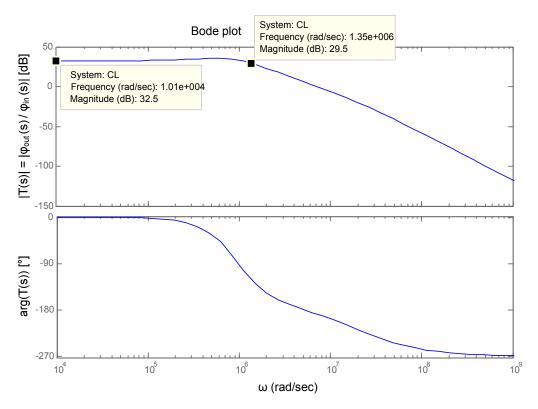

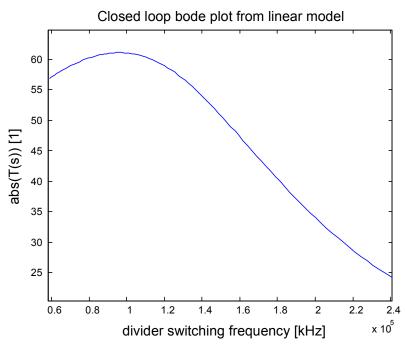

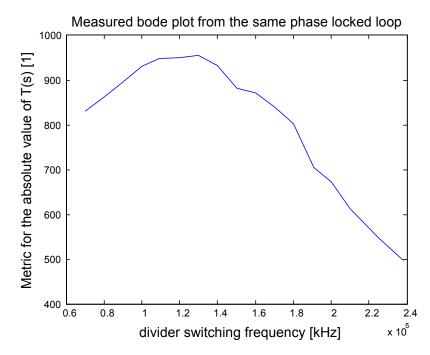

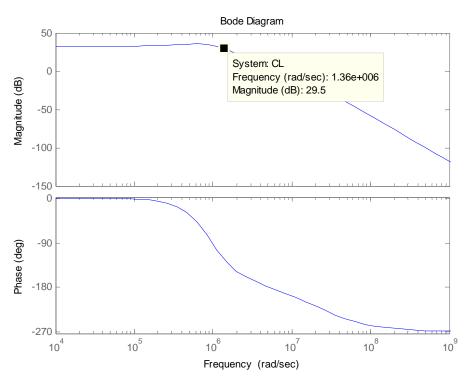

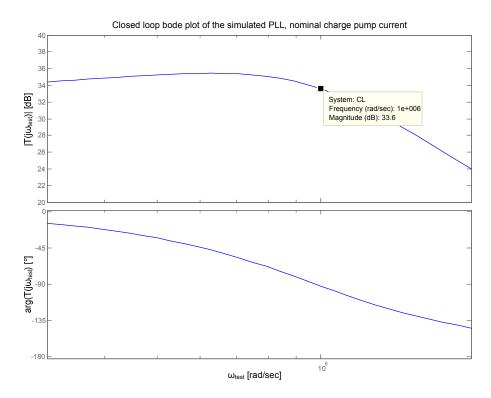

The bode plot of T(s) (Figure 2.34) tells us how the closed loop responds to sinusoidal signals at the reference input. For low frequencies  $\omega \ll \longrightarrow T(s)$  becomes N. In this case the output phase follows the input phase(see also [3]), and the relationship between the output and input equals N. For  $\omega \gg \longrightarrow T(s)$  becomes zero, and the input phase changes can not be seen anymore at the output of the system. At a specific frequency the output signal is attenuated by -3dB, and this frequency is called the -3dB bandwidth. A typical bode plot for T(s) is presented in Figure 2.34.

Figure 2.34: Closed Loop Transfer Function Bode Plot with Bandwidth

# 2.5.2 Voltage Model

The voltage model was created to gain the ability to run a transient simulation for the whole system consisting of the PLL and the bandwidth calibration circuit. In the voltage model, voltages and currents are used as the information parameters, thus information, which is not delivered by a phase model [9], about these variables over time is gained. All input and output signals are now time domain signals with a specific frequency, and so for example a time-to-digital converter can be used directly on the output of the PLL circuit to measure the output period in a simulation. A downside to this model is the higher amount of computing power which is needed.

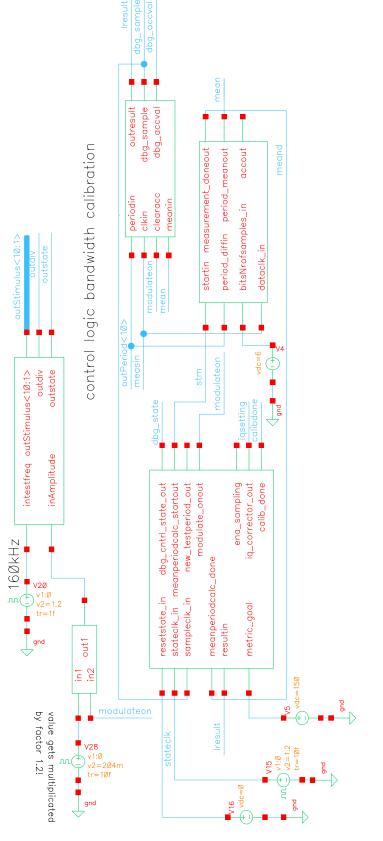

### Phase Frequency Detector

The phase frequency detector is constructed with digital gates, and its basic architecture is introduced in Figure 2.12. The circuit used in the transient simulation is more complicated, in order to get better accordance with the implemented circuit. The two output signals UP and DOWN of the phase frequency detector switch on or off two ideal current sources which represent the charge pump. This output current is then fed into the 3rd order loop filter.

#### Loop Filter

The loop filter is constructed with passive elements (Figure 2.24).

#### Voltage Controlled Oscillator

The voltage controlled oscillator is described in Verilog-A [9], and it does accept a voltage at its control input. The Verilog-A code does create the corresponding rectangular output signal. This signal is then feed into the feedback divider.

#### Feedback Divider

The divider is also a Verilog-A model. The divider allows the division of the input frequency by the integer N. The integer N is controlled by the voltage of a control input signal. In this way the divider can be used as a division by N or N + 1 circuit for the use in a fractional-N phase locked loop. The divider itself has an

internal variable which counts the rising edges from the frequency input signal. If this variable reaches the value of N, then the output signal state is changed and the internal variable is set back to zero.

#### $\Delta\Sigma$ Converter

Because the phase locked loop which is used in this diploma thesis is a deltasigma fractional-N PLL, a model for a converter was also necessary. The converter is also a Verilog-A model, which allows the output frequency of the PLL to be set in steps smaller than the reference frequency.

## 2.5.3 Comparison

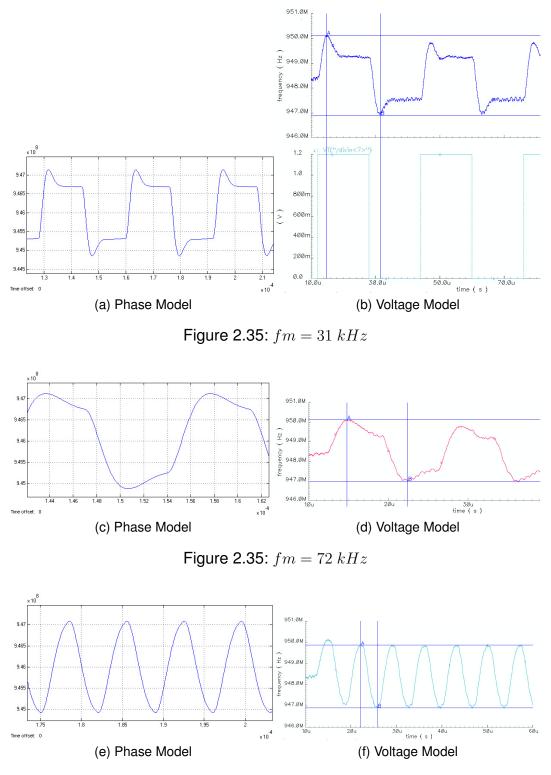

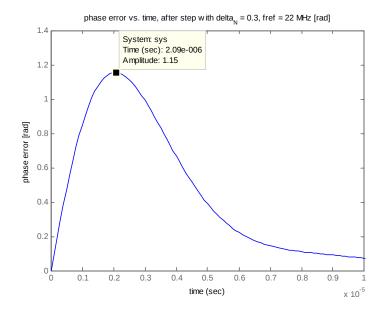

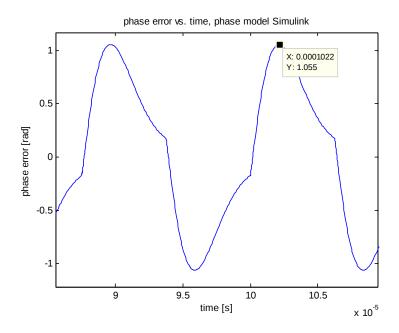

A comparision between the phase and voltage model was done. The phase model was simulated in Simulink, and the voltage model in a transient simulation in Spectre. First the loop responses to a single output frequency change were compared, and it is important that the amount of overshoot, the settling time, and the final output frequency are equal. Both models fit well together.

In a second step the feedback divider was periodically modulated in a rectangular manner, and for both models the output frequency trend was derived. Both results do fit together for all used divider switching frequencies. Because the reference frequency was slightly different in the Spectre simulation, the absolute value of the output frequency is not exactly the same as in Matlab, but the time behaviour is equal.

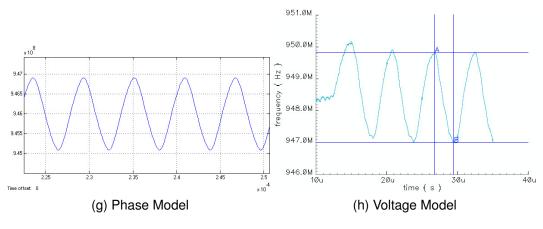

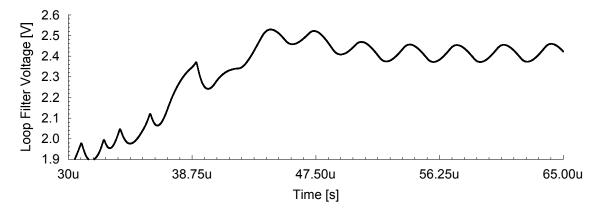

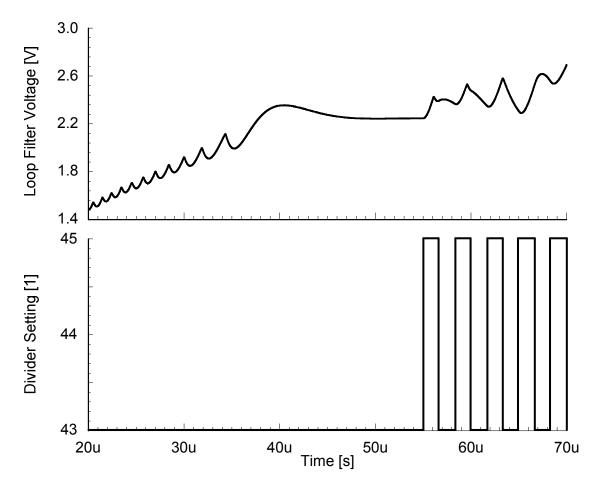

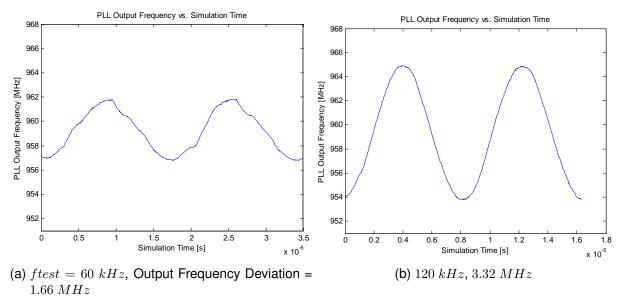

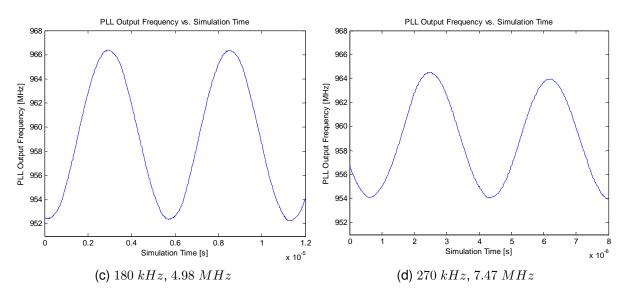

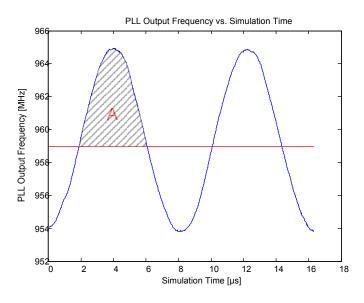

The waveforms in Figure 2.35b 2.35d 2.35f 2.35h are the result of transient simulations of the voltage model with different modulation frequencies fm. For comparision reasons in Figure 2.35a 2.35c 2.35e 2.35g the same results from SimuLink are shown.

Figure 2.35:  $fm = 142 \ kHz$ , PLL output frequency vs. time results for the phase and voltage model

# 3 Time-to-digital Conversion

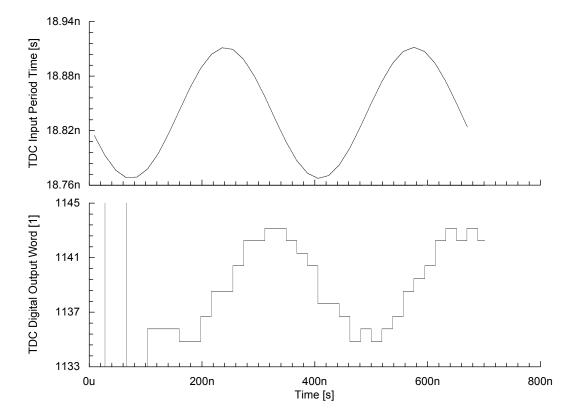

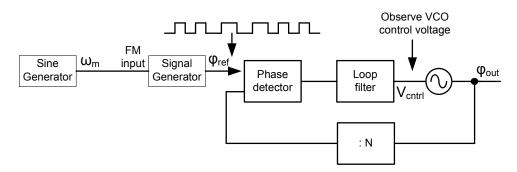

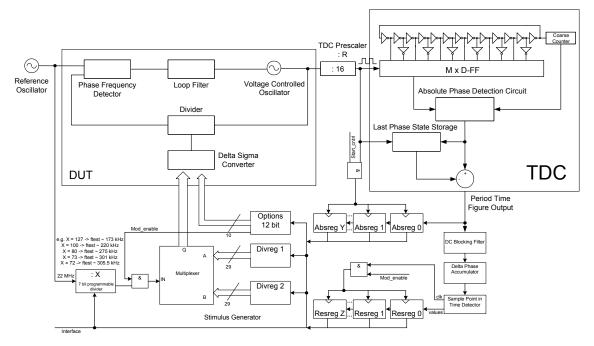

The time-to-digital converter is used in this concept to observe the output signal period time of the phase locked loop and to obtain a digital number for the closed loop bandwidth of the PLL under test. An introduction to this topic is given in this chapter.

# **3.1 Typical Applications**

TDC circuits are often used [10] in science [11, 12, 13, 14], especially in particle detectors [15] or time-of-flight detectors [16, 17]. Examples of such uses are how distance can be measured with the help of a laser device, or more exotic applications like time correlated imaging, which uses an array of a lot of smaller time-to-digital converters can be found [18]. Other applications use a TDC as a very fast analog-to-digital converter [19], or for the measurement of time jitter [2]. And also in the field of phase locked loops they are used as phase frequency detectors in newer architectures [20, 21].

# 3.2 Methods

Different possibilities are shown in [22, 10].

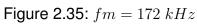

# 3.2.1 Analog Time Stretching

This technique allows the measurement of small time intervals with a relatively simple circuit (Figure 3.1) [22]. During the unknown time interval T, a capacitor C is charged with a constant current of  $I_1 - I_2$ , and the voltage over C is increased in a linear manner. Afterwards C is discharged again by a constant current  $I_2$  which is smaller than  $I_1$ , and its voltage decreases again. A fast comparator enables a

counter for the discharge time. The counter counts with a reference frequency, and from the final counter output the now stretched time interval T + Tr can be found.

The time stretching factor is given by [22]:

$$K = \frac{I_1 - I_2}{I_2}$$

(3.1)

Figure 3.1: Analog Time Stretching [22]

This technique is now rarely used in favor of digital time stretching (e.g. vernier oscillators), because it is more difficult to implement the needed high precision current sources in small analog circuits [22].

## 3.2.2 Time to Voltage Conversion

This method also uses a capacitor C which is charged with a constant current during the unknown time interval, but instead of discharging it again, the voltage at the capacitor is held and digitized by an analog-to-digital converter [22]. The duration of the time interval is found by the digital output word. The performance depends greatly on the analog-to-digital converter.

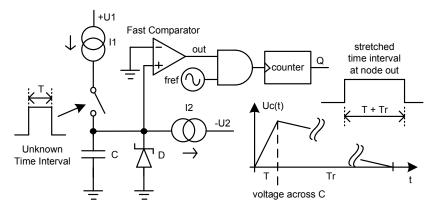

# 3.2.3 Tapped Delay Line

A line of matched delay elements is used to measure a time interval [22, 10, 12, 17]. A signal is applied to the first element when the start signal arrives, and it

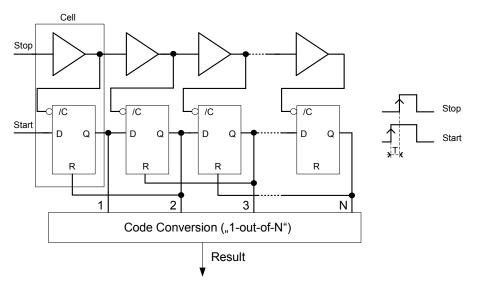

propagates from element to element until the end of the line. If all delay element outputs are evaluated after the unknown time interval T at the stop event, then Tcan be measured from the number of elements with a changed output state in this interval. Time T equals the propagation delay through a delay element multiplied with the number of elements. To get the absolute value of the time interval T the delay time of all elements have to be known exactly. Buffers or inverters are often used delay elements. A typical configuration is shown in Figure 3.2.

Figure 3.2: Tapped Delay Line [22]

The propagation delay changes with temperature, process parameters, or with the supply voltage. Stabilizing the delay over all operating conditions is not an easy task. Often the delay elements are embedded in a delay-locked-loop which stabilizes the propagation delay through the whole chain [17, 12]. Another possibility is to correct the measurement results digitally, without stabilizing the propagation delay. The needed reference can be gained by the measurement of a signal with a well known time duration. The resolution of this time measurement method is given by the delay of a single element.

## 3.2.4 Pseudo-Differential Delay Line

If two single ended delay lines are laid out parallel and an impulse is fed at the same time into both of the lines differentially, a pseudo-differential delay line can be built [20]. Differential flip flops can be used to monitor the state of the output nodes. The advantage is a better immunity against supply and substrate noise.

#### 3.2.5 Vernier Delay Line

The vernier delay line [22] is related to the vernier caliper or micrometer which is used to measure mechanical dimensions accurately. It uses two delay lines, one with slower delay elements (in this case latches, delay  $tp_a$ ), and a second one with slightly faster elements (here buffers with smaller delay  $tp_b$ ). The start signal is sent into the slow line, and the stop signal into the slightly faster line. Both signals propagate with a small delay difference of  $tp_a - tp_b$ , and so over time the faster travelling stop signal which was started later catches up with the slower start signal. Between opposite nodes of the two lines, so called arbiters (in this example also the latches) compare their states, and if a first transition occurs it remembers which node it happened at. Until the point in the line where the faster signal catches up the slower one, the outputs of the latches can be set to high, but behind it the propagation in the slower line is stopped. A thermometer code is generated at the output of the arbiters, from which the time interval between the start and stop signal can be measured. The circuit in Figure 3.3 translates the thermometer code to a single high output bit at the stopping position, because every activated latch resets the previous one. The resolution is  $tp_a - tp_b$ . The drawback is that for a longer time interval a huge amount of delay elements are needed. The increase in resolution is paid with increased complexity. Also a well defined delay difference has to be maintained.

Figure 3.3: Vernier Delay Line [22]

## 3.2.6 Vernier Oscillators

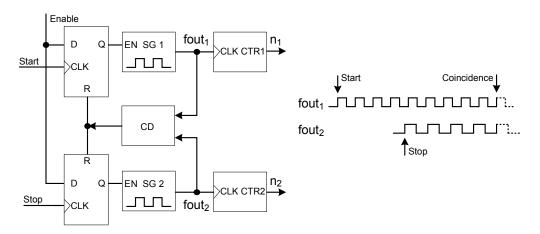

Vernier oscillators (Figure 3.4) [2, 23, 22] offer increased resolution like a vernier delay line, but with less area needed. They also utilize the vernier scale like the vernier delay line, but instead of a large amout of delay elements in a line they use two oscillators with a small output frequency difference  $fout_1 - fout_2$  to measure the unknown time interval. The start signal enables the first oscillator with a defined output signal phase state, and the stop signal the second oscillator with the same start phase state as the first one. Because both oscillators are started at another point in time, their output signal phase states are not equal; but because of the slightly different output frequencies, the phase difference between both outputs varies over time and at one point this difference will get zero. How much the phase difference does change with every output period of the oscillators is controlled by the output signals of the oscillators, and if they reach the same output phase state, then both oscillators are stopped immediately. At both oscillator outputs a counter counts the output periods until the coincidence.

From both counter values the unknown time interval is derived [22]. The following equation ignores the quantization error:

$$T = (n_1 - n_2) \cdot T_1 + (n_2 - 1) \cdot r \tag{3.2}$$

with  $n_1, n_2$ ...counter output after measurement  $T_1...\frac{1}{fout_1}, T_2...\frac{1}{fout_2}$

The resolution of this measurement method is  $r = T_1 - T_2$ . Building two oscillators with a stable and only small output frequency difference is a challenge. Additional area is needed, if calibration effort has to be done.

# 3.2.7 Pulse Shrinking

An impulse with a duration of the unknown time interval is injected into a ring of pulse shrinking elements. Every time the impulse has passed the complete ring

Figure 3.4: Vernier Oscillator Time Interval Measurement Method [22]

and starts a new cycle, its impulse width is shrunk by a certain and well defined amount. So with every cycle the width decreases, and subsequently the impulse fades away. A counter counts the number of full cycles the initial impulse does travel through the shrinking line until it disappears. From the counter value the initial impulse width can be derived [24].

# 3.2.8 Ring Oscillator

This architecture is related to the tapped delay line [22]. Examples for papers which use this kind of TDC setup are [16, 18, 11, 19, 13, 15]. An advantage is, that the inverters are scaled very well with the used technology.

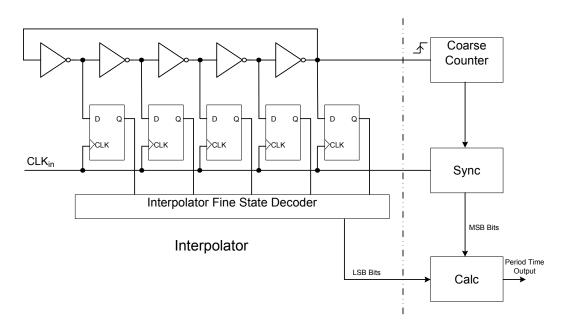

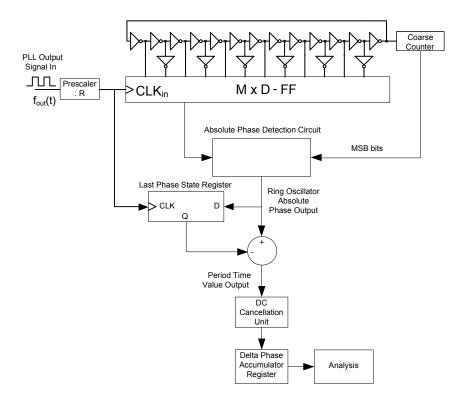

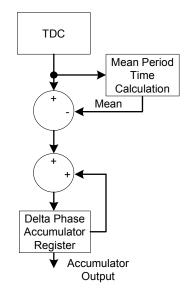

# 3.3 Implementation

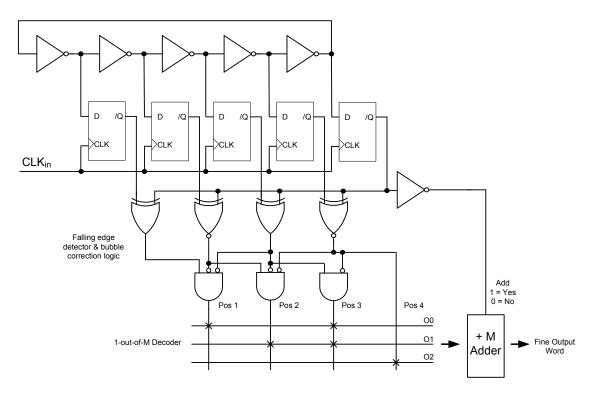

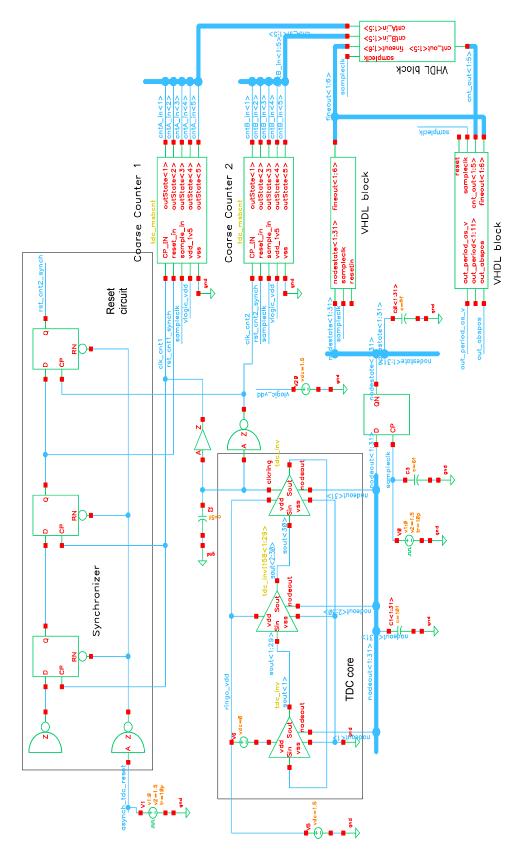

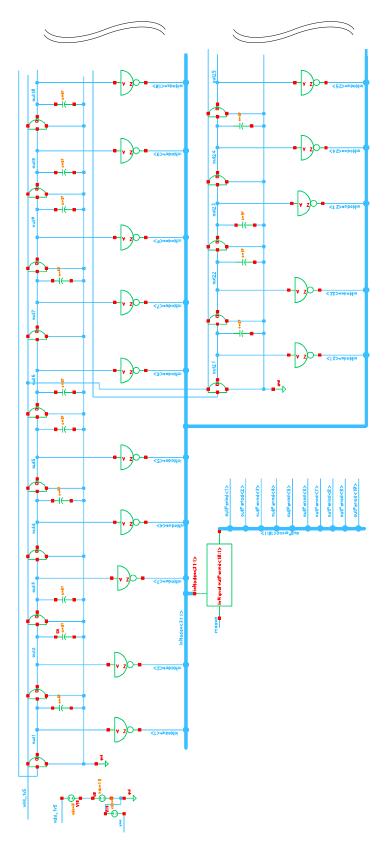

A ring oscillator architecture is used for the time-to-digital conversion in this diploma thesis. The TDC block (Figure 3.5) is composed of the ring oscillator, two coarse counters, the absolute phase detection circuit, and a calculation unit. The TDC unit measures the time interval between two rising edges of the  $CLK_{in}$  input signal.

Figure 3.5: Used TDC Unit System Overview

### 3.3.1 Interpolator

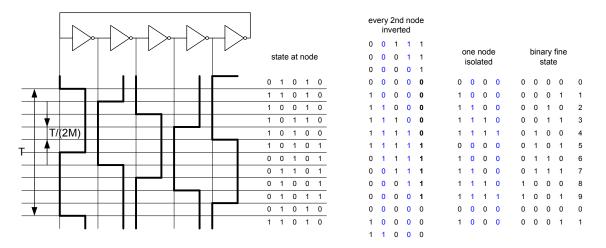

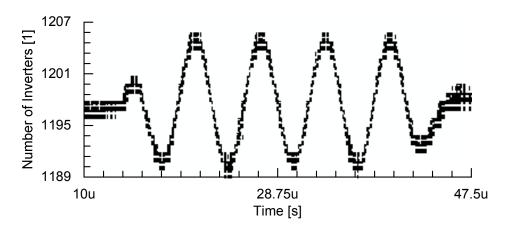

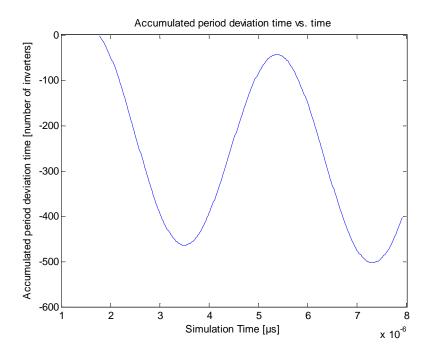

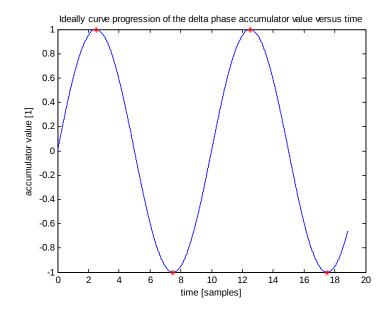

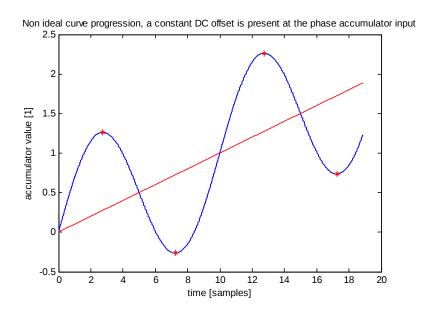

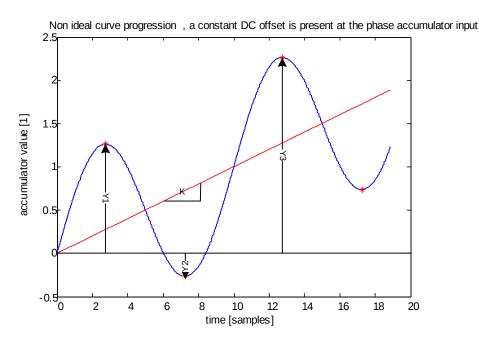

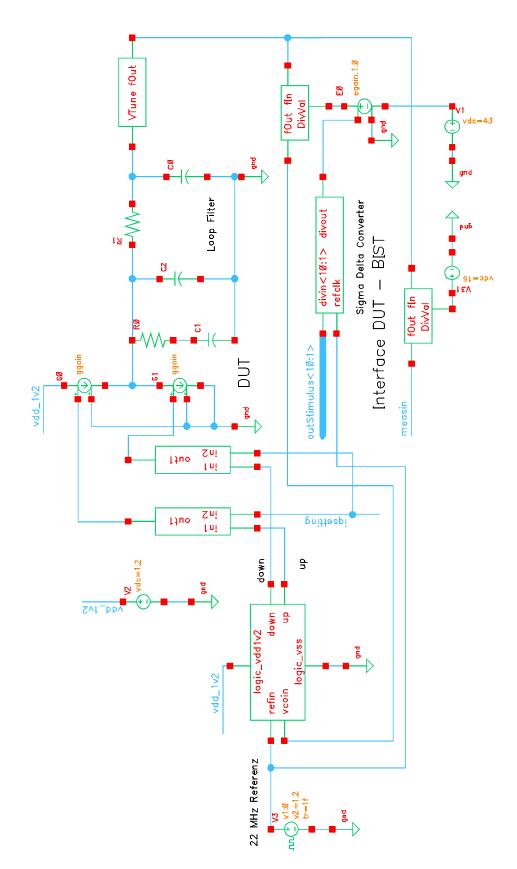

The interpolator (ring oscillator) allows the measurement of a time interval with a resolution equal to the typical inverter delay  $(=t_d)$ . If the ring uses M inverters then the longest time interval which can be measured without a coarse counter is  $2 \cdot M \cdot t_d$ . After this time the state of the ring oscillator repeats and is ambiguous. All possible states of a example ring oscillator are shown in Figure 3.6. In the figure every second node of the oscillator is drawn inverted, because this is also done in the circuit.

The differential nonlinearity (DNL) and the integral nonlinearity (INL) [14] depend on the statistic dispersion of the delays of the single inverters from the typical and specified delay. One can build a very high resolution TDC, but if the delay from the inverters is not very well controlled, then the DNL and INL errors inhibit the successful usage of the high resolution. Additional errors are created if the inverters do not have the same propagation delay for both signal transitions. The power supply of the ring oscillator must be filtered, to be as noise free as possible, to obtain a time constant propagation delay.

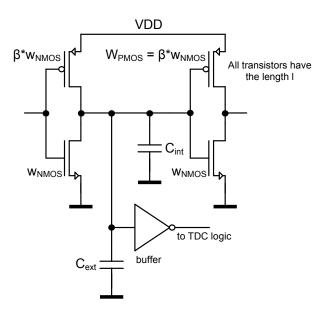

**Determination of the TDC Core Inverter Size** The inverter (Figure 3.7) [25] delay depends on the load capactiance at the output, its transistor sizes, and

Figure 3.6: Possible Interpolator Fine States

from the process parameters [26]. The load capacity can be divided into a part  $C_{int}$ , which consists of the input capacity of the next inverter in the line, and a second part  $C_{ext}$ .  $C_{ext}$  consists of parasitic capacitors from the output node to GND [25]. Two important examples for  $C_{ext}$  are the capacitance from the path which is used to couple the state out from every ring node, and also the input capacitance of the output buffer element. The buffers minimize adverse effects from the output back to the ring oscillator.

Figure 3.7: TDC Ring Oscillator Output Node Capacity Model [25]

Main part of  $C_{int}$  are both gate-source capacities of the inverter transistors. The

length of the transistors is minimized to maintain a very low delay. To cancel the reduced mobility in the PMOS transistor its size  $W_{PMOS}$  was selected beta times wider than the size  $W_{NMOS}$  of the NMOS counterpart. The value of  $\beta$  was chosen that the propagation delays for both transitions are identical.

$C_{int}$  can be approximated by (see [26]):

$$C_{int} = Cgs_{NMOS} + Cgs_{PMOS} \sim W_{NMOS} \cdot L \cdot C_{ox} + W_{PMOS} \cdot L \cdot C_{ox}$$

(3.3)

$$C_{int} \sim L \cdot C_{ox} \cdot (W_{NMOS} + \beta \cdot W_{NMOS}) \sim L \cdot C_{ox} \cdot W_{NMOS} \cdot (1+\beta)$$

(3.4)

$C_{int}$  is proportional to the width of the transistors, and also the current through the transistor  $I_{ds}$  in both operating regions [3].

"Linear" Region:

$$I_{ds} = \frac{K \cdot W}{L} \cdot \left[ (U_{gs} - U_{th}) \cdot U_{ds} - (\frac{U_{ds}^2}{2}) \right]$$

(3.5)

"Saturation" Region:

$$I_{ds} = \frac{K \cdot W}{2 \cdot L} \cdot (U_{gs} - U_{th})^2$$

(3.6)

If  $C_{ext}$  were 0, an increased width of the transistors would increase the output current and the output capactiance by the same factor. In this case the propagation delay does not change, but the power dissipation is increased. This is discussed in [25].

If  $C_{int}$  is 0, but  $C_{ext}$  is accounted then  $C_{ext}$  does not depend on the width of the transistors in the inverter, but with increased width more current is available

for charging and discharging of  $C_{ext}$ . So in this case, the propagation delay is inversely proportional to the width of the transistors. In the practical realization both  $C_{int}$  and  $C_{ext}$  are non zero.

For very small transistors  $C_{ext}$  is big in comparision to  $C_{int}$ . If the width is increased at this point the propagation delay can be decreased by a large amount. With the growing width of the transistors  $C_{int}$  becomes dominant in comparision to  $C_{ext}$ , and so the possible propagation delay decreases per width step do become smaller and smaller [25]. Only the dissipated energy in the ring oscillator increases with every step at the end.

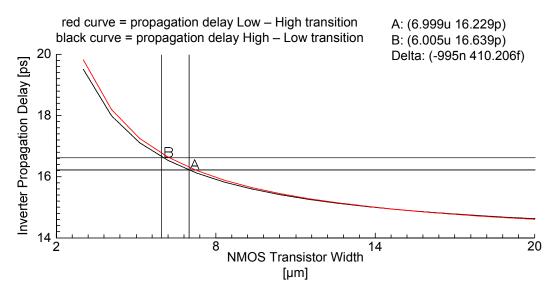

This is a tradeoff between the delay and the power dissipation. The width of the transistors was selected in a way that a short delay was reached, but without increasing the power consumption of the ring oscillator too much. A plot of the propagation delay versus the NMOS transistor width is presented in Figure 3.8.

Figure 3.8: NMOS Width Inverter Propagation Delay Dependence

**Dissipated Energy per Node** While the inverter output node is charged fully from GND to VDD, as much power is dissipated in the PMOS transistor as is stored in the output capactiance at the end [27]. This dissipated energy can be found by

$$C_{node} = C_{int} + C_{ext} \tag{3.7}$$

$$W_{dis} = \frac{1}{2} \cdot V dd^2 \cdot C_{node}$$

(3.8)

At the end of a charge-recharge cycle, the capacitor is discharged again by the NMOS transistor and the whole stored energy in  $C_{node}$  is dissipated again. So in a single cycle the dissipated energy is [25]

$$Wdis_{cycle} = 2 \cdot W_{dis} = vdd^2 \cdot C_{node}$$

(3.9)

If f cycles occur every second, that means the node is charged and discharged with a frequency of f, then the whole dissipated energy is

$$Wdis_{all} = vdd^2 \cdot C_{node} \cdot f \tag{3.10}$$

This equation does not account for crowbar and leakage currents.

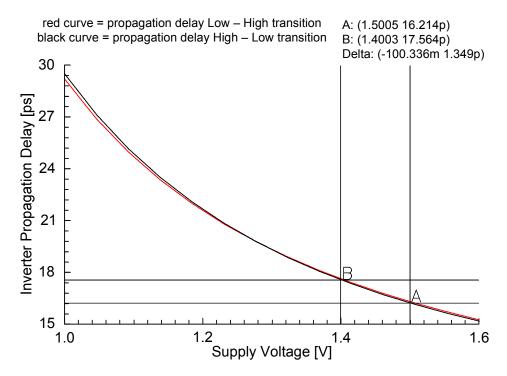

In terms of noise, the effect of the supply voltage on the propagation delay of the delay elements is unwanted [6], because it introduces small variations of the delay over time. In terms of calibrating the delay of the elements by variation of the supply voltage this effect is positive. In this way, delay changes because of process variations or the temperature dependence can be canceled. Figure 3.9 shows the effect of the supply voltage on the delay.

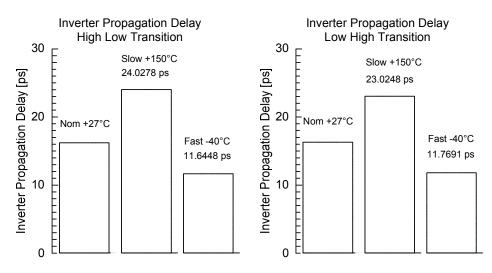

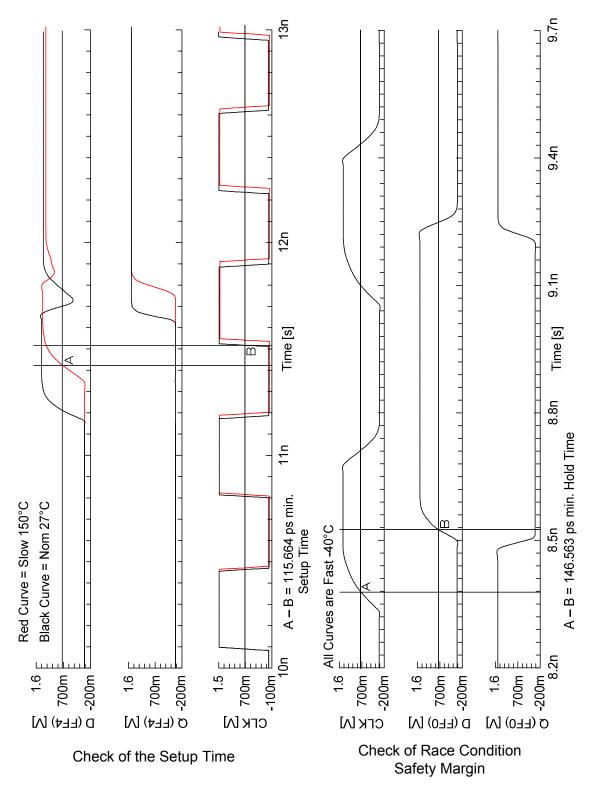

To find out how big or how small the propagation delay of an inverter could be, a corner simulation was done with minimum and maximum temperatures, and slow and fast process parameters (Figure 3.10).

The positive result is, that the propagation delay for both transitions stays almost the same, also over different temperatures or process parameters, as long as both transistors behave equally. Bad is that the delays have a very strong dependence on the temperature and process parameters. Care has to be taken on this topic, because the result of the bandwidth measurement also depends on this delay.

Figure 3.9: Supply Voltage Inverter Propagation Delay Dependence

Figure 3.10: Inverter Propagation Delay Corner Simulation

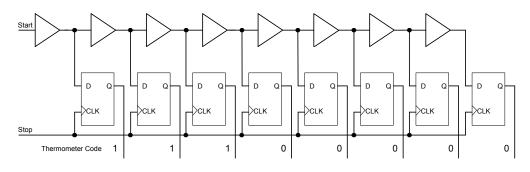

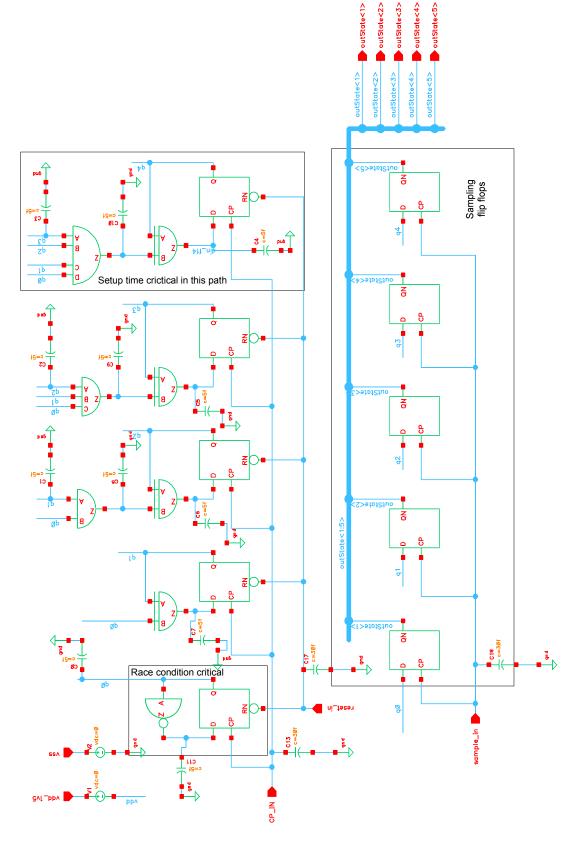

**Ring Oscillator current State Sampling** Every rising edge of the  $CLK_{in}$  signal triggers M rising edge triggered flip flops [11] at the same time, and a snapshot of the current ring oscillator state is done. If this does not happen concurrent for every node code bubbles can occur later in the thermometer code. Metastability can occur, because the  $CLK_{in}$  signal is asynchronous to the signals from the oscillator nodes, and so the setup and hold times of the flip flops can be violated any time [28, 29]. If this happens the propagation delay of the flip flop is greatly increased, and how much is a random process. The probability for a metastable state is minimized by using flip flops with a small setup and hold time. Because in this application the time duration between sampling the ring oscillator state is high, a metastable state do not introduce a big problem. This duration is high enough to allow the digital TDC logic to finish its work, also when a metastable state had occurred.

Additionally the metastable state will always occur at the current ring oscillator transient position which we want to obtain. If the result is altered by the metastable state a big error is not introduced to the fine result. Master slave flip flops are used for the sampling, and to be sure that all devices sample at the same time, and the propagation delay is equal, only one type of flip flop was used. Also the signal paths from the ring oscillator to the flip flops, and the flip flop layout has to be done carefully.

**Current Fine Position Decoding** In the first half of the possible ring oscillator states (Figure 3.6) it looks like a falling edge propagates through the inverter chain, and in the second half a rising edge. To get the fine position in the ring, the correct edge has to be located. If a single node of the oscillator is viewed isolated from all the other nodes, you get two almost equal tables for all the other nodes (one is the inversion of the other), depending on the isolated node. If in one case (e.g. when the isolated node is high) all other nodes are inverted, we now get two equal tables. In principle we have only M different states with M inverters in the chain, one time with the isolated node at high, and one time at low. This reduces the needed logic, and also now only one type of edge propagates through the inverter chain for both oscillation periods. This allows the use of NAND gates for the edge detection and for a single bubble correction, which increases the reliability of the whole circuit. The interpolator circuit is shown in Figure 3.11. A likewise decoding method is illustrated in [12, 13].

Figure 3.11: Interpolator Fine Decoder Logic

Every edge position in the interpolator has its own NAND gate, which checks if the left neighbour node is high, and that its input node, and the right neighbour are both low (bubble correction). Only in this case does the NAND gate output get high, and mark the current ring oscillator state. The activated output line is decoded by a 1 - out - of - M decoder, and a digital word for the current state is created. If the oscillator is in the second period, then an adder adds M to this word, otherwise the value is not altered. The XOR gates in front of the edge and bubble correction NAND gates do the inversion of all of the first M - 1 nodes for one of the two states of the isolated node. All the logic after the sample flip flops is later implemented in VHDL.

## 3.3.2 Coarse Counters

Because the measurement time interval exceeds the period time of the ring oscillator, an additional coarse counter is needed. At the first view a single counter which counts the number of full periods of the oscillator is enough. The counter value can always be increased by 1 if the output of the last inverter from the ring oscillator changes its state in every second run through the ring oscillator. So when the interpolator state again equals the state at the beginning, after a full period of oscillation, we do not lose this information because of the increased coarse counter value. Every increase in the counter value equals  $2 \cdot M$  inverters which were propagated.

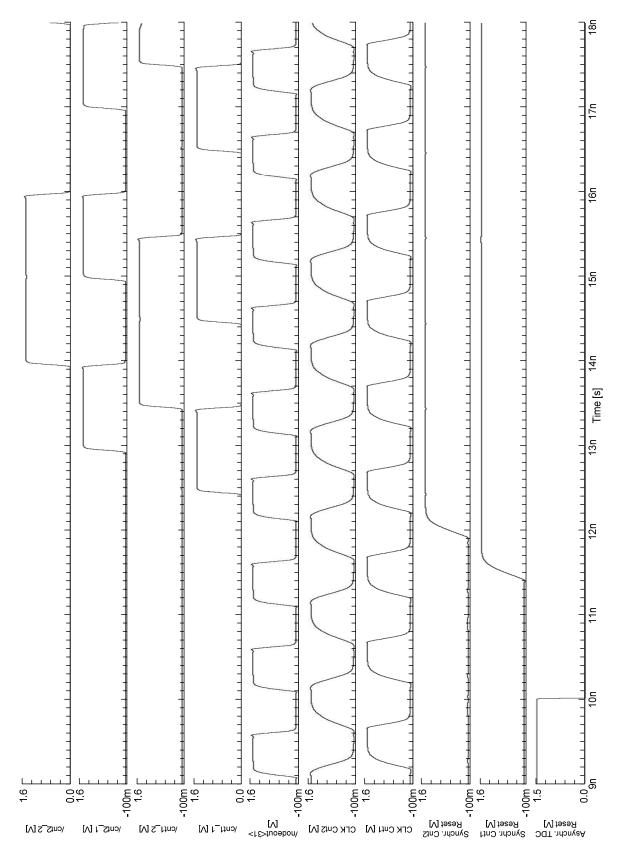

After this single counter is triggered, it needs time to settle again. If the second edge of the  $CLK_{in}$  signal arrives in that moment, no current counter state would be ready to read out, and so a single counter is not enough. Again we do not know when the second edge will arrive. Two counters can be used as a solution, which are triggered with a 180 degree phase shift [12, 17, 30]. So one counter settles while the other one is ready for readouts. The phase shift is done with a buffer instead of an inverter in one of both signal paths to the counters. At the rising edge of the  $CLK_{in}$  signal both counter states are sampled by D-flip flops. To select which counter is ready for readout first the fine position in the ring oscillator is decoded, and from this position now the decision is made.

Figure 3.12 shows an example of a 7-stage ring oscillator with both course counters. The same concept is applicable to the 31-stage oscillator. After the reset both counters start with a state of zero, and with the first rising edge at the counter control node of the ring counter A is triggered at state 7. Until this state, the counter can be used for readout, but to be sure that a stable value is read again already one state before counter B is used as the data source. The same is true for the next edge for counter A in state 0. Here again one fine state before the trigger event the change of the data source is done. If in fine state 13 counter B is used instead of counter A one can see by comparision between the two counters that here counter B leads counter A by a value of 1. To correct this, one is substracted from the read value from the counter B. For all other fine states no correction has to be done, and a continuous and steady readout can be accomplished with this two counters.

**Initialization of Two Coarse Counters** The relationship between both coarse counter values must stay correct the whole time, otherwise an error at the TDC output up to  $2 \cdot M$  inverters is possible, and so care has to be taken to reset both counters in a correct way. To be sure that after the release of the asynchronous reset signal both counters have the correct relationship a synchronizer consisting of two flip flops, and a additional flip flop for the second counter is used. The first

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         1         0         0         1         0         0         1         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 |

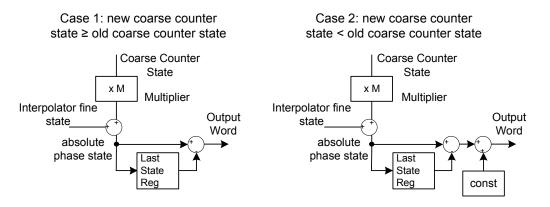

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|