Diploma Thesis DA 708

# Power Metering with Hall-based Current Sensor

Armin Wahl

Institute of Electronics Graz University of Technology Head: Univ.-Prof. Dipl.-Ing. Dr.techn. Wolfgang Bösch

in Cooperation with Infineon Technologies Austria AG

Supervisor: Ass.Prof. Dipl.-Ing. Dr.techn. Gunter Winkler External Supervisor: Dipl.-Ing. Thomas Herndl

Graz, March 2013

# **Statutory Declaration**

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

Armin Wahl

# Eidesstattliche Erklärung

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommene Stellen als solche kenntlich gemacht habe.

Armin Wahl

# Abstract

As a consequence of the growing energy demand and increased use of renewable energy sources a smart control for an efficient utilization of the grid is becoming more and more important. Unfortunately, local generation of renewables through photovoltaics or wind power can not be controlled directly, nor can energy be stored in large quantities. This problem can be solved by continuously adapting the demand to the availability of electrical power provided in the grid. By means of Wireless Sensor Networks (WSNs), whose nodes measure the power consumption of the respective consumers (lighting units, washing machines, etc.), the grid can be made "smart" enough to distribute the power provided in the grid.

The problem is that energy management systems which ensure an economical utilization of the grid are expensive and only affordable for industry and large scale commercial customers. The objective of this thesis is the development of a cost-efficient low-power power metering unit of small size, to enable integration in home appliances, suited for application in households as well as in small commercial buildings. The thesis is part of a project referred to as SmartCoDe<sup>1</sup> with a focus on precisely this challenge.

The development of the power metering unit is carried out by evaluating the architecture of a sensor node which enables cost-efficient low-power power measurement with little hardware. These specific requirements were fulfilled by using a test chip of an innovative current sensor TLI4970 and a transceiver Application-Specific Integrated Circuit (ASIC), both developed by Infineon Technologies AG.

<sup>&</sup>lt;sup>1</sup>EU Project within the 7<sup>th</sup> Framework Program (CT-2009-247473)

# Kurzfassung

Im Zuge des ständig wachsenden Energiebedarfs und dem zunehmenden Einsatz erneuerbarer Energien gewinnt eine intelligente Regelung zur effizienten Netzauslastung immer mehr an Bedeutung. Bedauerlicherweise kann die lokale Erzeugung elektrischer Energie aus erneuerbaren Ressourcen wie Photovoltaik oder Windanlagen nicht direkt beeinflusst werden, noch kann sie effizient in großen Mengen gespeichert werden. Durch eine Anpassung der Nachfrage an die zur Verfügung stehenden Leistung kann dieses Problem gelöst werden. Mit Hilfe von Wireless Sensor Networks (WSNs), dessen Sensorknoten den Leistungsverbrauch der jeweiligen Verbraucher (Beleuchtung, Waschmaschine, ...) messen, kann das Stromversorgungsnetz "'intelligent"' genug gemacht werden um die zur Verfügung stehende Leistung bedarfsgerecht zu verteilen.

Das Problem ist, dass Systeme, die eine ökonomische Auslastung des Energieversorgungsnetzes gewährleisten meist teuer und somit nur für Großkunden aus Wirtschaft und Industrie erschwinglich sind. Ziel dieser Arbeit ist es nun, ein kostengünstiges miniaturisiertes Leistungsmessgerät mit geringem Stromverbrauch zu entwickeln, das eine Integration in Haushaltsgeräte ermöglicht und für den Einsatz in Privathaushalten sowie kleineren öffentlichen Gebäuden geeignet ist. Diese Arbeit ist Teil eines Projektes mit dem Namen SmartCoDe<sup>2</sup>, das sich mit genau dieser Herausforderung beschäftigt.

Im Laufe des Entwicklungsprozesses wird eine Architektur eines Sensorknotens evaluiert, die mit geringem Hardwareaufwand, geringem Stromverbrauch und hohem Miniaturisierungspotential eine Leistungsmessung ermöglicht. Diese speziellen Anforderungen des Leistungsmessgerätes werden mit einem Testchip des innovativen Stromsensors TLI4970 und einem Transceiver Application-Specific Integrated Circuit (ASIC), beide entwickelt von Infineon Technologies AG, erfüllt.

<sup>&</sup>lt;sup>2</sup>EU Projekt innerhalb des 7<sup>th</sup> Framework Program (CT-2009-247473)

# Acknowledgement

First I would like to thank Ass.Prof. Dipl.-Ing. Dr.techn. Gunter Winkler, member of the Institute of Electronics at the Graz University of Technology, for supervising my thesis as well as for his outstanding support.

Furthermore, I would like to thank Dipl.-Ing. Gerald Holweg, head of the Contactless and Radio Frequency Exploration (CRE) Department of Infineon Technologies Austria AG, for giving me the opportunity to write my thesis in a practical environment.

Special thanks to my supervisor Dipl.-Ing. Thomas Herndl at Infineon Technologies Austria AG for his great technical support. I would also like to thank Dipl-Ing. Günter Hofer and Dipl.-Ing. Johannes Schweighofer for their outstanding technical support, and to my colleagues at CRE for the positive and creative work atmosphere and for plenty of amusing moments.

Above all I would like to thank my parents Klaudia and Karl Wahl for giving me the opportunity to complete an academic education and for their wonderful support during my whole life.

Armin Wahl

# Contents

| Li | List of Abbreviations viii |         |                                                              |     |  |  |  |

|----|----------------------------|---------|--------------------------------------------------------------|-----|--|--|--|

| Li | st of                      | Figures | 5                                                            | x   |  |  |  |

| Li | st of                      | Tables  |                                                              | xii |  |  |  |

| 1  | Intro                      | oductio | n                                                            | 1   |  |  |  |

|    | 1.1                        | Motiva  | ation, the SmartCoDe Project                                 | 1   |  |  |  |

|    | 1.2                        | Object  | tive of this Thesis                                          | 3   |  |  |  |

|    | 1.3                        | Thesis  | Outline                                                      | 3   |  |  |  |

| 2  | Fun                        | damen   | tals of Power Calculation                                    | 5   |  |  |  |

|    | 2.1                        | Hall Et | ffect, Hall-based Current Sensor                             | 5   |  |  |  |

|    | 2.2                        | Mathe   | matical Basics of Power Metering                             | 7   |  |  |  |

|    |                            | 2.2.1   | Terms and Definitions                                        | 7   |  |  |  |

|    |                            | 2.2.2   | Power at AC Current Voltage                                  | 9   |  |  |  |

|    | 2.3                        | Sampl   | ling and Quantization                                        | 14  |  |  |  |

|    |                            | 2.3.1   | Sampling of Continuous Signals, Sampling Theorem             | 14  |  |  |  |

|    |                            | 2.3.2   | Quantization in Value Domain                                 | 15  |  |  |  |

|    | 2.4                        | Power   | Calculation from a Digital Signal                            | 15  |  |  |  |

| 3  | Sys                        | tem Ov  | verview of Power Metering Unit                               | 17  |  |  |  |

|    | 3.1                        | Syster  | m Architecture                                               | 17  |  |  |  |

|    | 3.2                        | Currer  | nt and Voltage Sensor, Test Chip of the TLI4970              | 19  |  |  |  |

|    |                            | 3.2.1   | Pin Configuration                                            | 21  |  |  |  |

|    |                            | 3.2.2   | Functional Description                                       | 22  |  |  |  |

|    |                            | 3.2.3   | Single-wire Connection and Operation                         | 23  |  |  |  |

|    |                            | 3.2.4   | Flowchart for Current and Voltage Measurement by Single-wire | 24  |  |  |  |

|    |                            | 3.2.5   | Mapping of the Current Value                                 | 26  |  |  |  |

|    |                            | 3.2.6   | Mapping of the Voltage Value                                 | 27  |  |  |  |

|    |                            | 3.2.7   | Electrical Characteristics                                   | 27  |  |  |  |

|    | 3.3                        | Multi-c | channel Transceiver, CHOSeN SmartTransceiver                 | 28  |  |  |  |

|    |                            | 3.3.1   | Overview                                                     | 28  |  |  |  |

|    |       | 3.3.2 Protoc  | col Processo   | or                |           |         |        |       |       |       |      |    |   | 29 |

|----|-------|---------------|----------------|-------------------|-----------|---------|--------|-------|-------|-------|------|----|---|----|

|    |       | 3.3.3 Power   | r Manageme     | ent Unit          |           |         |        |       |       |       |      |    |   | 30 |

|    |       | 3.3.4 SPI In  | iterface, Sing | gle-wire (        | Connect   | ion .   |        |       |       |       |      |    |   | 33 |

|    |       | 3.3.5 Numb    | er Represer    | ntation .         |           |         |        |       |       |       |      |    |   | 33 |

|    |       | 3.3.6 Electr  | ical characte  | eristics .        |           |         |        |       |       |       |      |    |   | 35 |

| 4  | Hare  | lware Design  | of Power N     | <i>l</i> letering | Unit      |         |        |       |       |       |      |    |   | 36 |

|    | 4.1   | Schematic .   |                |                   |           |         |        |       |       |       |      |    |   | 36 |

|    | 4.2   | Capacitive Vo | oltage Divide  | ər                |           |         |        |       |       |       |      |    |   | 40 |

|    |       | 4.2.1 Dimer   | nsioning the   | Voltage I         | Divider . |         |        |       |       |       |      |    |   | 40 |

|    |       | 4.2.2 Time-   | dependent E    | 3ehavior          |           |         |        |       |       |       |      |    |   | 43 |

|    |       | 4.2.3 Simula  | ation Result   | S                 |           |         |        |       |       |       |      |    |   | 45 |

|    | 4.3   | Instrumentati | on Amplifier   | ·                 |           |         |        |       |       |       |      |    |   | 52 |

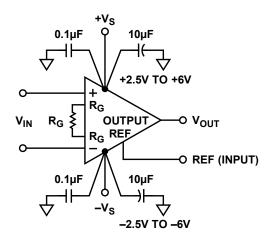

|    |       | 4.3.1 Basic   | Connection     |                   |           |         |        |       |       |       |      |    |   | 52 |

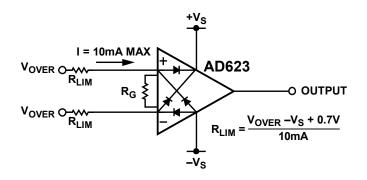

|    |       | 4.3.2 Input   | Protection     |                   |           |         |        |       |       |       |      |    |   | 53 |

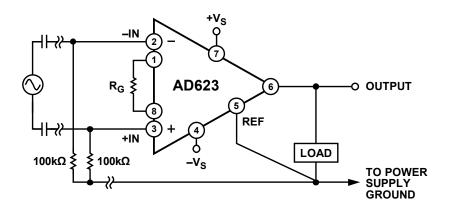

|    |       | 4.3.3 Grour   | nd Returns fo  | or Input E        | Bias Cur  | rents v | vith A | AC-co | ouple | ed In | outs | 5  |   | 54 |

| 5  | Soft  | ware Design   | of Power M     | letering l        | Unit      |         |        |       |       |       |      |    |   | 55 |

|    | 5.1   | Firmware Arc  | hitecture .    |                   |           |         |        |       |       |       |      |    |   | 55 |

|    |       | 5.1.1 Active  | Power Calo     | culation          |           |         |        |       |       |       |      |    |   | 60 |

|    |       | 5.1.2 Appar   | ent Power C    | Calculatio        | n         |         |        |       |       |       |      |    |   | 62 |

|    | 5.2   | Extracting So | uare Roots     | by Heror          | n's Meth  | od      |        |       |       |       |      |    |   | 66 |

|    | 5.3   | Implementati  | on of Multip   | lication A        | lgorithm  |         |        |       |       |       |      | •• |   | 67 |

| 6  | Меа   | surements w   | ith Power N    | letering          | Unit      |         |        |       |       |       |      |    |   | 70 |

|    | 6.1   | Measuremen    | t Condition    |                   |           |         |        |       |       |       |      |    |   | 70 |

|    | 6.2   | Measuremen    | t Results .    |                   |           |         |        |       |       |       |      |    | • | 71 |

| 7  | Con   | clusion       |                |                   |           |         |        |       |       |       |      |    |   | 74 |

|    | 7.1   | Summary and   | d Results .    |                   |           |         |        |       |       |       |      |    | • | 74 |

| Α  | Арр   | endix         |                |                   |           |         |        |       |       |       |      |    |   | 76 |

|    | A.1   | Small PCB of  | the Power      | Metering          | Unit      |         |        |       |       |       |      |    |   | 76 |

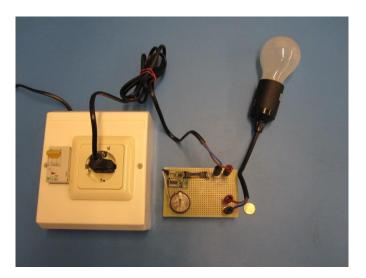

|    | A.2   | AC Plug Dem   | onstrator .    |                   |           |         |        |       |       |       |      |    |   | 77 |

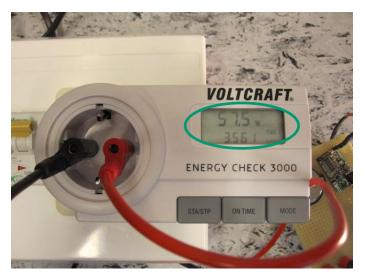

|    | A.3   | AC Plug Dem   | onstrator - I  | Results           |           |         |        |       |       |       |      |    |   | 78 |

|    | A.4   | LED Module    |                |                   |           |         |        |       |       |       |      |    |   | 79 |

| Bi | bliog | raphy         |                |                   |           |         |        |       |       |       |      |    |   | 80 |

|    |       |               |                |                   |           |         |        |       |       |       |      |    |   |    |

# **List of Abbreviations**

| AC    | Alternating Current                            |

|-------|------------------------------------------------|

| ADC   | Analog to Digital Converter                    |

| AMUX  | Analog MUX                                     |

| ASIC  | Application-Specific Integrated Circuit        |

| ASIP  | Application-Specific Instruction-set Processor |

| ASK   | Amplitude Shift Keying                         |

| DC    | Direct Current                                 |

| DIVT  | Dynamic Interrupt Vector Table                 |

| DSP   | Digital Signal Processor                       |

| ESR   | Equivalent Series Resistance                   |

| EUP   | Energy Using Product                           |

| FELV  | Functional Extra Low Voltage                   |

| FIFO  | First In, First Out                            |

| FSK   | Frequency Shift Keying                         |

| GPRAM | General Purpose RAM                            |

| HF    | High Frequency                                 |

| HVAC  | Heating, Ventilation, and Air Conditioning     |

| IO    | Input/Output                                   |

| ISM   | Industrial, Scientific and Medical             |

| LED   | Light-Emitting Diode                           |

| LSB   | Least Significant Bit                          |

| MUX   | Multiplexer                                    |

| PCB   | Printed Circuit Board                          |

| PFC   | Power Factor Correction                        |

| PMU   | Power Management Unit                          |

| PPU   | Protocol Processing Unit                       |

| PWM   | Pulse Width Modulation                         |

| RAM   | Random Access Memory                           |

| RF    | Radio Frequency                                |

| RISC  | Reduced Instruction-Set Computer               |

| ROM   | Read-Only Memory                               |

| RX   | Receiver                    |

|------|-----------------------------|

| SFR  | Special Function Register   |

| SOC  | System On Chip              |

| SPI  | Serial Peripheral Interface |

| SRAM | Static RAM                  |

| SRD  | Short-Range Devices         |

| TRX  | Transceiver                 |

| ТХ   | Transmitter                 |

| UHF  | Ultra-High Frequency        |

| WLB  | Wafer Level Ball Grid Array |

| WSN  | Wireless Sensor Network     |

# **List of Figures**

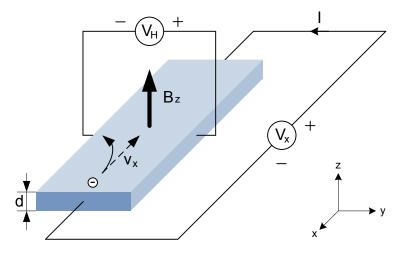

| 2.1  | Illustration of the Hall Effect                                            | 6  |

|------|----------------------------------------------------------------------------|----|

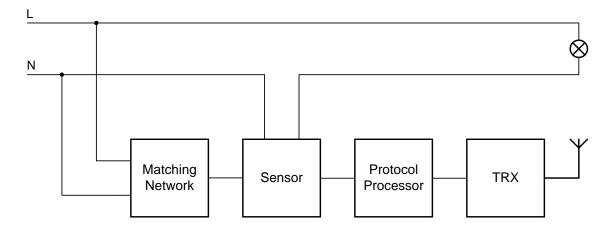

| 3.1  | Basic Block Diagram of the Power Metering Unit                             | 18 |

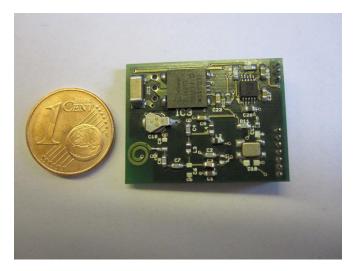

| 3.2  | Sensor in Comparison with 1 Cent Coin                                      | 20 |

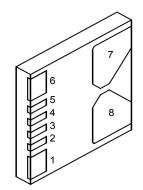

| 3.3  | Pin Configuration PG-TISON-8-1                                             | 21 |

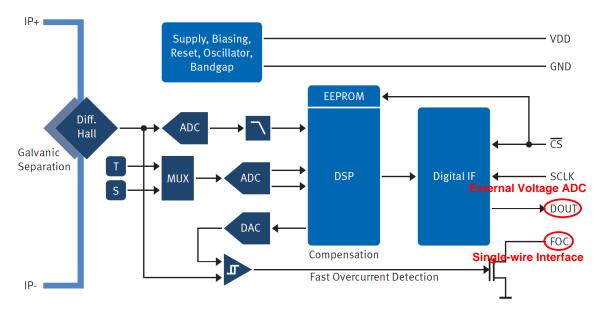

| 3.4  | Functional Block Diagram of the Current and Voltage Sensor                 | 22 |

| 3.5  | Single-wire Connection of the Current and Voltage Sensor                   | 23 |

| 3.6  | Current and Voltage Measurement Sequence                                   | 24 |

| 3.7  | Captured Current and Voltage Measurement Sequence                          | 26 |

| 3.8  | Block Diagram of the Transceiver                                           | 28 |

| 3.9  | Power Domains of the Transceiver                                           | 31 |

| 3.10 | Power States of the Transceiver                                            | 32 |

| 3.11 | Three- and Four-wire SPI of the Transceiver                                | 33 |

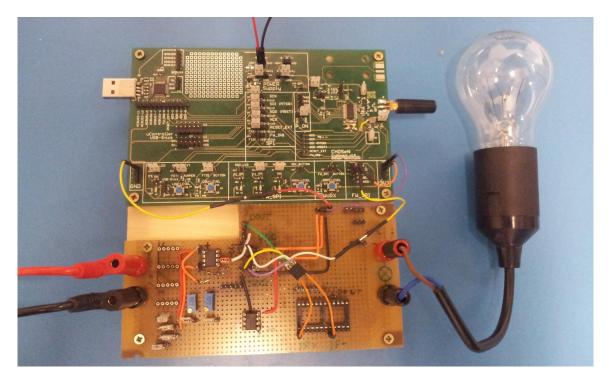

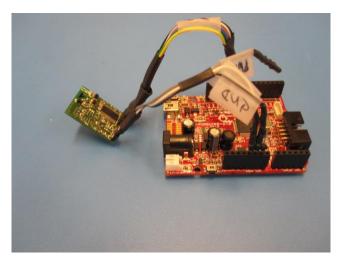

| 4.1  | Setup of the First Prototype                                               | 37 |

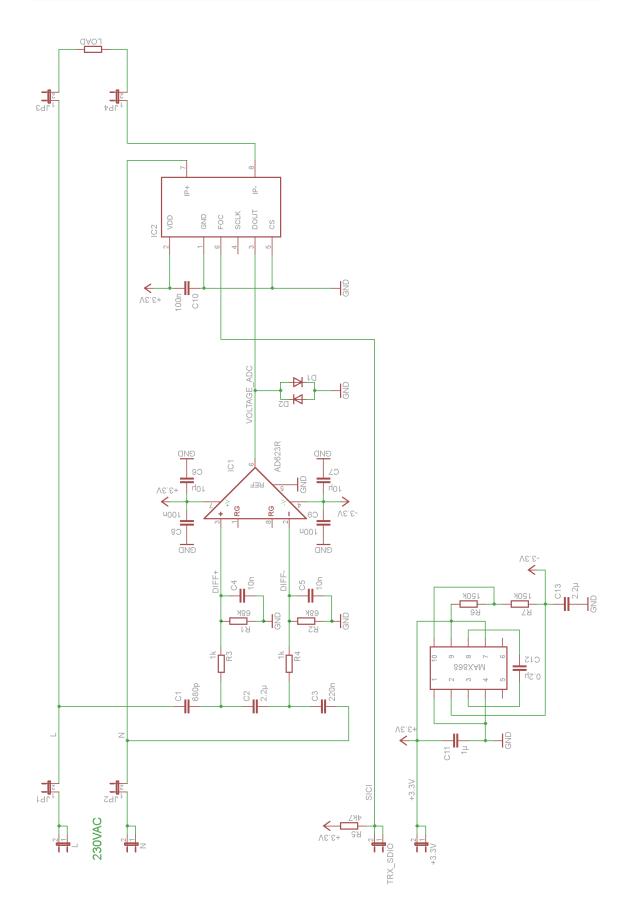

| 4.2  | Full Schematic without Transceiver                                         | 39 |

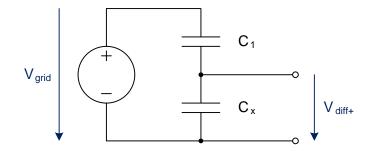

| 4.3  | Series Connection of $C_1$ and $C_x$                                       | 41 |

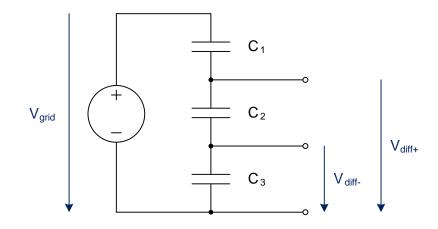

| 4.4  | Series Connection of $C_1$ , $C_2$ and $C_3$                               | 42 |

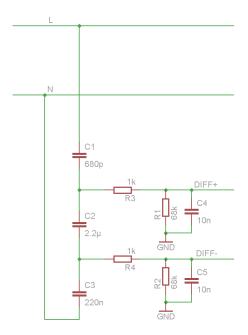

| 4.5  | Schematic of the Capacitive Voltage Divider                                | 44 |

| 4.6  | Legend for Simulation                                                      | 45 |

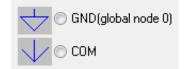

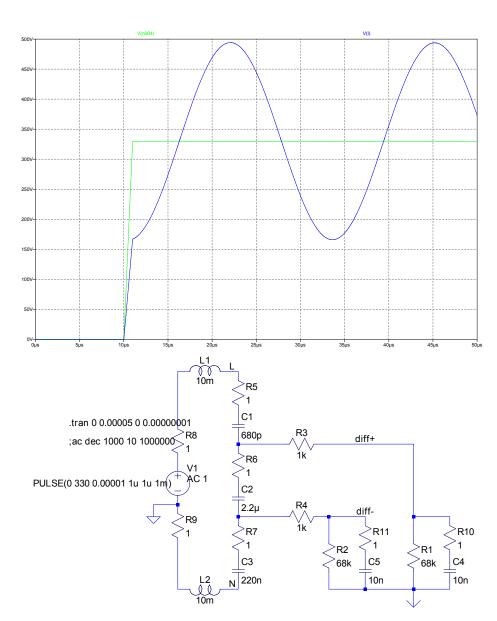

| 4.7  | Transient Simulation with Sine                                             | 46 |

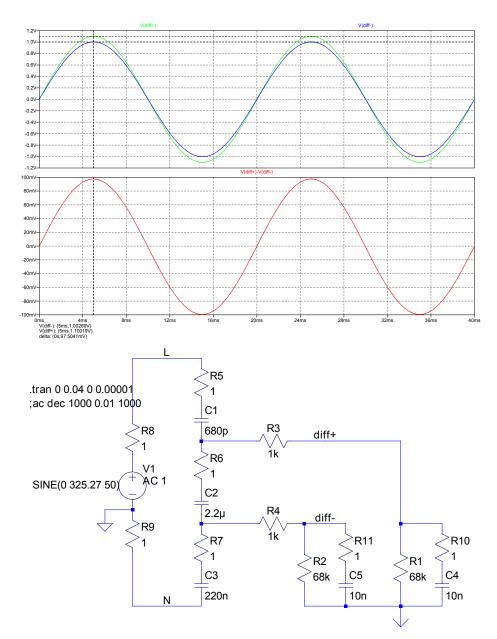

| 4.8  | Transient Simulation with Sine (L and N interchanged)                      | 47 |

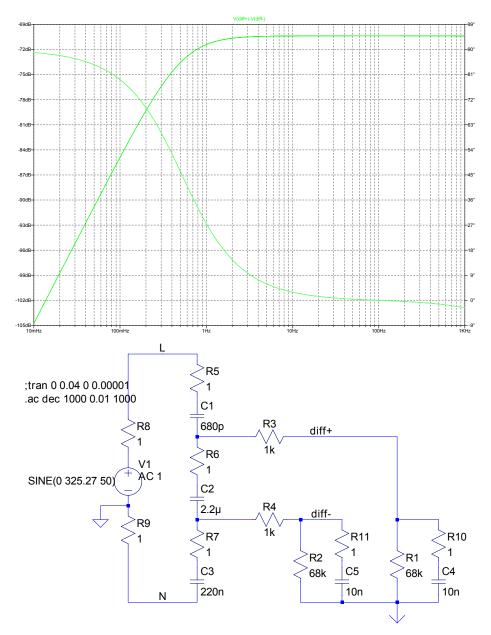

| 4.9  | Small Signal AC Simulation                                                 | 48 |

| 4.10 | Transient Simulation of Equivalent Circuit                                 | 49 |

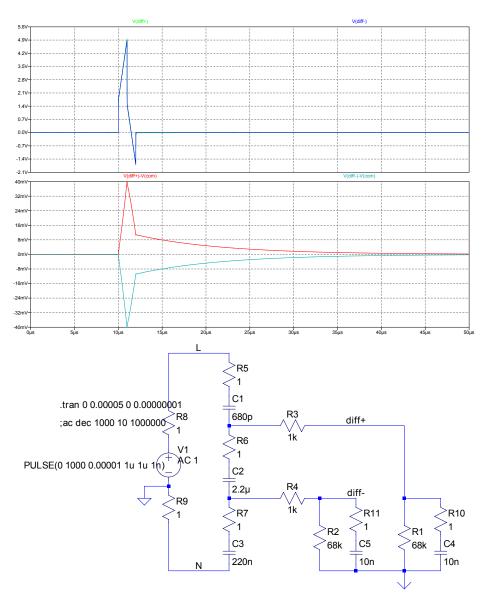

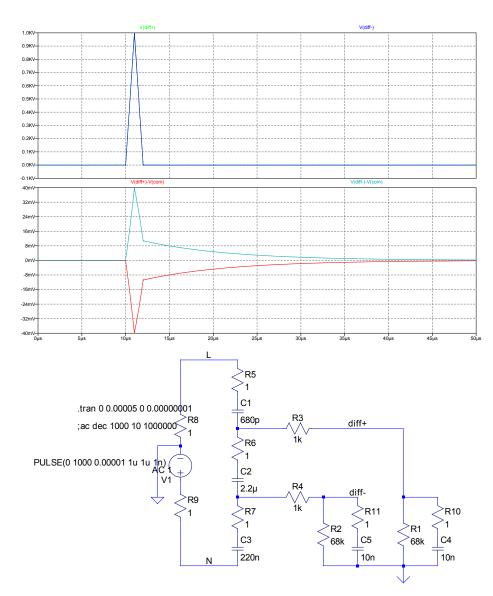

| 4.11 | Transient Simulation with Interference Voltage Peak                        | 50 |

| 4.12 | Transient Simulation with Interference Voltage Peak (L and N interchanged) | 51 |

| 4.13 | Dual-Supply Basic Connection                                               | 52 |

| 4.14 | Input Protection                                                           | 53 |

| 4.15 | Ground Returns for Input Bias Currents                                     | 54 |

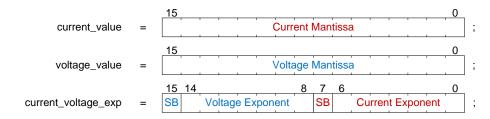

| 5.1  | Current and Voltage Value Registers                                        | 55 |

| 5.2  | Flowchart of Power Calculation                                             | 56 |

| 5.3 | Power Value Registers                                                 | 59 |

|-----|-----------------------------------------------------------------------|----|

| 5.4 | Cascading of the Multiplication                                       | 67 |

| 5.5 | Cascading of the Multiplication, Example                              | 68 |

| A.1 | Small PCB of the Power Metering Unit                                  | 76 |

| A.2 | Base Station                                                          | 77 |

| A.3 | Power Metering Node                                                   | 77 |

| A.4 | Measured Power at Plug                                                | 78 |

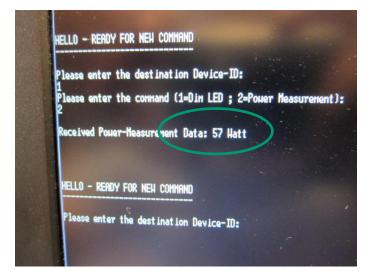

| A.5 | Monitored Power from Metering Node                                    | 78 |

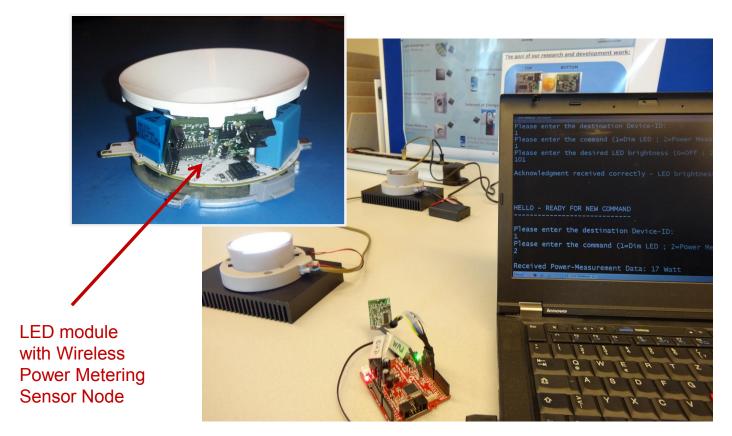

| A.6 | Power Metering Node integrated into a LED Module, with Power Metering |    |

|     | and Dimming Functionality                                             | 79 |

# **List of Tables**

| 3.1 | Pin Definition and Function                                              | 21 |

|-----|--------------------------------------------------------------------------|----|

| 3.2 | Relationship between Analog Current Value and its Internal Binary Repre- |    |

|     | sentation                                                                | 26 |

| 3.3 | Relationship between Analog Voltage Value and its Internal Binary Repre- |    |

|     | sentation                                                                | 27 |

| 3.4 | Electrical Characteristics of the Sensor                                 | 27 |

| 3.5 | Supply Voltages of the Transceiver                                       | 35 |

| 3.6 | Current Consumption of the Transceiver                                   | 35 |

| 6.1 | Dissipated Apparent Power on 60 W Light Bulb                             | 70 |

| 6.2 | Minimum, Maximum and Average Value of 50 Measurements                    | 71 |

| 6.3 | Measurement Results of Active Power and Apparent Power                   | 73 |

|     |                                                                          |    |

# **Chapter 1**

# Introduction

This diploma thesis was carried out at the Institute of Electronics at the Graz University of Technology in cooperation with the Contactless and Radio Frequency Exploration (CRE) Department at Infineon Technologies Austria AG.

The first chapter introduces the motivation leading to the topic of power measurement embedded in a wireless sensor node. While the economic and industrial background considerations are covered in section 1.1, the conceptual formulation of the objective of this thesis is presented in section 1.2. Finally, a brief outline of the project is given in section 1.3.

### 1.1 Motivation, the SmartCoDe Project

The project SmartCoDe is a 7<sup>th</sup> Framewok Program funded by the European Union, with the objective of handling the volatility of renewables and supporting the transition from centralized to distributed local energy production. [FP7 b]

"Future buildings and neighborhoods are expected to combine a manifold of Energy Using Products (EUPs) ranging from electrical lighting to Heating, Ventilation, and Air Conditioning (HVAC) with locally available renewable energy sources and energy storages. Until now, advanced techniques for energy management are not yet applicable in an economically reasonable way in the smaller entities like in energy-positive buildings and neighborhoods" [Mahlknecht et al. 2010].

A major challenge of our society is to reduce carbon dioxide emissions. To achieve this ambitious goal, we are in the process of replacing coal and gas-driven power plants with photovoltaics and wind power plants. This does not directly affect information technology. The problem is that electrical energy can not be stored in an efficient way in large quantities. To solve this problem we have to continuously adapt the demand to the generation of

electrical power provided in the grid. Unfortunately, the generation of electrical energy from renewables such as photovoltaics and wind power plants can not be controlled directly. For this reason, we need information technology to make the grid "smart" enough to handle the volatility of renewables and to support the transition from centralized to distributed local energy production. [FP7 b]

The problem is that energy management systems which ensure an economical utilization of the grid are expensive and only affordable for industry and large commercial customers. In addition the energy demand of consumers (lighting units, washing machines, etc.) varies greatly. Matching the increasing demand of the end user approaching peak consumption is already expensive and will become more so in future. In order to adapt the demand to the availability of electrical power, the project SmartCode is trying to enable a low cost application for demand side management and smart metering in households and small commercial buildings as well as neighborhoods. The result is a new architecture for wireless sensor/energy management nodes that specifically considers the requirements of EUPs, building up a fine grained infrastructure. [Mahlknecht *et al.* 2010]

Among others, one approach of the project SmartCoDe is to promptly schedule the use of energy or switch EUPs into standby if the customer process allows that. To enable the application of advanced energy management techniques in energy-positive buildings and neighborhoods, infrastructure and methods are needed which fulfill the following requirements:

- · No additional costs

- No new wires

- Small size

- Wireless communication infrastructure

- Information security

Lastly, intelligent management of energy contains a financial benefit for the end user and contributes to the stability of the grid. Things become even more advantageous if local energy production such as a small scale wind power plant becomes available. The varying energy demand of EUPs, and accordingly households or neighborhoods, can possibly be partially met with local energy production. [Mahlknecht *et al.* 2010]

# 1.2 Objective of this Thesis

The objective of this thesis was the development of a low-power power metering unit of small size for 230 V grid connected devices. The power metering unit will be part of a wireless monitoring node, supposed to be integrated into any given home appliance (for example lighting units, fridges, washing machines, dishwashers or intelligent power plugs).

The power metering unit shall be based on an available test chip developed by Infineon Technologies AG, which is able to perform both current and voltage digital sampling with high sampling rate. A transceiver Application-Specific Integrated Circuit (ASIC) including a programmable protocol processor shall be used for digital signal processing of the captured current and voltage samples for subsequent power calculation.

In the theoretical part of this, thesis among others, the mathematical definitions of active power and apparent power has to considered. An analysis of algorithms to be implemented have to be performed in order to calculate the power of a sampled signal.

A first prototype and the corresponding firmware have to be developed in the practical part of this thesis. In order to enable a voltage measurement hardware has to be designed which steps down line voltage. The calculation of active power and apparent power as well as the implementation of the single-wire communication interface between the transceiver and the test chip have to be implemented.

An integration of the power metering unit into a wireless node and the realization of the required radio communication protocol handler have to be supported.

# 1.3 Thesis Outline

The first chapter introduces the topic of power measurement and the associated economical and industrial aspects. Considering the requirements to enable a fine-grained infrastructure, and subsequent integration into a Wireless Sensor Networks (WSN), a first prototype was developed. Design challenges as well as simulation results and measurement results of the developed unit are presented.

#### Chapter 2 – Fundamentals of Power Calculation

The mathematical basics, including the definitions of active power, and apparent power are discussed. Taking into account the sampling theorem, power calculation from a discrete signal is introduced. Among others, this chapter also presents the physical background underlying the Hall effect.

#### Chapter 3 – System Overview of Power Metering Unit

A description of the current and voltage sensor and the applied transceiver with its programmable protocol processor is presented. A description of the single-wire operation and external wiring of the single-wire communication interface of both is depicted. The sequence used to perform current and external voltage measurement as well as the arising time delay between sensing the current and voltage value are introduced.

#### Chapter 4 – Hardware Design of Power Metering Unit

The current and voltage sensor presented in chapter 3 has its limitations. Enabling a measurement of line voltage by the sensor, it has to be stepped down using a capacitive voltage divider. An overview of capabilities realizing the required voltage divider with its advantages and drawbacks is given. The chapter gives insight into hardware design issues and implementation details and concludes with simulation results.

#### Chapter 5 – Software Design of Power Metering Unit

An insight into the designed firmware architecture including an example in the form of a pseudo code is given in this chapter. The transceiver presented in chapter 3 has a very limited language subset of the C compiler. The apparent power calculation demands a way to extract the square root, considering the limitations of the C compiler. Based on the characteristic number representation caused by the division operation, a floating point representation with mantissa and exponent was established. In order to achieve the highest accuracy of the measurements, a cascaded multiplication algorithm was implemented.

### Chapter 6 – Measurements with Power Metering Unit

Power metering is performed by sampling over 10 line voltage periods with a sampling rate of 400 Hz, leading to eight samples per line voltage period. Using the Gaussian distribution an assessment of accuracy can be determined. 50 measurements were carried out on a 60 W light bulb, resulting in an accuracy of the apparent power of approximately  $\pm 4.4 \%$ .

#### Chapter 7 – Conclusion

Results and findings of this thesis are summarized and a prospective on future work is given in this chapter.

#### Chapter A – Appendix

In this chapter, among others illustrations of the small Printed Circuit Board (PCB) of the power metering unit as well as the demonstrator are presented. An integration into an LED<sup>1</sup> module which can perform power metering as well as dimming is shown as well.

<sup>&</sup>lt;sup>1</sup>Light-Emitting diode

# **Chapter 2**

# **Fundamentals of Power Calculation**

This chapter covers the theoretical and mathematical background of power metering using a Hall-based current sensor. Section 2.1 explains the basic principle of Hall-based sensors and the physical background underlying the Hall effect. Section 2.2 gives an overview of the mathematical basics of power metering, the definition of individual powers and how power can be calculated from sinusoidal currents and voltages. The transition from continuous signals to time-discrete signals and the sampling theorem are covered in section 2.3. Furthermore, the calculation of active and accordingly apparent power of digital signals can be found in section 2.4.

# 2.1 Hall Effect, Hall-based Current Sensor

The Hall effect is a physical phenomenon which was discovered by American physicist E. H. Hall in 1879 as part of his doctoral thesis [Bridgman 1939]. It describes and explains the occurrence of a voltage transversely to the current flow in a current carrying conductor through the action of a perpendicular magnetic field. Further details concerning the Hall effect and its underlying Lorentz force can be found in [Renhart 2011] and [Hoffmann 2002].

The basic physical principle underlying the Hall effect is the Lorentz force, the force acting on moving charged particles due to a magnetic field. The effect is particularly prevalent in semiconductors as a result of the high mobility of charge carriers. A particle of charge  $\vec{q}$ with instantaneous velocity  $\vec{v}$  experiences a force

$$\vec{F} = q(\vec{E} + \vec{v} \times \vec{B})$$

due to the presence of an electrical field  $\vec{E}$  and a magnetic field  $\vec{B}$ . This relationship is referred to as Lorentz's equation. The first term  $q\vec{E}$  is contributed by the electrical field called Coulomb force, describing the action on unmoved charges due to electrical fields. The second term  $q(\vec{v} \times \vec{B})$  describes the magnetic force referred to as the Lorentz force,

the force experienced by a moving charge in a magnetic field. Accordingly the magnetic force acting on a moving charge is expressed by the following equation.

$$\vec{F} = q(\vec{v} \times \vec{B}) \tag{2.1}$$

This force has a direction perpendicular to both the velocity of the charge and the magnetic field. [Renhart 2011]

When a current flowing semiconductor plate is laying in an applied magnetic field which is not parallel to the direction of the moving charge carriers, the magnetic force given by equation 2.1 leads to a deflection of these charge carriers. Figure 2.1 illustrates the force on charge carriers in a conductor in a magnetic field.

Figure 2.1: Illustration of the Hall Effect Adapted from [Wikipedia 2012]

As a result charge carriers pile up on one side of the material and deplete from the opposite side. This separation of charge creates an electrical field acting on charge carriers which compensates the effect of the Lorentz force. Accordingly, for the resulting force acting on charge carriers, the following equation has to be applied.

$$0 = q(\vec{E} + \vec{v} \times \vec{B})$$

The separation of charge stops and a steady electrical potential is established, as long as the charge is flowing. This so-called Hall voltage,  $V_H$ , that develops across a conductor can be calculated by

$$V_H = c_h \frac{IB}{d},\tag{2.2}$$

where  $c_h$  is the Hall constant, *I* is the current across the plate, *B* is the magnetic field, and *d* is the thickness of the plate. The Hall voltage is directly proportional to the current, to the magnetic field, the nature of the particle conducting material itself, and inversely proportional to the thickness of the material. [Hoffmann 2002]

# 2.2 Mathematical Basics of Power Metering

An instrument measuring electrical currents is referred to as an ammeter, those instruments measuring electrical voltages are referred to as voltmeters, instruments measuring electrical power are referred to as wattmeters. The principle mode of operation of ammeters, voltmeters and wattmeters is based on the force acting on a current carrying conductor in a magnetic field. Generally both direct quantities and alternating quantities have to be measured. [Brasseur 2004]

Generally power metering is carried out either indirectly by simultaneous measurement of current and voltage or directly by using a active power meter such as a wattmeter for example. As we have a current sensor which is also able to measure voltages, power metering is carried out indirectly. The following sections are describing terms and definitions and how power can be calculated of continuous sinusoidal signals.

### 2.2.1 Terms and Definitions

In electrical engineering a distinction is made between direct quantities and alternating quantities. Direct quantities are characterized by their temporally constant electrical quantities, for example currents and voltages. Accordingly, the magnetic field, with corresponding magnetic quantities to its connected electrical field, is constant as well. Time variable quantities describing the electromagnetic phenomenon are called alternating quantities. Another distinction is made between the periodic and non-periodic. In this thesis it is assumed that all alternating quantities are periodic quantities. Periodic quantities take the same value in every specific subsequent time segment. [Weißgerber 2013]

### Direct (DC) Current and Direct (DC) Voltage

DC current and DC voltage are electrical quantities whose momentary values are constant at all times.

### Alternating (AC) Current and Alternating (AC) Voltage

AC current and AC voltage are electrical quantities whose momentary values are repetitive after time segment T, called period, and whose average values are zero. [Hoffmann 2002]

In electrical engineering alternating quantities take on a narrow meaning, as in the physical definition mentioned above. A further distinction is made between sinusoidal and nonsinusoidal quantities. Under the assumption that AC current and AC voltage have a sinusoidal shape, signals can be clearly identified by specifying **peak value**, **frequency** and **phase shift**. Sinusoidal quantities represent a special case in periodic signals. They are not only described as a function in time, but also as a function of angle  $\varphi = \omega t$ . The transition from the two notations is carried out by multiplying the time axis with the angular frequency  $\omega$ . Period T on time axis passes into angle  $\omega t = 2\pi$  on  $\omega t$ -axis. [Albach 2005], [Renhart 2011]

#### Peak Value $\hat{U}$

The peak value of a signal is defined by the maximum deviation from the neutral.

#### $\textbf{Period} \ T$

The time between two points of a signal with the same value is called period. Sinusoidal functions repeat themselves after expiry of an angle of  $360^{\circ}$  or  $2\pi rad$ .

#### Frequency f

The frequency of a signal specifies the number of oscillations from a signal per second. Frequency can be computed by using the reciprocal of the period.

$$f = \frac{1}{T}$$

In addition to these fundamental terms of electrical oscillations, there are other terms describing the physical effects of electrical alternating quantities. For these, it is more expedient to work with terms regardless of the signal shape. [Albach 2005], [Hartl 2008]

#### Average Value $\bar{U}$

According to its definition, the average value of a time-dependent periodic signal is the integral of the signal over period related to period. The average value of an electrical alternating signal equates to the containing direct component. It is equal to zero for pure sinusoidal quantities, symmetrically with respect to zero level.

$$\bar{U} = \frac{1}{T} \int_{t_0}^{t_0 + T} u(t) dt$$

(2.3)

### Rectified Value $|\bar{U}|$

The rectified value of a signal is defined as the average value (equation 2.3) of the absolute value of the signal. It describes an intended DC current which transports the same charge as the rectified AC current.

$$\left| \bar{U} \right| = \frac{1}{T} \int_{t_0}^{t_0+T} |u(t)| \, dt$$

For sinusoidal quantities the rectified value can be calculated by

$$\left|\bar{U}\right| = \frac{2}{\pi}\hat{U}.$$

#### Root Mean Square Value (rms-value)

The square root of the average value of the square of a signal is defined as the root mean square value of a signal. The root mean square value of an AC current or AC voltage causes the same effect on a resistance as a comparable value of DC current or DC voltage causes on the same resistance.

$$U_{eff} = \sqrt{\frac{1}{T} \int_{t_0}^{t_0 + T} u^2(t) dt}$$

(2.4)

For sinusoidal quantities the root mean square value can be calculated by

$$U_{eff} = \frac{\hat{U}}{\sqrt{2}}.$$

(2.5)

The definitions of these two values were shown using the voltage as an example; they were calculated in the same way for currents. With regard to all considerations in connection with powers, rms-values are used. For example, in charge and discharge processes in batteries the transported charge is the crucial factor. In this case, average value or rectified value has to be considered.

As we are subsequently using principally rms-values at alternating quantities, the index  $_{eff}$  is omitted, rectified values and average values are marked for distinction. [Hartl 2008]

#### 2.2.2 Power at AC Current Voltage

This section considers linear network stored or consumed power, in cases where the circuit is connected to an AC current voltage source. For the sake of simplicity the network is set up with individual two terminal networks. As the stored or consumed power of the entire network consists of the linear superposition contributed by the individual two terminal networks, the consideration is restricted to one linear two terminal network. At the linear two terminal network, active resistance and reactance are independent of the current through the components. The time dependent quantities are represented generally by equations 2.6.

$$u(t) = \hat{U}\cos(\omega t + \varphi_u)$$

$$i(t) = \hat{I}\cos(\omega t + \varphi_i)$$

(2.6)

with angular frequency  $\omega = 2\pi f$ , phase shift  $\varphi_u$  of voltage and  $\varphi_i$  of current compared to any reference value.

The electrical power is expressed by the product of current and voltage. Consequently, at the time dependent signals u(t) and i(t) as depicted in equation 2.6 the momentary value p(t) of the output power performed at the two terminal network is calculated by

$$p(t) = u(t)i(t) = \hat{U}\hat{I}\cos(\omega t + \varphi_u)\cos(\omega t + \varphi_i).$$

The calculated power can have both positive or negative values, depending on the instant of time. When p(t) > 0, the two terminal network absorbs power and is acting as a consumer load, at purely resistive loads the condition is fulfilled at any time. On the other hand, in the event of p(t) < 0, the two terminal network delivers power and is acting as a source. This case occurs when reactive power is oscillating between the source and two terminal device.

First of all an examination is made of the special cases, where the two terminal network contains one of the components R, L and C. Later on the results are generalized on a arbitrary composed two terminal network. Due to the fact that the considered two terminal networks do not include a current source or voltage source, they are referred to as passive two terminal networks. The dissipated power time-averaged over an entire period of a passive two terminal network always is greater than or equal to zero. [Albach 2005]

#### **Active Power**

At an ohmic resistance, electrical current and voltage are always in phase. Because of the connection  $\varphi_i = \varphi_u$ , the time-dependent power is composed of a time-independent expression and an expression oscillating with double frequency.

$$p(t) = \hat{U}\hat{I}\cos^2(\omega t + \varphi_u)) = \frac{\hat{U}\hat{I}}{2}\left[1 + \cos(2\omega t + 2\varphi_u)\right] = UI\left[1 + \cos(2\omega t + 2\varphi_u)\right]$$

The result is describing the power dissipated by a resistor, in other words the power converted into heat.

$$p(t) = UI \left[1 + \cos(2\omega t + 2\varphi_u)\right] = UI \left[1 + \cos(2\omega t + 2\varphi_i)\right]$$

Of particular importance is the dissipated time-averaged power on a resistor, referred to as **active power**. By integrating over the entire period, the expression with cosine function resolves, leaving the time-independent expression.

$$P = \frac{1}{T} \int_{t_0}^{t_0 + T} p(t) dt$$

(2.7)

With pure ohmic resistance, the active power is calculated by the product of the rms-value of current and voltage. [Albach 2005]

$$P = \frac{1}{T} \int_{t_0}^{t_0 + T} p(t) dt = UI$$

#### **Reactive Power**

At an inductance the current is lagging behind the voltage by  $\pi/2$ . With the existing phase relationship  $\varphi_i = \varphi_u - \pi/2$  and by means of addition theorems the time-dependent power can be described with the following equation.

$$p(t) = \hat{U}\hat{I}\cos(\omega t + \varphi_u)\cos(\omega t + \varphi_u - \pi/2) = \hat{U}\hat{I}\cos(\omega t + \varphi_u)\sin(\omega t + \varphi_u)$$

$$= \frac{\hat{U}\hat{I}}{2}\sin(2\omega t + 2\varphi_u) = UI\sin(2\omega t + 2\varphi_u) = -UI\sin(2\omega t + 2\varphi_i)$$

(2.8)

The resultant power just consists of the expression oscillating with double frequency, the average value disappears. This back and forth oscillation of the power is referred to as **reactive power**.

At capacitance the conditions are similar to the inductance. In that case the current is leading the voltage by  $\pi/2$ . Accordingly, the sign of current and therefore the time-depending power is changing.

$$p(t) = -UI\sin(2\omega t + 2\varphi_u) = UI\sin(2\omega t + 2\varphi_i)$$

(2.9)

In principle, no losses occur during the energy exchange between the AC current voltage source and inductance, and accordingly capacitance. The energy temporarily extracted from the source is used for building up the magnetic field and the electrical field, respectively. On the other side, by decreasing the field energy is returned to the source. [Albach 2005]

#### **Apparent Power and Power Factor**

Having discussed special cases with only one component, now the two terminal network is composed of any combination of the components R, L and C. This means the phase shift between current and voltage can take any value in a range of  $-\pi/2 \le (\varphi_u - \varphi_i) \le +\pi/2$ . By means of addition theorems the time-dependent power is rearranged to

$$p(t) = \hat{U}\hat{I}\cos(\omega t + \varphi_u)\cos(\omega t + \varphi_i) = \frac{UI}{2}\left[\cos(\varphi_u - \varphi_i) + \cos(2\omega t + \varphi_u + \varphi_i)\right]$$

$$= UI\cos(\varphi_u - \varphi_i) + UI\cos(2\omega t + \varphi_u + \varphi_i).$$

In this as well case the time-dependent power is comprised of a time-independent expression and an expression oscillating with double frequency. A further conversion of the oscillating expression

$$\cos(2\omega t + \varphi_u + \varphi_i) = \cos\left[(2\omega t + 2\varphi_u) - (\varphi_u - \varphi_i)\right]$$

$$= \cos(2\omega t + 2\varphi_u)\cos(\varphi_u - \varphi_i) + \sin(2\omega t + 2\varphi_u)\sin(\varphi_u - \varphi_i)$$

leads to a first representation of the momentary power

$$p(t) = UI\cos(\varphi_u - \varphi_i)\left[1 + \cos(2\omega t + 2\varphi_u)\right] + UI\sin(\varphi_u - \varphi_i)\sin(2\omega t + 2\varphi_u), \quad (2.10)$$

where the argument of the time-dependent functions includes only the phase shift of the voltage  $\varphi_u$ . In the same way a transformation of the expression oscillating with double frequency

$$\cos(2\omega t + \varphi_u + \varphi_i) = \cos\left[(2\omega t + 2\varphi_i) + (\varphi_u - \varphi_i)\right]$$

$$= \cos(2\omega t + 2\varphi_i)\cos(\varphi_u - \varphi_i) + \sin(2\omega t + 2\varphi_i)\sin(\varphi_u - \varphi_i)$$

yields a second representation of the momentary power

$$p(t) = UI\cos(\varphi_u - \varphi_i)\left[1 + \cos(2\omega t + 2\varphi_i)\right] - UI\sin(\varphi_u - \varphi_i)\sin(2\omega t + 2\varphi_i), \quad (2.11)$$

where the argument of the time-dependent functions includes only the phase shift of the current  $\varphi_i$ .

Setting the phase shift between current and voltage to zero,  $\varphi_u - \varphi_i = 0$ , due to the relation cos(0) = 1 the first summand in both equation 2.10 and equation 2.11 corresponds to the momentary active power and the second summand resolves. In the other case, where current and voltage are shifted by  $\pm \pi/2$ , the first summand drops out and the second summand simplifies to equation 2.8 with inductors and equation 2.9 with capacitors, respectively. Obviously the first summand in equation 2.10 and equation 2.11 is describing the momentary power percentage irreversibly transformed into another form of energy (heat) corresponding to the active power, while the second summand is describing the momentary power percentage responsible for the changing of the stored energy in the magnetic field, and accordingly in the electrical field corresponding to the reactive power.

In general, at a linear two terminal network with current and voltage according to relation 2.6 and phase shift between these quantities in a range of  $-\pi/2 \le (\varphi_u - \varphi_i) \le +\pi/2$ , the active power given by equation 2.3 can be calculated by integration of the expressions

2.10 and 2.11 over an entire period. Due to trigonometric identity  $\cos \varphi = \cos -\varphi$  the value of the active power is independent of whether the current leads or lags.

$$P = UI\cos(\varphi_u - \varphi_i)$$

Consequently the active power is dependent on both the amplitude of current and voltage and the phase shift between these quantities. The coefficient  $\cos(\varphi_u - \varphi_i)$  is typically abbreviated with  $\lambda = \cos(\varphi_u - \varphi_i)$  and referred to as **power factor**. When the two terminal network only consists of ohmic resistances, the relation  $\varphi_u = \varphi_i$  applies and the power factor contains the value  $\lambda = \cos(0) = 1$ . At pure reactances the phase shift is given by  $\varphi_u - \varphi_i = \pm \pi/2$  and  $\lambda = \cos(\pm \pi/2) = 0$  then applies for the power factor. Based on the definition of active power, the amplitude of the second summand

$$Q = UI\sin(\varphi_u - \varphi_i)$$

is referred to as **reactive power**. Therefore the active power at two terminal networks, consisting of the components R, L and C, is always taking positive values. The reactive power is accordingly reaching both positive and negative values, depending on whether the two terminal network is acting inductively or capacitively and the current is leading or lagging the voltage.

Viewing these powers as a vector diagram, the catheti correspond to the active power and the reactive power. The hypotenuse

$$S = UI = \sqrt{P^2 + Q^2}$$

(2.12)

is referred to as **apparent power**. Accordingly the apparent power is given by the vector product of active power and reactive power or by multiplying the rms-values of current and voltage, disregarding the power factor. The term is associated with the fact that it represents no power in the physical sense, as current and voltage occur in various instants of time.

With this definition the power factor can be calculated by the ratio of active power and apparent power.

$$\lambda = \cos(\varphi_u - \varphi_i) = \frac{P}{S}$$

The units for powers P, Q and S always result from the product of  $[U] \cdot [I] = V \cdot A$ . Instead of Watt (W) as it is used for active power, Volt-ampere reactive (Var) is used for reactive power and Volt-ampere (VA) for apparent power. [Albach 2005]

# 2.3 Sampling and Quantization

Generally, in analog electronics, continuous quantities were processed. In modern digital electronics these continuous quantities have been discretized; in other words they can only take specified values and accordingly they are only defined at specified instants of time. In digital processing these discrete signals are now used for computing. Accordingly there are four different possible types of time signals, depending on whether the discretization is carried out in the time domain or in the value domain. The continuous parameter t is replaced by an integer index variable k. A digital signal is discretized in the time domain referred to as sampling as well as in the value domain referred to as quantization and can be described with integer values. [Hartl 2008]

## 2.3.1 Sampling of Continuous Signals, Sampling Theorem

Discretization in the time domain means that a signal is sampled at a specified, exactly defined instant of time. In other words a continuous signal x(t) can be converted into a sequence of discrete values  $x_k$  by taking samples of the signal in equidistant instants of time  $t_k = kT_s$ .

$$x_k = x(kT_s), \text{ for } k \in \mathbb{Z}$$

with  $T_s$  referring to as sampling interval. The information on the signal sequence between the specific sampling points will get lost. If the signal is sampled often enough, then no loss of information occurs at discretization in the time domain leading to the sampling theorem. [Brasseur 2004], [Hartl 2008]

### Sampling Theorem

The theoretical foundations for a discretization in the time domain are given by the following sampling theorem. By sampling a continuous signal, the signal is discretized in the time domain.

$$x(t) \longrightarrow x_k$$

, for  $k \in \mathbb{Z}$

This is carried out with the sampling rate  $f_s$ , the reciprocal of sampling interval  $T_s$ . Afterwards, the value of the signal is only known at specified, exactly defined instants of time.

The sampling theorem states that, if a continuous band-limited signal is sampled with at least twice the highest frequency  $f_{max}$  of the signal, then at discretization in the time domain no loss of information occurs and the signal can be reconstructed completely.

$$f_s > 2f_{max} \tag{2.13}$$

Sampling Theorem

Violating the sampling theorem, referred to as undersampling, leads to loss of information as well as seemingly occurring components in the time-discrete signal referred to as aliasing. [Hartl 2008]

### 2.3.2 Quantization in Value Domain

A quantization in the value domain means that the signal value can be described with integer values. For that, the amplitude range is divided into equal intervals, referred to as quantizing intervals, and each interval is assigned to a value. After conversion into the binary system, the signal value can be represented by multiple bivalent variables independent of the range of values, referred to as encoding.

Further details concerning the quantizing intervals and the binary representation of the current and voltage values are given in section 3.2. A closer look at discretization in the time domain as well as in the value domain and the sampling theorem can be found in [Hartl 2008] and [Brasseur 2004].

### 2.4 Power Calculation from a Digital Signal

This thesis deals with the subject of power measurement of any of the loads connected to the line voltage concerning active power and apparent power. The rms-value of the line voltage is 230 V. It is assumed that the grid provides a continuous pure sinusoidal quantity with its maximum frequency of  $f_{max} = 50 Hz$ . As can be seen from section 2.2.2, power measurement can be done indirectly by simultaneous measurement of current and voltage. Timer-averaged power converted in the load is referred to as active power and can be expressed by equation 2.7. Referring to equation 2.12, apparent power can be calculated by multiplying the rms-values of current and voltage. This leads to the following equations for continuous signals.

$$P = \frac{1}{T} \int_{t_0}^{t_0+T} p(t)dt = \frac{1}{T} \int_{t_0}^{t_0+T} u(t)i(t)dt$$

(2.14)

$$S = UI = \frac{1}{T} \sqrt{\int_{t_0}^{t_0+T} u^2(t) dt \int_{t_0}^{t_0+T} i^2(t) dt}$$

(2.15)

Concerning the definition of an integral by Riemann sums, a definite integral can be defined as the area between the x-axis and the graph of a function. Choose a real-valued function f(x) which is defined on the interval [a, b]. For the purpose of describing an integral as a sum, the interval is subdivided into n partial intervals. In the limit of  $n \to \infty$  the sum of the individual areas describes exactly the area under the curve. In conclusion the definite integral of the function is equal to the limiting value of the sum of all rectangular areas

under the curve. The signed area under all the rectangles is referred to as the Riemann sum.

$$\int_{a}^{b} f(x)dx = \lim_{n \to \infty} \sum_{k=1}^{n} f(x_k)\Delta x, \text{ for } \Delta x = \frac{b-a}{n}$$

Decreasing the spacing between the samples and accordingly increasing the amount of partial intervals, the total area of the rectangles converges to the integral of the function.

By sampling the continuous quantities current i(t) and voltage u(t) with a frequency of fs = 400 Hz, the signal value at each sampling point is assigned to the corresponding quantizing interval and depicted as a binary value. According to this, current and voltage are converted into a sequence of discrete values  $u_k$  and  $i_k$ .

$$u(t) \longrightarrow u_k$$

, for  $k \in \mathbb{Z}$

$i(t) \longrightarrow i_k$ , for  $k \in \mathbb{Z}$

Considering the sampling theorem in equation 2.13, the requirement of sampling with at least twice the highest frequency of the signal is satisfied. From these digital signals  $u_k$  and  $i_k$ , which are discretized in the time domain and the value domain, active power and apparent power can be calculated by equation 2.16 and equation 2.17.

$$P = \frac{1}{n} \sum_{k=1}^{n} u_k i_k$$

(2.16)

$$S = \frac{1}{n} \sqrt{\sum_{k=1}^{n} u_k^2 \sum_{k=1}^{n} i_k^2}$$

(2.17)

# **Chapter 3**

# System Overview of Power Metering Unit

In this chapter an overview of used hardware which was made available is presented. A description of the main building blocks of the system is given in section 3.1. Section 3.2 refers to the test chip of the high-precision digital current sensor TLI4970, concerning its application for external voltage, current measurement and single-wire connection and operation. A short description of the multi-channel transceiver ASIC and the containing protocol processor can be found in section 3.3.

# 3.1 System Architecture

The developed power metering unit measures the power consumption in single-phase systems as part of a WSN. This wireless digital communication system operates in the Industrial, Scientific and Medical (ISM) radio bands. The term communication is always linked with the transport process of information from one point (the information source) to another (the destination or sink). The transmission medium (the channel) illustrates the physical medium over which the modulated information signal is transmitted. While wired channels imply the requirement of a direct connection in the form of a wire (copper, fiberglass etc.) between sending and receiving units to transmit information, wireless transmission channels rely on the effect of wave propagation over free space. [Proakis and Salehi 2004], [Finkenzeller 2010]

ISM bands are referred to as frequency ranges used for industrial, scientific and medical applications. ISM frequency ranges are internationally reserved for applications using High Frequency (HF) devices. The wave propagation in this Ultra-High Frequency (UHF) frequency range is quasi-optical. Buildings and other obstacles cause a strong dampening and reflection of the incident electromagnetic wave. The frequency range 868 MHz up to 870 MHz has been available for Short-Range Devices (SRDs) in Europe since the end of 1997. [Finkenzeller 2010]

The basic block diagram of the power metering unit is shown in figure 3.1. Power metering discussed in this thesis is carried out indirectly by current and voltage measurement. The main building blocks of the unit are the so-called matching network, the current and voltage sensor, a protocol processor and a transceiver (TRX) front end. The main task of the protocol processor is to stand-alone handle the radio communication protocols (MAC protocols) with a base station or gateway. This proprietary radio communication protocol will not be covered in this thesis.

Figure 3.1: Basic Block Diagram of the Power Metering Unit

The so-called matching network is required to comply with characteristics required for external voltage measurement. Because the sensor has its limitations on the external voltage Analog to Digital Converter (ADC) input, the line voltage to be measured has to be stepped down using a voltage divider. Thus, the external voltage ADC input is able to measure an single-ended voltage with respect to GND<sup>1</sup>; the stepped down voltage is amplified by an instrumentation amplifier and fed into the external voltage ADC input. The voltage measured by the ADC is multiplied by firmware with a constant factor in order to correspond to the line voltage. A detailed description concerning the matching network and the instrumentation amplifier can be found in chapter 4.

<sup>&</sup>lt;sup>1</sup>Ground

In order to perform current and voltage measurement, a test chip of the digital current sensor TLI4970 is used. In addition to current measurement, the test chip is also able to measure external voltages by the DOUT<sup>2</sup> pin. Single-wire communication between the sensor and the transceiver is carried out by the FOC<sup>3</sup> pin.

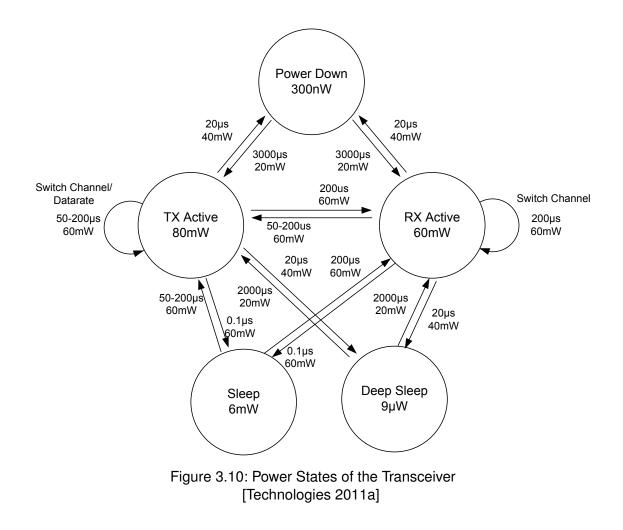

The entire controlling functionality is taken over by the protocol processor, consisting of a programmable state machine and Random Access Memory (RAM) for saving configurations. In addition to its main task of stand-alone handling the radio communication protocols, the protocol processor is also used to sequentially control the single-wire communication with the sensor as well as the calculation of the desired power ratings. Thus, the transceiver is supporting both three-wire SPI and four-wire SPI; single-wire communication with the sensor is carried out by connecting the FW\_SDO<sup>4</sup> pin and the FW\_SDI<sup>5</sup> of the SPI module. More information about the single-wire communication interface is given in figure 3.5 and in section 3.3.4.

As a result of the capacitive voltage divider used and its characteristics, the entire power metering unit must be operated as floating. The unit can be supplied either by batteries or by a potential-free (floating) voltage source. More details concerning the capacitive voltage divider can be found in section 4.2.

# 3.2 Current and Voltage Sensor, Test Chip of the TLI4970

The TLI4970 is a high-precision miniature coreless magnetic current sensor based on Infineon's well-established Hall technology, allowing galvanic isolation between the primary (current rail) and the secondary (interface to control unit) side. Using a coreless concept without a flux concentrator allows significant miniaturization and shows no hysteresis effects. As a result of the differential measurement principle and the implemented stray field suppression, the TLI4970 is extremely robust against external magnetic fields. There is no need for any external calibration of the sensor in manufacturing nor during application. The functionality of the TLI4970 is comparable to open- or closed-loop current measurement systems with a magnetic core, but enables a significantly smaller footprint (illustrated in figure 3.2) and consumes less power. [Technologies 2011d]

The implementation of digital temperature and stress compensation provides outstanding long-term stability of the output signal. Compared to a shunt resistor, for current measurements using the Hall effect there is no resistor immersed into the primary circuit and accordingly no voltage drop happens nor is there any power lost. [Technologies 2011d]

<sup>2</sup>SPI Data Out

<sup>&</sup>lt;sup>3</sup>Fast Overcurrent Detection Output

<sup>&</sup>lt;sup>4</sup>Serial Data Out

<sup>&</sup>lt;sup>5</sup>Serial Data In

Due to the digital concept, there is no need for any external calibration and additional parts such as ADCs, operational amplifier (op-amps) or reference voltage, reducing the overall implementation effort, PCB space and cost significantly. The TLI4970 is suitable for AC as well as DC current measurement applications such as photovoltaic inverters, Power Factor Correction (PFC) power supplies, chargers and drivers. The contact-free measurement principle causes no additional power loss and is therefore perfectly suited for systems with high efficiency. It is also suitable for fast overcurrent detection with a configurable threshold level, allowing the control unit to switch off and protect the affected system from damage, independently of the main measurement path. [Technologies 2011d]

Figure 3.2: Sensor in Comparison with 1 Cent Coin [Mann 2012]

In addition to the current measurement, the test chip of the TLI4970 is also able to perform external voltage measurement on the DOUT pin against GND, which is normally used to carry out three-wire Serial Peripheral Interface (SPI) communication. This is done by using the second internal Sigma-Delta-ADC; in conventional operation this ADC is used for temperature and stress compensation.

## 3.2.1 Pin Configuration

Pin configuration and description of the sensor in order to perform current and external voltage measurement are depicted in figure 3.3 and table 3.1.

Figure 3.3: Pin Configuration PG-TISON-8-1 [Technologies 2011d]

| Pin No. | Symbol | Function                                    |

|---------|--------|---------------------------------------------|

| 1       | GND    | Ground                                      |

| 2       | VDD    | Supply voltage                              |

| 3       | DOUT   | External voltage ADC input                  |

| 4       | SCLK   | Serial clock input                          |

| 5       | CS     | Chip select input (low-active)              |

| 6       | FOC    | Single-wire communication interface         |

| 7       | IP+    | Positive current terminal pin (current-in)  |

| 8       | IP-    | Negative current terminal pin (current-out) |

Table 3.1: Pin Definition and Function Adapted from [Technologies 2011d]

### 3.2.2 Functional Description

"The current flowing through the current rail on the primary side induces a magnetic field, which is measured by two differential Hall probes. The signal from the two Hall probes is directly digitized by a Sigma-Delta-ADC. After the programmable digital low-pass filter, the raw current signal is fed into the Digital Signal Processor (DSP). The differential measurement principle of the magnetic field provides a very good suppression of any ambient stray magnetic field." [Technologies 2011d]

"The temperature (T) and the mechanical stress (S) of the chip are measured and converted independently of the primary current by a second ADC. The DSP unit uses both temperature and stress information to compensate the raw current signal according to internally stored calibration tables." [Technologies 2011d]

Figure 3.4: Functional Block Diagram of the Current and Voltage Sensor Adapted from [Technologies 2012a]

In addition, the test chip of TLI4970 is able to perform an external voltage measurement on the DOUT pin. In order to to perform this feature the test chip of TLI4970 has to be switched in a so-called "test" mode. The signal applied on the DOUT pin is digitized by the second Sigma-Delta-ADC; in conventional operation this ADC is used for temperature and stress compensation. The digital interface unit (IF) transmits the fully compensated current value and accordingly the voltage value by the single-wire communication interface available on the FOC pin; in conventional operation this pin is used to detect an overcurrent in the measurement path.

### 3.2.3 Single-wire Connection and Operation

This interface is used to read out the measured current and voltage values as required for power metering used in this thesis. It is available and always functional on the FOC pin using a pull-up resistor of  $4.7 k\Omega$  illustrated in figure 3.5. [Technologies 2011b]

The transmission is based on transmitting a single bit to the sensor and immediately receiving a bit. These bits form a 16 bit communication similar to a SPI interface. The interface is bit-synchronous and very flexible in timing within quite large boundaries. Sensor and Protocol Processing Unit (PPU) must use an open-drain output, so they can actively pull only a 0V level. The 3.3V level is achieved by an external pull-up resistor, about  $4.7 k\Omega$  or larger.

Sequential control of the single-wire communication with the sensor is taken over by the protocol processor generating the requested timing. Timing is implemented in firmware, resulting in a possible bit transmission rate of  $143 \frac{kbit}{s}$ . Consequently, the required time for the transmission of 16 bit takes  $112 \,\mu$ s.

Figure 3.5: Single-wire Connection of the Current and Voltage Sensor Adapted from [Technologies 2011b]

### 3.2.4 Flowchart for Current and Voltage Measurement by Single-wire

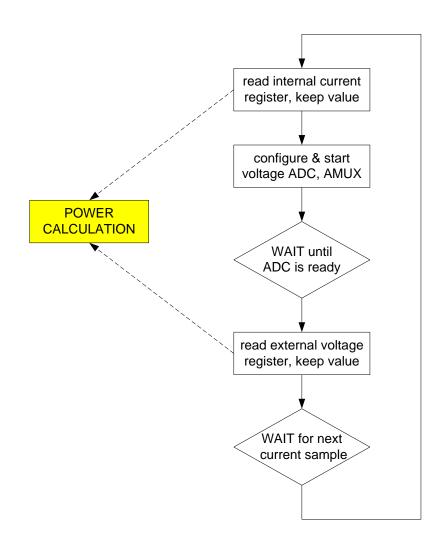

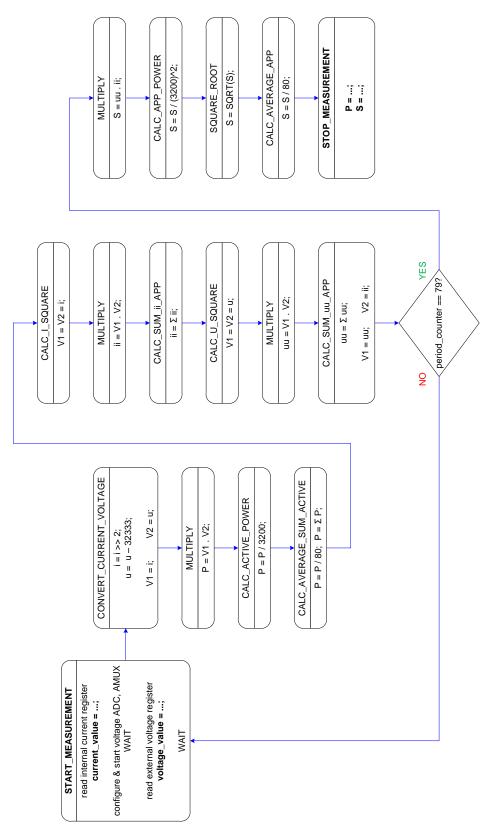

Figure 3.6 basically illustrates the sequence used to perform current and external voltage measurement, obtaining one value of current and the corresponding voltage. After the voltage value has been read out the system waits until the next current value read-out, to get an integer number of samples within a period of the line voltage. This pause is used to perform the on-the-fly power calculation. More details concerning the on-the-fly calculation can be found in section 5.1.

Figure 3.6: Current and Voltage Measurement Sequence

#### **Read Internal Current Register, "1"**

A current register read-out is executed by transmitting the appropriate commands. Thus, the single-wire communication is based on transmitting a single bit and immediately receiving a bit, the second command is used to set the sensor in a so-called "freeze" state and simultaneously receive the updated current value. To ensure that the signal processing activities do not interfere with test activities, the internal algorithm processing can be frozen. In this mode the ADCs are still functional and update its data, but the compensation algorithm is no longer executed.

#### Configure and Start Voltage ADC, "2"

In this block certain configurations were executed in order to perform external voltage measurement on the DOUT pin, followed by a pause until the external voltage ADC is ready. These configurations include:

- Enable "test" mode

- · Enable Analog Multiplexer (AMUX) operation on DOUT

- Enable "low common" mode

- Enable "input" mode on DOUT

- Enable ADC channel

#### Read External Voltage Register, "3"

An external voltage register read-out is executed by transmitting appropriate commands alike. The last "unfreeze" command starts algorithm processing again and simultaneously saves the updated voltage value.

#### Power Calculation, "4"

The last command of the sequence is followed by a pause until the next current value read-out, used to perform power calculation. Calculating one value of active power and apparent power takes about  $500 \,\mu s$ . After a time of  $2.5 \,ms$  the sequence repeats itself again, eight times within a period of the line voltage.

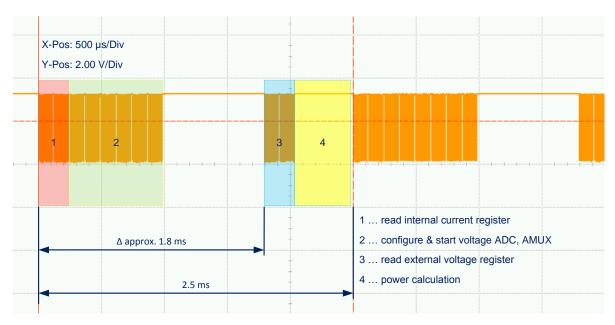

Figure 3.7 shows the same sequence used to perform current and external voltage measurement with a bit transmission of  $143 \frac{kbit}{s}$ . As can be seen from figure 3.7 the sequence is repeated every 2.5 ms; the outcome of this is a sampling rate of 400 Hz.

Note that due to the time delay of approximately 1.8 ms between sensing the current and voltage values a virtual phase shift is introduced into the calculation of real and apparent power ratings. Further details are discussed in chapter 6.

Figure 3.7: Captured Current and Voltage Measurement Sequence

# 3.2.5 Mapping of the Current Value

As mentioned before, the single-wire transmission form a 16 bit communication, but the value read from the internal current output register has two more Least Significant Bits (LSBs). After a data read from the internal current output register, the value thus has to be shifted 2 bits to the right to scale it similarly to table 3.2. [Technologies 2011b]

| Primary current value | Typical decimal current value (16 bit signed) | Note                  |

|-----------------------|-----------------------------------------------|-----------------------|

| +50 A                 | 4000                                          | Maximum allowed limit |

| +20 A                 | 1600                                          |                       |

| +5 A                  | 400                                           |                       |

| 0 A                   | 0                                             | Zero-point            |

| -5 A                  | -400                                          |                       |

| -20 A                 | -1600                                         |                       |

| -50 A                 | -4000                                         | Minimum allowed limit |

Table 3.2: Relationship between Analog Current Value and its Internal Binary Representation [Technologies 2011b]

# 3.2.6 Mapping of the Voltage Value

The binary representation of the external voltage value is given in table 3.3.

| External voltage value | Typical decimal current value (16 bit unsigned) | Note                  |

|------------------------|-------------------------------------------------|-----------------------|

| +0.2 V                 | 45667                                           | Maximum allowed limit |

| +0.1 V                 | 39000                                           |                       |

| 0 V                    | 32333                                           | Zero-point            |

| -0.1 V                 | 25666                                           |                       |

| -0.2 V                 | 18999                                           | Minimum allowed limit |

Table 3.3: Relationship between Analog Voltage Value and its Internal Binary Representation [Technologies 2011b]

### 3.2.7 Electrical Characteristics

Electrical characteristics of the current and voltage sensor are given in table 3.4. Note that because the line voltage has to be stepped down using a voltage divider, the sensitivity of the voltage values are specified to the full-scale voltage measurement range of  $\pm 200 \, mV$ .

| Parameter                                    |      | Value | Unit |             |

|----------------------------------------------|------|-------|------|-------------|

|                                              |      | Тур.  | Max. | Omt         |

| Supply voltage                               | 3.1  | 3.3   | 3.5  | V           |

| Current consumption                          | 5    | 12    | 25   | mA          |

| Full-scale primary current measurement range | -50  |       | +50  | А           |

| Update rate                                  |      | 80    |      | kS/s        |

| Sensitivity of current value                 |      | 12.5  |      | mA/LSB      |

| Full-scale voltage measurement range         | -200 |       | +200 | mV          |

| Update rate                                  |      | 1.2   |      | kS/s        |

| Sensitivity of voltage value                 |      | 15    |      | $\mu$ V/LSB |

Table 3.4: Electrical Characteristics of the Sensor Adapted from [Technologies 2011d]

# 3.3 Multi-channel Transceiver, CHOSeN SmartTransceiver

The multi-channel transceiver ASIC is a System On Chip (SOC) outcome of the project CHOSeN<sup>6</sup>. Main objective of the project CHOSeN project was to develop application-specific adaptable communication technologies using smart wireless sensor networks in application fields like the automotive and the aeronautic. The CHOSeN SmartTransceiver is enabling a wireless communication interface of a low power sensor node in order to establish a cooperative and heterogeneous sensor network. [FP7 a]

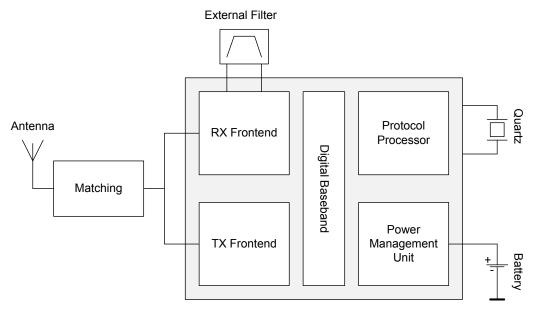

# 3.3.1 Overview

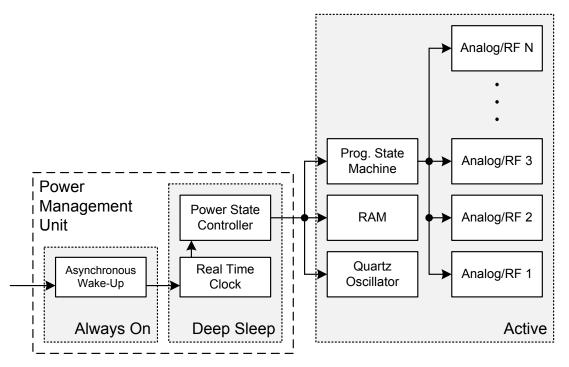

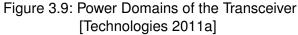

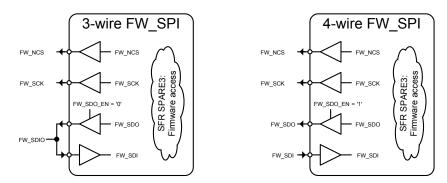

The ASIC is a low power Amplitude Shift Keying (ASK) and Frequency Shift Keying (FSK) transceiver for low data rate communication in the sub 1 GHz frequency bands. For SRDs the frequency range of 868 MHz up to 870 MHz has been available. A basic block diagram of the multi-channel transceiver is shown in figure 3.8. The main building blocks of the transceiver are the receiver (RX) and transmission (TX) front end, the digital baseband unit, the protocol processor, and the Power Management Unit (PMU). A quartz crystal is used for generating the reference frequency, and optionally an external ceramic filter can be used to improve the robustness and sensitivity of the receiver. The matching network of the transceiver is off-chip and can also include an interface for a wake-up receiver. [Technologies 2011a]

<sup>&</sup>lt;sup>6</sup>EU Project within the 7<sup>th</sup> Framework Program (ICT-2007-224327)

Because the main objective of the thesis is the development of a low power metering unit of small feature size for line voltage devices further sections elaborate blocks which are relevant for this application, like the protocol processor including used modules and the power management unit. Analog receiver and transmission front end as well as the digital baseband unit are based on the TDA5340 developed by Infineon Technologies AG [Technologies 2011c]. Details and the external wiring of the matching network can be found in the manual [Technologies 2012b].

### 3.3.2 Protocol Processor

The protocol processor consists of a programmable state machine and RAM for saving configurations. The state machine is a small Application-Specific Instruction-set Processor (ASIP), designed as a Reduced Instruction-Set Computer (RISC). It can be programmed in a very limited *C* subset that can be translated into machine code by a special compiler. The data path width also used for receiving and transmitting is 16 bit. [Technologies 2011a], [Technologies 2011c]

#### **Program Memory**

This architecture contains eight physical Read-Only Memory (ROM) pages each containing 2048 instructions, directly addressable by the state machine through its program memory addressing output. Accordingly there are 16 kWords ROM available. Switching between these external ROM pages is done explicitly using a so-called Dynamic Interrupt Vector Table (DIVT) module. This can be done by either jumping into the vector table or by switching into low power modes and waking up upon specific interrupts. [Technologies 2011c]

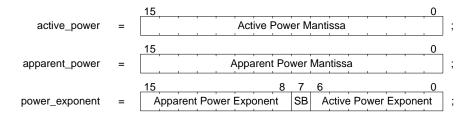

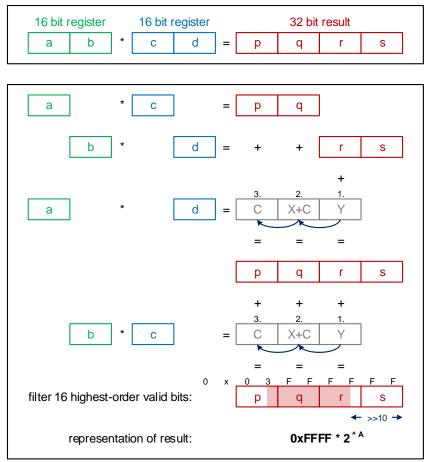

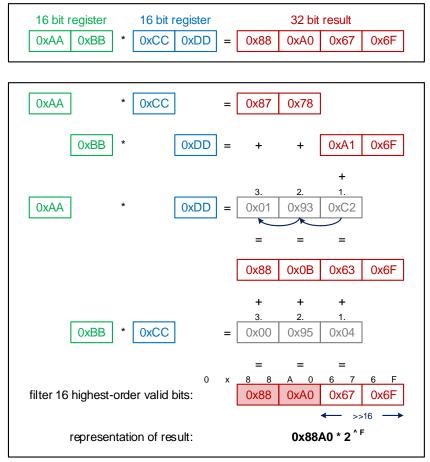

#### **Data Memory**