# **Harald Etschmaier**

# Novel interconnect technologies for packaging of microelectronic power devices

# **DOCTORAL THESIS**

For obtaining the academic degree of

Doktor der technischen Wissenschaften

Doctoral Programme of Technical Sciences Technical Physics

**Graz University of Technology**

Supervisor: Peter Hadley, Univ.-Prof. PhD Institute of Solid State Physics

Graz, February 2012

## Acknowledgments

During the past years I have collaborated with many different people who help me with my work and taught me in their field of expertise. I would like to use this opportunity to thank them all and mention a few.

I owe great thanks to Peter Hadley for his support and advice not only in scientific matters. I highly appreciate his efficient methods and motivating attitude from which I could benefit in many ways. I want to thank Hannes Eder who introduced me in the world of semiconductors and who always found the time to discuss my ideas and inspire me to new ones.

Thanks to Roland Resel, Jiri Novak and Markus Neuschitzer with whom I had the opportunity to conduct exciting in-situ X-ray diffraction experiments. Thanks Adolf Winkler and Walter Lukesch for exploring the secret of the Argon bubbles with me. I would like to express my appreciation towards my friends and coworkers at UPD 5 Andre Brockmeier, Thomas Fischer, Bernhard Goller, Marcella Hartl, Mark Harrison, Karsten Koblinski, Fritz Kröner, Gerald Lackner, Ingo Muri, Markus Ottowitz, Francisco Santos, Tobias Schmidt, Karin Schrettlinger, Martin Sporn and Sigrid Wabnig. Their professional support, their good company during these exciting times and the constant supply of cakes for my physical well-being have kept me going. I also received great support from my coworkers outside my immediate department at the Infineon sites in Villach, Regensburg and Warstein. Esspecially I want to mention Martin Faccinelli, Magdalena Forster, Alexander Heinrich, Philipp Koch, Wolfgang Köll, Kurt Matoy, Dietlinde Nagler, Evelin Napetschnig, Ivan Nikitin, Frank Paul, Michael Pinczolitsch, Mathias Plappert, Gerold Rangger, Katharina Schmut, Holger Torwesten, Hansi Voigtländer, Ulrich Wilke and Sandra Wirtitsch. Thanks for the scientific and non-scientific discussions during the extensive lunch and coffee breaks, the great atmosphere and the many little things that helped me to write this thesis.

A great thank you goes to the people of the failure analysis lab in Villach for all the beautiful images from the SEM, FIB, SAM, etc.

Particularly I want to thank my parents, my brother, Petra and Georg for their constant support and patience during the last years.

In conclusion I recognize that this research would not have been possible without the funding from Infineon Technologies Austria AG and I want to express my gratitude to the company.

### Abstract of the thesis

In order to function a microelectronic chip has to be connected to the macroscopic world and at the same time it has to be protected from harmful environmental influences. For this purpose the chip is packaged, which in most cases involves the attachment of the bare silicon chip to a metal substrate that provides the necessary mechanical stability, electrical connection and cooling. This thesis deals with novel interconnect technologies to create this joint between the silicon chip and the carrier substrate.

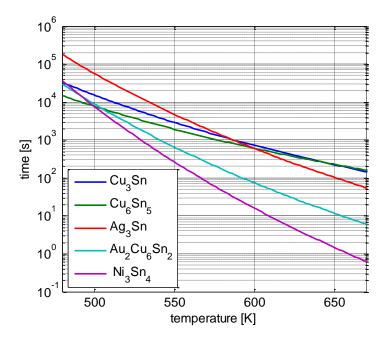

One method extensively studied in this work is diffusion soldering. It allows the formation of soldering joints with a thickness in the range of a few micrometers which can withstand service temperatures much higher than the soldering temperature. The formation of intermetallic phases during the process was investigated by various methods including in-situ X-ray diffraction and focused ion beam microscopy. Based on these results a semi-empirical model was found to describe the temperatures dependence of the reaction speed for various material systems.

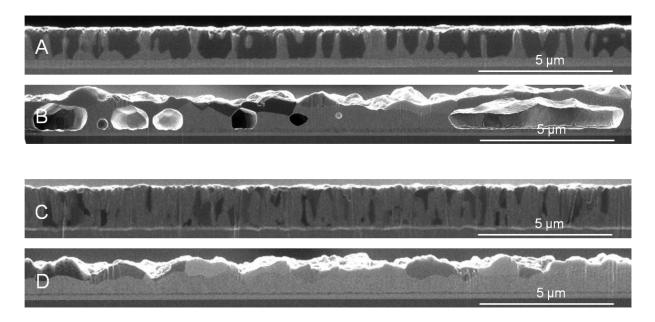

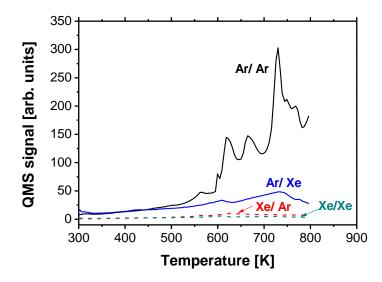

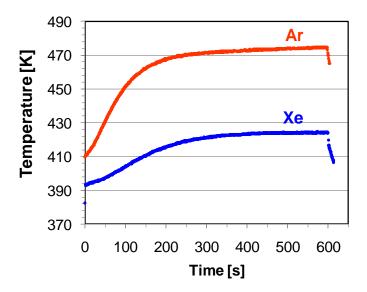

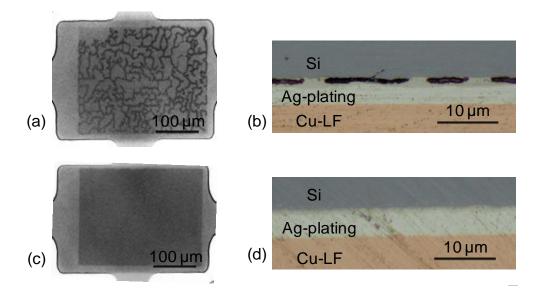

An important factor for the quality of such a joint is next to the process parameters the condition of the used materials. It was found that during sputtering of the eutectic gold/tin alloy, which is commonly used as a solder, significant amounts of the discharge gas can be incorporated in the film. This causes voids in the joint affecting its properties negatively. The effect is described by a model of elastic collisions and can be avoided by replacing the lighter discharge gas argon with the heavier xenon.

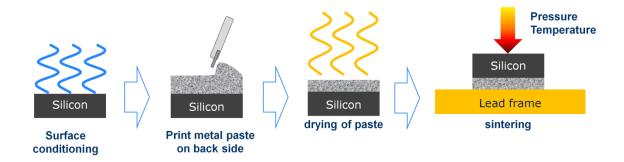

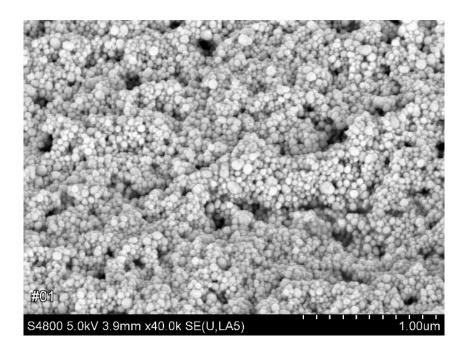

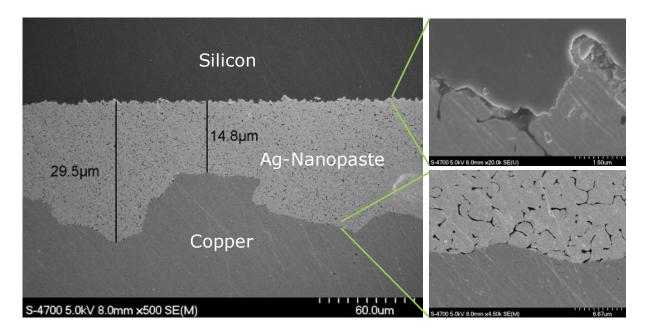

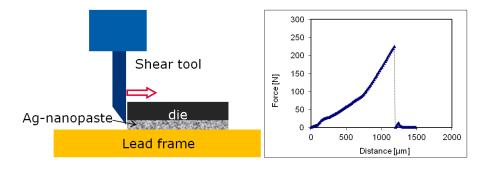

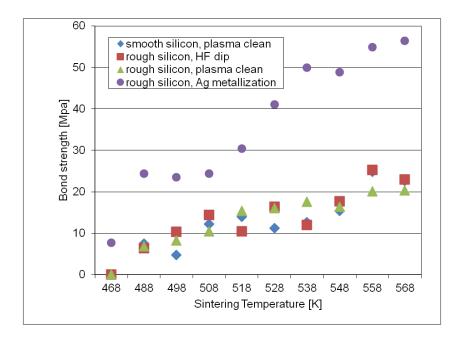

As an alternative to soldering the sintering of silver nanoparticles is explored. The nanoparticles form interconnects at low temperatures without the transition to a liquid phase or the necessity of a wafer backside metallization. The produced joints were tested in terms of the mechanical adhesion and their electrical performance. The results make this backside metallization-free die attach seem unsuitable for the attach of power device but it may find applications with logic chips, which do not require such high electrical conductivities.

# Kurzfassung der Dissertation

Damit ein mikroelektronischer Chip voll funktionsfähig ist, muss er einerseits mit der Makroskopischen Welt in Verbindung stehen und andererseits aber auch vor schädlichen Umwelteinflüssen geschützt sein. Zu diesem Zweck wird der Chip verpackt, was in den meisten Fälle die Fixierung auf einem metallischen Substrat miteinschließt, welches für die notwendige mechanische Stabilität, elektrischen Anschlüsse und Kühlung sorgt. Diese Dissertation beschäftigt sich mit neuartigen Fügetechnologien um diese Verbindung zwischen dem Silizium Chip und dem Trägersubstrat herzustellen.

Ein großer teil dieser Arbeit behandelt die Methode des Diffusionslötens, mit welcher Lötverbindungen mit Dicken von nur wenigen Mikrometern hergestellt werden können. Diese Verbindungen können Temperaturen aushalten die deutlich über der Löttemperatur liegen. Mittels verschiedener Methoden wie in-situ Röntgen Diffraktometrie und Fokussierter Ionenstrahl Mikroskopie wurde die Dynamik der Bildung der intermetallischen Phasen während des Prozesses untersucht. Basierend auf diesen Ergebnissen wurde ein halb-empirisches Modell erstellt um die Temperaturabhängigkeit der Reaktionsgeschwindigkeit für verschiedene Materialsysteme beschreiben zu können.

Neben der richtigen Wahl der Prozessparameter ist der Zustand der Ausgangsmaterialien ein wichtiger Faktor für die Qualität der Lötverbindung. Während des Sputterns der eutektischen Gold/Zinn Legierung, die oft als Lot verwendet wird, kann es zum Einschluss von Entladungsgas in den Film kommen. Dies führt weiter zu Hohlräumen in der Fügestelle, die deren Eigenschaften negative beeinflussen. Der Effekt kann vereinfacht durch ein elastisches Stoßmodell beschrieben werden. Wird das leichte Entladungsgas Argon durch das schwerere Xenon ersetzt wird der Gaseinschluss vermieden.

Als Alternative zum Löten wurde das Sintern von Silber-Nanopartikeln getestet. Mit Hilfe der Nanopartikel können Verbindungen hergestellt werden ohne den Übergang zur flüssigen Phase und daher auch ohne die Notwendigkeit einer Metallisierung der Waferrückseite. Die hergestellten Verbindungen wurden auf ihre mechanische Haftung und elektrische Leitfähigkeit getestet. Durch die erzielten Resultate erscheint es unwahrscheinlich das diese Methode für Leistungshalbleiter zum Einsatz kommt. Ein möglicher Anwendungsbereich sind jedoch logische Schaltungen die weniger gute elektrische Leitfähigkeit vorraussetzen.

# 1 Introduction to semiconductor manufacturing

he development of microelectronics is considered one of the most important achievements of our times, comparable to the invention of the steam engine or the discovery of electricity. It has revolutionized the fields of communications, information processing, and computing and the technology is still evolving rapidly. It has become an almost invisible part of our everyday lives, and yet our modern life style wouldn't be possible without it. Microchips are in everything from mobile phones to vacuum cleaners. A modern medium-sized car for instance contains more than 1,000 chips and up to 80 networked electronic systems.

Electronic devices are often used for vital tasks such as the trigger of an airbag, the control system of a plane or a cardiac pacemaker. Thus reliability is a very important theme and a lot of engineering effort and money is spent to prevent untimely failures that might have fatal consequences.

The reduction of power consumption has not just recently become another important issue. The internet is based on server farms around the world which consume electric power and transform it into heat. All this energy is lost due to the inefficiency of electronic devices, from the power converter to the processor. Including the energy necessary for cooling of the servers about 14 GW worldwide are consumed for only this purpose. [1] This example is to illustrate that the increase of the efficiency of microelectronic devices has great potential to contribute to an economical handling of energy.

Because electronic devices are used so much it is becoming increasingly important that they are environmentally friendly not only in their function but also by the materials they are made of. The cycle life time of electronic products is becoming shorter and more and more electronic scrap is disposed in landfills. Often these parts contain hazardous materials such as heavy metals or

halogens, which over time can leak out and poison ground water and people. Thus there are governmental regulations in many countries that ban the use of these harmful materials in electronics manufacturing.

This thesis considers one small aspect of the total semiconductor manufacturing process: the bonding the silicon that contains the transistors to the metal frame that holds the silicon in the final product, the die attach. Traditionally the silicon was soldered to the frame using Pb/Sn solder. The lead has been banned due to environmental concerns. Here alternatives to the traditional soft soldering using Pb/Sn are described and it is shown that they have better performance and greater reliability than the traditional soldering.

In the first chapter a short review of semiconductor processing is given so that the reader can get an impression of the place of the die attach among the many processes involved in the production of a microelectronic device. The production line starts with the preparation of the raw materials, the growth of the semiconductor crystals, which are cut into the raw wafers. The electrical functionality is given to the semiconductor in the planar process, involving many unit processes. In the last processing block, the back end of line, the raw chips are packaged to form functioning electrical circuits.

The material presented in this chapter was in parts obtained during the work of this thesis but is not of scientific novelty. Its purpose is to serve as an introduction for the reader, to make him familiar with the topic of semiconductor packaging.

# 1.1 Crystal growth

The vast majority of semiconductor devices are based on silicon due to its great abundance, electronic properties and relatively easy processing. Elementary silicon is won by the reduction of quartz sand with carbon at temperatures just below the melting point of silicon. Iron is added to the reaction chamber to prevent the formation of silicon carbide. [2] To be used for electronics manufacturing the silicon has to be further purified. The silicon is reacted with hydrofluoric acid to form trichlorosilane, which is liquid at room temperature and thus can be separated from

impurities by distillation. Then the process is reversed. The trichlorosilane is heated together with hydrogen to a temperature of 1100°C and elementary silicon is precipitating from the gas phase in polycrystalline form. The so called electronic grade silicon has only one impurity atom every one billion silicon atoms, but often this is not enough for the production of devices. [3]

To be used as a substrate in semiconductor technology the silicon has to be in a single crystalline form. The majority of the single crystal silicon ingots are grown by the Czochralski method. The polycrystalline silicon is melted in a rotating quartz crucible and dopant atoms are added to achieve the desired electronic properties. A silicon seed crystal is dipped into the melt and slowly withdrawn. The liquid silicon solidifies upon contact with the seed crystal, adopting its crystalline orientation. This way a cylindrical silicon single crystal (ingot) is made. The ingot can be grown at a speed of 2-20 cm/s, where its diameter is the smaller the faster the pulling speed is. [4] A disadvantage of the Czochralski method is that impurities from the walls of the crucible like oxygen, carbon or boron can get into the silicon. Thus for the production of ultrapure silicon the floating zone process is applied. This process relies on the fact that most impurities have a higher solubility in the melt than in the crystalline material. A cylinder of polycrystalline silicon is mounted vertically, so that its upper end is touching the seed crystal. The top of the cylinder is locally melted by a high frequency magnetic field so that the liquid can wet the seed. The disc shaped liquid zone is moved from one end of the cylinder to the other, taking the impurities with it and concentrating them on one end of the crystal. This way, single crystals with impurity concentrations down to 10<sup>10</sup> cm<sup>-3</sup> can be grown. [2]

Next the ingots are sliced into thin wafers by an annular diamond blade or a wire saw. The wire saw inflicts less damage to the wafer surface but has also a lower cutting speed. The surfaces produced by the cutting process are rough; defects in the crystal lattice have been introduced. Thus about 50 µm of the surface of the silicon wafer have to be removed by mechanical and chemical methods, so that the undisturbed crystal surface is exposed. [5] Currently the standard diameter of silicon wafers is 200 mm, but 300 mm are already being implemented. An increase in wafer diameter is connected to significant reduction in production costs of the semiconductor devices as the number of chips that can be made from a single wafer is roughly proportional to the square of its diameter.

# 1.2 Planar manufacturing technology

The basis of the fabrication of highly integrated circuits on silicon is the planar process. It consists of a series of unit processes which are applied to the complete wafer surface. In most cases their effect is limited by suitable masks to specific locations on the semiconductor enabling the processing of hundreds of billions of transistors on a single wafer at the same time. By sequentially applying hundreds of these unit processes, the electrical functionality is given to the semiconductor material. Generally the wafer processing can be subdivided in two parts: The front-end-of-line refers to the patterning of the individual devices directly in the semiconductor, whereas the back-end-of line includes the interconnection of the devices with metal wiring on the wafer.

#### 1.2.1 Oxidation

A typical unit process sequence starts with the oxidation of the silicon. The silicon oxide layer can serve as an insulator, e.g. the gate oxide of a transistor, a mask to protect the underlying silicon locally from a subsequent process, a diffusion barrier to inhibit the diffusion of dopants out of the silicon, or simply as a passivation layer to protect the surface of the wafer. The oxide layers used in the planar process are either generated by thermal oxidation or chemical vapor deposition. Thermal oxidation can be split into dry and wet oxidation. Dry oxidation uses oxygen as the reactive gas, which produces high quality oxide layers at low speed which have a higher resistivity to electrical stress whereas for wet oxidation water is added to the oxygen gas. This speeds up the reaction, but decreases also the layer quality. If there is not silicon available for oxidation, for instance on an aluminum metallization, the oxide can be deposited directly. The most important methods for this process are the tetraethyl orthosilicate (TEOS) deposition or the low temperature oxidation of silane. The high quality and superior electrical properties of silicon oxide is the most important reason why silicon is still the dominant material in semiconductor industry.

#### 1.2.2 Lithography

To pattern the silicon oxide layer a lithography step is applied. In this process the layout information is transferred from a mask onto the wafer. The layout is recorded on a set of masks which defines the specific patterns necessary for the device fabrication, e.g. the gate area of a transistor. They are recorded on a radiation sensitive film, the resist, which the wafer is coated with. This resist is usually an organic compound that changes its properties upon exposure to radiation. The resist can be either positive or negative. Positive resist is dissolved during the development where it has been illuminated and the not illuminated areas stay covered. The kind of radiation used mainly determines the minimum feature size that can be transferred as it is limited by the wavelength. Standard lithography tools work with ultra violet light at wavelength of 436 nm and 365 nm which is the G- and I-line of the mercury spectrum or with a deep UV laser at 248 nm and 193 nm. [3] The minimum feature sizes that can be resolved on planar surfaces with this technology are 0.8 µm and 0.4 µm respectively. Advanced technologies like X-ray lithography (XRL), electron projection lithography (EPL), and ion projection lithography (IPL) are currently introduced into commercial semiconductor production allowing the generation of feature sizes down to 32 nm. [6]

#### 1.2.3 Etching

To transfer the patterns of the resist layer to the underlying material, an etching process is applied. In semiconductor processing the most common materials to be etched are silicon oxide, silicon nitride, silicon, aluminum, tungsten and titanium. The etching can be achieved chemically by wet etching, physically by dry etching or by a combination of both.

Wet etching transforms the solid material into a liquid compound by the application of an acidic or alkaline solution. The wet etching is generally very isotropic and selective, which means that the etch rate is similar along all directions, but it depends strongly on the material that is removed. The process suffers from poor reproducibility because the etch rate is very unstable and extremely difficult to control. The isotropy of the process also limits its applicability as it results in a so-called under etching effect which can lead to a partial or full detachment of the mask from

the underlying material and makes it unsuitable to transfer patterns with sub-micron features. [7] Furthermore the devices are often contaminated by etching agents. Thus wet etching is mainly used for the removal of whole unpatterned layers.

With dry etching in contrast, reproducible and homogenous etching of most materials used in the planar process is achievable. In this technique the material is removed by momentum transfer between plasma particles and the target material. The etching can be isotropic as well as anisotropic depending on the process parameters like the pressure in the plasma chamber. The lower the pressure the higher is the resolution but the lower is the selectivity. With the right parameter set it is possible to transfer structures with sub-micron features.

#### 1.2.4 Implantation

The patterns produced this way can again be used as masks to locally introduce dopant impurities into the crystal. Typically a masking layer of 1 µm thickness is sufficient to absorb the ions. Apart from silicon dioxide also silicon nitride, polysilicon, aluminum or some photo resists are suitable as masking layers. [6] The dopants can enhance, attenuate or inverse the substrate doping in specific areas as needed for the functionality of the device. As acceptors elements of the third group, i. e. boron, aluminum, gallium and indium are available. Of these only boron has a sufficient solubility in silicon to achieve a high conductivity. As donors elements of the fifth group could be used in principle, but only phosphor and arsenic have a sufficient solubility and antimony can be used only for weak doping. Historically the impurities were introduced by alloying and diffusion, but due to reason of reproducibility nowadays in industry mainly ion implantation is used. [2] A beam of ionized dopant atoms is accelerated in an electrical field towards the wafer. The ions penetrate into the target and dissipate their kinetic energy by elastic and inelastic collisions with the atoms of the substrate material. The penetration depth of the ions is proportional to their acceleration voltage, which can be controlled very accurately. The absolute dose of ions can be controlled by the charge introduced to the substrate. Thus it is possible to generate very well controlled doping profiles, which is necessary for achieving the desired electrical functionality. The bombardment with the high energy ions damages the lattice of the semiconductor crystal and thus alters its electrical properties. Furthermore the dopants introduced by implantation initially reside on interstitial lattice site where they are electrically inactive. To heal the crystal and electrically activate the dopants, a high temperature annual is necessary after implantation.

#### 1.2.5 Deposition

The completed semiconductor wafer is composed of many layers with different properties and functions. They are either part of the integrated circuit or serve as sacrificial layers that are removed in a later processing step. These layers have to be deposited on the substrate with temperature and intrinsic stress as low as possible. They can be single crystalline, polycrystalline or amorphous. Most often deposition is used to produce on-chip interconnections of the single circuit elements. If those interconnections would be done on the same level as the active elements they would consume up to 80 % of the surface area of the chip. [8] Therefore multilevel structures have been developed, consisting of patterned conducting layers and silicon dioxide as insulator in between. As conductor aluminum, copper and also polycrystalline silicon are available. The latter is only used for short interconnections with low current densities due to its high resistivity. The conducting layers are connected with each other by vertical interconnect areas (vias). Generally there are two lower levels of polycrystalline silicon and 2 to 6 levels of metal on top. [3] Especially power devices require an electrical connection not only on the front side but also on the back side, which often has to carry large currents. Usually this backside metallization is not patterned and has to provide and mechanically stable connection with a low thermal and electrical resistivity. Often all of this cannot be achieved by a single metal layer. Therefore a multilayer stack, consisting of a contact layer, a diffusion barrier, a wetting layer and an oxidation protection layer is applied. The contact layer has to provide good ohmic contact and adhesion to the semiconductor; the diffusion barrier prevents intermetallic compound formation between the contact layer and the cover layer, which would have a negative influence on their performance and the cover layer provides the interface to the package and has to be chosen according to the chip-package interconnection technology used.

The different technologies which are available for deposition can be divided in chemical vapor deposition (CVD), electrochemical deposition (ECD), and physical vapor deposition (PVD).

#### 1.2.5.1 CVD

CVD is mainly used to deposit polysilicon, silicon oxide or silicon nitride. It is based on the thermal dissociation of chemical compounds in the gas phase upon contact with the hot substrate. The precursor gas contains all components necessary for the growth of the layer. The substrate itself does not take part in the reaction. The gas molecules are split in a solid part that attaches to the substrate surface and a gaseous part which is removed by convection. [9] This process requires a high temperature of the substrate which is not always acceptable. A technology to overcome this problem is the plasma enhanced chemical vapor deposition (PECVD), where the dissociation of the molecules is enhanced by high-frequency gas discharge. PECVD can be done in the temperature range between 250 °C and 350 °C, whereas for standard CVD often 900 °C are necessary. [10]

#### 1.2.5.2 ECD

Electrochemical deposition or simply electroplating is another process widely used in semiconductor industry for the deposition of metal layers.[11] It has several advantages compared to PVD and CVD due to its low cost, low processing temperature, and good ability to fill structured surfaces. [12] Simplified, the deposition of the metal layer is achieved by putting a negative charge on the wafer and immersing it into a solution which contains a salt of the metal, called the electrolyte. The wafer acts as the cathode of the electrolytic cell and the positive metal ions in the electrolyte are attracted to it. Upon contact with the wafer the ions are reduced and converted into their metallic form. The ions can be supplied directly from the anode, which is in this case consumed over time, or they can be added directly to the electrolyte and the anode is made from an inert metal like platinum. A requirement for ECD is a conducting substrate. The bare silicon wafer cannot be plated directly but a conducting seed layer is needed, which has to be applied in a separate process step by PVD.

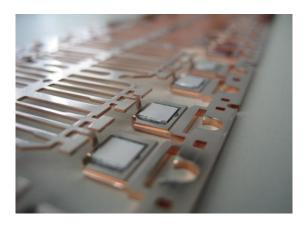

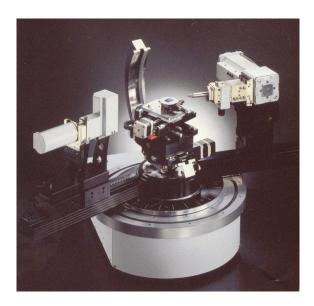

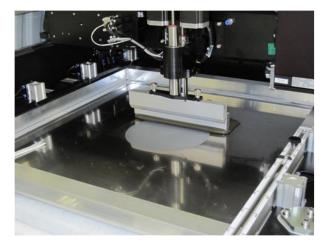

For industrial application it is important to achieve a good thickness uniformity of the deposited layer as well as high deposition rate. Therefore commercial electroplating is a very sophisticated operation with means for agitation, filtration, electric field shaping, temperature control, and multistep or pulsed current programs. Organic additives are added to the electrolytes to improve the film morphology and surface roughness. The right part of Figure 4 shows an industrial scale plating line for deposition of multilayer metal stacks as it was used for the work in the thesis.

#### 1.2.5.3 PVD

Physical vapor deposition involves the condensation of a vapor from of atoms, molecules or clusters on a substrate surface. The material physically adsorbs to the surface without any chemical reactions and thereby forms a solid film. Typical PVD processes include evaporation, molecular beam epitaxy (MBE) and sputtering.

The simplest and oldest method to deposit metal layers is thermal **evaporation**. The metal is heated either by resistance heating in a tungsten carrier or by an electron beam in high vacuum (HV) so that the atoms escape into the gaseous phase. In the vacuum there are only little particles so that the mean free path of the metal atoms is larger than the distance between the evaporation source and the wafer. The particles travel on strait trajectories towards the wafer and condense on its cooler surface in polycrystalline form. Because their kinetic energy is so low (~0.1 eV) they cannot damage the substrate surface. [13] Due to the straight trajectories of the metal atoms the method has very poor side wall coverage on structure wafer front sides. Thus it is most suitable for cheap coating of planar wafer backsides.

MBE is mainly used to deposit thin layers of doped silicon or other semiconductor materials. Pure silicon or another semiconductor is evaporated by an electron beam in an ultra high vacuum (UHV) chamber. At the same time dopants can be added to the beam by resistance heated Knudsen effusion cells. The atoms hit the surface of the substrate where they form homoepitaxial, single crystalline layer. [10] The deposition temperature of about 700°C is too low for significant diffusion of the dopants. Thus it is possible to achieve very well defined pn-junctions with this method. A major drawback is the slow layer growth of only 1 μm/h and the necessary UHV.

Only about 10 wafers can be processed per tool per day and it is therefore not suitable for mass production. [3]

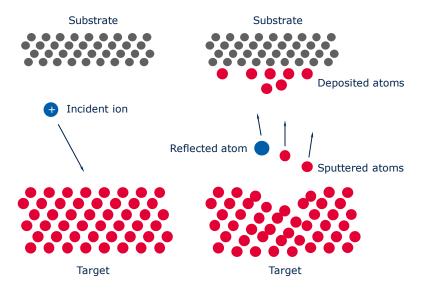

To overcome the disadvantages of thermal evaporation, **sputtering** is widely used for metallizations in semiconductor manufacturing. [14] Typically in sputtering, inert gas ions are accelerated towards a target. These ions knock atoms of the target loose which diffuse in the gas phase over to the substrate where they condense and form a solid film. This process is not affected by the temperature and therefore it is possible to produce a gas phase from a cold solid. [15] The interaction between the high energy inert gas ions and the atoms of the solid can be seen as an elastic collision. For this case the momentum transfer between two particles is most efficient when the particles have similar mass. The atoms in the sputtered target, are not isolated but they are rather within a matrix of metal atoms. Thus the impact of high energy ions does not only sputter atoms, but also causes damage to the target. The dependence of the sputtering efficiency on the energy of the ions, the involved materials and other factors is complicated. It can be described by a quantity named sputtering yield, which is defined as the ratio of emitted atoms of the target material to the number of incident particles. A schematic of the sputtering process is shown in Figure 1.

Figure 1: Schematic of the sputtering process. An incident high energy ion transfers momentum to atoms of the sputter target, vaporizing the matter. The sputtered atoms condensate on the substrate.

Once the atoms are in the gas phase they readily condense on any surface available as they are not in thermal equilibrium with the surroundings. A wafer is positioned in closed distance to the target, so that most of the depositing atoms can form thin homogeneous films on its surface. When the atoms condensate on the wafer surface, their kinetic energy as well as their energy of recrystallization is converted to heat. Therefore the wafer is heated during the process until it reaches a radiative equilibrium with its surroundings. The final temperature depends very much on the deposition rate.

The most prevailing method for sputtering in semiconductor industry is discharge sputtering. In this setup the sputtering chamber is designed like a discharge tube. It is composed of two facing electrodes in the sputter chamber. The wafer resembles the anode which is grounded and on the cathode, to which the target is fixed, a high negative voltage is applied. The space in between the electrodes is filled with a noble gas, usually argon. Electrons are emitted from the target and accelerated in the electrical field towards the wafer. They collide with the Argon atoms and ionize them. The generated ions and electrons are accelerated themselves, hit other Argon atoms and cascade is started. Eventually the ions hit the target surface, where the generate secondary electrons and free neutral atoms. The secondary electrons are necessary to sustain the plasma and the neutral atoms make up the deposited material. [15]

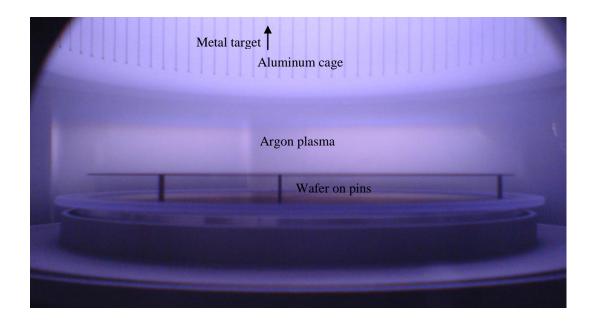

In order to achieve a high deposition rate which is a requirement for an industrial process, a high plasma density and a high gas pressure of about 100 Pa is required, but this in turn hinders the sputtered neutral atoms to reach the wafer. Additionally the secondary electrons that are accelerated in the electrical field are heating the target material and it can ultimately exceed its melting point. For this reasons a magnetic field parallel to the target surface is applied, which forces the electrons on a cycloid path close to target surface. The ion generation is strongly enhanced in this very limited space and sufficient ions are generated even at gas pressures down to  $10^{-2}$  Pa. [13] This allows the sputtered atoms to travel from the target to the wafer without being scattered by the discharge gas atoms. The method of sputtering using an electrical and a magnetic field is called magnetron sputtering. For reasons of conformity the electrical field is often rotated around an axis perpendicular to the wafer surface at low frequencies. Figure 2 shows the setup of the wafer in the magnetron sputtering chamber.

Figure 2: Argon plasma inside a vacuum chamber during plasma etching. The wafer is resting on three pins underneath the target in the loading position. For sputtering it is lifted up closer to the target. (Courtesy of Mark Harrison)

Some of the noble gas ions that hit the target get implanted but most of them are reflected. Their charge is neutralized upon impact and they are no longer affected by the electrical field. For an acceleration voltage of about 1 keV, their energy is in the range of several tens to a few hundreds of electron volts. This energy strongly depends on the target material and the discharge gas used. The more similar the atomic masses of the two elements are, the more energy can be transferred from the discharge gas atom to the sputtered atom and the less energy is left for the reflected atoms. These atoms can collide with the deposited film and hinder its growth. They can directly hit already deposited metal atoms and hammer them inside the deposited film. These atoms reside then on interstitial sites inside the crystal lattice expanding it and causing a compressive stress in the deposited film. [16] This effect is called the "peening effect".

The reflected noble gas atoms can also be incorporated in the deposited film themselves. They have a kinetic energy high enough to be implanted directly into the metal. [17] An incorporation of the noble gas atoms by simple adsorption is very unlikely, because the adsorption energy of the gas atoms on metal surfaces ranges only from 0.05 to 0.35 eV. [15]

Additionally to these properties, sputtered thin films have a very distinctive columnar structure.

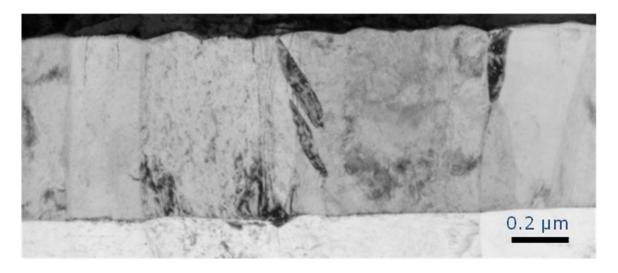

[18] The transmission electron microscope (TEM) image in Figure 3 shows a cross section of a

typical sputtered thin film. The eutectic Au/Sn film on top of a titanium film was prepared by magnetron sputtering. Single crystalline columns grow perpendicular to the film surface. As a general rule of thumb the columns are wide and well defined at high temperatures and low discharge gas pressures. At increasing temperature and lower pressure the columns become smaller and thinner and the film surface becomes rougher. [19]

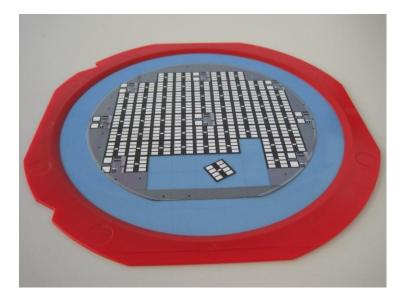

Industrial scale metallization tools often include multiple deposition chambers for different metals together with an automatic wafer handling system. With this setup it is possible to deposit multiple metal layers on top of each other without exposing their surface to the atmosphere before the complete stack is finished. In the left part of Figure 4 a magnetron sputter tool with six chambers that was used for the film preparation in this thesis is shown.

Figure 3: Transmission electron microscope image of a eutectic Au/Sn film on top of a titanium layer. The films were prepared by magnetron sputtering and show the typical columnar structure.

Figure 4: Technical scale equipment used for deposition of metal layers. Left: Sputter tool Oerlikon Clusterline 200 with six sputtering chambers. Right: NEXX Stratus 200 electrochemical plating line

#### 1.2.6 Singulation

After the wafer has gone through all the processes of the planar technology it contains from hundreds to hundred thousands of chips which themselves can consist of one to one billion transistors. The single chips are separated from each other by a 50 to 100 µm wide area, the "scribe line". In this area there are except from test structures no circuit elements, as it is destroyed when the wafers are cut into single chips, the so called dies. In a conventional processing flow, the wafers are mounted on a dicing tape and clamped into a rigid frame. The dicing can be done either by laser cutting or by mechanical sawing, which is the prevailing method with a market share of more than 90 %. [20] For sawing, a diamond blade rotating at high speed with a thickness ranging from 20 to 50 µm is used. The process is abrasive, similar to grinding and produces chipping and cracks at the die edges. To achieve smoother edges and narrower dicing streets a high power Nd:YAG laser is employed. In this technology the material is removed by ablation. The material is locally evaporated and partially deposited on the wafer surface and the sidewalls of the die. To avoid this contamination the wafer surface can be protected by a coating that is washed off after the process. Another possibility is to use a water

guided laser. The laser is coupled into a water beam, tens of microns in diameter, which is washing off most of the generated debris and cools the dicing street (see Figure 5). [20]

After dicing, the chips are ready for the final electrical test and packaging (see Figure 6).

Figure 5: A pulsed high power Nd:YAG laser with a second harmonic generator emitting at a wavelength of 532 nm is guided by a narrow water beam to separate the individual dice.

Figure 6: Wafer on dicing foil after singulation. The chips are fully functional and ready for packaging.

# 1.3 Chip packaging

Electronic packages can contain many electrical circuit components like transistors, diodes, resistors, capacitors and other components, all of which have to be connected with each other to form electrical circuits. To function, the electrical circuits have to be supplied with electrical energy which is partially converted heat. Because all circuits operate best within a certain temperature range, this heat has to be removed sufficiently fast. Thus the package has four major functions: It has to distribute signals; it has to provide connections for electrical power; it is responsible for the heat dissipation and it has to protect the bare dies from environmental influences. The electronic packaging technology significantly contributes to the overall performance of the whole system. It is considered to be the biggest bottleneck in the development of microelectronics, because it controls the system's electrical performance, cost, size and reliability. [21]

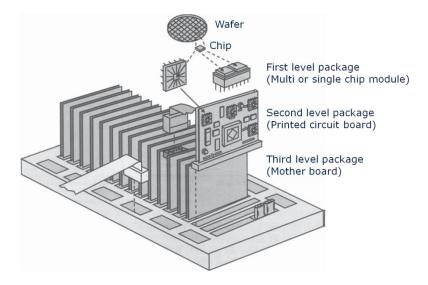

Electronic packaging is done on several levels (see Figure 7). All interconnections which are directly integrated on the chip are commonly not considered as packaging. It begins with the interface of the bare semiconductor chip. This is the first level or chip-level packaging. Modern first level chip packages can also contain more than one chip and are then referred to as multi chip modules. Typically these devices are soldered onto printed circuit boards. These cards make up the second level of packaging. In the example of a personal computer this is a graphics card or a random access memory card. The third level of packaging then provides sockets for these cards to be plugged in. In a personal computer this is the motherboard. Often the packaging hierarchy deviates though from this traditional order, depending on the application. [22]

Figure 7: [21] Schematic of microelectronic packaging hierarchy

The first level involves the attachment of one or more bare dice to a substrate, the electrical connection from these chips to the package leads, and the encapsulation. Especially in power electronic systems, chip-level packaging plays an important role because it directly interfaces with the power chip not only electrically but also thermally and mechanically. The requirements to the power package are different from those to the package of a microelectronic integrated circuit. Larger cross-sectional areas are needed and it has to be able to support much higher current flow. Wide bandgap semiconductors, such as silicon carbide, which are currently developed for high power and temperature applications, drive the development of chip level packaging to improve its performance in heat dissipation and thermal management. Rapid progress in semiconductor manufacturing technology in the recent past has enabled the fabrication of smaller and thinner power electronic chips, with thicknesses in the order of only several micrometers. This imposes a serious challenge to the precision of the first level packaging technology. Furthermore power chips are usually installed in heavy machines like trains or windmills and thus a high lifetime of the first level power-interconnections is needed to ensure the long term reliability of the complete system.

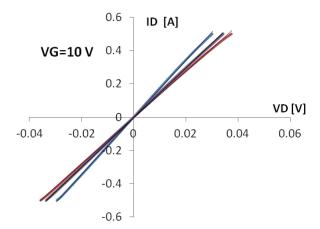

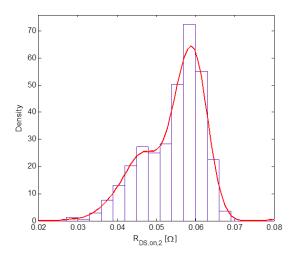

#### 1.3.1 Die attach

Most of the work done in this thesis is concerned with the characterization and development of the die attach process. It is only a small part in the production of a microelectronic device, but its quality significantly affects the performance and especially the reliability of the device. The die attach layer often provides an electrical connection, such as the drain of a power MOSFET or the emitter of an insulated gate bipolar transistor (IGBT). Thus it directly affects the electrical characteristics of the chip, such as the turn-on resistance of the device (R<sub>DSon</sub>). In contrast, the electrical connections of an integrated circuit are usually only on the front side and the die attach layer merely holds the chip mechanically on the substrate. [23]

A low ohmic resistance is a central requirement for the die attach layer in power devices, but even more important is the thermal impedance. The majority of the heat generated by the device is dissipated through this layer. Due to its low thickness and the large area its thermal impedance is much lower than the one of the front side interconnections such as the wire bond or the ball grid array. With a constant power efficiency of the semiconductor device and a maximum operating temperature, the maximum power that can be dissipated by the chip is mainly determined by the thermal properties of the die attach layer. Also a thin chip is advantageous. Although the thermal resistance of silicon is quite low, a thinner layer has still a lower resistance. Often the reliability of the complete system is highly related to the quality of the die attach layer. Due to the mismatch in the coefficients of thermal expansion between the semiconductor of the device and the metal of the lead frame, a considerable thermomechanical stress can occur during the assembly and operation. The die attach layer not only has to withstand this stress but also needs to cushion it in order to ensure a long lasting stability of the system. Good mechanical properties of the die attach material are essential for the reliability of the device.

Recent governmental restrictions that prohibit the use of potentially harmful substances in the production of electronics impose additional requirements on the die attach process. [24] Lead, which was often used as a die attach material due to its high ductility, was banned and new material systems have to be explored to find a suitable replacement.

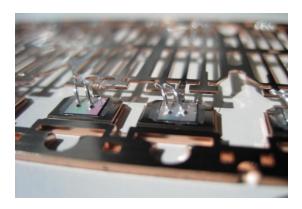

Figure 8 depicts the Tresky T-3202 die bonder which was used for the work of this thesis. The diced wafer on the dicing frame is loaded into the machine. The chips are picked from the foil by a vacuum tool from the top. When the tool touches the chip, needles push it up from beneath at the same time, lifting it up from the sticky foil. Then it is moved over the lead frame and aligned with an accuracy of less than 10 µm by an optical camera. If necessary a solder paste or a conductive glue is applied on the position where the chip will be placed with a pneumatic needle dispenser. For soldering the lead frame is heated so that the solder is melted. The chip is then set down on the lead frame with a specified pressure and the connection to the substrate is formed. Figure 9 shows a chip soldered on a lead frame directly after the die attach. This kind of semiautomatic die bonder is design for maximum flexibility in terms of the process parameters and handling of various chip sizes. Fully automatic die bonders as they are used for high volume production are dedicated to a very limited range of products, but are capable of processing a chip in less than 170 ms. [25]

Figure 8: Tresky T-3202 semiautomatic die bonder. The chips are directly picked from the dicing foil and accurately placed on the lead frame.

Figure 9: Transistor chips on a nickel plated copper lead frame. The chips have been attached with soft solder.

Several methods for die attach are currently used in industry which are applied for various products and can fulfill the requirements to a certain extend:

#### 1.3.1.1 Conductive adhesives

[27]

Electrically conductive adhesives (ECA) are used as a die attach material due to the simple processing and the low curing temperature. [26] They mainly consist of an organic binder matrix and conductive metal fillers. The matrix is usually made of thermosetting polymers, which means that it can be solidified by a curing step and remains in the solid state even if it is subsequently subjected to higher temperatures. In contrast, thermoplastic materials will reflow at high enough temperatures even if the curing has already been done. Because the polymers are bad electrical and thermal conductors, a large percentage of metal filler has to be added. Generally silver flakes and particles are selected for this purpose owing to their high conductivity. Initially the adhesives also contain solvents that lower the viscosity for easier application on the lead frame. These solvents are then decomposed with the help of catalysts during curing. The ECA can be divided into two types: isotropically conductive adhesives for which the conductivity is the same in all directions and anisotropically conductive adhesives, for which the conductivity is enhanced for one direction. This effect is caused by the application of the pressure from only one direction during the die attach. The metal particles mainly form interconnections in this direction of space.

Compared to solder based technologies, ECA have several advantages. They are more environmental friendly as they don't use lead or flux cleaning. They offer a higher resolution capability and can be processed under milder conditions and in fewer steps which reduces the processing costs. [28] However currently commercialized ECAs are still limited in their properties. The majority of the electrical and thermal conduction is attributed to the metal filler particles. Under the mild processing conditions these cannot fuse together and are only in loose contact with each other. This small area of contact is responsible for the low conductivity of the ECAs. Moreover their performance also suffers significantly at elevated temperature or humidity because polymers tend to get unstable under these conditions. All of the qulaities that ECAs lack, high-temperature stability, high electrical and thermal conductivity, are essential for power semiconductor device attachment. Thus ECAs are rarely used in this field of industry.[29]

#### 1.3.1.2 Soft soldering

Compared with ECAs soft solders have better electrical and thermal conductivity and are thus widely used for die attach. There are different methods used to apply the solder to the joint. In reflow soldering a sticky mixture of metal particles und solder flux is printed on the lead frame to temporarily hold the die in place. The entire assembly is then heated over the melting point of the solder. The liquid solder wets the joint surfaces and the bond is formed upon cooling when the solder solidifies.

Another method is to apply the solder directly to the hot lead frame in the form of a wire, a preform or a drop of solder paste. It is melted upon contact with the hot surface and the die is then placed on the liquid metal.

To minimize stress on the device, the melting temperature of the solder needs to be as low as possible. Thus solder alloys usually contain an element that has a low melting temperature such as tin, indium, lead or bismuth. [20] Lead-bearing solders, especially the eutectic and near eutectic tin-lead alloy have widely been used in the assembly of electronic circuits due to its good mechanical properties (e.g. low melting temperature, wettability, mechanical integrity, manufacturability, and affordable cost). [30] However increasing environmental concern about the

toxicity of lead has caused legislative restrictions on its use in electronics assembly. The European Union has banned lead from many electronic applications since 2006 [31], [32]. In the soldering process, the solder reacts with the substrate material to form the bond. The adhesion is initiated by the formation of an intermetallic compound, which is a chemical reaction. Therefore the soldering environment must provide the conditions that favor this reaction. Initially, the solder and the surfaces that need to be joined are covered with oxides. The melting temperature of these oxides is much higher than the soldering temperature and they cannot be melted in the process. [33] For instance Cu<sub>2</sub>O melts at 1235°C and SnO at 1080°C. They also have a lower density than the solder which means that they can float on the surface of the melted solder, forming a barrier that prevents the contact of the joint surface and the solder. This contact is needed to start the chemical reaction and bonding cannot be achieved without the removal of the oxides. For this purpose fluxes are often used. They can reduce the oxides and prevent solder and base metal from further oxidation. In solder pastes they are mixed with the metal particles owing to its pasty consistency. Solder wires often have a hollow core filled with flux. The key components are resin acids, which can react with the oxides forming metal salts. The salt can be dissolved in the molten flux and thus doesn't hinder the soldering reaction.

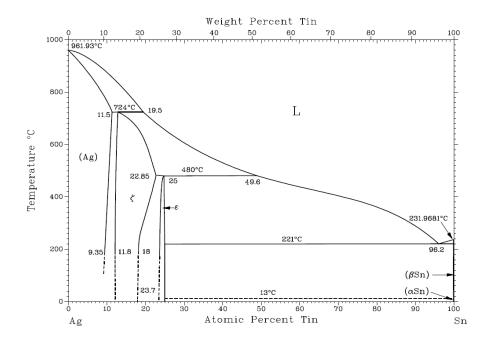

In the following example the lead free eutectic tin-silver solder is used to attach dice with 500 nm thick nickel backside metallization to copper lead frames in a reflow soldering process. An addition of 3.5 wt.% Ag to the Sn reduces the melting point of the alloy by 11°C to 221°C (see phase diagram in Figure 10). This alloy is quite important as it is generally recognized as the first choice for a lead free solder. [30]

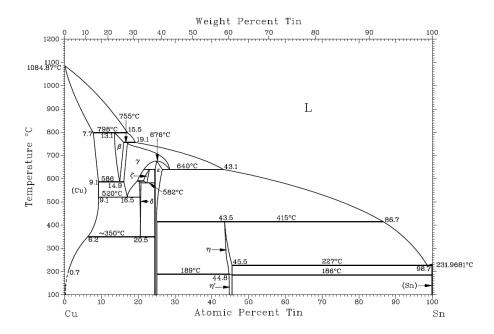

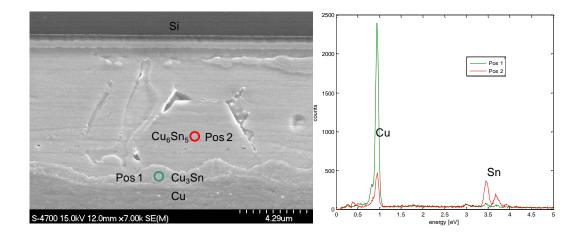

For soldering a 300 µm thick layer of the solder paste is stencil printed on a copper substrate. The dice are then placed on the paste and the whole assembly is then heated in a vacuum oven to the peak temperature of 240°C or 290°C, at which it is held for four minutes. The oven is kept under forming gas atmosphere (4 vol.% H<sub>2</sub>, 96 vol.% N<sub>2</sub>) to prevent the oxidation of the copper substrates. At the peak temperature, vacuum is temporarily applied to suck out gas bubbles in the liquid solder. During the soldering process, the liquid tin reacts with the copper of the substrate forming the Cu<sub>6</sub>Sn<sub>5</sub> intermetallic compound (IMC) on the interface, which is known as the wetting action. This IMC has a melting temperature of 415°C and thus remains solid during a

22

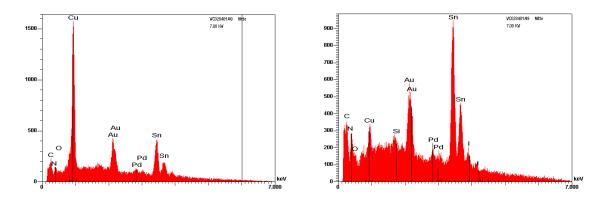

typical soldering process (see Figure 11). On the other side at the interface of the solder with the nickel backside metallization of the die Ni<sub>3</sub>Sn<sub>4</sub> is formed in a similar process. [34] This reaction is much slower though and the intermetallic layer formed is much thinner. The IMC layer links the solder and the substrate together and it is found in all known soldering systems. Without it a soldering process would not be successful. [20] The properties of the IMCs are significantly different from the parent materials. A property that virtually all intermetallic compounds have in common is that they are very hard and brittle materials. On one hand they are crucial for the success of the soldering operation and give strength and fatigue resistance to the joint. On the other hand, if they are abundant in excessive quantities they cause joint embrittlement. [35] At the soldering peak temperature of 250°C and 290°C, 2 at.% and 4 at.% of copper are soluble in the liquid tin respectively. At room temperature the solubility of copper in tin is very low (0.007 at.%) [35] and so the amount that dissolves during soldering will segregate upon cooling in the form of Cu<sub>6</sub>Sn<sub>5</sub> grains. The nucleation happens preferentially at interfaces where the energy barrier that has to be overcome for nucleation is minimal. As can be seen in Figure 12 the Cu<sub>6</sub>Sn<sub>5</sub> IMC is not only found at the solder-lead frame interface but also at the interface between the solder and the die. The higher the temperature, the more IMC is formed. At a reflow temperature of 290°C, there is significantly more Cu<sub>6</sub>Sn<sub>5</sub> on both interfaces compared to the sample reflowed at 250°C. The phases were identified by energy dispersive X-ray spectroscopy (EDX). The recorded spectra are shown in Figure 13.

Figure 10: Binary phase diagram of silver and tin. [36] An addition of 3.5 wt.% silver to the tin is reducing the melting point of the alloy from 232°C to 221°C. (Reprinted with permission of ASM International. All rights reserved. www.asminternational.org)

Figure 11: Binary phase diagram of copper and tin. [36] During the soldering reaction the  $\eta$ -phase (Cu<sub>6</sub>Sn<sub>5</sub>) is formed. (Reprinted with permission of ASM International. All rights reserved. www.asminternational.org)

Figure 12: Scanning electron micrographs (SEM) of the solder-die (top) and the solder-lead frame interface. The solder was reflowed for 4 minutes at a peak temperature of 250°C (left) and 290°C (right). The positions where the EDX spectra shown in Figure 13 were recorded are marked.

Figure 13: Energy dispersive X-ray spectra taken at positions marked in Figure 12. The left spectrum was taken at position 1. It clearly has a high copper content and can therefore be identified as the  $\text{Cu}_6\text{Sn}_5$  phase. At position 2 only a small amount of copper is dissolved in the tin. The gold and palladium lines stem from the sample coating which was applied for SEM investigations.

A common failure mechanism in soft solder die attach is due to voids in the joint. A void is a gas or liquid filled volume in the die attach layer which drastically increases the thermal and electrical resistance between chip and package at that point. Voids can be built in directly during the die attach, be introduced later in the assembly or only occur during operation of the device.

[37]

During the die attach, fluxes or other clean up agents form gases as reaction products which then get trapped in the joint. Also the fluxes themselves can be enclosed in the solder layer. In some cases there are areas on the joining surfaces where the solder does not wet because of the variable nature of the interfaces, e.g. dewetted areas may develop as portions of the metallization are leached away by the solder.

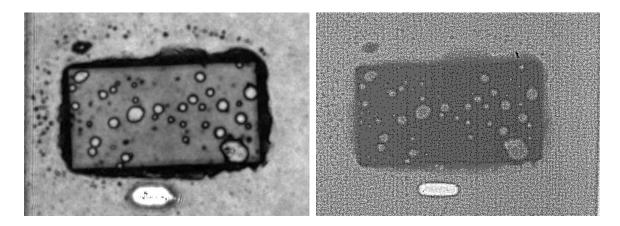

Built-in voids are difficult to control because of the many variables involved, but they can be detected effectively. Figure 14 shows an example of voids in the solder layer of chip detected by X-ray photography and Scanning Acoustic Microscopy (SAM).

Figure 14: Voids in the die attach layer of a reflow soldered chip are detected X-ray photography (left) and by scanning acoustic microscopy (right).

In X-ray photography a void will stand out as brighter, non-absorbing area, especially if the solder contains heavy elements. SAM uses ultrasonic waves that are reflected at solid-gaseous interfaces. Thus voids appear bright in reflection mode and dark in transmission mode. The advantage of the SAM compared to the X-rays is that it is able to detect voids even if they are very thin such as cracks. Cracks are usually introduced after the die attach during cooling,

storage, or operation. They are caused by excessive mechanical stress between chip and package, or by metallurgical fatigue of the solder when the device is temperature or power cycled. Although a crack has almost only a two dimensional shape compared to other voids it still has an adverse effect on the thermal resistance.

A void in the die attach layer will result in a hot spot in the chip area directly above it during operation of the device. The heat generated by the power dissipated in the semiconductor above the void must flow laterally along the chip around the void, thus increasing the length of the thermal path. Even very thin voids usually dominate the thermal resistance completely. [37] Generally voids can be divided into two groups: Hot voids and cold voids. For a cold void the power dissipation in the chip area above the void is also reduced. This is the case if the electrical resistance of the solder layer between the void and the chip is significant compared to the resistance of the semiconductor device, e.g. if the backside metallization of the chip has been leeched away by the solder.

For a hot void the metallization is sufficiently thick thus maintaining the same current density in the chip above the void as elsewhere. In this case the high thermal resistance of the void is not balanced by a reduced power dissipation which results in a hot spot and possibly in the failure of the whole device.

#### 1.3.1.3 Diffusion soldering

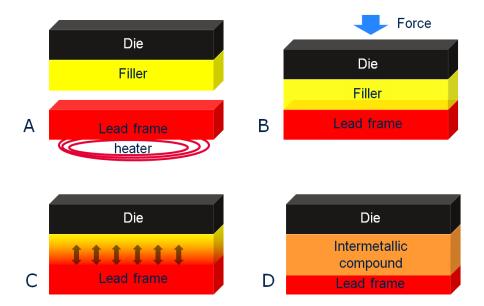

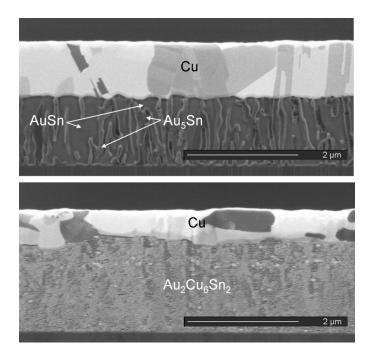

Diffusion soldering or transient liquid phase joining (TLP), as it is sometimes also referred to, is an alternative joining method with several advantages compared to conventional soldering. [38] This technology uses a few micrometer thick layer of a filler metal that is deposited directly on the backside of the wafer. For die attach the die is pressed with its metalized backside on the preheated lead frame. The filler metal melts and fills the joint clearance. During the successive heating stage the filler and the metal of the lead frame diffuse into each other, forming intermetallic phases with higher melting points than the process temperature. This means that the joint is formed by isothermal solidification, having a remelt temperature much higher than the process temperature. Figure 15 illustrates the process. The dynamics of this process are investigated for several material systems in this thesis.

Figure 15: schematic of the diffusion soldering process. A: The backside of the die is coated with a thin layer of a low-melting-point metal. The lead frame consists of a high-meting-point metal and is heated to process temperature. B: The die is pressed on the lead frame and the filler melts upon contact. C: Filler and lead frame material diffuse into each other, forming intermetallic compounds which are solid at the process temperature. D: After the reaction is completed the joint has solidified isothermally and the layer entirely consists of high-melting-point intermetallic compounds.

The biggest advantage of this method is low processing temperature which is only limited by the melting temperature of the filler metal and the comparatively high service temperature with a difference of up to 600 °C depending on the material system. [39] This enables the formation of joints at mild process conditions, which protects the sensitive unpackaged die and minimizes the intrinsic stress; i.e. the stress that is arising during cooling after the die attach due to a difference in the coefficient of thermal expansion between the silicon of the die and the metal of the lead frame. During further processing or operation of the device the bond can withstand higher temperatures without weakening.

Another advantage lies in the precise control of the thickness of the filler material. This enables excellent joint filling of small and large area joints with high reproducibility. The obtained joints can be made very thin which is beneficial to the thermal and electrical conductivity. Furthermore edge spilling (squeeze out) is minimized because of the exact control over the amount of filler material applied. This is essential for thin wafer technologies, where the thickness of the silicon is

only a few tens of micrometers and a shorting of the chip from frontside to backside has to be avoided.

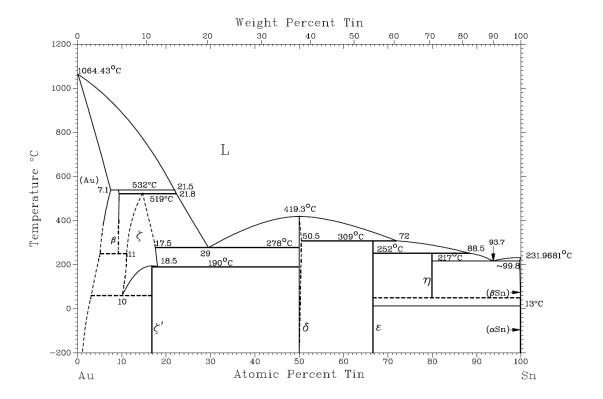

The resulting joints consist entirely of intermetallic compounds and are thus very hard and brittle. Stress arising between the lead frame and the chip is effectively transferred through the joint. For some applications this is desirable as silicon decreases its resistance under stress and the diffusion soldering die attach can have a positive effect on the electric parameters of the device. [40] Several material systems for diffusion soldering, consisting of a low-melting-point filler material and a high-melting-point substrate material, have been studied. Some examples are Copper/Indium [41], Copper/Tin [42], Silver/Tin [43], Silver/Indium [43], Gold/Tin [44], Gold/Indium [45], and Platinum/Indium [46]. Many involve precious metals and their cost might be considered an impediment. However the metals are applied only in thin films and the quantities needed are very low. Furthermore they have the advantage of being resistant to corrosion and therefore easier to bond even in slightly oxidizing environment. The binary eutectic alloy of gold and tin as the filler metal has the advantage of the corrosion resistance of gold and the low melting point of the eutectic alloy of only 278 °C. Due to these advantageous properties, the eutectic gold/tin alloy is often used as a filler material for industrial diffusion soldering in combination with substrates like copper, silver or nickel and is discussed in detail in chapter 3. Nevertheless a material system lower in cost, avoiding the use of precious metals, is desirable from an economic point of view. Thus a possible alternative is the copper/tin system, which is also discussed in chapter 2.

#### 1.3.2 Chip front side connection

The chip front side connections provide the electrical path for signal and power distribution. In contrast to the backside of the chip, the front side is structured, having multiple pads for various input/output connections. Therefore the area available per contact is lower and the thermal resistance higher. The core requirements to the front side connection are low electrical resistance and high reliability, especially concerning electro migration. Figure 16 shows a power transistor with all electrical connections. Source and gate contact are made by wire bonding to the frontside

of the chip. The drain contact is formed on the backside by the die attach. The most commonly applied technologies for frontside connections for power devices are briefly discussed in the following.

Figure 16: Single transistor chips on a lead frame with frontside connections made by wire bonding. Two thick wires connect the source pad to the corresponding lead and one thinner wire the gate pad. The drain contact is the backside of the die.

#### 1.3.2.1 Wire bonding

In this technology a combination of heat, pressure and ultrasonic vibrations are used to connect the chip frontside to the lead frame by a thin metal wire. All wire bonding processes are similar in that they rub off the oxide layer on the wire and the substrate by applying pressure, heat and ultrasonic energy. The joining surfaces are brought in intimate contact, so that metal bonds can be formed and a stable joint is achieved. There are two basic wire bonding techniques: ball bonding and wedge bonding. Each of those can be applied in thermocompression, thermosonic or ultrasonic mode, depending on the energy supplied for the bonding process. [47]

For ball bonding the wire is passed through a thin capillary leaving a small portion of it extending beneath the capillary. An electric discharge is used to melt this part. The surface tension of the liquid metal forms the ball as it solidifies. The ball is then pressed onto the bond pad on the die with sufficient force to cause plastic deformation. Atomic interdiffusion of the wire and the underlying and the removal of surface contamination is enhanced by thermal and ultrasonic energy. This ensures an intimate contact between the two metal surfaces and forms the first bond (see Figure 17). Then the capillary is raised and moved over the second bond position,

the lead frame. The trajectory of the capillary tip gives the wire connection its shape. The second bond is formed by pressing the capillary against the lead frame and thereby breaking the wire. This so called stitch bond has a crescent shape caused by the imprint of the capillary. Then the tool is raised again leaving an exact wire length sticking out to form a new ball for the new bond. By the use of fully automated machines and precisely controlled process parameters it is possible to make more than ten wire connections per second. [48]

Wedge bonding is named after the shape of the bond tool. The wire is fed through a hole on the back of the wedge at a low angle. The main difference to ball bonding is that the wire is bonded on its side and not vertically on the bond pad (see Figure 18). This is a considerable advantage as it gives a smaller footprint than a ball bond and allows a denser placing of the wires. Still approximately 90 % of all semiconductor packages are manufactured using ball bonding, because of its unmatched speed. [48]

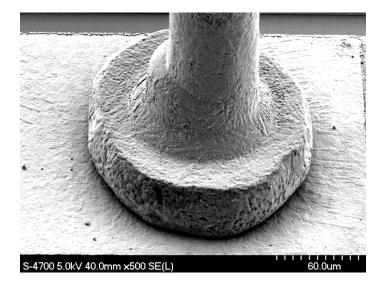

Figure 17: Ball bond of a 60 µm thick aluminum wire on an aluminum bond pad.

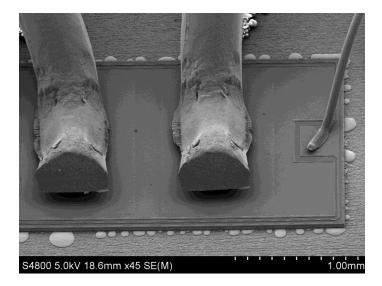

Figure 18: Wedge bonded aluminum wires as source (left and middle wire) and gate (right wire) connections on a power transistor.

#### 1.3.2.2 Flip chip bonding

In flip chip bonding the chip is attached upside down. Solder or conductive polymer bumps between the chip contact pads and the substrate serve as a mechanical and electrical interconnection. This method requires the mirrored contact pad pattern of the chip frontside on the printed circuit board. The chip is placed upside down directly on the printed circuit board. In a reflow process the solder bumps are melted and establish the connection to the substrate. To prevent a spreading of the solder over the whole lead, the contact areas are surrounded by a non wetting material like glass or epoxy resin. Thus, in the case of a slight misalignment, the chip can be pulled in the correct position by the surface tension of the liquid solder.

The advantages of this relatively simple method are the relatively low footprint of the device on the circuit board as well as the low ohmic resistance and inductivity of the thin solder joints. A drawback though is small contact area of chip and substrate. The heat generated by the chip has to be dissipated completely over the connections of its frontside as the backside has no connection to a lead frame. To overcome this problem an additional heat sink can be attached to the chip backside. But this increases the footprint of the device and the major advantage of the flip chip method is lost. An example of such a technology is shown in Figure 19.

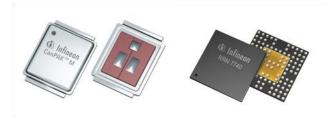

Figure 19: Examples of flip chip packages. CanPAK<sup>TM</sup> (left): A single transistor is equipped with a metal heat sink on the backside, which also acts as the drain contact. The two source contacts and the gate contact are covered with solder bumps on the frontside. Embedded Wafer Level Ball Grid Array (right): flip chip package of an integrated circuit. Solder balls are applied to all the contact pads on the frontside.

#### 1.3.3 Encapsulation

To protect the chips from mechanical damage, humidity, corrosive gases and other external influences they are encapsulated in epoxy molding compounds (EMC). Various substances are added to the EMC so that it can meet the requirements on reliability, stability and moldability. Typically an EMC consists to 70 to 90 wt. % of silica filler (SiO<sub>2</sub>) to achieve a coefficient of thermal expansion close to the silicon of the chip. [20] The epoxy resin makes up only 5 to 10 wt. %. Epoxy resins are used because they have high adhesion strength, small shrinkage during curing, good electrical properties and a superior resistance to chemicals, moisture and heat. Only 5 wt. % remain for other additives such as the hardener, the curing promoter, coupling agents and flame retardants. The amount and type of hardener mainly determines the melt viscosity of the EMC. A curing promoter is a catalyst which reduces the heat and time needed for curing of the EMC. Silane coupling agents ensure the adhesion between the epoxy resin and the filler particles. To fulfill the flammability rating, antimony based flame retardants such as antimony trioxide are added, but recently they have been replaced by halogen free substances due to environmental concerns.

In a typical transfer molding process, the lead frame with the chips is placed in a heated cavity (~180 °C) and the EMC is fed by a plunger under pressure into a single chamber for every die. After about two minutes when the EMC is sufficiently cured the cavity is opened and the molded lead frame is released. [20] To fully cure the EMC, the devices have to be annealed for up to 8

hours at elevated temperatures. In a so called deflash process, the redundant EMC at the edges of the devices is removed. Then the lead frames are plated with a thin layer of tin to improve the wettability during board assembly. The left part of Figure 20 shows a lead frame in this state. In the final process step before the electrical test the single devices are separated by punching. Up to this point the single leads have been connected for reasons of mechanical stability. Now the chip is ready for the assembly on a circuit board.

Figure 20: Lead frame after molding and tin plating.

### 1.4 References

- [1] J. G. Koomey, "EXECUTIVE SUMMARY", 2007.

- [2] W. C. O'Mara, R. B. Herring, und L. P. Hunt, Handbook of semiconductor silicon technology. William Andrew, 1990.

- [3] U. Hilleringmann, Silizium-Halbleitertechnologie. Vieweg + Teubner, 2004.

- [4] J. Czochralski, "Ein neues Verfahren zur Messung der Kristallisationsgeschwindigheit der Metalle", Z. phys. Chemie., Bd. 92, S. 219–221, 1918.

- [5] M. E. Levinshteĭn und M. Shur, Semiconductor technology: processing and novel fabrication techniques. Wiley, 1997.

- [6] B. El-Kareh, Fundamentals of semiconductor processing technology. Springer, 1994.

- [7] A. Hössinger, "Simulation of ion implantation for ULSI technology", Tech. Univ. Vienna, Vienna, Austria, 2000.

- [8] P. C. Andricacos, "Copper on-chip interconnections", The Electrochemical Society Interface, S. 32–37, 1999.

- [9] P. V. Zant, Microchip fabrication: a practical guide to semiconductor processing. McGraw-Hill, 1997.

- [10] C. Y. Chang und S. M. Sze, ULSI technology. McGraw-Hill, 1996.

- [11] Y. D. Gamburg und G. Zangari, Theory and Practice of Metal Electrodeposition. Springer, 2011.

- [12] S. Murarka und S. Hymes, "Copper metallization for ULSL and beyond", Critical Reviews in Solid State and Materials Sciences, Bd. 20, Nr. 2, S. 87-124, 1995.

- [13] Praxiswissen Mikrosystemtechnik. Wiesbaden: Vieweg+Teubner, 2006.

- [14] C. S. Yoo, Semiconductor manufacturing technology. World Scientific, 2008.

- [15] WILEY-VCH Verlag GmbH & Co KGaA, Hrsg., digital Encyclopedia of Applied Physics. Weinheim, Germany: WILEY-VCH Verlag GmbH & Co KGaA, 2003.

- [16] J. A. Thornton, J. Tabock, und D. W. Hoffman, "Internal stresses in metallic films deposited by cylindrical magnetron sputtering", Thin Solid Films, Bd. 64, Nr. 1, S. 111–119, 1979.

- [17] H. F. Winters, "Gas Incorporation into Sputtered Films", Journal of Applied Physics, Bd. 38, Nr. 10, S. 3928, 1967.

- [18] S. D. Dahlgren, "Equilibrium phases in 304L stainless stell obtained by sputter-deposition", Metallurgical and Materials Transactions B, Bd. 1, Nr. 11, S. 3095–3099, 1970.

- [19] J. A. Thornton, "The microstructure of sputter-deposited coatings", Journal of Vacuum Science & Technology A: Vacuum, Surfaces, and Films, Bd. 4, Nr. 6, S. 3059–3065, 1986.

- [20] D. Lu und C. P. Wong, Materials for advanced packaging. Springer Verlag, 2008.

- [21] R. R. Tummala, Fundamentals of microsystems packaging. McGraw-Hill Professional, 2001.

- [22] G. Bai, "Low-temperature sintering of nanoscale silver paste for semiconductor device interconnection", Virginia Polytechnic Institute and State University, 2005.

- [23] Z. Zhang, "Processing and Characterization of Micro-scale and Nanscale Silver Paste for Power Semiconductor Device Attachment", Virginia Polytechnic Institute and State University, 2005.

- [24] "Directive 2002/95/EC of the European Parliament and of the Council". Official Journal of the European Union, 2003.

- [25] "BE semiconductor industries". [Online]. Available: http://www.besi.com/products-and-technology/die-attach/die-bonding/esec-2100-xp-3. [Accessed: 22-Juli-2011].

- [26] Y. Li, C. P. Wong, und D. Lu, Electrical Conductive Adhesives with Nanotechnologies. Springer, 2009.

- [27] D. D. Chang u. a., "An overview and evaluation of anisotropically conductive adhesive films for fine pitch electronic assembly", Components, Hybrids, and Manufacturing Technology, IEEE Transactions on, Bd. 16, Nr. 8, S. 828–835, 1993.

- [28] H. Takezawa, M. Itagaki, T. Mitani, Y. Bessho, und K. Eda, "Development of solderless joining technologies using conductive adhesives", in Advanced Packaging Materials: Processes, Properties and Interfaces, 1999. Proceedings. International Symposium on, S. 11–15.

- [29] Y. Li und C. P. Wong, "Recent advances of conductive adhesives as a lead-free alternative in electronic packaging: Materials, processing, reliability and applications", Materials Science and Engineering: R: Reports, Bd. 51, Nr. 1-3, S. 1-35, Jan. 2006.

- [30] K. Suganuma, "Advances in lead-free electronics soldering", Current Opinion in Solid State and Materials Science, Bd. 5, Nr. 1, S. 55–64, 2001.

- [31] K.-H. Florenz, "Committee on the Environment, PublicHealth and Consumer Policy Draft Report", European Parliament, Bd. 2001.

- [32] C. o. t. E. Communities, "Proposal for a Directive of the European Parliament and the Council on Waste Electrical and Electronic Equipment: Proposal for a Directive of the European Parliament and of the Council on the restriction of theuse of certain hazardous substances in electrical and electronic equipment", WEEE Directive Brussels, Bd. 13, 2000.

- [33] K. N. Chen, A. Fan, C. S. Tan, und R. Reif, "Bonding parameters of blanket copper wafer bonding", Journal of Electronic Materials, Bd. 35, Nr. 2, S. 230-234, Feb. 2006.

- [34] K. Zeng und K. N. Tu, "Six cases of reliability study of Pb-free solder joints in electronic packaging technology", Materials Science and Engineering: R: Reports, Bd. 38, Nr. 2, S. 55–105, 2002.

- [35] P. G. Harris und K. S. Chaggar, "The role of intermetallic compounds in lead-free soldering", Soldering & Surface Mount Technology, Bd. 10, Nr. 3, S. 38-52, 1998.

- [36] T. Massalski, "Binary alloy phase diagrams". Materials Park: ASM International, 1996.

- [37] A. Yerman, J. Burgess, R. Carlson, und C. Neugebauer, "Hot Spots Caused by Voids and Cracks in the Chip Mountdown Medium in Power Semiconductor Packaging", IEEE Transactions on Components, Hybrids, and Manufacturing Technology, Bd. 6, Nr. 4, S. 473-479, Dez. 1983.

- [38] G. Humpston und D. M. Jacobson, Principles of soldering. Asm Intl, 2004.

- [39] S. A. Sommadossi, "Investigation on Diffusion Soldering in Cu/In/Cu and Cu/In-48Sn/Cu Systems", Universit\ätsbibliothek, 2002.

- [40] P. W. Bridgman, "The effect of homogeneous mechanical stress on the electrical resistance of crystals", Physical Review, Bd. 42, Nr. 6, S. 858, 1932.

- [41] S. Sommadossi u. a., "Development of Cu/Cu interconnections using an indium interlayer", Metal Matrix Composites and Metallic Foams, S. 214–218, 2000.

- [42] F. Bartels, J. W. Morris, G. Dalke, und W. Gust, "Intermetallic phase formation in thin solid-liquid diffusion couples", Journal of electronic materials, Bd. 23, Nr. 8, S. 787–790, 1994.

- [43] G. Humpston und D. M. Jacobson, Methods of joining components. Google Patents, 1992.

- [44] G. S. Matijasevic, C. Y. Wang, und C. C. Lee, "Void free bonding of large silicon dice using gold-tin alloys", Components, Hybrids, and Manufacturing Technology, IEEE Transactions on, Bd. 13, Nr. 4, S. 1128–1134, 1990.

- [45] C. C. Lee, C. Y. Wang, und G. Matijasevic, "Au-In bonding below the eutectic temperature", Components, Hybrids, and Manufacturing Technology, IEEE Transactions on, Bd. 16, Nr. 3, S. 311–316, 1993.

- [46] T. Studnitzky und R. Schmid-Fetzer, "Phase formation and diffusion soldering in Pt/In, Pd/In, and Zr/Sn thin-film systems", Journal of electronic materials, Bd. 32, Nr. 2, S. 70–80, 2003.

- [47] W. Menz, J. Mohr, J. Mohr, und O. Paul, Microsystem technology. Wiley-VCH, 2001.

- [48] G. Harman, Wire Bonding in Microelectronics. McGraw Hill Professional, 2010.

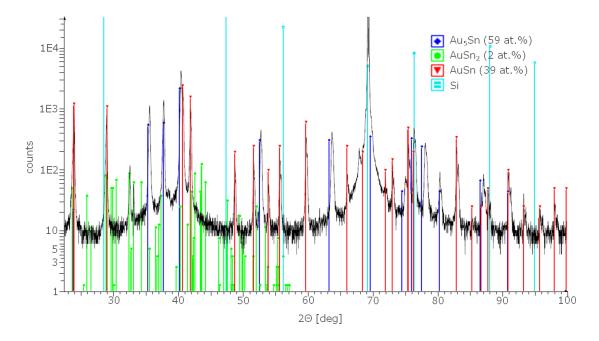

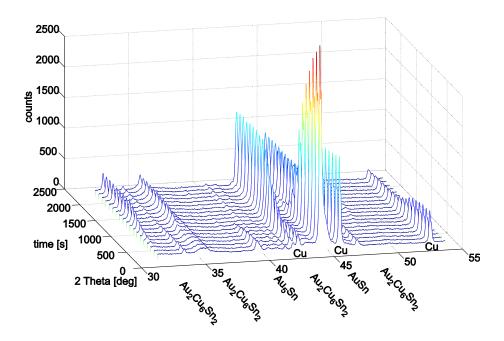

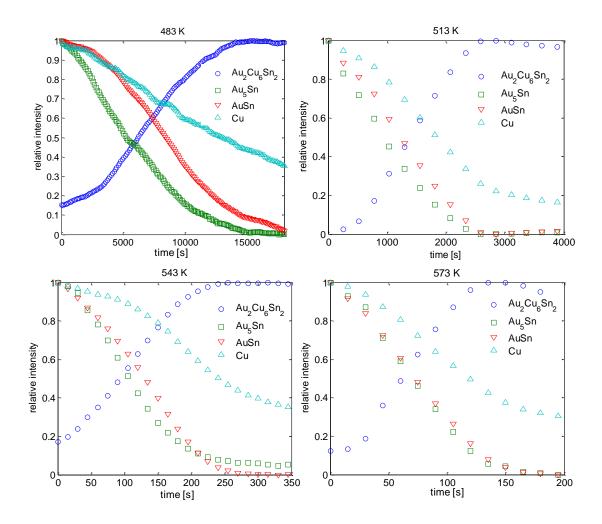

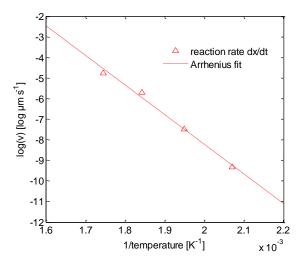

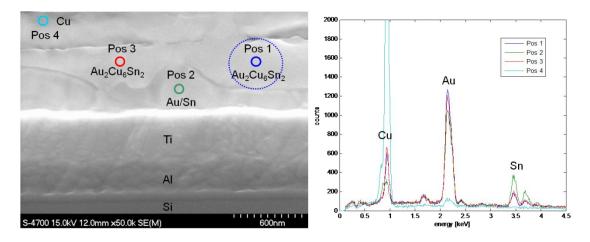

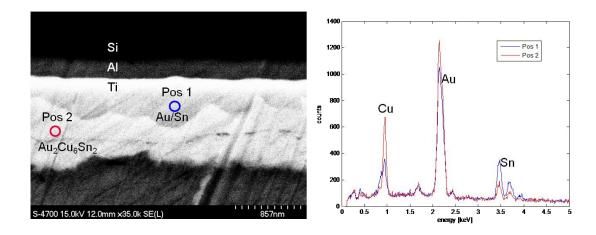

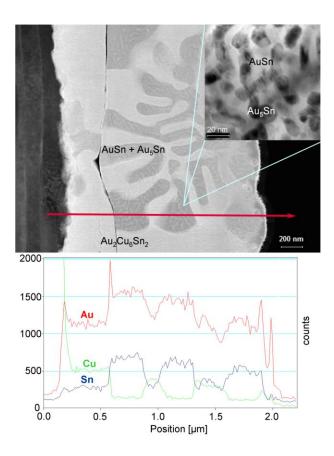

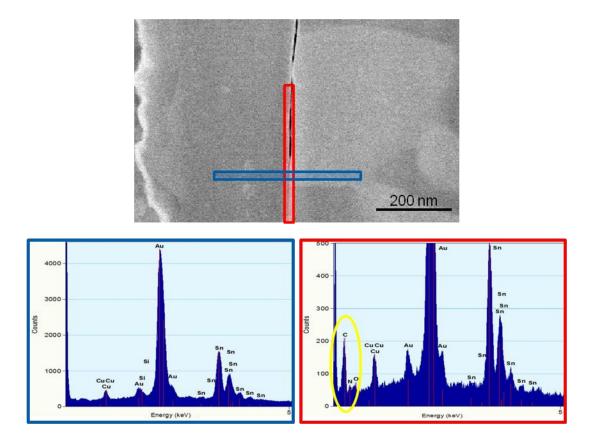

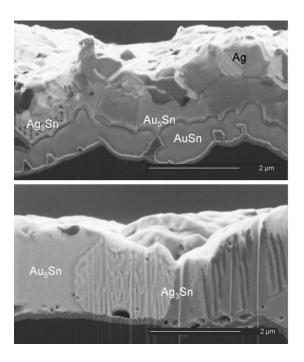

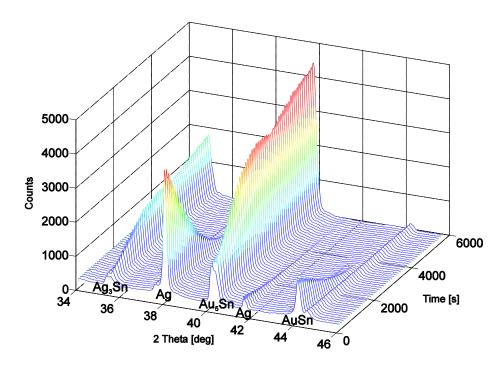

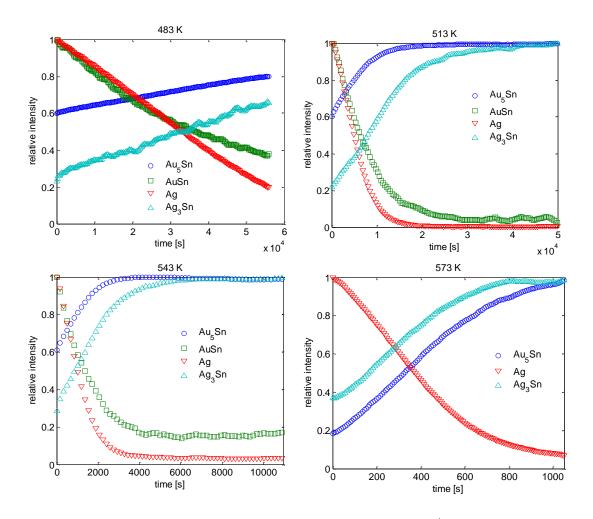

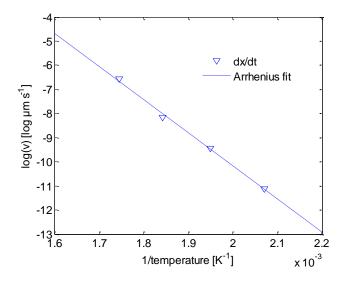

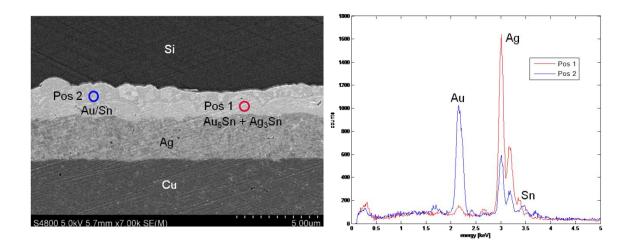

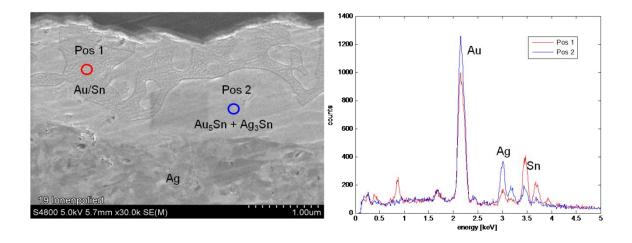

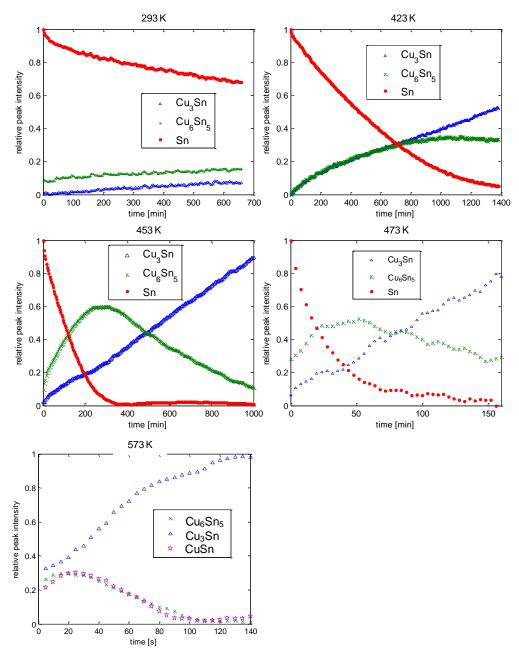

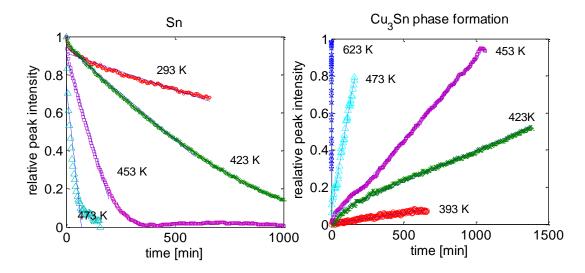

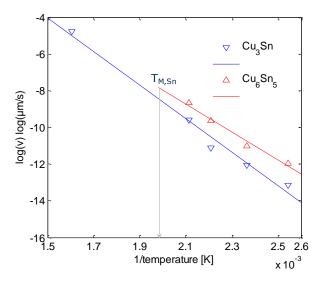

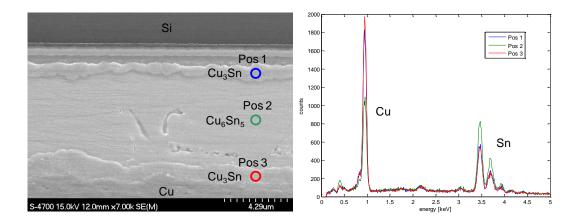

# 2 Dynamics of diffusion soldering<sup>1</sup>

but still not well understood. Process parameters such as bond time, force and temperature are different for every chip type and are often defined only based on trial and error. This method has the disadvantage that a lot of effort has to be undertaken for the qualification of every new package, even if the material system is known from existing products. Slight variations in the processing conditions, which cannot be avoided in high volume production at multiple sites across the globe, can lead to a complete failure of the joint if the parameters are not chosen within a safe margin. Furthermore it is very difficult to predict the long term reliability of the package. Therefore a deeper understanding of the dynamics of diffusion soldering is desirable. This would at least reduce the amount of necessary trials and enable the design of a process that produces joints with the necessary quality.

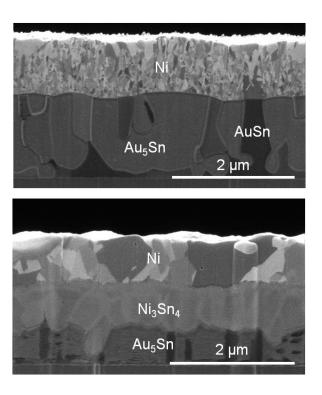

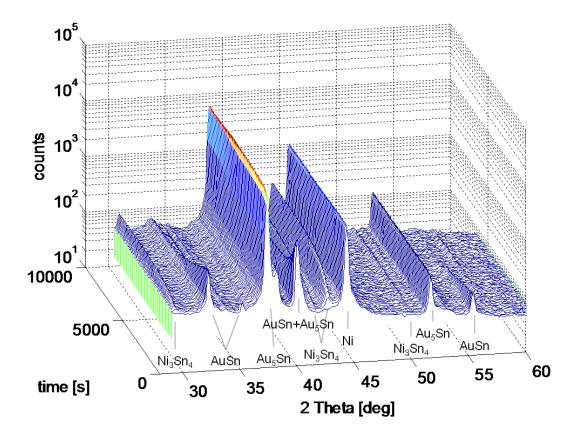

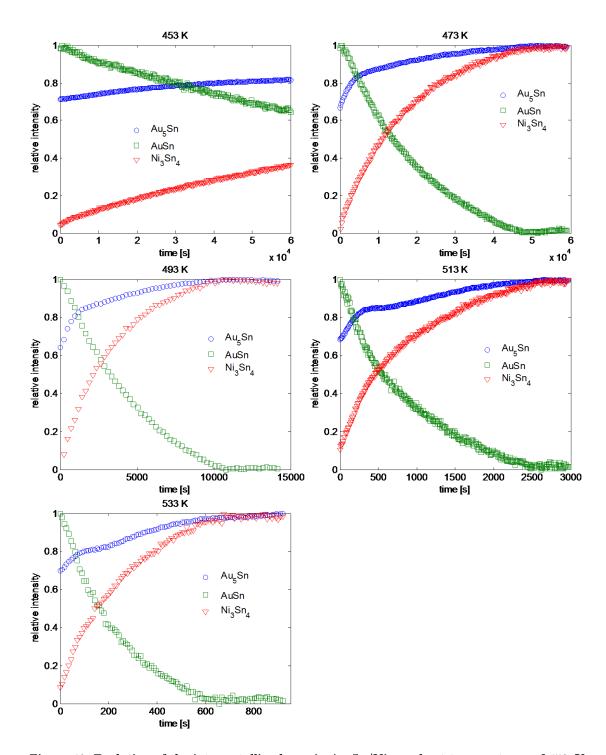

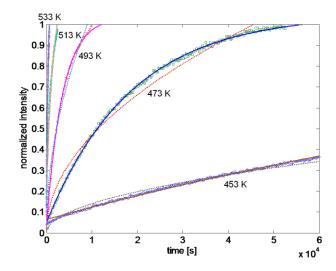

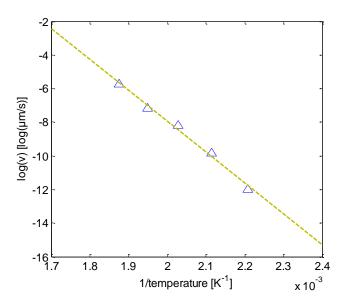

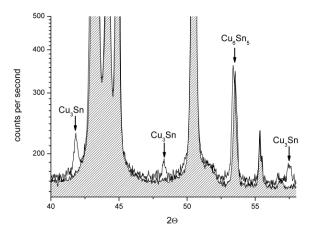

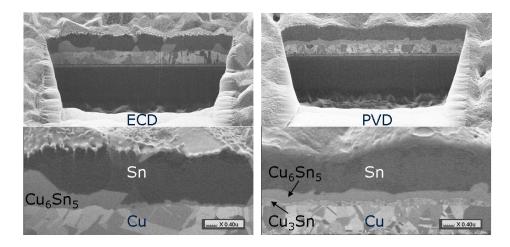

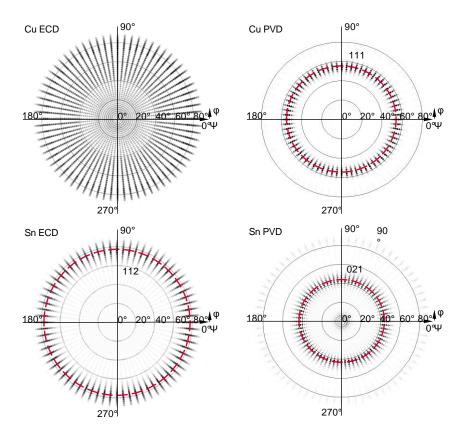

Several studies have already been done on various combinations of filler and substrate materials. The evolution of the intermetallic phases involved in the soldering process has been studied so far mainly ex-situ by analysis of joint cross-sections or fractured joint surfaces [1–9]. The analysis of quenched samples can reveal the composition across the thickness of the joint and the phase structure at the fractured surfaces after certain reaction times. However, it is not possible by these methods to observe the course of the reaction at the elevated process temperatures directly. Therefore it is difficult to track the structural phase evolution, as some phases formed during the process might not be stable at room temperature. By microscopy, only a 2-dimensional area can be investigated which might not be representative for the whole volume of the sample. In situ X-ray diffraction (XRD) is an integral method enabling the direct investigation of the intermetallic phase evolution in a macroscopic volume at elevated temperatures. Gollas at al. [10] have