**Graz University of Technology** Faculty of Computer Science Institute for Applied Information Processing and Communications IAIK

#### Security Aspects of Low-Cost RFID Tags – From Evaluation to Hardware Implementation

Assessors: Prof. Dr. Karl Christian Posch Prof. Dr. Kerstin Lemke-Rust A PhD Thesis Presented to the Faculty of Computer Science in Fulfillment of the Requirements for the PhD Degree

by Thomas Plos

September 2011

### Security Aspects of Low-Cost RFID Tags – From Evaluation to Hardware Implementation

by

Thomas Plos

A PhD Thesis Presented to the Faculty of Computer Science in Partial Fulfillment of the Requirements for the PhD Degree

Assessors

Prof. Dr. Karl Christian Posch (TU Graz, Austria) Prof. Dr. Kerstin Lemke-Rust (UoAS BRS, Germany)

September 2011

Institute for Applied Information Processing and Communications (IAIK) Faculty of Computer Science Graz University of Technology, Austria

#### Abstract

Radio-frequency identification (RFID) technology is the enabler for applications like the future Internet of Things (IoT). Especially passive RFID tags that are cheap in price will we used in the future IoT. With the IoT, new applications will arise where security will play an important role. In this work we focus on security aspects that are important for designing the next generation of passive low-cost tags.

In the first part of this work we evaluate the susceptibility of current low-cost tags against implementation attacks. We conduct side-channel analysis (SCA) attacks as well as fault-analysis attacks on commercially available RFID tags from various tags vendors. All evaluated tags have shown a vulnerability to implementation attacks. This emphasizes that integrating proper countermeasures to low-cost tags is necessary when adding security to them. We further analyze the effectiveness of two countermeasures that aim for protecting low-cost tags from SCA attacks: randomizing the execution order of a cryptographic algorithm and detaching the power supply.

In the second part of this work we present a flexible tag architecture that bases on a low-resource 8-bit microcontroller. The flexible architecture allows to efficiently handle complex protocol tasks on low-cost tags. We further show that it is advantageous to reuse the microcontroller for computing cryptographic algorithms on it. By using the microcontroller for both protocol handling and computing cryptographic algorithms, costly resources like memory can be easily reused. Our results clearly point out that this combined approach is even more efficient in terms of additional hardware costs than using dedicated hardware coprocessors that are optimized for low chip area.

#### Acknowledgements

I would like to thank all the people who supported me during my research within the last years and with whom I had the pleasure to work with. Especially, I want to thank my parents and my girlfriend Christiane. I am also grateful to my good friends Mario and Mihai for their moral support over all the years.

I would like to thank the advisor of this thesis Karl Christian Posch for his guidance through my PhD and for the interesting discussions. A dedicated thanks goes to my assessor Kerstin Lemke-Rust for the valuable comments and for taking the time to travel to Graz. I also want to thank the former group leader Manfred Aigner as well as the current group leader Jörn-Marc Schmidt for decoupling us from management and administrative tasks so that we could focus on our research work.

I am grateful to all people from IAIK and especially the SEnSE group for the good cooperation and the nice working environment. In particular I would like to thank my colleagues Michael Hutter, Jörn-Marc Schmidt, Mario Kirschbaum, and Martin Feldhofer for their help and the fruitful discussions about technical and non-technical topics. Finally I want to thank my coauthors Michael Hutter, Martin Feldhofer, Jörn-Marc Schmidt, Mario Kirschbaum, Stefan Tillich, Christoph Herbst, Marcel Medwed, Hannes Groß, Erich Wenger, Manfred Aigner, and Alexander Szekely who have contributed to my work.

> Thomas Plos Graz, September 2011

# Table of Contents

| A        | bstra                                    | act                                                                                      | iii                                     |

|----------|------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------|

| A        | ckno                                     | wledgements                                                                              | $\mathbf{v}$                            |

| Li       | ist of                                   | Publications                                                                             | xiii                                    |

| Li       | ist of                                   | Tables                                                                                   | xvii                                    |

| Li       | ist of                                   | Figures                                                                                  | xix                                     |

| A        | crony                                    | yms                                                                                      | xxiii                                   |

| 1        | <b>Intr</b><br>1.1<br>1.2                | coduction         Contribution of this Thesis         Organization of this Thesis        | <b>1</b><br>3<br>5                      |

| I<br>m   |                                          | plementation Attacks and Evaluation of Counter-<br>ures in Context of Low-Cost RFID Tags | 7                                       |

| <b>2</b> | RF                                       | ID Technology                                                                            | 9                                       |

|          | 2.1                                      | Description of a Basic RFID System                                                       | 9                                       |

|          | 2.2                                      | Frequency Ranges of RFID Systems                                                         | 10                                      |

|          |                                          | 2.2.1 Low-Frequency Range                                                                | 10                                      |

|          |                                          | 2.2.2 High-Frequency Range                                                               | 11                                      |

|          |                                          | 2.2.3 Ultra-High Frequency Range                                                         | 11                                      |

|          | ~ ~                                      | 2.2.4 Microwave Range                                                                    | 11                                      |

|          | $\begin{array}{c} 2.3\\ 2.4 \end{array}$ | Coupling Methods of RFID Systems                                                         | $\begin{array}{c} 11 \\ 12 \end{array}$ |

|          | 2.4                                      | runctionanty of KF1D Tags                                                                | 12                                      |

| 3        |                                          | ics of Implementation Attacks                                                            | 15                                      |

|          | 3.1                                      | Side-Channel Analysis                                                                    | 16                                      |

|          |                                          | 3.1.1 SCA Attacks Using Timing Information                                               | 17                                      |

|          |                                          | 3.1.2 SCA Attacks Using Power Consumption                                                | 18                                      |

|          | 2.0                                      | 3.1.3 SCA Attacks Using Electromagnetic Emanations                                       | 22                                      |

|          | 3.2                                      | Fault Analysis   Nonintime                                                               | 23<br>25                                |

|          |                                          | 3.2.1 Temperature Variations                                                             | 25                                      |

|   |      | 3.2.2  | Supply Voltage and Clock Variations                   | 25 |

|---|------|--------|-------------------------------------------------------|----|

|   |      | 3.2.3  | Electromagnetic Interferences                         | 26 |

|   |      | 3.2.4  | Optical Inductions                                    | 26 |

|   | 3.3  | Summ   | nary                                                  | 26 |

| 4 | Coι  | interm | easures Against Implementation Attacks                | 29 |

|   | 4.1  |        | Channel Analysis Countermeasures                      | 30 |

|   |      | 4.1.1  | Countermeasures Against SCA Attacks Using Timing In-  |    |

|   |      |        | formation                                             | 30 |

|   |      | 4.1.2  | Countermeasures Against SCA Attacks Using Power Con-  |    |

|   |      |        | sumption                                              | 30 |

|   |      | 4.1.3  | Countermeasures Against SCA Attacks Using Electromag- |    |

|   |      |        | netic Emanations                                      | 33 |

|   | 4.2  |        | Analysis Countermeasures                              | 33 |

|   | 4.3  | Summ   | nary                                                  | 34 |

| 5 | Side | e-Char | nnel Analysis of Low-Cost UHF RFID Tags               | 37 |

|   | 5.1  | Gener  | al Information About UHF RFID Tags                    | 38 |

|   | 5.2  |        | ption of Examined UHF RFID Tags                       | 39 |

|   |      | 5.2.1  | Description of the UHF Tag Prototype                  | 40 |

|   |      | 5.2.2  | Description of Passive UHF RFID Tags                  | 40 |

|   | 5.3  | Measu  | rement Setup for UHF RFID Tags                        | 40 |

|   |      | 5.3.1  | Near-Field Measurements                               | 42 |

|   |      | 5.3.2  | Far-Field Measurements                                | 43 |

|   |      | 5.3.3  | Contact-Based Measurements                            | 43 |

|   | 5.4  | Side-C | Channel Analysis Results                              | 44 |

|   |      | 5.4.1  | Side-Channel Analysis of the UHF Tag Prototype        | 46 |

|   |      | 5.4.2  | Side-Channel Analysis of Passive UHF RFID Tags        | 47 |

|   | 5.5  | Summ   | nary                                                  | 50 |

| 6 | Fau  | lt Ana | lysis of Low-Cost RFID Tags                           | 53 |

|   | 6.1  |        | ction Mechanisms of Passive RFID Tags                 | 54 |

|   | 6.2  | Fault- | Analysis Techniques Suitable for Passive RFID Tags    | 55 |

|   |      | 6.2.1  | Temperature Variations                                | 56 |

|   |      | 6.2.2  | Supply Voltage and Clock Variations                   | 56 |

|   |      | 6.2.3  | Electromagnetic Interferences                         | 57 |

|   |      | 6.2.4  | Optical Inductions                                    | 57 |

|   | 6.3  | Descri | iption of Evaluated Tags and Conducted Fault Analyses | 57 |

|   | 6.4  | Measu  | rement Setups for Fault Analysis                      | 58 |

|   |      | 6.4.1  | Measurements Setups for Global Fault Injections       | 59 |

|   |      | 6.4.2  | Measurement Setup for Local Fault Injections          | 61 |

|   | 6.5  | Fault- | Analysis Results                                      | 61 |

|   |      | 6.5.1  | Global Fault Injections                               | 63 |

|   |      | 6.5.2  | Local Fault Injections                                | 65 |

|   | 6.6  | Summ   | hary                                                  | 65 |

| 7 | Eva | luating the Effectiveness of Randomization                                                                                      | 67 |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------|----|

|   | 7.1 | Description of the RFID Tag Prototypes                                                                                          | 68 |

|   |     | 7.1.1 HF Tag Prototype                                                                                                          | 69 |

|   |     | 7.1.2 UHF Tag Prototype                                                                                                         | 70 |

|   | 7.2 | Noise in Side-Channel Analysis Measurements                                                                                     | 71 |

|   |     | 7.2.1 Noise in RFID Measurements                                                                                                | 71 |

|   |     | 7.2.2 Techniques to Lower the Impact of Noise and to Ease the                                                                   |    |

|   |     | Attacking of Hiding Countermeasures                                                                                             | 72 |

|   | 7.3 | Description of the Randomized AES Implementation                                                                                | 73 |

|   | 7.4 | Measurement Setup                                                                                                               | 74 |

|   | 7.5 | Results                                                                                                                         | 75 |

|   |     | 7.5.1 Results with Noise in the Amplitude Dimension                                                                             | 75 |

|   |     | 7.5.2 Results with Noise in the Amplitude Dimension and Ac-                                                                     |    |

|   |     | tivated Shuffling                                                                                                               | 77 |

|   | 7.6 | Summary                                                                                                                         | 79 |

| 8 | Eva | luating the Detached Power Supply                                                                                               | 81 |

|   | 8.1 | Description of the Detached Power Supply                                                                                        | 82 |

|   |     | 8.1.1 Basic Version of the Detached Power Supply                                                                                | 83 |

|   |     | 8.1.2 Enhanced Version of the Detached Power Supply                                                                             | 84 |

|   | 8.2 | Implementation of the Detached Power Supply                                                                                     | 84 |

|   | 8.3 | Results of the Side-Channel Analysis                                                                                            | 86 |

|   |     | 8.3.1 Results of the Basic Version of the Detached Power Supply                                                                 | 87 |

|   |     | 8.3.2 Results of the Enhanced Version of the Detached Power                                                                     |    |

|   |     | $Supply \ldots \ldots$ | 88 |

|   | 8.4 | A Suggestion for Preventing Side-Channel Leakage at Output Pins                                                                 | 90 |

|   | 8.5 | Discussing the Costs of Integrating the Detached Power Supply .                                                                 | 91 |

|   | 8.6 | Summary                                                                                                                         | 92 |

|   |     |                                                                                                                                 |    |

# II Hardware-Implementation Aspects of Low-Cost RFID Tags

| 9 D         | esign of Digital Hardware Circuits                | 97  |

|-------------|---------------------------------------------------|-----|

| 9.1         | 1 Design Cycle                                    | 98  |

| 9.2         | 2 Design Space                                    | 100 |

| 9.3         | 3 Testability                                     | 102 |

| 9.4         | 4 Requirements for Passive Low-Cost RFID Tags     | 103 |

|             | 9.4.1 Chip Area                                   | 103 |

|             | 9.4.2 Power Consumption                           | 104 |

| 9.5         | 5 Summary                                         | 105 |

| <b>10 H</b> | ardware Implementation of a Flexible Tag Platform | 107 |

| 10          | .1 Overview of the Flexible Tag Platform          | 108 |

| 10          | .2 Functionality of the NFC-Compatible Tag        | 110 |

|             | 10.2.1 Basic Tag Functionality                    | 110 |

95

|    |      | 10.2.2 Advanced Tag Functionality                              | 111 |

|----|------|----------------------------------------------------------------|-----|

|    | 10.3 | Splitting Functionality into Hardware and Software             |     |

|    | 10.4 | Detailed Description of the Flexible Tag Platform              | 114 |

|    |      | 10.4.1 Framing Logic                                           |     |

|    |      | 10.4.2 8-Bit Microcontroller                                   |     |

|    | 10.5 | Design Flow for Code Development                               |     |

|    |      | Implementation Results                                         |     |

|    | 10.0 | 10.6.1 ROM Code for the Microcontroller                        |     |

|    |      | 10.6.2 Chip Area and Power Consumption                         |     |

|    |      | 10.6.3 Comparison with Related Work                            |     |

|    | 10.7 | Integration into the CRYPTA Tag-Prototype Chip                 |     |

|    |      | Summary                                                        |     |

|    | 10.0 | Summary                                                        | 120 |

| 11 | Imp  | lementation of Symmetric-Key Algorithms                        | 127 |

|    |      | Extension of the 8-Bit Microcontroller                         | 128 |

|    |      | Overview of the Selected Cryptographic Algorithms              |     |

|    |      | 11.2.1 AES                                                     |     |

|    |      | 11.2.2 NOEKEON                                                 |     |

|    |      | 11.2.3 Present                                                 |     |

|    |      | 11.2.4 SEA                                                     |     |

|    |      | 11.2.5 XTEA                                                    |     |

|    |      | 11.2.6 Trivium                                                 |     |

|    | 11.3 | Implementation Results                                         |     |

|    | 11.0 | 11.3.1 AES                                                     |     |

|    |      | 11.3.2 NOEKEON                                                 |     |

|    |      | 11.3.3 Present                                                 |     |

|    |      | 11.3.4 SEA                                                     |     |

|    |      | 11.3.5 XTEA                                                    |     |

|    |      | 11.3.6 Trivium                                                 |     |

|    |      | 11.3.7 Summary of Implementation Results                       |     |

|    | 11 4 | Discussing the Costs of Integrating the Implemented Algorithms | 140 |

|    |      | Summary                                                        |     |

|    | 11.0 | Summary                                                        | 110 |

| 12 | Con  | abined Implementation on the Microcontroller                   | 145 |

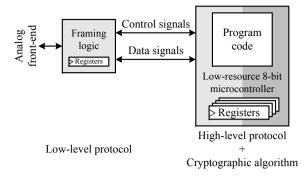

|    | 12.1 | System Overview                                                | 146 |

|    | 12.2 | Description of the Security Layer                              | 147 |

|    |      | 12.2.1 Tag Authentication                                      |     |

|    |      | 12.2.2 Reader Authentication                                   | 147 |

|    |      | 12.2.3 Security-Layer Variants                                 | 148 |

|    |      | 12.2.4 Selected Block Ciphers                                  | 149 |

|    | 12.3 | Concept for Implementing the Security-Layer Variants           | 149 |

|    |      | Implementation Results                                         | 151 |

|    |      | 12.4.1 Low-Resource 8-Bit Microcontroller                      | 151 |

|    |      | 12.4.2 Implementation Results of AES and NOEKEON               | 152 |

|    |      | 12.4.3 Implementation Results of the Security-Layer Variants   | 153 |

|    | 12.5 | Summary                                                        | 158 |

|    |      |                                                                |     |

| 13 Conclusion | 161 |

|---------------|-----|

| Bibliography  | 165 |

| Index         | 187 |

| Author Index  | 187 |

#### List of Publications

- Thomas Plos. Susceptibility of UHF RFID Tags to Electromagnetic Analysis. In Tal Malkin, editor, Topics in Cryptology - CT-RSA 2008, The Cryptographers' Track at the RSA Conference 2008, San Francisco, CA, USA, April 8-11, 2008, Proceedings, volume 4964 of Lecture Notes in Computer Science, pages 288–300. Springer, April 2008.

- Thomas Plos, Michael Hutter, and Martin Feldhofer. Evaluation of Side-Channel Preprocessing Techniques on Cryptographic-Enabled HF and UHF RFID-Tag Prototypes. In Sandra Dominikus, editor, Workshop on RFID Security 2008 (RFIDSec08), July 9-11, Budapest, Hungary, pages 114–127, July 2008.

- Michael Hutter, Jörn-Marc Schmidt, and Thomas Plos. RFID and its Vulnerability to Faults. In Elisabeth Oswald and Pankaj Rohatgi, editors, Cryptographic Hardware and Embedded Systems – CHES 2008, 10th International Workshop, Washington DC, USA, August 10-13, 2008, Proceedings, volume 5154 of Lecture Notes in Computer Science, pages 363–379. Springer, August 2008.

- Thomas Plos, Michael Hutter, and Christoph Herbst. Enhancing Side-Channel Analysis with Low-Cost Shielding Techniques. In Michael Sams Christoph Lackner, Timm Ostermann and Ronald Spilka, editors, *Proceedings of Austrochip 2008, October 8, 2008, Linz, Austria*, pages 90–95, October 2008. ISBN 978-3-200-01330-8.

- 5. Thomas Plos. Evaluation of the Detached Power Supply as Side-Channel Analysis Countermeasure for Passive UHF RFID Tags. In Marc Fischlin, editor, Topics in Cryptology - CT-RSA 2009, The Cryptographers' Track at the RSA Conference 2009, San Francisco, CA, USA, April 20-24, 2009, Proceedings, volume 5473 of Lecture Notes in Computer Science, pages 444-458. Springer, April 2009.

- Michael Hutter, Jörn-Marc Schmidt, and Thomas Plos. Contact-Based Fault Injections and Power Analysis on RFID Tags. In European Conference on Circuit Theory and Design 2009, ECCTD, 2009.

- 7. Thomas Plos, Michael Hutter, and Martin Feldhofer. On Comparing Side-Channel Preprocessing Techniques for Attacking RFID Devices. In

Heung Youl Youm and Moti Yung, editors, Information Security Applications, 10th International Workshop, WISA 2009, Busan, Korea, August 25-27, 2009, Revised Selected Papers, volume 5932 of Lecture Notes in Computer Science, pages 163–177. Springer, December 2009.

- Jörn-Marc Schmidt, Michael Hutter, and Thomas Plos. Optical Fault Attacks on AES: A Threat in Violet. In David Naccache and Elisabeth Oswald, editors, Fault Diagnosis and Tolerance in Cryptography, Sixth International Workshop, FDTC 2009, Lausanne, Switzerland September 6, 2009, Proceedings, pages 13–22. IEEE-CS Press, September 2009.

- Jörn-Marc Schmidt, Thomas Plos, Mario Kirschbaum, Michael Hutter, Marcel Medwed, and Christoph Herbst. Side-Channel Leakage Across Borders. In Dieter Gollmann and Jean-Louis Lanet, editors, Smart Card Research and Advanced Applications 9th IFIP WG 8.8/11.2 International Conference, CARDIS 2010, April 13-16, 2010, Passau, Germany, Proceedings, Lecture Notes in Computer Science, pages 36–48. Springer, April 2010.

- Michael Hutter, Martin Feldhofer, and Thomas Plos. An ECDSA Processor for RFID Authentication. In Siddika Berna Ors Yalcin, editor, Workshop on RFID Security RFIDsec 2010, 6th Workshop, Istanbul, Turkey, June 7-9, 2010, Proceedings, volume 6370 of Lecture Notes in Computer Science, pages 189–202. Springer, 2010.

- Thomas Plos, Hannes Groß, and Martin Feldhofer. Implementation of Symmetric Algorithms on a Synthesizable 8-Bit Microcontroller Targeting Passive RFID Tags. In Alex Biryukov, Guang Gong, and Douglas Stinson, editors, 17th Annual Workshop on Selected Areas in Cryptography - SAC 2010, Waterloo, Canada, August 12-13, 2010, Proceedings, volume 6544 of Lecture Notes in Computer Science, pages 114–129. Springer, 2010.

- Stefan Tillich, Martin Feldhofer, Mario Kirschbaum, Thomas Plos, Jrn-Marc Schmidt, and Alexander Szekely. Uniform Evaluation of Hardware Implementations of the Round-Two SHA-3 Candidates. August 2010.

- Stefan Tillich, Martin Feldhofer, Mario Kirschbaum, Thomas Plos, Jrn-Marc Schmidt, and Alexander Szekely. Hardware Implementations of the Round-Two SHA-3 Candidates: Comparison on a Common Ground. In Proceedings of Austrochip 2010, October 6, 2010, Villach, Austria, pages 43–48, October 2010. ISBN 978-3-200-01945-4.

- Martin Feldhofer, Manfred Josef Aigner, Michael Hutter, Thomas Plos, Erich Wenger, and Thomas Baier. Semi-Passive RFID Development Platform for Implementing and Attacking Security Tags. In Workshop on RFID / USN Security and Cryptography - RISC 2010, November 9-10, London, UK, 2010., 2010.

- Michael Hutter, Thomas Plos, and Martin Feldhofer. On the Security of RFID Devices Against Implementation Attacks. *International Journal of* Security and Networks 2010, 5(2/3):106–118, 2010.

- 16. Thomas Plos and Martin Feldhofer. Hardware Implementation of a Flexible Tag Platform for Passive RFID Devices. In Proceedings of the 14th Euromicro Conference on Digital System Design Architectures, Methods and Tools (DSD 2011), Oulu, Finland, August, 2011, Proceedings. IEEE Computer Society, August 2011.

- 17. Thomas Plos and Martin Feldhofer. Analyzing the Hardware Costs of Different Security-Layer Variants for a Low-Cost RFID Tag. In Security and Privacy in Communication Networks 7th International ICST Conference, SecureComm 2011, London, UK, September 7-9, 2011, Proceedings, Lecture Notes of the Institute for Computer Sciences, Social Informatics and Telecommunications Engineering. Springer, 2011.

## List of Tables

| 5.1  | Summary of the side-channel analysis results                                                                                                                                                                                                              | 51         |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 6.1  | Overview of the different fault types with the resulting EEPROM values after the write operation and the estimated thread level.                                                                                                                          | 62         |

| 6.2  | Summary of the occurred fault types and their fault-reproducibility rate.                                                                                                                                                                                 | 66         |

| 7.1  | Summary of the side-channel analysis results that have been ob-<br>tained by performing DEMA and DFA attacks on the tag proto-<br>types.                                                                                                                  | 80         |

| 8.1  | Summary of the side-channel analysis results obtained with basic<br>and enhanced version of the detached power-supply countermea-<br>sure.                                                                                                                | 93         |

| 9.1  | Typical power values of HF and UHF tags at different distances from the reader antenna                                                                                                                                                                    | 105        |

|      | Overview of the instruction set used by the low-resource 8-bit<br>microcontroller. Each instruction is listed with its type, the name,<br>the number of cycles, and a short description.                                                                  | 117        |

|      | Distribution of ROM code with respect to tag functionality Synthesis results of the flexible tag platform (excluding EEPROM and cryptographic unit)                                                                                                       | 120<br>121 |

| 11.1 | Synthesis results of the extended microcontroller with 64 x 8-bit register file excluding the ROM.                                                                                                                                                        | 130        |

| 11.2 | Overview of the adapted instruction set used by the low-resource<br>8-bit microcontroller. Each instruction is listed with its type,<br>the name, the number of cycles, and a short description (new or<br>adapted instructions are highlighted in gray). | 131        |

| 11.2 | Comparison of the selected cryptographic algorithms.                                                                                                                                                                                                      | 132        |

|      | Implementation results of the cryptographic algorithms and com-                                                                                                                                                                                           | 102        |

| 11.7 | parison with related work.                                                                                                                                                                                                                                | 136        |

| 11.5 | Synthesis results of the algorithm implementations on the micro-                                                                                                                                                                                          | -          |

|      | controller and comparison with dedicated hardware modules                                                                                                                                                                                                 | 142        |

| 11.6 | Comparison of our AES implementations with ISE                                                                                                                                                                                                            | 143        |

| 12.1 | Overview of the features and requirements of the three security-     |     |

|------|----------------------------------------------------------------------|-----|

|      | layer variants.                                                      | 149 |

| 12.2 | Summary of the implementation results of the block ciphers AES       |     |

|      | and NOEKEON that are used for the security-layer variants            | 152 |

| 12.3 | Overview of the overhead costs introduced by the different security- |     |

|      | layer variants in terms of additional registers and increased code   |     |

|      | size                                                                 | 155 |

| 12.4 | Overview of the overhead costs in terms of additional chip area      |     |

|      | (GEs) after place and route introduced by the different security-    |     |

|      | layer variants.                                                      | 156 |

| 12.5 | Overview of the answer times of the INTERNAL_AUTHENTICATE            | Ξ   |

|      | command and the EXTERNAL_AUTHENTICATE command for                    |     |

|      | different security-layer variants.                                   | 158 |

# List of Figures

| 2.1  | Overview of a basic RFID system consisting of a back-end database,<br>a reader, and a tag.                                                                              | 10 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Schematic overview of the components of a typical low-cost RFID tag.                                                                                                    | 12 |

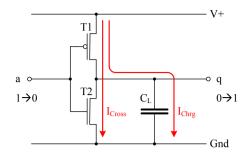

| 3.1  | Inverter circuit that demonstrates the dynamic power consump-<br>tion in CMOS devices.                                                                                  | 18 |

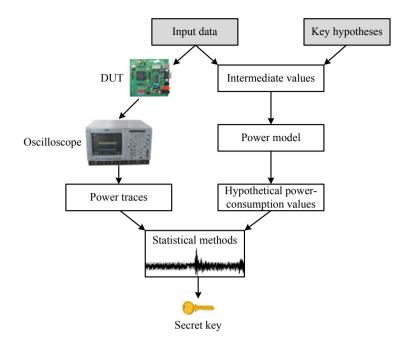

| 3.2  | Overview of the steps required for a DPA attack.                                                                                                                        | 22 |

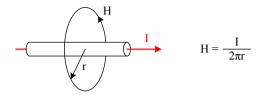

| 3.3  | Relation between current $I$ and magnetic field $H$ in a single wire.                                                                                                   | 23 |

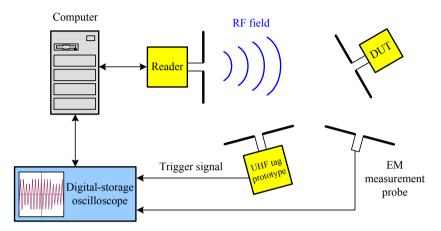

| 5.1  | Measurement setup for examining the emanation of a passive UHF RFID tag (DUT) in the far field.                                                                         | 41 |

| 5.2  | Near-field probes that have been used for the measurements                                                                                                              | 42 |

| 5.3  | Self-made dipole antenna that has been used for the measurements.                                                                                                       | 42 |

| 5.4  | Picture of the Lecroy LC584AM digital-storage oscilloscope.                                                                                                             | 42 |

| 5.5  | Picture of the 30 dB amplifier for the near-field measurements.                                                                                                         | 42 |

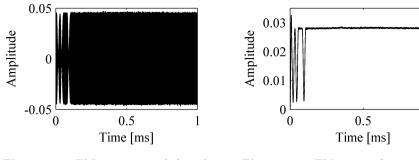

| 5.6  | EM trace recorded with our self-made dipole antenna                                                                                                                     | 44 |

| 5.7  | EM trace after transformation to baseband using demodulation<br>in software.                                                                                            | 44 |

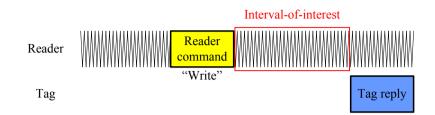

| 5.8  | Communication between reader and tag when handling a <i>Write</i> command. The interval-of-interest marks the time range that is used for recoding EM and power traces. | 45 |

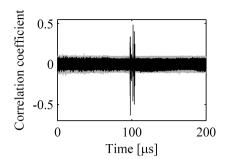

| 5.9  | Result of the DEMA attack on the UHF tag prototype by doing<br>low-pass filtering directly on the digital-storage oscilloscope.                                         | 47 |

| 5.10 | Result of the DEMA attack on the UHF tag prototype by doing<br>low-pass filtering via software in an additional preprocessing step.                                     | 47 |

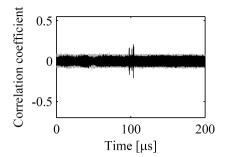

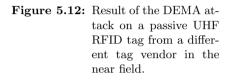

| 5.11 | Result of the DEMA attack on a passive UHF RFID tag in the near field.                                                                                                  | 48 |

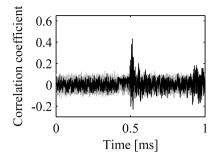

| 5.12 | Result of the DEMA attack on a passive UHF RFID tag from a different tag vendor in the near field.                                                                      | 48 |

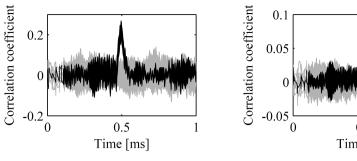

| 5.13 | Result of the DEMA attack on a passive UHF RFID tag at a distance of 20 cm using 1 000 EM traces.                                                                       | 49 |

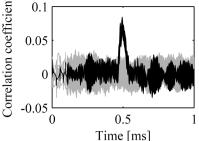

| 5.14 | Result of the DEMA attack on a passive UHF RFID tag at a distance of 1 m using 10 000 EM traces.                                                                        | 49 |

| 5.15 | Photo of a microchip that is separated from the tag antenna and connected to the reader via a shielded cable                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.16 | Result of the DPA attack on a passive UHF RFID tag using a contact-based measurement technique                                                                          |

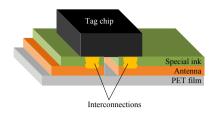

| 6.1  | Cross section of a tag where the chip is mounted onto the antenna via direct-chip attach                                                                                |

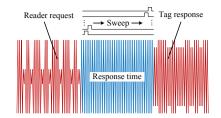

| 6.2  | Indication of the response time that is used by the tag for pro-<br>cessing the write operation                                                                         |

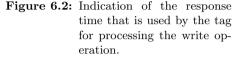

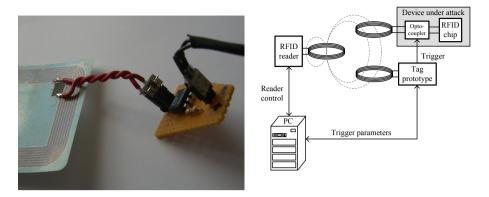

| 6.3  | Picture of the optocoupler circuit that has been inserted between tag chip and antenna                                                                                  |

| 6.4  | Schematic view of the measurement setup for performing antenna-<br>tearing attacks using an optocoupler that is placed between tag<br>antenna and chip                  |

| 6.5  | Picture of high-voltage generator with the cover of the case re-<br>moved                                                                                               |

| 6.6  | Probe coil with needle that is directly placed above the tag chip. 6                                                                                                    |

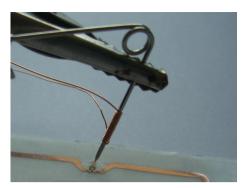

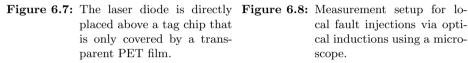

| 6.7  | The laser diode is directly placed above a tag chip that is only covered by a transparent PET film                                                                      |

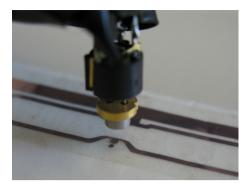

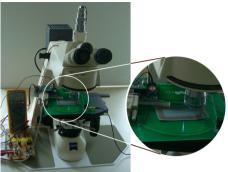

| 6.8  | Measurement setup for local fault injections via optical induc-<br>tions using a microscope                                                                             |

| 6.9  | Overview of the different fault types that occurred during globalfault injection.6                                                                                      |

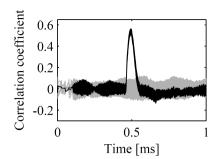

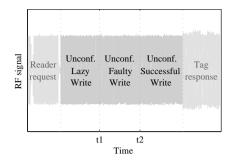

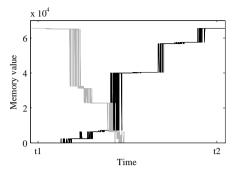

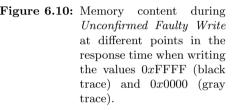

| 6.10 | Memory content during Unconfirmed Faulty Write at different<br>points in the response time when writing the values $0xFFFF$<br>(black trace) and $0x0000$ (gray trace)  |

| 7.1  | Picture of the HF (top) and the UHF (bottom) tag prototype 6                                                                                                            |

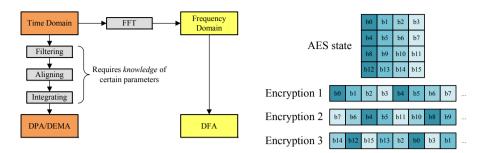

| 7.2  | Overview of the preprocessing steps necessary for DEMA and DPA as well as DFA attacks                                                                                   |

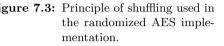

| 7.3  | Principle of shuffling used in the randomized AES implementa-<br>tion                                                                                                   |

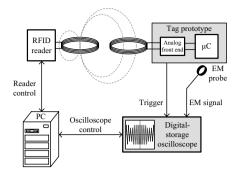

| 7.4  | Schematic view of the general measurement setup used to gather<br>the EM emissions of the tag prototypes                                                                |

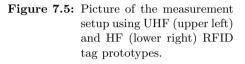

| 7.5  | Picture of the measurement setup using UHF (upper left) and HF (lower right) RFID tag prototypes                                                                        |

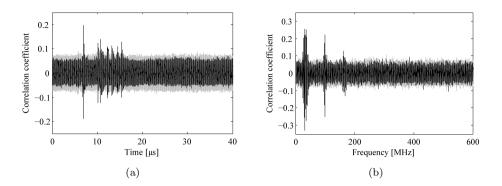

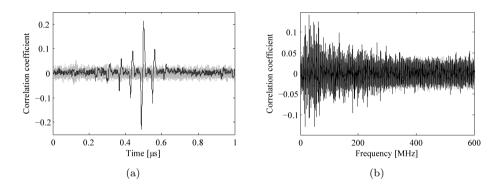

| 7.6  | Result of the filtered DEMA attack (a) and DFA attack (b) on<br>the HF tag prototype when introducing noise in the amplitude<br>dimension                               |

| 7.7  | Result of the filtered DEMA attack (a) and DFA attack (b) on<br>the UHF tag prototype when introducing noise in the amplitude<br>dimension                              |

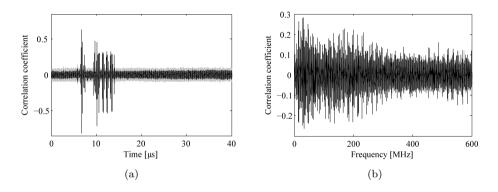

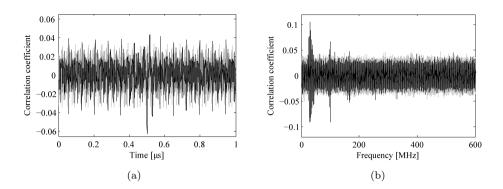

| 7.8  | Result of the windowing attack (a) and DFA attack (b) on the HF tag prototype when introducting noise in the amplitude dimension and shuffling 8 bytes of the AES state |

| 7.9         | Result of the windowing attack (a) and DFA attack (b) on the UHF tag prototype when intrducing noise in the amplitude dimension and shuffling 16 bytes of the AES state                                                          | 78         |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

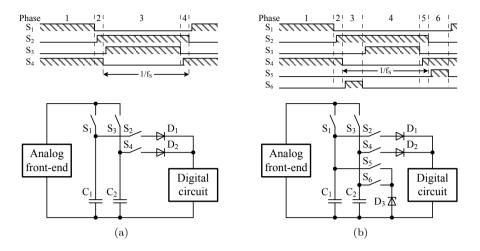

| 8.1         | Sequence diagrams comprising the states of the switches during<br>the particular phases and a schematic overview of the circuits<br>used for the basic version (a) and the enhanced version (b) of<br>the detached power supply. | 83         |

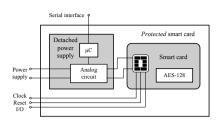

| 8.2         | Overview of the smart card protected with the detached power-<br>supply countermeasure.                                                                                                                                          | 85         |

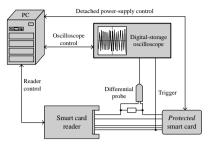

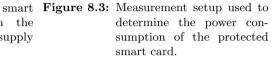

| 8.3         | Measurement setup used to determine the power consumption<br>of the protected smart card.                                                                                                                                        | 85         |

| 8.4         | Photo of the actual measurement setup containing the protected<br>smart card, a smart-card reader, and a differential probe (the<br>differential probe is connected between smart-card reader and<br>protected smart card).      | 86         |

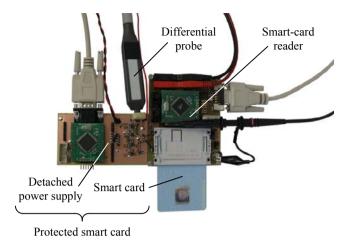

| 8.5         | Power trace of the protected smart card with the basic version of<br>the detached power supply using a switching frequency of 100 kHz.                                                                                           | 88         |

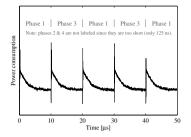

| 8.6         | Correlation coefficient as a function of the number of measure-<br>ments for the enhanced version of the detached power supply<br>using a switching frequency of 100 kHz.                                                        | 88         |

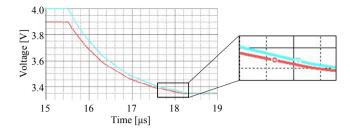

| 8.7         | Screenshot of the two discharge curves that have been obtained<br>with the computer simulation.                                                                                                                                  | 89         |

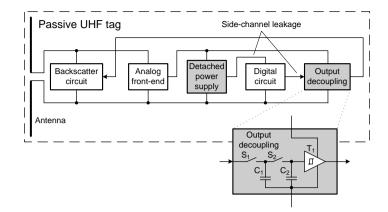

| 8.8         | Schematic of the decoupling principle for the output pin and its combination with the detached power supply to protect passive UHF tags.                                                                                         | 91         |

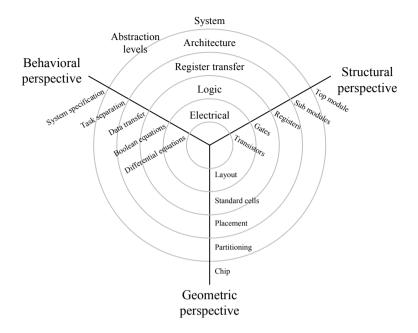

| 9.1         | Y-diagram according to Gajski and Kuhn [60] showing the differ-<br>ent design perspectives and abstraction levels of digital hardware                                                                                            |            |

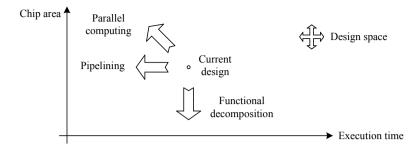

| 9.2         | circuits                                                                                                                                                                                                                         | 99<br>102  |

|             |                                                                                                                                                                                                                                  |            |

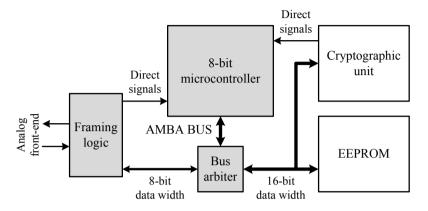

| 10.1        | Overview of the tag's digital components                                                                                                                                                                                         | 110        |

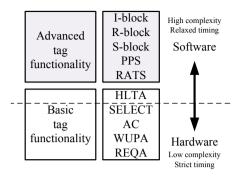

| 10.2 $10.3$ | Commands for file-access functionality and security features<br>Hardware-software separation of basic and advanced tag func-<br>tionality                                                                                        | 112<br>114 |

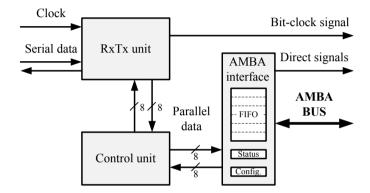

| 10.4        | Overview of framing-logic architecture.                                                                                                                                                                                          | 115        |

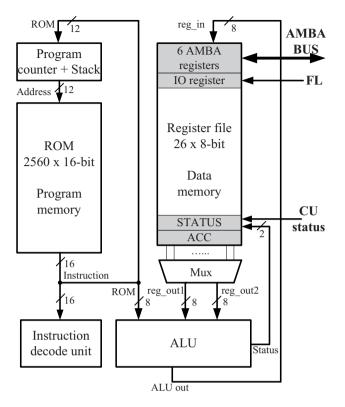

| 10.5        | Overview of microcontroller architecture.                                                                                                                                                                                        | 116        |

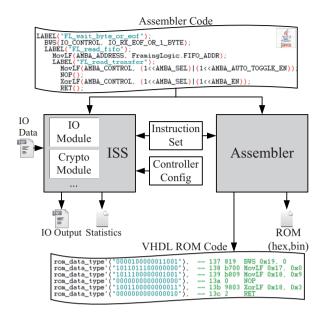

| 10.6        | Design flow for program development.                                                                                                                                                                                             | 119        |

| 10.7        | FPGA prototype communicating with an NFC-enabled mobile phone.                                                                                                                                                                   | 120        |

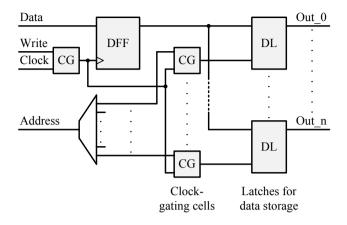

| 10.8        | Latch-based register file for the general-purpose registers of the microcontroller to reduce chip area.                                                                                                                          | 120        |

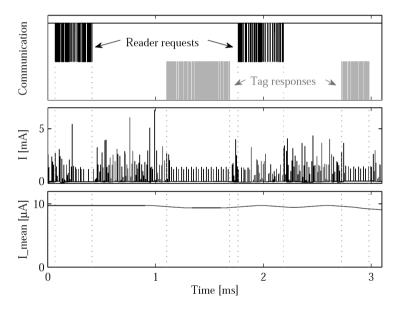

| 10.9  | Simulated power consumption $I$ (middle plot) and mean power           |     |

|-------|------------------------------------------------------------------------|-----|

|       | consumption $I\_mean$ (bottom plot) of the microcontroller to-         |     |

|       | gether with the communication between reader and NFC-compatible        | le  |

|       |                                                                        | 122 |

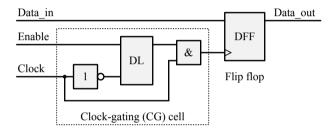

| 10.10 | Schematic of a clock-gating cell to reduce toggle activity and         |     |

|       | power consumption of the enclosed flip flop                            | 123 |

| 10.11 | Schematic overview of the tag-prototype chip architecture              | 124 |

| 10.12 | Photo of the RFID tag-prototype chip.                                  | 125 |

| 10.13 | Photo of the PCB with the packaged chip                                | 126 |

|       |                                                                        |     |

| 11.1  | Overview of the extended microcontroller architecture                  | 129 |

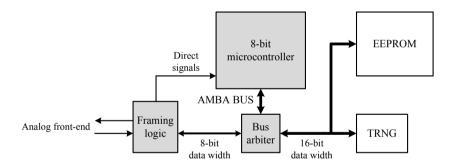

| 12.1  | Architectural overview of the tag's digital part.                      | 146 |

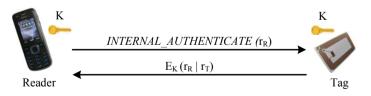

| 12.2  | Basic principle of tag authentication.                                 | 147 |

|       |                                                                        |     |

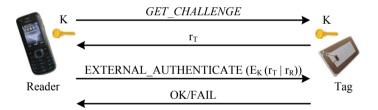

| 12.3  | Basic principle of reader authentication.                              | 148 |

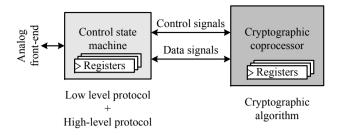

| 12.4  | Traditional approach where protocol handling and cryptographic         |     |

|       | algorithm are implemented separately                                   | 150 |

| 12.5  | Combined approach where high-level protocol and cryptographic          |     |

|       | algorithm are handled by a low-resource microcontroller                | 151 |

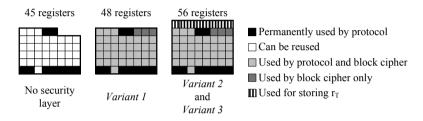

| 12.6  | Utilization of the register file for different security-layer variants |     |

|       | when using the code-size optimized version of AES                      | 153 |

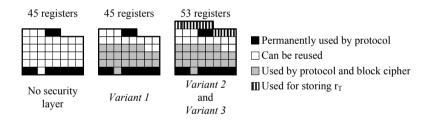

| 12.7  | Utilization of the register file for different security-layer variants |     |

|       | when using the code-size optimized version of NOEKEON                  | 153 |

# Acronyms

| ACC                 | Accumulator                                            |  |

|---------------------|--------------------------------------------------------|--|

| AES                 | Advanced Encryption Standard                           |  |

| ALU                 | Arithmetic-Logic Unit                                  |  |

| AMBA                | Advanced Microcontroller Bus Architecture              |  |

| APB                 | Advanced Peripheral Bus                                |  |

| APDU                | Application Protocol Data Unit                         |  |

| BIST                | Built-In Self Test                                     |  |

| CISC                | Complex Instruction-Set Computer                       |  |

| CMOS                | Complementary Metal-Oxide-Semiconductor                |  |

| CRC                 | Cyclic Redundancy Check                                |  |

| CRT                 | Chinese Remainder Theorem                              |  |

| CRYPTA              | Cryptographic Protected Tags for new RFID Applications |  |

| DEMA                | Differential Electromagnetic Analysis                  |  |

| DES                 | Data Encryption Standard                               |  |

| DFA                 | Differential Frequency Analysis                        |  |

| DPA                 | Differential Power Analysis                            |  |

| DRP                 | Dual-Rail Precharge                                    |  |

| DST                 | Digital Signature Transponder                          |  |

| DUT                 | Device Under Test                                      |  |

| EAN                 | European Article Number                                |  |

| ECC                 | Elliptic Curve Cryptography                            |  |

| ECDSA               | Elliptic-Curve Digital Signature Algorithm             |  |

| EDA                 | Electronic Design Automation                           |  |

| EEPROM              | Electrically Erasable Programmable ROM                 |  |

| $\mathbf{EM}$       | Electromagnetic                                        |  |

| EPC                 | Electronic Product Code                                |  |

| EPROM               | Erasable Programmable ROM                              |  |

| $\mathrm{FFT}$      | Fast Fourier Transform                                 |  |

| FIB                 | Focused Ion Beam                                       |  |

| FIFO                | First-In First-Out                                     |  |

| FIPS                | Federal Information Processing Standards               |  |

| $\operatorname{FL}$ | Framing Logic                                          |  |

| FPGA                | Field-Programmable Gate Array                          |  |

| $\mathbf{FSM}$      | Finite State Machine                                   |  |

| GCD                 | Greatest Common Divisor                                |  |

| GE                  | Gate Equivalent                                        |  |

|                     |                                                        |  |

| HDL                  | Handman Description Language                   |

|----------------------|------------------------------------------------|

|                      | Hardware Description Language                  |

| HF                   | High Frequency                                 |

| IC                   | Integrated Circuit                             |

| iMDPL                | Improved MDPL                                  |

| ISE                  | Instruction-Set Extension                      |

| ISO                  | International Organization for Standardization |

| ISP                  | In-System Programming                          |

| ISS                  | Instruction-Set Simulator                      |

| IV                   | Initial Value                                  |

| IoT                  | Internet of Things                             |

| JTAG                 | Joint Test Action Group                        |

| $_{ m LF}$           | Low Frequency                                  |

| MDPL                 | Masked Dual-Rail Precharge Logic               |

| NFC                  | Near-Field Communication                       |

| NIST                 | National Institute of Standards and Technology |

| NOP                  | No Operation                                   |

| NVM                  | Non-Volatile Memory                            |

| OBIC                 | Optical Beam Induced Current                   |

| PCB                  | Printed Circuit Board                          |

| PDA                  | Personal Digital Assistant                     |

| PET                  | Polyethylene Terephthalate                     |

| POR                  | Power-On-Reset                                 |

| PPS                  | Protocol and Parameter Selection               |

| RAM                  | Random Access Memory                           |

| RATS                 | Request for Answer to Select                   |

| $\mathbf{RF}$        | Radio Frequency                                |

| RFID                 | Radio-Frequency Identification                 |

| RISC                 | Reduced Instruction-Set Computer               |

| ROM                  | Read-Only Memory                               |

| RSA                  | Rivest-Shamir-Adleman                          |

| RSL                  | Random Switching Logic                         |

| RTL                  | Register-Transfer Level                        |

| SABL                 | Sense Amplifier Based Logic                    |

| SCA                  | Side-Channel Analysis                          |

| SEA                  | Scalable Encryption Algorithm                  |

| SEMA                 | Simple Electromagnetic Analysis                |

| SHA                  | Secure Hash Algorithm                          |

| $\operatorname{SNR}$ | Signal-to-Noise Ratio                          |

| SPA                  | Simple Power Analysis                          |

| $\operatorname{SPN}$ | Substitution-Permutation Network               |

| TRNG                 | True Random-Number Generator                   |

| UCC                  | Uniform Code Council                           |

| UHF                  | Ultra-High Frequency                           |

| UID                  | Unique Identifier                              |

| USB                  | Universal Serial Bus                           |

|                      |                                                |

| VLSI | Very Large Scale Integration       |

|------|------------------------------------|

| WDDL | Wave Dynamic Differential Logic    |

| WTX  | Waiting Time Extension             |

| XTEA | Extended Tiny Encryption Algorithm |

|      |                                    |

# Introduction

The technological advances of the last decades have strongly influenced our daily life. We are surrounded by devices that are equipped with small integrated circuits that have computing capability. Integrated circuits are not only found in personal computers and laptops, but also in cars, domestic appliances, and in any device that has communication functionality. Computers that once filled a whole room fit now in the palm of your hand and you can easily carry them around in your pocket. Computers even no longer look like computers since they are inherently integrated into the devices.

Integrated circuits are manufactured from silicon as so-called microchips. Continuous migration to more-advanced manufacturing techniques allows increasing the functionality of the microchips and lowering their power consumption. Reducing the power consumption of integrated circuits has pushed the development of mobile devices and contactless communication techniques. An important contactless communication technique is radio-frequency identification (RFID) technology, which is used for example in ticketing, electronic passports, logistics, and car immobilizers. Even the latest generation of smart phones has integrated RFID functionality, which emphasizes the relevance of this technology.

In an RFID system a reader and a tag communicate contactlessly by means of a radio-frequency (RF) field. The tag is a small microchip attached to an antenna. More than 2 billion tags have been sold in 2010. Most of them are so-called passive tags that directly receive their power from the RF field. The functionality of passive tags ranges from contactless smart cards with cryptographic coprocessors and large memories to low-cost tags that only provide a unique identifier and have very limited resources. Especially low-cost tags that can be produced at high volume are the enabler for the future Internet of Things (IoT). The vision of this future IoT is to provide communication capabilities to every object by attaching an RFID tag to it. With the IoT, many new applications will arise that have increased demands concerning functionality and security of the underlying RFID system. Since this concerns all components of the RFID system, also the tags will have to integrate more advanced functionality and security.

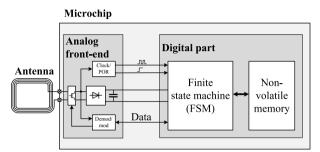

Integrating additional functionality to passive low-cost tags is challenging because of two constraints: chip size and power consumption. Chip size influences the tag price and has to be kept low. Power consumption is limited since passive tags are supplied by the RF field of the reader. Current low-cost tags are implemented as hardwired finite-state machines (FSM) to minimize chip size and power consumption. This approach is time consuming and gets even inefficient when functionality and control complexity of tags increases. Hence, programmable solutions based on a simple microcontroller are advantageous to cope with increased complexity of the tags. Moreover, using a simple microcontroller also eases the integration of security into low-cost tags.

A lot of effort has been made by the research community to bring state-ofthe-art cryptographic security to RFID tags. Prominent examples among others are symmetric-key schemes like the Advanced Encryption Standard (AES) [55, 69, 127, or public-key schemes like Elliptic Curve Cryptography (ECC) [16, 20, 71, 183]. However, low-cost tags currently available on the market neglect to consider state-of-the-art cryptographic security. They rather rely on weak security measures like passwords or make use of proprietary cryptographic algorithms that are not widely approved and kept secret instead. Several incidents of the last years have shown that proprietary cryptographic algorithms can easily be broken when they get public. The most famous examples are the reverse engineering of the CRYPTO1 algorithm in Philips' Mifare tags [135] and the breaking of the DST40 cipher in Texas Instrument's Digital Signature Transponders (DST) [27]. Moreover, weak structures of proprietary algorithms are an easy target for algebraic attacks, as it has been shown in case of the Hitag 2 cipher [40]. Hence, using cryptographic algorithms that provide state-of-the-art security is inevitable for protecting RFID systems.

State-of-the-art cryptographic algorithms are secure in a mathematical and cryptanalytical sense. However, also the devices and systems that implement the algorithms need to be secure. Weaknesses at implementation level can be exploited to dramatically lower the effort that is necessary to deduce secret information from a device (*e.g.* the secret key). Techniques that use such weaknesses are called implementation attacks. When implementing cryptographic algorithms on RFID tags, appropriate countermeasures have to be integrated to make implementation attack less effective. Further, it is necessary to evaluate the susceptibility of RFID tags against implementation attacks to get a better understanding of the potential threat scenarios.

In this thesis we address two topics that are very important for designing future low-cost RFID tags. First, we evaluate the vulnerability of low-cost tags against implementation attacks. We present successful side-channel analysis (SCA) attacks and fault-analysis attacks on commercially available RFID tags from various tag vendors. Our results clearly illustrate that low-cost RFID tags are susceptible to implementation attacks similar to contact-based devices. Hence, when implementing cryptographic algorithms on low-cost tags, countermeasures have to be integrated. This has motivated us to also evaluate the effectiveness of countermeasures like shuffling of operations and detaching the power supply that are potentially interesting for protecting RFID tags against SCA attacks.

The second topic covers hardware-implementation aspects of low-cost RFID tags. We suggest a flexible tag architecture based on a low-resource microcontroller. The flexible architecture addresses the demand of future low-cost tags in the IoT that have to deal with increased protocol complexity and advanced tag functionality. Our architecture is easily adaptable for integrating new functionality and fulfils the fierce requirements of passive low-cost tags in terms of power consumption and chip area. We further show that the microcontroller of the flexible tag architecture can be used for both protocol handling and execution of cryptographic algorithms. This combined approach is highly advantageous as it allows to reuse expensive hardware resources like memory. In that way, we can implement cryptographic algorithms like the AES with less resource usage than dedicated low-resource hardware modules.

#### **1.1** Contribution of this Thesis

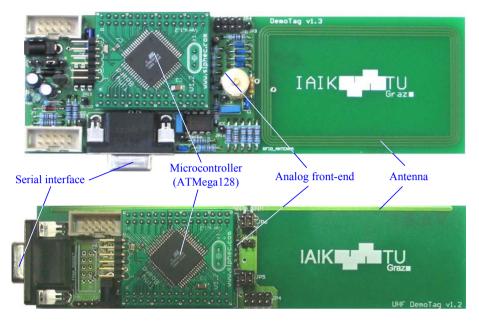

We have started our research on the topic security in RFID systems with a master thesis in [146]. A security-enabled semi-passive tag prototype for the ultra-high frequency (UHF) range has been implemented. The prototype allows not only extension of protocols but it is also very practical for evaluating the security of existing RFID systems. A description of semi-passive high frequency (HF) and UHF tag prototypes is given in [54]. This is a joint work with Martin Feldhofer, Manfred Aigner, Michael Hutter, Erich Wenger, and Thomas Baier.

Using the semi-passive UHF tag prototype has allowed us to mount first differential electromagnetic analysis (DEMA) attacks on commercially available UHF RFID tags [147]. Passive UHF RFID tags suffer from so-called parasitic-backscatter attacks that allow remote attacks from one meter and more.

In a joint work with Michael Hutter and Jörn-Marc Schmidt, the vulnerability of commercially available HF and UHF RFID tags against fault analysis has been evaluated. Fault-injection techniques based on temporarily antennatearing, electromagnetic interferences, and optical induction have been applied. First results on successful fault attacks on RFID tags have been published in [80].

Contact-based fault injections and power-analysis techniques on RFID tags have been presented in [81]. This is also a work that has been carried out together with Michael Hutter and Jörn-Marc Schmidt. Further results on implementation attacks on RFID tags have been presented with Michael Hutter and Martin Feldhofer in a Journal paper in [79].

The effectiveness of randomization as a side-channel analysis (SCA) counter-

measure for passive RFID tags has been evaluated in a joint work with Michael Hutter and Martin Feldhofer in [152, 153]. Several preprocessing techniques such as differential frequency analysis and windowing have been applied to enhance SCA attacks on randomization-based countermeasures. Another SCA countermeasure that has been analyzed is the detached power supply. The countermeasure is intended for protecting passive UHF RFID tags from remote attacks. Results of this work have been published in [148].

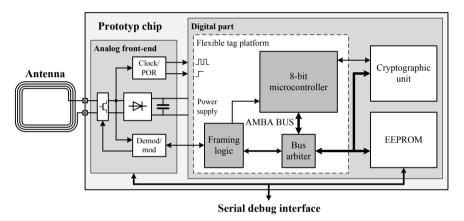

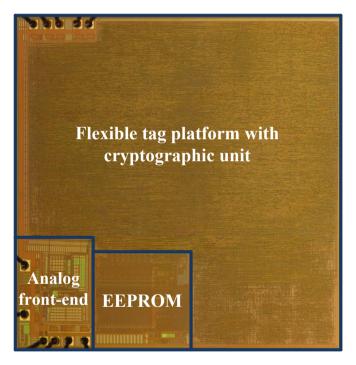

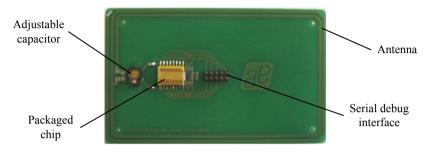

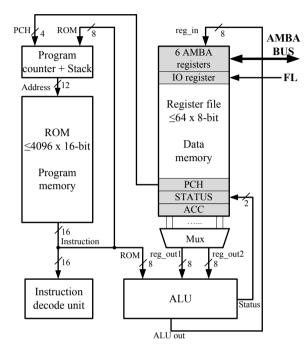

A flexible tag platform that is based on a low-resource 8-bit microcontroller has been published in [150]. The tag platform aims for low resource usage and has been developed together with Martin Feldhofer. Using this flexible tag platform allows efficiently integrating additional functionality to future low-cost RFID tags. The flexible tag platform has been used within the CRPYTA prototype chip, which is a near-field communication (NFC) enabled tag with advanced file-management functionality and security features. The prototype chip works fully passive and contains besides the flexible tag platform an analog front-end, an EEPROM, and a cryptographic unit. Analog front-end and EEPROM have been designed by the CRYPTA project partner Austriamicrosystems. The cryptographic unit that contains symmetric-key as well as public-key cryptography has been implemented by Michael Hutter. A paper that describes the cryptographic unit of the prototype chip has been published in [76] together with Michael Hutter and Martin Feldhofer.

The low-resource 8-bit microcontroller from the flexible tag platform has been adapted and used for implementing several symmetric-key algorithms on it. Symmetric-key algorithms such as AES, NOEKEON, SEA, and Trivium have been implement and compared with implementations on other microcontroller platforms. The work has been carried out together with Hannes Groß and Martin Feldhofer. The results have been published in [151] and clearly point out that our low-resource 8-bit microcontroller allows a very compact implementation of the algorithms.

We have integrated the symmetric-key algorithm implementations into the flexible tag platform in [149]. This is a joint work with Martin Feldhofer and illustrates that a combined implementation of high-level protocol handling and computation of cryptographic algorithms on the microcontroller is a highly advantageous approach. Expensive resources like memory that are used by both protocol handling and cryptographic algorithms can be easily reused. This leads to a very compact implementation that even outperforms dedicated hardware implementations of cryptographic algorithms.

A so-called new work-item proposal has been submitted to the Austrian ISO standardization committee. The proposal suggests the integration of a security layer to low-cost UHF RFID tags that operate according to the ISO 18000-6C standard. The proposal has been accepted and has served as starting point for the development of the ISO 29167 standard, which is still in its early stages.

The following publications are beyond the scope of RFID systems. In [153] a low-cost shielding device has been presented that allows to improve SCA attacks in presence of environmental noise. This is a joint work with Michael Hutter

and Christoph Herbst. Optical fault attacks on AES implementations have been published in [164] with Jörn-Marc Schmidt and Michael Hutter. We have evaluated the SCA leakage of I/O pins in [165]. The work has been carried out with Jörn-Marc Schmidt, Mario Kirschbaum, Michael Hutter, Marcel Medwed, and Christoph Herbst. High-speed implementations of the round-two SHA-3 candidates have been published in [181, 182] with Stefan Tillich, Martin Feldhofer, Mario Kirschbaum, Jörn-Marc Schmidt, and Alexander Szekely.

#### **1.2** Organization of this Thesis

We have organized this thesis into two parts. The first part covers Chapter 2-8. After a short introduction to RFID technology, we focus on implementation attacks and the evaluation of countermeasures in context of low-cost RFID tags. The second part involves Chapter 9-12 and addresses hardware-implementation aspects of low-cost RFID tags. In the following we present a short outline of the chapters in this thesis.

**Chapter 2** provides a brief introduction to RFID technology. We describe frequency ranges as well as coupling techniques of RFID systems and give details about the functionality of typical RFID tags.

**Chapter 3** gives information about implementation attacks and provides the basis for the chapters afterwards. We start with a description of side-channel analysis attacks, followed by an introduction to fault-analysis attacks.

**Chapter 4** provides basic information about countermeasures against implementation attacks. First, countermeasures against side-channel analysis attacks that use timing information, power consumption, and electromagnetic emanations are presented. Afterwards, countermeasures against fault-analysis attacks are described.

**Chapter 5** presents practical side-channel analysis results of low-cost UHF RFID tags. We give details about UHF RFID tags in general and describe the examined UHF tags as well as the utilized measurement setup. Side-channel analysis results of both a semi-passive UHF tag prototype and commercially available UHF tags from various tag vendors are presented. Attacks are conducted in the near field of the tags and in the far field.

**Chapter 6** deals with fault-analysis attacks on low-cost RFID tags. After elaborating fault-analysis techniques that are suitable for passive RFID tags, we give a description of the measurement setups that we have used for fault analysis. Further, results for globally as well as locally induced faults on HF and UHF tags are presented. Temporarily antenna tearing and electromagnetic interferences are used for global fault injections. Optical inductions are used for both global and local fault injections.

**Chapter 7** evaluates the effectiveness of randomization as a countermeasure for RFID devices against side-channel analysis attacks. We start with a description of HF and UHF tag prototypes that have been used for the evaluation. Afterwards we deal with noise in SCA measurements, followed by a discussion of techniques that lower the impact of noise and that ease the attacking of hiding countermeasures. We give a description of the deployed measurement setups and present the achieved evaluation results.

**Chapter 8** evaluates the suitability of the detached power supply as sidechannel analysis countermeasure for passive UHF RFID tags. We start with a description of the principle of the detached power supply and present a practical implementation of it. Afterwards, the measurement setup is elaborated and the side-channel analysis results are given. A simple countermeasure for preventing side-channel leakage at the modulation pin of RFID tags is presented, and the costs for integrating the detached power supply into passive UHF tags is discussed.

**Chapter 9** introduces to the design of digital hardware circuits. We describe design cycle, design space, and testability of digital hardware circuits. Afterwards, power consumption and chip-area requirements for hardware circuits used in passive low-cost tags are given.

**Chapter 10** describes the hardware implementation of a flexible tag platform that is suitable for passive low-cost tags. We start with an overview of the flexible tag platform and describe its functionality as well as the separation of tasks in hardware and software. The components of the flexible tag platform are described and implementation results are provided, followed by a short presentation of the CRYPTA tag chip that used the flexible platform.

**Chapter 11** presents the implementation of symmetric-key algorithms on a low-resource 8-bit microcontroller. Six symmetric-key algorithms are implemented: the Advanced Encryption Standard (AES), NOEKEON, Present, the Scalable Encryption Algorithm (SEA), the Extended Tiny Encryption Algorithm (XTEA), and Trivium. After a short overview of the algorithms, implementation results are provided and discussed with respect to passive RFID tags.

**Chapter 12** describes a combined implementation of protocol handling and cryptographic algorithm on a low-resource 8-bit microcontroller. We start with a system overview and introduce three security-layer variants that are implemented on the microcontroller. The security-layer variants base on the symmetric-key algorithms AES and NOEKEON, respectively. After presenting the implementation results of the different security-layer variants, their resource usage is compared.

**Chapter 13** finalizes this thesis. We give a short summary of the achieved results, draw conclusions, and discuss open research points.

### Part I

# Implementation Attacks and Evaluation of Countermeasures in Context of Low-Cost RFID Tags

# 2 RFID Technology

Radio-frequency identification (RFID) technology is a contactless communication technique that has gained a lot of attention over the last years. Many applications already relay on RFID technology. The most prominent examples among others are: inventory control, pallet tracking, ski ticketing, public transportation, access-control systems, electronic passport, animal identification, anti-theft systems, and immobilizers. The basis for modern RFID technology has been laid by the Swedish engineer Harry Stockmann in 1948. Inspired by radar engineering, he came up with the idea of transmitting data contactlessly by using reflected power [175]. However, it has taken more than forty years until the technological progress has allowed the integration of RFID technology into commercial applications.

This chapter aims to provide a brief introduction to RFID technology. We describe a basic RFID system in Section 2.1. Frequency ranges and coupling techniques used by RFID systems are explained in Section 2.2 and Section 2.3, respectively. A description of the functionality of typical RFID tags is given in Section 2.4.

#### 2.1 Description of a Basic RFID System

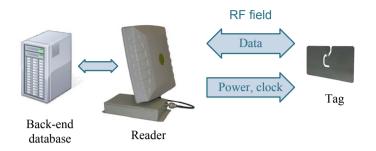

A typical RFID system consists of three components: a back-end database, a reader, and one or more tags. As depicted in Figure 2.1, the reader is connected to the back-end database and communicates with the tags contactlessly by means of a radio-frequency (RF) field. The tag is a small microchip attached to an antenna. Data is transmitted from the reader to the tags by modulating the carrier signal of the RF field. Tags demodulate the carrier signal to extract

Figure 2.1: Overview of a basic RFID system consisting of a back-end database, a reader, and a tag.

the data and potentially also derive the clock signal from the RF field. Data transmission from tag to reader is done in a similar way. The tags directly modulate the field (load modulation) or change the amount of power that is reflected by their antenna in step with the data (backscatter modulation). Power supply of the tags is either obtained from a battery or from the reader field itself. Active tags are equipped with a battery that allows them to send their response independently of the reader field. Passive tags on the other hand are completely powered by the RF field and require no additional power supply. Semi-passive tags are something between an active tag and a passive tag. They are equipped with a battery like active tags, but use the RF field for sending their response like passive tags. Especially passive tags are widely deployed since they have a simple design and are cheap in price. However, the read range of passive tags is limited because the strength of the RF field rapidly decreases with increasing distance to the reader.

# 2.2 Frequency Ranges of RFID Systems

RFID systems operate at different frequency ranges starting from 125 kHz up to 5.8 GHz. Exact frequencies can vary from country to country due to local regulations. The frequency of an RFID system has a strong impact on achievable read range, maximum data rate, and size (*i.e.* dimensions) of the tag. Mainly there are four frequency ranges used by RFID systems: low frequency (LF) range, high frequency (HF) range, ultra-high frequency (UHF) range, and microwave range [59].

## 2.2.1 Low-Frequency Range

LF systems typically operate at frequencies of 125 kHz and 135 kHz. Due to the low frequencies, there are no problems with reflections or absorbtion of the RF signal. This makes LF systems ideal for applications like animal identification. Data rates are rather low and read ranges are less than 1 m.

## 2.2.2 High-Frequency Range

RFID systems in the HF range are the ones that are most prevalent. The primer operating frequency of HF systems is 13.56 MHz. The higher frequency of the RF signal allows to use also higher data rates (*e.g.* 848 kHz [90]). Read ranges of HF systems are similar to the ones of LF systems. Well-known examples that utilize HF tags are contactless payment systems, ticketing, and library systems.

## 2.2.3 Ultra-High Frequency Range

UHF systems use frequencies from 860 MHz to 960 MHz. In contrast to HF and LF systems, read ranges of UHF systems are much larger. Typical read ranges of UHF systems are 3 to 8 m. Due to the high frequency of the RF signal, environmental influences such as refraction, absorption, and reflection have to be considered when using UHF systems. Important applications for UHF systems are toll collection, logistics, and supply-chain management.

## 2.2.4 Microwave Range