# Fully Integrated Low Power and Low Drop DC/DC Converters

Dipl.-Ing. Stefan Gruber

Submitted as thesis to attain the academic degree "Dr.techn." at the

Graz University of Technology

Institute of Electronics

Supervisor: \_\_\_\_\_

Univ.-Prof. Dipl.-Ing. Dr.techn. Wolfgang Pribyl

Co-Supervisor:

Prof. Dr.-Ing. Yiannos Manoli

Graz, November 2011

# **Statutory Declaration**

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

# Eidesstattliche Erklärung

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe.

Stefan Gruber

### Abstract

Wireless Sensor Nodes (WSNs) are an emerging technology with a wide range of applications. Different types are presented in literature or sold by companies. The principle is always similar: A self-sustained sensor is deployed to provide or route information to a different location. One major issue is the availability of energy to supply the WSN. This conflicts with the claim of extending the functionalities of sensor nodes, as demanded by the market. To accomplish this requirement, chip designers have to reduce the current consumption of the individual blocks of the sensor node and increase the efficiency of the power management.

Three different chapters discuss unique regulator architectures and a power management unit. These implementations address a variety of requirements demanded by the different power sources and operational units used for WSNs. This thesis presents implementation details and general considerations on the design of voltage regulators dedicated to WSNs having load currents in the microampere range. State-of-the-art circuits are analyzed for their adaptability to ultra-low power implementations. Whenever traditional approaches cannot be used, new circuit concepts are presented. In addition to details on circuit level, novel system design concepts are also introduced.

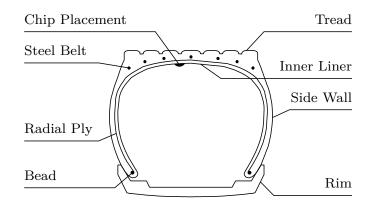

As an application example, a rich-featured WSN dedicated to, but not exclusively designed for, an in-tire Tire Pressure Monitoring System (TPMS) is presented. After an introduction of the various building blocks, the power management of this sensor node is discussed. Special attention is given to the voltage regulators required to provide the necessary supply voltages for the Integrated Circuit (IC). As WSNs operate in a harsh environment, the power management has to perform reliably. Whereas this usually conflicts with reducing the current consumption, this thesis presents novel circuits which operate in the automotive environment (-40 °C to 125 °C) and still require only a few nanoamperes.

In addition to a highly efficient DC/DC conversion, fast dynamic response times of the regulators are also required. To follow this requirement, a novel voltage regulator is presented. A Switched Capacitor (SC) regulator is combined with a linear regulator. The SC regulator provides the highly efficient DC/DC conversion, while the fast dynamic response is achieved by the linear regulator. Both regulators operate in parallel, but the linear regulator is disabled by default. It only operates if a fast dynamic response is required. The current consumption of the building blocks is below 150 nA to keep the efficiency high. To achieve this low current consumption, bias currents down to 1 nA are used. The efficiency of this regulator is up to 20 % higher than the one a conventional linear regulator provides.

Some power sources used for WSNs generate voltage levels too low to supply the IC. This thesis presents two different boost converters which utilize the SC approach. One generates a constant output voltage whereas the other one enters a periodic operation to reduce the current consumption during low input voltages. The input voltage has to be at least 0.52 V even if the output voltage is 1.2 V.

All discussed circuits have been fabricated in an Infineon  $0.13\,\mu$ m low-cost CMOS process. The obtained measurement results support the theory and the simulation results presented in this thesis.

## Kurzfassung

Wireless Sensor Nodes (WSNs) erfuhren in den letzten Jahren eine große Verbreitung. Eine große Anzahl verschiedener Sensorknoten wurden in einschlägiger Literatur publiziert und von Firmen zum Kauf angeboten. Das Prinzip ist immer ähnlich: Ein autarker Sensorknoten wird platziert, um Information zu sammeln und zu verteilen. Da keine Energieversorgung über Stromleitungen möglich ist, müssen diese Sensoren mit möglichst wenig Energie auskommen. Der Markt fordert aber immer mehr Funktionen des Sensorknotens. Deshalb muss der Stromverbrauch der integrierten Schaltung reduziert werden. Der Entwickler kann dazu die Effizienz der Spannungsregler des Leistungsmanagements erhöhen und den Stromverbrauch der individuellen Schaltungsblöcke reduzieren.

In drei verschiedenen Kapiteln werden verschiedene Spannungsregler vorgestellt. Diese Spannungsregler werden den verschiedenen Anforderungen, welche sich durch die unterschiedlichen Energiequellen für WSNs ergeben, gerecht. Bei der Implementierung der Schaltungen liegt das Augenmerk auf der Reduktion des Stromverbrauchs. Dazu werden Schaltungen, die dem neuesten Stand der Technik entsprechen, analysiert. Es wird untersucht wie sich diese Strukturen für den Betrieb am Sensorknoten eignen. Zusätzlich werden gänzlich neue Schaltungskonzepte vorgestellt, die immer dann Anwendung finden, wenn traditionelle Schaltungen nicht mehr die gewünschten Eigenschaften erzielen.

Als Anwendungsbeispiel wird ein Sensorknoten für *Tire Pressure Monitoring Systems (TPMSs)* mit den notwendigen Schaltungsblöcken vorgestellt. Der Fokus liegt dabei auf den unterschiedlichen Spannungsreglern, die für das Leistungsmanagement benötigt werden. Da Sensorkonten oft in einer rauen Umgebung arbeiten, benötigen sie zuverlässige Schaltungen. Dies steht oft im Widerspruch zur Reduktion des Stromverbrauches. In dieser Arbeit werden Schaltungen vorgestellt, die in der Automotive-Umgebung (-40 °C bis 125 °C) zuverlässig arbeiten und trotzdem nur wenige Nanoampere benötigen.

Die Spannungsregler müssen nicht nur eine effiziente Spannungsumsetzung ermöglichen, sondern sie müssen auch ein schnelles Regelverhalten zeigen. In dieser Arbeit wird eine neuartige Kombination aus einem Switched Capacitor (SC) Regler und einem Linearregler präsentiert, welche beide Anforderungen erfüllt. Während des Normalbetriebs ist der Linearregler ausgeschaltet. Kann der SC Regler die benötigte Leistung nicht zur Verfügung stellen, beginnt der Linearregler automatisch zu arbeiten. Der Gesamtstromverbrauch des Reglers liegt unter 150 nA. Dazu werden Biasströme in der Größe von 1 nA verwendet. Die Effizienz des Reglers ist bis zu 20 % höher als jene eines konventionellen Linearreglers.

Manche Energiequellen die für die WSNs verwendet werden, liefern eine niedrigere Spannung als zur Versorgung des Sensorknotens notwendig ist. Um die Eingangsspannung entsprechend hochzusetzen, werden SC Schaltungen verwendet. Es werden zwei verschiedene Konzepte vorgestellt. Während ein Regler eine konstante Ausgangsspannung liefert, arbeitet der andere periodisch, um bei kleinen Eingangsspannungen die Stromaufnahme zu reduzieren. Bei einer Ausgangsspannung von 1.2 V kann die Eingangsspannung so bis auf 0.52 V reduziert werden.

Alle vorgestellten Schaltungen wurden in einem Infine<br/>on  $0.13\,\mu{\rm m}$  CMOS Prozess gefertigt und anschließend vermessen.

# Acknowledgments

This work has been carried out at the Institute of Electronics at the Graz University of Technology in cooperation with the Contactless and RF-Exploration (CRE) Department at Infineon Technologies Austria AG. During my thesis many people gave me support, whom I would like to thank in the following:

Univ.-Prof. Dipl.-Ing. Dr.techn. Wolfgang Pribyl and Prof. Dr.-Ing. Yiannos Manoli for supervising my thesis and giving me the opportunity to carry out this thesis.

Dipl.-Ing. Gerald Holweg, head of the CRE department, for asking me to be a part of his team. I also would like to thank for the technical and administrative support and for the smooth and efficient project management.

Special thanks go to my college Günter Hofer. He always has a sympathetic ear for all kinds of problems. This thesis could not have reached this quality without his engagement.

Thanks also to all my colleges at the CRE department. My Ph.D. colleges Hannes Reinisch, Martin Wiessflecker, and Hartwig Unterassinger always had a helping hand and found time for many discussions.

Many thanks to all proof readers: Jessica, Hartwig Unterassinger, Michael Stadler, and Günter Hofer.

Finally, I would like to thank my mother Maria and my girlfriend Luzia for supporting me throughout my life.

Stefan Gruber

# **Table of Contents**

| 1 | Intr         | oduction                                                                      | 1         |

|---|--------------|-------------------------------------------------------------------------------|-----------|

|   | 1.1          | The Need for Ultra-low Power Power Management                                 |           |

|   |              | (Motivation and Problem Statement)                                            | 1         |

|   | 1.2          | Introduction to Linear and Switched Regulators                                | 3         |

|   |              | 1.2.1 Linear Regulators in CMOS Technology                                    | 4         |

|   |              | 1.2.2 SC Regulators in CMOS Technology                                        | 5         |

|   | 1.3          | Challenges in the Analog Design of Ultra-low Power Circuits                   | 6         |

|   |              | 1.3.1 Parasitic Capacitors                                                    | 7         |

|   |              | 1.3.2 Weak Inversion                                                          | 7         |

|   |              | 1.3.3 Leakage Currents                                                        | 8         |

|   | 1.4          | Simulation and Measurement Methodology                                        | 9         |

|   |              | 1.4.1 Stability Analysis                                                      | 10        |

|   |              | 1.4.2 High Ohmic Nodes                                                        | 12        |

|   |              | 1.4.3 Current Accuracy                                                        | 12        |

|   | 1.5          | Performance Parameters of Linear Regulators                                   | 13        |

|   |              |                                                                               |           |

| 2 |              | ver Management for an Ultra-low Power Wireless Sensor Node                    | 17        |

|   | 2.1          | Tire Pressure Monitoring Systems                                              | 17        |

|   | 2.2          | Wireless Sensor Node                                                          | 18        |

|   |              | 2.2.1 System Overview                                                         | 18        |

|   | 2.3          | Power Management of the Wireless Sensor Node                                  | 25        |

|   |              | 2.3.1 System Overview                                                         | 25        |

|   |              | 2.3.2 Regulator for the On-Chip Temperature Sensor along with the Analog to   |           |

|   |              | Digital Converter                                                             | 27        |

|   |              | 2.3.3 Regulator for the Digital Control Unit                                  | 44        |

|   |              | 2.3.4 Regulator for the Carrier Generation Unit                               | 50        |

|   |              | 2.3.5 Regulator for the Power Amplifier                                       | 56        |

|   | 2.4          | Conclusion                                                                    | 58        |

| 3 | • •          | a burge and Fruite Talanane Contrate of Constations Deputation                | 61        |

| 3 | ак<br>3.1    | Cobust and Fault Tolerant Switched Capacitor Regulator           Introduction | <b>61</b> |

|   | $3.1 \\ 3.2$ |                                                                               | 62        |

|   | 3.2          | A Hybrid DC/DC Converter                                                      | 62        |

|   |              | 1                                                                             |           |

|   |              |                                                                               | 66<br>70  |

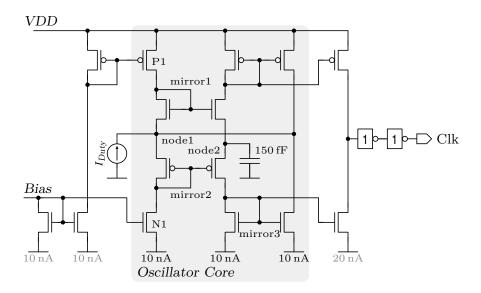

|   |              | 3.2.3 Oscillator                                                              | 70<br>70  |

|   |              | 3.2.4 Level Detectors                                                         | 76        |

|   |              | 3.2.5 Transient Analysis                                                      | 77        |

|     |        | 3.2.6 Measurement Results and Comparison                                                                           | 79  |  |  |  |  |

|-----|--------|--------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

|     | 3.3    | Conclusion                                                                                                         | 81  |  |  |  |  |

| 4   | Volt   | age Regulators for Low Input Voltages                                                                              | 83  |  |  |  |  |

|     | 4.1    | Introduction                                                                                                       | 83  |  |  |  |  |

|     | 4.2    | Regulator for Permanent Supply Requirements                                                                        | 83  |  |  |  |  |

|     |        | 4.2.1 Input Voltage Adjustment                                                                                     | 84  |  |  |  |  |

|     |        | 4.2.2 Measurement Results                                                                                          | 85  |  |  |  |  |

|     |        | 4.2.3 Conclusion                                                                                                   | 87  |  |  |  |  |

|     | 4.3    | Regulator for Slot-Based Operation                                                                                 | 87  |  |  |  |  |

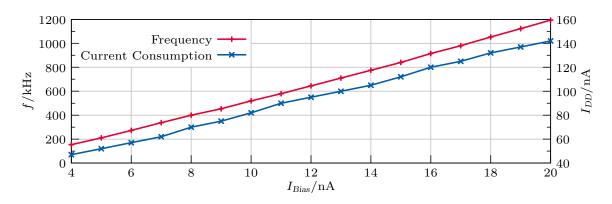

|     |        | 4.3.1 Clock Generation                                                                                             | 89  |  |  |  |  |

|     |        | 4.3.2 Input Voltage Adjustment and Control Unit                                                                    | 92  |  |  |  |  |

|     |        | 4.3.3 Linear Regulator                                                                                             | 96  |  |  |  |  |

|     |        | 4.3.4 Measurement Results                                                                                          | 96  |  |  |  |  |

|     |        | 4.3.5 Conclusion                                                                                                   | 99  |  |  |  |  |

|     | 4.4    | Conclusion                                                                                                         | 100 |  |  |  |  |

| 5   | Con    | clusion and Research Summary                                                                                       | 101 |  |  |  |  |

| -   | 5.1    |                                                                                                                    |     |  |  |  |  |

|     | -      | 5.1.1 Analog to Digital Interface                                                                                  | 101 |  |  |  |  |

|     |        | 5.1.2 Power Switch                                                                                                 | 103 |  |  |  |  |

|     |        | 5.1.3 Voltage Level Shifters                                                                                       | 104 |  |  |  |  |

|     |        | 5.1.4 Voltage Level Detectors                                                                                      | 104 |  |  |  |  |

|     |        | 5.1.5 Current Starved Ring Oscillator                                                                              | 104 |  |  |  |  |

|     |        | 5.1.6 Bias Cell                                                                                                    | 104 |  |  |  |  |

|     | 5.2    | Implemented DC/DC Converters $\ldots \ldots \ldots$ | 105 |  |  |  |  |

| Α   | Test   | t chip Layouts                                                                                                     | 107 |  |  |  |  |

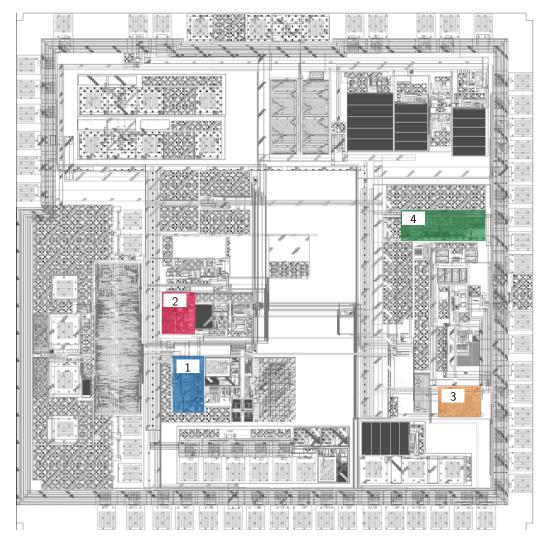

|     |        | Power Management for an Ultra-low Power Wireless Sensor Node                                                       | 108 |  |  |  |  |

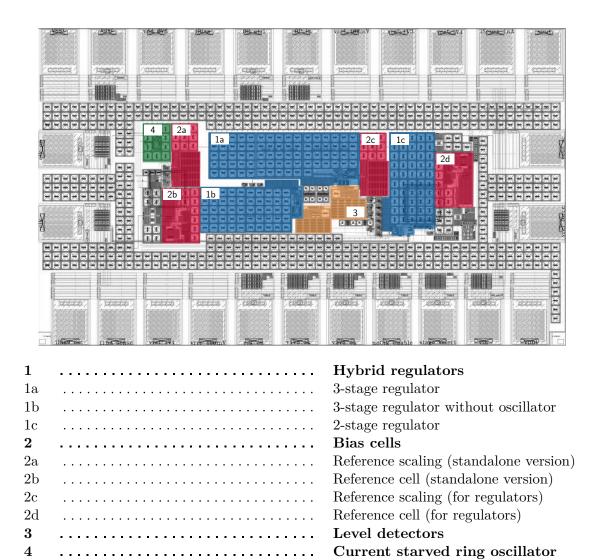

|     |        | A Robust and Fault Tolerant Switched Capacitor Regulator                                                           | 109 |  |  |  |  |

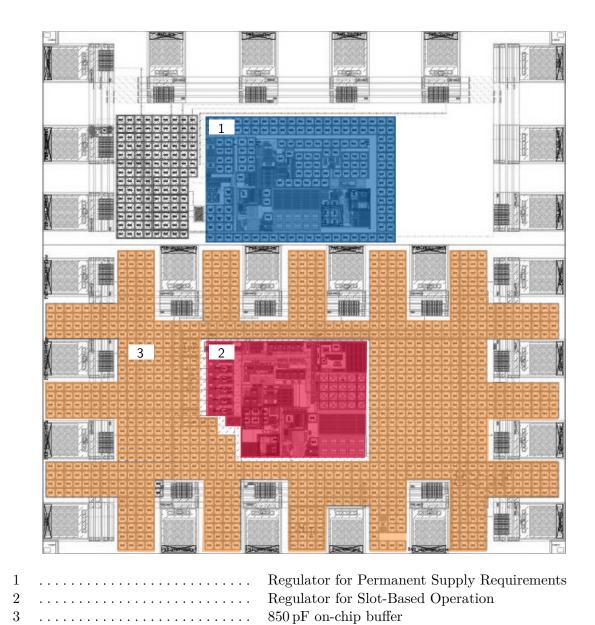

|     |        | * 0                                                                                                                | 110 |  |  |  |  |

| Bil | hlingi | raphy                                                                                                              | 111 |  |  |  |  |

|     | -      |                                                                                                                    |     |  |  |  |  |

| O١  | vn Pi  | ublications                                                                                                        | 117 |  |  |  |  |

# List of Figures

| 1.1  | Basic linear and switching regulator circuits                                     | 3  |

|------|-----------------------------------------------------------------------------------|----|

| 1.2  | Block diagram of the NMOS and the PMOS regulator                                  | 4  |

| 1.3  | Basic SC regulator architectures                                                  | 6  |

| 1.4  | Cross section of the CMOS process showing the STI stress and well proximity       |    |

|      | effect                                                                            | 7  |

| 1.5  | Leakage currents mechanisms of deep submicron transistors according to $[75]$ .   | 8  |

| 1.6  | Comparison of the leakage current of a thick oxide and a thin oxide NMOS          |    |

|      | transistor at 27 °C and $V_{GS} = 0$ V                                            | 9  |

| 1.7  | Feedback system with its Norton equivalent                                        | 10 |

| 1.8  | Middlebrook's Double-Injection Technique                                          | 11 |

| 1.9  | Double-Injection in an OTA feedback loop                                          | 11 |

| 1.10 | Bode plot showing the different transfer functions of an OTA in negative loop .   | 12 |

| 1.11 | EMI sensitive nodes in ultra-low power designs                                    | 13 |

| 2.1  | Simplified scheme of a tire showing the estimated chip placement position         | 18 |

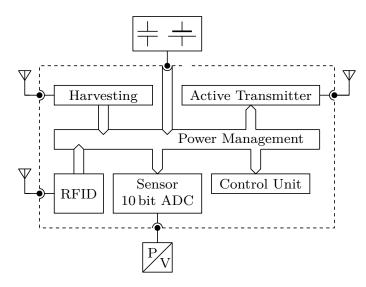

| 2.2  | Block diagram of the WSN                                                          | 19 |

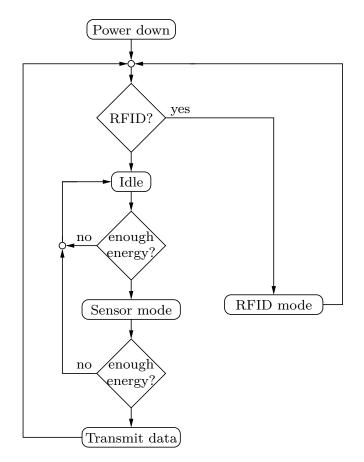

| 2.3  | Flow chart of the state machine used for controlling the sensor                   | 21 |

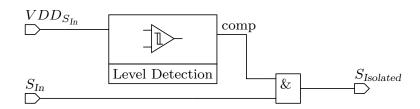

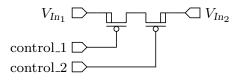

| 2.4  | Isolation logic to isolate undefined digital signals                              | 22 |

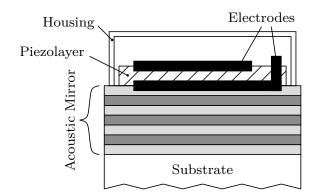

| 2.5  | Cross section of a BAW resonator as reported in [65]                              | 23 |

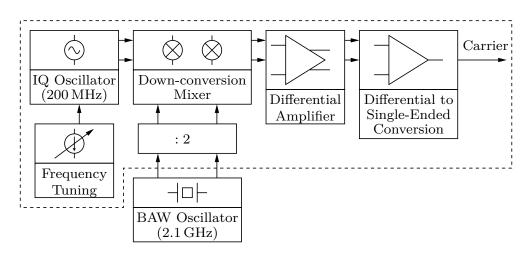

| 2.6  | Block diagram of the carrier generation for the active transmitter                | 24 |

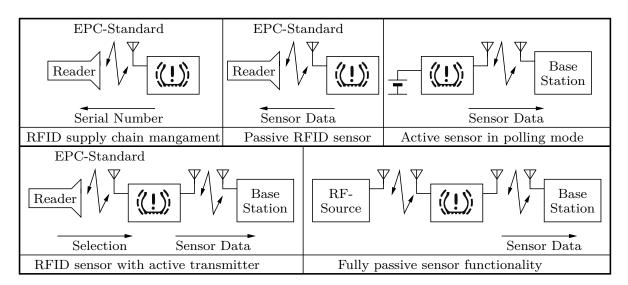

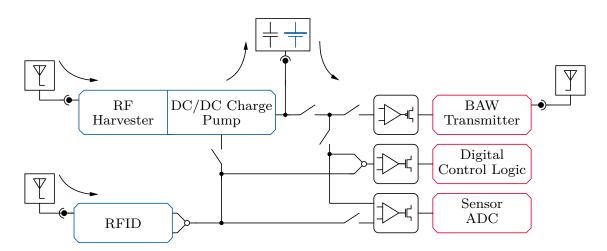

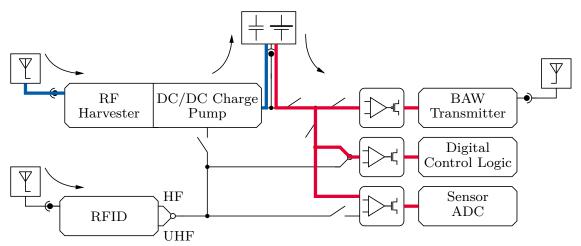

| 2.7  | Communication scenarios possible with the presented wireless sensor node          | 25 |

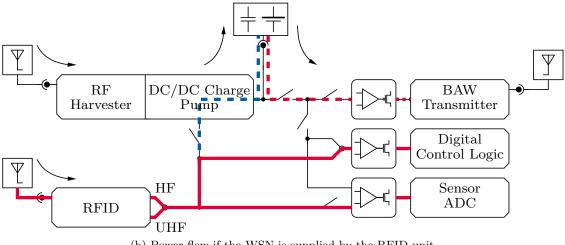

| 2.8  | Block diagram of the WSN from the power management's point of view                | 26 |

| 2.9  | Power routing on the WSN                                                          | 27 |

| 2.10 | Simplified block diagram of the regulator used for the on-chip temperature sensor |    |

|      | along with the ADC                                                                | 28 |

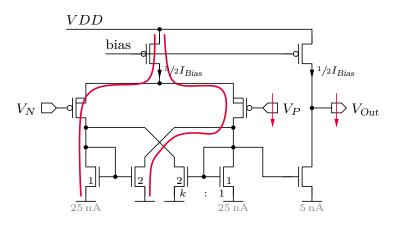

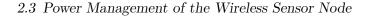

|      | Architecture of the error amplifier                                               | 29 |

|      | Comparator with built-in hysteresis                                               | 30 |

|      | Simulation of the hysteresis voltage of the window comparator                     | 30 |

|      | Delay element                                                                     | 31 |

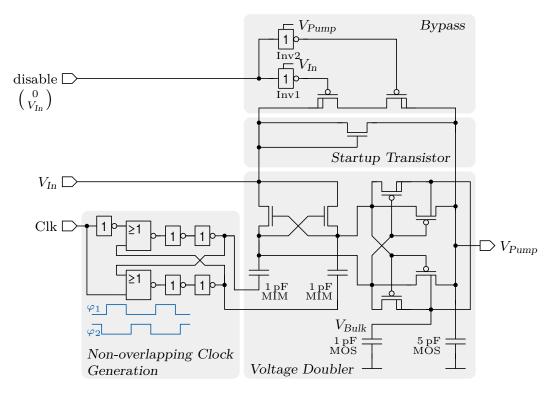

|      | Voltage doubler proposed in [22]                                                  | 32 |

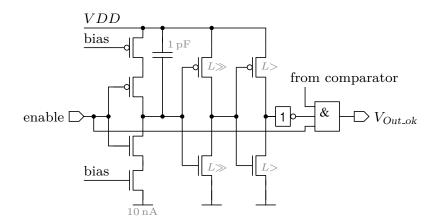

| 2.16 | Comparison of the current consumption of the charge pump voltage sensor by        |    |

|      | using different transistor lengths during startup                                 | 33 |

|      | Input voltage detector                                                            | 34 |

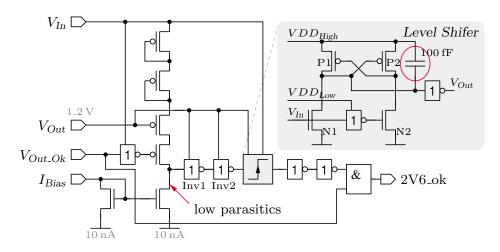

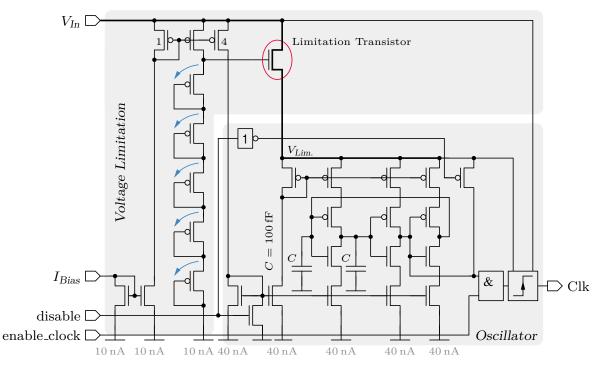

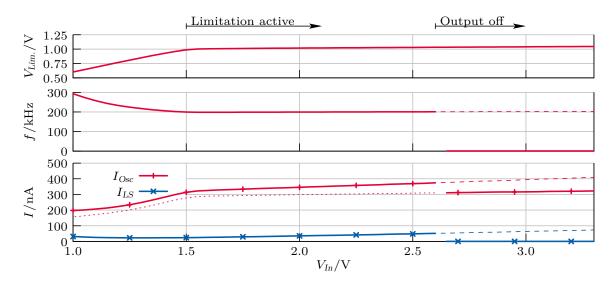

|      | Ring oscillator with supply voltage limitation                                    | 37 |

| 2.19 | Current consumption and frequency of the ring oscillator on different input       |    |

|      | voltage levels                                                                    | 38 |

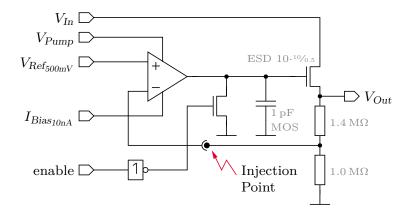

| 2.20 | Core of the regulator showing the injection point                                 | 38 |

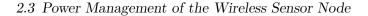

| 2.21 | Loop gain of the regulator                                                        | 39 |

|------|-----------------------------------------------------------------------------------|----|

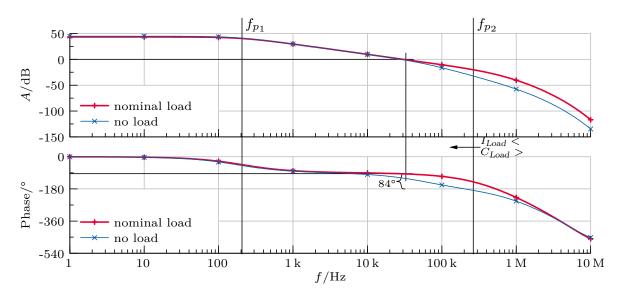

| 2.22 | Control logic of the regulator                                                    | 40 |

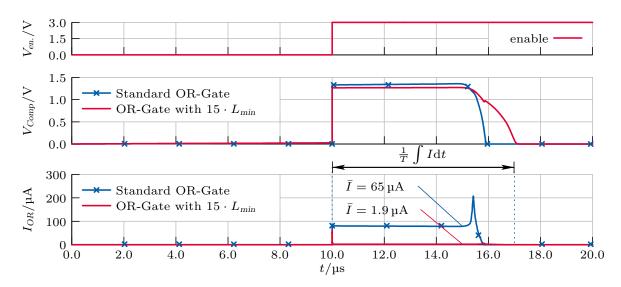

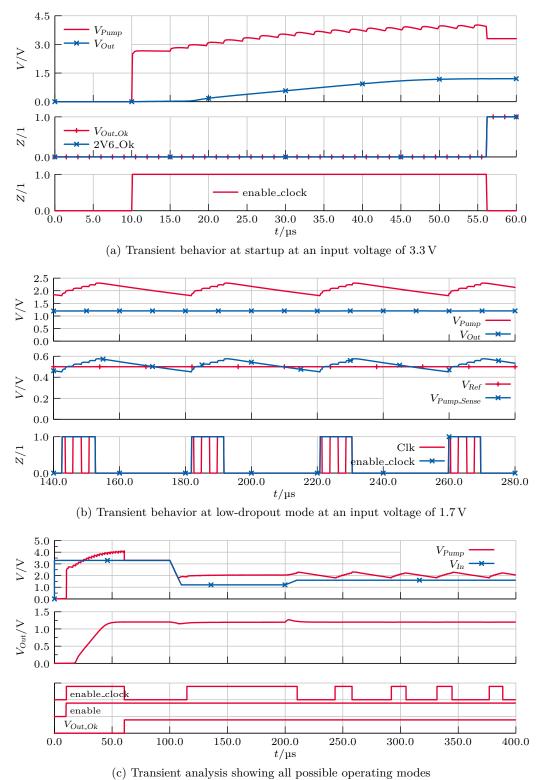

| 2.23 | Detailed transient analysis of the operating modes of the regulator               | 41 |

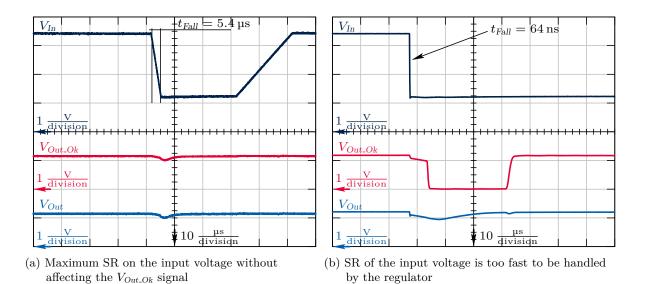

| 2.24 | Measurement of the regulator's behavior during different input voltage slew rates | 42 |

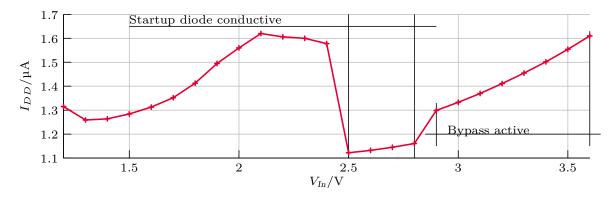

| 2.25 | Measured current consumption of the regulator                                     | 43 |

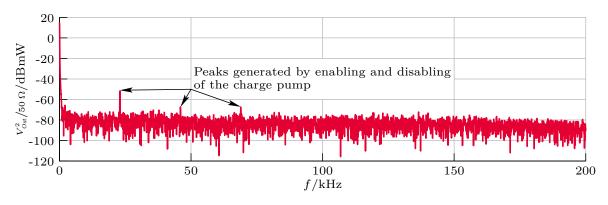

| 2.26 | Measured FFT of the output voltage referred to $50\Omega$                         | 44 |

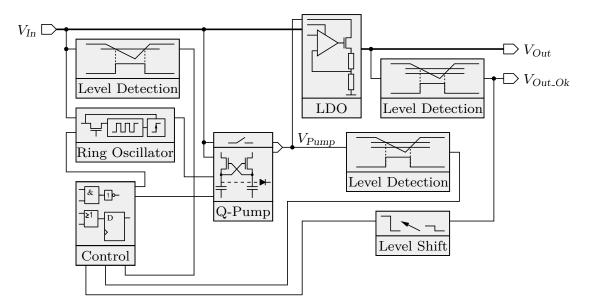

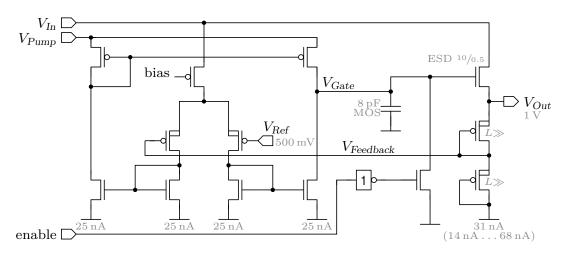

| 2.27 | Simplified block diagram of the regulator used for the digital control unit       | 45 |

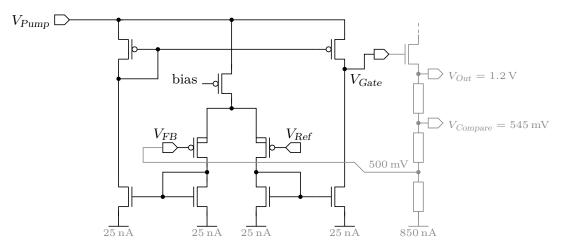

| 2.28 | Core of the regulator                                                             | 46 |

|      | Illustration of the push on the output voltage of the charge pump during an       |    |

|      | input voltage drop                                                                | 47 |

| 2.30 | Measurement of the regulator's behavior on different input voltage and load       |    |

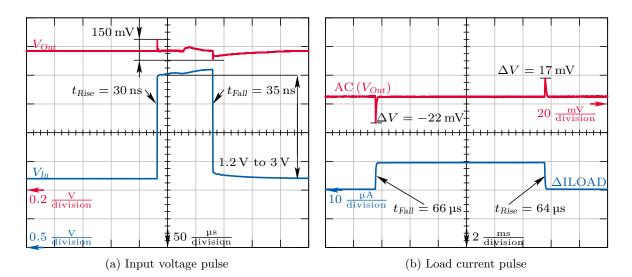

|      | current transients                                                                | 48 |

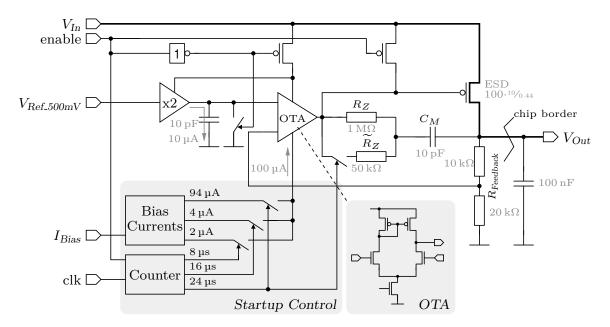

| 2.31 | Simplified architecture of the regulator supplying the carrier generation unit    | 51 |

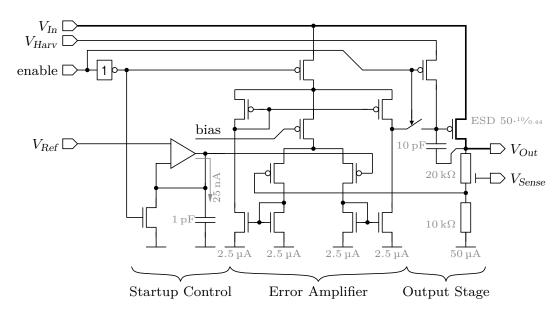

| 2.32 | Equivalent circuit of a two-stage amplifier                                       | 51 |

| 2.33 | Input transient monitor                                                           | 53 |

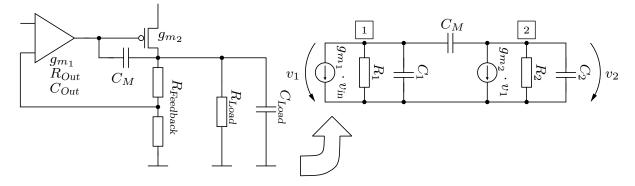

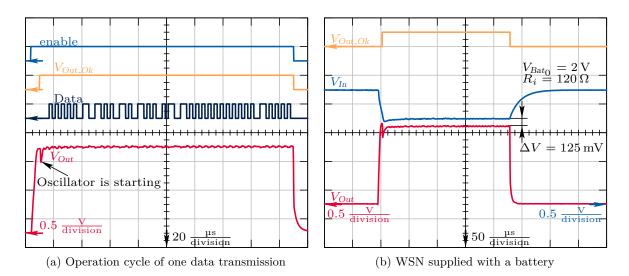

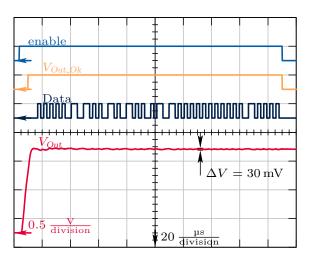

| 2.34 | Measurement results of the regulator used for the carrier generation unit         | 54 |

| 2.35 | Simplified architecture of the regulator supplying the power amplifier            | 56 |

| 2.36 | Transient output of the regulator                                                 | 58 |

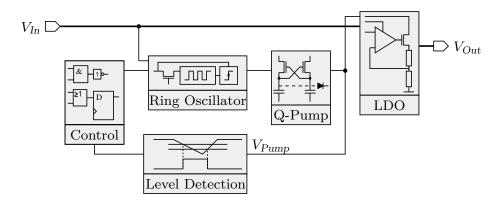

| 3.1  | Simplified block diagram of the hybrid DC/DC converter                            | 62 |

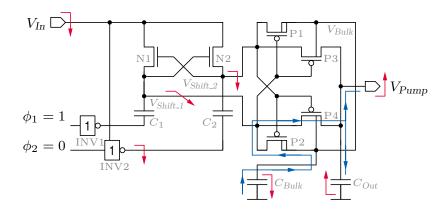

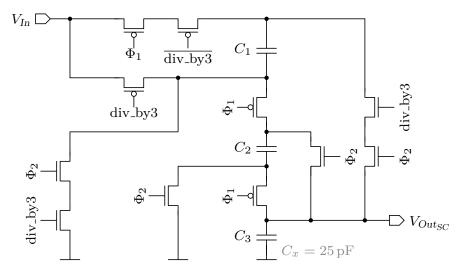

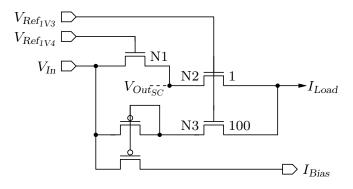

| 3.2  | SC regulator                                                                      | 64 |

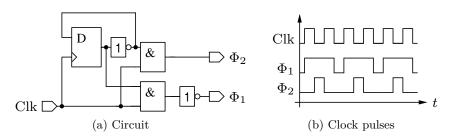

| 3.3  | Non-overlapping clock generation                                                  | 64 |

| 3.4  | Comparison of the output of the SC divider using a non-overlapping and an         |    |

|      | overlapping clock                                                                 | 65 |

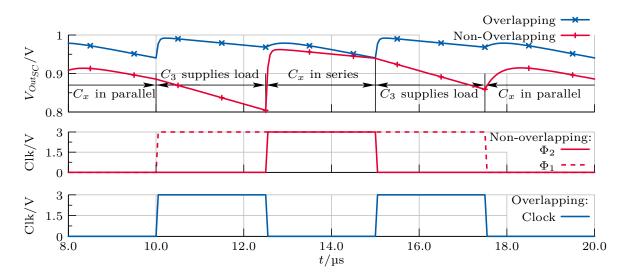

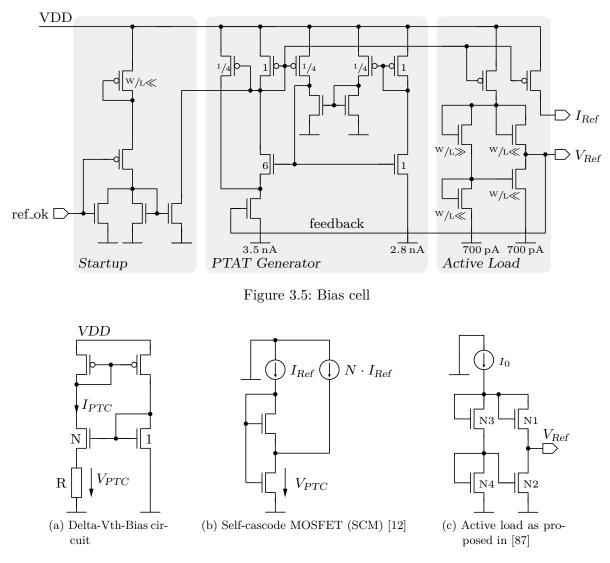

| 3.5  | Bias cell                                                                         | 67 |

| 3.6  | Building blocks of the bias cell                                                  | 67 |

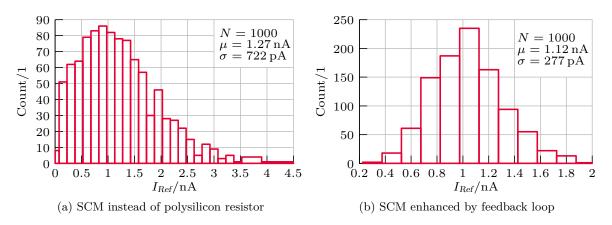

| 3.7  | Distribution of the reference current                                             | 68 |

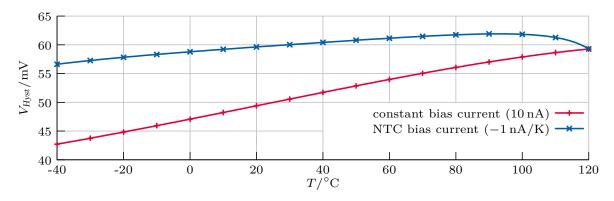

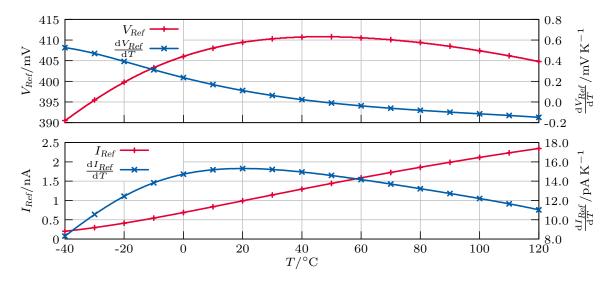

| 3.8  | Temperature behavior of the reference voltage and the reference current           | 68 |

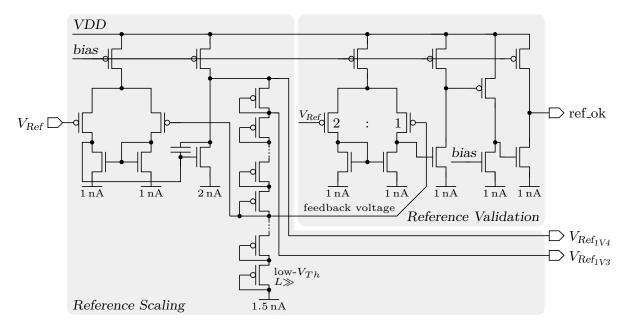

| 3.9  | Scaling of the reference voltage                                                  | 69 |

| 3.10 | Current-conveyor relaxation oscillator proposed in [64]                           | 71 |

| 3.11 | Frequency and current consumption of the current-conveyor oscillator at different |    |

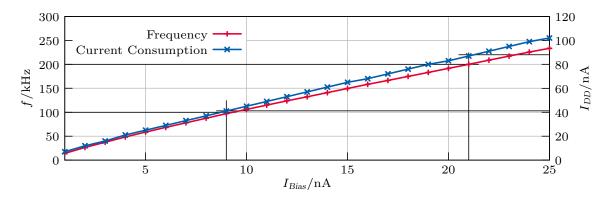

|      | bias currents at 1 V                                                              | 71 |

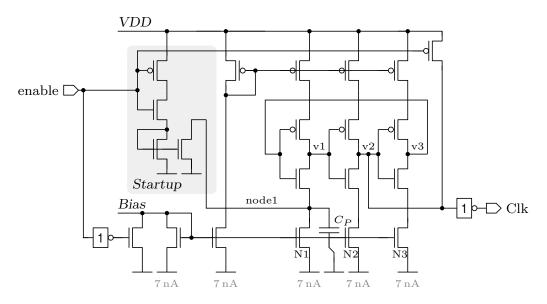

| 3.12 | Three-stage current starved ring oscillator                                       | 72 |

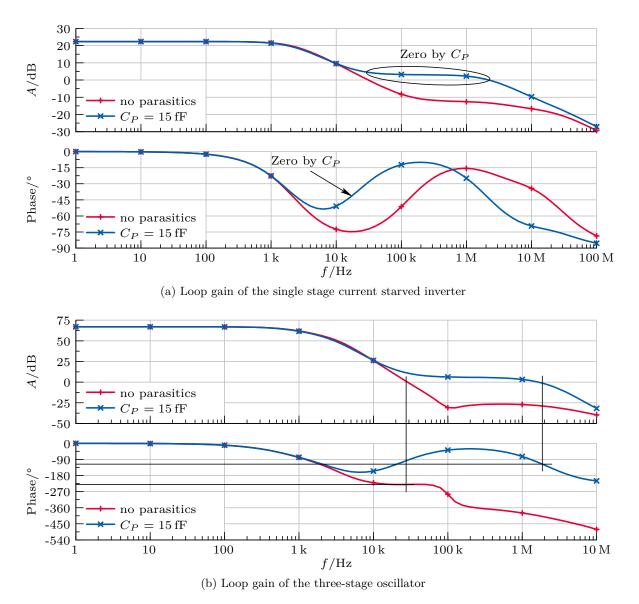

|      | Loop gain analysis of current starved inverters                                   | 73 |

| 3.14 | Frequency and current consumption of the three-stage current starved oscillator   |    |

|      | at different bias currents at 0.8 V                                               | 74 |

| 3.15 | Circuit to derive the bias current for the oscillator                             | 75 |

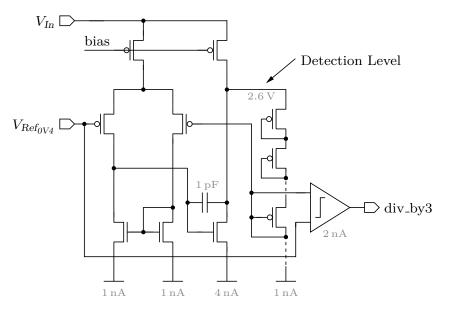

|      | Concept of the level detector                                                     | 75 |

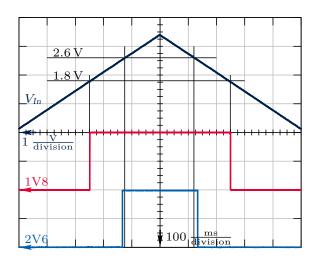

|      | Measurement results of the level detectors                                        | 76 |

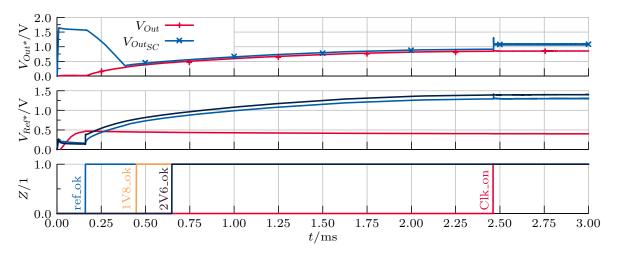

|      | Startup of the hybrid regulator at an input voltage of $3.3\mathrm{V}$            | 77 |

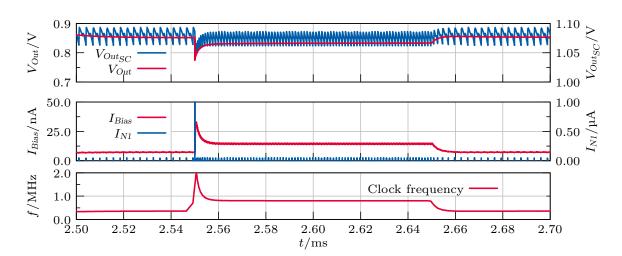

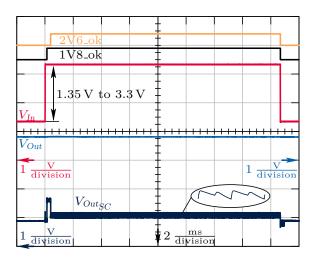

|      | Behavior of the hybrid regulator on load variations                               | 78 |

|      | Measured behavior of the regulator during input voltage transitions               | 79 |

| 3.21 | Measured efficiency of the regulator using different load currents in comparison  |    |

|      | to a linear regulator at $V_{Out} = 0.8 \mathrm{V}$                               | 80 |

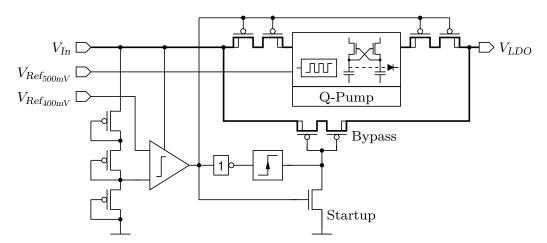

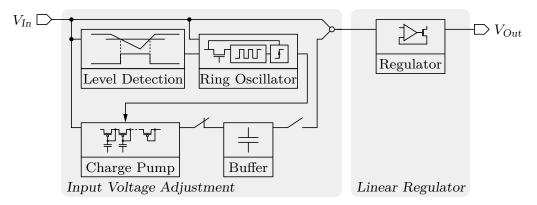

| 4.1          | Architecture of the regulator for permanent supply requirements                            |

|--------------|--------------------------------------------------------------------------------------------|

| 4.2          | Architecture of the input voltage adjustment                                               |

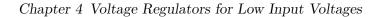

| 4.3          | Measured current consumption at $I_{Load} = 5 \mu A$                                       |

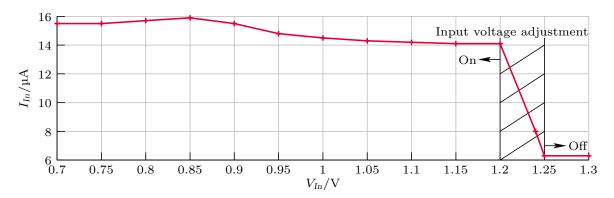

| 4.4          | Measurement results of the regulator                                                       |

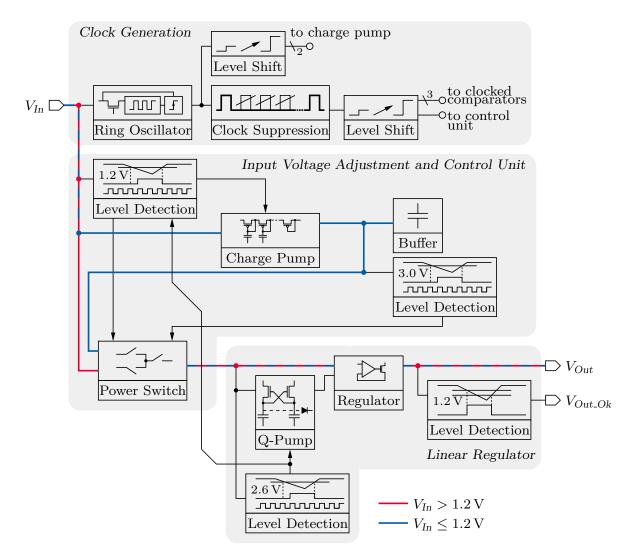

| 4.5          | Architecture of the regulator for slot-based operation                                     |

| 4.6          | Detailed architecture of the regulator for slot-based operation                            |

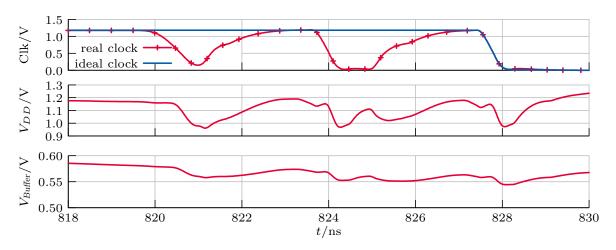

| 4.7          | Glitches generated by the oscillator                                                       |

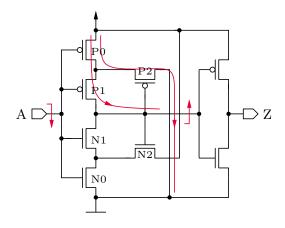

| 4.8          | Schmitt trigger                                                                            |

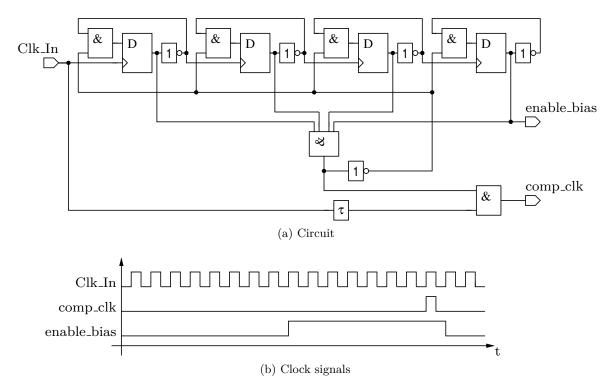

| 4.9          | Circuit of the clock suppression and the generated clock signals $\ldots \ldots \ldots 91$ |

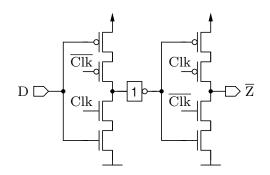

| 4.10         | Gated D latch                                                                              |

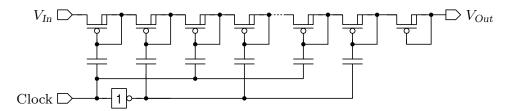

| 4.11         | Dickson charge pump in CMOS technology                                                     |

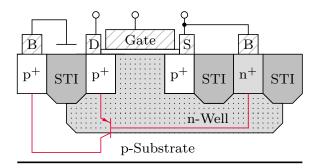

| 4.12         | Cross section of a PMOS transistor showing the parasitic pnp transistor $\ldots$ 93        |

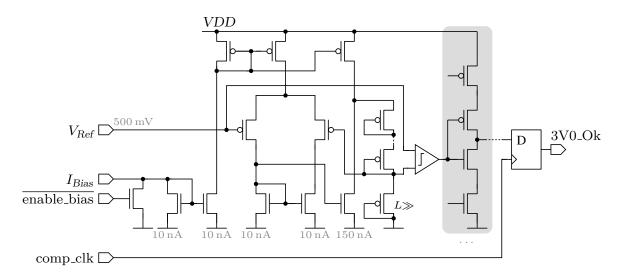

| 4.13         | 3.0V detector                                                                              |

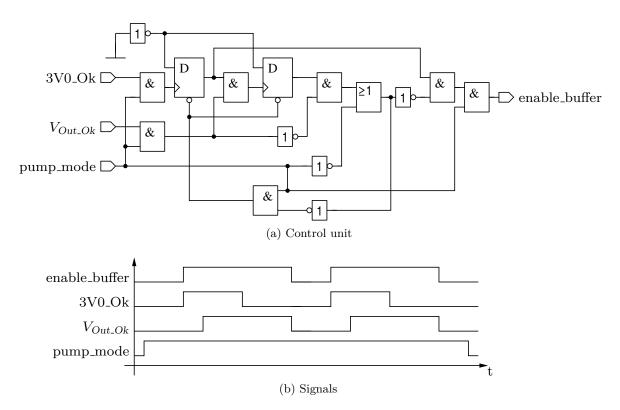

| 4.14         | Control unit and signals                                                                   |

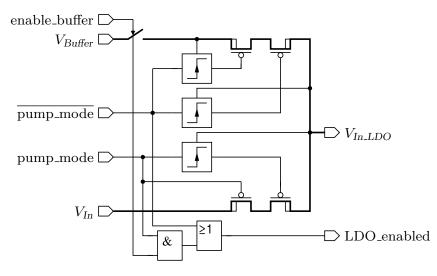

| 4.15         | Power switch                                                                               |

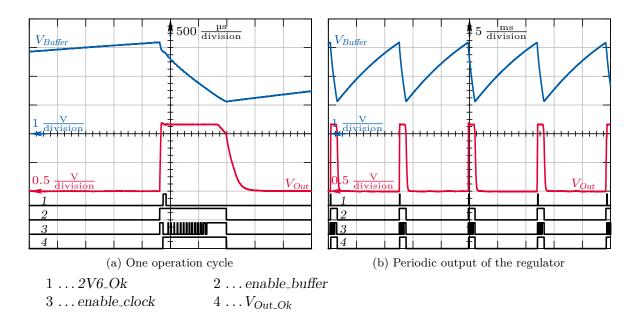

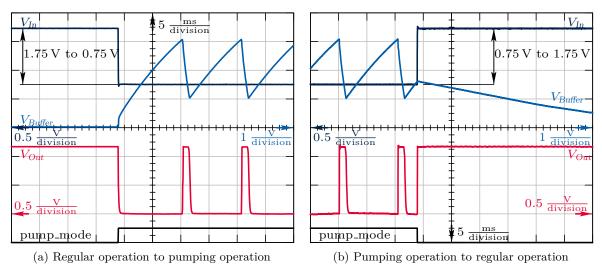

| 4.16         | Measured behavior of the regulator in pumping operation                                    |

|              | Measured behavior of the regulator during operating mode changes 98                        |

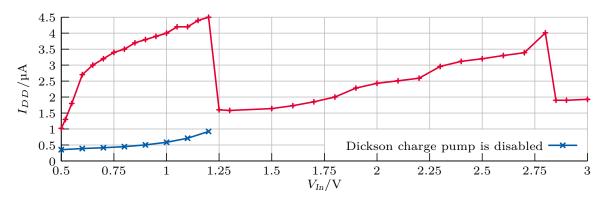

| 4.18         | Measured current consumption of the regulator                                              |

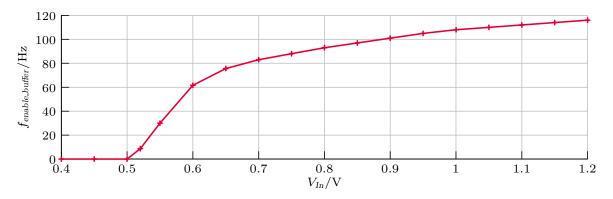

| 4.19         | Measured frequency of the enable signal of the buffer                                      |

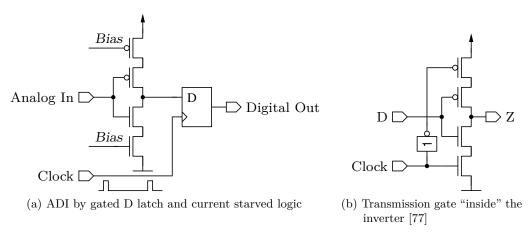

| 5.1          | Clocked ADI                                                                                |

| $5.1 \\ 5.2$ |                                                                                            |

| 0.2          | Power switch                                                                               |

| A.1          | Test chip TO1209                                                                           |

| A.2          | Test chip TO0709                                                                           |

| A.3          | Test chip $TO1210$                                                                         |

|              | •                                                                                          |

# List of Tables

| 1.1 | Comparison of different DC/DC converter topologies [28]                         | 3  |

|-----|---------------------------------------------------------------------------------|----|

| 2.1 | Summary of the different power sources used for the WSN                         | 20 |

| 2.2 | Design recommendations for the voltage doubler                                  | 32 |

| 2.3 | Performance summary of the regulator used for the on-chip temperature sensor    |    |

|     | and of the regulator dedicated to the control unit                              | 49 |

| 2.4 | Performance comparison of the regulator used for the carrier generation unit to |    |

|     | recent published similar work                                                   | 55 |

| 2.5 | Performance summary of the regulator used for the carrier generation unit and   |    |

|     | the regulator for power amplifier                                               | 59 |

| 3.1 | Performance comparison of the reference cell to recent publications             | 69 |

| 3.2 | Performance summary of the hybrid regulator compared to recent publications     | 81 |

|     |                                                                                 |    |

# Acronyms

| ABS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Alternating Current<br>Alternating Current to Direct Current<br>Analog to Digital Converter |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| BAW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bulk Acoustic Wave                                                                          |

| CAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Computer-Aided Design<br>Complementary Metal-Oxide-Semiconductor                            |

| DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Direct Current                                                                              |

| EMI       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | Electronic Product $Code^{TM}$<br>Electronic Stability Control                              |

| FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Focused Ion Beam                                                                            |

| GFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | General Feedback Theorem                                                                    |

| HF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | High Frequency                                                                              |

| IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                             |

| LTI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Linear and Time-Invariant                                                                   |

| MEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Metal-Insulator-Metal                                                                       |

| NMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |

| ОТА                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Operational Transconductance Amplifier                                                      |

| PMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | p-channel MOSFET                                                                            |

## Glossary

| PMU                                                             | Power Management Unit                               |

|-----------------------------------------------------------------|-----------------------------------------------------|

| PSRR                                                            | Power Supply Ripple Rejection                       |

| PTAT                                                            | Proportional to Absolute Temperature                |

| PTC                                                             | Positive Temperature Coefficient                    |

| RF                                                              | Radio Frequency                                     |

| RFID                                                            | Radio Frequency Identification                      |

| SC                                                              | Switched Capacitor                                  |

| SCM                                                             | Self-cascode MOSFET                                 |

| SOC                                                             | System on Chip                                      |

|                                                                 | Simulation Program with Integrated Circuit Emphasis |

| SR                                                              |                                                     |

| STI                                                             | Shallow Trench Isolation                            |

| TPMS                                                            | Tire Pressure Monitoring System                     |

| UGF                                                             | Unity Gain Frequency                                |

| $(U)HF \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | (Ultra) High Frequency                              |

| ÚHF                                                             |                                                     |

| WSN                                                             | Wireless Sensor Node                                |

# Chapter 1

# Introduction

The beginning of knowledge is the discovery of something we do not understand.

(Frank Herbert)

# 1.1 The Need for Ultra-low Power Power Management (Motivation and Problem Statement)

As proposed by M. Niedermayer in [58]: To be competitive and to reach a large market potential, the development costs of Wireless Sensor Nodes (WSNs) need to be cost-efficient. These costs are mainly formed by the manufacturing costs and by the Integrated Circuit (IC) costs. IC costs can be minimized by feature size reduction and increasing the yield in production. Manufacturing costs are decreased by simplification of the assembly and by reducing the off-chip devices. Developing fully integrated Systems on Chips (SOCs) seems to be the future approach. If the power consumption of the IC is minimized, it is even possible to integrate the battery, which is used to supply the node [78]. WSNs down to a few cubic millimeters using 3D stacking technology are already available [14]. From science's point of view the topic of fully integrated WSNs is quite challenging. This field offers a lot of open research fields and open tasks.

As discussed in [3], WSNs are classified by different applications. These applications have different requirements concerning the design and the implementation of the sensor. They have in common that they suffer from limited energy. This limitation requires new techniques in the power management. On the one hand the power consumption of the power management itself has to be reduced and on the other hand the power or the energy gathered from the power supply needs to be distributed in an efficient manner.

The reduction of the current consumption of the power management leads to more noise, less bandwidth and thus to worse load and line regulation capabilities of the regulators used for the power management. This work presents techniques on how to cope with these effects and provides design solutions. To manage the limited current budget, new design concepts are found as well as traditional methodologies are adapted to suit the new requirements.

This thesis refers several times to *ultra-low power* designs and approaches. In literature ultra-low power is defined differently. Unless noted otherwise, in this thesis ultra-low power is referred

#### Chapter 1 Introduction

to as an overall power dissipation of a functional block (for instance a temperature sensor or a digital control circuit) of  $10 \,\mu\text{W}$  and below. Individual building blocks, like reference cells, oscillators, or voltage level detectors usually have a power dissipation of  $50 \,\text{nW}$  and below. Tail currents<sup>\*</sup> down to one nanoampere are used.

The first chapter introduces the topic of ultra-low power regulator design. Well known design concepts are analyzed for their suitability to fully integrated WSNs. Problems arising when the power consumption is reduced are discussed. Design challenges as well as simulation and measurement methodologies are presented.

The main part of the thesis discusses implementation details of regulators used in ultra-low power designs. These regulators provide a stable supply voltage for circuits having current consumptions from several microampere to several milliampere. The power supplies, which are used to supply WSNs, are very different in their characteristics. So voltage regulators capable of voltage sources with an output voltage up to 3.3 V and sources having an output down to 0.5 V are discussed. Additionally, the presented regulators face input voltage transient speeds considered to be slow as well as fast transients. Clearly, these requirements need different regulator implementations. The main part is divided into three parts:

#### Chapter 2 – Power Management for an Ultra-low Power Wireless Sensor Node

This chapter presents the power management which has been implemented for a WSN dedicated to in-tire Tire Pressure Monitoring Systems (TPMSs). The design of the chip is done in a way which allows the IC to operate in different application scenarios as well. The sensor can be supplied by three different power sources and consists of four power sinks from the power management's point of view. Besides detailed analysis of the behavior of the power management, four different voltage regulators are presented in detail. The chapter gives insight into design issues and implementation details and concludes with measurement results. Comparisons to state-of-the-art implementations are also given.

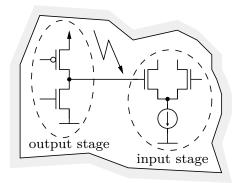

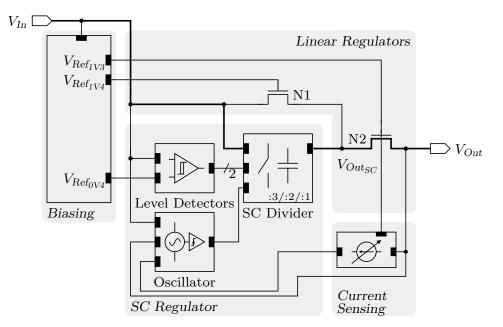

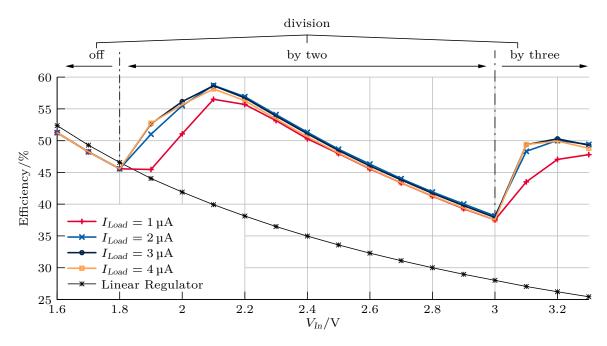

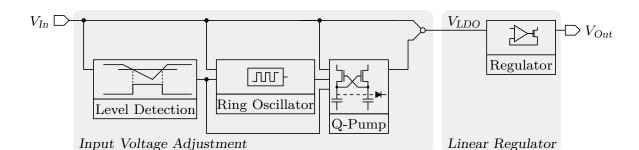

#### Chapter 3 – A Robust and Fault Tolerant Switched Capacitor Regulator

The power management presented in Chapter 2 provides no efficient conversion of the input voltage of the WSN. This chapter introduces a Switched Capacitor (SC) voltage regulator. The conversion efficiency of the power management is improved and thus the lifetime of the WSN. As fully customized implementations are not preferable, the regulator supports many different power sources used for WSNs with a supply voltage range of 1.35 V to 3.3 V. The nominal load current is 1 µA and the output voltage is 0.8 V. The regulator adapts itself to higher load current demands. For this regulator innovative analog blocks are designed and compared to recent publications. The measurement results of the regulator presented at the end of this chapter are comparable to recently published similar works.

#### Chapter 4 – Voltage Regulators for Low Input Voltages

Some power supplies used for WSNs provide a nominal voltage below the voltage required to power the IC. This chapter presents two solutions to solve this issue: Whereas one approach is a straightforward implementation, the other one tries to minimize the current

<sup>\*</sup> A tail current is the current which exists at the source of a transistor.

#### 1.2 Introduction to Linear and Switched Regulators

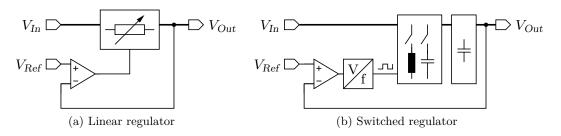

Figure 1.1: Basic linear and switching regulator circuits [74]

|                  | Linear Regulator | Switched Capacitor | Switched Inductor |

|------------------|------------------|--------------------|-------------------|

| Efficiency       | Lowest           | Low                | Highest           |

| Cost             | Lowest           | Low                | Highest           |

| Dynamic response | Fastest          | Slowest            | Fast              |

| Load current     | Low to High      | Low                | High              |

| Fully integrated | Yes              | Yes                | $\mathrm{No}^*$   |

\*A few fully integrated solutions are published (i.e. [89, 91]).

Table 1.1: Comparison of different DC/DC converter topologies [28]

requirements on low input voltages. The minimization is achieved by a periodic operation of the regulator.

### 1.2 Introduction to Linear and Switched Regulators

Gabriel Alfonso Rincón-Mora defines voltage regulators in his book Analog IC Design with Low-Dropout Regulators [74]:

A regulator generates and regulates accurate and stable output voltages that are impervious to variations in the input supply, loading environment, and various operating conditions. Unlike references, regulators supply substantial DC currents. Regulators also protect and filter ICs from exposure to voltages exceeding junctionbreakdown levels.

Voltage regulators are classified as: (1) linear and (2) switched regulators. Linear regulators make use of a resistive device in series (pass device) as shown in Figure 1.1a. The resistance is adjusted to set the desired output voltage. In CMOS technology an NMOS or a PMOS transistor is used as pass device. Switched regulators make use of an energy storage device like inductors or capacitors as illustrated in Figure 1.1b. A switch enables or disables the current flow through this device. Switching regulators first convert DC into AC and afterwards back to DC. At the output a filter is required.

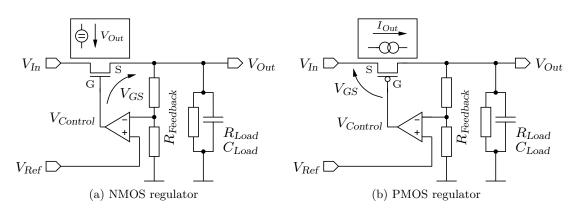

Figure 1.2: Block diagram of the NMOS and the PMOS regulator

Each type of regulator has specific advantages and disadvantages. A comparison of these parameters is shown in Table 1.1. This thesis has the focus on fully integrated ultra-low power solutions. So, only linear and SC regulators are presented.

The next paragraphs revise the basic theory of fully integrated regulators. The presentation is done differently compared to actual literature. Design issues arising from to the need of low currents are discussed. General solutions and design considerations for DC/DC converters in the ultra-low power domain are presented.

#### 1.2.1 Linear Regulators in CMOS Technology

Linear regulators used for ICs in CMOS technology have a wide range of applications. Especially whenever a stable and low noise supply voltage is required, linear regulators are in favor. Depending on the pass device type, two regulator categories are distinguished: (1) PMOS regulators, and (2) NMOS regulators.

#### **NMOS Regulators**

Figure 1.2a shows the block diagram of an NMOS regulator. To achieve an output voltage  $(V_{Out})$  mostly independent of external influences, an error amplifier is used which adjusts the gate of the pass device  $(V_{Control})$ . The advantage of this implementation is the low output impedance of the NMOS transistor. Usually, stabilization of the feedback is easy and the output is rather insensitive to input voltage variations. These advantages make this architecture preferable for low power implementations, since the error amplifier can be very simple. Despite these advantages the architecture has a major drawback. The gate voltage  $(V_{Control})$  of the pass device needs to be at least one threshold voltage higher than the output voltage of the regulator. If the input voltage of the regulator is lower than  $V_{Out} + V_{Th}$ , the required gate voltage is not available. Thus an input voltage multiplication circuit is necessary to generate  $V_{Control}$ . Usually, a charge pump is used for this multiplication. Depending on the regulator

requirements the charge pump can either supply the error amplifier [29, 94] or the gate of the pass device [11, 25, 26, 37].

#### **PMOS** Regulators

The block diagram of the PMOS regulator shown in Figure 1.2b is similar to the NMOS block diagram in Figure 1.2a. Here the pass device is formed by a PMOS transistor. The PMOS device has a high output impedance and operates as current source. Clearly, stabilization and regulating the pass device is more sophisticated than for the NMOS type. So PMOS regulators are not the ideal solution for lower power implementations. As  $V_{Control}$  is always smaller than the input voltage, this architecture is advantageous if the input and the output voltage of the regulator are in the same region.

#### Low-dropout Recovery Problem

Linear regulators, as shown in Figure 1.2, suffer from the so-called low-dropout recovery problem. PMOS and NMOS regulators are affected similarly. For the PMOS type, the gate of the pass device is at a very low level when the regulator is in low-dropout mode. If the input voltage is rising fast, the gate voltage of the pass device must also rise fast. Otherwise, overshoots on the output voltage occur. Especially for ultra-low power implementations this is a serious problem as the high current required for a fast rising gate voltage is not available. The most effective solution (besides a large off-chip capacitor) is to ensure that the gate voltage of the pass device is always higher than a certain limit. For the NMOS regulator, it is necessary to keep the gate voltage below a certain limit.

#### **Regulation of the Output Voltage**

The presented architectures make use of an error amplifier to adjust the gate potential of the pass device for different input, output, and environmental conditions. If the output voltage of the regulator must not be very accurate, the feedback can be omitted. In this case it is for instance possible to supply the gate of the pass device with a reference voltage. This reference voltage can be dependent on various parameters like temperature or load current to achieve a more or less independent output voltage of the regulator.

#### 1.2.2 SC Regulators in CMOS Technology

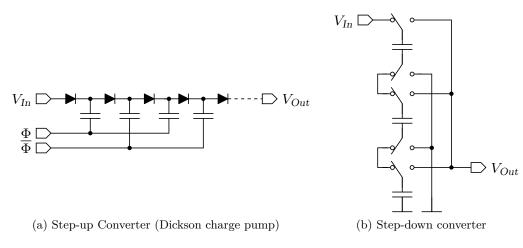

SC regulators provide a power efficient DC/DC conversion. According to [45], SC regulators can be categorized into three different types: (1) step-down (or buck) converters, (2) step-up (or boost) converters, and (3) step-down-step-up (or buck-boost) converters. The most famous implementation of step-up converters are charge pumps, like the Dickson charge pump presented in [17] and shown in Figure 1.3a. Step-down converters usually alternatingly switch capacitors in series or parallel. Figure 1.3b shows a step-down converter which divides the

Figure 1.3: Basic SC regulator architectures

input voltage by three. To achieve a highly efficient voltage conversion, a certain capacitor size or oscillator frequency is necessary. Otherwise, the necessary charge cannot be provided by the SC circuit.

If on-chip capacitors are used, the efficiency is lower than by using off-chip devices [56]. One reason is that on-chip capacitors are limited to several hundred picofarad in their size, while off-chip capacitors can have a size of several microfarad. Using off-chip capacitors allows conversion efficiencies higher than 90 % [42, 95]. For on-chip implementations, the achieved efficiency strongly depends on the load current. If the load is in the milliwatt range, the efficiency is about 50 % to 80 % [9, 43, 62]. For low power circuits delivering load currents in microampere range the efficiency is about 70 % [5, 6, 34, 39, 67, 92]. If the load current is reduced to below one microampere, the efficiency drops below 60 % [92]. To achieve the optimum efficiency, the charge transferring capacitors and the clock frequency need to be optimized. For SC regulators in the microwatt range and below, the current consumption of the oscillator is one of the limiting factors in the achievable efficiency.

# 1.3 Challenges in the Analog Design of Ultra-low Power Circuits

Reducing the current consumption of a circuit results in less speed and more noise. These parameters fundamentally depend on the current and cannot be influenced beyond a certain value unless the power is increased. Besides the decrease of the speed and the increase of the noise other challenges arise if the current consumption in analog circuits is decreased to a few nanoamperes. The most critical problems designers have to be aware of are discussed in this section.

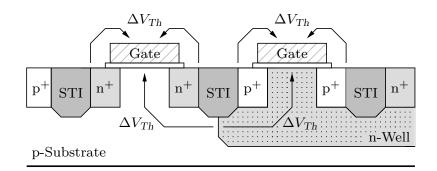

Figure 1.4: Cross section of the CMOS process showing the STI stress and well proximity effect

#### 1.3.1 Parasitic Capacitors

For ultra-low power circuits, capacitive loads become a serious issue. Loading a capacitor of only 100 fF with a current of 10 nA to 1 V already requires 10 µs. So capacitive loads need to be avoided. The lower the current consumption gets the more important the layout becomes. Parasitic capacitors generated by wires routed in parallel can slow down a circuit significantly. Modern Computer-Aided Design (CAD) tools allow the extraction of the layout of an IC to obtain parasitic capacitors generated due to the layout. As the layout is generated very late in the design process, the designer already has to estimate the parasitic capacitors in the schematic based view. Experience is essential for this estimation process.

#### 1.3.2 Weak Inversion

In ultra-low power designs tail currents of 10 nA down to 1 nA or even below that value are typical values. Usually, this current is too small to operate a transistor in the strong inversion region. A typical current mirror in an ultra-low power design operates in weak inversion, unless the length of the transistor is increased to an unreasonably large value. According to [88], the drain current of a transistor in weak inversion can be estimated using (1.3.1).  $I_{DO}$  is the specific current of a transistor,  $W_{L}$  are its dimensions,  $V_{GS}$  is the gate-source voltage,  $V_{Th}$  is the threshold voltage, n is the slope factor, and  $V_T$  is the thermal voltage.

$$I_D = I_{D0} \cdot W/L \cdot e^{\frac{V_{GS} - V_{Th}}{n \cdot V_T}}$$

(1.3.1)

(1.3.1) shows that the drain current grows exponentially as a function of the threshold voltage of the transistor. So matching becomes very important to keep differences in threshold voltage small. In the layout Shallow Trench Isolation (STI) stress and the well proximity effect influence the threshold voltage of a transistor [18]. Both effects are illustrated in Figure 1.4. As the influence is unknown before the layout is available, these effects require post-layout simulation. To minimize these influences, common centroid and similar layout matching techniques are unavoidable [76].

Not only the threshold voltage has a high impact on the drain current, but also the gatesource voltage is important. Due to the low current, analog circuits have high ohmic nodes

Figure 1.5: Leakage currents mechanisms of deep submicron transistors according to [75]

in the gigaohm region. These nodes are very sensitive to crosstalk. So distortions have to be avoided.

Of course, source degeneration reduces the sensitivity of the current mirror. (1.3.2) shows the transconductance of the degenerated transistor. If  $R_{Source}$  is increased, transconductance and thus the sensitivity decreases. As this technique requires a large ohmic resistor which increases the chip size and the complexity of the layout, it is often not feasible.

$$\widetilde{g}_m = \frac{g_m}{1 + R_{\text{Source}} \cdot (g_m + g_{mbs} + g_{ds})}$$

(1.3.2)

#### 1.3.3 Leakage Currents

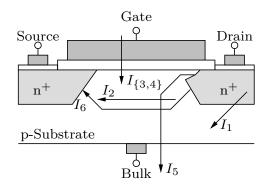

The performance of MOS transistors suffers from leakage currents. According to [75] the most significant leakage mechanisms are (refer also to Figure 1.5):

- pn-junction reverse-bias current  $(I_1)$ : Currents which leak through reverse biased pn-junctions.

- Subthreshold leakage  $(I_2)$ : If the gate-source voltage of the transistor is smaller than the threshold, it operates in the subthreshold region. The current which occurs is caused by six different phenomena (weak inversion effect, drain induced barrier lowering, body effect, narrow width effect, effect of channel length, and temperature) [55].

- Tunneling into and through gate oxide  $(I_3)$ : The thin gate oxide leads to a high electromagnetic field, which results in tunneling electronics from or into the substrate.

- Injection of hot carriers from substrate to gate oxide  $(I_4)$ : Due to the high electric field near the gate oxide, electrons gain enough energy to cross the interface barrier into the oxide layer.

- Gate-induced drain leakage  $(I_5)$ : If the transistor is in accumulation mode and the negative gate bias is large (large voltage difference between gate and drain), the drain region under the gate can be depleted or even inverted. Caused by different effects

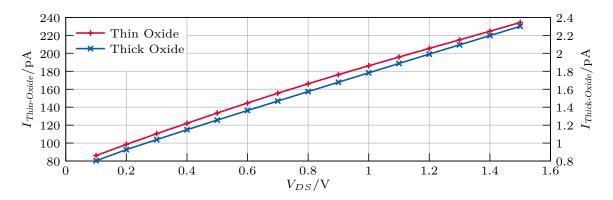

Figure 1.6: Comparison of the leakage current of a thick oxide and a thin oxide NMOS transistor at 27 °C and  $V_{GS} = 0$  V

(e.g. avalanche multiplication and band-to-band tunneling) minority carriers are emitted underneath the gate and drawn into the substrate.

• Punchthrough  $(I_6)$ : In short channel devices the depletion regions of drain and source are close to each other. At a high drain source voltage the two depletion region merge. Punchthrough has taken place. In this state, majority carriers in the source enter the substrate. Some of them are collected by the drain [55].

If the design is not done carefully, the leakage current of one transistor can be in the region of its tail current. Leakage currents can most effectively minimized by reducing the voltage drop across the transistor terminals. Using thick oxide transistors also allows for significant reduction of the gate leakage. The threshold voltage of the transistor has a major impact on the drain leakage current. Figure 1.6 shows the difference between the leakage current into the drain region of a thick oxide with having a large threshold voltage and a thin oxide NMOS transistor having a low threshold voltage in the technology used in this thesis. Concerning leakage the thick oxide device is clearly preferable. As the thick oxide transistor has also disadvantages (e.g. lower mobility or larger minimum length), this type cannot always be used.

### 1.4 Simulation and Measurement Methodology

This chapter summarizes the most challenging problems in the measurement and simulation of ultra-low power circuits, in particular linear voltage regulators. Simulation as well as measurement methodologies are discussed.

Linear regulators are considered as Linear and Time-Invariant (LTI) feedback systems, if they are treated as small-signal models. So, stability of the closed loop needs to be ensured. Various methods to verify stability exist. Here the mathematical approach of one method is presented.

Figure 1.7: Feedback system with its Norton equivalent

High ohmic nodes on the IC make it sensitive to crosstalk. This fact has to be considered in measurement. Both measurement and simulation results are affected by the limited current accuracy of the measurement and the simulation setup.

#### 1.4.1 Stability Analysis

Most types of voltage regulators have a built-in negative feedback loop. The loop is required to measure and compare the output voltage of the regulator with a reference voltage. As in any negative feedback system, stability analysis is essential. Depending on the application, different methods to verify the stability of linear systems have been developed (Routh Hurwiz Criterion, Nyquist Criterion, Bode Plot Method, Lyapunov's method, and so on). Not all methods are applicable to ultra-low power designs. This section summarizes the method used for stability analysis in this thesis.

Based on the work published by H. Bode in [8], the transfer function of negative feedback amplifiers is given by (1.4.1).

$$A_{FB}(j\omega) = \frac{A_{OL}(j\omega)}{1 + \beta(j\omega) \cdot A_{OL}(j\omega)} = \frac{A_{OL}(j\omega)}{1 + L(j\omega)}$$

(1.4.1)

$A_{FB}(j\omega)$  is the gain of the amplifier with feedback,  $\beta(j\omega)$  is the feedback factor, and  $A_{OL}(j\omega)$  is the gain of the open-loop amplifier. Necessary for stability is that the *phase margin* defined by (1.4.2) of the loop gain at unity gain ( $|L(j\omega_{UG})| = 1$ ) is greater than 0°. The phase margin for linear regulators or buffers is usually designed to be about 60°.

$$PM = \angle L(\jmath\omega_{UG}) - 180^{\circ} \tag{1.4.2}$$

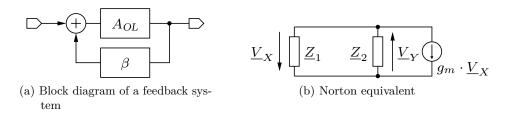

To determine the loop gain by measurement or by simulation, different methods are used. Here, the *Double-Injection Technique* published by R. D. Middlebrook in [51] is presented. A negative feedback loop as shown in Figure 1.7a can be transformed into a *Norton equivalent* depicted in Figure 1.7b or *Thévenin equivalent*. The loop gain of the equivalent circuit can be calculated using (1.4.3).

$$L(j\omega) = g_m \cdot \frac{\underline{Z}_1 \cdot \underline{Z}_2}{\underline{Z}_1 + \underline{Z}_2}$$

(1.4.3)

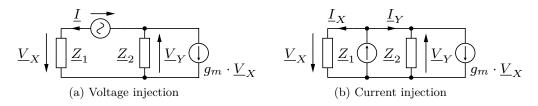

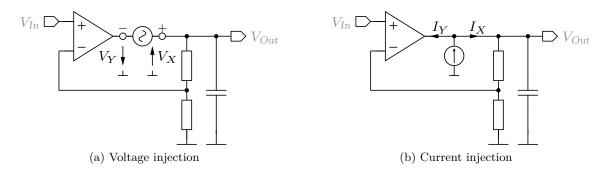

The complex impedances  $\underline{Z}_1$  and  $\underline{Z}_2$  are unknown. To obtain these values and thus the loop gain, the feedback is broken at an injection point. At this point two injections (Figure 1.8) are

Figure 1.8: Middlebrook's Double-Injection Technique

Figure 1.9: Double-Injection in an OTA feedback loop

done. The resulting transfer functions at this point are calculated or measured. The transfer function using a voltage source as shown in Figure 1.8a can be calculated using (1.4.4a). The transfer function using a current source as shown in Figure 1.8b can be calculated using (1.4.4b). The results in (1.4.4a-b) are combined and plugged in (1.4.3) to get the overall loop gain in (1.4.5). This result is then analyzed in terms of phase margin.

$$T_V(j\omega) = \frac{\underline{V}_Y}{\underline{V}_X} = \frac{\underline{Z}_2}{\underline{Z}_1} + g_m \cdot \underline{Z}_2$$

(1.4.4a)

$$T_I(j\omega) = \frac{\underline{I}_Y}{\underline{I}_X} = \frac{\underline{Z}_1}{\underline{Z}_2} + g_m \cdot \underline{Z}_1$$

(1.4.4b)

$$L(j\omega) = \frac{T_V(j\omega) \cdot T_I(j\omega) - 1}{T_V(j\omega) + T_I(j\omega) + 2}$$

(1.4.5)

The described method only works accurately if the signal flow in the loop is unilateral. Reverse transmissions are generated for instance by coupling effects from the drain to the gate of a transistor. A method which accounts for reverse gain effect is proposed by M. Tian in [80]. Also, R. D. Middlebrook developed a more general method, the General Feedback Theorem (GFT), which allows complete analysis of feedback circuits [52]. As reverse transmissions usually occur at frequencies much higher than the Unity Gain Frequency (UGF), they are negligible in stability analysis. The resulting loop gain is independent of the location of the injection point in the loop as long as the direction and the orientation of the current and voltage probes with respect to the loop is ensured.

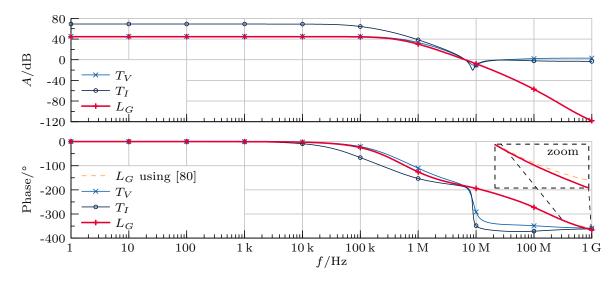

Figure 1.10: Bode plot showing the different transfer functions of an OTA in negative loop

For illustration an Operational Transconductance Amplifier (OTA) used in a closed negative feedback is analyzed. For the OTA a real model of an implemented amplifier is used. As shown in Figure 1.9, the feedback is broken and current and voltage injections are done. The respective transfer functions  $T_V$  and  $T_I$  at the injection point are plotted in Figure 1.10. The overall transfer function  $L_G$  is calculated using (1.4.5). For comparison the result of the method proposed by [80], which accounts for reverse feedback effects, is also shown.

Modern simulation tools provide the Double-Injection Technique. The user has to specify the injection point and the tool automatically runs two simulations – current injection and voltage injection. With the results of both simulations the loop gain is calculated.

#### 1.4.2 High Ohmic Nodes

The gate of an MOS transistor is high ohmic. So CMOS circuits are sensitive to crosstalk at the input. For circuits having only a few nanoamperes tail current, the output is also high ohmic. The resistance of the channel of a transistor having a drain current of 1 nA is in the gigaohm region. So ultra-low power circuits have a lot of Electromagnetic Interference (EMI) sensitive nodes. This sensitivity requires caution when measuring the IC in the lab. On-chip buffers and decoupling networks are required to get accurate measurement results.

#### 1.4.3 Current Accuracy

As discussed in Chapter 1.4.2, measuring ultra-low power circuits requires decoupling networks because of the high sensitivity to crosstalk. Therefore, off-chip capacitors are used for the measurement setup. As evaluated by measurement, these decoupling capacitors have leakage

#### 1.5 Performance Parameters of Linear Regulators

Figure 1.11: EMI sensitive nodes in ultra-low power designs

currents in the range of a few nanoamperes. Of course, these currents need to be determined by a preliminary measurement of the decoupling network.

Not only the measurements need to be verified, but the simulation results also need special attention. When simulating ultra-low power circuits, the simulator's default settings need to be revised. Simulation Program with Integrated Circuit Emphasis (SPICE) simulators usually terminate open nodes automatically with resistors to ensure convergence. Additionally, a resistor is added across nonlinear components [38]. It is necessary to ensure that these resistors have a sufficiently large value, especially when using post-layout extracted circuits. When simulating SC circuits, large current peaks appear during the switching period. These peaks are several decades larger than the average current of the circuit. To get an accurate current profile, the parameters of the simulator setting the accuracy need to be tightened.

## 1.5 Performance Parameters of Linear Regulators

Voltage regulators are characterized by different performance parameters and key figures. As such a regulator is a complicated system operating in different modes and conditions, a large number of parameters are required to describe the performance. Depending on the field of application, different specifications are decisive. This chapter summarizes the most important parameters including their definitions used for ultra-low power linear regulators. The focus is on power consumption and related parameters, whereas regulation accuracy or similar specifications have minor attention. Figures which affect CMOS circuits in general, like active area size, are not discussed.

#### **Operation Regions**

The operating regions define the possible input voltage range of the regulator with respect to the output voltage. It is common to distinguish between three different operation regions:

1. Linear operation,

- 2. Low-dropout operation, and

- 3. Below low-dropout operation.