Dipl.-Ing.(FH) Dipl.-Ing. Robert Kappel

## Development of an Ultra-Low Voltage Digital Cell Library to Reduce the Startup Voltage of Thermoelectric Harvesting Systems in Body Area Networks

## **DOCTORAL THESIS**

to achieve the university degree of

Doktor der technischen Wissenschaften

submitted to

## Graz University of Technology

Supervisor

Univ.-Prof. Dipl.-Ing. Dr.techn. Wolfgang Pribyl

Institute of Electronics

a.Univ.-Prof. Dipl.-Ing. Dr.techn. Timm Ostermann Institute for Integrated Circuits/JKU Linz

## EIDESSTATTLICHE ERKLÄRUNG AFFIDAVIT

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe. Das in TUGRAZonline hochgeladene Textdokument ist mit der vorliegenden Dissertation identisch.

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present doctoral dissertation.

Datum / Date

Unterschrift / Signature

### Abstract

Wireless sensor nodes have gained increasing interest in recent years as they enable flexible networks for control and monitoring in the field of industrial and home automation systems. Another field of application is medical diagnostics where in- and on-body sensor nodes can be used for continuous monitoring of vital parameters of patients with chronic diseases in their home environment which reduces the amount of in-hospital medical checkups. Those such devices are typically very small and consist of a measurement unit, a processor, a wireless communication unit and a local power supply. A frequently addressed problem in the field of sensor nodes is their limited operation time due to the limited energy storage capability which causes unwanted maintenance effort.

The scope of this thesis is the development of a fully integrated thermoelectric energy harvesting circuit for on-skin sensors in body area networks and covers the complete development flow. This thesis begins with the development of a thermoelectric equivalent circuit diagram to allow power output optimization. This follows investigations into the characteristics of the human body as a heat source. As thermoelectric energy sources on the human body are known to provide a low output voltage, the next part deals with the development of an ultra-low voltage digital cell library which allows operation in the deep sub-threshold region at  $90 \,\mathrm{mV}$  to  $1.2 \,\mathrm{V}$ and functionality over a wide temperature range. Due to their characteristics, on-skin sensors can be directly operated from the voltage provided by the thermoelectric generator and this then enables the system to self-start. The third topic to be discussed is the power conversion stage which has to be self-sustaining. Consequently, an analytical model of a self-sustaining charge pump was then developed, to calculate the optimum number of stages to achieve high power conversion efficiency. Finally, the implementation of the complete system on silicon is described in detail. It starts to become functional at an input voltage of 90 mV and generates a nominal output voltage of 1.2 V from a voltage of 140 mV provided by the thermoelectric generator. After the startup the output voltage remains steady down to 110 mV at the input node.

In this thesis three test chips were carried out using an Infineon 130 nm low-cost CMOS process. All implementations were done without using any special process options, e.g. low- $V_{TH}$  transistors.

### Kurzfassung

Drahtlose Sensorknoten erfahren zunehmendes Interesse in den letzten Jahren da sie flexible Netzwerke zur Überwachung und Steuerung im Bereich von Industrie und Heimautomatisierungssystemen ermöglichen. Ein weiteres Anwendungsgebiet ist die medizinische Diagnostik durch Sensoren im Körper und auf der Haut, welche zur Langzeitüberwachung von Patienten mit chronischen Erkrankungen im häuslichen Umfeld verwendet werden können und die Anzahl der Kontrolluntersuchungen in Krankenhäusern reduzieren. Diese Sensorsysteme sind üblicherweise sehr klein und bestehen aus einer Messeinheit, einem Prozessor, einer drahtlosen Kommunikationsschnittstelle und einer lokalen Energieversorgung. Ein häufig auftretendes Problem von Sensorknoten ist die limitierte Betriebsdauer aufgrund des begrenzten Energiespeichers, was den Wartungsaufwand erhöht.

Diese Dissertation beschäftigt sich mit der Entwicklung einer vollständig integrierten thermoelektrischen harvesting Schaltung für Sensoren auf der Haut in Körpernetzwerken und deckt sämtliche Bereiche der Entwicklung ab. Zu Beginn erfolgen Untersuchungen zu Eigenschaften des menschlichen Körpers als Wärmequelle, um ein thermoelektrisches Ersatzschaltbild zur Optimierung der Ausgangsleistung zu entwickeln. Thermoelektrische Energiequellen am menschlichen Körper sind bekannt für ihre geringe Ausgangsspannung. Daher beschäftigt sich diese Arbeit im nächsten Schritt mit der Entwicklung einer digitalen Schaltungsbibliothek für einen Versorgungsspannungsbereich im tiefen sub-threshold Bereich, startend ab 90 mV bis 1.2 V und einer Funktionalität über einen weiten Temperaturbereich. Aufgrund ihrer Eigenschaften kann die Logik direkt mit der Ausgangsspannung des Thermogenerators betrieben werden. Dies ermöglicht ein selbststartendes System. Das dritte Thema zur Diskussion behandelt die selbsterhaltende Spannungswandlungsstufe. Dazu wird zuerst ein analytisches Model der selbsterhaltenden Ladungspumpe entwickelt, um die optimale Anzahl der Stufen für maximale Wandlungseffizienz zu berechnen. Anschließend wird die Implementierung des Systems auf Silizium im Detail beschrieben. Es beginnt ab einer Eingangsspannung von 90 mV zu arbeiten und erzeugt eine nominale Ausgangsspannung von 1.2 V ab einer vom thermo-elekrischen Generator erzeugten Spannung von 140 mV. Nach erfolgtem Start wird die nominale Ausgangsspannung bis zu einer Eingangsspannung von 110 mV gehalten.

In der Disseration werden drei Testchips vorgestellt, welche in einem Standard Infineon 130 nm CMOS Prozess implementiert wurden. Dabei wurde auf speziellen Prozessoptionen, wie z.B. Low- $V_{TH}$  Transistoren, verzichtet.

## Acknowledgments

This work has been carried out at the Institute of Electronics at the Graz University of Technology in cooperation with the Contactless and RF-Exploration (CRE) Department at Infineon Technologies Austria AG, within the research projects, "MAS – Nanoelectronics for Mobile Ambient Assisted Living-Systems", funded by ENIAC and "NanoCaTe - Nano-carbons for versatile power supply modules", funded by EU. During my thesis many people gave me support, whom I would like to thank in the following acknowledgments:

Univ.-Prof. Dipl.-Ing. Dr.techn. Wolfgang Pribyl and a.Univ.-Prof. Dipl.-Ing. Dr.techn. Timm Ostermann for supervising my work and giving me the opportunity to carry out this thesis.

Dipl.-Ing. Gerald Holweg, head of the CRE department, for giving me the opportunity to be a part of his team. I also would like to thank Dipl.-Ing. Günter Hofer and Dipl.-Ing. Johannes Schweighofer for the technical and administrative support. Special thanks go to Dipl.-Ing. Thomas Herndl for his cooperation and help in applying for funding projects and his continuous support during the entire duration of the project.

I want to thank Univ.-Prof. Dipl.-Ing. Dr.techn. Bernd Deutschmann, Dipl.-Ing. Dr.techn. Mario Auer and Ass. Prof. Dipl.-Ing. Dr.techn. Gunter Winkler for their assistance and the time they made for discussions.

Thanks also to all my colleagues at the CRE department. My Ph.D. colleagues Walther Pachler and Martin Wiessflecker would always lend a hand and found time for many discussions. In addition I would like to thank all other colleagues from the department of CRE at Infineon who always provided a friendly and pleasant working atmosphere without naming them. I wish them all the best for finishing their work successfully.

Many thanks to all proofreaders: Ass. Prof. Dipl.-Ing. Dr.techn. Peter Söser, Dipl.-Ing. Dr.techn. Mario Auer and Sarah Waddingham.

Finally, I would like to thank my family, my wife Linda and my children Lisa and Julian for their patience during the thesis and my parents for supporting me throughout my life.

Thank you very much, all of you.

Robert Kappel

# **Table of Contents**

| 1 | Intro | oduction                                                               | 1  |

|---|-------|------------------------------------------------------------------------|----|

|   | 1.1   | Motivation                                                             | 1  |

|   | 1.2   | Organization of the Thesis                                             | 2  |

|   | 1.3   | Thermoelectric Energy Harvesting                                       | 3  |

|   |       | 1.3.1 System Architecture of a Thermoelectric Generator                | 4  |

|   |       | 1.3.2 Thermoelectric Equivalent Circuit Diagram and Power Optimization | 5  |

|   | 1.4   | Thermal Resistance of the Human Body                                   | 8  |

| 2 | Dev   | elopment of an Ultra-Low Voltage Digital Logic Cell Library            | 11 |

|   | 2.1   | Minimum Supply Voltage of Digital Logic Cells                          | 11 |

|   |       | 2.1.1 Sub-threshold Conduction of MOS Transistors                      | 13 |

|   |       | 2.1.2 MOS Transistor as Leakage Current Source                         | 13 |

|   |       | 2.1.3 Short-Channel Effect                                             | 14 |

|   |       | 2.1.4 Transistor Sizing for Maximum Operation Frequency                | 15 |

|   | 2.2   | Reducing Process-dependent Variations in the Deep Sub-threshold Region | 16 |

|   |       | 2.2.1 Standard CMOS Inverter                                           | 16 |

|   |       | 2.2.2 N-type Inverter                                                  | 17 |

|   |       | 2.2.3 P-type Inverter                                                  | 19 |

|   |       | 2.2.4 Proposed CMOS Inverter                                           | 20 |

|   |       | 2.2.5 Area, Speed and Power Analysis of the Proposed CMOS Inverter     | 21 |

|   | 2.3   | Cell Library                                                           | 23 |

|   |       | 2.3.1 Inverter                                                         | 23 |

|   |       | 2.3.2 NAND-Gate                                                        | 25 |

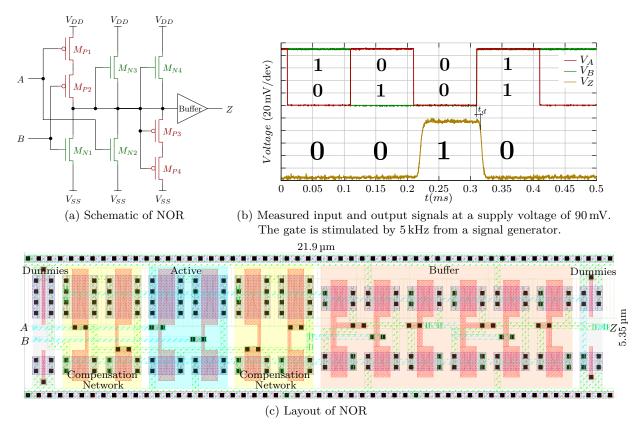

|   |       | 2.3.3 NOR-Gate                                                         | 27 |

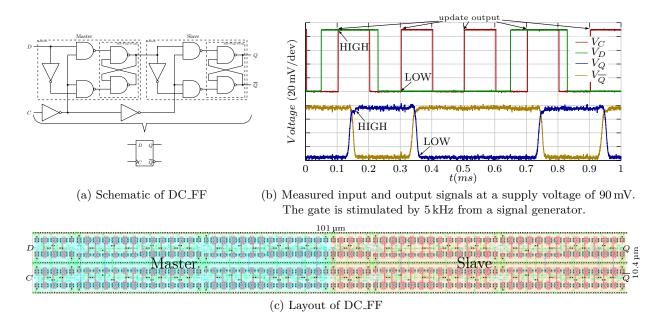

|   |       | 2.3.4 Flip-Flop                                                        | 28 |

|   | 2.4   | Sub-threshold Digital Circuits                                         | 30 |

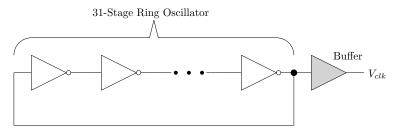

|   |       | 2.4.1 Ring Oscillator                                                  | 30 |

|   |       | 2.4.2 Full Adder                                                       | 33 |

|   |       | 2.4.3 4 bit Shift Register                                             | 35 |

|   |       | 2.4.4 3 bit Counter                                                    | 36 |

|   | 2.5   | Conclusion                                                             | 38 |

| 3 | Line  | ar Charge Pumps for Ultra-Low Voltage Inputs                           | 41 |

|   | 3.1   | Introduction to Charge Pumps                                           | 41 |

|   | 3.2   | Gate Control Strategies under Low Voltage Conditions                   | 42 |

|   | 3.3   | Impact of On-Chip Stray Capacitances                                   | 44 |

|   | 3.4  | Modeling of Self-Sustaining Linear Charge Pumps 45                                                                                                    |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 3.4.1 Voltage gain $\ldots \ldots 46$                                           |

|   |      | 3.4.2 Efficiency                                                                                                                                      |

|   |      | 3.4.3 Optimum Number of Stages                                                                                                                        |

|   | 3.5  | Conclusion                                                                                                                                            |

| 4 | Desi | gn of a Fully Integrated Thermoelectric Energy Harvester with Sub-threshold                                                                           |

|   | Star | t-up Capability 53                                                                                                                                    |

|   | 4.1  | Introduction                                                                                                                                          |

|   | 4.2  | System Architecture                                                                                                                                   |

|   | 4.3  | On-chip Capacitor                                                                                                                                     |

|   | 4.4  | Charge Pump Stage                                                                                                                                     |

|   |      | 4.4.1 Type 1                                                                                                                                          |

|   |      | 4.4.2 Type 2                                                                                                                                          |

|   | 4.5  | Clock Signal Generation                                                                                                                               |

|   |      | 4.5.1 Free-Running Start-up Clock Generator                                                                                                           |

|   |      | 4.5.2 Ramp-up/Regular Mode Clock Generator                                                                                                            |

|   | 4.6  | Oscillators                                                                                                                                           |

|   |      | 4.6.1 Ramp-up Oscillator                                                                                                                              |

|   |      | 4.6.2 Regular Mode Oscillator                                                                                                                         |

|   | 4.7  | Voltage Level Detection                                                                                                                               |

|   |      | 4.7.1 350 mV Detector                                                                                                                                 |

|   |      | 4.7.2 700 mV and 850 mV Detector $\dots \dots \dots$  |

|   | 4.8  | Charging Controller                                                                                                                                   |

|   |      | 4.8.1 Clock Stop Level Detector                                                                                                                       |

|   | 4.9  | Evaluation and Measurement                                                                                                                            |

|   |      | 4.9.1 Start-Up and Voltage Gain                                                                                                                       |

|   |      | 4.9.2 Output Current                                                                                                                                  |

|   |      | 4.9.3 Efficiency                                                                                                                                      |

|   | 4.10 | Conclusion                                                                                                                                            |

| 5 | Rese | earch Summary and Outlook 95                                                                                                                          |

| Ū | 5.1  | Summary of Achievements                                                                                                                               |

|   | 5.2  | Concepts of System Design                                                                                                                             |

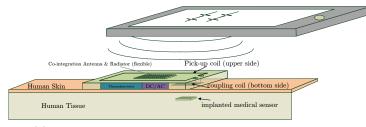

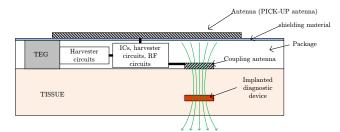

|   | 0.2  | 5.2.1 Continuous Data Logging of Conventional Implanted Passive Sensor                                                                                |

|   |      | Grains Using a Smart Booster Antenna Skin Patch                                                                                                       |

|   |      | 5.2.2 Co-integration of Antenna and Heat Sink on a Flexible Substrate 98                                                                              |

|   | 5.3  | Future Work                                                                                                                                           |

| ~ | Τ- · | Chin Levente 102                                                                                                                                      |

| A |      | Chip Layouts 103                                                                                                                                      |

|   | A.1  | Development of an Ultra-Low Voltage Digital Logic Cell Library 104<br>Design of a Fully Integrated Thermoelectric Energy Harvester with Sub threshold |

|   | A.2  | Design of a Fully Integrated Thermoelectric Energy Harvester with Sub-threshold<br>Start up Capability (Version 1)                                    |

|   | ΛQ   | Start-up Capability (Version 1)                                                                                                                       |

|   | A.3  | Start-up Capability (Version 2) Including a Low-power Temperature Sensor 108                                                                          |

|   |      | Start-up Capability (version 2) menuting a now-power reinperature sensor 108                                                                          |

Table of Contents

| Bibliography     | 109 |

|------------------|-----|

| Own Publications | 114 |

# List of Figures

| 1.1  | Internal structure of a thermoelectric generator, typically provided in a package.                     | 5  |

|------|--------------------------------------------------------------------------------------------------------|----|

| 1.2  | Equivalent circuit diagram of a thermoelectric generator                                               | 6  |

| 1.3  | Estimated power delivered to an electrically matched load by a thermoelectric                          |    |

|      | generator at different temperature differences                                                         | 8  |

| 1.4  | Typical values of the thermal resistance on the human body as published in [41,                        |    |

|      | 42]                                                                                                    | 9  |

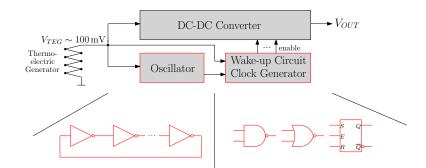

| 2.1  | Use case for sub-threshold logic reducing the start-up voltage of a DC-DC converter.                   | 12 |

| 2.2  | Schematic diagram of the output characteristic of a leakage current source                             | 14 |

| 2.3  | Dependency of the threshold voltage on the gate length of a transistor                                 | 15 |

| 2.4  | Dependency of the slew rate of the gate length of a transistor                                         | 16 |

| 2.5  | Standard CMOS inverter and its simplified equivalent circuit diagram                                   | 18 |

| 2.6  | Simulated voltage transfer curve of a standard CMOS inverter at a supply voltage                       |    |

|      | of 80 mV applying 10000 Monte Carlo runs.                                                              | 18 |

| 2.7  | N-type inverter. Using a single transistor type reduces the influence of process                       |    |

|      | dependencies due to correlation effects.                                                               | 19 |

| 2.8  | P-Type Inverter. Using a single transistor type reduces the influence of process                       |    |

|      | dependencies due to correlation effects                                                                | 19 |

| 2.9  | Proposed CMOS inverter and its simplified equivalent circuit diagram.                                  | 22 |

| 2.10 | Monte-Carlo simulation of the output characteristic of the proposed CMOS                               |    |

|      | inverter using 10000 runs.                                                                             | 22 |

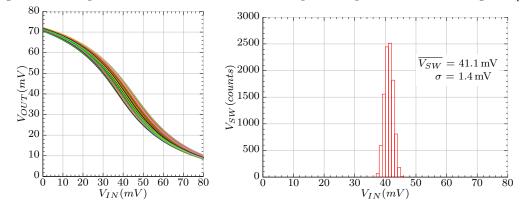

|      | Schematic, measurement and layout of the proposed inverter $INV1.$                                     | 25 |

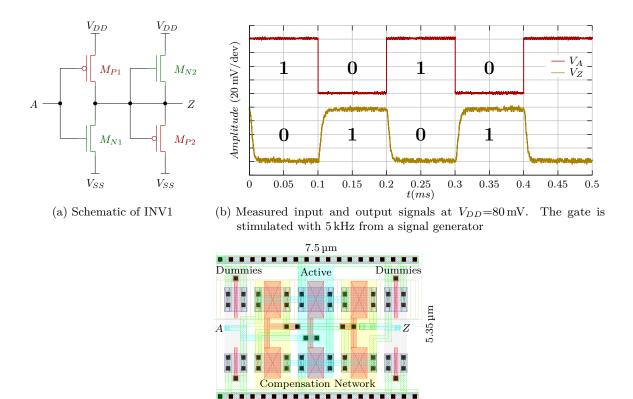

|      | Schematic, layout and proof of operation of the proposed NAND gate                                     | 27 |

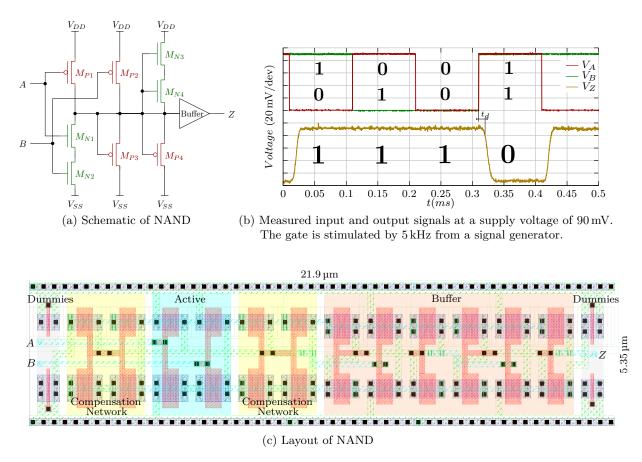

|      | Schematic, layout and proof of operation of the proposed NOR gate                                      | 29 |

|      | Schematic, layout and proof of operation of the proposed D-flip-flop                                   | 30 |

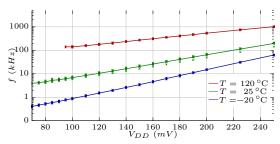

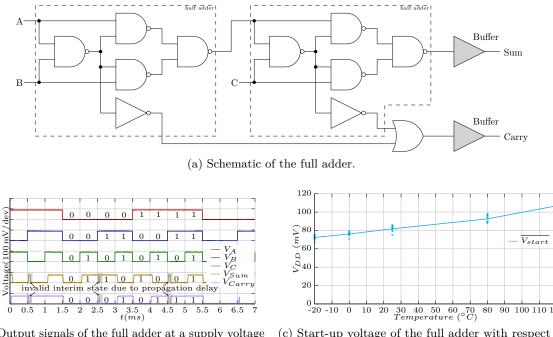

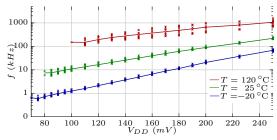

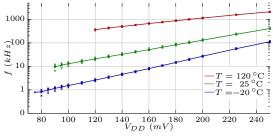

| 2.15 | Schematic and measurement data based on $N = 10$ samples of the 31-stage ring os-                      |    |

|      | cillator. A temperature range from $-20$ °C to $120$ °C is investigated at a supply                    |    |

|      | voltage range from $80 \mathrm{mV}$ to $250 \mathrm{mV}$ . The average value and variation of indi-    |    |

|      | vidual test chips is plotted in the figures                                                            | 31 |

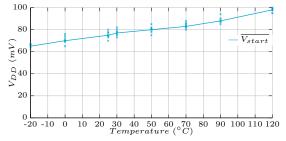

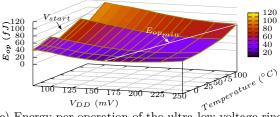

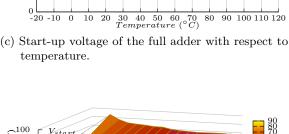

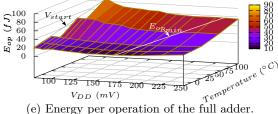

| 2.16 | Schematic and measurement data based on $N = 10$ samples of the full adder. A                          |    |

|      | temperature range of $-20$ °C to $120$ °C is investigated at a supply voltage range                    |    |

|      | of $80 \mathrm{mV}$ to $250 \mathrm{mV}$ . The average value and variation of individual test chips is |    |

|      | plotted in the figures.                                                                                | 34 |

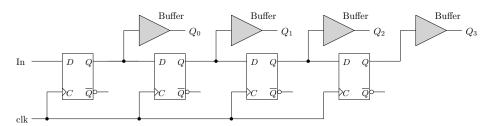

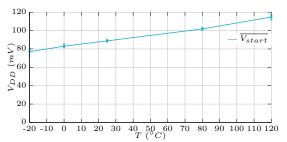

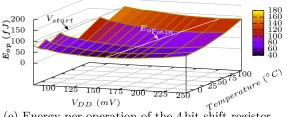

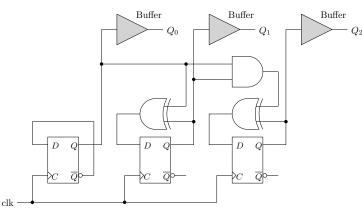

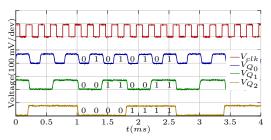

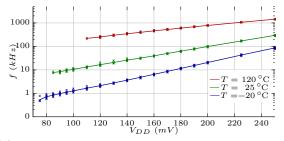

| 2.17 | Schematic and measurement data based on $N = 10$ samples of the 4 bit shift                            |    |

|      | register. A temperature range from $-20$ °C to $120$ °C is investigated at a sup-                      |    |

|      | ply voltage range from $80 \mathrm{mV}$ to $250 \mathrm{mV}$ . The average value and variation of      |    |

|      | individual test chips is plotted in the figures.                                                       | 35 |

## List of Figures

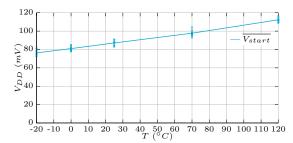

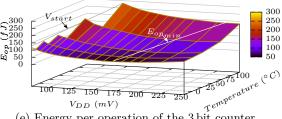

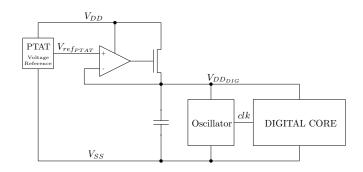

|              | Power management unit of an ultra-low voltage digital core using a self-adapting                                                                     | 37<br>40 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

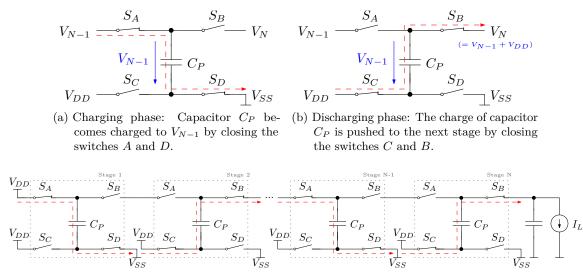

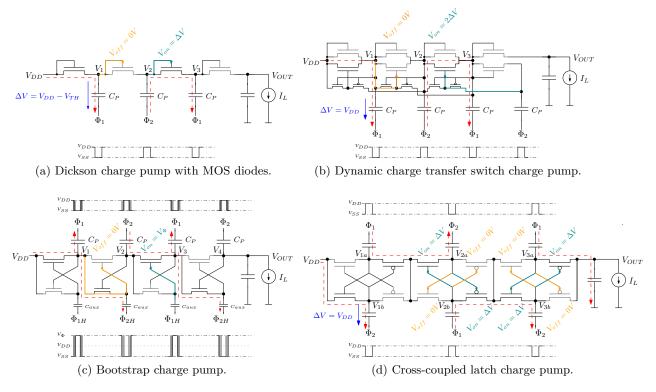

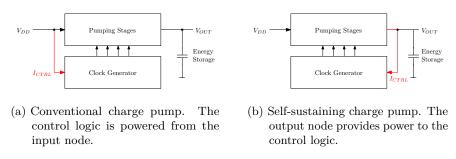

| 3.1          | Schematic of an N-stage linear charge pump using active switches to control the                                                                      |          |

| $3.2 \\ 3.3$ | Conventional charge pump control strategy for low voltage operation Charge transfer phases of a linear charge pump including the effect of parasitic | 42<br>43 |

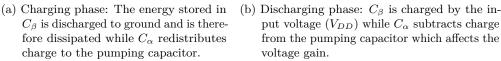

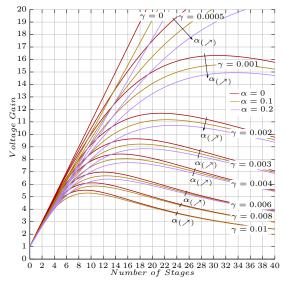

| 3.4          | *                                                                                                                                                    | 45<br>46 |

| 3.5          | Calculated voltage gain versus the number of stages considering the impact of                                                                        |          |

| 3.6          | Calculated efficiency versus the number of stages considering the impact of                                                                          | 47<br>51 |

| 4.1          | Circuit topologies of thermoelectric energy harvesting systems considering dif-                                                                      | 01       |

| 1.1          |                                                                                                                                                      | 54       |

| 4.2          | * 0                                                                                                                                                  | 55       |

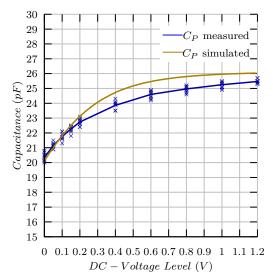

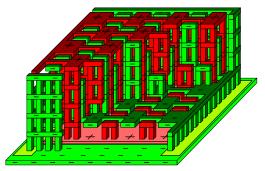

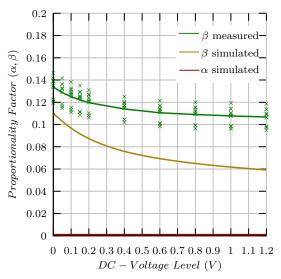

| 4.3          |                                                                                                                                                      | 58       |

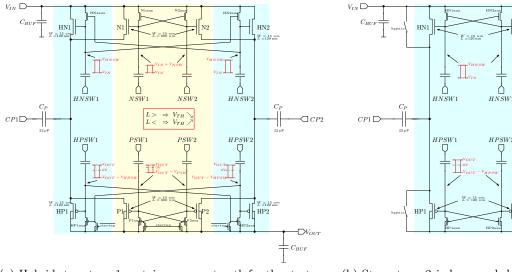

| 4.4          | Cross-coupled latch charge pump stage using capacitively coupled control signals.                                                                    | 60       |

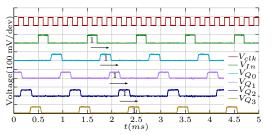

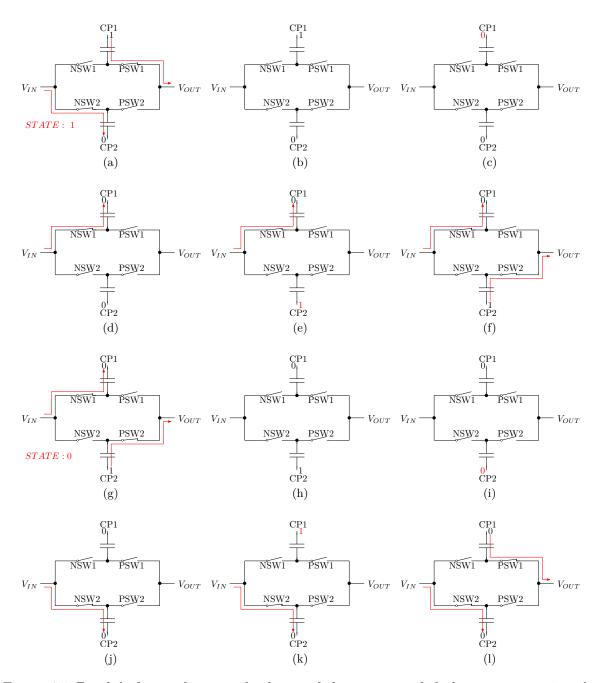

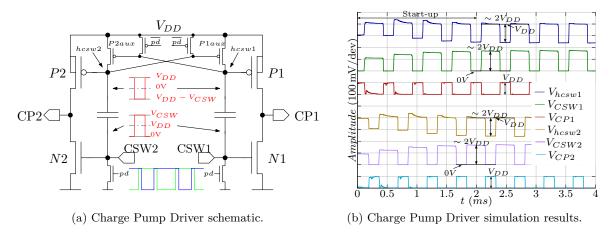

| 4.5          | Break-before-make control scheme of the cross-coupled charge pump using the signals generated by the LV clock generator in Figure 4.7.               | 63       |

| 4.6          | Free-running low voltage clock generator using cells from the ultra-low volt-<br>age digital cell library.                                           | 64       |

| 4.7          | Simulated transient behavior of the low voltage clock generator to control the                                                                       | 64       |

| 4.8          | Clock doubler schematic and simulation result at a supply voltage of 100 mV to                                                                       | 66       |

| 4.9          |                                                                                                                                                      | 66       |

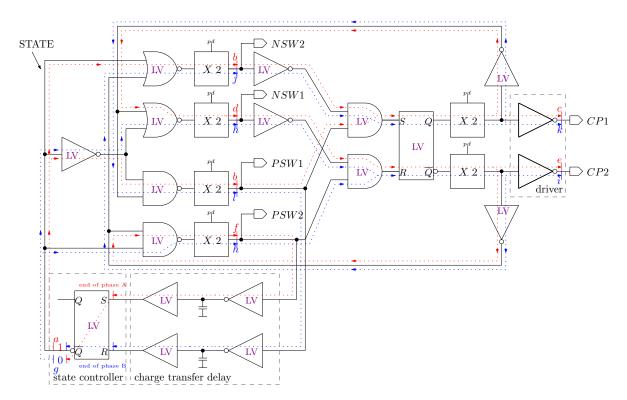

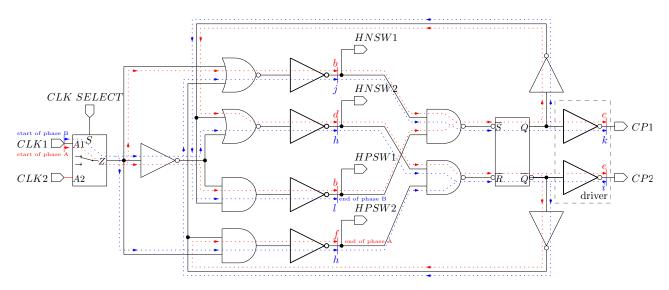

|              | Schematic and signal path through the ramp-up/regular mode clock generator                                                                           |          |

|              | based on standard logic cells.                                                                                                                       | 67       |

| 4.11         | Simulated transient behavior of the ramp_up/regular mode clock generator at a                                                                        |          |

| 1 1 0        |                                                                                                                                                      | 68       |

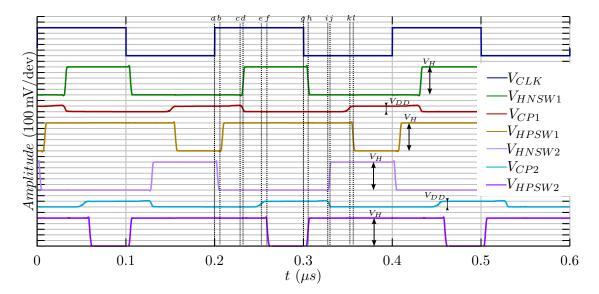

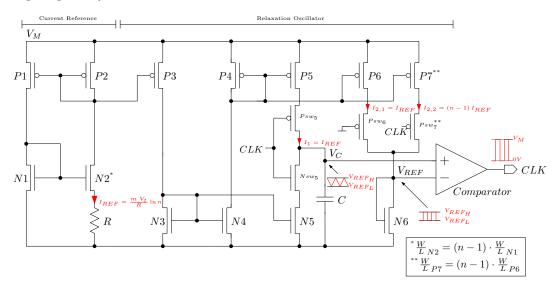

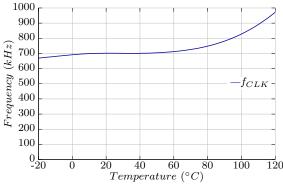

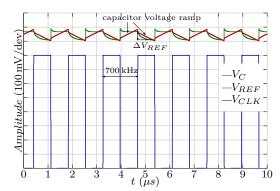

| 4.12         | Ramp-up oscillator consisting of a local voltage reference, a voltage regulator                                                                      | 71       |

| 1 10         | 0                                                                                                                                                    | 71       |

| 4.13         | Simulated behavior of the voltage regulator and the ramp-up oscillator operated                                                                      | 70       |

| 111          | in the deep sub-threshold region                                                                                                                     | 72       |

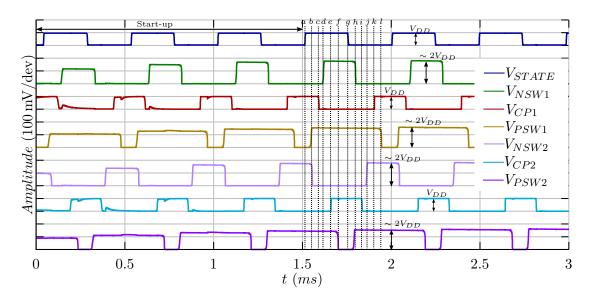

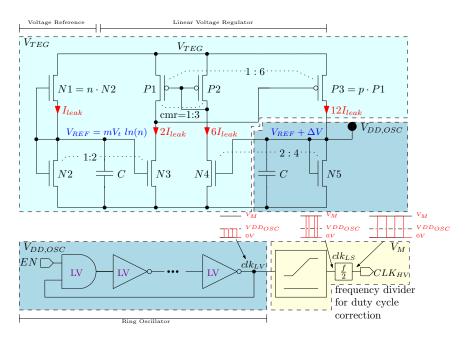

| 4.14         | -                                                                                                                                                    | 73       |

| 115          | during the ramp-up procedure                                                                                                                         | 13       |

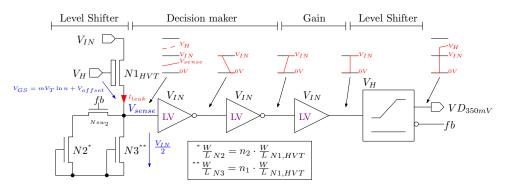

| 4.10         |                                                                                                                                                      | 74       |

| 4.16         |                                                                                                                                                      | 74       |

|            | Schematic of the 350 mV detector                                                                                                                                                                                                                                                                                                           | 76       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

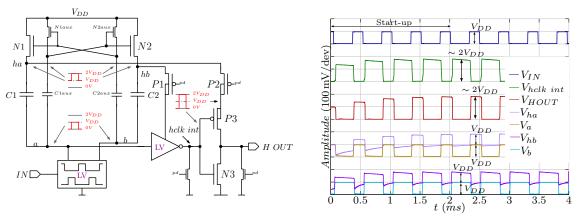

|            | detector                                                                                                                                                                                                                                                                                                                                   | 76<br>80 |

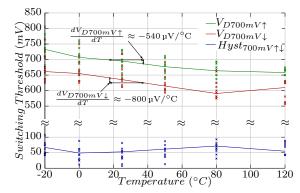

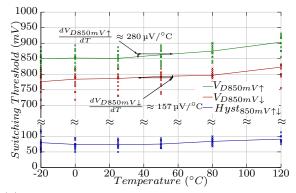

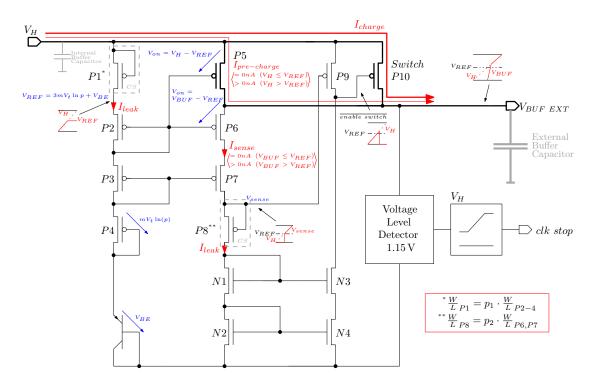

| 4.20       | and 850 mV level detector                                                                                                                                                                                                                                                                                                                  | 81       |

|            | Schematic of the charge controller.                                                                                                                                                                                                                                                                                                        | 83       |

| 4.22       | Simulation results of the charging controller. Process variations and temperature behavior are considered in addition to the transient behavior.                                                                                                                                                                                           | 84       |

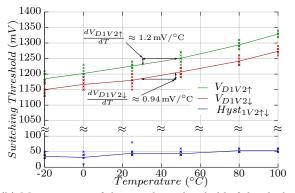

| 4.23       | Measurement of the on-/off switching threshold for 10 test samples of the clock                                                                                                                                                                                                                                                            | 04       |

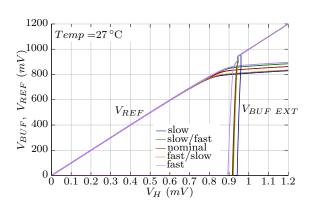

|            | stop level detector.                                                                                                                                                                                                                                                                                                                       | 85       |

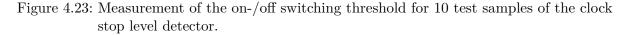

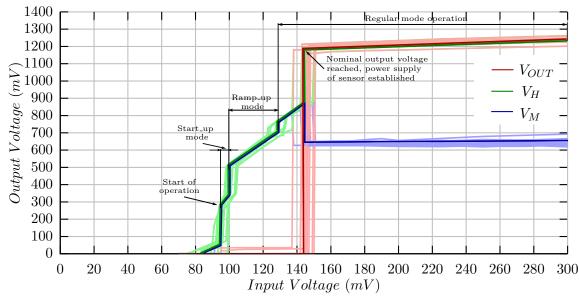

| 4.24       | Measurement of the output voltage in dependency of the input voltage based on                                                                                                                                                                                                                                                              | 07       |

| 4.25       | 10 test samples                                                                                                                                                                                                                                                                                                                            | 87       |

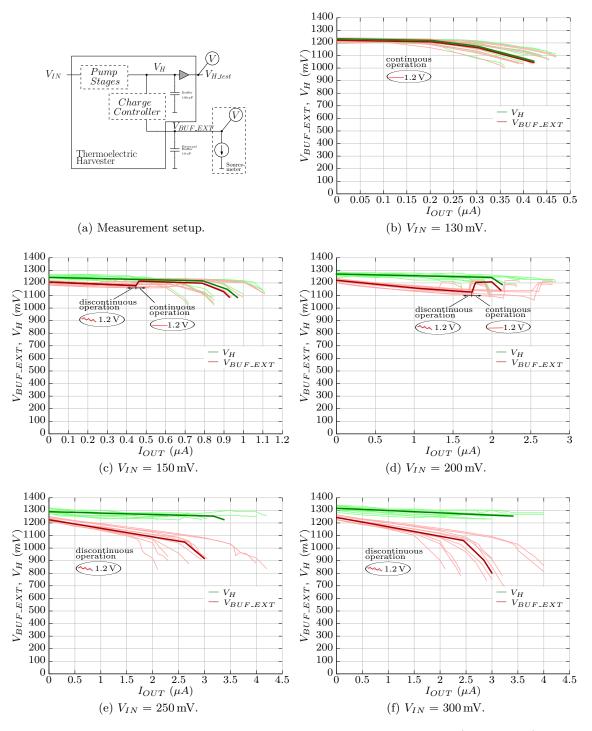

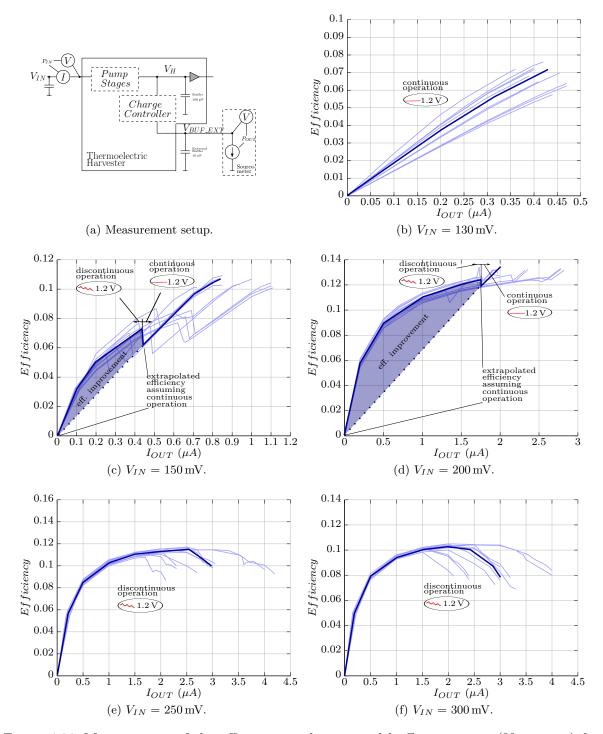

|            | the internal high voltage domain $(V_H)$ for different input voltages in dependency<br>of the output current. The characteristics are based on 10 test samples<br>Measurement of the efficiency at the external buffer capacitor $(V_{BUF\_EXT})$ for<br>different input voltages in dependency of the output current. The characteristics | 89       |

|            | are based on 10 test samples                                                                                                                                                                                                                                                                                                               | 92       |

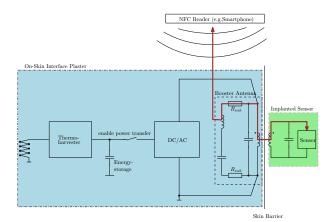

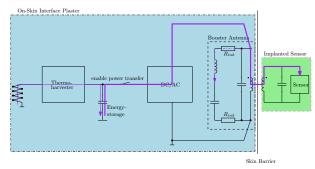

| 5.1        | Continuous Data Logging of conventional implanted passive sensor grains using<br>a smart booster antenna skin patch. System architecture and description of                                                                                                                                                                                |          |

|            | operation                                                                                                                                                                                                                                                                                                                                  | 99       |

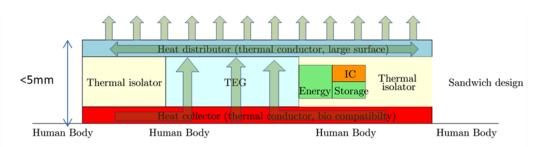

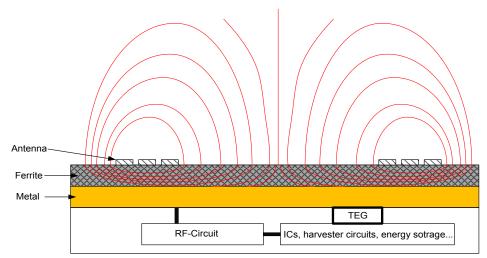

| 5.2        | Co-integration of antenna and heat sink on a flexible substrate using a three-layer architecture.                                                                                                                                                                                                                                          | 101      |

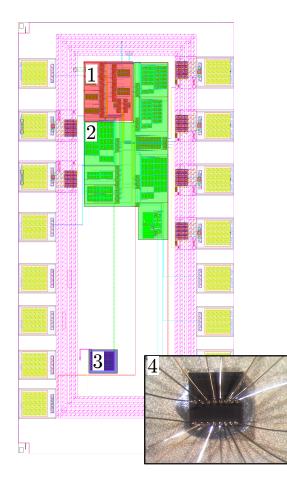

| A.1        | Test Chip ultra-low voltage digital logic cells.                                                                                                                                                                                                                                                                                           | 104      |

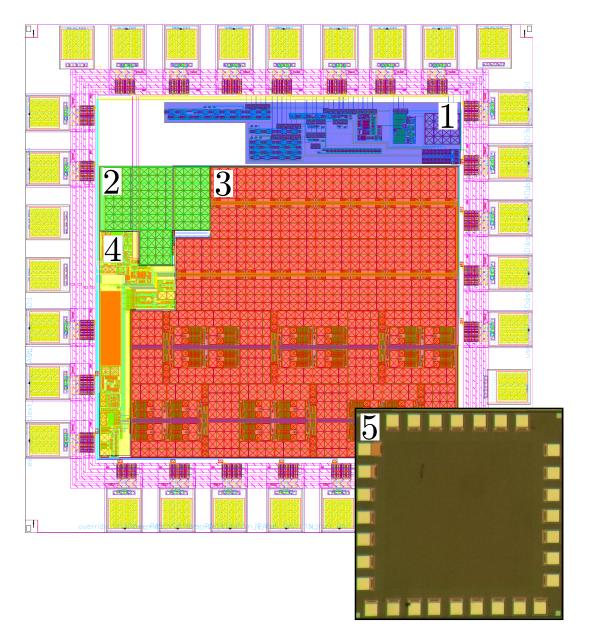

| A.2<br>A.3 | Version 1 of the thermoelectric energy harvesting test chip                                                                                                                                                                                                                                                                                | 106      |

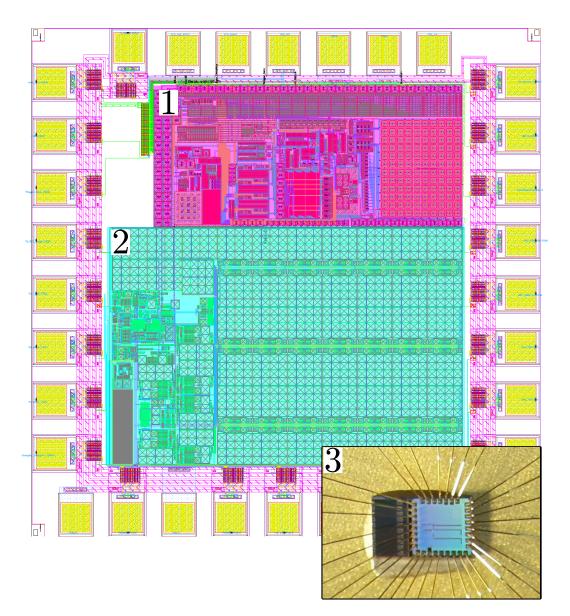

|            | interface and a low power temperature sensor                                                                                                                                                                                                                                                                                               | 108      |

# List of Tables

| 1.1 | Comparison of different harvesting sources in Body Area Networks                     | 2  |

|-----|--------------------------------------------------------------------------------------|----|

| 1.2 | Characteristic data of the MPG-D751 thermoelectric generator $\ldots \ldots \ldots$  | 5  |

| 2.1 | Geometry of the inverters of the ultra-low voltage digital cell library              | 24 |

| 2.2 | Geometry of the NAND and NOR cell data base.                                         | 26 |

| 2.3 | Overview of the characteristics of the ultra-low voltage digital circuits            | 39 |

| 2.4 | Performance comparison of ultra-low voltage digital logic cells                      | 40 |

| 4.1 | Specification of the thermoelectric energy harvester.                                | 55 |

| 4.2 | Characteristics of the three operation modes of the thermoelectric energy harvester. | 57 |

| 4.3 | Simulated equivalent load capacitance of the oscillator, clock generator and         |    |

|     | pump stage switches to estimate the control effort factor. The parasitic extracted   |    |

|     | circuit is used.                                                                     | 69 |

| 4.4 | Performance comparison of transformer based and inductive thermoelectric             |    |

|     | energy harvesters.                                                                   | 94 |

| 4.5 | Performance comparison of capacitive thermoelectric energy harvesters                | 94 |

|     |                                                                                      |    |

List of Tables

## Chapter 1

## Introduction

### 1.1 Motivation

The Internet-of-Things and Machine-to-Machine communication are terms that are frequently used nowadays when talking about future developments in home automation and human assistance systems. The idea is to equip physical objects we use in our daily life with embedded computing systems to achieve a greater value. Wireless Sensor Networks are part of this technology and consist of distributed sensor nodes that monitor physical or environmental conditions. In medical applications, Wireless Senor Networks are typically called Body Area Networks and enable the continuous monitoring of vital parameters of patients with chronic diseases, even in domestic surroundings. These nodes typically consist of a local power source, a sensor and a processing unit as well as an RF-interface. A frequently addressed issue in Wireless Sensor Networks is the power supply which is typically realized by using finite energy sources which leads to a high maintenance effort. A solution to this problem is energy harvesting or scavenging which is the approach of deriving electric power locally from different environmental sources (e.g. solar power, thermal energy, electromagnetic energy, kinetic energy, ...) and enables battery-less operation. A recently published summary of characteristics and research achievements can be found in Proceedings of IEEE (Issue 11, Nov. 2014). Energy harvesting systems suffer from a generic approach and finding a suitable source requires careful investigation into the corresponding application scenario. A detailed investigation of feasible harvesting sources found on the human body is carried out in [26] and a brief summary of the characteristic is given in Table 1.1. Photovoltaics can rarely be used, as 90% of the skin is typically covered by clothing. Clothes are no barrier for RF-signals but their energy density rapidly decreases with increasing distance from the transmitter. So, to provide sufficient power to an on-skin sensor a powerful RF source needs to be installed not too far away. Kinetic harvesters represent an unpredictable source with irregular power output which relies on people's mobility. The only stable energy source of a human being is the body temperature which is typically about  $10 \,^{\circ}\text{C}$ higher than the ambient air. It is therefore the aim of this thesis to develop a fully integrated thermoelectric energy harvesting interface with self-starting capabilities. The thesis presents the full scope of the development, starting from the physical background of the harvesting principle right through to the complete system integration on silicon.

|                   | Characteristics                                                                                                                                                                               | Suitability in Body Area Networks                                                                                                                                   |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Optical<br>Energy | <ul> <li>+ high efficiency outside</li> <li>+ good scalability</li> <li>+ flexible organic cells</li> <li>o moderate efficiency inside</li> <li>- no power generation overnight</li> </ul>    | + usable in "intelligent clothes"<br>o limited applicability in on-skin sensors<br>$(\approx 90\%$ of the skin is typically covered)<br>- not for implanted devices |

| RF<br>Energy      | <ul> <li>+ simple and cheap realization</li> <li>- power output 100-1000 times<br/>lower than alternative sources</li> <li>- bad reputation of "electric smog"</li> </ul>                     | + wireless power transmission through<br>skin barrier to power implants                                                                                             |

| Kinetic<br>Energy | <ul> <li>+ simple design</li> <li>+ low costs of macroscopic devices</li> <li>o unsteady source</li> <li>- bad scalability<br/>(MEMS technology necessary)</li> </ul>                         | + implantable                                                                                                                                                       |

| Thermal<br>Energy | <ul> <li>+ body heat is a constant source</li> <li>o high costs of thermal electric</li> <li>generators</li> <li>o power conversion challenging</li> <li>due to low output voltage</li> </ul> | + usable for on-skin sensors<br>- unusable for implanted sensors                                                                                                    |

Table 1.1: Comparison of different harvesting sources in Body Area Networks.

## 1.2 Organization of the Thesis

Chapter 1 deals with the basics regarding thermoelectric energy harvesting in Body Area Networks. The characteristics of a thermoelectric generator are discussed through investigation of the thermal and electrical properties of the device. As the power conversion efficiency highly depends on the thermal resistances of the entire system in an application scenario a literature study is performed to provide the corresponding data for the human body. Finally a simple model combining the thermal and electrical is developed which allows estimation of the power conversion efficiency in dependency on the parasitic thermal resistances of the complete harvesting system.

The development of digital logic gates so that they are functional in the deep sub-threshold region is presented in Chapter 2. It starts with investigations into the behavior of MOS transistors in this operation region. Then, a leakage compensation technique is introduced which allows a significant reduction in the minimum supply voltage of CMOS gates without requiring special process options or post-fabrication steps. The principle is used to develop an ultra-low voltage digital cell library which contains inverter, NAND- and NOR-gates as well as flip-flops. The functionality of interconnected gates is demonstrated with measurements of basic digital circuits over a wide temperature range.

In Chapter 3 an analytical model of fully integrated charge pumps for ultra-low voltage inputs is derived. It considers the impact of stray capacitances as well as the control effort which is caused by the self-sustaining operation. Expressions for voltage gain, efficiency and optimum number of stages are derived which allows optimization during the design flow.

Chapter 4 combines the achievements of the previous chapters by presenting the design of a fully integrated thermoelectric energy harvesting system with self-starting capabilities. The ultra-low voltage digital logic cells enable an autonomous start in the deep sub-threshold region. By using the analytical model of chapter 3 the entire system is implemented in a chip area and power efficient way which is proven by measurements of multiple samples.

Finally, Chapter 5 summarizes the achievements of the thesis and provides a conceptual system design for a smart booster antenna skin patch based on thermoelectric energy harvesting for continuous data logging of conventional implanted passive sensor grains.

### 1.3 Thermoelectric Energy Harvesting

The thermoelectric effect, or Seebeck effect was first discovered by Thomas Johann Seebeck in 1821 and describes the direct conversion of a temperature gradient induced heat flow into electric power. Interconnecting two dissimilar materials and forcing their interconnects to be different temperatures results in a diffusion current from the hot to the cold side (and vice versa) in order to reach energy equilibrium. Due to the higher speed of hot charge carriers compared to cold ones an electric field and therefore a measurable voltage is developed. Its value depends on material properties expressed by the Seebeck coefficient ( $\alpha^*$ ) and decreases with charge carrier concentration. In metals it is typically less than  $30 \,\mu\text{V/K}$  and in semiconductors a few  $100 \,\mu\text{V/K}$  [10]. To compare different materials a figure of merit (Z) was employed in 1949 by A.F. Ioffe [70], taking into account electrical ( $\sigma$ ) and thermal ( $\lambda$ ) conductivity of thermocouples (1.3.1). Consequently a well performing thermoelement provides a low thermal conductivity to increase the temperature gradient across the device, a high electrical conductance to reduce the Joule heating losses and a high Seebeck coefficient.

$$Z = \alpha^2 \frac{\sigma}{\lambda} \tag{1.3.1}$$

Isolators typically provide the lowest thermal conductivity combined with a very high electrical resistivity, making them inapplicable in thermocouples. Metals on the other hand are excellent electrical and heat conductors, which again leads to a low Z. A trade-off is semiconductor material which provides a low thermal and in case of proper doping a relatively high electrical conductivity in addition to an attractive  $\alpha$ . Therefore the latter is widely used in thermoelectric power generation. Since all parameters of Z are in fact temperature dependent, different operation temperature regions require certain materials. At room temperature bismuth telluride

<sup>\*</sup>  $\alpha$  is defined by the differential Seebeck coefficient of two materials in a thermocouple

#### Chapter 1 Introduction

$(Bi_2Te_3)$  is the state-of-the-art thermoelectric material outside laboratories providing a Z of  $0.003 \,\mathrm{K}^{-1}$  [61]. In order to improve Z scientists are focusing on the development of new materials and low-dimensional structures (e.g. nanowires). It is expected by J.H. Goldsmid that Z will be improved by a factor of 4 in the near future and up to a factor of 20 in the long term [18].

An important aspect in thermoelectric power generation is the optimum conversion efficiency  $(\eta_{max})$  of a thermoelectric device which is generally determined by the electrical power output at a certain thermal input. It can be shown that for small gradients, where temperature independency can be assumed,  $\eta_{max}$  is given by (1.3.2) [64]. The first expression in (1.3.2) is the Carnot factor  $(\eta_c)$ , well known from thermodynamics to describe the fundamental limit of ideal heat engines. It depends on the difference in temperature of the hot side  $(T_H)$  and the cold side  $(T_C)$  divided by  $T_H$ . The second expression is called reduced efficiency  $(\eta_r)$  and considers the device properties multiplied by the average temperature  $\overline{T} = (T_H - T_C)/2$ .

$$\eta_{max} = \eta_c \cdot \eta_r = \frac{T_H - T_C}{T_H} \cdot \frac{\sqrt{1 + Z\overline{T}} - 1}{\sqrt{1 + Z\overline{T}} + \frac{T_C}{T_H}}$$

(1.3.2)

In order to get a rough estimation of the achievable efficiency using on-body applications, values are inserted in the above formula. Assuming a body temperature of  $T_H=310$  K in an ambient environment of  $T_C=300$  K results in a Carnot factor of about 0.032. Taking into account Z of Bi<sub>2</sub>Te<sub>3</sub> further reduces this result to 0.0056. In other words, just about 0.56 % of the delivered thermal power is converted to electrical power. It has to be noted that this calculation neglects additional parasitic parameters e.g. thermal resistances of the heat source and sink.

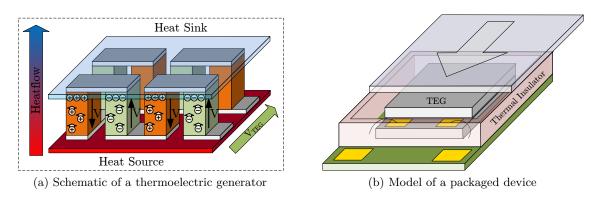

#### 1.3.1 System Architecture of a Thermoelectric Generator

A simplified schematic of a thermoelectric generator (TEG) is shown in Figure 1.1a. The structure is similar to a Peltier heat pump, used in small refrigerators. It is built of an array of thermocouples arranged vertically in between a non conducting heat absorber and rejection ceramic plate. As a result the elements of the device are connected thermally in parallel and electrically in series. In semiconductor thermoelectric materials the majority carriers drift to the cold side. Therefore doping influences the sign of the Seebeck coefficient. By alternating n- and p-type elements the voltage contribution of all pillars add up while the entire temperature gradient is applied to each element. As shown in (1.3.3) the open circuit output voltage ( $V_{TEG_{open}}$ ) of a thermoelectric generator depends on the number of pillars (N),  $\alpha$  and the temperature gradient across the device ( $\Delta T_{TEG} = T_H - T_C$ ).

$$V_{TEG_{open}} = N\alpha\Delta T_{TEG} \tag{1.3.3}$$

In principle any voltage per kelvin ratio is feasible by choosing a proper N, but each thermocouple adds electrical resistance while providing an additional heat path which effects the overall device performance. This trade-off will be discussed later in this thesis.

Figure 1.1: Internal structure of a thermoelectric generator, typically provided in a package.

|                                               | MPG-D751                                 |

|-----------------------------------------------|------------------------------------------|

| Dimension                                     | $4.248\mathrm{mm}\times3.364\mathrm{mm}$ |

| Thickness                                     | $1.090\mathrm{mm}$                       |

| Number of Pillars                             | 540                                      |

| Thermal Resistance @ $85^{\circ}C$            | $12.5\mathrm{K/W}$                       |

| Electrical Resistance @ $23 ^{\circ}\text{C}$ | $300\Omega$                              |

| Output Voltage                                | $140\mathrm{mV/K}$                       |

Table 1.2: Characteristic data of the MPG-D751 thermoelectric generator [49].

Manufacturers of commercially available thermoelectric generators are using hundreds of thermocouples in order to reach a reasonable output voltage. Additionally a package is required to protect the generators from mechanical stress. It is typically the same sandwich architecture of two heat conducting plates, separated by thermally isolating sidewalls (Figure 1.1b). In this thesis a commercially available thin film thermoelectric generator from Micropelt GmbH is used. The device MPG-D751 is originally designed for wireless sensor nodes in industrial applications and provides a relatively high output voltage per Kelvin ratio. Due to its small physical size it is a suitable candidate to power on-skin sensor nodes of Body Area Networks. Table 1.2 shows the characteristics taken from the data sheet [49].

#### 1.3.2 Thermoelectric Equivalent Circuit Diagram and Power Optimization

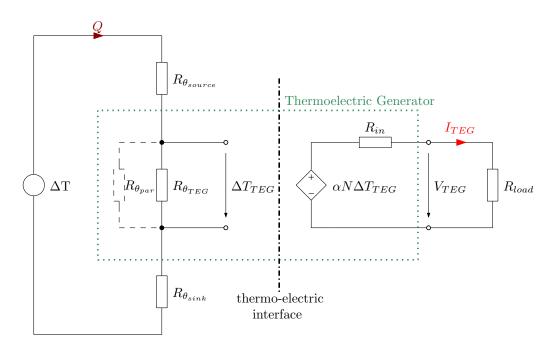

A thermoelectric generator converts thermal energy into electrical power. Therefore its model has to consider the thermal and electrical properties in order to optimize the device in both directions. V. Leonov did a lot of research in this area by investigating thermoelectric generators in Body Area Networks [38–40, 43]. He stated the importance of matching the thermal resistance of a device to the environment by design. Derived from his work an equivalent circuit diagram, respecting the thermal and electrical relationship, is given in Figure 1.2.

The device can be represented by a temperature dependent voltage source having an internal

Figure 1.2: Equivalent circuit diagram of a thermoelectric generator.

series resistance  $(R_{in})$  which increases with the number of thermocouples. Applying a load  $(R_{load})$  results in a current  $(I_{TEG})$  and an output voltage, defined by the ratio of the resistive divider (1.3.4).

$$V_{TEG} = V_{TEG_{open}} \frac{R_{load}}{R_{load} + R_{in}} \tag{1.3.4}$$

In the thermal domain, a difference in temperature  $(\Delta T)$  is generated by a heat source (e.g. human metabolism) and initializes a heat transfer Q to the sink (e.g. ambient air). Similarly to Ohm's law the height of Q is defined by the ratio of the gradient and the thermal resistance of the heat path. In this simplified model the latter is represented by three thermal resistors. While  $R_{\theta_{source}}$  includes the body-to-TEG resistance (human tissue, skin, ...),  $R_{\theta_{sink}}$  is mainly given by the junction resistance to the ambient air. The third one  $(R_{\theta_{TEG}})$  is introduced by the device itself and decreases with the number of thermocouples.  $R_{\theta_{par}}$  represents the parasitic heat path from the bottom to the top plate defined by the thermal conductance of the air and the thermally isolating sidewalls of the package. In macro-scale devices  $R_{\theta_{par}}$  is typically much higher compared to  $R_{\theta_{TEG}}$ . In Figure 1.2 it is therefore just added for the sake of completeness and will be neglected in further investigations.

As it can be seen from the equivalent circuit diagram in Figure 1.2, a difference in temperature alone is not sufficient to generate electric power. It requires a heat flow from the source to the sink causing a temperature gradient across the device (1.3.5). Due to the thermal resistances of source and sink the effective temperature gradient applied to the thermoelectric generator is less than provided by the heat source. This is especially an issue in Body Area Networks where

$R_{\theta_{sink}}$  and  $R_{\theta_{source}}$  are typically much larger than  $R_{\theta_{TEG}}$ . As a result a low output voltage must be addressed in such an application.

$$\Delta T_{TEG} = Q R_{\theta_{TEG}} = \frac{\Delta T}{R_{\theta_{TEG}} + R_{\theta_{sink}} + R_{\theta_{source}}} R_{\theta_{TEG}}$$

(1.3.5)

To calculate the power generated by a thermoelectric generator, (1.3.5) is substituted into (1.3.3) and the latter into (1.3.4) in order to get the output voltage under load conditions. Using  $V_{TEG}$  the delivered power is given by (1.3.6).

$$P_{load} = \frac{V_{TEG}^2}{R_{load}} = N^2 \alpha^2 \Delta T^2 \frac{R_{\theta_{TEG}}^2}{(R_{\theta_{TEG}} + R_{\theta_{sink}} + R_{\theta_{source}})^2} \frac{R_{load}}{(R_{in} + R_{load})^2}$$

(1.3.6)

Due to the fact that in (1.3.6) the parameters N,  $\alpha$ ,  $R_{\theta_{TEG}}$  and  $R_{in}$  are device specific, there are only a few opportunities left for optimization. According to the maximum power theorem, one way is to align the load to the inner resistance of the device [5]. Another option is to minimize the parasitic thermal resistances  $R_{\theta_{source}}$  and  $R_{\theta_{sink}}$ . In industrial applications this is achieved by mounting the thermoelectric generator close to the heat source and applying a large radiator. This approach is only suitable to a limited extent in Body Area Networks as the thermal resistance of the source is defined by the human body and a large radiator is inapplicable due to size restrictions.

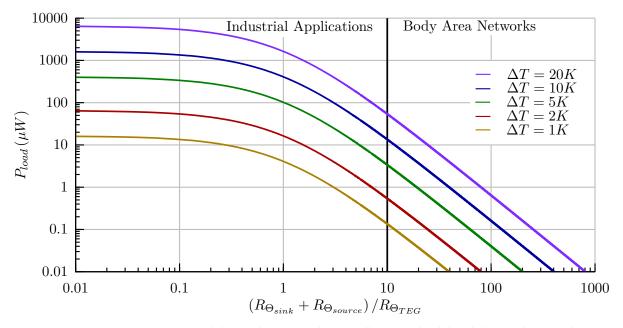

To demonstrate the effect of parasitic thermal resistances, the power delivered by a single MPG-D751 to a matched load is shown in Figure 1.3. For calculation purposes, device specific parameters are taken from Table 1.2 and inserted in equation (1.3.6).  $P_{load}$  is plotted as a function of the normalized thermal resistance of the ambiance with respect to  $R_{\theta_{TEG}}$ . In the figure each curve represents another difference in temperature seen from the source to the sink. Since in industrial applications the parasitic thermal resistances are typically low, an output power in the milliwatt range is feasible. Unlike Body Area Networks where due to the high ratio less than 100 µW can be expected. Considering the thermal path during the design phase of a sensor node is therefore of great importance.

Figure 1.3: Estimated power delivered to an electrically matched load by a thermoelectric generator at different temperature differences.

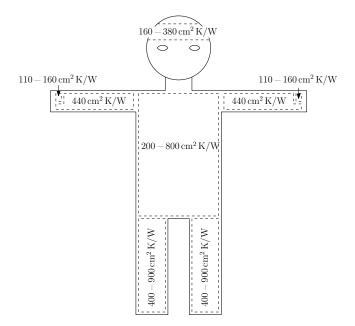

### 1.4 Thermal Resistance of the Human Body

The human body continuously generates heat from metabolic processes and mainly dissipates it by convection and radiation through the skin to the environment. In order to keep the core temperature at about 310 K, blood circulation distributes excess thermal energy to peripheral regions using a network of blood vessels. Temperature regulation is achieved by changing the flow rate through vascular constriction and dilatation. As a result the thermal resistance of the human body is variable and depends on body mass, environmental conditions and the activity level. Location plays another important role. Muscles and body fat insulate the blood vessels from the ambient temperature and increase the thermal resistance in certain regions. This was confirmed by measurements performed in [41, 42] where the typical thermal resistance is given at different places on the human body. Arms, legs and the lower trunk are highly resistive while, for example, the forehead, inner wrist and chest provide a value five to ten times lower. Therefore those locations are more suitable for energy harvesting. The results are summarized in Figure 1.4.

From medical literature the basal metabolic rate is known to be about  $2.9 \,\mathrm{kW}$  h per day for a sitting human of 75 kg. Assuming a body surface of  $2 \,\mathrm{m}^2$  results therefore in a mean heatflow of  $6 \,\mathrm{mW/cm^2}$ . In order to concentrate the heatflow in a certain area, a lower resistive path to the environment can be established by applying a radiator. As shown in [38], the body resistance significantly reduces with the heatflow. This might be caused by a compensation activity of the body. Directing thermal energy away from the body reduces the temperature locally. To counteract, the diameter of the blood vessels enlarges in this area to provide a

#### 1.4 Thermal Resistance of the Human Body

Figure 1.4: Typical values of the thermal resistance on the human body as published in [41, 42].

higher amount of energy. Therefore applying a radiator not just influences the surface to the ambient temperature, but causes some kind of positive feedback which helps to increase the power output of a thermoelectric generator. However increasing the heatflow beyond a certain level results in an uncomfortable sensation of coldness. According to [38], it should therefore be limited to  $15-25 \,\mathrm{mW/cm^2}$ .

## Chapter 2

## Development of an Ultra-Low Voltage Digital Logic Cell Library

The following chapter is mainly taken from [27], [28], [29] and [30] (own publications). ■

### 2.1 Minimum Supply Voltage of Digital Logic Cells

The complexity of electronic circuits is steadily increasing and with it the number of transistors in electronic circuits is also constantly increasing too. Efficiency enhancement is therefore of great importance in order to minimize power consumption, especially in portable systems with limited power budget. The conventional method of reducing the switching losses by lowering the supply voltage affects the drive strength and therefore the propagation delay. As a consequence the time required to finish an operation is extended. Leakage energy is proportional to the time required for a certain operation. Therefore the losses due to leakage increase with a lower supply voltage. These two effects counter each other and therefore an optimum supply voltage level can be found. Several publications discuss this minimum energy point for optimized digital circuits design [63, 71, 73]. Dependent on the process technology, it is in general close to the threshold voltage. In some applications, such as thermoelectric energy harvesting, the power source provides even lower voltages in the order of 100 mV. Therefore voltage conversion has to be preceded when using conventional logic gates. At least for start-up, some components of the DC/DC converter still need to be functional in the deep sub-threshold region for wake-up and generation of a clock signal (Figure 2.1).

When compared to strong-inversion operation the electrical properties of transistor devices significantly change below the threshold voltage, resulting in a couple of challenges that have to be considered [16].

• **Speed:** The propagation delay of logic cells is determined by the slope of the switching edge which is a function of the output current divided by the load capacitance. The latter includes the input capacitance of the following stage and parasitic capacitances of connection wires. The former shrinks exponentially with the supply voltage, used to control the gate. This leads to an extended delay which limits the maximum operation frequency to the kHz region in deep sub-threshold operation.

- Figure 2.1: Use case for sub-threshold logic reducing the start-up voltage of a DC-DC converter. The minimum supply of the clock generator defines the start-up voltage of the circuit [30].

- Gain: Lowering the supply voltage to below 3-4 times the thermal voltage ( $V_t = kT/q$ ) causes degradation of the on/off current ratio due to  $V_{DS}$  roll-off. As a result the gain and the voltage swing is greatly reduced.

- **Temperature:** The behavior of a MOS transistor on a rising temperature is affected by two counteracting properties, a decreasing threshold voltage and mobility degradation. While the former causes a higher current, the latter reduces it. The overall behavior is therefore determined by the dominating effect which depends on the operation region. In strong-inversion the mobility degradation predominates and reduces the speed of a circuit. In weak-inversion the exponential dependency on the threshold voltage overtakes and allows higher operation frequencies.

- **Process:** The exponentially decreasing on/off current ratio of transistors in push-pull gates, affected by process variations, leads to a serious reliability issue with sub-threshold circuits [9]. Considering an inverter in a worst case scenario of a strong PMOS and a weak NMOS (or vice versa), the leakage current of the strong device may remain higher than the current capability of the weak one. As a result the weak device is not able to change the state of the output node which causes a logic failure. Additionally, layout techniques for good matching have to be applied to ultra-low voltage logic gates, as the threshold voltage is influenced by well proximity effects and Shallow Trench Isolation (STI) stress [13].

Several techniques have been introduced to lower the minimum voltage level of digital cells. By proper transistor sizing and circuit topology optimization a 180 mV FFT-processor was realized in [72], using standard CMOS transistors. Another approach is to shift the sub-threshold region to lower values by applying forward body biasing to the devices. Different topologies of dynamic or static body biasing were introduced in [65] and [52]. Those techniques typically require triple-well technologies and suffer from additional circuitry effort, due to biasing generation or limitation circuits to prevent the forward-biased PN junction diode from conducting. Nevertheless a successful demonstration of an 8 bit microprocessor operating at

160 mV was shown in [20]. Post-fabrication process steps, such as charge injection into the gate oxide, significantly reduce the threshold voltage of transistors. Therefore a minimum  $V_{DD}$  of 95 mV was achieved accepting an exponentially growing leakage current and higher fabrication costs [8]. A different digital circuit family, based on logic operations in the current domain, is source-coupled logic and was introduced for sub-threshold operation in [68]. In comparison to CMOS logic this approach uses source-coupled differential pairs connected to a highly resistive load. The switching network consists only of NMOS transistors which decreases the process variation sensitivity. Nevertheless as a differential input stage consists of a series connection of three transistors, the supply voltage reduction is limited.

#### 2.1.1 Sub-threshold Conduction of MOS Transistors

The threshold voltage  $(V_{TH})$  is defined by the gate-source voltage  $(V_{GS})$  required to build up an inverted channel from the source to the drain of a MOS transistor. Below  $V_{TH}$  this conducting channel does not exist. Charge carrier movement is therefore caused by diffusion instead of a drift current. As a result the characteristics change significantly. While in superthreshold operation the drain-source current  $(I_{DS})$  increases quadratically with  $V_{GS}$ , it shows an exponential dependency in the sub-threshold region. According to [73], the expression of  $I_{DS}$  is given by (2.1.1). W/L represents the geometry, m the sub-threshold slope factor and  $V_t$ the thermal voltage kT/q. The factor  $\eta$  models the Drain-Induced Barrier Lowering (DIBL), which is the major second-order effect occurring in that region.  $I_0$  defines the saturation current of a transistor and considers process dependent parameters such as mobility ( $\mu_0$ ) and oxide capacitance ( $C_{ox}$ ) (2.1.2). In the following equations the process dependent parameters are printed in bold letters.

$$I_{DS} = \mathbf{I}_{\mathbf{0}} \frac{W}{L} e^{\left(\frac{V_{GS} - \mathbf{V}_{TH} - \eta V_{DS}}{m V_t}\right)} \left(1 - e^{-\frac{V_{DS}}{V_t}}\right)$$

(2.1.1)

$$I_0 = \mu_0 C_{ox} (m-1) V_t^2$$

(2.1.2)

The sub-threshold current of a MOS device is much more sensitive to process variation compared to super-threshold operation. By investigation of equation (2.1.1), two process dependent parameters are identified.  $I_0$  and  $V_{TH}$ , where in particular the latter is critical due to its exponential impact on  $I_{DS}$ . Strictly speaking, the sub-threshold slope factor also shows a weak process dependency, which is neglected here for simplicity.

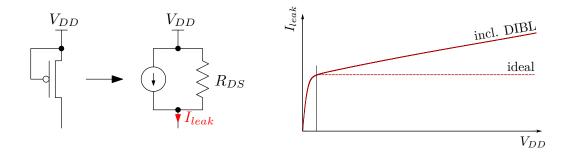

#### 2.1.2 MOS Transistor as Leakage Current Source

The leakage current  $(I_{leak})$  of a MOS transistor is defined by the drain-source current at  $V_{GS} = 0$  V. Therefore interconnecting gate and source results in a leakage current source. As

Figure 2.2: Schematic diagram of the output characteristic of a leakage current source.

shown in Figure 2.2, such a device nearly provides a constant output current with a weak dependence on  $V_{DD}$  due to Drain-Induced Barrier Lowering. In a first order approximation it is therefore modeled by a current source with a resistor in parallel. In order to get the output current of a leakage current source, (2.1.1) can be rewritten as shown in (2.1.3).

$$I_{leak} = \mathbf{I_0} \frac{W}{L} e^{\left(\frac{-\mathbf{V_{TH}} - \eta V_{DS}}{mV_t}\right)} \left(1 - e^{-\frac{V_{DS}}{V_t}}\right)$$

(2.1.3)

The leakage current itself strongly depends on process and temperature variations, but due to correlation effects it can be used as a high-resistive load for a digital logic gate. This issue is discussed in more detail in Chapter 2.2.

#### 2.1.3 Short-Channel Effect

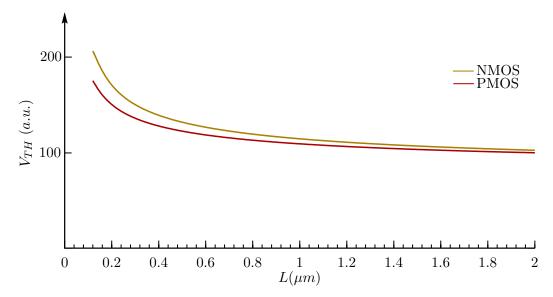

Another parameter affecting  $V_{TH}$  is the gate length of a device due to short-channel effects. As is known from the literature, short transistors suffer from a reduced threshold voltage caused by charge sharing (CS) at the overlapping space-charge region of drain and source junctions [60]. Therefore in current process technologies, the effective doping level is increased by applying halo implants. As a result the threshold voltage rises again which is commonly known as reverse short-channel effect (RSCE) [60]. In Figure 2.3, the dependency of the threshold voltage on the gate length was simulated for an N- and P-MOS device, assuming a constant width. As can be seen, for the Infineon 130 nm process technology, RSCE causes the highest  $V_{TH}$  for minimum gate length. Therefore the sub-threshold design methodology of digital logic cells is different to super-threshold operation. Instead of increasing the current capability by changing the width, it is more effective to increase the gate length of a device. This is true for short-channel devices where RSCE has an effect on  $V_{TH}$ .

Figure 2.3: Dependency of the threshold voltage on the gate length of a transistor.

#### 2.1.4 Transistor Sizing for Maximum Operation Frequency

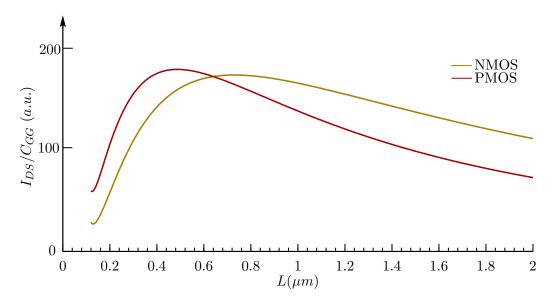

To change the state of the output node of an inverter, a driving transistor has to charge or discharge the input capacitance of the following logic gate which consists at least of one NMOS and PMOS pair. As a result the circuit's maximum operation frequency is determined by the slew rate, which is given by current divided by capacitance. Enlargement of the transistor width for higher frequencies increases current capability and gate capacitance and therefore affects nominator and denominator of the slew rate in the same direction. Conventional digital logic cells use minimum channel length and set the current capability by the width in order to keep the gate capacitance low. As discussed in the previous chapter, in the deep sub-threshold region the length is an additional (nonlinear) parameter used to increase  $I_{DS}$  in the process technology used. Finding the optimum gate length for a minimum propagation delay is therefore the next step in the optimization process.

To verify the impact of the gate length on the slew rate a parametric sweep simulation was performed by applying a gate voltage of 100 mV to an NMOS and a PMOS transistor of similar width for different device lengths. The drain-source current as well as the gate capacitance of the two transistors were monitored and set in relation to plot the slew rate for different values of L. The resulting curves in Figure 2.4 show some interesting properties in comparison to strong inversion operation. Starting at minimum length the PMOS transistor shows a higher current capability compared to its counterpart up to a length of 600 nm. The reason can be found in the lower rise of the threshold voltage due to RSCE of the PMOS transistor (review Figure 2.3). Above, the lower mobility dominates and the PMOS becomes the weaker device. At the intersection point, which is close to the maximum slew rate, both transistors have similar strength. Therefore a gate length of 600 nm was chosen for the gates of the ultra-low voltage digital cell library.

Figure 2.4: Dependency of the slew rate of the gate length of a transistor.

## 2.2 Reducing Process-dependent Variations in the Deep Sub-threshold Region

The aim of this chapter is to discuss the issue, which is related to process variation, of reducing the supply voltage of a CMOS inverter to the deep sub-threshold region of less than 100 mV. Therefore, the equivalent circuit diagram of the gate is analyzed at the transition point of  $V_{IN} = V_{DD}/2$ , which is the switching threshold of the idealized digital circuitry. Then, in the following chapters, the topology is adapted by introducing N- and P-type inverters. This results in the creation of a CMOS inverter with reduced sensitivity to process variations for ultra-low voltage operation.

#### 2.2.1 Standard CMOS Inverter

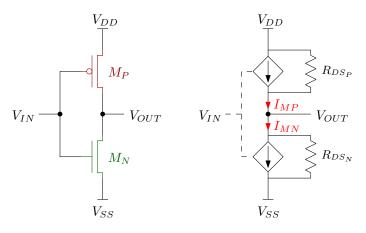

A standard CMOS inverter is shown in Figure 2.5 and consists of an interconnected NMOS and PMOS pair, implementing logical negation. It can be modeled by two complementary current sources operating in a push-pull configuration. The output voltage is determined by the current capability of the stronger transistor which is controlled by the gate-source voltage.

2.2 Reducing Process-dependent Variations in the Deep Sub-threshold Region

$$I_{MN} = e^{\left(\frac{V_{IN}}{mV_t}\right)} \cdot \boldsymbol{I}_{leak_N}$$

(2.2.1)

$$I_{MP} = e^{\left(\frac{V_{DD} - V_{IN}}{mV_t}\right)} \cdot I_{leak_P}$$

(2.2.2)

$$\boldsymbol{V_{SW}} = \frac{1}{2} \left( V_{DD} + mV_t \ln \frac{\boldsymbol{I_{leak_N}}}{\boldsymbol{I_{leak_P}}} \right)$$

(2.2.3)

For the purpose of this discussion the behavior a logical low at the input node is assumed. While the PMOS is fully turned on, the NMOS transistor is just leaking. Its drain-source current is therefore given by (2.1.3). As a result the output node is pulled up to a logical high. Raising the input voltage increases the current capability of the NMOS by amplification of  $I_{leak}$  with an exponential factor (2.2.1). The opposite behavior is observed for the PMOS which becomes weaker due to  $V_{GS}$  reduction (2.2.2). As soon as the input voltage exceeds the switching threshold ( $V_{IN} = V_{DD}/2$ ), the NMOS transistor sinks more current than the PMOS can deliver, therefore the drain-source voltage drops to a low level. At the transition point, both current sources are of similar strength resulting in an output voltage of  $V_{OUT} = V_{DD}/2$ , due to the finite drain-source resistances.

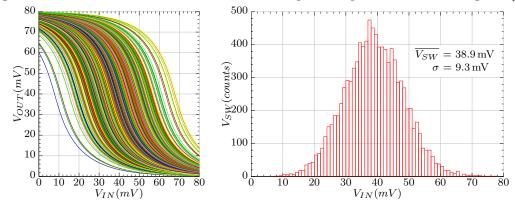

Process related variations influence the leakage currents and therefore the switching threshold  $(V_{SW})$  of the inverter. In order to discuss this issue the transition point is investigated by setting up the current balance equation  $(I_{MP} = I_{MN})$  at the output node. Solving  $V_{IN}$  results in the ideal switching threshold of  $V_{DD}/2$  which is shifted by an error term, depending on the leakage currents ratio given by (2.2.3). This expression shows that the switching level  $V_{SW}$  has a logarithmic dependency on the saturation currents  $I_{0N}$  and  $I_{0P}$  and changes linearly with the transistors threshold voltage  $(V_{THN}, V_{THP})$ . As the parameters of both devices vary in an uncorrelated way, a large deviation in the switching threshold of the standard CMOS inverter in Figure 2.5, the voltage transfer curve was simulated by performing a Monte Carlo simulation at a supply voltage of 80 mV. The corresponding output characteristic is illustrated in Figure 2.6 and shows a six-sigma deviation of  $\pm 55.6 \text{ mV}$ . This confirms the assumption that conventional CMOS logic cells are unusable in the deep sub-threshold region.

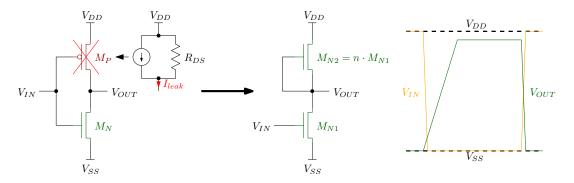

## 2.2.2 N-type Inverter

As shown in the previous chapter the deviation of the switching threshold causes serious issues in conventional CMOS logic cells in ultra-low voltage domains, due to uncorrelated process parameter dependencies of NMOS and PMOS transistors. A solution to this problem is to replace the active PMOS by a leakage current source of its opposite type as illustrated in Figure 2.7. The leakage current source consists of a certain amount of NMOS devices, as used for the active part. This is because in order to provide a logical high, the load needs to be

Figure 2.5: Standard CMOS inverter and its simplified equivalent circuit diagram [30].

Figure 2.6: Simulated voltage transfer curve of a standard CMOS inverter at a supply voltage of 80 mV applying 10000 Monte Carlo runs.

able to pull-up the output node. The advantages of such a configuration are correlated process parameters of the active device and the load.

$$I_{MN1} = e^{\left(\frac{V_{IN}}{mV_t}\right)} \cdot \boldsymbol{I_{leak_N}}$$

(2.2.4)

$$I_{MN2} = n \cdot I_{leak_N} \tag{2.2.5}$$

$$V_{SW} = mV_t \cdot \ln\left(n\right) \tag{2.2.6}$$

In order to discuss the behavior of the n-type inverter of Figure 2.7, the switching threshold is again calculated by setting up the current balance equation at the output node. The current capability of  $M_{N1}$  is known from the previous chapter and given by (2.2.4), while the load  $(M_{N2})$  provides *n* times the leakage current of the active device. Unlike the standard CMOS inverter,  $I_{leak}$  drops out of the current balance equation resulting in a process- and supply

Figure 2.7: N-type inverter. Using a single transistor type reduces the influence of process dependencies due to correlation effects.

Figure 2.8: P-Type Inverter. Using a single transistor type reduces the influence of process dependencies due to correlation effects.

independent switching threshold.  $V_{SW}$  is adjustable to the number of devices used for the leakage source (2.2.6). The cost of the process independence is a slow rising edge as it is just the leakage current charging the load capacitance. Additionally the voltage swing is reduced due to a lower logical high state.

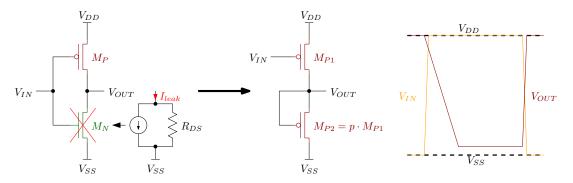

# 2.2.3 P-type Inverter

The same approach can be applied by replacing the NMOS by a certain amount (p) of PMOS leakage current sources to get a P-type inverter (Figure 2.8). The corresponding current equations are given in (2.2.7) and (2.2.8) again resulting in a process independent switching threshold when setting up the current balance equation at the output node (2.2.9). In contrast to the N-type inverter, the switching threshold  $V_{SW}$  is referred to  $V_{DD}$ . When studying the shape of the output voltage in Figure 2.8, it shows a weak falling edge due to the leakage current discharging the load capacitance. Additionally the voltage swing is reduced due to a higher logical low state.

$$I_{MP1} = e^{\left(\frac{V_{DD} - V_{IN}}{mV_t}\right)} \cdot \boldsymbol{I_{leak_P}}$$

(2.2.7)

$$I_{MP2} = p \cdot \boldsymbol{I_{leak_P}} \tag{2.2.8}$$

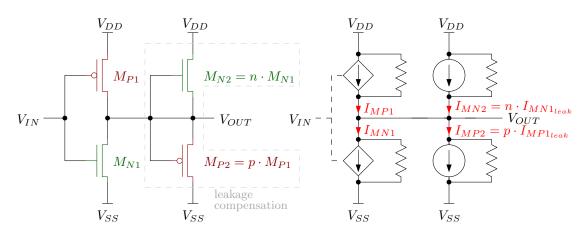

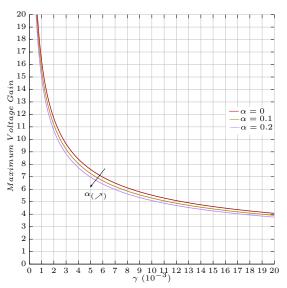

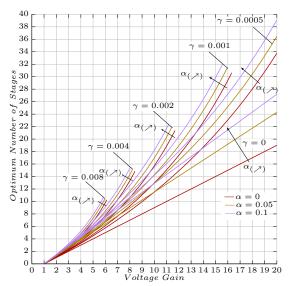

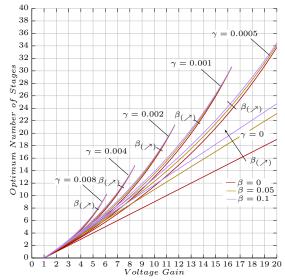

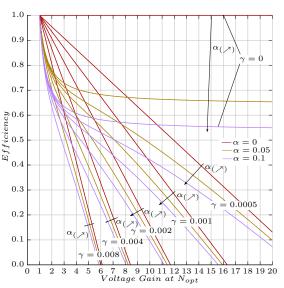

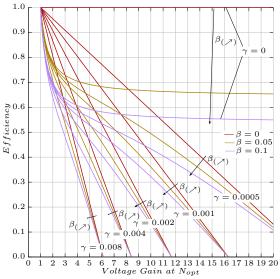

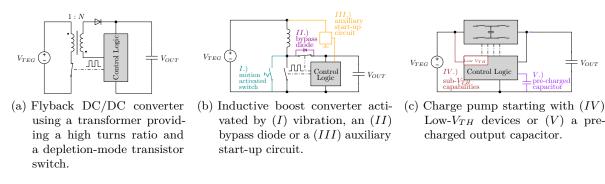

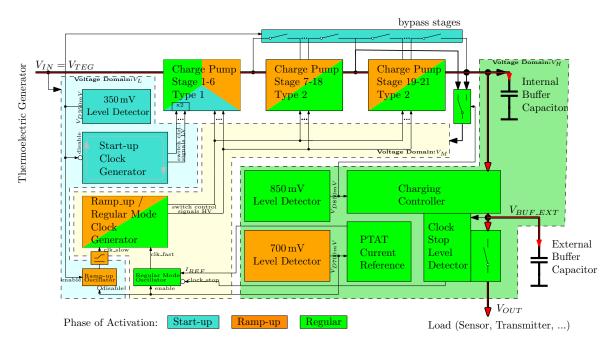

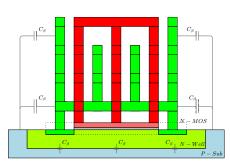

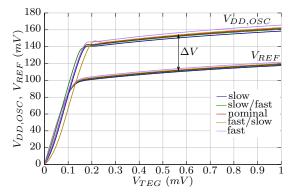

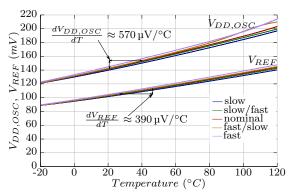

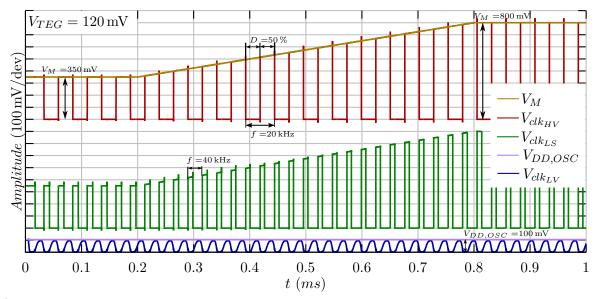

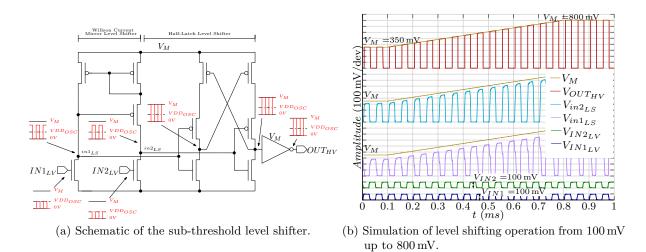

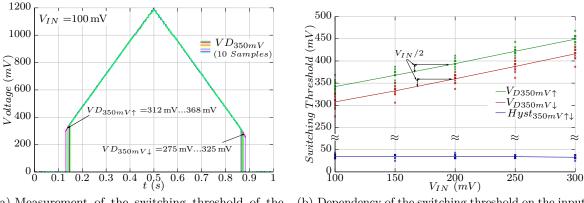

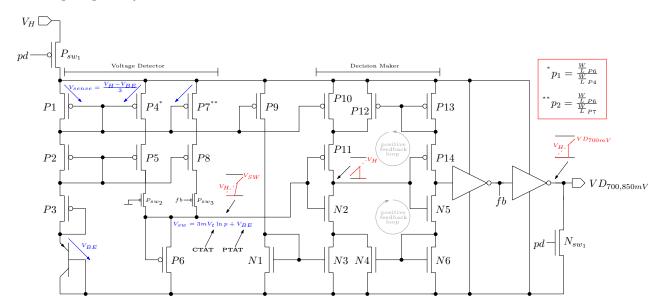

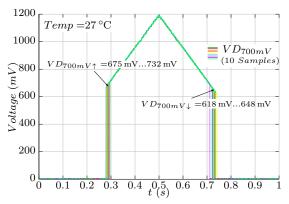

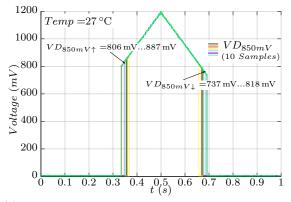

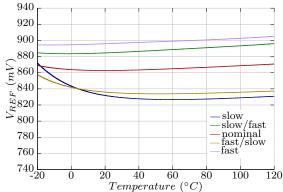

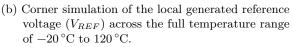

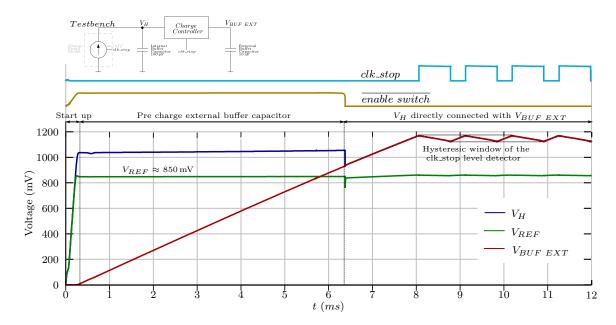

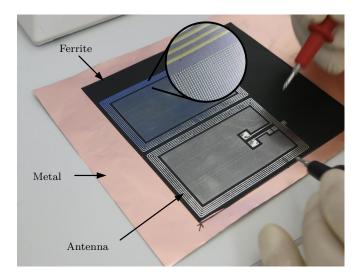

$$V_{SW} = V_{DD} - mV_t \cdot \ln\left(p\right) \tag{2.2.9}$$