Dipl.-Ing. Armin Krieg

## Control State Based Fault Detection and Analysis in Multi-Processor Systems-On-Chip

Dissertation

vorgelegt an der Technischen Universität Graz

zur Erlangung des akademischen Grades Doktor der Technischen Wissenschaften (Dr. techn.)

durchgeführt am Institut für Technische Informatik Technische Universität Graz Vorstand: Em. Univ.-Prof. Dipl.-Ing. Dr. techn. Reinhold Weiß

Graz, im Januar 2013

## EIDESSTATTLICHE ERKLÄRUNG

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen / Hilfsmittel nicht benutzt und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe.

## STATUTORY DECLARATION

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

Graz, the .....

(Signature)

### Kurzfassung

In den vergangenen Jahren gab es einen dramatischen Anstieg der Systemintegrationsdichte von integrierten Halbleiterimplementierungen. Diese Marktentwicklung wurde in erster Linie von zwei Faktoren getrieben. Erstens, der Markt für Unterhaltungselektronik forderte eine wachsende Menge an integrierter Funktionalität in mobilen Anwendungen. Zweitens, neue Fertigungstechnologien im deep-submicron Bereich erlaubten diese steigende Integration bei nahezu gleichbleibendem Energiebedarf. Ein negativer Nebeneffekt dieser hohen Integrationsdichten ist ein breites Spektrum an Zuverlässigkeitsproblemen, die von den Systemdesignern gelöst werden müssen. Weiters müssen auch absichtliche Fehler berücksichtigt werden, welche durch einen Angreifer in das System eingebracht werden um dieses in einen fehlerhaften Zustand zu bringen. Während es in den letzten Jahren ein breites Spektrum an Forschung auf dem Gebiet von Untersuchungstechniken in frühen Designständen gab, z.B. simulations- oder emulationsbasierte Ansätze, gab es kaum Bewegung am Gebiet der Fehlererkennung.

In dieser Arbeit werden neue Methoden der effizienten kontrollflussbasierten Laufzeitprüfung der Ausführungsintegrität gesucht und evaluiert. Zu diesem Zwecke wurden neue signatur-basierte Techniken eingeführt, welche eine Verschmelzung der Fehlerdetektionsmit einer Leistungsabschätzunginfrastruktur ermöglichen. Auf Grund der stark eingeschränkten Resourcen in der gewählten Zieldomäne werden weiter neue Methodiken zur Abschätzung der Fehlererkennungs-, Resourceverbrauchs-, Stromverbrauchseffizienz benötigt. Diese Eigenschaften sollen mit Hilfe einer FPGA-basierten Emulationsplatform evaluiert werden. Daher wurden im Rahmen dieser Arbeit neue Methodiken entwickelt, um schnelle und genaue Evaluierungen mittels solcher Emulationssysteme zu ermöglichen. Die hierfür implementierten Fallstudien basieren auf einer von Gaisler Research entwickelten SPARC-v8 Implementierung (LEON3). Weiters wurde die generelle Anwendbarkeit der vorgestellten Techniken in einem industriellen Anwendungsbeispiel demonstriert, welches auf einem echten Smart-Card System inklusive einem sicheren Betriebssystem basiert.

#### Abstract

Recent years showed a dramatic increase in system integration density of embedded semiconductor implementations. This development was driven by two main factors. First, market demand for ever more functionality residing in small mobile devices. Second, deep-submicron semiconductor manufacturing processes allowed to increase density at a steady power consumption. High integration density, on the other side, results into a variety of additional problems for the system designers. A major concern in recent and future designs in this context is execution reliability caused by operational faults. Another fault source that got into the focus of various research groups are intentional ones caused by malicious attackers, trying to put the target system into an unintended state. While there has been a wide range of research concerning early design phase investigation techniques, like simulation or emulation approaches, detection has only slightly improved.

In this work novel techniques are explored to enable efficient on-line checking of operation integrity. For this task novel signature-based techniques are introduced, which enable the integration of fault detection mechanisms into power estimation infrastructure. Also, such new implementations require methodologies to test their effectiveness in terms of fault detection, resource usage, and power consumption. These operational properties are evaluated using two FPGA-based emulation systems, one of academic nature and an industrially used one. Therefore, this work introduces new techniques to enable fast and accurate system evaluations using general emulation-based evaluation platforms. The provided case-studies are based on the open available SPARC-v8 implementation provided by Gaisler Research (LEON3). Furthermore, an industrial case study using a smart-card hardware implementation and secure operating system is presented to prove the general applicability of the introduced approaches.

#### Acknowledgements

This thesis has been pursued as part of the POWER-MODES research project, which is a successful cooperation between Infineon Technologies Austria AG, AustriaCard GmbH and the Institute for Technical Informatics of Graz University of Technology. Considering all these organizations and their employees that supported me during the accomplishment of my thesis, I would like to thank them all, but of course I am only able to mention a few.

First of all, I would like to thank Prof. Reinhold Weiss for providing this possibility to work in the hardware/software co-design research group at the Institute for Technical Informatics. Especially, I would thank for the helpful comments and advice given during the review phases of this work. Furthermore, I would like to express my gratitude to Christian Steger for his thoughtful supervision of the project and support concerning the academic publishing process.

Our industry partners provided us with continuing insight into state-of-the-art products and industrial design environments. In this regard I would like to thank Josef Haid for deep insight into idea creation processes and his knowledge concerning low power design and power estimation. Also, I would like to give my thanks to Holger Bock for his efficient project management and his deep knowledge of smart-card security. Furthermore, my thanks are due to Christiane Ulbricht and Thomas Aichinger for sharing their experiences with smart-card operating systems.

Special thanks go to my PhD colleagues Norbert Druml and Manuel Menghin for their in-depth review of this work and their helpful comments on this thesis. Also, I would like to thank Christian Bachmann and Andreas Genser for their comprehensive insight into power emulation and their various tips that were a tremendous help during my PhD. In this regard I would also like to give my thanks to my project partner Johannes Grinschgl for the great cooperation during the accomplishment of the POWER-MODES project.

Finally, I would like to thank my family for their continuing support and especially my dear Sisi for her enduring understanding even when this thesis consumed most of my free time. Without you I would not have been able to finish this work. Thank you!

Graz, January 2013

Armin Krieg

#### **Extended Abstract**

In 1965 Gordon Moore of the Intel Cooperation postulated that the amount of transistors integrated into semiconductor systems will double every two years. His assumptions stand true up until now and, according to Intel, will hold for the many years to come. This development was enabled by a continuous improvement of semiconductor manufacturing processes and system integration techniques. Currently, deep sub-micron processes enable structures of 22nm and smaller sizes, resulting in an isolation thickness of only a few atomic layers. From a system perspective, dense *Systems-on-Chip* (SoCs) implementations concentrated many different functions (processor cores, audio and video IP cores, and communication interfaces to name a few) into single packages.

This highly increased integration density came at a price: high peak power consumption caused by the high number of sub-systems; dependability issues and device degradation problems caused by the fragility of deep sub-micron structures; security issues caused by the intermixture of personal data and entertainment functions. These challenges have to be dealt with at the earliest possible design-stage to avoid problems after market entry of the finalized product. Hardware emulation approaches, based on *field programmable gate arrays* (FPGAs), aim to solve previously described challenges at once. First, direct synthesis of the RTL description of the final product for FPGA evaluation platforms, provides functional equivalence of the evaluation and production hardware model. Second, the hardware implemented model is enabled to be evaluated at realistic clock-rates, improving speed and timing equivalence (depending on system complexity). These advantages are used in hardware-accelerated software verification platforms, already supporting the hardware/software co-design process for years. Unfortunately, these verification systems do not provide power information or allow the investigation under fault conditions.

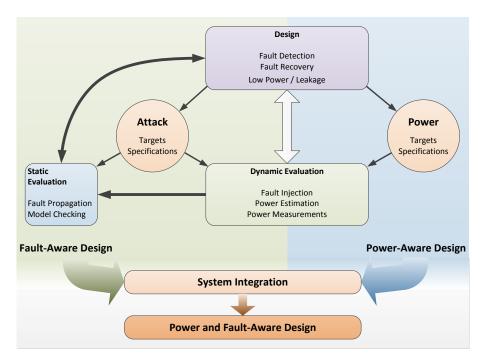

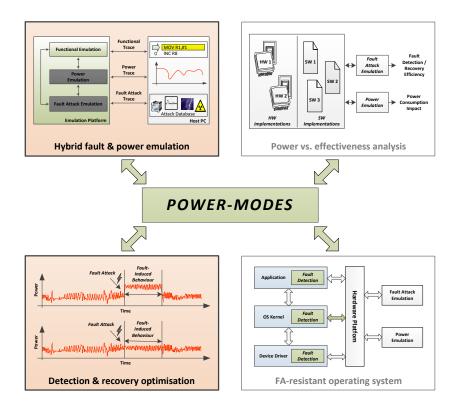

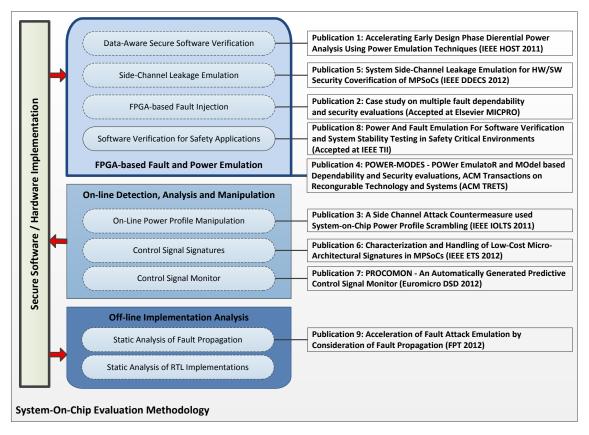

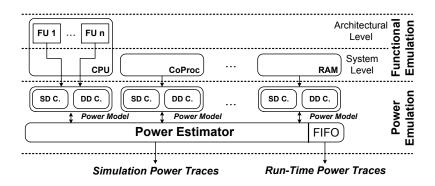

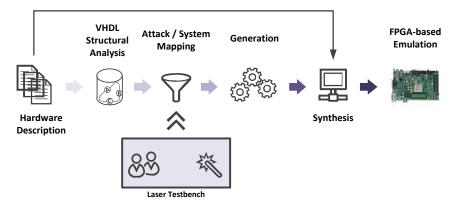

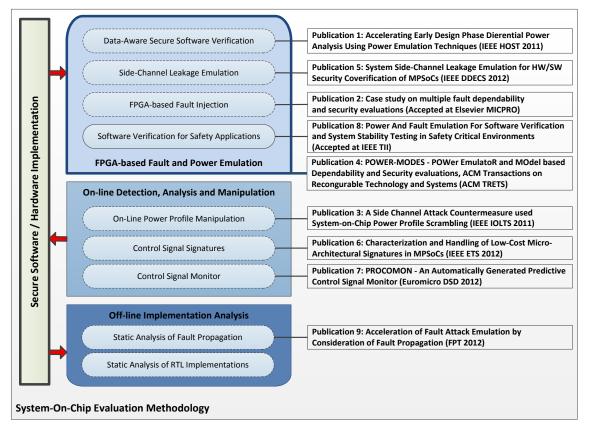

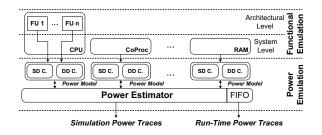

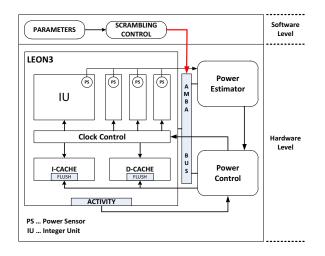

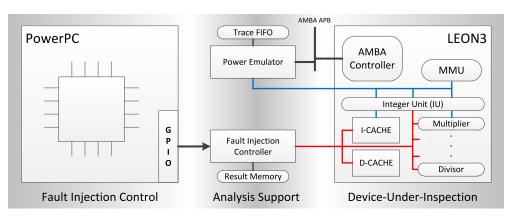

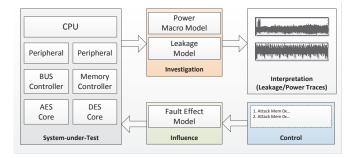

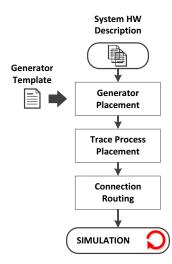

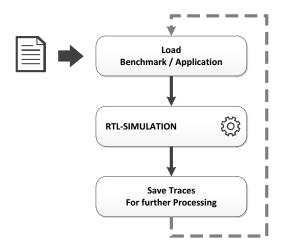

The POWER-MODES project<sup>1</sup>, which included and financed this work, aims at providing a comprehensive evaluation platform for security, dependability, and power investigations. This inter-disciplinary approach merges solutions for different but highly connected problem spaces into a single hardware-accelerated evaluation system. While the focus lies on the high performance verification of software implementations, the derived techniques are also applicable on highly focused hardware verification tasks. This way, an efficient possibility for *hardware/software codesign* is created for the estimation of system power efficiency and dependability under fault conditions. An overview over such a comprehensive approach, combining two different domains into a single evaluation platform, is depicted in Figure 1.

<sup>&</sup>lt;sup>1</sup>POWer EmulatoR and MOdel based DEpendability and Security evaluation platform, collaborative research project of the Graz University of Technology, Infineon Austria AG and AustriaCard GmbH. Funded by the Austrian Federal Ministry for Transport, Innovation, and Technology under the FIT-IT contract FFG 825749.

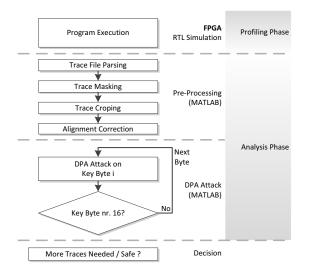

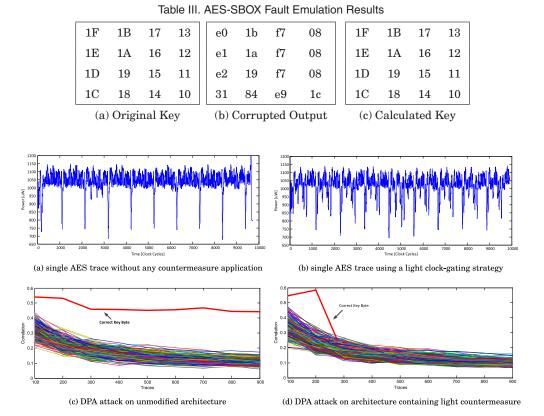

Figure 1: Control-flow-based Online Fault Detection and Analysis - A Comprehensive Approach

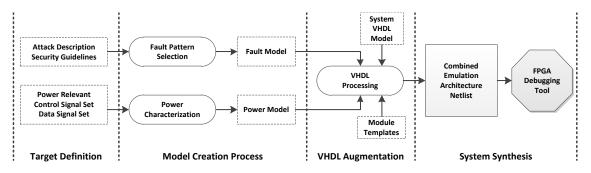

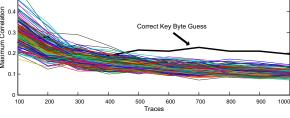

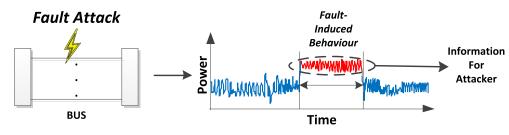

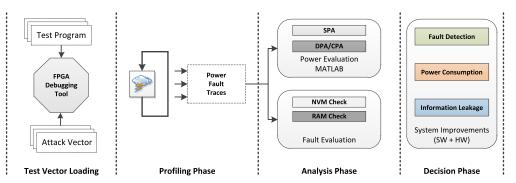

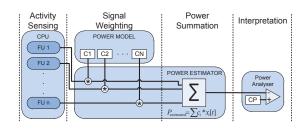

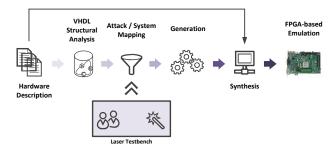

As visualized in Figure 1, power-aware and fault-aware design relies on techniques from various backgrounds. This thesis aims at providing a novel methodology to evaluate existing system implementations, using static and dynamic techniques, and to design variants that solve identified weaknesses. First, the power-aware design approach for the development of embedded software has to be extended for enabling *power analysis* techniques used in security evaluations. For this purpose, a hardware-accelerated methodology has been presented, introducing such functionality into a proven power characterization and evaluation flow<sup>2</sup>. Such strategies can be categorized as *dynamic evaluation* techniques.

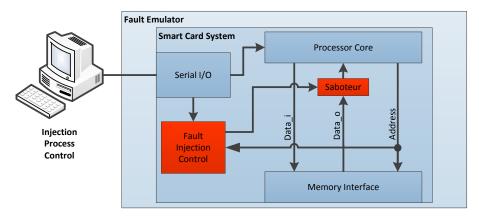

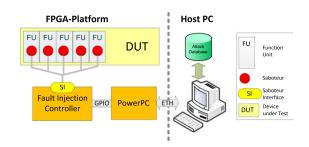

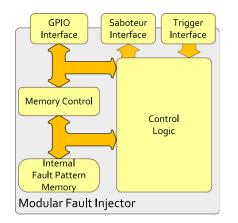

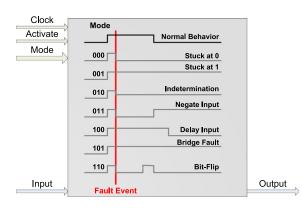

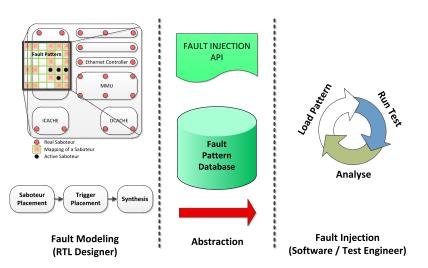

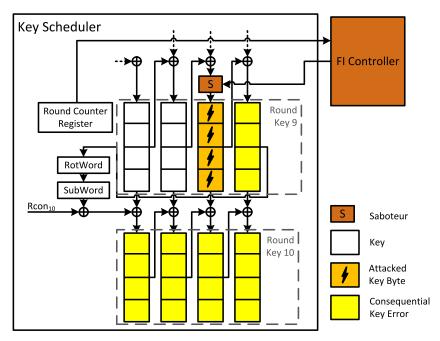

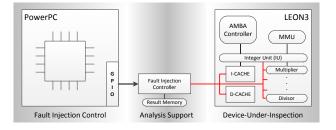

Second, to enable the merger of security-aware power estimation, as discussed earlier, and direct fault-attack investigations into a single evaluation platform, additional *fault injection* circuitry is necessary. In the course of this work, a modular implementation of such fault injection hardware has been derived and integrated into existing software verification infrastructure<sup>3</sup>. The experiences gained during the creation of a data-aware power estimation platform has been used to introduce novel countermeasures against such forms of attack. Under the consideration of the challenges posed by the design of resource-constrained systems, only existing infrastructure has been reused to keep additional hardware effort as low as possible<sup>4</sup>.

<sup>&</sup>lt;sup>2</sup>Krieg et al., Accelerating Early design Phase Differential Power Analysis Using Power Emulation Techniques, 4th IEEE International Symposium on Hardware-Oriented Security and Trust 2011 (HOST '11), San Diego, United States of America, 5-6th of June 2011.

<sup>&</sup>lt;sup>3</sup>Grinschgl et al., Case Study on Multiple Fault Dependability and Security Evaluations, Elsevier Microprocessors and Microsystems (MICPRO), accepted for publication, 2013.

<sup>&</sup>lt;sup>4</sup>Krieg et al., A Side Channel Attack Countermeasure using System-On-Chip Power Profile Scrambling, 17th IEEE Intl. On-Line Testing Symposium 2011 (IOLTS '11), Athens, Greece, 13-15th of July 2011.

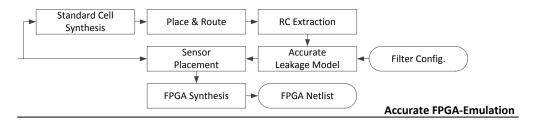

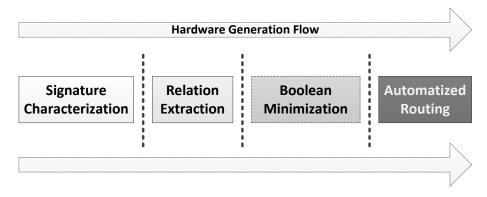

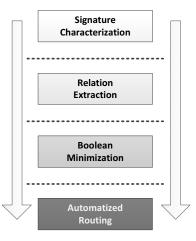

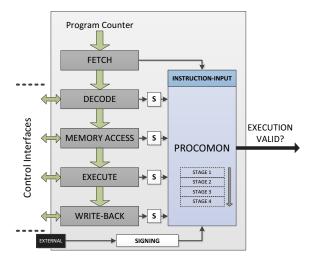

All previously discussed evaluation techniques and design practices have been integrated and investigated inside a single platform. Furthermore, hardware security attacks, as shown in previous literature, have been mapped onto this system and successfully presented<sup>5</sup>. Large multi-processor system-on-chip (MPSoC) implementations introduced various new issues concerning security and dependability. Under the consideration of these new challenges, also the power estimation approach was modularized and data from the physical implementation was included to increase the evaluation accuracy<sup>6</sup>. Again, advances in the field of evaluation techniques can be used to improve various design methodologies. The heterogeneous nature of MPSoCs poses a tremendous challenge for secure system design. Considering that system-wide fault detection has to be provided, a microarchitectural signature approach has therefore been introduced to cover this gap in existing literature<sup>7</sup>. The integration of such novel techniques into existing implementation is a major concern in the design of large systems. Therefore, an automatized approach has been shown to generate complete monitor modules using the previously presented signature characterization process<sup>8</sup>.

The major drive behind all introduced techniques for evaluation and design of digital systems shown in this work, has been security-aware engineering. Safety engineering suffers from many similar problems, with the difference that faults are caused by random sources<sup>9</sup>. The dynamic evaluation of large heterogeneous digital systems is increasingly limited by available investigation techniques and resources. Hence, formal verification methods are introduced in various parts of the verification process. Furthermore, static analysis of the hardware description allows for the linking of the high-level RTL view and the low-level physical implementation of the design<sup>10</sup>.

<sup>&</sup>lt;sup>5</sup>Krieg et al., POWER-MODES - POWer EmulatoR and MOdel based Dependability and Security evaluations, ACM Transactions on Reconfigurable Technology and Systems (TRETS), Volume 5, Issue 4, Article 19, 2012

<sup>&</sup>lt;sup>6</sup>Krieg et al., System Side-Channel Leakage Emulation for HW/SW Security Coverification of MPSoCs, 15th IEEE Symposium on Design and Diagnostics of Circuits and Systems 2012 (DDECS '12), Tallinn, Estonia, 18-20th of April 2012.

<sup>&</sup>lt;sup>7</sup>Krieg et al., Characterization and handling of Low-Cost Micro-Architectural Signatures in MPSoCs, 17th IEEE European Test Symposium 2012 (ETS '12), Annecy, France, 28th of May to 1st of July 2012.

<sup>&</sup>lt;sup>8</sup>Krieg et al., PROCOMON - An Automatically Generated Predictive Control Signal Monitor, 15th Euromicro Conference on Digital System Design 2012 (DSD '12), Izmir, Turkey, 5-8th of September 2012.

<sup>&</sup>lt;sup>9</sup>Krieg et al., Power and Fault Emulation For Software Verification and System Stability Testing in Safety Critical Environments, IEEE Transactions on Industrial Informatics (TII), to be published in Volume 9, Issue 2, 2013.

<sup>&</sup>lt;sup>10</sup>Krieg et al., Acceleration of Fault Attack Emulation by Consideration of Fault Propagation, 11th Intl. Conference on Field-Programmable Technology 2012 (FPT '12), Seoul, Korea, 10-12th of December 2012.

# Contents

| 1 Introduction |     | roduction                                                                      | 1          |

|----------------|-----|--------------------------------------------------------------------------------|------------|

|                | 1.1 | Motivation                                                                     | 1          |

|                |     | 1.1.1 David and Goliath - Design Challenges of the Large and Tiny              | <b>2</b>   |

|                |     | 1.1.2 Power- and Fault-Awareness in Modern System-On-Chip Designs              | 4          |

|                |     | 1.1.3 Hardware-Accelerated Emulation for Software Verification                 | 5          |

|                | 1.2 | Control-State-Based Fault Detection and Analysis in Multi-Processor System-On- |            |

|                |     | Chips                                                                          | 7          |

|                |     | 1.2.1 The POWER-MODES Project                                                  | 7          |

|                |     | 1.2.2 Problem Statement                                                        | 8          |

|                |     | 1.2.3 Contributions and Significance                                           | 8          |

|                |     | 1.2.4 Structure of the Work                                                    | 9          |

| 2              | Rol |                                                                                | 10         |

| 4              | 2.1 |                                                                                | 10         |

|                | 2.1 | v i                                                                            | 10         |

|                |     |                                                                                | 11         |

|                |     | J I                                                                            | $11 \\ 12$ |

|                | 2.2 | 0 0 0                                                                          | $12 \\ 12$ |

|                | Z.Z |                                                                                |            |

|                |     | 0                                                                              | 13         |

|                |     | 0                                                                              | 13         |

|                | 0.0 |                                                                                | 13         |

|                | 2.3 | <ul> <li>V</li> </ul>                                                          | 14         |

|                |     |                                                                                | 14         |

|                |     | 11                                                                             | 14         |

|                |     | v                                                                              | 15         |

|                |     | 100                                                                            | 16         |

|                | 2.4 | Summary and Difference to the State-of-the-Art                                 | 17         |

| 3              | Fau |                                                                                | 18         |

|                | 3.1 | Overview                                                                       | 18         |

|                | 3.2 |                                                                                | 19         |

|                |     | 3.2.1 Data-Aware Emulation-Based Power Estimation                              | 19         |

|                |     | 3.2.2 Software Verification under Fault Conditions                             | 22         |

|                |     |                                                                                | 24         |

|                | 3.3 |                                                                                | 24         |

|                |     |                                                                                | 25         |

|                |     |                                                                                | 27         |

|                |     |                                                                                | -          |

| 4 | Eva          | luation of the MPSoC Fault Detection and Analysis Techniques                       | 28              |

|---|--------------|------------------------------------------------------------------------------------|-----------------|

|   | 4.1          | Overview                                                                           | 28              |

|   | 4.2          | Target and Evaluation Platforms                                                    | $\frac{28}{28}$ |

|   |              | 4.2.1 Software vermeation in Smart-Card Systems                                    | $\frac{28}{29}$ |

|   | 4.3          | Power-Aware and Fault-Aware Software Verification                                  | 30              |

|   |              | 4.3.1 Hardware-Accelerated Power-Aware Hardware and Software Fault Attack          |                 |

|   |              | EvaluationEvaluation-based Secure Software Verification for Smart-Card Products in | 30              |

|   |              | an Industrial Setting                                                              | 35              |

|   | 4.4          | 4.3.3 Power-Aware Evaluation of Self-tests in the Safety Domain                    | $\frac{36}{38}$ |

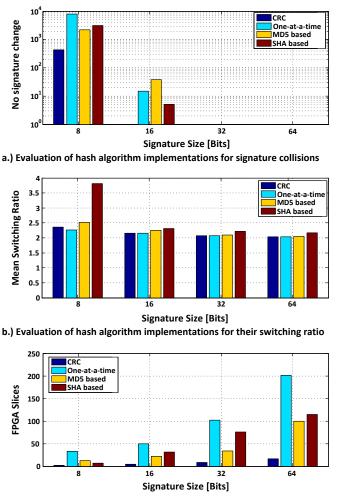

|   | 4.4          | 4.4.1 Characterization of Systems for Optimized Signature Implementations          | - 38<br>- 38    |

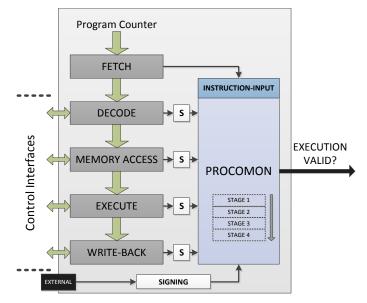

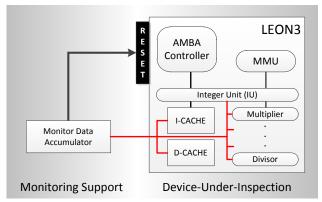

|   |              | 4.4.2 Automatized Generation of Signature Checking Hardware                        | 40              |

|   | 4.5          | Hardware Testing Support using Static Analysis Methods                             | 42              |

| 5 | Cor          | clusion and Future Work                                                            | 44              |

|   | 5.1          | Conclusion                                                                         | 44              |

|   | 5.2          | Directions for Future Work                                                         | 45              |

|   |              | 5.2.1 High-Level Evaluation of Security Policies during Early Design Phases        | 45              |

|   |              | 5.2.2 System-Level Power and Security Evaluations of Mobile Systems                | 45              |

| 6 | Pub          | olications                                                                         | <b>47</b>       |

|   | 6.1          | Accelerating Early Design Phase Differential Power Analysis Using Power Emulation  |                 |

|   | <u> </u>     | Techniques                                                                         | 50              |

|   | $6.2 \\ 6.3$ | Case study on multiple fault dependability and security evaluations                | 56              |

|   | 0.5          | bling                                                                              | 66              |

|   | 6.4          | POWER-MODES - POWer EmulatoR and MOdel based Dependability and Security            | 00              |

|   |              | evaluations                                                                        | 72              |

|   | 6.5          | System Side-Channel Leakage Emulation for HW/SW Security Coverification of         |                 |

|   | ~ ~          | MPSoCs                                                                             | 93              |

|   | 6.6          | Characterization and Handling of Low-Cost Micro-Architectural Signatures in MP-    | 00              |

|   | 6.7          | SoCs                                                                               | $99 \\ 105$     |

|   | 6.8          | Power And Fault Emulation For Software Verification and System Stability Testing   | 100             |

|   |              | in Safety Critical Environments                                                    | 112             |

|   | 6.9          | Acceleration of Fault Attack Emulation by Consideration of Fault Propagation       | 120             |

|   |              |                                                                                    |                 |

#### References

124

# List of Figures

| 1    | Control-flow-based Online Fault Detection and Analysis - A Comprehensive Approach                                                                             | v               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.1  | Dawn of the Machine-to-Machine (M2M) Age (adapted from [1]) - the development<br>of the mobile device market is far from over, M2M communication will further |                 |

| 1.2  | increase the number of mobile devices sold                                                                                                                    | 1               |

| 1.3  | performance, and implementation effort, according to the ITRS                                                                                                 | 2               |

|      | continuously widening if no countermeasures are taken in time (adapted from $[2]$ ).                                                                          | 3               |

| 1.4  | Challenges concerning the verification of future complex systems according to Men-<br>tor Graphics                                                            | 4               |

| 1.5  | Manufacturing variability is strongly worsening for deep sub-micron technologies, according to [2]                                                            | 5               |

| 1.6  | Usage trends for hardware-accelerated emulation during system design and verifica-                                                                            | -               |

| 1.7  | tion, according to [3]                                                                                                                                        | 6               |

|      | evaluations concurrently using a single hardware-accelerated emulation platform (adapted from [4])                                                            | 7               |

| 3.1  | Publication overview concerning a comprehensive system-on-chip evaluation method-<br>ology for secure/reliable software and hardware implementations          | 19              |

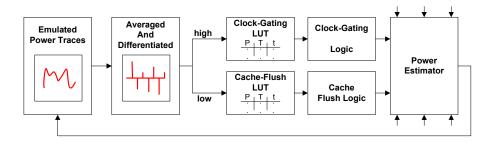

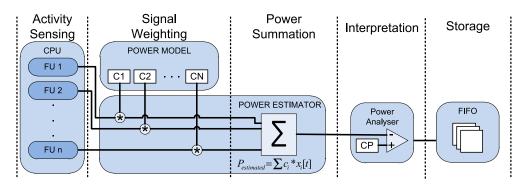

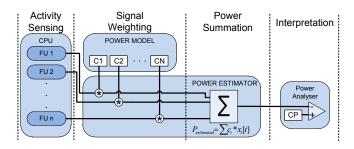

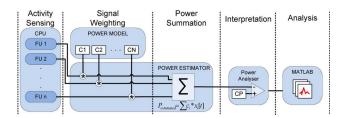

| 3.2  | Basic power emulation principle - Generating run-time power estimates from the                                                                                |                 |

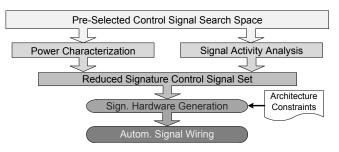

| 3.3  | current state of selected control signals (adapted from [5])                                                                                                  | 20              |

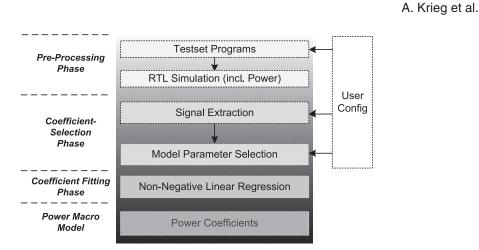

| 3.4  | reduced power macro models (adapted from [6, 5])                                                                                                              | $21 \\ 21$      |

| 3.5  | Power emulation architecture - Flexible and integratible hardware power estimator (adapted from [5])                                                          | 22              |

| 3.6  | Automatized System Augmentation and Verification Platform Generation (adapted                                                                                 | 22              |

| 3.7  | from [5])                                                                                                                                                     | 22              |

| 3.8  | Conditions (adapted from [5])                                                                                                                                 | 23              |

|      | (adapted from [7])                                                                                                                                            | 23              |

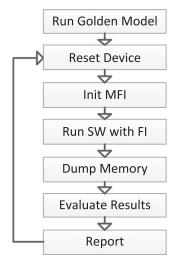

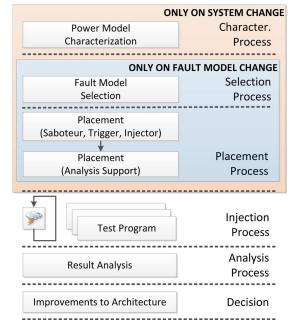

| 3.9  | Global Fault Attack Analysis Flow under the Consideration of Fault Propagation (adapted from [8])                                                             | 24              |

| 3.10 | Control Signal Signature Characterization and Implementation Methodology (adapted from [9])                                                                   | 25              |

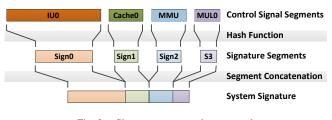

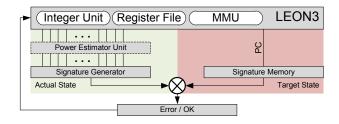

|      | Signature Checking Architecture for a General Purpose Processor (adapted from [9])                                                                            | $\frac{25}{26}$ |

| 3.12 | Hardware generation process for modular signal monitor architectures (adapted from [10])                                                                      | 26              |

|      |                                                                                                                                                               |                 |

| 3.13         | Online Power Consumption Manipulation Methodology (adapted from [11]) $\ . \ . \ .$                                                                                                                                                                      | 27 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1          | SLE77 system-on-chip architecture overview                                                                                                                                                                                                               | 29 |

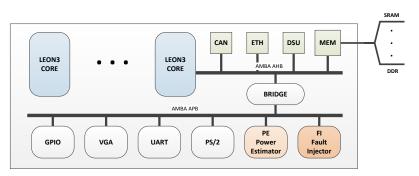

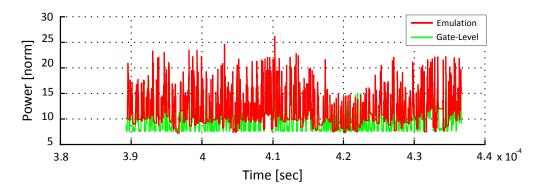

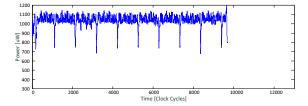

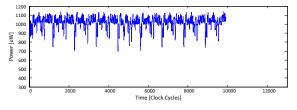

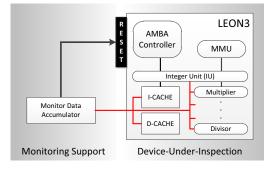

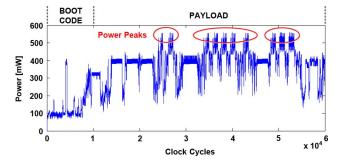

| $4.2 \\ 4.3$ | LEON3 system-on-chip architecture overview - Obtained with modifications from [12] Power-aware software verification, run-time power estimation of the dhrystone bench-                                                                                  | 29 |

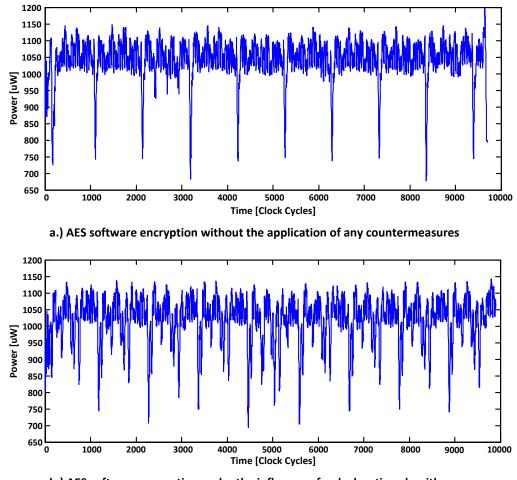

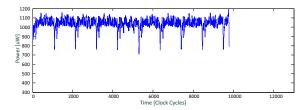

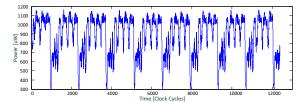

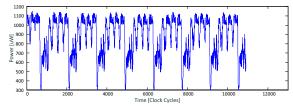

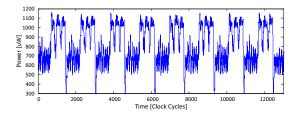

| 4.4          | mark program running on the SLE platform - Obtained with modifications from [5]<br>Power consumption trace of an AES software encryption with and without the appli-<br>cation of countermeasures using the LEON3 platform - Obtained with modifications | 30 |

| 4.5          | from [5]                                                                                                                                                                                                                                                 | 31 |

| 1.0          | - Obtained with modifications from [5]                                                                                                                                                                                                                   | 32 |

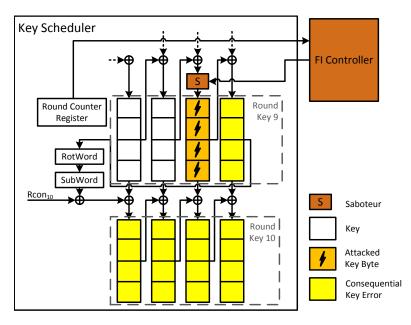

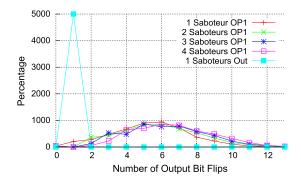

| 4.6          | AES-SBOX fault emulation results                                                                                                                                                                                                                         | 32 |

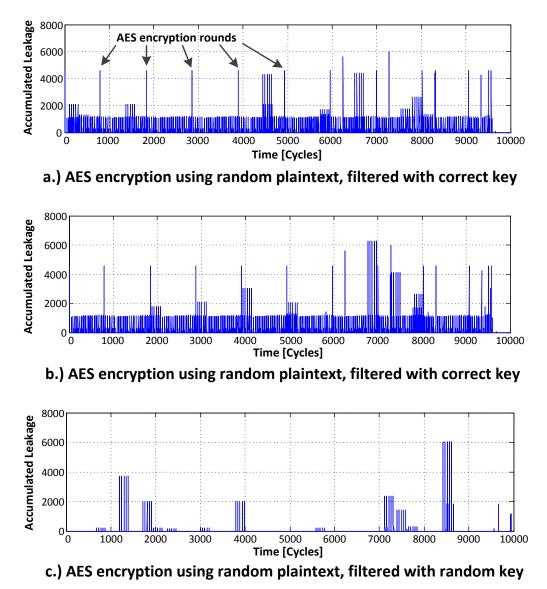

| 4.7          | Leakage sensor results for an AES software implementation - Obtained with modi-                                                                                                                                                                          | -  |

|              | fications from [7]                                                                                                                                                                                                                                       | 33 |

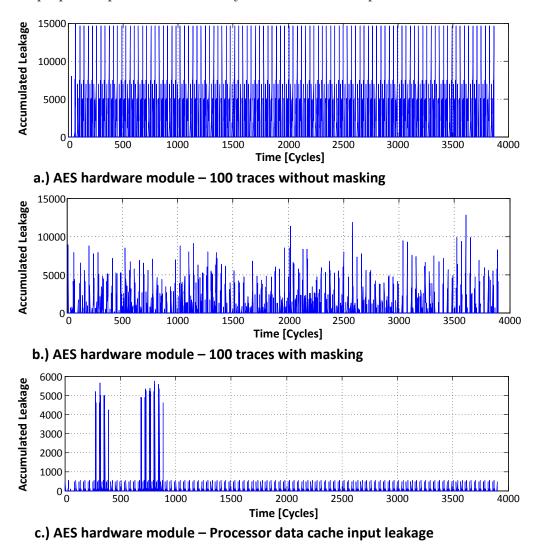

| 4.8          | Leakage sensor results for an AES hardware implementation - Obtained with mod-                                                                                                                                                                           |    |

|              | ifications from [7]                                                                                                                                                                                                                                      | 34 |

| 4.9          | Mapping of memory attack scenarios onto an FPGA-based software verification                                                                                                                                                                              |    |

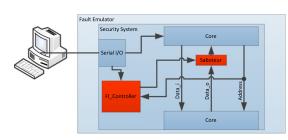

|              | system - Obtained with modifications from [13]                                                                                                                                                                                                           | 35 |

| 4.10         | Evaluation architecture for the software verification of automotive implementations                                                                                                                                                                      |    |

|              | - Obtained with modifications from [14]                                                                                                                                                                                                                  | 36 |

| 4.11         | Evaluation of various reduced hash algorithm implementations, depending on dif-                                                                                                                                                                          |    |

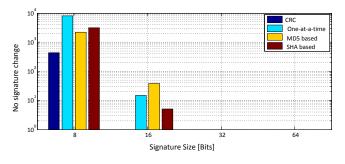

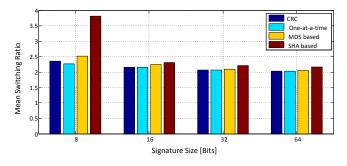

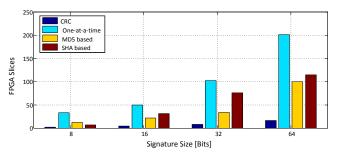

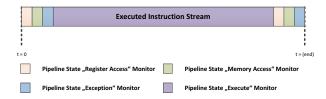

|              | ferent signature sizes - Obtained with modifications from [9]                                                                                                                                                                                            | 38 |

| 4.12         | Signature-based on-line monitoring architecture for a processor pipeline - Obtained                                                                                                                                                                      |    |

|              | with modifications from [10]                                                                                                                                                                                                                             | 40 |

| 4.13         | Full system checking architecture - Example implementation for the LEON3 system-                                                                                                                                                                         |    |

|              | on-chip - Obtained with modifications from [10]                                                                                                                                                                                                          | 40 |

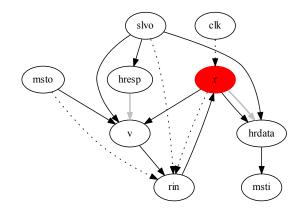

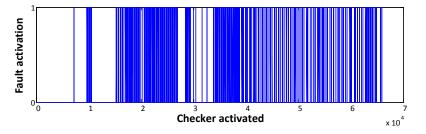

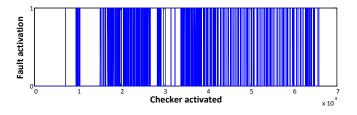

|              | Dependencies for an attacked circuit node - Obtained with modifications from $[8]$ .                                                                                                                                                                     | 42 |

| 4.15         | Checker results for a specific attack point - Obtained with modifications from $[8]$ .                                                                                                                                                                   | 42 |

| 6.1          | Publication overview concerning a comprehensive system-on-chip evaluation method-                                                                                                                                                                        |    |

|              | ology for secure software and hardware implementations                                                                                                                                                                                                   | 48 |

# List of Tables

| 4.1  | Long-time attack run using an commercial verification platform | 35 |

|------|----------------------------------------------------------------|----|

| 4.2  | Fault injection into Ethernet communication results [14]       | 36 |

| 4.3  | Fault injection into Ethernet controller memory results [14]   | 37 |

| 4.4  | Fault injection into embedded processor memory results [14]    | 37 |

| 4.5  | Evaluation of embedded processor self-test procedures [14]     | 37 |

| 4.6  | Resource usage comparison [9]                                  | 39 |

| 4.7  | Characterization results [10] - Instruction/Signature Pairs    | 41 |

| 4.8  | Resource usage comparison on the LEON3 platform [10]           | 41 |

| 4.9  | Fault detection efficiency comparison [10]                     | 41 |

| 4.10 | Checker evaluation result for a single attacked node [8]       | 43 |

# List of Abbreviations

| ACM                  | Association for Computing Machinery                              |

|----------------------|------------------------------------------------------------------|

| AES                  | Advanced Encryption Standard                                     |

| API                  | Application Programming Interface                                |

| ASIP                 | Application-Specific Instruction Processor                       |

| BDD                  | Binary Decision Diagram                                          |

| CAN                  | Controller Area Network                                          |

| CMOS                 | Complementary Metal Oxide Semiconductor                          |

| CRC                  | Cyclic-Redundancy-Check                                          |

| DES                  | Data Encryption Standard                                         |

| FPGA                 | Field Programmable Gate Array                                    |

| FSM                  | Finite-State Machine                                             |

| HDL                  | Hardware Description Language                                    |

| HW                   | Hardware                                                         |

| IDE                  | Integrated Development Environment                               |

| IP                   | Intellectual Property                                            |

| IEEE                 | Institute of Electrical and Electronics Engineers                |

| ITRS                 | International Technology Roadmap for Semiconductors              |

| LUT                  | Look-Up Table                                                    |

| MBU                  | Multi-Bit Upset                                                  |

| MPSoC                | Multi-Processor System-on-Chip                                   |

| NoC                  | Network-on-Chip                                                  |

| NVM                  | Non-Volatile Memory                                              |

| $\mathbf{PE}$        | Power Emulation                                                  |

| RFID                 | Radio Frequency Identification                                   |

| RAM                  | Random-Access Memory                                             |

| ROM                  | Read Only Memory                                                 |

| RSA                  | Rivest-Shamir-Adleman Public Key Cryptography                    |

| RTL                  | Register Transfer Level                                          |

| SER                  | Soft Error Reliability                                           |

| SEU                  | Single Event Upset                                               |

| $\mathrm{SMV}$       | Symbolic Model Verifier                                          |

| $\operatorname{SoC}$ | System-on-Chip                                                   |

| $\operatorname{SMP}$ | Symmetric Multi-Processing                                       |

| SPARC                | Scalable Processor Architecture                                  |

| SPICE                | Simulation Program with Integrated Circuit Emphasis              |

| SW                   | Software                                                         |

| VHDL                 | Very High Speed Integrated Circuit Hardware Description Language |

| WCET                 | Worst-Case Execution Time                                        |

WCET Worst-Case Execution Time

# Glossary

#### **Control State Based Fault Detection**

The term *control state based fault detection* has been artificially formed from the commonly used concept *control flow checking* [15, 16] and the concept of *processor fingerprinting* as described in [17]. This technique uses checkpoint signatures of the current processor state, hence, such hashes allow to check if the system behaves correctly compared to a given reference. The latter principle is not generic enough for the purpose of this work, as it is only applicable to modular-replicated processors running in lock-step mode or by comparing with long pre-recorded signatures.

#### Multiprocessor Systems-on-Chip (MPSoC)

The term *multiprocessor systems-on-chip* (MPSoC) has been used in recent years to describe complex heterogeneous chip implementations combining the advantages of data processing parallelism of *multi-processors* and high-level integration of *systems-on-chip* [18, 19]. The large scale introduction of these multi-functional devices enabled many functionalities common in today's smart-phones (i.e. multi-protocol communication, audio and video codecs etc.).

#### Efficiency

The term *efficiency* has to be substantiated depending on the field it is applied to. Concerning fault detection, *detection efficiency* specifies the ability to detect a fault during run-time. *Power efficiency* describes a system's capability to regulate its power consumption and to utilize available resources in an effective way. If system performance is concerned, *efficiency* means the ability to execute a given program using available resources in an effective manner.

#### Information Leakage

The term *information leakage* means the dependency of the power profile on processed data. This direct or indirect dependency could lead to the leakage of internal information to the outside, if an external person applies profile-processing techniques.

#### Fault

A *fault* constitutes a deviation of normal internal system states or signals. Such deviation could lead to the generation of wrong results, but it could also be masked by the current system state.

#### Error

An *error* describes a deviation from the expected system behavior caused by a fault. Therefore, an error is a final consequence after a fault was activated and the result is stored by internal or external resources.

#### Deep-submicron process technology

Commonly the expression *deep-submicron process technology* is used for manufacturing processes using transistor channel lengths smaller than 0.18um. Such a distinction was necessary as scaling below this size resulted in increasing problems concerning process variability, leakage power and signal integrity.

# Chapter 1 Introduction

### 1.1 Motivation

As of today, since the introduction of the latest smart-phones, we are all living in a mobile world. Regardless of our current local position, we are able to communicate with everyone who is also connected to one of the many open communication channels. This was mostly made possible by the semiconductor design, verification, and manufacturing industry that enabled the ongoing validity of moore's law.

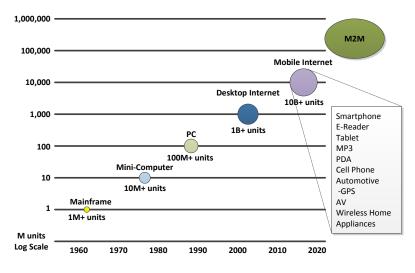

Figure 1.1: Dawn of the Machine-to-Machine (M2M) Age (adapted from [1]) - the development of the mobile device market is far from over, M2M communication will further increase the number of mobile devices sold

Billions of mobile devices are already sold world-wide, with increasing numbers every year. The now gradual introduction of  $IPv6^1$  will boost these markets even more in the near future, enabling *machine-to-machine* (M2M) communication (see Figure 1.1).

This development introduced a variety of new challenges for system designer, especially

<sup>&</sup>lt;sup>1</sup>Internet Protocol version 6, extending the addressing capability of the Internet protocol version 4 significantly to  $2^{128}$  devices

concerning power-aware and fault-aware design. First, while research made a continuing increase in integration density of integrated circuits possible, mobile power sources improved much slower. This development gap made the introduction of various power estimation (during design) and management (during operation) techniques necessary to efficiently use finite power sources. Second, deep sub-micron semiconductor processing technologies, necessary to integrate billions of transistors in small energy efficient devices, increasingly reach the physical limits of atomic barriers. Besides increasing manufacturing and testing challenges, long-term reliability is a concern in modern devices suffering from device degradation effects like *negative bias temperature instability* (NBTI). Third, a variety of mobile devices is now involved in the processing of critical personal data. In 2012, over seven billion smart secure devices will be shipped, with annual growth rates of up to 20 percent [20]. These gigantic markets and the increasing complexity of the involved devices call for ever improving hardware and software co-design, verification, and test support.

#### David and Goliath - Design Challenges of the Large and Tiny 1.1.1

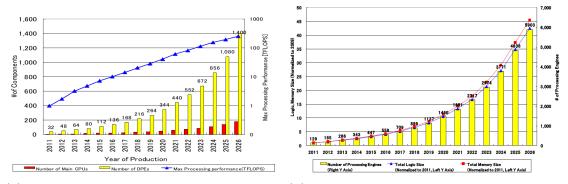

Recent years showed an increasing usage of specialized hardware and multi-core processors. This development was driven by the need for higher operation performance while classic energy sources did not develop as quickly. Also the introduction of the green com*puting* idea, made the design of highly energy-aware systems for data-centers necessary. In case of system-on-chip implementations, the semiconductor industry publishes forecasts concerning design and market challenges. In Figure 1.2 such developments of the *inter*national technology roadmap for semiconductors (ITRS) concerning system heterogeneity and complexity are depicted. Figure 1.2a shows the non-linear growth in system components during the following years. It can be seen that the usage of classic central processing units (CPUs) is not growing as strongly as dedicated processing elements (DPE). The reason for that is that dedicated hardware can solve specific problems much more efficiently than generalized hardware can. This is true for both, operating performance and energy efficiency.

(a) Heterogeneity for large stationary com- (b) The complexity of mobile system-on-chip deputing systems [2]

signs [2]

Figure 1.2: Market developments in stationary and portable systems concerning complexity, performance, and implementation effort, according to the ITRS

In Figure 1.2b the complexity of future mobile-systems is presented. Here, it is clearly visible that such portable system-on-chips increase non-linearly in complexity, while energy sources are only improving slowly. Therefore, every part of such complex system-inchips has to be optimized for their power consumption. To guarantee a certain level of reliability of such systems, including their large in-chip communication networks like *network-on-chips* (NoCs), system-level fault detection and management mechanisms have to be provided.

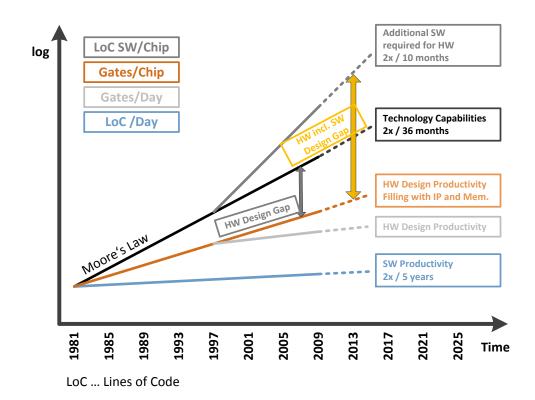

Figure 1.3: The gap between software, hardware design productivity, and required firmware is continuously widening if no countermeasures are taken in time (adapted from [2])

The semiconductor and system industries also have to solve various challenges concerning the software/hardware co-design process. In Figure 1.3 a disturbing development in recent years is depicted, that will worsen in future years if no solutions are found. In this figure, it can be seen that while technology capabilities (according to Moore's law) double every 36 months, hardware design productivity improved much slower. Only concerning hardware development, this challenge has been partially mastered by reusing *intellectual property* (IP) blocks and memory-based techniques. On the other hand, software productivity evolves even slower and, at the same time, these complex systems rely on ever more software to control this hardware (doubling every 10 months). This leads to a strongly opening shear between the demand for software and hardware, and the ability to provide these. Only interdisciplinary approaches, for example the introduction of software product line engineering and the wider usage of system-describing languages that can be compiled into hardware, will be able to reduce this challenge.

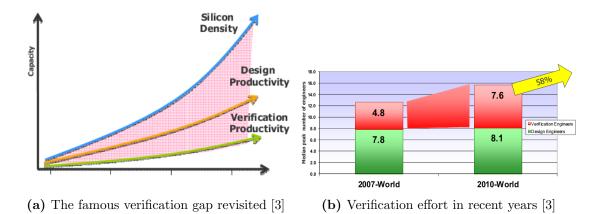

Figure 1.4: Challenges concerning the verification of future complex systems according to Mentor Graphics

Another urgent challenge in the implementation of large heterogeneous system-onchips concerns test and verification. Already in 1999, the SEMATECH industry consortium published data concerning the so called "verification gap", meaning the increasing challenge to verify large systems. In 2011, Mentor Graphics showed that this gap is still, even after the growing introduction of formal methods, widening as shown in Figure 1.4a. This situation led to an increasing demand for verification engineers while the demand for design personnel was stagnating (visualized in Figure 1.4b). This increase in verification effort was mostly driven by functional verification, hence, the validation of requirements concerning power consumption and fault-robustness have to be supported in the coming years to counteract the widening of this verification gap.

#### 1.1.2 Power- and Fault-Awareness in Modern System-On-Chip Designs

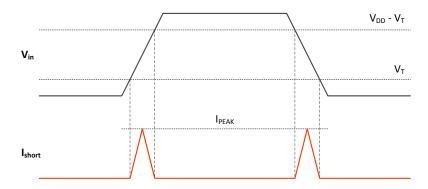

As described in previous paragraphs, the complexity of modern SoC implementations is increasing tremendously and power-awareness has already been a strong challenge in recent years. One major step towards system energy efficiency was the stop to the frequency race and the large scale introduction of parallelism into consumer products. Integrated cores or functional units can be completely deactivated during run-time if they are not currently needed. This was made possible by advances in recent years concerning techniques like *clock and power gating* as shown in [21] and *dynamic voltage and frequency scaling* (DVFS) as described in [22]. These techniques all work on a global scale, meaning they reduce consumption by manipulating architectural contributers.

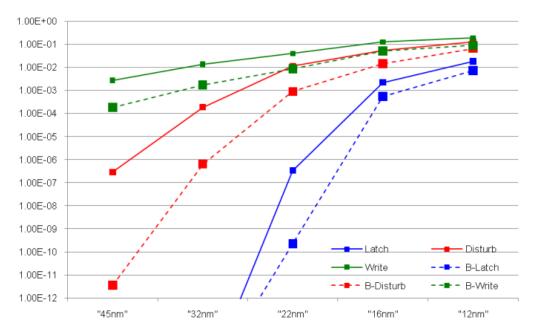

The recent increase in implementation density has been mostly driven by the continuing shrinkage of semiconductor technology nodes. While small transistor sizes have a positive effect on power consumption (except leakage power, which is dramatically worsening if no manufacturing techniques like *silicon-on-insulator* (SOI) are used) and available chip space, thinner isolation and shorter transistor channels introduced tremendous reliability problems. Besides faster device aging, manufacturing variability is affected by the demands of modern deep sub-micron processes. To emphasize how strongly this factor is worsening, current data and a forecast for future process nodes is depicted in Figure 1.5.

Figure 1.5: Manufacturing variability is strongly worsening for deep sub-micron technologies, according to [2]

This development led to a wide variety of research concerning fault detection, recovery, and fault-robust devices such as [23]. However, on a system-level duplication is still the first choice for high-reliability implementations, specifically triple-module-redundancy. Therefore, novel strategies for such system-level techniques, that do not rely on duplication, and the evaluation concerning their power-awareness, are strongly needed.

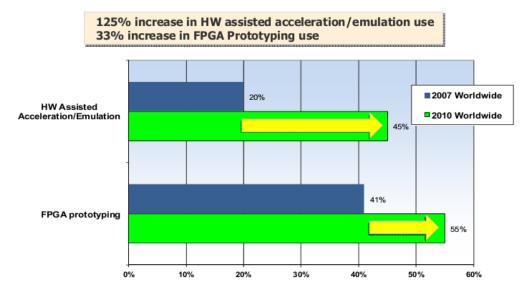

#### 1.1.3 Hardware-Accelerated Emulation for Software Verification

Traditional simulation techniques to verify software/hardware co-designs are increasingly suffering from performance bottlenecks and therefore, limit their usability in the design flow. This situation led to the increasing usage of hardware assisted emulation or FPGA prototyping as depicted in Figure 1.6.

These techniques can be divided into several subgroups depending on their application in the design process and the system abstraction. For this work we will identify two major fields:

• Mapping of hardware implementations onto hardware accelerated evaluation platforms and systems. Depending on the size and abstraction of the system implementation, single FPGAs or large reconfigurable logic clusters are used. This approach has the advantage that even finalized netlists can be verified for their correctness without any influence of the applied test hardware. Otherwise, large FPGA clusters can only provide investigations at low clock rates. There is an additional problem of trust, if such platforms should be provided to external parties, for example software providers. • System or hardware descriptions are extended with additional structures to allow for internal monitoring or manipulation during run-time. The design is directly optimized for the target platform, therefore it is not completely equivalent to a real final implementation. The main advantage is the strict separation between hardware and software using defined interfaces. Therefore, such evaluation platforms can also be provided to external parties when the used netlists are encrypted.

Figure 1.6: Usage trends for hardware-accelerated emulation during system design and verification, according to [3]

While the first field has been researched very thoroughly in recent years (for example [24]), instrumented verification platforms for software/hardware co-verification have only been covering selective implementation challenges. For example instrumented emulation for fault testing as shown in [25], software verification for power consumption as presented in [26], or variability emulation as introduced in [27]. To the best of our knowledge, there is no comprehensive approach providing all this information inside one evaluation platform, also considering challenges of trust and security available in literature.

## 1.2 Control-State-Based Fault Detection and Analysis in Multi-Processor System-On-Chips

#### 1.2.1 The POWER-MODES Project

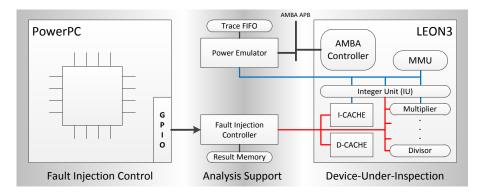

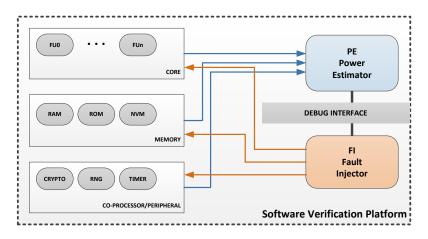

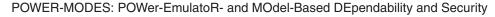

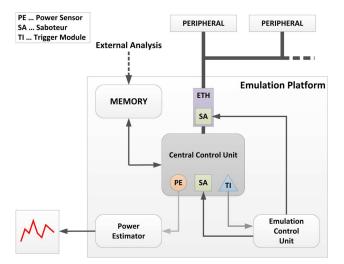

This thesis is part of the "**POW**er **E**mulato**R** and **MO**del based **DE**pendability and **S**ecurity evaluation platform" (POWER-MODES) collaborative research project<sup>2</sup>, shared between the Institute for Technical Informatics at the Graz University of Technology, Infineon Technologies Austria AG, and AustriaCard GmbH. This combined effort targets the combination of early power estimation and fault injection techniques into a single software verification platform as depicted in Figure 1.7.

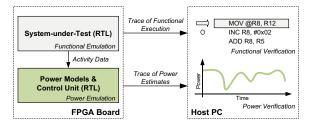

Figure 1.7: The POWER-MODES project - Tackling power-aware and fault-aware software evaluations concurrently using a single hardware-accelerated emulation platform (adapted from [4])

The POWER-MODES approach covers four main fields of research: *hybrid fault and* power emulation, optimization of fault detection and recovery techniques, comparative analysis of power-effectiveness versus detection effectiveness, and fault-attack resistant operating system, design. This work will concentrate on the first two topics, enabling a hybrid emulation system combined with the exploration of novel detection and recovery techniques.

$<sup>^2 \</sup>rm Funded$  by the Austrian Federal Ministry for Transport, Innovation, and Technology under the FIT-IT contract FFG 825749.

#### 1.2.2 Problem Statement

Large heterogeneous system-on-chips as well as resource-constrained systems used in security-critical and safety-critical applications demand significant optimization and verification effort. State-of-the-art hardware/software co-design flows have not been developed with these corner cases in mind and therefore, the following deficiencies can be identified:

- Traditional fault detection techniques provide local detection

- Power efficiency of fault detection mechanisms are scarcely researched

- Lack of early evaluation techniques for the testing of power-awareness and faultawareness

- Lack of information-leakage estimation during secure software verification

- Simulation-based investigation flows demand high computational effort

- Lack of static analysis methods leads to a large evaluation space and missing knowledge about the system-internal process during faults

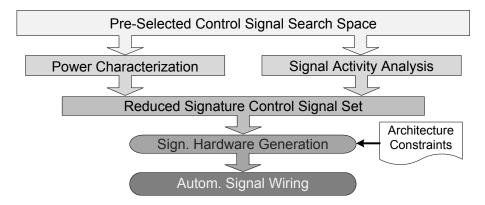

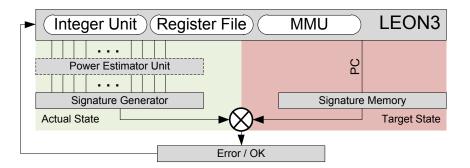

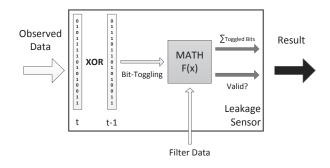

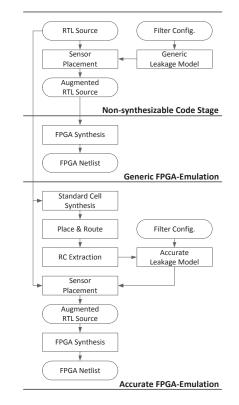

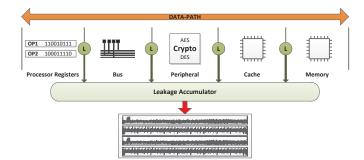

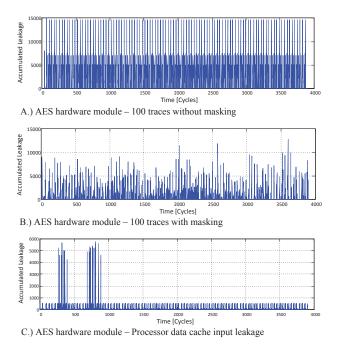

These limitations have been addressed by the combination of existing hardware accelerated evaluation techniques and novel estimation and detection methodologies. Signaturebased mechanisms are introduced to provide system-level fault detection capability that is highly scalable depending on detection and power requirements. Early evaluation of power consumption and information leakage during the software verification process is tackled by a novel data-aware emulation methodology. Hence, the presented signature-based detection mechanisms can also be evaluated for their power consumption effort.

This thesis also introduces automatized techniques to integrate these new detection and evaluation mechanisms into system-on-chips and FPGA-based software verification platforms. The problem of investigation complexity is addressed by novel static analysis techniques. Furthermore, the similarity of design challenges in the security and safety domains have been considered.

#### **1.2.3** Contributions and Significance

In summary, this thesis provides contributions to the following fields:

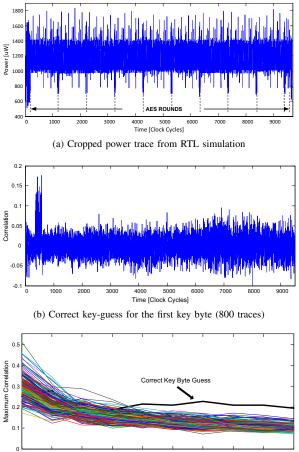

1. System-Level Control-State-Based Fault Detection: A fully automated process analysis hardware behavior for a given set of benchmark applications. The introduced methodology allows for the selection of significant control signals to derive signatures of the system state. Resource-constrained systems are supported by a hardware characterization process to determine the signature generation quality of reduced hash implementations. Finally, control-state information is utilized to automatically generate hardware checker modules for run-time integrity checking. This novel approach enables signature-based on-line testing for both, large heterogeneous systems and resource-constrained designs. 2. Emulation-Based Analysis of Fault Induced Security and Safety Issues: The emulation framework, as introduced in this thesis, allows the concurrent evaluation of power-related, security-related, and safety-related issues in a single platform. The hardware-accelerated approach uses an abstracted programming interface to allow the direct integration of the presented techniques into standardized software verification systems. This novel combined methodology has been further extended with data-aware power sensors to enable the early estimation of information leakage for a given leakage intensity. The presented investigation techniques have been thoroughly tested using software implementations of the AES algorithm and safety self-test routines.

#### 1.2.4 Structure of the Work

The remaining parts of this work are organized as follows. In Chapter 2 the current state-of-the-art concerning power-estimation and fault-injection in hardware/software codesign methodologies is reviewed. This complex thematic field first has to be split into hardware-accelerated and simulation-based power-estimation for the early investigation of a program's power consumption. Second, FPGA-based fault-injection approaches are investigated, considering both security and dependability fields. Third, the static and dynamic evaluation of software and hardware, as part of the co-design process, is reviewed to connect all three investigation parts into a single verification system. Chapter 3 presents a novel methodology for the efficient evaluation of secure software implementations under fault conditions. Part of this approach is also the resource-saving integration of novel control-flow-based fault detection mechanisms into MPSoCs. Therefore, these techniques cover the complete hardware/software co-design process, from system evaluation to novel design possibilities to counteract detected deficiencies. Chapter 4 provides data from comprehensive evaluations that show the applicability of the previously introduced techniques. These results are generated using open available implementations of system-on-chip code bases to show the generality of the approach. In Chapter 5 the results of this thesis are concluded summarizing novel insights gained into secure system designs. Furthermore, an outlook into future work in this dynamic field of engineering is given. Finally, Chapter 6 presents a selection of publications on which this work is based. These give a deeper understanding of the implemented techniques and additional evaluation data generated during the POWER-MODES project.

# Chapter 2 Related Work

The comprehensive power-aware and fault-aware hardware/software co-design process presented in this work is built on three basic pillars: hardware-accelerated software verification techniques, fault detection in secure and dependable system-on-chips, and static system evaluation. These topics have been partially covered by many publications in recent years, improving the state-of-the-art for selective problems. Only both, the dynamic and static evaluation of the system-under-test can provide global coverage of the system security and dependability problem. The following section gives an overview about existing work in these three categories. Finally, a summary is given showing how this work improves the state-of-the-art in these fields, and how they are connected into a comprehensive approach.

## 2.1 Hardware-Accelerated Dynamic Verification Techniques

Dynamic verification of hardware and software has been researched for many years with different evaluation targets. Here, we will concentrate on three main topics: *emulation-based power estimation* to cover the power-awareness field, *power analysis techniques for software verification* including all early applicable measures to analyze the power consumption profile for information leakage, and *fault injection-based system analysis* covering approaches to test systems under the influence of operational faults. Concerning power estimation and characterization of computing devices, a thorough overview is given in [28].

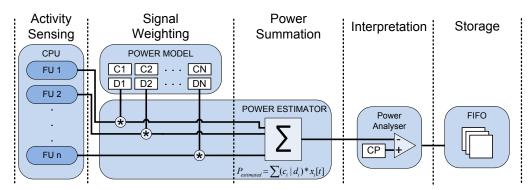

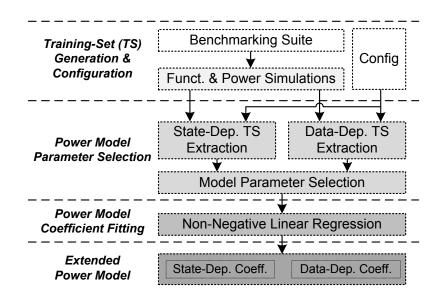

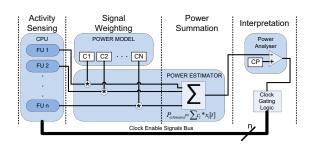

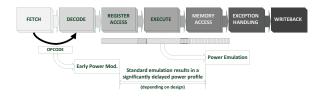

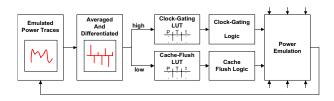

#### 2.1.1 Emulation-Based Power Estimation

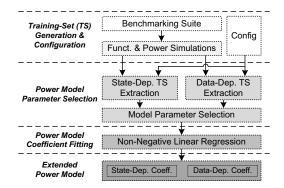

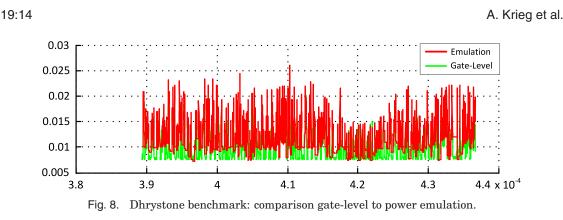

An overview on the basic principles of the power emulation technique is shown in [29]. This hardware-accelerated methodology provides run-time improvements of factor 10 to 500 compared to simulation-based power estimation approaches. Also strategies to minimize the hardware overhead caused by the emulation methodology are given in the presented work. This approach has been extended by the authors of [30] into a hybrid power estimation methodology for complex SoCs. The use of combined simulation and emulation techniques led to significantly reduced power consumption investigation times. The possibility of direct interpretation is a main advantage of hardware-assisted run-time power estimation. This has been exploited for the power-aware process migration between cores as shown in [31]. A real-time power profiling unit that can be directly integrated into FPGA-based software evaluation platforms has been presented in [26].

To allow for high estimation accuracy and low preparation effort, an automated systemon-chip characterization methodology has been introduced in [32]. The application of these novel early power estimation techniques for software power profiling has been further investigated in [33]. Another application is the evaluation of *dynamic voltage and frequency* scaling (DVFS) strategies as introduced in [34].

#### 2.1.2 Power Analysis Techniques for Software Verification

Depending on the abstraction level, information leakage can be estimated using a variety of different techniques. First, a purely software-based solution could be applied as introduced in [35]. Side channel leakage information is extracted from a given program by execution and tracing of instruction and processor states. Extensible analysis module are then used to process the resulting information. These analysis modules are directly implemented for the Microsoft Debugger API, integrating the functionality into the *integrated development environment* (IDE). Unfortunately, no information about accuracy and simulation performance has been given by the authors.

Second, instruction set simulators can provide in-system knowledge for power consumption estimation. Although, high simulation speeds can be reached using this approach, it is depending on data only available for thoroughly profiled general purpose architectures. Such methodologies have been presented in [36] and [37]. While not giving any hints about the accuracy of the used power profiles, both solutions promise high simulation speeds. In a case of badly estimated information leakage, a software engineer could be led into a sense of false security if this leakage is higher than anticipated. The work shown in [37] relies on several abstract power models to isolate possible sources of information leakage. As described earlier, well characterized general purposes processors are necessary for this approach. In this case, the AVR microcontroller series of Atmel has been chosen. Based on a performance simulator a comprehensive approach for power, area, and timing modeling has been taken in [38].

Third, highly accurate gate-level or even transistor-level simulations can be applied to identify critical parts of a system-under-test. High costs in terms of simulation speed and needed simulation equipment are the price of such estimation accuracy. Therefore, a system designer has to decide whether to choose between very short simulation times or the isolated evaluation to the smallest possible leakage contributer. As it is of utmost importance to know if an adversary could extract information using a high number of power traces, the first choice can be considered infeasible. Highly accurate analog simulations using SPICE simulators have been used in the following work: [39]. *register transfer level* (RTL) simulations as presented in [40] can be also used to improve simulation speed. Furthermore, it has been noted by the authors of [40] that RTL simulations could hide information leakage that will only be visible after later design flow steps.

#### 2.1.3 Fault Injection-Based System Analysis

The reliability of high-safety applications under the influence of faults is an important feature for which testing methods using fault injection have been introduced [41]. Depending on the design stage, faults can be injected into finalized parts e.g., using radiation, manipulation, or during earlier phases using adaptable prototyping approaches. These methodologies can be further divided into simulation-based and emulation-based techniques depending on the application of the evaluated models.

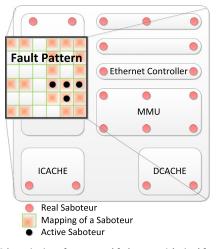

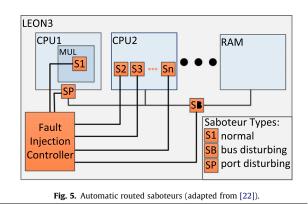

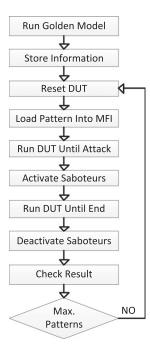

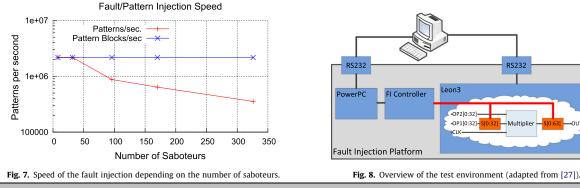

High-level hardware descriptions offer the possibility to be simulated directly during early design phases. This fact has been exploited by first non-invasive fault injection tools using logic simulation. During design concept phases, it could also be of interest to apply such injection methods using system-level description languages like SystemC as shown in [42]. Advances to simulation-based techniques have been introduced for the VFIT tool in [43]. Compared to previous work, the authors complemented this approaches with automatized saboteur and mutant insertion techniques. Furthermore, various injection performance improvements of simulation and emulation approaches have been shown in [44]. Recent work utilizes existing scan-chain infrastructure for high-performance processor reliability evaluations [45].

Higher fault injection coverage and therefore, higher evaluation performance could only be achieved by the introduction of hardware-accelerated emulation techniques. Such emulation methodologies promise significantly higher injection rates as presented in [25]. Therefore, a higher amount of possible fault configurations could be evaluated than using traditional simulation-based approaches. The introduction of novel FPGA devices featuring the possibility of run-time reconfiguration, without influencing the data- and control-flow, opened new possibilities for non-invasive fault injection. Since the introduction of these techniques several improvements concerning flexibility and performance have been introduced [24].

These approaches have been developed for dependability investigations, targeting mostly single event upsets (SEU). Multiple event upsets (MEU) need more complex emulation techniques, such as the extensive use of run-time reconfiguration as described in [24]. Such fault constellations are especially important for security evaluations as intentional faults could be injected at several positions at once. The complexity of today's security and safety systems often results in the separation of software and hardware development, done by different entities. This introduces a conflict of trust and intellectual property that has not been considered by previous work described in literature.

#### 2.2 Fault Detection in Secure and Dependable Systems

The detection of operational faults during the execution of critical software sequences has been a very active field of research for many decades. Such faults can be detected and managed on three different abstraction levels. In this work, we will concentrate on signature-based techniques: only on software-level using *software-based signature mechanisms*, on hardware-level using *hardware-based signature mechanisms*, and comprehensive techniques exploiting *hardware-software co-design solutions*.

#### 2.2.1 Software-Based Signature Mechanisms

Signature-based approaches on the software-level mostly rely on the automatic or semiautomatic generation of source-code signatures. These can then be used to detect changes in the program flow caused by adversarial tampering or environmental influences. Such signatures are directly embedded into the executed binaries, so for the checking procedure itself processor internal resources have to be reused. This will result in a severe increase of program run-time.

First software solutions have been relying on the usage of extensive redundancy. Another strategy would be the application of control-flow state checking to identify unforeseen execution behavior as introduced in [46] and [47]. A pure software signature-based approach, generating these signatures during compile time is proposed in [16]. These software-only approaches come with the big disadvantage of having a significant impact on execution performance (40 - 600% performance and memory overhead). Additionally, an adversary could manipulate these software checks if such techniques are implemented in security critical systems.

#### 2.2.2 Hardware-Based Signature Mechanisms

Hardware monitors have been the most commonly used hardware blocks for integrity checking for many decades. While monitoring capability can be implemented very efficiently depending on the monitored unit, this advantage could be annulled if pre-computed signatures are stored in large memories. Furthermore, the selection of the monitored system region is a not well covered field in the current state-of-the-art. For system-on-chip design's heterogeneous nature approaches that only cover a processor's pipeline are insufficient. The use of multiple monitors increases system complexity, decreases area efficiency and therefore, is also not well suited.

As the impact of the monitoring process on the execution performance has to be reduced, direct access to hardware resources is needed. Therefore, control flow-monitoring implementations using dedicated monitoring hardware have been presented. Early work concerning dedicated monitoring hardware have been watchdog-type modules such as [48] have been introduced. Another possibility would be the integration of smaller specialized monitoring circuits covering only selected parts of the system as described in [49] and [50]. While these techniques use an external view of the target, also approaches relying on a modification of a processor pipeline itself have been shown to enable the on-line evaluation of the control flow. As stated earlier these techniques are very effective when monitoring only processor applications, but are not sufficient for heterogeneous applications like system-on-chips that include various different processing units.

#### 2.2.3 Hardware/Software Co-Design Solutions

In recent years, various hardware/software co-design based approaches have been published to provide wide detection coverage. These techniques exploit the possibility to adapt both software support and hardware structure to reduce memory overhead and performance degradation. Predestined for such systems are *application-specific instruction processors* (ASIP) as described in several recent papers [51]. However, such methodologies can only be applied if the target architecture is either highly adaptable or the design process is at a very early stage allowing for strong interventions in existing development flows.

If such design flow changes are not possible, it is also possible to extend existing hardware to generate representative values to track control changes. For this purpose test infrastructure like scan-out-chains can be exploited like the approach presented in [52]. While the impact on the complexity of the targeted system is small, it relies on periodic tests and therefore, cannot be considered a real on-line testing solution. The same research group presented fingerprinting techniques based on hash-values generated from the architectural state [17]. This very accurate fault detection mechanism leads to high demands on circuit bandwidth because of the large amount of data collected from system components. Further improvements and extensions to this technique for large chip multi-processors have been presented in [53].

#### 2.3 Static System Evaluation

The increasing complexity of system-on-chip designs becomes a growing challenge for test and verification engineers. Therefore, static system information has to be utilized to decrease the evaluation space or to verify the implementation in a formal manner. This led to the increasing usage of formal methods in various parts of the design process: highlevel verification for security and safety domains, classic application of formal methods in hardware verification, static VHDL code analysis, and finally, fault propagation modeling.

#### 2.3.1 High-Level Verification for Security and Safety Domains

The implications of *loss of trust* (security) or *loss of life* (safety) led to the introduction of strong regulatory bodies in the security and safety engineering domains. In recent years, researchers in the safety engineering field spent a significant research effort on the verification of software implementations concerning their correctness and standard compliance. Model checking is a formal verification technique with the goal to determine whether a finite state machine (FSM) satisfies a set of specified criteria under all circumstances. If the criterion is not fulfilled, a counterexample for debug support is generated. This technique proved to be a powerful tool for such tasks. A comprehensive approach, using the NuSMV model checker including the consideration of fault injection, has been introduced in [54]. Nonetheless, the presented work is limited to software implementations and classic verification challenges like liveness or reachability properties. An efficient application of model checking to verify fault tolerance by using mutated models of sub-systems has been shown in [55]. For the application of formal methods to a secure software implementation flow, principal concepts have been introduced in [56, 57]. As abstraction is a challenge concerning RTL hardware descriptions, the presented techniques cannot be directly applied to hardware certification.

#### 2.3.2 Classic Application of Formal Methods in Hardware Verification

Disadvantages of dynamic verification can be counteracted by the application of static formal techniques to prove the correctness of a circuit using mathematical methods. These do not depend on signals, clocks, waveforms, or test patterns and therefore, do not suffer from large exploration spaces. For this work, we will concentrate on the model checking technique, as it has been shown to work well for the automatized verification of software implementations.