## Low Power Wireless Receiver Frontends for Sensor Network Applications

Dipl.-Ing. Markus Dielacher

Submitted as thesis to attain the academic degree "Dr. techn." at the

Graz University of Technology

Institute of Electronics

| Supervisor:    | UnivProf. DiplIng. Dr. techn. Wolfgang Pribyl                            |

|----------------|--------------------------------------------------------------------------|

| Co-Supervisor: | Prof. Dr. ir. Willy Sansen<br>(Katholieke Universiteit, Leuven, Belgium) |

Graz, May 2011

### **EIDESSTATTLICHE ERKLÄRUNG**

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen / Hilfsmittel nicht benutzt und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe.

Graz, am .....

.....(Unterschrift)

### STATUTORY DECLARATION

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

(date)

(signature)

iii

## Kurzfassung

Immer mehr Anwendungen, von der Kontrolle von Körperfunktionen und diversen Umweltparametern bis hin zu Funktionen im Automobil- und Flugzeugsektor basieren heutzutage auf Sensornetzwerken. Aufgrund dieses breiten Spektrums von Anwendungen können auch die Anforderungen an solche Netzwerke sehr unterschiedlich sein, je nachdem ob es sich um reine Komfortfunktionen handelt, oder um sicherheitskritische Anwendungen. Die Lebensdauer, und damit verbunden die Leistungsaufnahme, sind mitunter die größten Hürden in der Entwicklung von Sensorknoten, die an unzugänglichen Orten installiert werden, wo ein Austausch von Batterien schwierig oder unmöglich ist. In sternförmigen Netzwerken, in denen die einzelnen Sensorknoten lediglich Informationen senden, ohne Nachrichten zu empfangen, ist diese Problematik ein wenig entspannter. Die Sender sind die meiste Zeit in einem inaktiven Stromsparmodus, aus dem sie nur von Zeit zu Zeit erwachen, um eine Messung durchzuführen und die ermittelten Daten an einen zentralen Knoten zu senden. Dieser zentrale Knoten ist der einzige, der permanent aktiv auf eine Übertragung wartet und kann mithilfe einer leistungsstarken Energieguelle betrieben werden. Ganz anders sieht es in wirklich autonomen Sensornetzwerken aus. In solchen Netzen kann jeder Knoten Daten empfangen und an seine Nachbarn weiterübermitteln, bis sie schließlich an ihrem Bestimmungsort angelangt sind. Diese Arbeit beschreibt einen miniaturisieren Sensorknoten für Anwendungen im Automobilbereich, wobei der Schwerpunkt der Arbeit auf den Empfängerschaltungen liegt. Sowohl der Sender, als auch der Empfänger beruhen auf der Verwendung von sogenannten BAW Resonatoren zur Erzeugung einer Referenzfrequenz. Diese sind kleiner und robuster als herkömmliche Quarzkristalle. Dies ist wichtig, da die Überwachung des Reifendrucks als exemplarische Anwendung ausgewählt wurde. Im Gegensatz zu herkömmlichen Modulen zur Reifendruckkontrolle, die auf der Felge montiert sind, werden die in dieser Arbeit vorgestellen Sensorknoten direkt an der Lauffläche befestigt, wo sie enormen Beschleunigungen standhalten müssen. Daher sind auch die Abmessungen auf 1 cm<sup>3</sup> limitiert, um Gradienten in den einwirkenden Kräften aufgrund von Verformungen zu vermeiden. In dieser Arbeit wird die Architektur der Sensorknoten vorgestellt. Eine geeignete Empfängerarchitektur wird entwickelt, und ein rauscharmer Verstärker mit filternden Eigenschaften wird gezeigt. Diese Filterung erfolgt wieder mit BAW Resonatoren. Um eine ausreichend niedrige Leistungsaufnahme zu erzielen genügt es nicht, die einzelnen Schaltungen zu optimieren, auch die Kommunikatinonsprotokolle und Ablaufsteuerung müssen speziell für die Anwendung angepasst werden. In dieser Arbeit wird gezeigt wie mit der verwendeten BAW basierten Architektur die niedrigste Leistungsaufnahme erzielt werden kann. Schlussendlich werden einige Technologien vorgestellt, die verwendet werden um einen dreidimensionalen miniaturisieren Aufbau zu ermöglichen.

### Abstract

Today sensor networks are emerging in various fields, from fitness and health monitoring, environmental monitoring to automotive and aeronautic applications. Due to the broad range of applications, also the requirements may differ significantly, from safetycritical to pure comfort features. Lifetime and therefore power consumption are among the most important obstacles to overcome in order to establish sensor networks in hostile places where batteries cannot be replaced. This issue is a bit relaxed when star-topology networks are used where the individual nodes only transmit data according to a certain schedule and can be switched off most of the time. In those networks there is only one central node which is connected to a high capacity power supply and listening for incoming messages. In truly autonomous sensor networks however, each sensor node contains a receiver and a transmitter, such that it can receive messages and pass them on to other neighboring nodes. This work describes a miniaturized sensor node for automotive applications, focusing on the receiver architecture and circuits. The transmitter as well as the receiver in the developed sensor node use bulk acoustic wave (BAW) resonators instead of quartz crystals to generate the reference frequency and in the receiver those resonators are also used for filtering. The advantage of using BAW resonators instead of crystals is that they are more robust and smaller in size. This is important because as a first target application, tire pressure monitoring has been chosen. In contrast to conventional modules which are mounted on the rim, the developed sensor nodes are meant to be attached to the inner liner of the tire where they have to withstand extremely high accelerations. That is why also the size of the sensor nodes has been limited to 1 cm<sup>3</sup> in order to avoid force gradients due to device deformation. In this work the architecture of the sensor node is presented. A suitable architecture for the receiver frontend is developed and a low noise amplifier (LNA) with filtering capabilities is described. The filtering in the LNA is accomplished by integrating BAW resonators into the circuit. Measurement results are provided to enable comparison with state of the art solutions. In order to achieve a power consumption that is low enough for wireless sensor networks, not only the circuits have to be optimized, but also the communication protocols and the scheduling have to be tailored for the application. In this work it is shown how the benefits of the presented BAW based architecture can be exploited to achieve the lowest possible power consumption. Finally some technologies for 3D-integration are explained and it is shown how to achieve a sensor node that is smaller than 1 cm<sup>3</sup> including the power supply.

## Acknowledgements

This work has been carried out at Infineon Technologies Austria, Design Center Graz, within the research project e-Cubes, funded by the EU. I would like to thank my supervisors Prof. Wolfgang Pribyl and Prof. Willy Sansen. Special thanks go to Thomas Lentsch who provided the opportunity to carry out this research work within the professional environment of the department of Sense and Control at Infineon. The project has been coordinated by Thomas Herndl and Werner Weber who provided the playground for this research work, to try out new concepts and ideas, and who were always helpful in solving problems of any kind. To finally end up with a working demonstrator has only been possible because of the excellent teamwork of my colleagues and friends Josef Prainsack, Rainer Matischek, Martin Flatscher, and Hartwig Unterassinger who always provided a friendly and pleasant working atmosphere. And of course I would like to thank all other colleagues from the departments of SC and CRE at Infineon who were always helpful in discussing problems and finding solutions without naming all of them.

Markus Dielacher Graz, May 2011

## Contents

| 1 | Introduction         1           1.1         The e-Cubes Project         1           1.1.1         Wireless Sensor Networks in Cars         2                                                                                                                                            |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1.2 Application - TPMS       3         1.2 The eCubes Automotive Demonstrator       4         1.2.1 Constraints       4         1.2 Constraints       5                                                                                                                                |

| 2 | 1.3 Conclusion       5         Sensor Node Architecture       7         2.1 Demonstrator Generations       8         2.2 Conclusion       9                                                                                                                                              |

| 3 | The eCubes Transceiver113.1 Architecture113.2 Channel Properties123.3 Receiver Specifications and Link Budget133.4 Conclusion15                                                                                                                                                          |

| 4 | The eCubes Receiver Frontend174.1 eCubes Receiver Frontend Architecture174.2 Analog to Digital Conversion and Digital Processing194.3 Conclusion20                                                                                                                                       |

| 5 | <b>RF Filters</b> 215.1Working Principle215.2Equivalent Circuit215.3Filter Topologies215.4SAW235.5BAW235.6Key Features of Piezoelectric Resonators255.7Comparison between SAW and BAW Technology265.8Resonators in the eCubes Transceiver275.9Temperature Compensation285.10Conclusion30 |

| 6 | Input Matching         31           6.1         Matching         31                                                                                                                                                                                                                      |

|    | 6.1.1       Resistive Feedback       3         6.1.2       Common Gate       3         6.1.3       Inductive Source Degeneration       3         6.2       Resonant Circuit       3         6.3       Implemented eCubes Matching Network       3         6.4       Conclusion       3                           | 3<br>4<br>5<br>6                     |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

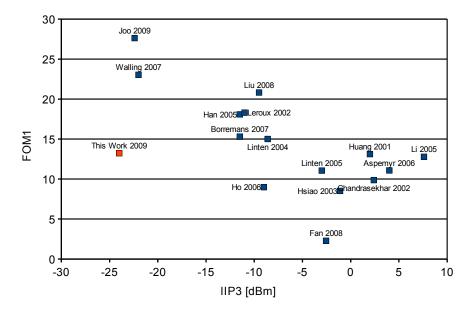

| 7  | Low Noise Amplifier (LNA)37.1LNA Circuit37.2Active Inductor47.3Source Follower with Feedback47.4Simulation Results47.5Figure of Merit57.5.1Comparison and Interpretation of the Results57.6Comparison with a Similar Reported Topology57.7Conclusion5                                                            | 9<br>2<br>5<br>6<br>0<br>2<br>5      |

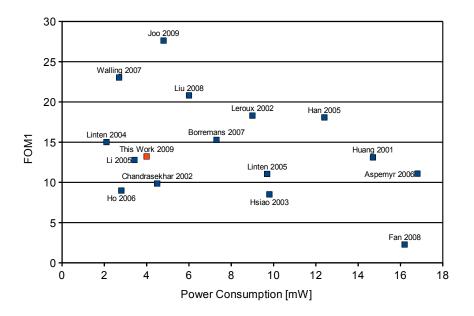

| 8  | Polyphase Networks (PPF)58.1Polyphase Networks58.2Dimensioning of a Polyphase Network58.3Conclusion5                                                                                                                                                                                                             | 7<br>8                               |

| 9  | Mixer and IF path         6           9.1         Mixer         6           9.2         IF Path         6           9.3         Conclusion         6                                                                                                                                                             | 1<br>2                               |

| 10 | Measurements610.1 Matching of LO and Filtering BAWs610.2 Measurement Setup610.3 Measurable Input Frequencies610.4 Gain, Image Rejection and Noise Figure610.5 Nonlinearity710.6 Limiter Sensitivity710.7 Bit Error Rate710.8 Interpretation of the Results and Comparison with State of the Art710.9 Conclusion7 | 6<br>7<br>8<br>9<br>2<br>3<br>3<br>4 |

| 11 | Power Supply of the eCubes Sensor Node711.1 Energy Harvesting711.2 Conclusion8                                                                                                                                                                                                                                   | 9                                    |

| 12 | Receivers in Multi Hop Sensor Networks       8         12.1 Wireless Sensor Networks       8         12.1.1 Calculating the Duty Cycle       8         12.1.2 Lower Limit of the Start-Up Time       8         12.2 Optimization of the Overall Power Consumption       8                                        | 1<br>2<br>4                          |

| в  | Bibliography                                                               | 107       |

|----|----------------------------------------------------------------------------|-----------|

| A  | Own Publications                                                           | 103       |

|    | 14.2 Novelties in the Presented Work       14.3 Summary of Published Works |           |

| 14 | Research Summary                                                           |           |

|    | 13.4 Conclusion                                                            |           |

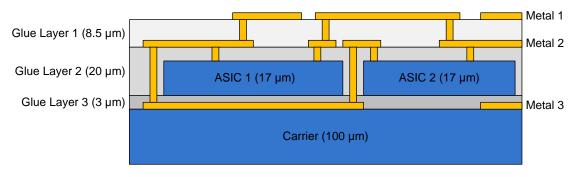

|    | 13.3.1 TSV Stack                                                           |           |

|    | 13.3 D3 - Stacked Versions                                                 |           |

|    | 13.2 D2 - MID Version no Stack                                             |           |

| 13 | <b>3D Integration</b><br>13.1 D1 - Functional Demonstrator                 | <b>91</b> |

|    | 12.5 Conclusion                                                            |           |

|    | 12.4 Power Management Unit                                                 |           |

|    | 12.3 Required Extension to the Presented Transceiver                       |           |

## Nomenclature

| μController | Microcontroller                            |  |

|-------------|--------------------------------------------|--|

| ABS         | Anti-lock Braking System                   |  |

| ADC         | Analog to Digital Converter                |  |

| AGC         | Automatic Gain Control                     |  |

| ASIC        | Application Specific Integrated Circuit    |  |

| В           | Bandwidth                                  |  |

| BAW         | Bulk Acoustic Wave                         |  |

| BER         | Bit Error Rate                             |  |

| BVD         | Butterworth-Van-Dyke                       |  |

| CHOSeN      | Cooperative Hybrid Objects Sensor Networks |  |

| CMOS        | Complementary Metal Oxide Semiconductor    |  |

| CPU         | Central Processing Unit                    |  |

| F           | Noise Factor                               |  |

| FOM         | Figure of Merit                            |  |

| FSK         | Frequency Shift Keying                     |  |

| IF          | Intermediate Frequency                     |  |

| IIP3        | Input Referred Third Order Intersept Point |  |

| ISM         | Industrial, Scientific, and Medical        |  |

| LDS         | Laser Direct Structuring                   |  |

| LF          | Low Frequency                              |  |

| LNA         | Low Noise Amplifier                        |  |

| LO          | Local Oscillator                           |  |

| MBVD        | Modified Butterworth-Van-Dyke              |  |

| MEMS        | Micro-Electro-Mechanical System            |  |

| MID  | Molded Interconnect Device                  |

|------|---------------------------------------------|

| NCO  | Numerically Controlled Oscillator           |

| NF   | Noise Figure                                |

| OIP3 | Output Referred Third Order Intersept Point |

| P1dB | 1 dB Compression Point                      |

| PCB  | Printed Circuit Board                       |

| PDC  | Park Distance Control                       |

| PLL  | Phase Locked Loop                           |

| PPF  | Polyphase Filter                            |

| Q    | Quality Factor                              |

| RAM  | Random Access Memory                        |

| RKE  | Remote Keyless Entry                        |

| ROM  | Read Only Memory                            |

| RSSI | Received Signal Strength Indicator          |

| RTC  | Real Time Clock                             |

| SiP  | System in Package                           |

| SMD  | Surface Mounted Device                      |

| SMR  | Solidly Mounted Resonator                   |

| SNR  | Signal to Noise Ratio                       |

| SoC  | System on Chip                              |

| SPI  | Serial Peripheral Bus                       |

| TPMS | Tire Pressure Monitoring System             |

| VCO  | Voltage Controlled Oscillator               |

| WSN  | Wireless Sensor Network                     |

# **List of Figures**

| 1.1<br>1.2<br>1.3                                                   | Miniaturization of a sensor node. Source: [101]                                                             |     | 1<br>3<br>4                      |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|----------------------------------|

| 2.1<br>2.2                                                          | Sensor Node                                                                                                 |     | 7<br>8                           |

| 3.1<br>3.2                                                          | The ecubes transceiver                                                                                      |     | 11<br>13                         |

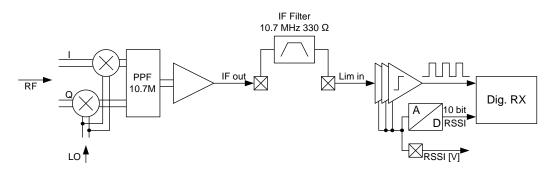

| 4.1<br>4.2                                                          | The ecubes receiver frontend                                                                                |     | 17<br>19                         |

| 5.1<br>5.2                                                          | Primitive model of a piezoelectric resonator                                                                | . : | 22                               |

| 5.3<br>5.4<br>5.5<br>5.6<br>5.7                                     | ture                                                                                                        |     | 24<br>24                         |

| 5.8<br>5.9                                                          | deviceMeasured temperature drift of a 2.1 GHz resonatorMeasured temperature drift of two 2.4 GHz resonators |     | 29                               |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10 | Equivalent Circuit of an Antenna                                                                            |     | 33<br>33<br>34<br>35<br>35<br>36 |

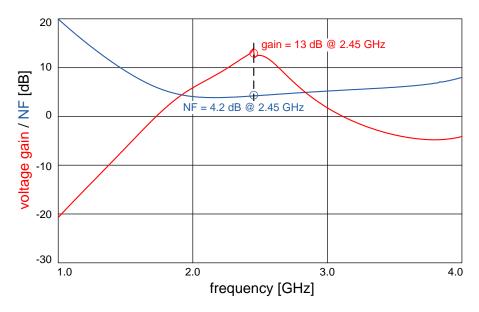

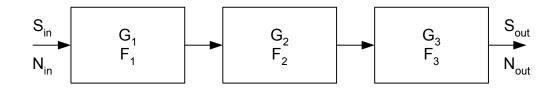

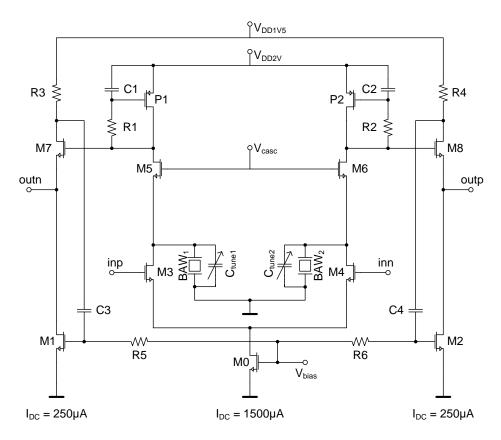

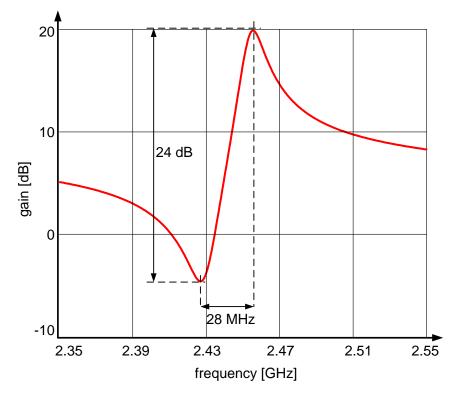

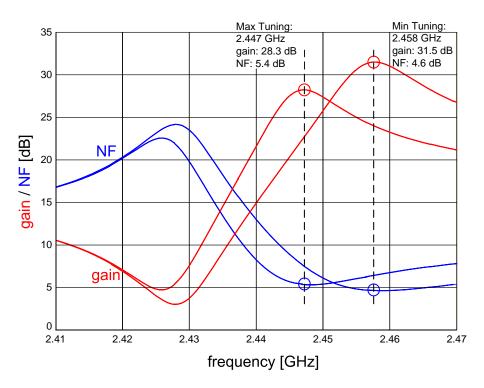

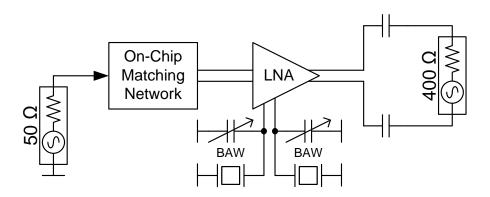

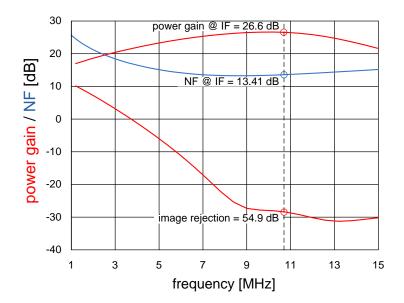

| 7.1<br>7.2<br>7.3                                                   | Noise figure of cascaded stagesLNA CircuitVoltage gain and image rejection of LNA including BAWs            | . ' | 40                               |

|                                                                     |                                                                                                             |     |                                  |

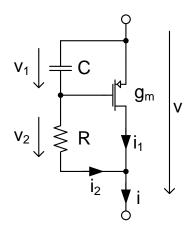

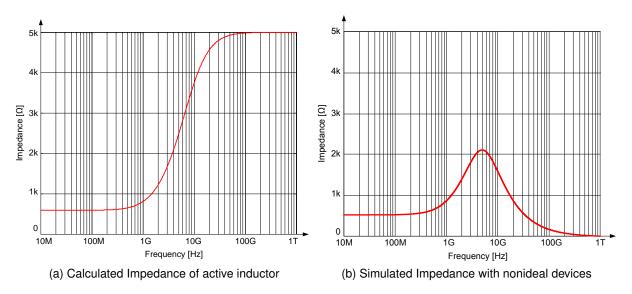

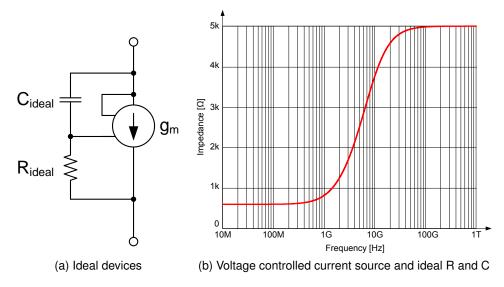

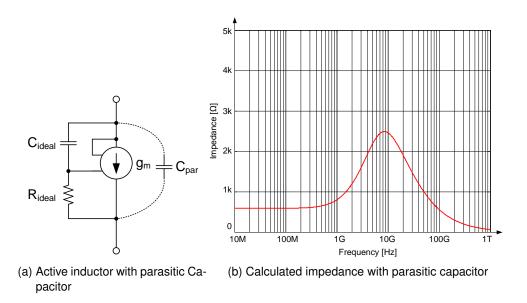

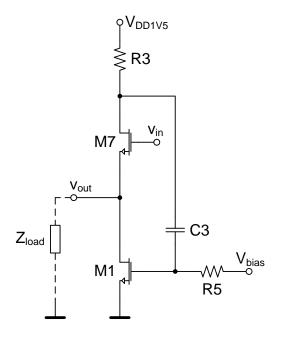

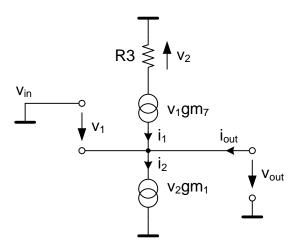

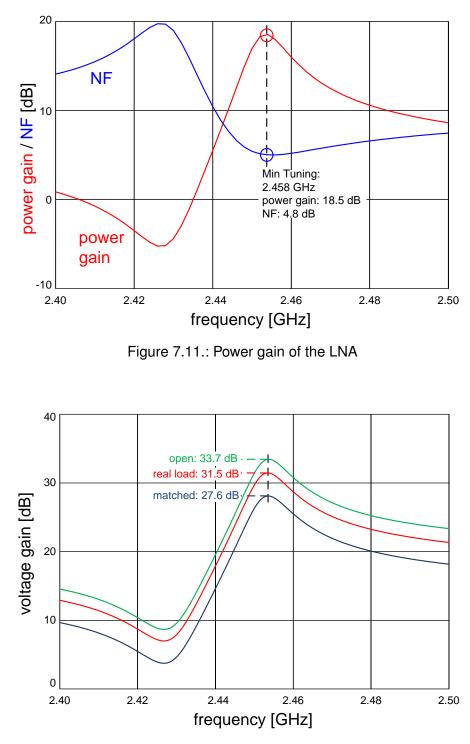

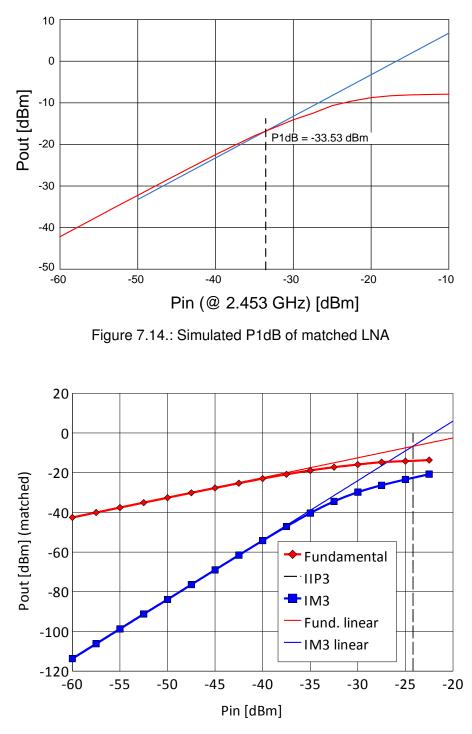

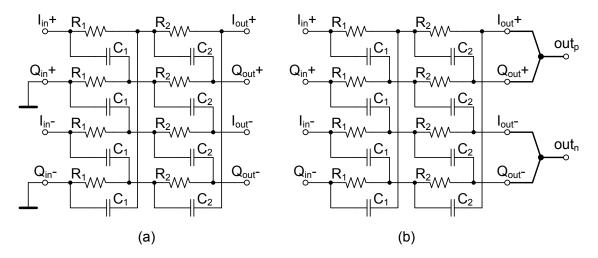

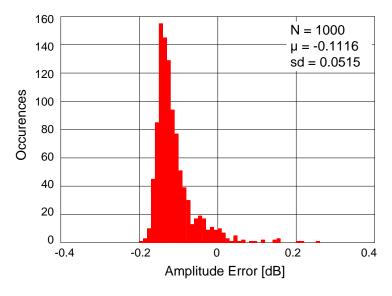

| 7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9<br>7.10<br>7.12<br>7.11<br>7.13<br>7.14<br>7.15<br>7.16<br>7.17 | Active inductor                                | 43<br>44<br>45<br>46<br>47<br>47<br>48<br>48<br>49<br>49<br>54 |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------|

| 8.1<br>8.2                                                                                             | Polyphase Network Configurations               |                                                                |

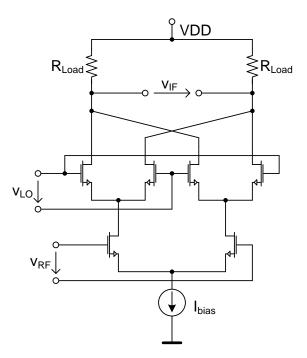

| 9.1<br>9.2<br>9.3                                                                                      | Gilbert mixer                                  | 62                                                             |

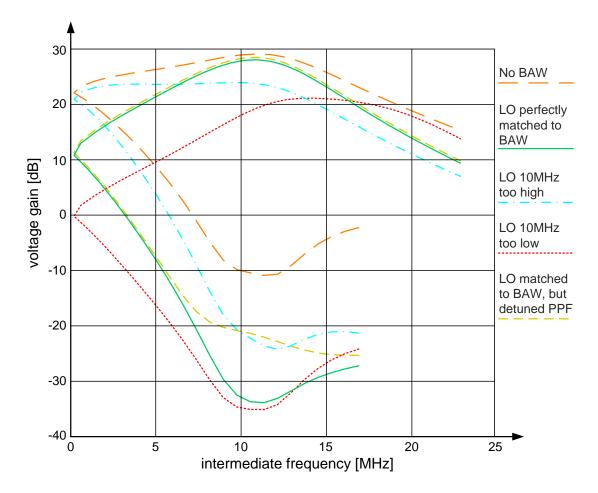

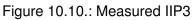

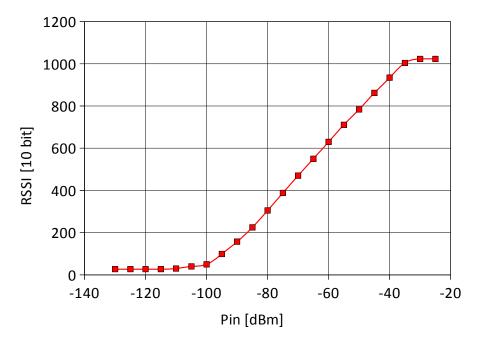

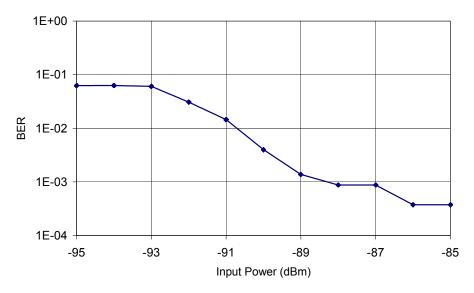

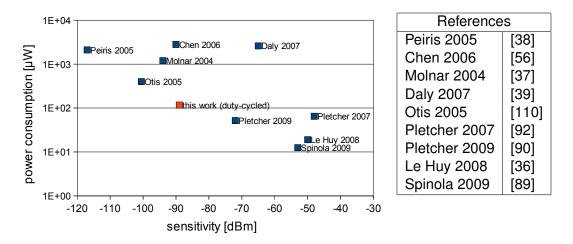

| 10.11<br>10.12                                                                                         | Effect of different mismatches on RX gain      | 67<br>68<br>69<br>70<br>71<br>71<br>72<br>72<br>73<br>74       |

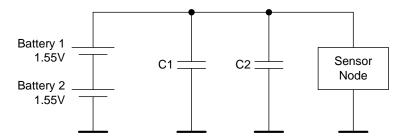

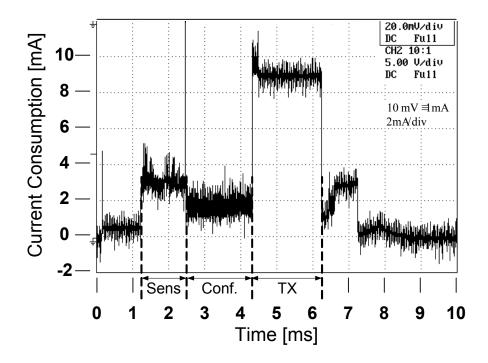

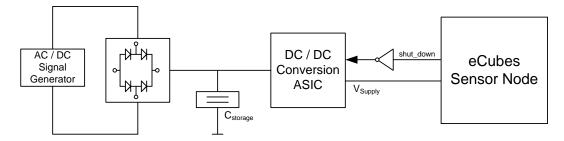

| 11.1<br>11.2<br>11.3<br>11.4                                                                           | Battery based power supply of the sensor nodes | 78<br>79                                                       |

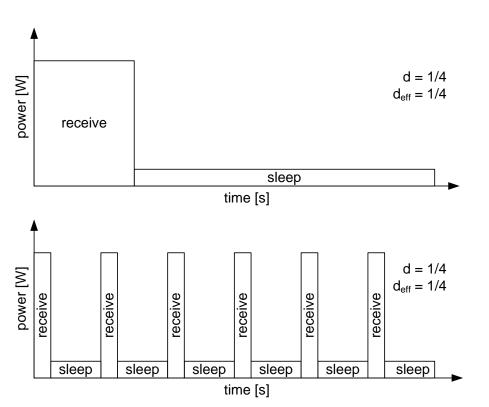

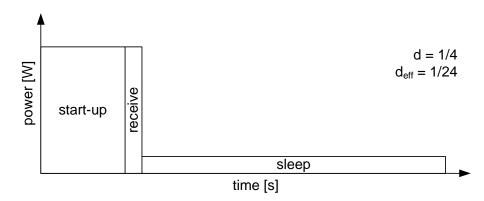

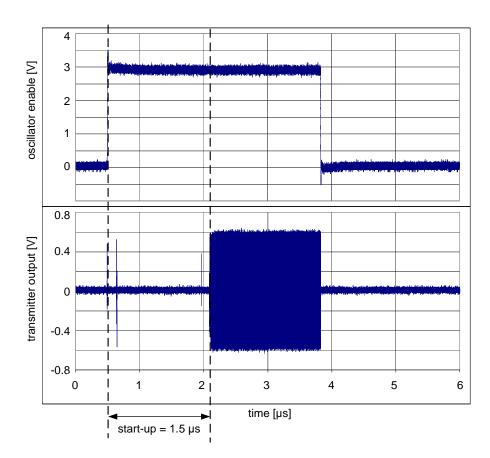

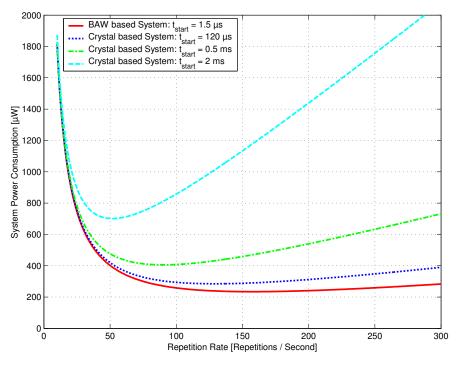

| 12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6                                                           | Duty cycle with different repetition rates     | 84<br>85<br>87<br>88                                           |

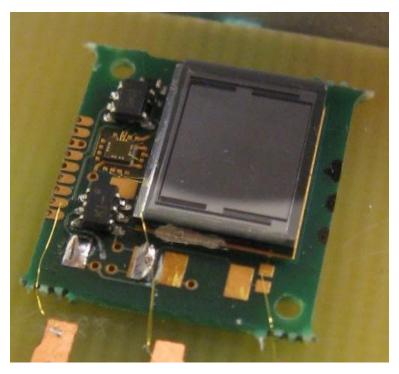

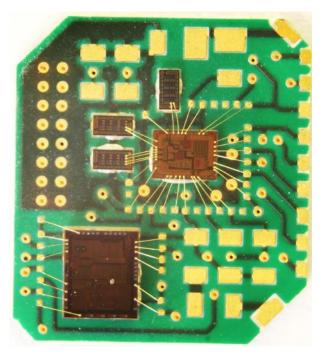

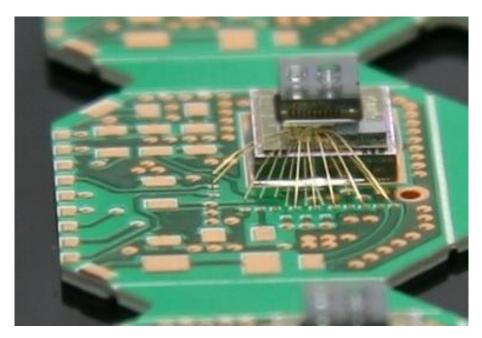

| 13.1  | D1 board                             | 91 |

|-------|--------------------------------------|----|

| 13.2  | D2 Demonstrator - Version 1          | 92 |

| 13.3  | D2 Demonstrator - Version 2          | 93 |

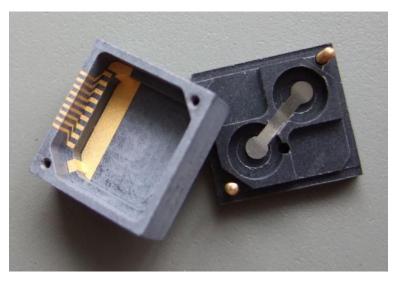

| 13.4  | Empty MID with Lid                   | 93 |

| 13.5  | MID with energy harvester pcb as lid | 94 |

| 13.6  | TSV process                          | 95 |

| 13.7  | TSV stack                            | 96 |

| 13.9  | UTCS process                         | 96 |

| 13.8  | Transparent MID, Source: SINTEF      | 97 |

| 13.10 | TCI stack                            | 97 |

| 13.11 | UTCS Stack with pads for SMDs        | 98 |

## **List of Tables**

| 3.1        | Specifications for the sensor node and for the receiver              | 14       |

|------------|----------------------------------------------------------------------|----------|

| 6.1        | Component values of the passive devices used in the matching network | 37       |

| 7.2<br>7.3 | Component values of the passive devices used in the LNA              | 42<br>53 |

| 8.1        | Component values of the 2.45 GHz PPF as shown in Figure 8.1a         | 58       |

|            | Comparison with reported receivers                                   |          |

|            | Transmitter and receiver parameters                                  |          |

## 1. Introduction

This work describes the architecture of a wireless sensor node for tire pressure monitoring with focus on the analog frontend and the low noise amplifier (LNA) of the employed receiver.

Figure 1.1.: Miniaturization of a sensor node. Source: [101]

Parts of this work have been published in journals, books, and conference proceedings. These publications are referenced in the text as [1] - [16].

### 1.1. The e-Cubes Project

The work has been carried out within the framework of the EU-funded FP6-project e-Cubes. The objectives of this project are to advance the micro-system technologies to allow for the cost effective realization of highly miniaturized, truly autonomous systems for ambient intelligence [101]. In other words the project targets at the development of wireless sensor networks (WSN). A WSN is defined as a number of devices communicating with each other and at least some of these devices sense some physical quantity in their environment. Common examples for these physical quantities are temperature, humidity, pressure, acceleration, sound, light, infrared, magnetic fields, radiation, location, chemical compositions and mechanical stress [98].

In order to achieve miniaturization of the sensor nodes, the different functional units of the node are meant to be organized in a vertical stack as shown in Figure 1.1. Three demonstration scenarios are targeted within the e-Cubes project: Health and Fitness, Aeronautics and Space, and Automotive applications. The automotive demonstrator which is focused in this work has been developed by Infineon Technologies Austria together with several academic and industrial partners.

#### 1.1.1. Wireless Sensor Networks in Cars

The number of electronic devices in today's cars is increasing steadily. Not only upper class cars, but also medium and small sized vehicles are affected by this trend. Most of these devices are connected via cables, however there is an increasing demand for wireless applications [105, 107, 108, 109]. One reason for this increase is that the large number of cables inside the car accounts for additional weight and fuel consumption. Today's cars contain more than 4 kilometers of wiring [106]. Although single wires for every device or application have already been replaced by sophisticated bus systems like the CAN bus, Byteflight or FlexRay, wireless sensor networks could increase the flexibility of a car's electronic system considerably. Another reason for using wireless links is, that in certain places it is simply not possible to attach cabled devices or sensors. For example in rotating structures wireless devices are much more convenient than cabled ones. In the future, wireless sensor networks will not only be used inside vehicles, but car to car communication and car to infrastructure communication will become more and more interesting [94].

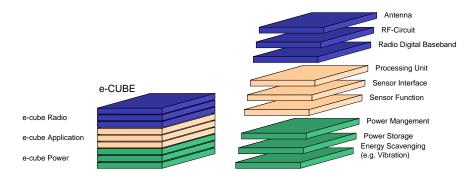

Tire pressure monitoring has been chosen as target application for the e-Cubes automotive demonstrator, because it is a typical example for a wireless sensor network which is already available in vehicles today. This sensor network is built up in a typical star topology. Wireless sensor nodes inside the tires transmit their data to a central unit which is located somewhere in the car and connected to the car battery. This sensor network can be extended by a number of additional devices, for example the electronic car key for remote keyless entry (RKE), which is also already a very common wireless automotive application today. In the future, also other sensing devices like park distance control (PDC), radar, light sensors or temperature sensors for the air condition could be included in this network and transmit their data through a wireless channel. The startopology which is used today could be replaced by ad-hoc multihop networks, however this imposes severe constraints on the power consumption of the wireless sensor nodes because this new architecture requires sensor nodes with receivers which are continuously listening into the channel. Different network topologies are shown in Figure 1.2.

The first network in Figure 1.2 (a) shows a typical star topology network for tire pressure monitoring. There is only one receiving sensor node, located in the dashboard and powered by the car battery. The sensor nodes inside the tires only include transmitters. The power consumption of the central node in the dashboard is not that critical, although it also has to stay below a certain limit, so as not to drain the car battery, even if the car is parked for several weeks. The power consumption of the nodes inside the tires on the other hand has to be extremely low, because their batteries cannot be replaced or recharged and they have to work for up to ten years [22].

The second network in Figure 1.2 (b) is a multihop network, where each sensor node contains a receiver and a transmitter. The measured data are passed from node to node to their destination via several hops. The advantage of this approach is, that the network can organize itself and it can be rerouted if a node is busy. With this approach, it is also possible to scale down the output power of the transmitters because the data can take several hops and do not have to be transmitted across the whole car in worst case. To enable such a network, a sophisticated power management is required in each sensor node.

Figure 1.2.: Topologies for Wireless Sensor Networks

The third network in Figure 1.2 (c) is a heterogeneous network. It consists of sensor nodes which only contain transmitters as well as sensor nodes with full functionality, also containing receivers. So the functionality and power consumption of each node can be scaled individually.

#### 1.1.2. Application - TPMS

State of the art Tire Pressure Monitoring Systems (TPMS) are modules which measure the pressure and acceleration inside the tire and transmit the data to a central unit in the car. These modules are mounted on the rim of the wheel using the valve as antenna [28]. There are TPMS modules available which also include a low frequency (LF) receiver with very low power consumption. Due to the low power consumption the LF receiver can be always on and act as a wakeup receiver. A transmitter unit in the car can then activate the TPMS modules by sending an LF signal. Other TPMS modules do not contain the LF receiver, they wake up from standby and perform their measurements according to a fixed schedule. Figure 1.3 shows a state of the art TPMS module. Another way of monitoring the tire pressure is to evaluate the data coming from the anti-lock braking system (ABS).

Figure 1.3.: TPMS module

Under-inflated tires will result in a higher rotation speed of the according tire, and this can be detected by the ABS. This indirect TPMS however is inferior to the direct pressure measurement in terms of accuracy and it only detects pressure loss of a tire relative to the other tires.

### **1.2. The eCubes Automotive Demonstrator**

This work describes a miniaturized sensor node for TPMS. In contrast to state-of-the-art TPMS the presented sensor nodes are designed for being mounted on the inner liner of the tire instead of the rim. This special mounting location allows sensing of additional data like side-slip, wheel speed, tire wearout, road condition, tire friction, and vehicle load. These data can be used for improved tracking and engine control, feedback to the power train, car-to-car communication purposes and safety features [1]. Also the developed sensor nodes include receivers in order to enable other network topologies than the standard star-topology.

#### 1.2.1. Constraints

Mounting a TPMS on the inner liner of a tire instead of the rim imposes severe constraints on the design. The required temperature range is from -40 °C to +125 °C. The acceleration caused by the circular movement of the tire can reach values higher than 1,000 g [28]. This value does not include the acceleration caused by vibrations or the impacts when the TPMS module hits the road surface. Including also these effects, acceleration peaks of 4,000 - 5,000 g must be taken into account [22]. Because of these high forces, the volume of the modules has to be below 1 cm<sup>3</sup> in order to avoid force gradients due to device deformation. The weight is limited to five grams including package and power supply. Not only because of the additional weight, power supply is a critical issue. Once the system is installed inside the tire, the power supply has to last for ten years. Batteries providing the required capacity and at the same time being small enough are not available today. New developments try to include energy harvesting devices into the module instead of batteries. A very promising approach is to use the vibrations inside a vehicle's tires to generate electrical energy. The power which can be delivered by vibrational energy harvesters with the desired dimensions is only in the range of up to 10  $\mu$ W [25, 24, 22]. So the power consumption of the TPMS modules has to be extremely low.

### 1.3. Conclusion

This chapter introduces the background of the thesis. The target is to develop a miniaturized sensor node for automotive wireless sensor networks. The application is described and the most important constraints are derived based on existing sensor nodes for TPMS. However the targeted sensor nodes clearly exceed state-of-the-art by:

- being mounted on the inner liner of a tire instead of the rim in order to gain additional information,

- reducing the size to below 1 cm<sup>3</sup>,

- being powered by energy harvesting devices delivering only a few  $\mu W$  of power, and by

- including a receiver and in this way enabling new network topologies.

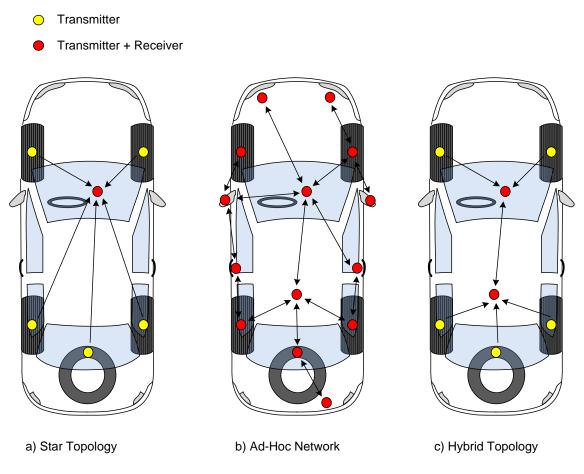

## 2. Sensor Node Architecture

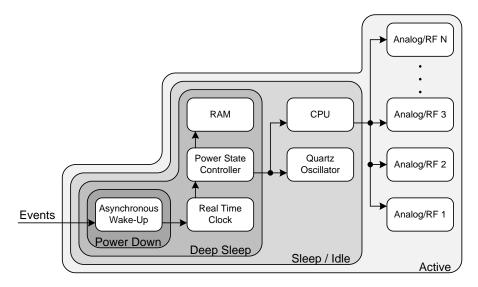

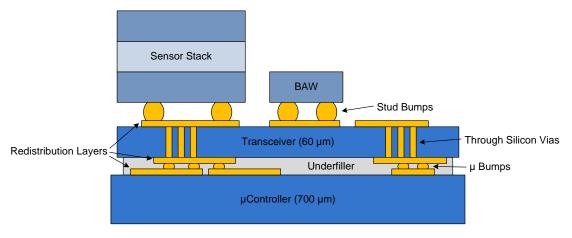

This chapter describes the architecture of the developed sensor nodes. More detailed descriptions can be found in [1] and [5]. The automotive demonstrator is a sensor node consisting of

- a microcontroller ASIC (µController),

- a sensor for pressure and acceleration, based on a micro-electro-mechanical system (MEMS)

- · a bulk acoustic wave (BAW) based transceiver,

- and a power supply module.

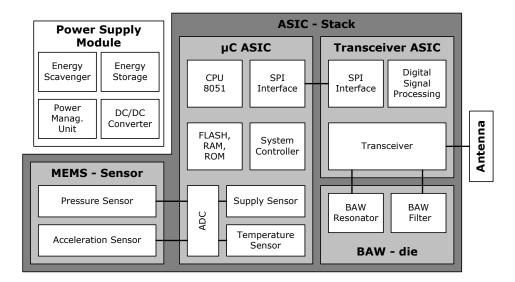

A block diagram of the system is given in Figure 2.1.

Figure 2.1.: Sensor Node

The  $\mu$ Controller is fabricated in a 0.25  $\mu$ m CMOS process. It is based on an 8051 CPU and contains an interface for the pressure and acceleration sensor, an analog to digital converter (ADC) and several types of memory (RAM, ROM, FLASH). The  $\mu$ Controller can be programmed via an I<sup>2</sup>C interface and communicate with the transceiver via a serial peripheral bus interface (SPI). The  $\mu$ Controller ASIC is qualified for automotive applications, thus it supports the required temperature range from -40 °C to +125 °C.

The sensor die is a bulk micromachined MEMS device which contains sensors for pressure and acceleration. It consists of a glass-silicon-glass triple stack. One of the glass layers contains a cavity which is sealed by the active silicon layer. The silicon

layer contains a membrane which is located above the cavity. So the pressure inside this sealed chamber is used as a reference for the pressure measurements. The glass layer on the other side of the stack contains a pressure inlet which leads to the other side of the membrane.

The transceiver, which is the main topic of this work, is fabricated in a 0.13 µm CMOS process. In contrast to conventional transceivers, it does not use a quartz crystal as frequency reference, but it uses BAW resonators to generate the carrier signal in transmit mode and the local oscillator (LO) signal in receive mode. Using BAW resonators offers a number of advantages compared to conventional crystal based systems. The crystal itself is very bulky and shock sensitive. When mounted on the inner liner of a tire, there is a high risk that the crystal is damaged due to the high acceleration. And also for the power consumption, the use of a BAW instead of a crystal is very beneficial. The BAW based oscillators directly oscillate at the carrier frequency of 2.1 GHz or 2.45 Ghz. They do not require another voltage controlled oscillator (VCO) and a phase locked loop (PLL) which drastically reduces the turn on time of the transceiver. The turn on time is an important factor for applications such as sensor networks. If the data payload is very small, the turn-on time can become the dominating factor for power consumption. This will be explained in detail in Chapter 12. The crystal- and PLL-less approach is described in [6].

### 2.1. Demonstrator Generations

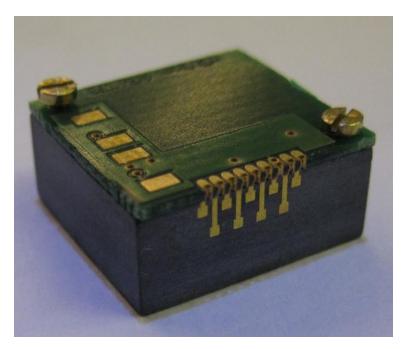

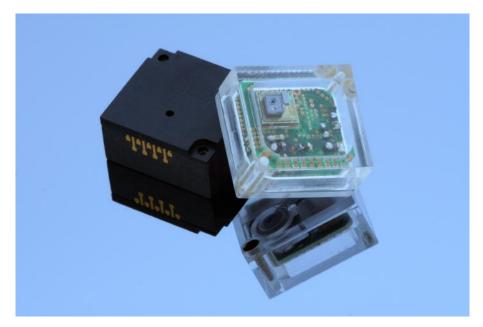

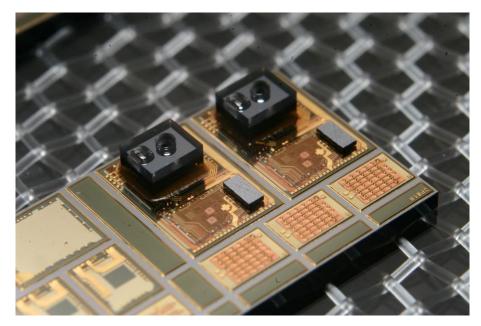

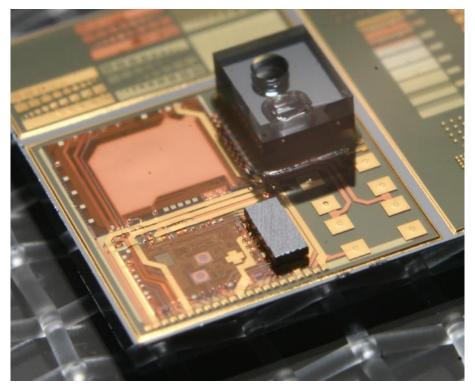

Figure 2.2.: 3D Package

The automotive demonstrator has been developed in three stages with three generations of Demonstrators.

D1: The first demonstrator is a functional proof of concept, with the system's components mounted onto a large printed circuit board (PCB). This PCB offers a number of debugging possibilities.

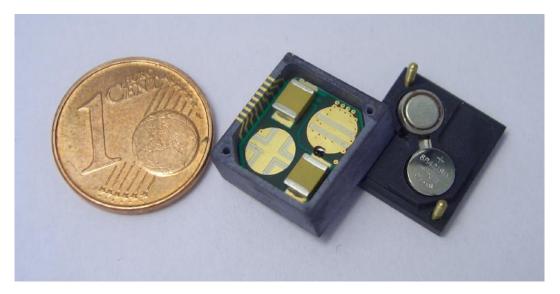

- D2: The second demonstrator already targets at the miniaturization of the system, but the components are still arranged in a lateral way. A three dimensional package containing also the batteries is used to achieve the small system size. Figure 2.2 shows the small size module.

- D3: the third and last demonstrator uses 3D vertical chip stacking technologies to further reduce the volume. These technologies will be briefly described in Chapter 13.

### 2.2. Conclusion

In this chapter the architecture of the sensor nodes is introduced. The most important components are described and the steps toward miniaturization are explained. With the presented architecture a completely autonomous sensor node with multi-hop capabilities can be achieved.

## 3. The eCubes Transceiver

This chapter explains the architecture of the transceiver which has been developed for the eCubes sensor nodes.

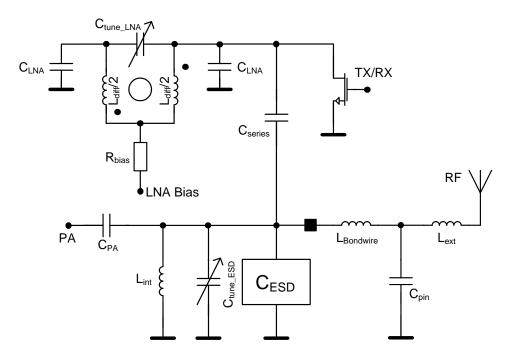

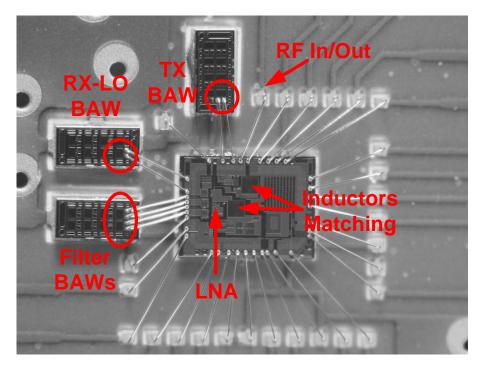

#### Analog BAW BAW IF Filter ィ 7 $\vdash \not\models$ PPF PPF Q LNA Temp. ADC Sensor RSSI ANT LO BAW Matching Filter Network FSK NCO Demod. clock Frequency Чuх Divider Matched Filter PA Data FIFO BAW Data / Clk Recovery Digital Asvn. DAC Baseband SPI ΤХ Interface Digital

### 3.1. Architecture

Figure 3.1.: The ecubes transceiver

In Figure 3.1 the schematic of the BAW based transceiver is shown. It contains two fully integrated BAW oscillators, one is used for generating the modulated carrier in transmit mode and the other provides the LO signal in receive mode. The two oscillators have a frequency offset, accomplished with different BAW resonators, for realizing a heterodyne receiver with a low IF of 10.7 MHz. The transceiver has been evaluated with two different BAW devices. In the first version the resonant frequency of the BAW is around 2.1 GHz

and in the second version it is around 2.45 GHz. The oscillators are tunable over a certain frequency range to enable temperature compensation, process compensation, and to perform modulation in the transmit path. In the 2.4 GHz ISM (industrial, scientific, and medical) band the tuning range of the BAW oscillators will not be sufficient to cover all channels, but due to the low costs and due to the fact that the BAW devices can easily be integrated, a bank of BAW resonators with slightly different resonant frequencies can be used to solve this problem. As the presented transceiver is only a proof of concept, it is not necessary to cover the whole band, and only single resonators are used. The oscillators have a very short turn on time and this fact in combination with the small data packet of the sensor node results in a very narrow active time slot and therefore the system is very energy efficient. The short turn-on time is feasible because the reference frequency is already at RF. The BAW based oscillator together with the transmitter architecture is not part of this work, but is described in detail in [5].

The core of this work is the receiver frontend of the sensor node. In order to be able to specify the requirements for the frontend and to choose an appropriate architecture, it is necessary to investigate the environment where it is meant to be installed and to consider any other constraints which are imposed by the system.

#### 3.2. Channel Properties

The transmission range of a transmitter - receiver system can be derived from the output power of the transmitter, the input sensitivity of the receiver, and the path loss.

Path loss in free space can be calculated according to Friis's transmission formula [80]:

$$L = 10 \cdot \log\left(\frac{4\pi d}{\lambda}\right)^2 - G_{\mathrm{Tx}} - G_{\mathrm{Rx}},\tag{3.1}$$

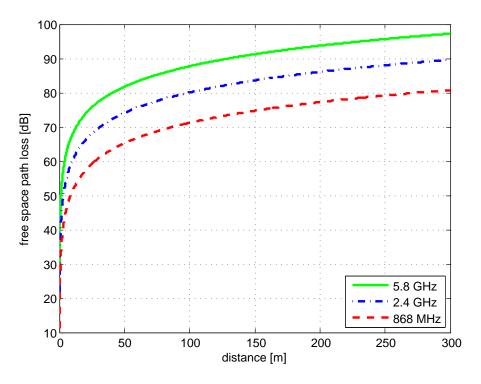

where *d* is the distance in meters, and  $\lambda$  is the wavelength of the transmitted signal.  $G_{\rm Tx}$  and  $G_{\rm Rx}$  are the antenna gains of the transmitter and the receiver respectively. The antenna gain is defined as the ratio of the power transmitted in a certain direction relative to the power transmitted by an ideal isotropic antenna. Figure 3.2 shows the free space path loss for different frequencies, assuming an antenna gain of 0 dB for both the transmitter and the receiver antenna. For a sensor node, an isotropic antenna is the best solution, because the mounting location and orientation is not known.

Indoor path loss cannot be expressed by such a generic equation as free space path loss because indoors a lot of effects like echo and multipath fading have to be considered. For sensor networks inside a car, the quality of the communication channel strongly depends on the location of the sensor nodes and also the movement and surroundings of the car itself. Channel measurement results inside a car have been reported in [84]. The results in [84] show that the path loss in two different scenarios does not exceed 76.8 dB in the 2.4 GHz frequency band. The reported values represent the mean path loss over the bandwidth from 2.36 GHz to 2.5 GHz which is important to notice because fading can be very strong at single frequencies within this band and negligible in others. Many considerations for communication requirements in wireless sensor networks as presented in [113] cannot be used for automotive sensor networks because they assume short range

Figure 3.2.: Free space path loss for different frequency bands

(10 m) communication at free line of sight. This assumption leads to sensitivity requirements which are not sufficient for automotive scenarios.

The sensitivity of a receiver defines the minimum signal level which can be detected with a signal-to-noise ratio (SNR) that is acceptable for the demodulator. It can be derived from the bandwidth (B), the required SNR and the noise figure (NF) of the frontend [99].

$$P_{\text{in.min}} = -174 \frac{\text{dBm}}{\text{Hz}} + NF + 10 \log B + SNR_{\text{min}}$$

(3.2)

The required SNR depends on the chosen modulation scheme, the data rate, the available bandwidth and the desired bit error rate (BER).

#### 3.3. Receiver Specifications and Link Budget

As the transceiver is part of the sensor node, the general requirements concerning temperature range, power consumption, mechanical robustness, and size listed in Section 1.2.1 are all valid also for the transceiver. The most relevant specifications and requirements which only concern the receiver and not the whole system are given below:

Power Consumption: As for the whole system, power consumption is one of the most important constraints for the receiver frontend. However, there is always a trade-off with performance. It is not useful sacrificing too much performance just to achieve an ultra low power consumption, because it might turn out that power may be saved more efficiently with fast and reliable transmission of signals and with

| Sensor Node                       |                     |  |

|-----------------------------------|---------------------|--|

| Size                              | < 1 cm <sup>3</sup> |  |

| Weight                            | < 5 grams           |  |

| Lifetime                          | 10 years            |  |

| Temperature range                 | -40℃ to +125℃       |  |

| Max. acceleration                 | 1,000 g             |  |

| Avg. power consumption            | < 10 μW             |  |

| Receiver                          |                     |  |

| Data rate                         | < 100 kbit/s        |  |

| Modulation                        | FSK                 |  |

| Power consumption                 | < 8 mA              |  |

| Demodulator SNR                   | 10.8 dB             |  |

| Sensitivity (at BER = $10^{-3}$ ) | -92.8 dBm           |  |

| Noise figure                      | 26.4 dB             |  |

Table 3.1.: Specifications for the sensor node and for the receiver

sophisticated protocols and sleep modes when the system is not active. Those aspects will be covered in Chapter 12. As a good compromise, the total current consumption of the receiver including LO generation, voltage regulators, and all other peripheral blocks has been specified not to exceed 8 mA.

- Data Rate: As the data payloads which have to be transmitted and received by the sensor nodes are very small, data rates of up to 100 kbit/s are sufficient for the application. In Chapter 12 it will be shown that for very small data packets, the start-up time of the system can be dominating in terms of power consumption. The employed modulation scheme is incoherent frequency shift keying (FSK). For this modulation scheme the required  $\frac{E_b}{N_0}$  at a BER of 10<sup>-3</sup> is about 10.8 dB [78]. With the assumed data rate of 100 kbit/s and a system bandwidth of about 300 kHz which is determined by the channel filter, the required SNR can be calculated as 6.2 dB. The BER of 10<sup>-3</sup> is sufficient because of the small data payloads. To add some redundancy, packets can be sent repeatedly.

- Sensitivity: The required sensitivity for the receiver can be estimated taking the wireless channel inside the car into account. Taking the value of 76.8 dB from [84] and assuming an antenna loss of -5 dB at both the transmitter and the receiver, the total path loss calculates to 86.8 dB. With a transmitter output power of 0 dBm, the given path loss, and the required SNR, the desired sensitivity can be calculated as -92.8 dBm.

- Noise Figure: With the desired sensitivity, the maximum allowable noise figure of the receiver frontend can be calculated. The noise floor is -174 dBm/Hz multiplied with the bandwidth of 300 kHz, resulting in -119.2 dBm. By subtracting the sensitivity from the noise floor, the maximum allowed noise figure of 26.4 dB can be obtained.

Table 3.1 summarizes all requirements for the sensor node in general and for the receiver frontend in particular.

### 3.4. Conclusion

In this chapter, the architecture of the employed transceiver has been introduced. The required performance has been evaluated according to the expected channel properties. As the transceiver is not operating in free space, channel properties reported in literature have been taken as a reference. Although the requirements regarding data rate and sensitivity might seem relaxed compared to applications like UMTS or wireless LAN, the requirements are very challenging considering the low power consumption.

## 4. The eCubes Receiver Frontend

This chapter describes the receiver architecture which has been chosen for the eCubes transceiver. It has been published in [2].

### 4.1. eCubes Receiver Frontend Architecture

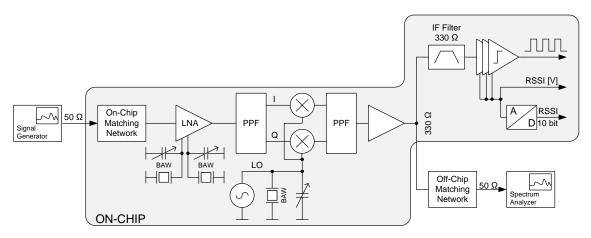

Figure 4.1.: The ecubes receiver frontend

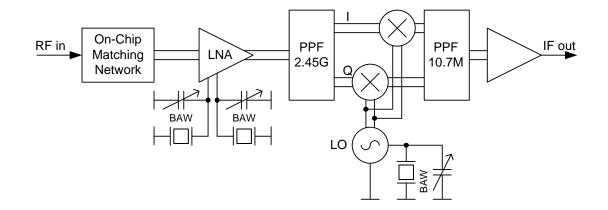

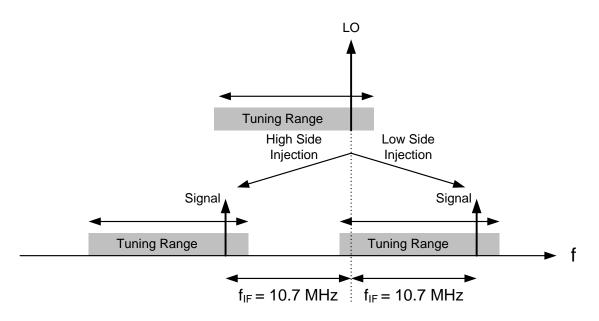

The receiver architecture which has been chosen for the eCubes sensor nodes is based on the Hartley image reject architecture. Additionally, it uses the narrow bandwidth of single BAW resonators to suppress the image before downconversion. A block diagram of the eCubes receiver frontend is shown in Figure 4.1. The choice for this architecture has been made for several reasons:

- As miniaturization of the system is a very important constraint for the system, a combined matching network for the receiver and the transmitter has been designed which does not require any external components. A detailed description of the circuit is given in Chapter 6. The matching network exploits the fact that the capacitive input of the LNA can be brought into resonance with an on-chip inductor and so an additional voltage gain can be achieved.

- The system uses a BAW based oscillator to generate the LO signal for downconversion. This BAW based oscillator does not provide quadrature phases and it directly oscillates at the frequency of interest. In PLL based systems, the VCO often oscillates at a multiple of the desired frequency such that I- and Q- phases can be obtained easily from an integer frequency division. Designing an oscillator with quadrature outputs would be possible but at the cost of a prohibitively high

current consumption. That is why a homodyne receiver frontend has not been implemented, as it requires exact I- and Q- signals. Another drawback of homodyne receivers is, that flicker noise and DC offsets due to second order nonlinearities may distort the downconverted signal.

- The intermediate frequency has been chosen to be 10.7 MHz. With this IF it is

possible to perfectly use the BAW resonators in the receive path for image rejection,

because it is about half the difference between the series and the parallel resonance

of the resonators. The resonators are described in Chapter 5 and their integration

into the LNA is explained in detail in Chapter 7. Another advantage of this frequency

is that cheap ceramic IF filters are available.

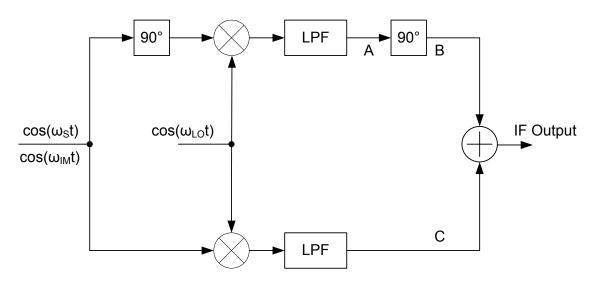

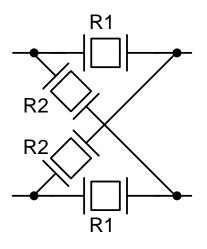

- In order to achieve an even higher image suppression than with the BAW resonators alone, an image reject architecture has been implemented but unlike the typical Hartley architecture [99] where the I- and Q- phases are provided by the LO, the quadrature phases in this receiver frontend are generated in the signal path by a polyphase network. This polyphase network is designed for quite a large bandwidth, because resonators with different resonant frequencies between 2.1 and 2.45 GHz have been assembled. Over this large bandwidth, amplitude errors in the quadrature phases might occur, which has been the reason for not using the homodyne frontend. In an image reject architecture however it is just the image rejection that might suffer from such a problem. The signal path itself is not affected by amplitude errors because the contributions of the desired signal sum up at the output of the frontend. This behavior is shown in Equations 4.1 4.6.

Figure 4.2 shows a simplified representation of the frontend concept. The on-chip matching network, containing also the RX/TX switch feeds the incoming RF signal to the differential LNA. The LNA is followed by a polyphase network which generates the quadrature phases required for the I- Q-mixers. After downconversion, another polyphase network is used for image cancellation. In this simplified representation, the polyphase networks are included as 90° shifts in the I-path. In reality, the polyphase networks cause shifts of 45° with opposite signs in the I- as well as in the Q-path.

Assuming that  $\omega_S < \omega_{LO}$ , and  $\omega_{IM} > \omega_{LO}$ , then the contribution of the desired signal in node A can be calculated as

$$y_{A_{S}}(t) = \frac{1}{2} [\cos((\omega_{S} - \omega_{LO})t - 90^{\circ})]$$

=  $\frac{1}{2} [\cos(-\omega_{IF}t - 90^{\circ})]$

=  $\frac{1}{2} [\cos(\omega_{IF}t + 90^{\circ})].$  (4.1)

The contribution of the image can be calculated in the same way as

$$y_{A_{IM}}(t) = \frac{1}{2} [\cos((\omega_{IM} - \omega_{LO})t - 90^{\circ})] \\ = \frac{1}{2} [\cos(\omega_{IF}t - 90^{\circ})].$$

(4.2)

Figure 4.2.: Image reject architecture containing two polyphase networks

After another 90° shift, the contribution of the desired signal to the signal in node B becomes

$$y_{\rm B_S}(t) = \frac{1}{2} [\cos(\omega_{\rm IF} t)].$$

(4.3)

And the image becomes

$$y_{\rm B_{IM}}(t) = \frac{1}{2} [\cos(\omega_{\rm IF} t - 180^{\circ})] = -\frac{1}{2} [\cos(\omega_{\rm IF} t)].$$

(4.4)

Node C carries the downconverted signals without any additional phase shift:

$$y_{C_{S}}(t) = \frac{1}{2} [\cos(\omega_{IF} t)],$$

(4.5)

and

$$y_{\rm C_{IM}}(t) = \frac{1}{2} [\cos(\omega_{\rm IF} t)].$$

(4.6)

At the output, the contributions of the desired signals sum up, whereas the contributions of the image signals are opposite-phased and cancel out. Which of the two sidebands is canceled by the image reject architecture and which is passed through can be changed easily by inverting the polarity of either the I- or the Q- path. In a fully differential design this can be done by simply crossing the two branches of the differential signal.

# 4.2. Analog to Digital Conversion and Digital Processing

After downconversion and image rejection, the signal is fed to an off-chip IF-filter where the channel is selected. Afterwards the analog to digital conversion is performed by means of a limiter. A limiter is a multi stage amplifier with a very high gain, in the case of this design more than 80 dB. The limiter used in this work has been designed by [73]. It clips the signal at the upper and lower supply voltages and produces a rectangular output signal. So the amplitude information is removed but the result is a binary signal and the need for an automatic gain control (AGC) is eliminated, which reduces the complexity of the system. The binary output signal of the limiter is sampled and further processing is done in the digital domain. Besides the binary output signal, the limiter also provides a received signal strength indicator (RSSI). This RSSI signal can be fed into an on-chip ADC and converted to a 10-bit digital value. So it can be used as a wake-up criterion for the system or to fine-tune the BAW based oscillators, the filters in the LNA or the matching network. In the digital domain the sampled output signal of the limiter is mixed into complex baseband by using a numerically controlled oscillator (NCO) which allows tuning the frequency in very fine steps. The digital clock can be derived from any of the two BAW based oscillators. After additional digital filtering and demodulation the signal is passed to the matched filter. By means of the clock and data recovery unit the output of the matched filter is sampled and the received payload is stored in a data FIFO where is can be accessed via the SPI [1].

# 4.3. Conclusion

A receiver architecture specially suitable for the BAW based approach is introduced in this Chapter. On the one hand it deals with the drawback of a BAW based oscillator providing only in-phase and no quadrature signals by using a polyphase filter in the signal path to generate the quadrature phases. On the other hand, it benefits from the narrow bandwidth of single BAW resonators to achieve an extraordinary image suppression. Calculations show how the chosen architecture is able to reject the image frequency while downconverting the desired signal.

# 5. RF Filters

As pointed out in the previous chapters, the presented transceiver makes extensive use of BAW resonators. That is why this chapter explains in detail the working principle of such resonators. Bulk acoustic wave (BAW) and surface acoustic wave (SAW) have become the dominating technologies in RF filter design. In terms of performance, size, and cost they are superior to other RF filter technologies [97, 100]. This chapter explains the working principle of the two technologies and provides a comparison between them.

# 5.1. Working Principle

SAW and BAW resonators are Micro-Electro-Mechanical Systems (MEMS). In a MEMS device, electrical energy is converted to mechanical energy and vice versa. In a SAW or BAW resonator acoustic waves are generated and transformed back to electrical signals by means of transducers and piezoelectric materials. The quality factor (Q) of BAW and SAW devices is very high compared to other technologies, because the applied acoustic materials have very low propagation loss. Another advantage of these devices is, that they are very small. The propagation speed of an acoustic wave is four to five orders of magnitude less than the speed of the electromagnetic wave. This means that also the wavelength is much smaller and indeed the first applications for BAW and SAW devices was to use them as delay lines [100].

# 5.2. Equivalent Circuit

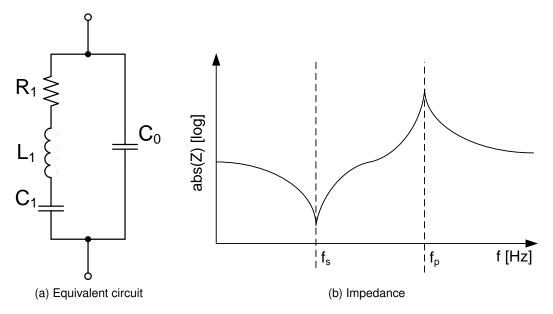

Basically a piezoelectric resonator behaves like a RLC-resonant circuit. A very simple equivalent circuit is sketched in Figure 5.1a. Figure 5.1b shows the impedance of the resonant circuit. Two frequencies, the series resonant frequency  $f_s$ , set by  $L_1$  and  $C_1$ , and the parallel resonant frequency  $f_p$ , defined by  $C_0$  in series with  $L_1$  and  $C_1$  [77], can be determined.  $f_s$  is defined as the frequency of maximum conductance and  $f_p$  is defined as the frequency of maximum conductance and  $f_p$  is defined as the frequency of maximum resistance [86]. The model in Figure 5.1a is called the Butterworth-Van-Dyke model (BVD) [100].  $C_0$  is the static or plate capacitance. It determines the impedance of the device in the regions far away from  $f_s$  and  $f_p$ .  $R_1$ ,  $C_1$ , and  $L_1$  represent the motional resistance (acoustic loss), capacitance, and inductance respectively [100].

# 5.3. Filter Topologies

Both BAW and SAW filter devices always consist of more than just one single resonator. Due to the high Q of a single resonator (in the range of 1,000 - 2,000), its bandwidth is

Figure 5.1.: Primitive model of a piezoelectric resonator

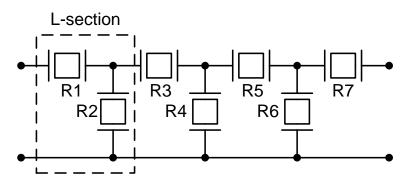

Figure 5.2.: Filter device consisting of several resonators connected in a ladder structure

very narrow, and a number of resonators with different center frequencies are used to achieve a certain desired bandwidth. Usually, these resonators are connected in a ladder structure, as shown in Figure 5.2.

BAW and SAW resonators have two resonant frequencies, a series resonant frequency  $f_{\rm s}$  where the impedance is very low, and a parallel resonant  $f_{\rm p}$  where the impedance is very high. Each L-section of the ladder structure consists of a resonator in series and a resonator in parallel with slightly different resonant frequencies. The series resonant frequency of the series resonator R1 is used to preserve desired signals while the parallel resonant frequency rejects undesired signals. The resonator R2 in the parallel path works the other way round. The series resonant frequency rejects undesired signals while the parallel resonant frequency preserves the desired components of the input spectrum. This behavior is shown in Figure 5.3.

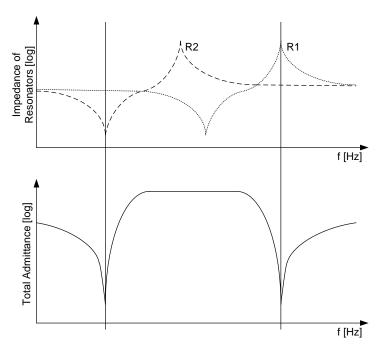

Another filter topology which is less common than the ladder topology is the lattice topology. Its drawback is, that it can only be used for differential signals, whereas the

Figure 5.3.: Frequency response of one L-section

ladder topology performs better for single ended inputs, which is more common. The lattice topology is shown in Figure 5.4.

## 5.4. SAW

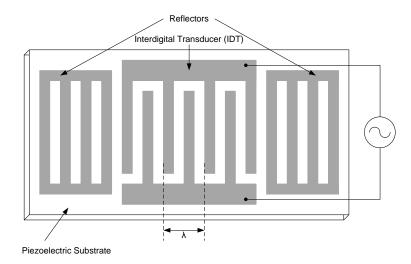

As its name indicates, a surface acoustic wave is a wave travelling along the surface of a structure. The basic structure of a SAW resonator is shown in Figure 5.5.

The substrate of a SAW resonator consists of a piezoelectric material. On top of it, it contains a pair of interleaving combs called interdigital transducer (IDT) between two grating reflectors. When the IDT is excited with an alternating voltage, a wave is launched along the substrate. The two grating reflectors form an acoustic cavity which is many wavelengths long. For a certain wavelength  $\lambda$ , a standing wave can be generated between the two reflectors. The resonant frequency is determined mainly by the pitch of the IDT. The IDT and the grating reflectors are typically made of thin-film metal, in most cases aluminum.

## 5.5. BAW

The difference between SAW and BAW resonators is that in BAW resonators the acoustic waves are launched into the bulk of the device instead of travelling along the surface. Basically a BAW resonator consists of a thin-film layer of piezoelectric material between two thin-film metal electrodes. When the piezoelectric layer is excited by a voltage or an

Figure 5.4.: Lattice Filter Topology

Figure 5.5.: Structure of a SAW Resonator

electric field between the two electrodes, an acoustic wave is generated. The resonance frequency is determined by the thickness of the piezoelectric layer and the thickness and mass of the electrodes. At the resonance frequency, there is exactly one half of the acoustic wavelength between the top and the bottom of this stack. The propagation speed of the acoustic wave is four to five orders of magnitude less than the speed of the electromagnetic wave. Therefore the acoustic wavelength is also much shorter than that of the electromagnetic wave.

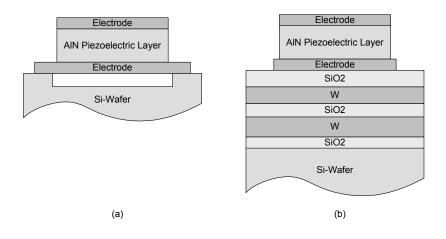

Acoustic waves with the desired frequency are trapped within the resonator. In order to prevent acoustic waves with other wavelength from propagating any further into the substrate, they have to be reflected. There exist two types of BAW resonators, with different means of reflecting the waves at the bottom electrode. The first ones are the free-standing bulk acoustic resonators (FBAR) and the second ones are the solidly mounted resonators (SMR). FBARs are based on a cavity underneath the resonator, and SMRs

Figure 5.6.: FBAR (a) and SMR (b) Technologies

use a Bragg reflector underneath the bottom electrode to reflect the waves. A Bragg reflector consists of alternating high and low impedance  $\lambda/4$  thin-film layers. The two different topologies are sketched in Figure 5.6. Large ratios of high to low impedance materials are required to reflect the acoustic energy over a wide bandwidth, for example Tungsten (W) and Silicon-Dioxide (SiO2) with a ratio of 7:1.

# 5.6. Key Features of Piezoelectric Resonators

This section describes the key features used for characterizing piezoelectric resonators.

**Piezoelectric effective coupling coefficient** The effective coupling coefficient  $k_{\text{eff}}^2$  is defined as the ratio of the stored mechanical energy to the electrical energy [112]. It can be expressed according to Equation 5.1 [87].

$$k_{\rm eff}^2 = \frac{\pi^2}{4} \cdot \frac{f_{\rm s}}{f_{\rm p}} \cdot \frac{f_{\rm p} - f_{\rm s}}{f_{\rm p}}$$

(5.1)

The effective coupling coefficient determines the bandwidth of a filter device as in Figure 5.2 [85]. The best reported value is 6.9% [100]. There are two reasons why a high  $k_{\text{eff}}^2$  is desirable. On the one hand, a higher  $k_{\text{eff}}^2$  improves the insertion loss of a filter, and on the other hand it can be traded off for Q [97].

**Bandwidth** The bandwidth (B) of a resonator is defined as  $B = (f_p - f_s)/f_p$ . Here the best reported value is 2.8% [100].

**Quality Factor** One of the most significant parameters describing a filter is its quality factor. Not only filters can be described by this parameter but all kinds of resonant circuits,

not limited to electric circuits. The most generic definition of Q is that it describes for a sinusoidal excitation of a system with frequency  $\omega$  how much energy is lost per cycle.

$$Q = \omega \frac{\text{energy stored}}{\text{average power dissipated}}$$

$$= 2\pi \frac{\text{energy stored}}{\text{energy dissipated per cycle}}$$

(5.2)

A more comprehensive definition of Q for a filter is the center frequency ( $f_c$ ) divided by the 3-dB bandwidth [88]. Regarding BAW resonators, the Q values of series and parallel resonance do not necessarily have to be equal.

$$Q_{\rm p} = \frac{f_{\rm p}}{\Delta f_{\rm 3dB}}$$

, regarding the impedance Z of the resonator, (5.3)

and

$$Q_{\rm s} = \frac{f_{\rm s}}{\Delta f_{\rm 3dB}}$$

, regarding the admittance  $Y = \frac{1}{Z}$  of the resonator. (5.4)

$Q_{\rm s}$  mainly depends on the ohmic loss of the electrodes, while  $Q_{\rm p}$  is determined mostly by the acoustic loss in the resonator. Q is a dimensionless parameter.

For each of the two resonant frequencies in Figure 5.1b the quality factors can be calculated with the equations above, but a more accurate method of obtaining  $Q_s$  and  $Q_p$  is to use the phase derivative.

$$Q_{\rm s,p} = \frac{f}{2} \left| \frac{\mathrm{d}\phi}{\mathrm{d}f} \right|_{f=f_{\rm s}} \text{ or } f_{\rm p}$$

(5.5)

In a ladder filter, the values of  $Q_{\rm s}$  and  $Q_{\rm p}$  determine the insertion loss and the selectivity.

**Impedance Z**<sub>C</sub> The impedance  $Z_{\rm C}$  is defined as the impedance of the plate capacitance  $C_0$  at  $(f_{\rm s} + f_{\rm p})/2$ . Typical values are in the range between 50  $\Omega$  and 100  $\Omega$ .

### 5.7. Comparison between SAW and BAW Technology

Although the two technologies are very similar, BAW resonators have shown to be superior to SAW in some aspects.

- Especially above 2 GHz BAW resonators have higher Q values than SAW resonators. Due to this filters with lower insertion loss and better selectivity are available [100].

- The required BAW chip size is smaller than SAW (Factor of 2 for 1.8 GHz filters [32]).

- BAW resonators have a lower temperature drift of only up to -20 ppm/°C compared to -45 ppm/°C of SAW. This makes the design easier and less guardband is required for filters [100].

- BAW can operate up to higher frequencies than SAW [100].

- SAW filters require a hermetically sealed package, whereas BAW resonators only need a cavity [32].

- BAW technology is compatible with any wafer processing such as silicon or gallium arsenide [100]. So it is possible to integrate BAW resonators directly on radio ASICS and even above active die area. This is not the case with SAW resonators [31, 30, 29]. On the other hand, SAW resonators require only two layers of photo masks, compared to up to ten layers for BAW [100].

The decision whether to integrate BAW resonators directly above active area or as separate dies has to be made separately for every application. On the one hand, chip cost will increase if the small size resonators are processed on top of it and the total yield will decrease. On the other hand, assembly cost and packaging can be significantly cheaper for a SoC than for a SiP. Regarding miniaturization, a SoC will be hard to beat. According to [32], filters above active area are rather unlikely to become mainstream in the near future although it would be beneficial for certain applications. The feasibility has already been proven [31, 30, 29].

## 5.8. Resonators in the eCubes Transceiver

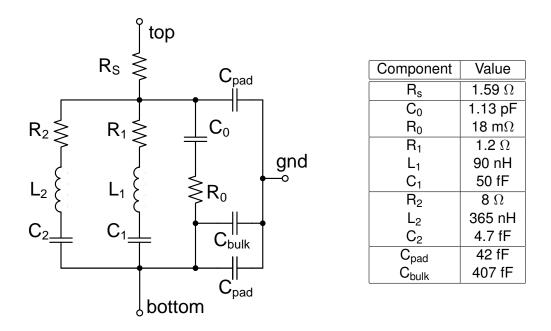

For the eCubes transceiver BAW resonators of SMR type have been used. Although above-IC resonators would have been very beneficial in this case, only separate dies have been available. A model of the employed resonators is shown in Figure 5.7. Adding  $R_{\rm S}$  and  $R_0$  to the BVD model results in the commonly used modified Butterworth-Van-Dyke model (MBVD). In order to get the component values, a resonator can be measured using a network analyzer and the model can be fitted to the measured s-parameters by means of a least mean squares algorithm as described in [77]. The model used for the e-Cubes resonators is shown in Figure 5.7. In addition to the MBVD model it contains parasitic capacitances  $C_{\rm pad}$  representing the bond pads and another capacitor  $C_{\rm bulk}$  which is required because the bottom electrode has a higher capacitance against ground than the top electrode. So the device is not symmetrical which will be important for the LNA design in Chapter 7.  $R_2$ ,  $L_2$ , and  $C_2$  represent the first harmonic of the resonator.

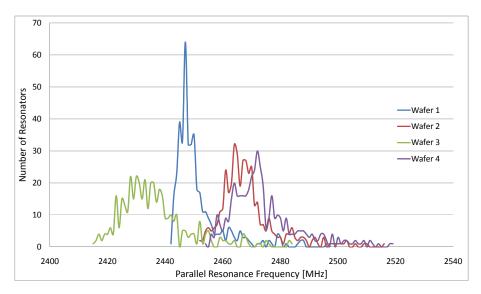

As commercially available filters always consist of a number of resonators, connected in a certain way, and encapsulated under a cavity it is not possible to contact single resonators out of such a device as it is required for the eCubes transceiver. However, on every BAW wafer there are test structures available distributed over the whole wafer, which are used for process calibration. Those test structures contain single resonators which can be contacted individually during the processing of a wafer. For the eCubes transceiver resonators from those test structures have been used and no dedicated mask set has been manufactured for eCubes BAWs. Nevertheless, two different types of resonators have been used in the eCubes transceiver:

· The first type of resonators has been taken from a wafer carrying filters for mobile

Figure 5.7.: Model used for BAW resonators and component values of the 2.4 GHz device

phones with a resonant frequency of about 2.1 GHz. The model extraction for those resonators has been done by [71], using values measured in the lab.

The second type of resonators has been designed for the eCubes transceiver. The

mask set itself has not been modified, but an additional process step has been

introduced. In order to mechanically compensate for the temperature drift of the

resonators, an additional layer with an inverse temperature coefficient to that of the

piezoelectric material has been introduced [76, 75]. Additionally the thickness of

the resonators has been modified to shift the resonant frequency from 2.1 GHz to

2.45 GHz. The parameters for the model of those resonators have been estimated

and provided by the designer of the resonators. So the model is less accurate than

that for the 2.1 GHz resonators.

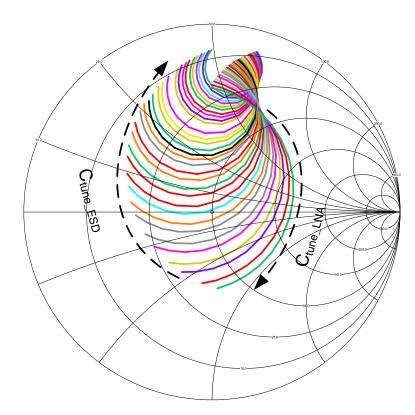

### 5.9. Temperature Compensation

In order to compensate for the temperature drift of the resonators, the oscillators include a bank of binary weighted capacitors to tune the frequency [71]. Copies of this bank of capacitors are switched in parallel to the filtering BAWs in the LNA. The oscillator itself is not part of this work, but as it determines the performance of the receiver, some results are shown below. The oscillator together with the transmitter architecture of the e-Cubes transceiver is described in [71].

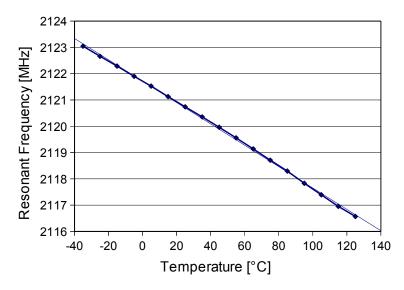

Figure 5.8 shows the measured temperature drift of an uncompensated 2.1 GHz resonator together with a linear trendline. The temperature drift has a slope of -19 ppm/°C and can be compensated electrically by switching capacitors in parallel. Due to a nonlinear behavior of the tuning network, the required digital codeword has to be calculated

Figure 5.8.: Measured temperature drift of a 2.1 GHz resonator

using a second order polynomial, but the resulting temperature drift can be shown to be within  $\pm 40$  ppm/°C over the whole temperature range [7]. Another way of tuning the resonance frequency is to apply a DC voltage across a resonator. The DC voltage changes the stiffness of the piezoelectric material and so the frequency is shifted. This effect is very linear and in the transmit path of the transceiver it is exploited for modulation. It cannot be used for process and temperature compensation however, because the tuning range is limited to 40 kHz/V [5]. The accurate compensation of the temperature drift is directly related to the performance of the receiver because a drift of only a few hundreds of kHz completely shifts the received signal out of the bandwidth of the IF filter. In [8, 10, 9] the temperature drift due to self-heating of the demonstrator during transmission is explored.

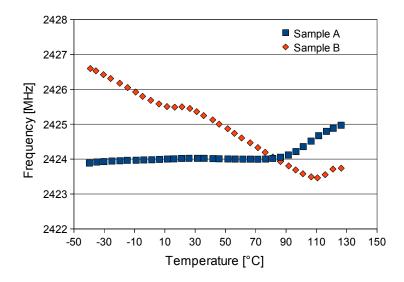

Figure 5.9 shows the temperature drift of two 2.4 GHz resonators. These samples have been mechanically temperature compensated as described in [76, 75]. The overall drift is indeed much smaller than that of the 2.1 GHz resonator, but unfortunately it differs very much from lot to lot and from wafer to wafer. So the remaining required codeword for the electrical compensation cannot be calculated by simply using a second order polynomial. For the 2.1 GHz version, only the coefficients of the polynomial have to be adapted for every resonator. In the 2.45 GHz version not only the coefficients but the whole equation differs from sample to sample. So the benefit of the mechanical temperature compensation is questionable because in the end it increases the system complexity instead of reducing it. It has to be mentioned however, that those samples have only been taken from test-wafers. Sample A in Figure 5.9 looks very promising, indicating that the mechanical temperature compensation might be a good solution.

Figure 5.9.: Measured temperature drift of two 2.4 GHz resonators

# 5.10. Conclusion

This chapter explains the operating principle of BAW and SAW resonators. The differences are described and the advantages as well as the drawbacks of each technology are highlighted. It is shown how the BAW is modeled for circuit simulations and the temperature drift is explored. Finally the behavior of mechanically temperature compensated BAW resonators is evaluated.

# 6. Input Matching

This chapter describes the meaning of matching the impedance of the antenna to the input of the LNA. Different architectures are examined and finally a suitable topology for the e-Cubes transceiver is chosen.

### 6.1. Matching

Most RF circuits are matched to a certain impedance. This means that the antenna impedance equals the input impedance of the receiver and the output impedance of the transmitter. A very common value is  $50 \Omega$ . In this way, the maximum power can be delivered from the antenna to the receiver and from the transmitter to the antenna. In most receiver frontends, the LNA is the first active block in the receiver chain, which follows right after the antenna or an external band select filter. In the case of an external filter, the input impedance is even more important because the transfer characteristics of many filters are sensitive to the termination [88]. In order to match the LNA to the antenna, a resistive input impedance is required. Different techniques are known to transform the input impedance to a desired value.

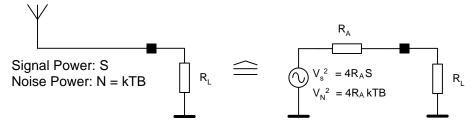

Figure 6.1.: Equivalent Circuit of an Antenna

Figure 6.1 shows the equivalent circuit of an antenna connected to a load resistor. The antenna is modeled as a voltage source in series with a noiseless resistor. The signal power delivered from the antenna to the load is denoted as S, and N is the noise power which can be calculated as N = kTB. The signal voltage  $V_S$  can thus be expressed as

$$V_{\rm S} = \sqrt{4R_{\rm A}S},\tag{6.1}$$

and the noise voltage is

$$V_{\rm N} = \sqrt{4R_{\rm A}kTB}.$$

(6.2)

The signal power  $P_{\rm L}$  which is delivered to the load can be calculated as

$$P_{\rm L} = V_{\rm S}^2 \frac{R_{\rm L}}{(R_{\rm A} + R_{\rm L})^2}.$$

(6.3)

As explained in [99] the Noise Factor F can be expressed as

$$F = \frac{\text{total output noise power}}{\text{output noise power due to input source}}.$$

By making  $R_A = R$  and  $R_L = \alpha R$ , and assuming that the load resistor adds noise to the signal itself, the above expression evaluates to:

$$F = \frac{4kTB\left[\frac{\alpha}{(1+\alpha)^2} + \frac{1}{(1+\alpha)^2}\right]}{4kTB\frac{\alpha}{(1+\alpha)^2}}$$

$$= \frac{1+\alpha}{\alpha}$$

(6.4)

Equation 6.4 shows that when the load is matched to the antenna ( $\alpha = 1$ ), F = 2 and the NF is 3 dB respectively.

Figure 6.2 shows the noise figure (a), the ratio of the total power to the power delivered to the load (b), and the voltage across the load resistor (c) for different values of  $\alpha$ .

Figure 6.2.: Matching Aspects

A very obvious way to achieve a resistive input impedance of a certain value is to add a shunt resistor with the desired value in front of the input transistor. As shown in Figure 6.4 however, this approach imposes a lower limit of 3 dB on the noise figure. So this is not a very good idea.

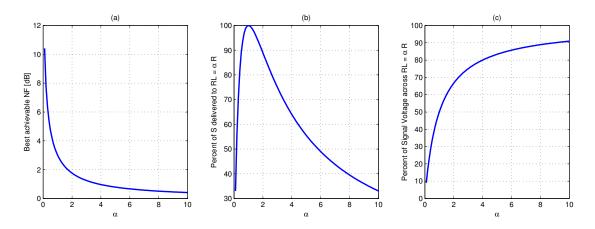

#### 6.1.1. Resistive Feedback

Figure 6.3 shows an LNA using resistive feedback to achieve a certain input impedance. As shown in [88], the real part of its input impedance can be expressed as:

$$R_{\rm in} = \frac{R_{\rm F}}{1 + \frac{R_{\rm L}}{R_{\rm S}}} \tag{6.5}$$

Figure 6.3.: Matching with resistive feedback

Although the resistive feedback also contributes to the overall noise, the performance of such a circuit is better than with a simple shunt resistor [88]. Due to its broadband input matching capabilities, this circuit is often used for wideband LNAs as for example in [69], [26] or [68].

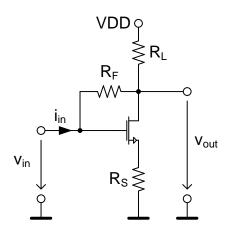

#### 6.1.2. Common Gate

Another easy way to achieve a resistive input of a certain value is to implement an LNA in a common gate configuration with an input impedance of  $Z_{in} = \frac{1}{g_m}$  as shown in Figure 6.4. In terms of noise figure however, also this topology does not lead to an optimum, because there is still a noisy resistor in the signal path, although in this case, it is not a device, but it is the channel resistance of the transistor.

Figure 6.4.: Common Gate Amplifier

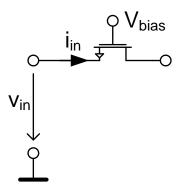

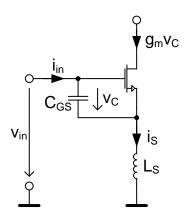

#### 6.1.3. Inductive Source Degeneration

Typically LNAs make use of common source amplifier input stages. The input of a common source amplifier is purely capacitive as it is only defined by the gate-source capacitance  $C_{\rm GS}$ . A very common approach of generating a resistive component in the input impedance is to apply inductive source degeneration. This technique uses a series inductor  $L_{\rm S}$  following the source of the input transistor, as shown in Figure 6.5. In contrast to the resistive feedback approach, inductive source degeneration is specially suitable for narrowband LNAs.

Figure 6.5.: Inductive Source Degeneration

With  $v_{\rm C} = \frac{i_{\rm in}}{j\omega C_{\rm GS}}$  and  $i_{\rm S} = i_{\rm in} + g_{\rm m} v_{\rm C}$ , the input impedance  $Z_{\rm in}$  can be calculated as:

$$Z_{\rm in} = \frac{v_{\rm in}}{i_{\rm in}}$$

$$= \frac{v_{\rm C} + j\omega L_{\rm S} \cdot i_{\rm S}}{i_{\rm in}}$$

$$= \frac{\frac{i_{\rm in}}{j\omega C_{\rm GS}} + j\omega L_{\rm S} \cdot \left(i_{\rm in} + g_{\rm m} \frac{i_{\rm in}}{j\omega C_{\rm GS}}\right)}{i_{\rm in}}$$

$$= \frac{1}{j\omega C_{\rm GS}} + j\omega L_{\rm S} \cdot \left(1 + \frac{g_{\rm m}}{j\omega C_{\rm GS}}\right)$$

$$= \frac{g_{\rm m} L_{\rm S}}{C_{\rm GS}} \cdot j \left(\omega L_{\rm S} - \frac{1}{\omega C_{\rm GS}}\right)$$

(6.6)

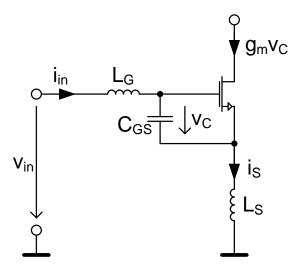

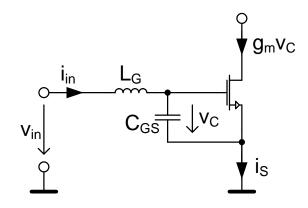

$L_{\rm S}$  can be used to tune the real part of the input impedance to a desired value. As the resistive term is generated by a pure reactance however, it does not introduce any noise to the circuit, so it does not degrade the noise figure. With another series inductor  $L_{\rm G}$  ahead of the gate of the transistor as shown in Figure 6.6, the reactance can be tuned to zero. Equation 6.7 shows the input impedance of an inductively degenerated common source LNA with a series inductor  $L_{\rm G}$ .

$$Z_{\rm in} = \frac{g_{\rm m}L_{\rm S}}{C_{\rm GS}} \cdot j\left(\omega L_{\rm S} - \frac{1}{\omega C_{\rm GS}}\right) + j\omega L_{\rm G}$$

$$= \frac{g_{\rm m}L_{\rm S}}{C_{\rm GS}} \cdot j\left(\omega L_{\rm G} + \omega L_{\rm S} - \frac{1}{\omega C_{\rm GS}}\right)$$

(6.7)

Figure 6.6.: Inductive Source Degeneration with Additional Series Inductor

# 6.2. Resonant Circuit

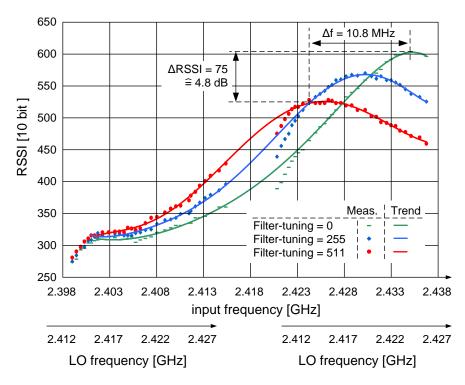

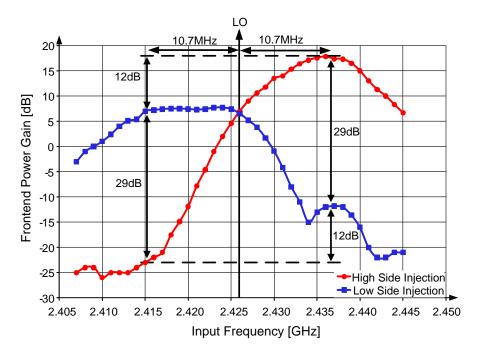

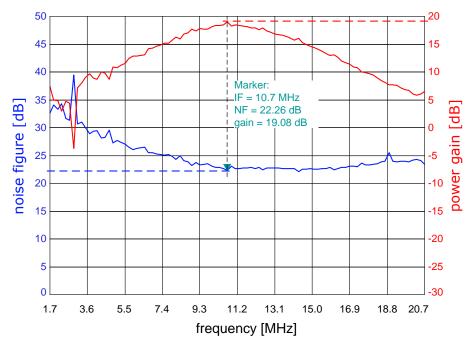

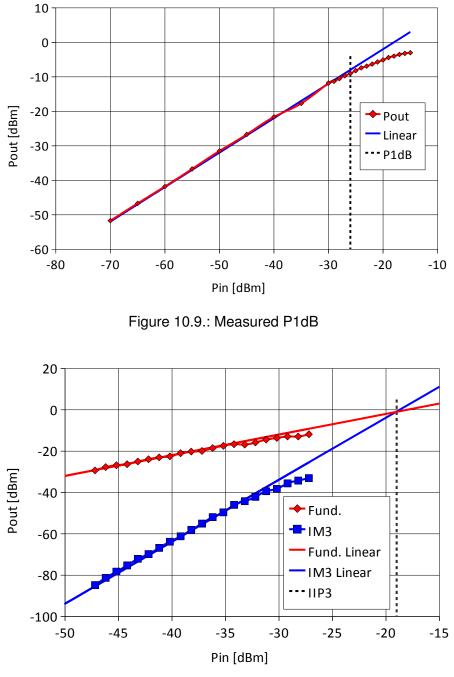

Figure 6.7.: Resonant Circuit with LNA and inductor