## Design of an Analog Interface for Frequency Band Comprehensive RFID Systems

Dipl.-Ing. Albert Missoni

Submitted as thesis to attain the academic degree "Dr. techn." at the

Graz University of Technology

Institute of Electronics

| Supervisor:    | UnivProf. DiplIng. Dr. techn. Wolfgang Pribyl  |

|----------------|------------------------------------------------|

| Co-Supervisor: | Ao.UnivProf. DiplIng. Dr. techn. Erich Leitgeb |

Graz, Juni 2010

## Eidesstattlich Erklärung

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe.

Graz, am .....

Copyright © 2010 Albert Missoni

## Kurzfassung

In passiven RFID Applikationen haben sich drei Frequenzbänder - LF, HF und UHF - durchgesetzt. Welches Band eingesetzt wird, hängt von den Bedürfnissen der Applikation, von den lokalen Regulatorien, der etablierten Infrastruktur oder zum Beispiel von den Herstellungskosten ab. Ziel dieses Projektes war es, einen RFID Chip mit angepasster Antenne zu entwickeln, der gemeinsam als Tag sowohl in einem standardisierten HF als auch in einem UHF Frequenzband mit entsprechenden Readern kommunizieren kann. Ebenso wird die durch den Reader generierte bzw. abgestrahlte Energie für die Versorgung des Chips herangezogen. Nach Auswahl des entsprechenden Frequenzbandes arbeitet der CTS Chip gleich wie ein handelsüblicher HF oder UHF RFID IC der nur auf einer Trägerfrequenz selektiv ist und auf diese optimiert wurde.

Der Schwerpunkt dieser Dissertation lag auf dem Entwurf und Entwicklung eines integrierten Schaltkreises, bestehend aus diversen Analogschaltung die für den Betrieb von mehrfach Frequenz selektiven RFID Chip notwendige sind und deren Verifizierung samt meßtechnischer Erfassung. Im Rahmen der Dissertation wurden neue Gleichrichter, Oszillatoren und Module für die kontaktlose Kommunikation vorgestellt. Der Chip wurde als Testchip in einer Infineon 120nm CMOS Technologie gefertigt.

Das Ergebnis dieser Arbeit sind drei neue Schaltungsarchitekturen für passive RFID ICs, die sowohl im HF als auch im UHF Band selektiv sind. Die Leistungsfähigkeit der Schaltungen wird in drei Kapiteln beschrieben und mit Simulationen bzw. Messungen untermauert. Es handelt sich bei dieser Arbeit um den weltweit ersten EPCglobal Transponder, der sowohl den HF als den UHF Standard unterstützt. Mittels eines Demonstrators (bestehend aus HF und UHF Reader, CTS Antenne und CTS Chip) kann die Leistungsfähigkeit verdeutlicht werden.

## Abstract

In passive RFID applications three frequency bands predominate worldwide - the LF, HF and the UHF band. Which of these bands is finally chosen depends on the application, on the local regulations, on the established infrastructure or on the costs. The aim of this thesis was to develop an analog front-end together with a digital control unit which can work together with a multi frequency selective antenna. This bundle should be able to communicate in standardized HF or UHF frequency bands with corresponding readers. The generated and radiated field of the reader antenna will be used to power the chip. After selection of the corresponding frequency band, the CTS chip behaves equivalent to a single frequency chip which is selective only in one carrier frequency.

The focus of this thesis is the development and the design of an integrated circuit for this purpose. This circuit consists of a chip - antenna interface and an integrated analog unit which is necessary for a multi frequency selective RFID chip. New rectifier architectures, local oscillator concepts and modules for the contactless communication are presented in this thesis. The test chip has been manufactured in a low cost 120nm Infineon CMOS process.

The results of this project are three new design architectures for low power RFID applications. The performance of the introduced circuits are presented in three chapters of this thesis and are confirmed by simulations and measurement results. This work presents the very first EPCglobal chip which supports both the HF and UHF standard. A fully functional demonstrator (composed of HF and UHF reader, CTS antenna and CTS chip) represents the capability of the CTS transponder.

## Acknowledgements

During this project I was working part-time at Infineon Technologies Design Center Graz as a system engineer and analog designer responsible for analog front-ends which are used in contactless Smart Cards. It was a pleasure for me to meet many people who I would like to thank in the following:

Univ.-Prof. Dipl.-Ing. Dr.techn. Wolfgang Pribyl, head of the Institute of Electronics at Graz University of Technology, for having been my academic supervisor, for his advice and support and for giving me the opportunity to be a part of this project.

Dipl.-Ing. Gerald Holweg, head of the Contactless and Radio Frequency Exploration team at Infineon Technologies Graz, for asking me to be a part of this project. I also would like to thank for the technical and administrative support and for the smooth and efficient project progression.

Special thanks to my colleague Dipl.-Ing. Günter Hofer from Infineon Technologies for the introduction into the field UHF RFID engineering and especially for the great layout support.

Thanks also to my colleague Dr.techn. Dipl.-Ing. Christian Klapf for many discussions and his helping hand before tape-out.

I would also like to thank Dipl.-Ing. Johann Heyszl for providing an efficiently working digital EPC state machine , for the good cooperation and the well implemented EPCglobal codec.

Without a compact antenna the best chip could not be presented in a performance demonstration. For the well working antenna I would like to thank Dr.techn. Dipl.-Ing. Lukas Mayer.

Finally, I would like to thank FIT-IT and Infineon Technologies for funding the CTS project.

Albert Missoni Graz, June 2010

## Contents

| 1 | Motivation - The CTS Project                                   | 17 |

|---|----------------------------------------------------------------|----|

|   | 1.1 The CTS - Comprehensive Transponder Systems Project        | 17 |

|   | 1.2 Project progress                                           | 20 |

| 2 | Introduction to passive RFID                                   | 21 |

|   | 2.1 EPC Standard linked with Passive RFID                      | 21 |

|   | 2.2 CTS transponder - An application example                   |    |

|   | 2.3 EPC Global Regulations                                     |    |

|   | 2.3.1 EPC standards                                            |    |

|   | 2.4 Air interface parameters                                   |    |

|   | 2.4.1 Power Matching                                           |    |

|   | 2.4.2 Quality Factor - Q                                       |    |

|   | 2.5 Air Interface Circuits                                     |    |

|   | 2.6 How to combine different frequency bands?                  |    |

| 3 | Infineon Si process information                                | 29 |

| Ŭ | 3.1 MOS transistors - electrical parameters                    |    |

|   | 3.2 MOS transistors - Symbols                                  |    |

|   | 3.3 Passive components                                         |    |

| 4 | Power Generation Units                                         | 33 |

| • | 4.1 Passive RFID power generation                              |    |

|   | 4.2 Available power in different RFID frequency bands          |    |

|   | 4.3 Balanced and unbalanced rectifier structures               |    |

|   | 4.4 Proposed CTS power architecture                            |    |

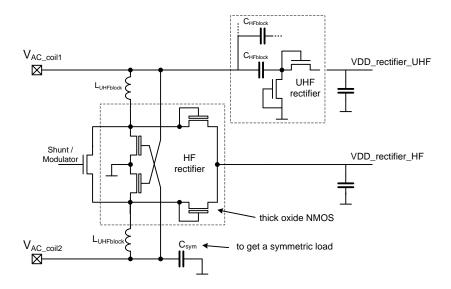

|   | 4.4.1 HF rectifier                                             |    |

|   | 4.4.2 UHF rectifier                                            |    |

|   | 4.5 Frequency selection                                        |    |

|   | 4.6 CTS power architecture - An overview                       |    |

|   | 4.6.1 CTS Rectifier and secondary charge pumps                 |    |

|   | 4.6.2 Bulk Potential Generation                                |    |

|   | 4.6.3 DC/DC charge pump for UHF operation                      |    |

|   | 4.6.4 Serial NMOS voltage regulator                            |    |

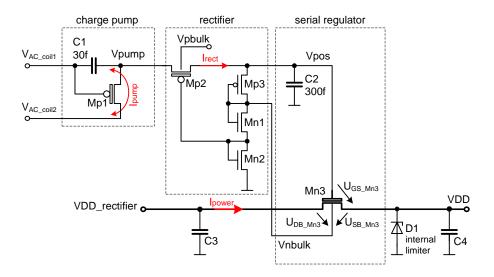

|   | 4.7 Alternative rectifier concepts for multi band applications |    |

|   | 4.8 Measurement results of different rectifier architectures   |    |

|   | 4.9 Layout                                                     |    |

| 5 | Clock Generation Units                                         | 69 |

|   | 5.1 Requirements for the clock generation units                | 69 |

|   |                                                                |    |

| Contents |

|----------|

|----------|

# List of Figures

| 2.1<br>2.2<br>2.3 | HF and UHF RFID systems in transportationCTS tags are fixed on label products, pallets and containerParallel RLC tank circuit | 23<br>24<br>26 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.3               | Equivalent tag electrical circuit                                                                                             | 20<br>27       |

| 3.1<br>3.2        | Symbol of thick oxide NMOS transistor (left) and PMOS transistor (right) Symbol of thin oxide NMOS and PMOS transistor        | 30<br>30       |

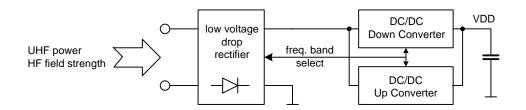

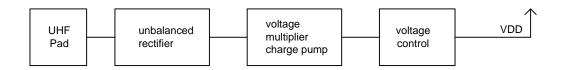

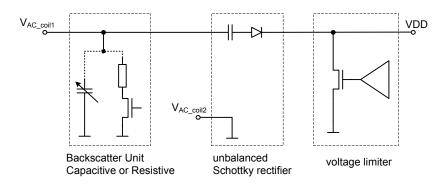

| 4.1               | Power generation modules - An architectural overview                                                                          | 33             |

| 4.2               | RFID frequencies and corresponding maximum power levels [Fin06]                                                               | 35             |

| 4.3               | Is there an unbalanced signal applied, we only have one "hot" node - in balanced                                              |                |

|                   | configuration two                                                                                                             | 37             |

| 4.4               | A typical UHF RFID antenna - chip interface                                                                                   | 37             |

| 4.5               | A typical HF RFID antenna - chip interface which is also used for the CTS chip                                                | 38             |

| 4.6               | Typical power generation in the HF and UHF frequency bands                                                                    | 39             |

| 4.7               | Proposed CTS architecture to handle HF and UHF bands                                                                          | 39             |

| 4.8               | First, a resistor only and then, additionally a rectifier is connected to an inductance                                       | 40             |

| 4.9               | Simple rectifier with additional big AC-coupling capacitor                                                                    | 41             |

|                   | Simplified antenna to chip interface                                                                                          | 41             |

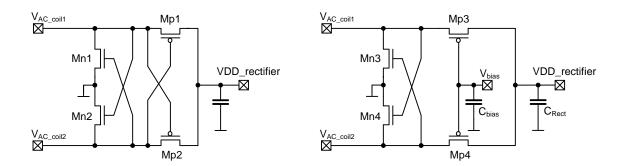

|                   | HF rectifier structures with two NMOS diodes and PMOS mirror transistors                                                      | 42             |

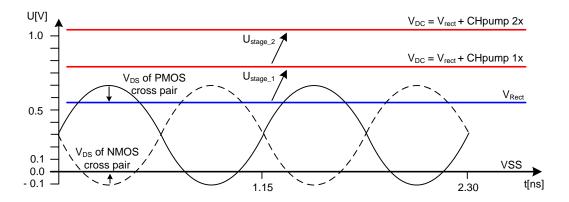

|                   | Coil voltage of both HF rectifier versions                                                                                    | 42             |

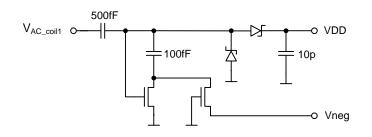

|                   | Simple rectifier with additional big AC-coupling capacitor                                                                    | 43<br>43       |

|                   | UHF rectifier principle and typical implementation                                                                            | 43<br>44       |

|                   | UHF rectification and additional UHF charge pump                                                                              | 44<br>44       |

|                   | Proposal for power generation with ideal passive components                                                                   | 44<br>45       |

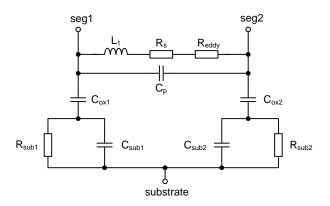

|                   | Equivalent circuit for one segment of an on-chip inductor                                                                     | 43<br>46       |

|                   | Power generation concept valid for CTS and Bergeret [BGP07]                                                                   | 47             |

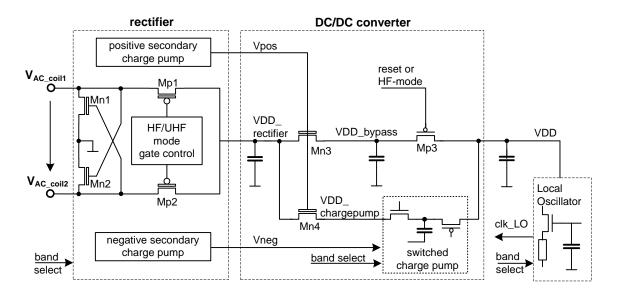

|                   | Power architecture of the CTS chip                                                                                            | 47             |

|                   | More detailed power architecture of the CTS chip                                                                              | 48             |

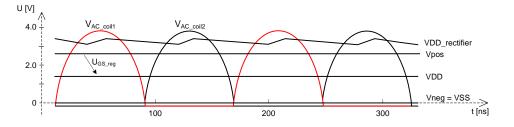

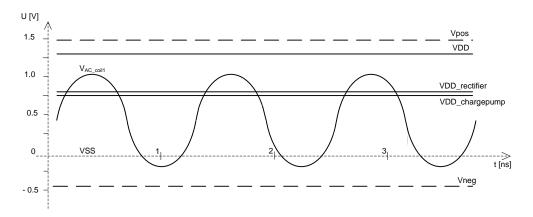

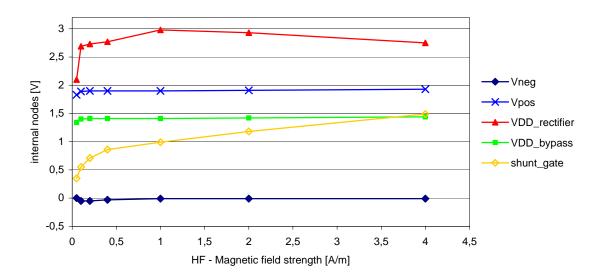

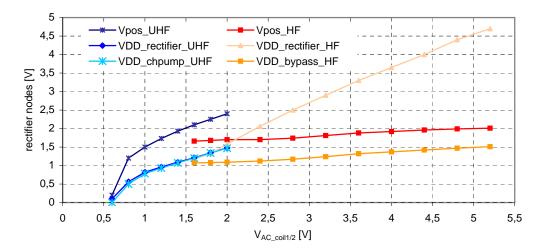

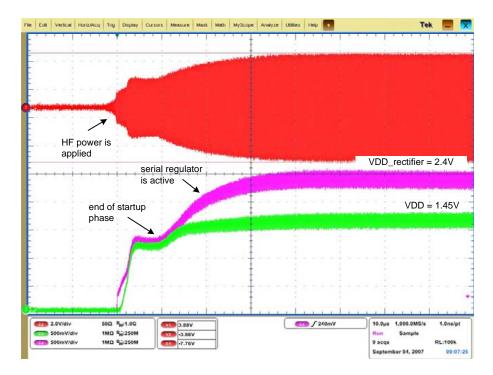

|                   | Some power relevant voltages in HF mode                                                                                       | 48             |

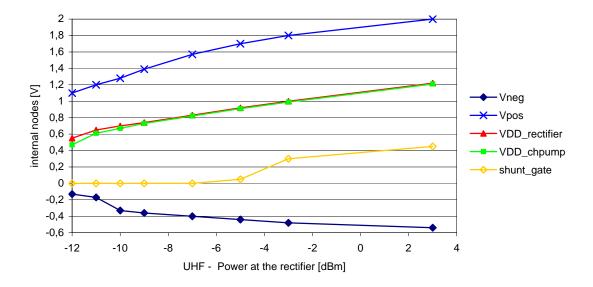

|                   | Some power relevant voltages in UHF mode                                                                                      | 49             |

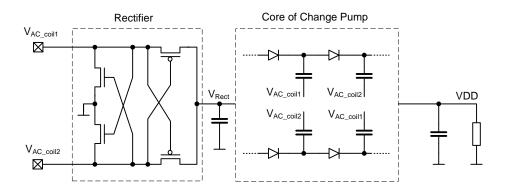

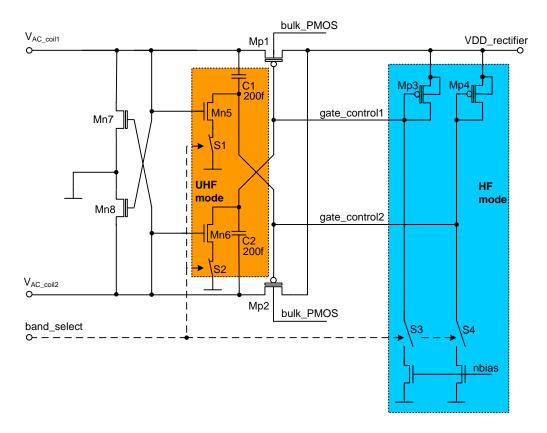

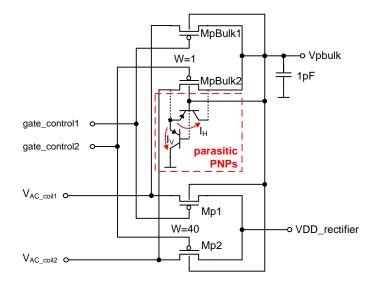

|                   | Core module of the CTS rectifier                                                                                              | 50             |

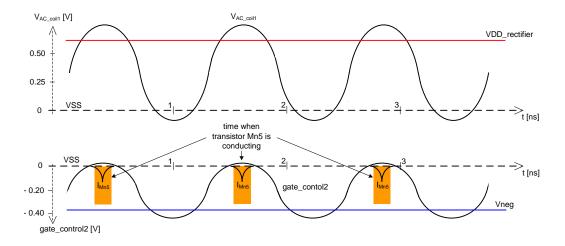

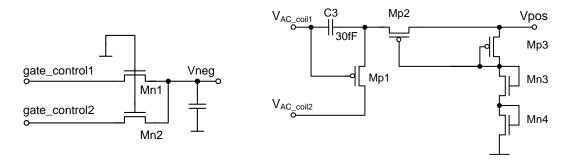

|                   | Gate control in UHF mode and generation of the negative secondary voltage Vneg                                                | 51             |

| 4.26              | Negative charge pump                                                                                                          | 51             |

| 4.27              | Positive charge pump                                                                                                          | 51             |

| 4.28              | HF magnetic field strength sweep and bearing of some internal power path nodes                                                | 52             |

| 4.29              | UHF power sweep at the rectifier and the impact on power path nodes                                                           | 53             |

| 4.30              | Concept for generating the highest DC voltage from the AC antenna voltage                                                     | 54             |

## List of Figures

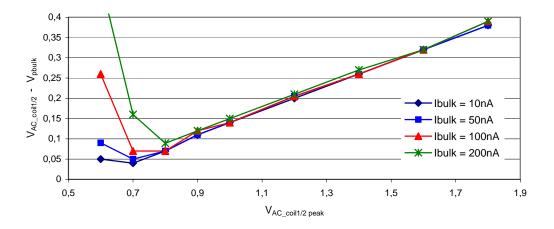

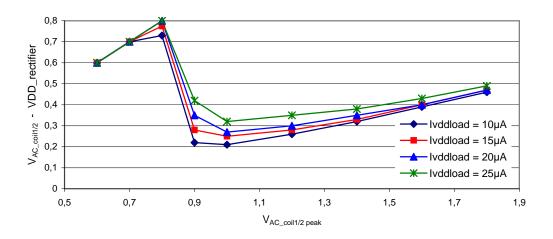

| 4.31 | Difference between coil-peak and Vpbulk-DC voltage                                   | 55 |

|------|--------------------------------------------------------------------------------------|----|

| 4.32 | Difference between coil-peak and Vrectifier-DC voltage                               | 55 |

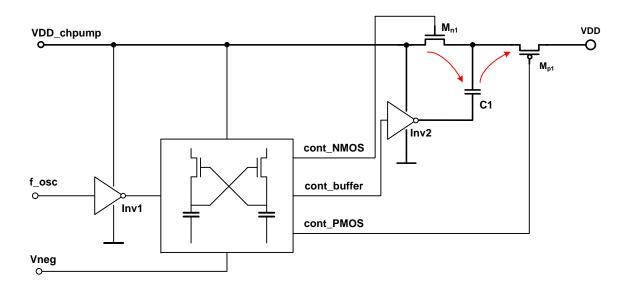

| 4.33 | Architecture of the CTS single stage charge pump                                     | 56 |

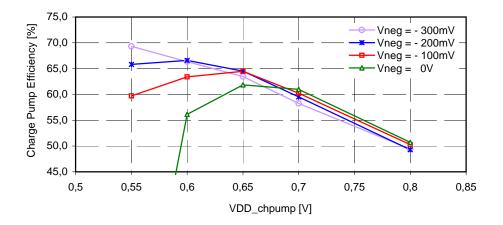

| 4.34 | Measured power transfer efficiency versus Vneg voltage level                         | 57 |

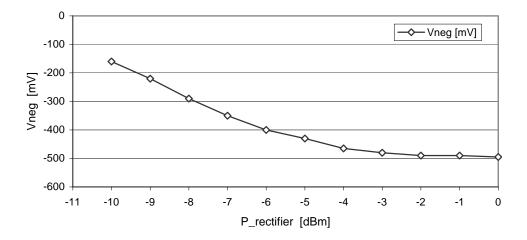

| 4.35 | Measured negative charge pump Vneg versus incoming rectifier power                   | 57 |

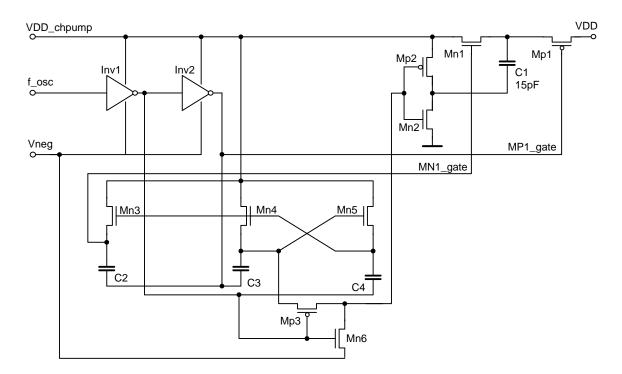

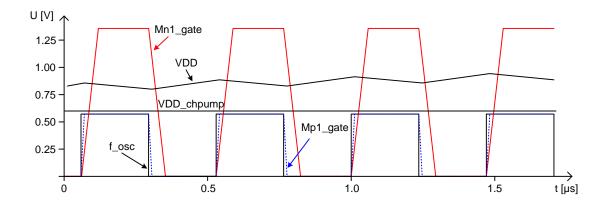

| 4.36 | Schematic of the CTS charge pump                                                     | 58 |

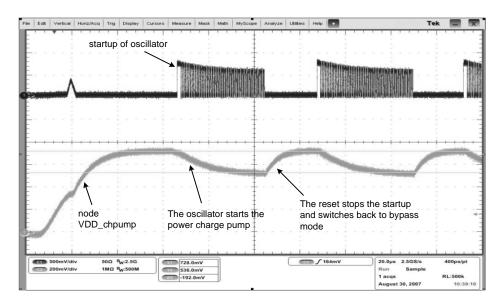

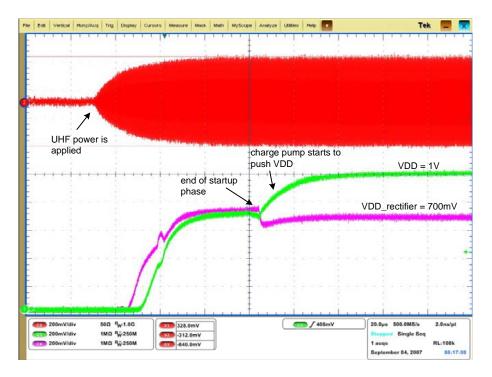

| 4.37 | Some transient nodes of the DC/DC converter during charging of VDD_internal          | 59 |

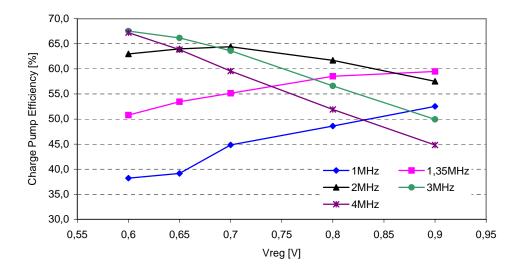

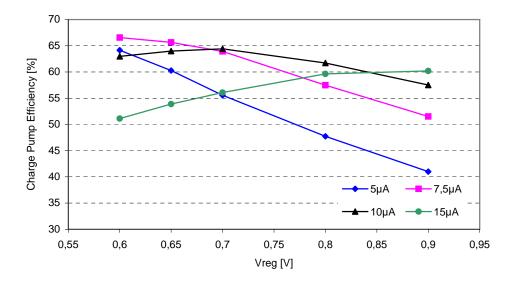

| 4.38 | Charge pump efficiency versus local oscillator frequency at constant load (Vreg =    |    |

|      | VDD_chpump)                                                                          | 59 |

| 4.39 | Charge pump efficiency versus different constant load current at constant oscillator |    |

|      | frequency (Vreg = VDD_chpump)                                                        | 60 |

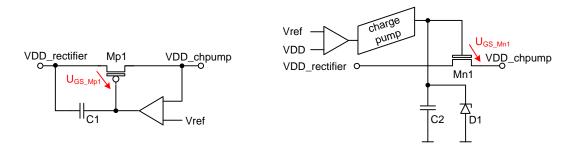

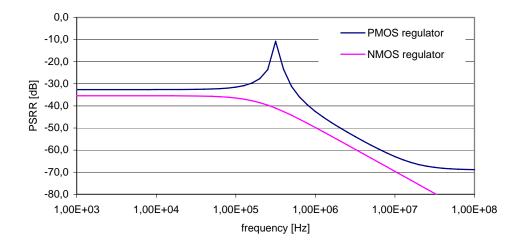

|      | PMOS or NMOS transistor used as power regulator                                      | 60 |

| 4.41 | PSRR Comparison of NMOS and PMOS serial regulator with same testbench and            |    |

|      | similar transistor geometry                                                          | 61 |

|      | Detailed schematic of the serial regulator                                           | 62 |

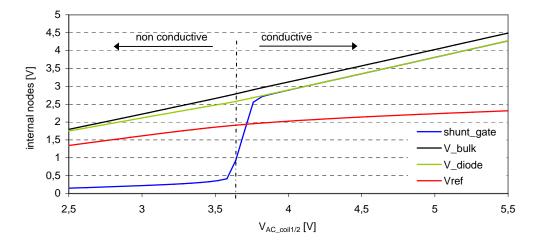

|      | Serial regulator nodes measured at different Coil or Antenna voltages                | 63 |

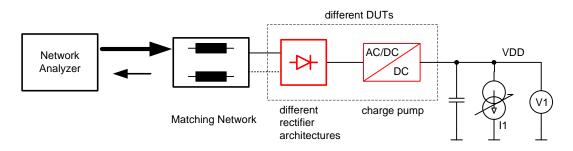

|      | Some rectifier architectures are measured and finally compared                       | 63 |

|      | A cross-coupled and a constant bias voltage controlled rectifier                     | 64 |

|      | Unbalanced Schottky diode rectifier with generation of negative secondary potential  | 64 |

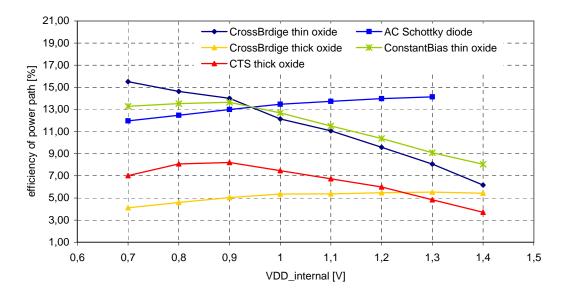

| 4.47 | Comparison of different rectifier architectures and the impact on the overall power  |    |

|      | path efficiency                                                                      | 65 |

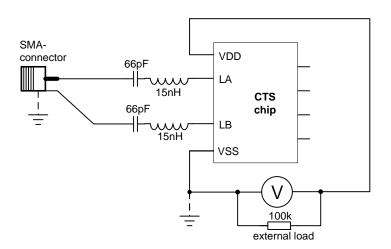

|      | Circuitry for incoming power measuring versus generated DC voltage                   | 66 |

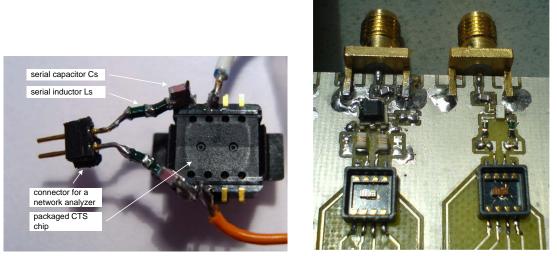

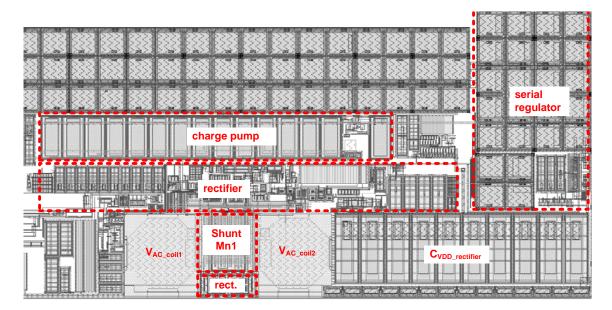

|      | Optional caption for list of figures                                                 | 67 |

| 4.50 | Modules necessary for the power generation of the CTS chip                           | 67 |

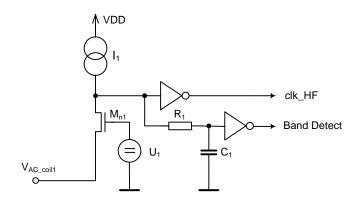

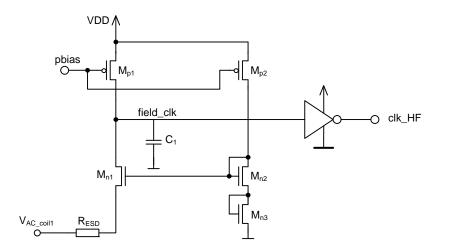

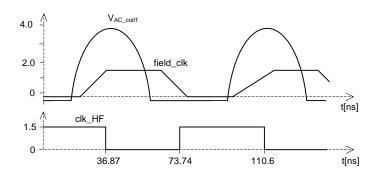

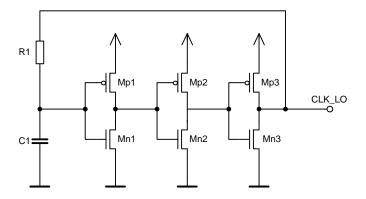

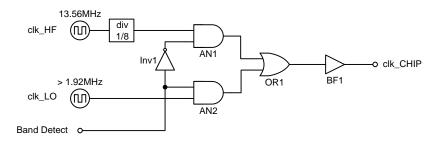

| 5.1  | Block architecture of clock recovery and band detect                                 | 70 |

| 5.2  | HF clock recovery                                                                    | 71 |

| 5.3  | Timing - HF clock recovery                                                           | 71 |

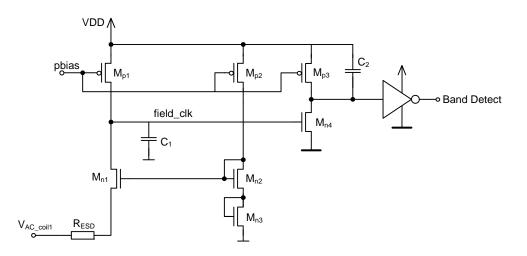

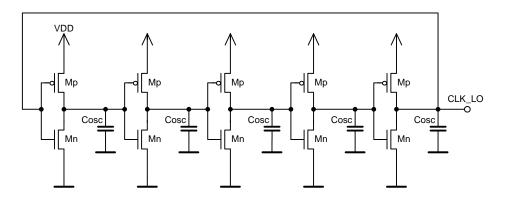

| 5.4  | Frequency band detection unit                                                        | 72 |

| 5.5  | Reader to tag preamble is part of the EPC specification [EPC07a]                     | 72 |

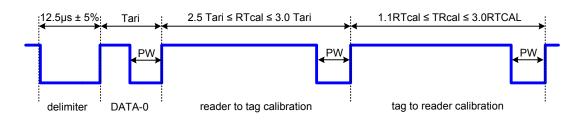

| 5.6  | Ring oscillator with weak inverter-stages                                            | 74 |

| 5.7  | RC-time defined oscillator with inverter as amplifier                                | 75 |

| 5.8  | Current Controlled Oscillator (CCO)                                                  | 76 |

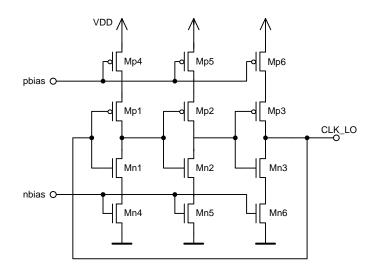

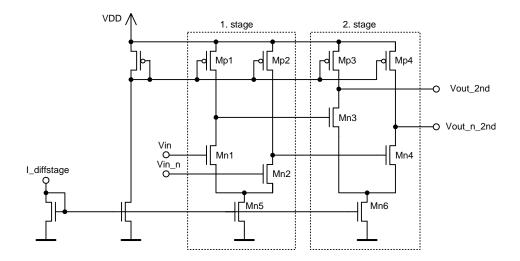

| 5.9  | Two units of an oscillator with differential stages                                  | 76 |

| 5.10 | Optional caption for list of figures                                                 | 77 |

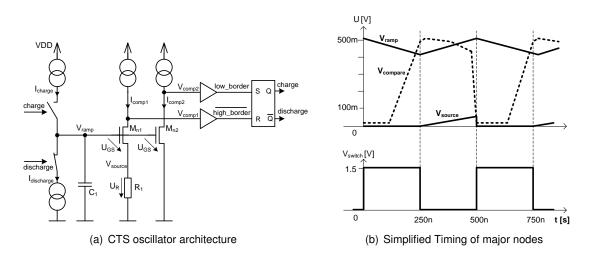

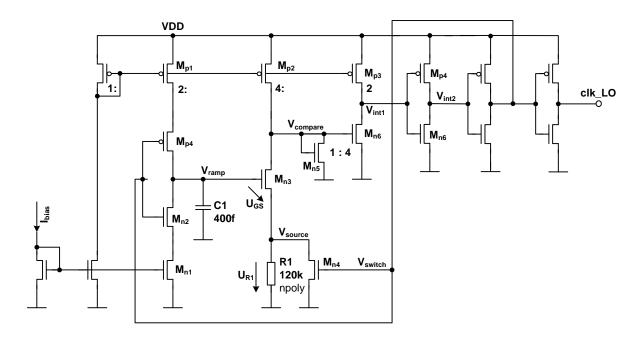

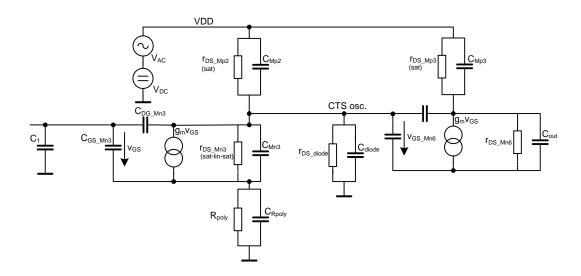

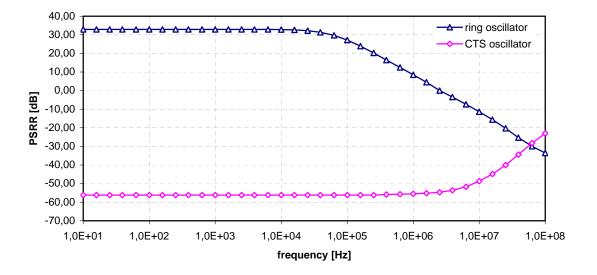

| 5.11 | New CTS relaxation oscillator                                                        | 78 |

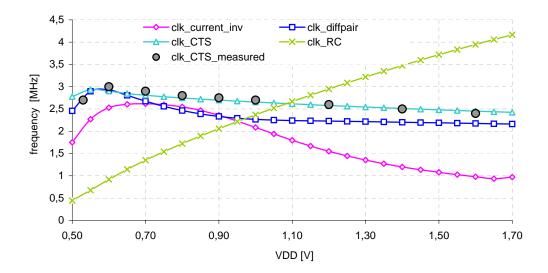

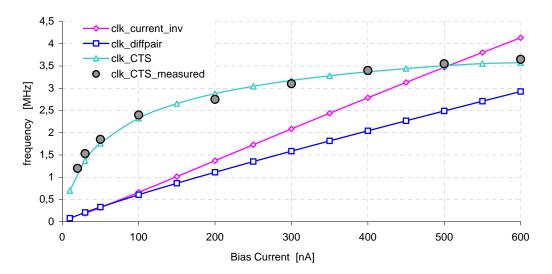

| 5.12 | Power supply variation                                                               | 79 |

| 5.13 | Bias current sweep                                                                   | 80 |

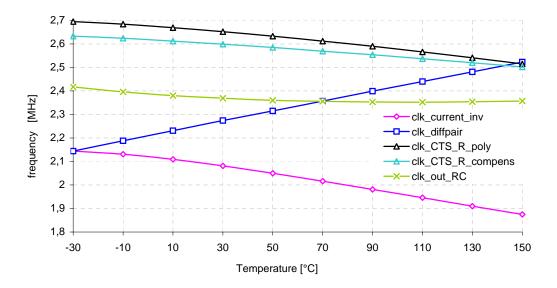

| 5.14 | Temperature sweep                                                                    | 81 |

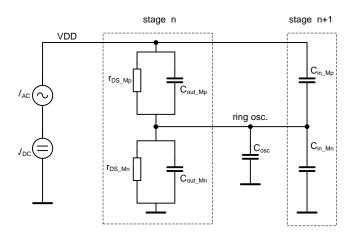

| 5.15 | AC circuit of one ring oscillator stage                                              | 82 |

| 5.16 | AC circuit CTS oscillator core                                                       | 82 |

| 5.17 | PSRR Comparison between ring and CTS oscillator                                      | 83 |

| 5.18 | Generation of two clock sources the master clock of the chip                         | 83 |

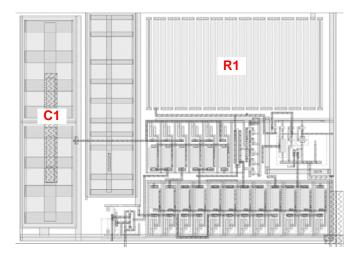

| 5.19 | Layout of the CTS oscillator                                                         | 84 |

|      |                                                                                      |    |

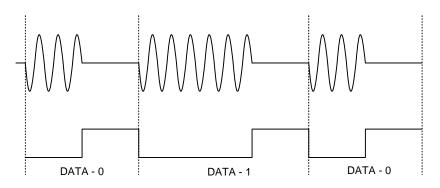

| 6.1  | Pulse interval coding and ASK with 18% down to 100% modulation depth are used        |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | for RxD                                                                              | 85  |

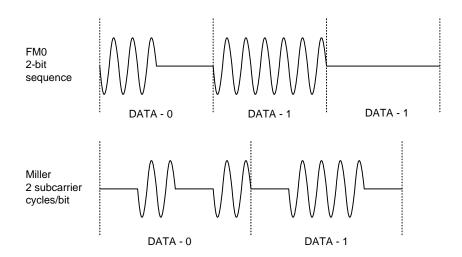

| 6.2  | Uplink - Two examples of operation                                                   | 87  |

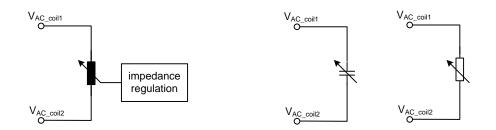

| 6.3  | Impedance control by a regulation loop. Could be either capacitive detuning or       |     |

|      | resistive load change                                                                | 88  |

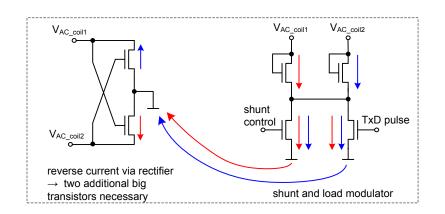

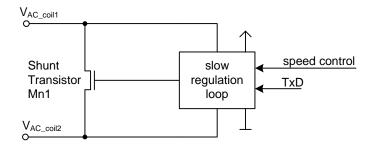

| 6.4  | A common shunt/load-modulator structure of a HF TAG                                  | 88  |

| 6.5  | In UHF the shunt is situated behind the rectifier/charge pump. The TxD module is     |     |

|      | typically located in front of the rectifier                                          | 89  |

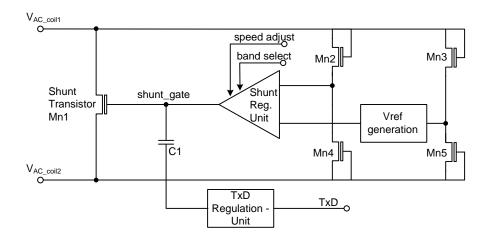

| 6.6  | CTS chip voltage limiter with one shunt transistor directly between the antenna      |     |

|      | terminals and a slow regulation loop                                                 | 90  |

| 6.7  | Some parameters to determine the shunt transistor dimension                          | 90  |

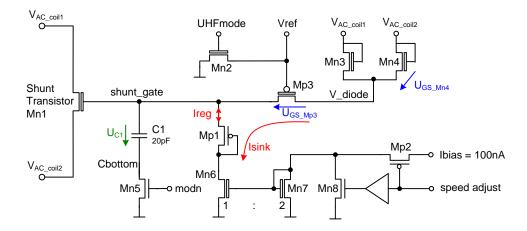

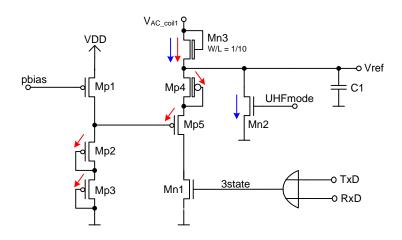

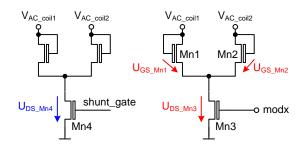

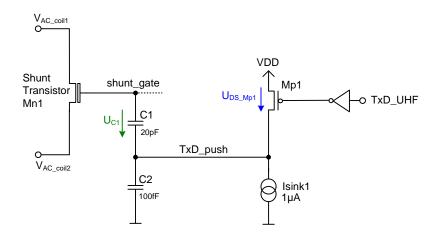

| 6.8  | More detailed voltage limiter concept with integrated TxD unit                       | 93  |

| 6.9  | Detailed shunt regulation loop                                                       | 93  |

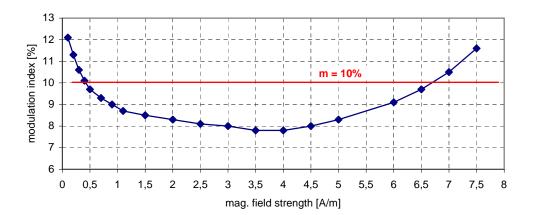

|      | A modulation index applied of m=10% is compressed by the CTS shunt down to           |     |

|      | 8% voltage change at the coil                                                        | 95  |

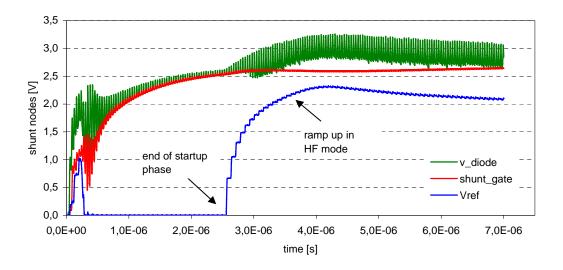

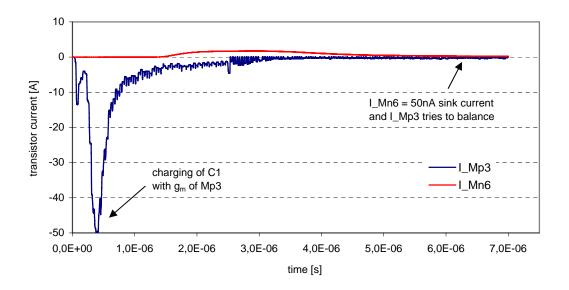

| 6.11 | A maximum field-strength of 10mA/m HF mode startup phase                             | 97  |

|      | Charging current $I_{Mo3}$ and balanced current in normal shunt mode $\ldots$        | 97  |

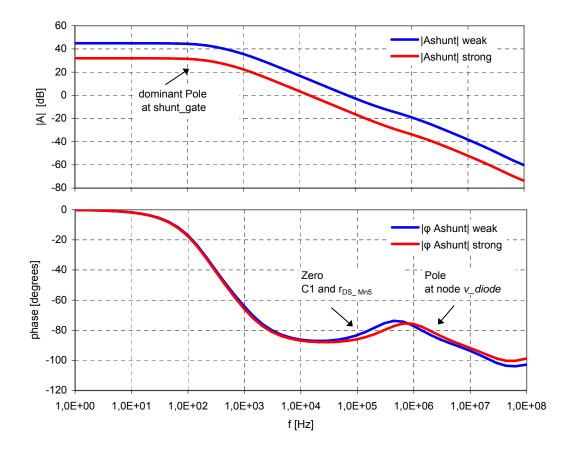

|      | AC small signal simulation in conditions equivalent to weak an strong field-strength | 99  |

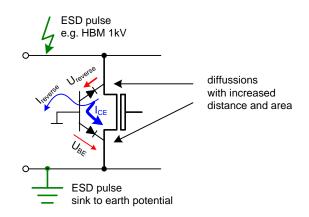

|      | Activation of parasitic bipolar transistor during ESD stress                         | 99  |

|      | Gate voltage generation for the PMOS Regulator                                       | 100 |

|      | Vref variation during active shunt area of only 380mV                                | 101 |

|      | A typical schematic for commercial products with separate shunt and TxD path,        | 101 |

| 0.17 | each equipped with a rectifier                                                       | 102 |

| 6 18 | TxD Unit for HF load modulation                                                      | 102 |

|      | Control signals of the shunt/modulator for EPC-HF Gen2 at 53kbit/s load modula-      | 102 |

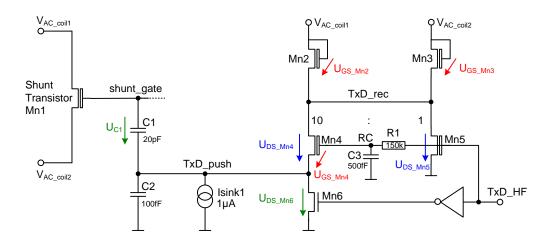

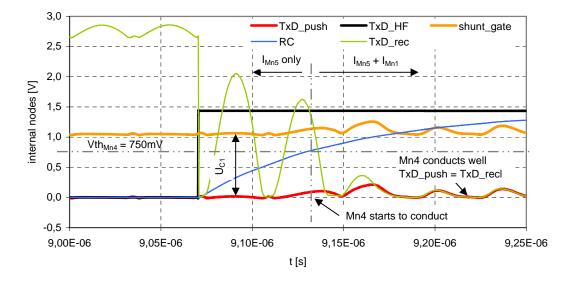

| 0.10 | tion and moderate field-strength                                                     | 103 |

| 6 20 | HF load modulation at 1.5A/m                                                         | 104 |

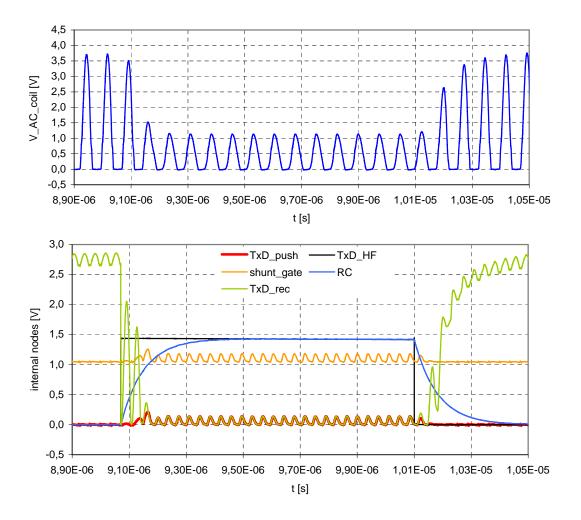

|      | Zoomed start phase of HF load modulation                                             | 105 |

|      | TxD Unit for UHF backscatter                                                         | 107 |

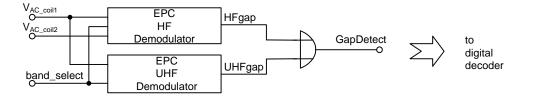

|      | Two specialized analog demodulators are used in the CTS project                      | 107 |

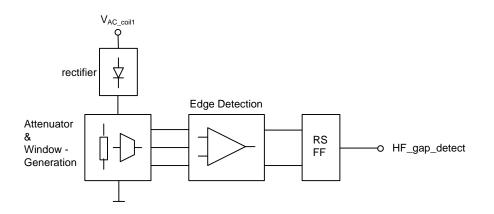

|      | CTS HF demodulator block schematic                                                   | 108 |

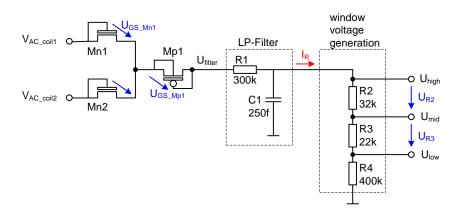

|      | Attenuator, low-pass filter and window voltage generation                            | 108 |

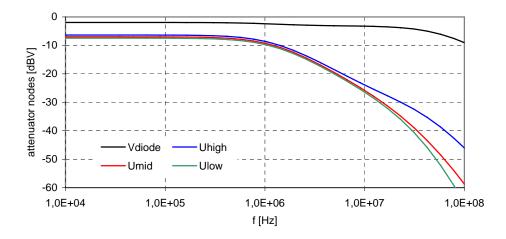

|      | Small signal AC analysis of the input attenuator                                     | 110 |

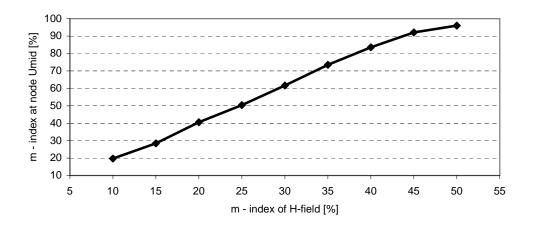

|      | The modulation index - m is almost doubled at node $U_{mid}$                         | 110 |

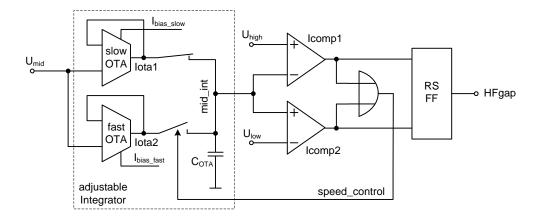

|      | Edge detector with adjustable integrator and 1 bit ADC                               | 111 |

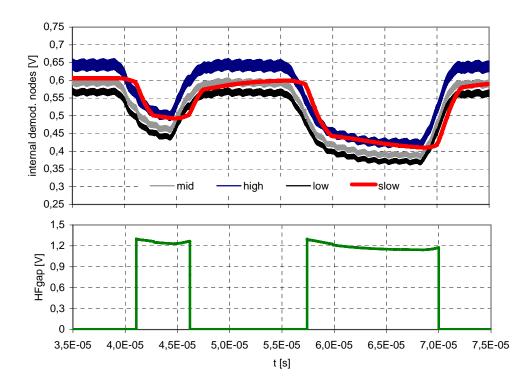

|      | Signals at the comparators and the resulting gap-detecting signal after the RS-FF    | 112 |

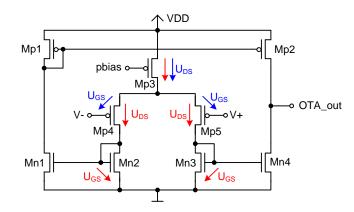

|      | OTA used in the edge detector for slow and fast integrator path                      | 113 |

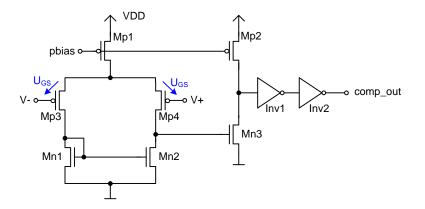

|      | Comparators used to detect either a rising or a falling coil voltage                 | 113 |

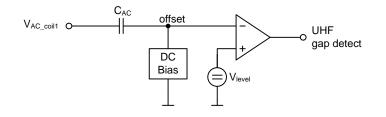

|      | Low power ASK demodulator concept for the UHF frequency band                         | 114 |

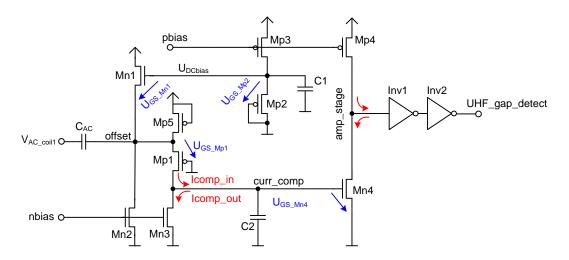

|      | CTS UHF demodulator                                                                  | 114 |

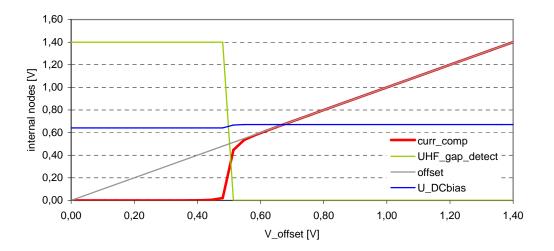

|      | DC sweep of node <i>of fset</i> and current comparator reply                         | 115 |

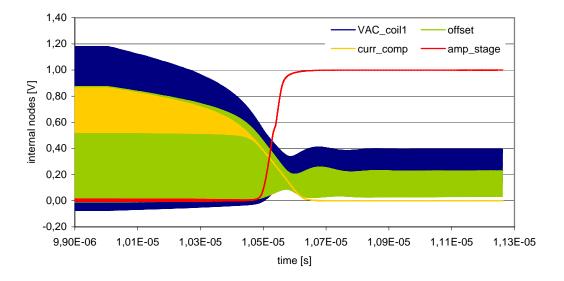

|      | Start of an UHF gap in moderate field strength conditions                            | 116 |

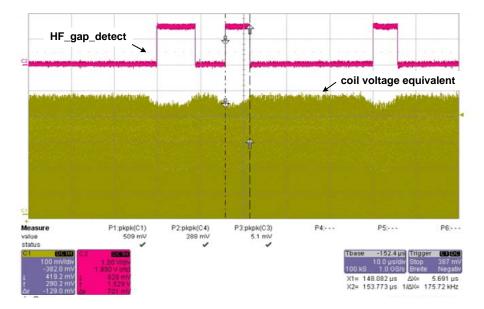

|      | 10% modulation index response of the HF demodulator                                  | 117 |

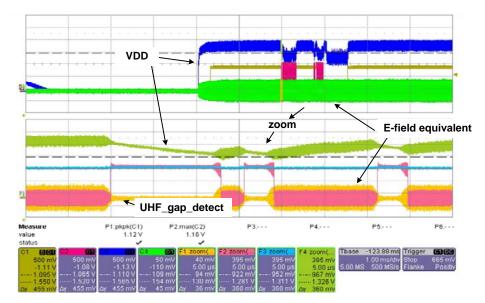

|      | Response of the UHF demodulator on field strength variations                         | 118 |

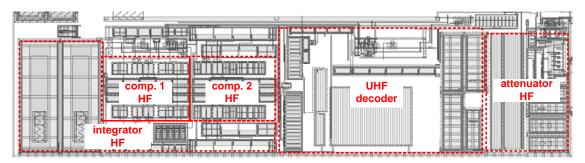

|      | HF and UHF decoder layout - the lowest two metals are routed                         | 118 |

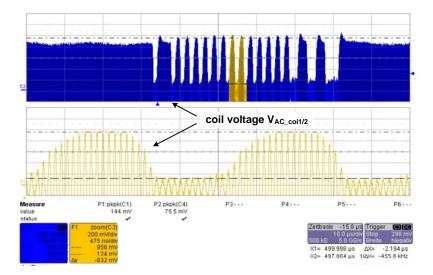

|      | Load modulation response of the coil voltage $V_{AC_{coil1/2}}$                      | 119 |

|      |                                                                                      |     |

## List of Figures

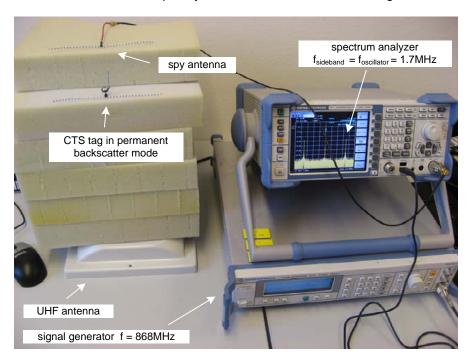

| 6.40 | One way to measure the internal oscillator frequency is to operate the TxD backscat-                       |     |

|------|------------------------------------------------------------------------------------------------------------|-----|

|      | ter unit straight with the LO                                                                              | 120 |

| 6.41 | HF reader antenna (left side) and UHF reader antenna (in the background). In                               |     |

|      | between the CTS transponder                                                                                | 121 |

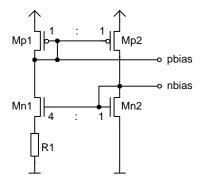

| 7.1  | Standard beta-multiplier circuit for good power supply rejection                                           | 123 |

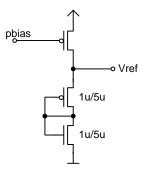

| 7.2  | Reference voltage generation                                                                               | 124 |

| 7.3  | Power Up/Down reset with unidirectional lagging                                                            | 124 |

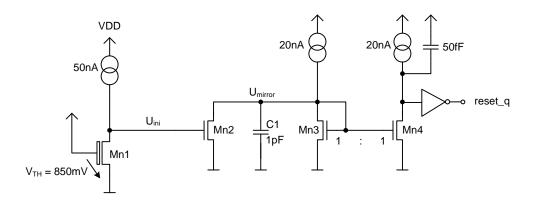

| 7.4  | Impact of the power down reset on the local oscillator in weak UHF field                                   | 126 |

| 7.5  | Start-up when minimum UHF power is applied to the tag antenna                                              | 127 |

| 7.6  | HF field of 1A/m is applied to the tag antenna                                                             | 127 |

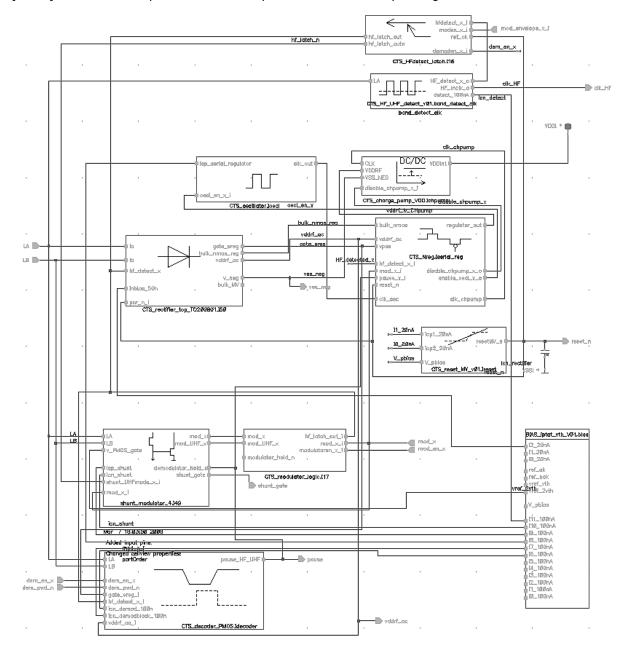

| 7.7  | CADENCE CTS top schematic view                                                                             | 128 |

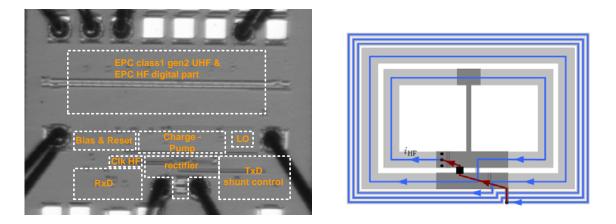

| 8.1  | Bonded CTS chip with modules and CTS antenna with chip and HF current flow $% \mathcal{A} = \mathcal{A}$ . | 131 |

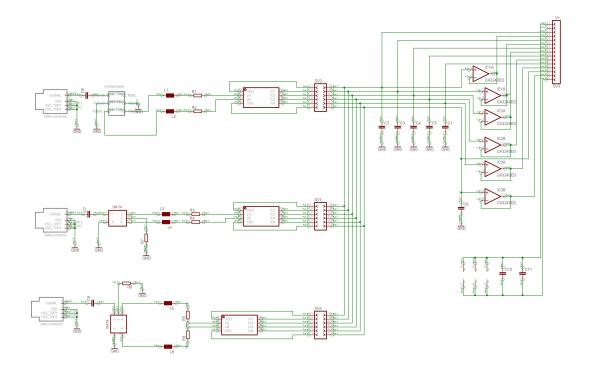

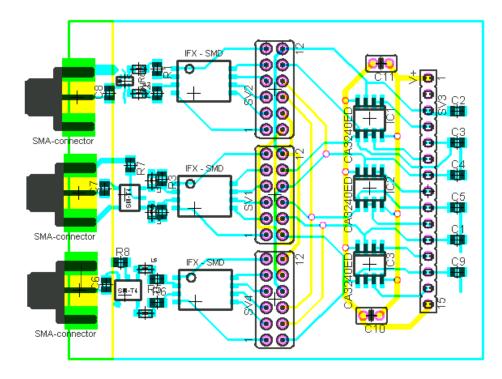

| A.1  | CTS Testboard schematic                                                                                    | 133 |

| A.2  | CTS Testboard layout                                                                                       | 134 |

## **List of Tables**

| 1.1 | Most common frequency bands and characteristics                                          | 18  |

|-----|------------------------------------------------------------------------------------------|-----|

|     | EPC specification for TxD       Different modulation types and power loading             |     |

| 7.1 | Simulation results for $Vref$ at its worst case temperature and technology split corners | 123 |

List of Tables

## Nomenclature

- AC Alternating Current

- AFE Analog Front End

- AM Amplitude Modulation

- ASK Amplitude Shift Keying

- CCO Current Controlled Oscillator

- CL ContactLess

- CMOS Complementary Metal Oxide Semiconductor

- CTAT Complementary To Absolute Temperature

- CTS Comprehensive Transponder Systems

- DC Direct Current

- DUT Device Under Test

- EAS Electronic Article Surveillance

- EEPROM Electrically Erasable Programmable Read Only Memory

- ENOB Effective Number Of Bits

- EPC Electronic Product Code

- FIT-IT Forschung, Innovation, Technologie Informationstechnologie

- GDS Global Data Synchronization

- HF High Frequency

- IC Integrated Circuit

- ICO Current Controlled Oscillator

- ID Identification Number

- ISM Industrial Scientific and Medical

- ISO International Standards Organization

- LF Low Frequency

### List of Tables

LO Local Oscillator

MIM capacitor Metal Isolator Metal - capacitor

- MIT Massachusetts Institute of Technology

- NVM Non Volatile Memory

- OTA Operational Transconductance Amplifier

- PCB Printed Circuit Board

- PPM Parts Per Million

- PTAT Proportional To Absolute Temperature

- RF Radio Frequency

- RFID Radio Frequency IDentification

- RxD Receive Data

- SCR Silicon Controlled Rectifier

- TO Tape-out

- TxD Transmit Data

- UHF Ultra High Frequency

- VCO Voltage Controlled Oscillator

## **1 Motivation - The CTS Project**

Several ISM frequency bands are defined for RFID applications and so far three of them - LF, HF and UHF - have been established worldwide. To profit from frequency band synergies, a new chip for transport and identification will be developed during the CTS (Comprehensive Transponder Systems) project.

## 1.1 The CTS - Comprehensive Transponder Systems Project

As LF transponders are not used in transport applications because of higher transponder costs, size and low read distance, the CTS chip does not focus on this band. The next higher RFID frequency band is the popular HF 13.56MHz ISM band, which is approved worldwide with similar power levels; therefore it is the most universal frequency band. Tag operation distance is well defined to approximately half a meter with small reader antennas. In the UHF frequency band around 900MHz we have country specific frequency slots with different power levels. Already close to the micro wave band the popular 2.45GHz slot is also available for RFID applications. All UHF 900MHz low power tags are designed for far field operation and can reach a distance of about 5 meter. Electrical far field radar reflections are typical for higher frequencies where the wave is already solved from the antenna. The low damping factor in the far field causes a maximum tag operational distances of 10 meter [LKL06]. Compared to HF, this 20 times higher distance could also be a disadvantage when privacy or other reasons for a reliable low distance operation are desired. Shielding or multiple reader systems with distance estimation are necessary for a traceable reduced operation distance. Both methods to reduce the UHF operation distance are very expensive compared to the new CTS proposal. Material sensitivity of radiated waves could also be a reason to go either for a UHF- or for a HF - RFID system [BMU09]. In table 1.1 some differences and affinities of the three most frequently used RFID bands are shown. It illustrates the specific benefits of each frequency band.

The aim of the frequency band comprehensive project is to combine a multiple selective antenna, a single port analog frontend and a digital control unit to one chip. The CTS demonstrator which consists of an antenna and an attached IC shows the benefits of a frequency band comprehensive transponder system.

To be cost-competitive, the CTS chip area of the analog and of the digital module are similar to single band products. Most of the chip modules are able to support the 13.56MHz HF band as well as the 900MHz UHF frequency band. Some minor modules are single frequency selective only. If both frequencies are applied simultaneously, the chip can choose which band will be the preferred one. Typically, the IC will prefer the HF band, because the transponder has to be very close to the reader antenna; therefore, the possibility of an intended HF communication is very high.

Moreover, the CTS antenna costs and performance should be comparable to commercial HF coil

### 1 Motivation - The CTS Project

| Frequency band             | LF         | HF                       | UHF                 |  |

|----------------------------|------------|--------------------------|---------------------|--|

| Frequency range            | 125/134kHz | 13.56MHz                 | 860 - 960MHz        |  |

| Typical operating distance | 10cm       | 50cm                     | 5m                  |  |

| Tag costs                  | high       | medium                   | low                 |  |

| Skin depth<br>of water     | 8m         | 2m                       | 4cm                 |  |

| Typical<br>Tag design      |            | EIE                      | O 176854-801 HEY 4D |  |

|                            | Sokymat ®  | Infineon Technologies AG | Alien ®             |  |

Table 1.1: Most common frequency bands and characteristics

antennas. Finally, from the overall transponder cost point of view, the CTS chip can be compared to a typical HF tag and delivers the UHF functionality as an important additional feature.

The intent of this work was to design an analog front end for passive RFID with two antenna pads (single port) which can operate either in the HF or UHF frequency band. Power generation and communication units have to fulfill air interface requirements according to the chosen EPC-global specifications. A low cost 120nm CMOS Infineon process with EEPROM option was used without special RF transistors or Schottky diodes. Within the scope of the technology limitations, the chip performance was measured and compared to single frequency ICs. According to the chip input impedance, an impedance matching comprehensive transponder antenna was developed together with the Vienna University of Technology - Institute of Communications.

The chip was developed at Infineon Technologies Design Center Graz in cooperation with the Institute of Electronics at Graz University of Technology. The project was funded by the Austrian research funding agency FFG with the program FIT-IT and Infineon Technologies Austria AG.

This thesis comprises the development and design of the analog front end for the CTS chip. In the course of the project four new CMOS low power design concepts were developed and presented at international conferences [MKP<sup>+</sup>08] [MKH07] [KMP<sup>+</sup>08] [MHP10]. These design concepts are described in the following chapters of this thesis:

### **Chapter 4 - Power Generation Units**

After a short introduction in Chapter 2 the power generation module, which is necessary for a good power performance, will be discussed and the new CTS power supply design architecture will be introduced. The final power path design is a compromise between the power generation performance for both frequency bands and a robust RxD and TxD communication. Also impedance matching between the analog front end of the IC and the selective CTS antenna will be mentioned. Several alternative rectifier concepts then will be reviewed. Finally, power path performance measurement results and the chip layout of this module will be illustrated in this chapter.

### **Chapter 5 - Clock Generation Units**

Beside the HF clock recovery module, which derives the clock signal directly from the alternating coil voltage, a low-power local oscillator at about 2MHz is necessary. In this section, a new low-voltage and low-power relaxation oscillator will be presented and will be compared with conventional UHF RFID oscillator designs. Measurement results of several design studies and the module layout will conclude this chapter.

#### **Chapter 6 - Contactless Communication Units**

A new UHF RxD DC bias generation scheme and a new HF/UHF TxD unit applicable for both frequency bands will be introduced in this chapter. Due to this load modulator and backscatter concept not only the power transistor area but also the parasitic capacitance are reduced significantly compared to common modulator implementations.

#### Chapter 7 - Secondary Units and top cell

In this chapter, bias current and reference voltage generation will be shown. Next, minor modules like a power-down reset unit or the impact of the frequency band selector will be presented. Last, in the CADANCE top cell schematic all previously mentioned CTS modules will be shown interconnected.

#### **Chapter 8 - Research Summary and Outlook**

In the concluding chapter, the research and evaluation section of this thesis will be provided.. The extended research summary will mention all innovative highlights of this work and will refer to publications and submitted invention disclosures. Finally, an outlook with some ideas for future improvements will be listed. 1 Motivation - The CTS Project

## 1.2 Project progress

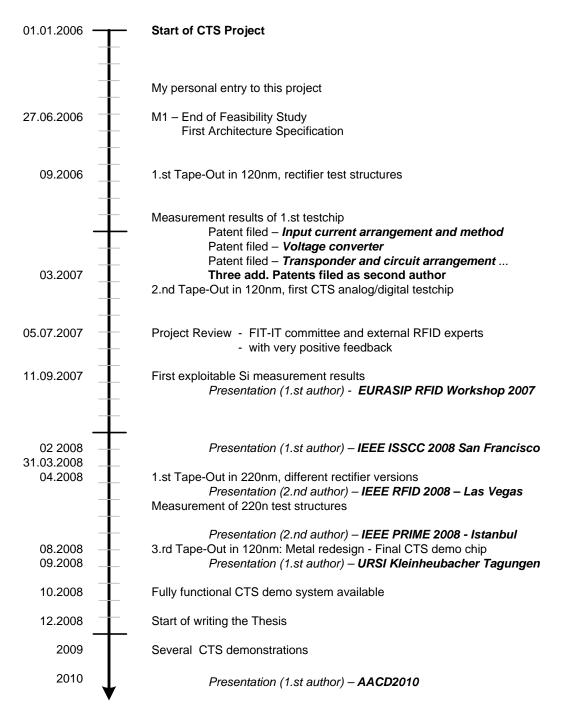

The time line shows the progress and achievements of the CTS project. The nominal duration of a FIT-IT funded project usually amounts to two years. As the last tape-out was delayed by half a year till summer 2008, the duration of the CTS project was extended by 3 additional months to the end of March 2008.

## 2 Introduction to passive RFID

RFID can be a major technology enabler or a simple supplement. RFID is already used in different quantity in payment, identification, supply chains, packaging, sensor network and many other applications. RFID is launched in the LF frequency band or even in the microwave band (SHF).

The bandwidth of these segments grows with inventive market requirements and with the corresponding technical RFID solution in response. A general passive RFID introduction will not be given in this thesis. Detailed information about the broad field of passive RFID can be found in literature [Fin06] [FKFS02] [Bak07] [Ker06] and [CH07].

EPCglobal AUTO-ID labs have defined UHF as the preferred RFID band and the latest EPCglobal Class-1 Generation-2 specification. Meanwhile, labs also have been working together with companies to establish an EPC standard for the 13.56MHz HF band, which will finally be similar to existing standards. The availability of similar standards for two frequency bands favors EPCglobal to be used in the CTS chip. A short general historical survey about the origin of the EPC standard and about the current efforts to establish RFID as one important EPC medium will be given in the following:

## 2.1 EPC Standard linked with Passive RFID

Using the Electronic Product Code (EPC) it is possible to identify every object with an ubiquitous and globally singular code. Attached to a worldwide network and compatible software infrastructure - to the Global Data Synchronization (GDS) - it should be possible to define the appearance of each object in the database or to get information from each EPC tagged object [Eng02]. In 1999, the first AUTO-ID Lab Center was established at the MIT in Chicago. In the following years several centers were set up all over the world. Soon a RFID supply chain management flow was established and finally standardized. AUTO-ID lab recommends the 900MHz UHF band as target frequency band because of its increased read distance and additional high data-rate compared to former established RFID standards. Only a well defined small memory size is necessary to store the EPC number [War06]. All these restrictions will result in a small and cheap EPCglobal compliant chip. In UHF, the antenna can be designed within one metal layer which is also cheaper compared to lower frequency coils.

EPC air interface standards Class 0 and Class 1 were defined in the early AUTO-ID Lab formation phase. As these two additional standards are not compliant and not optimized for EPC requirements, the new Class1 - Generation 2 standard was ratified 2006 by the Internal Organization for Standardization as ISO 18000-6C [Bak07] [Ker06] [EPC07a]. In 2005, Wal-Mart in the USA and Metro in Europe already started to use tagged pallets and transport cases in the commercial logistics flow.

#### 2 Introduction to passive RFID

A pre-released EPC specification - the "HF Version 2 Draft Version 0.3" [EPC07b] - was published in 2007, is very similar to the UHF EPC specification and it also shows affinity to the HF vicinity standard. An official HF Generation 2 tag protocol standard is still not available and will be published soon at *www.epcglobalinc.org*. We started the CTS project with the very first Version 0.0 and modified our latest CTS product according to Version 0.3.

Why use RFID alongside bar-code or other printed optical coding concepts which are unrivaled in price? Some benefits of an EPC RFID supported logistics chain could be:

- Increased speed of supply chain cycles all items are recognized quickly worldwide by an unique code

- · It is not necessary to search for the barcode on the product any more

- · Additional electronic information can be stored directly on this item

- EAS anti-theft protection combined with smart-shelf technology alerts the staff earlier [Sys03]

- The chip can be locked with a key and a kill command. No information is passed over to unknown individuals.

Obviously, there are also concerns about data privacy and data security or production cost disadvantages when RFID is used instead of printed paper labels. However, to balance the pros and cons of using RFID for an application is the task of the systems integrator after all.

## 2.2 CTS transponder - An application example

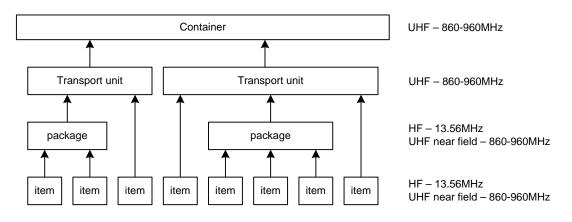

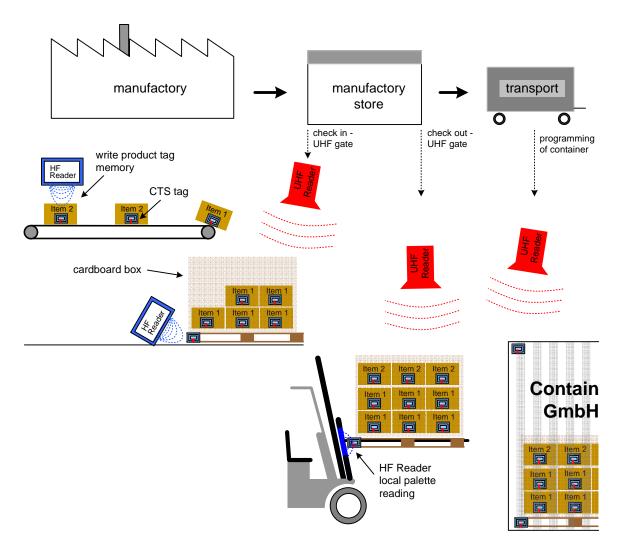

Let me take transport and logistics to explain and show the benefits of using a multi frequency RFID tag. Figure 2.2 shows products which are manufactured in a factory, stored and finally carried on transport vehicles to local outlets or international key account customers. On several items, a CTS transponder is attached. The question is when to use either the HF or the UHF band for communication. The customer could decide to use one of the two frequency bands for best performance. One feasible fragmentation for a transport application is shown in figure 2.1. When individual items are programmed, operation distance should be short and reliable because only this target unit in front of the reader antenna should be programmed and prepared. For this application, it is appropriate to use short-range HF RFID. For capturing the according IDs of items in a region around the reader antenna, a far distance application like RFID UHF is necessary. This hierarchy view is transformed into the transport flow shown in figure 2.2. In this example, the customer would like to get the products packaged in a cardboard box. 6 items of type 1 and 3 items of type 2 should be placed into each box. To be able to track each item stored in the container already during the production phase, each product is signed with its unique ID (identification number) with the help of an HF reader. The type of product is also stored in the tag memory. When the box is carried into the factory store, a final scan with a UHF reader could read all items at once and check each box for completeness. A central computer records all incoming and outgoing products and guarantees an accurate manufactory store data base. On each pallet a CTS tag can be accessed by an HF reader. This HF reader is mounted on a fork-lift truck to

### 2.3 EPC Global Regulations

Figure 2.1: HF and UHF RFID systems in transportation

check if the driver has taken the right pallet. Finally, outside on the container skin one CTS chip packaged in a special outdoor label could store the content of the container.

## 2.3 EPC Global Regulations

Why did we choose EPC HF and UHF as air interface standard?

Digital:

In a CTS related diploma thesis by Johann Heyszl [Hey07] a detailed comparison of how to merge different RFID standards into one homogeneous digital interface was performed. The result was a clear preference for a combination of the EPCglobal version 2 standards (UHF Gen2 and HF version 0) because both use the EPCglobal UHF Gen2 logic layer. Digital encoder and decoder are very similar and the number of gates overhead is small. Also a control logic for analog modules was implemented in the digital unit.

Analog:

For the analog power generation unit, the big frequency step of a factor of 64 between HF and UHF frequency bands was more significant than the question of the chosen protocol standard. Only two RF pads and a high reuse of transistors are the essential goals of the CTS project in order to minimize the area overhead. As regards the TxD communication unit architecture and the voltage limiter, the separation between the two frequency bands was done with a small transistor overhead. For the RxD path two separated demodulators were designed for HF and UHF. As these module areas are small, the disadvantage in the total chip area is negligible.

### 2.3.1 EPC standards

As already mentioned, the following air interface protocol standards are used during the CTS project:

• EPCglobal HF Version 2, Draft Version 0.3 [EPC07b] (pre-release)

2 Introduction to passive RFID

Figure 2.2: CTS tags are fixed on label products, pallets and container

• EPCglobal UHF Class 1 Generation 2 [EPC07a]

The final HF Generation 2 tag protocol standard is still pending. In each of the following chapters there are some EPCglobal standard numbers listed which are necessary to specify the features of the local oscillator, modulator and demodulators. There is no introduction or summary of the EPCglobal standards in this thesis but it can be downloaded from the EPCglobal homepage - www.epcglobalinc.org

## 2.4 Air interface parameters

The wavelength  $\lambda$  for a given frequency f can be written as [Fin06]:

$$\lambda = \frac{c}{f} \tag{2.1}$$

$c \approx 300.000 km/s$  is the velocity of light. The wavelength for UHF (868MHz) is about 34cm and for HF (13.56MHz) about 22.1m.

Damping factor:

In general, the magnetic or electric field damping in free space can be separated into two regions: The near-field region with a damping factor of -60dB/dec and the far-field region with a damping factor of -20dB/dec. In between, an intermediate zone - the Fresnel zone - smoothens the intersection between far and near field. In HF after a constant magnetic field strength region, the field drops by  $1/r^3$ . This is equivalent to -60dB/dec. For small HF antennas, the near field region ends at a distance r away from the antenna:

$$r = \frac{\lambda}{2 \cdot \Pi} \tag{2.2}$$

For HF conditions, this border is at about 3,5 m. At farther distances, the magnetic field strength decreases less rapidly and finally reaches a slope of -20dB/dec in the far field. Is the transponder in this far-field region, the residual field strength is far below the chip sensitivity [Kla09] [Fin06]. Thus, a passive HF RFID transponder will only operate properly in the near-field region.

For 868MHz UHF, the calculated near-field border is at about 5,4 cm. When the transponder is moved away from the reader antenna, it passes an intermediate zone, the radiating near field or *Fresnel region*. Equation 2.3 describes the end of the intermediate zone.

$$r > \frac{2 \cdot D^2}{\lambda} \tag{2.3}$$

D is the largest dimension of the reader antenna [m]. Farther away from the reader antenna the far field starts [Hol07] [Sto07]. This far-field region is also the normal operation distance for a UHF transponder. The damping is only -20dB/dec and guarantees operation distances up to 10 meters. Precondition is a low-power consumption of the chip and a reader which operates at its maximum allowed power level as shown in figure 4.2.

#### 2.4.1 Power Matching

Maximum power from the source to the load is transfered when power matching is fulfilled. The source impedance has to be conjugate-complex compared to the load impedance.

$$Z_{source} = Z_{load}^* \tag{2.4}$$

Especially in the UHF RFID band, a careful impedance matching is necessary for optimum performance. Radiation resistance and resistive conductor losses on the antenna system have to match with the non-linear chip input resistance. The resulting antenna inductance has to be matched with the non-linear chip input capacitance.

Another term for the impedance matching is the reflection coefficient value  $\rho$  or the S-parameter S11 value.

$$S_{11} = \frac{Z_{load} - Z_{source}^*}{Z_{load} - Z_{source}}$$

(2.5)

#### 2 Introduction to passive RFID

$$S_{11} = \sqrt{\frac{P_{reflected}}{P_{incoming}}}$$

(2.6)

In equation 2.6, the transferred power to the load is marked as  $P_{incoming}$  and the hopefully small reflected power amount at the input of the load is called  $P_{reflected}$ .

In real UHF RFID applications, the right matching will only be possible at a dedicated incoming power level close to the minimum power required to start the chip. Reason for this is the non-linear capacitance of the input stage which is formed by the semiconductor rectifier and the power generation circuits. Moreover, the chip resistance is non-linear and will therefore also cause a reduction of the performance of the tag. With a serial chip resistor value of  $15\Omega$  and even lower, the compatibility to the common  $50\Omega$  system is not valid anymore. This increases the measurement efforts when the antenna or chip has to be characterized.

#### 2.4.2 Quality Factor - Q

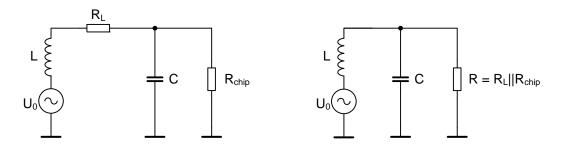

Beside the resonance frequency f<sub>res</sub>, the quality factor Q is the second characteristic number which describes a parallel or serial LRC resonance circuit [CR64]. Finally, after some simplifications the antenna to IC interface is similar to a parallel resonator as shown in figure 2.3. A very

Figure 2.3: Parallel RLC tank circuit

general description of the quality factor on power levels is presented in equation 2.7.

$$Q = \omega \cdot \frac{energy \ stored}{average \ power \ dissipated} \quad [Lee04]$$

(2.7)

Energy stored in a capacitor is handed over to an inductance once a period and is stored there for half a period. A part of this energy is dissipated during each cycle in the resistor R. This alternating current has to be considered when the on-chip metal wire width is calculated in order to avoid electro-migration problems when the current density gets too high. As the peak energy stored in the capacitor is the same as in the inductor, only one energy reservoir is considered in the following equations:

$$E_{blind} = \frac{C \cdot U^2}{2} = \frac{C \cdot (I_{pk}R)^2}{2}$$

(2.8)

$$P_{dissipated} = \frac{I_{pk}^2 \cdot R}{2} \tag{2.9}$$

Taking both formulas in relation, the maximum peak current  $I_{pk}$  can be extracted and only the component values of the LRC tank are in the final equation.

$$Q = \omega_0 \cdot \frac{E_{blind}}{P_{absorbed}} = \frac{R}{\sqrt{L/C}} = \frac{R}{\omega_0 \cdot L} = \omega_0 \cdot C \cdot R$$

(2.10)

This equation is valid for all frequencies and, therefore, valid for all passive RFID frequency bands.

Finally, the bandwidth of the resonance circuit is considered:

$$BW = \frac{\omega}{Q} \tag{2.11}$$

One definition of the bandwidth of a resonant circuit is shown in equation 2.11. The bandwidth B is inversely proportional to the quality factor Q. Higher data rates during communication cause a larger frequency gap between sideband and carrier. Damping of these sidebands is avoided when the Q factor is reduced. From the technical point of view, the reduction of the Q factor is not a problem, but with the smaller voltage multiplication the maximum operation distance will be reduced too. As already mentioned, all equations are valid only for sinusoidal signal wave forms. As passive RFID is supplied with big amplitude wave forms and the attached components like switches, diodes or transistor regulators are not linear, it is obvious that the weak input signal is not a sinusoidal wave form anymore and this reduces the accuracy of previously mentioned equations.

### 2.5 Air Interface Circuits

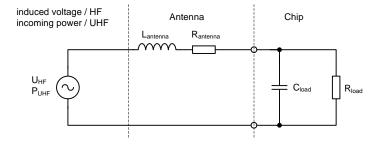

HF or UHF air interface circuits are similar to resonance circuits. Antenna and chip are represented with only two components. In figure 2.4 the source symbol represents the induced coil voltage or the received power delivered from the attached antenna. The mathematical conversion from magnetic field strength to an induced voltage and vice versa can be taken from [Fin06]. This simple air interface could be extended with parasitic or non-linear components to get a model

Figure 2.4: Equivalent tag electrical circuit

that is closer to the real application. Difficult to estimate are 3 dimensional resistive Si-substrate losses [KN99] and also DC voltage dependent junction-capacitors form active diffusions to the substrate. Special software tools used for spiral on-chip inductors will help to get an estimation of these substrate losses.

2 Introduction to passive RFID

## 2.6 How to combine different frequency bands?

As the number of chip pads on the CTS chip is limited to two and the form factor of the antenna is limited to a credit card format, the separation of both frequency bands with two analog interfaces for two antennas is not possible. One antenna which is selective at both frequency bands is attached to both balanced chip interface pads. Only one analog chip interface - especially one rectifier - is necessary to be compliant with the CTS interface definition. The challenge with taking only one antenna is getting two separated high quality factors - one at the HF and one at the UHF frequency band.

## **3 Infineon Si process information**

Next, a brief description of the used Infineon 120nm process will be given. All values are typical and do not include process variations (fast/slow) or temperature aspects.

### 3.1 MOS transistors - electrical parameters

Thin oxide transistors are used for digital and analog modules. They withstand a permanent power supply voltage of 1.5V (considering the short RFID product lifetime). The process option NVM memory (EEPROM) also delivers transistors with an increased oxide thickness - so called thick oxide transistors. These transistors can withstand a permanent voltage stress of 7V.

| transistor type    | V <sub>th₋typ</sub> | L <sub>min</sub> | R <sub>poly-</sub> /square |

|--------------------|---------------------|------------------|----------------------------|

| Thin oxide N/PMOS  | 350mV               | 120nm            | $5\Omega$                  |

| Thick oxide N/PMOS | 600mV               | 1000nm           | $200\Omega$                |

To be compliant with commercial HF RFID products, a coil voltage of 4V is necessary. Only the thick oxide transistor withstands the electrical field and have to be used close to the HF-coil/UHF-antenna.

However, thick oxide transistors have disadvantages at high frequencies:

The specific resistor of the thick oxide gate-poly is 40 times higher than that of the thin oxide transistor. It causes a delay in transistor switching and a reduction in the overall quality factor Q of the IC.

According to formula 3.1, maximum speed is reduced inversely proportionally to  $L^2$ . Moreover, at each power level applied to the antenna, the overdrive voltage  $V_{GS} - V_T$  is always smaller than thin oxide transistors [San08].

$$f_T = \frac{g_m}{2\pi C_{GS}} = \frac{3\mu}{4\pi L^2} (V_{GS} - V_T)$$

(3.1)

$$f_T \approx = \frac{v_{sat}}{2\pi L} \tag{3.2}$$

When one observes the disadvantages of thick oxide transistors, it becomes quite clear that in the long run, a performance loss in UHF operation will be the consequence compared to thin oxide transistors or Schottky diodes.

3 Infineon Si process information

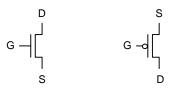

## 3.2 MOS transistors - Symbols

Especially at the interface antenna to chip, several thick oxide transistors are used. For a better distinction of transistors used in the following schematics, the symbols can be seen in figure 3.1 and 3.2. The typical threshold voltage of a NMOS thick oxide transistor is  $\approx 0.65V$ . The comple-

Figure 3.1: Symbol of thick oxide NMOS transistor (left) and PMOS transistor (right)

mentary PMOS transistor has a slightly higher threshold voltage of  $\approx -0.70V$ . The gate length of N/PMOS transistors is limited to a minimum of 1µm.

Thin gate oxide transistors are also called "low voltage" transistors and are used in analog and digital designs. The oxide withstands a permanent stress level of 1.5V. The typical threshold

Figure 3.2: Symbol of thin oxide NMOS and PMOS transistor

voltage for a NMOS or PMOS thin oxide transistor is  $\approx \pm 0.4V$ . Minimum gate length is 120nm. Because of the drastically improved performance of thin oxide transistors compared to thick oxide ones, each application of a high-Vth transistor is carefully considered during the design phase of the project. Naturally, these transistors are inserted only when absolutely necessary.

## 3.3 Passive components

Integrated passive components like resistors and capacitors change their values according to the applied voltage, silicon temperature and process parameter variations [Bak07].

### Capacitors

Because of the second poly gate (the floating gate) in the EEPROM process technology, linear poly to poly capacitors are available. Their capacitance is independent of the applied voltage on either of the two poly plates. The area capacitance with  $\approx 2fF/\mu m^2$  is clearly smaller than a thin oxide transistor capacitance but it withstands up to 15V constant voltage stress. Therefore, it can also be used as resonance capacitor at the coil input pads. The parasitic capacitor from the lower poly plate down to the lossy substrate is  $\approx 8\%$  of the nominal poly to poly capacitance. Especially in RF applications these parasitic losses may increase the equivalent serial resistance of the chip which will finally result in a reduced power performance in the UHF frequency band [BVR<sup>+</sup>09], [KF03]. A MIM capacitor with a much lower parasitic capacitors without special isolation are feasible but as there are no dedicated Infineon simulation models available for them, they are not used in the following designs.

#### Resistors

To minimize the resistor area, the analog design has been carried out with only a small number of poly resistors. Wherever possible, resistors have been replaced in the CTS design by transistors. A specific sheet resistance of  $\approx 300\Omega/square$  and a voltage independent resistor value are the crucial factors for using a poly resistor. Temperature dependency can be compensated when n-poly and p-poly resistors are combined in the right ratio together to one resistor with temperature stable resistor value.

3 Infineon Si process information

## **4 Power Generation Units**

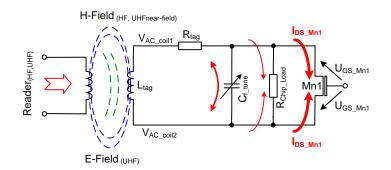

Coupling between reader and transponder relies on magnetic field (inductive coupling), electric field (capacitive coupling) or radiation field (electromagnetic coupling) [Pur08]. Inductive and capacitive coupling are usually near-field powering methods with an operation distance which is proportional to the reader antenna size. At UHF frequencies, the far-field coupling is applicable and is a guarantor for a big operating distance over several meters.

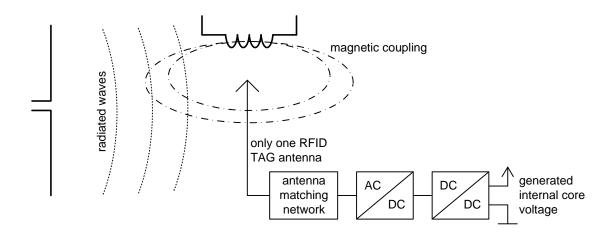

## 4.1 Passive RFID power generation

Any RFID ISM band reader generates a magnetic or electric field into the near-field region and radiates an electromagnetic wave into the far field. The CTS transponder power generation unit receives and converts the incoming power into a stable internal DC power supply. In figure 4.1, only one antenna is gathering energy form the field and transfers the power to the attached rectifier. New CTS design concepts for the AC/DC and DC/DC converter are necessary to fulfill the selective circumstances of each frequency band. These concepts are described in the following. The most crucial characteristic of the CTS AC/DC converter is its high efficiency in each of the

Figure 4.1: Power generation modules - An architectural overview

two frequency bands. The diction "highly efficient" comprises the following key aspects:

- best chip impedance to antenna impedance matching in the HF and especially in the UHF band

- · the right voltage potential at the antenna-chip interface

#### 4 Power Generation Units

- high rectifier and DC/DC converter efficiency

- · damping of internal chip noise to avoid wrong backscatter information to the reader

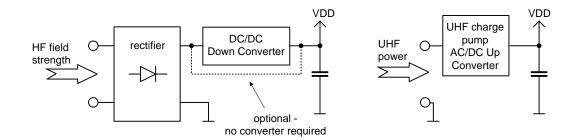

In the HF near-field operation, the amplitude of the rectifier rises to 4Vpeak already at a weak field strength. The low drop rectifier generates an output voltage of about 3.6V, which is much too high to be used as internal power supply voltage. For a voltage level reduction the first DC/DC converter is necessary. In the far-field, the voltage at the rectifier input rises more slowly compared to HF. To get a stable internal power supply voltage, an up-converter has to be used. This is the second DC/DC converter.

The contactless power and data performance, silicon chip area and the developed chip technology complexity have to be competitive with typical HF/UHF band products, which are already established in the market. For example, no on-chip energy reservoir capacitor for energy harvesting is allowed to increase the UHF operating range. A drawback of these cost-saving measures, however, is the reduced chip sensitivity in the UHF mode.

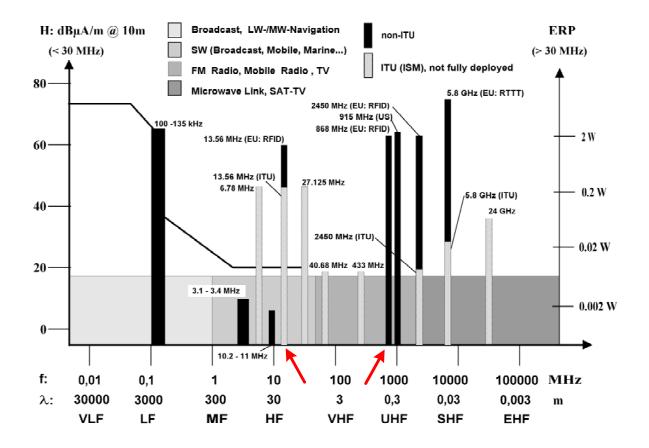

## 4.2 Available power in different RFID frequency bands

Power levels at the corresponding ISM frequency bands are shown in figure 4.2. Reasons to choose and to invest into the right frequency band are:

- · local RF regulations and limitations in each country

- already used reader infrastructure

- · necessary operation distance of the transponder

- maximum data rate

- transponder costs

The intent of the CTS power generation unit is to be able to handle every applied RFID frequency form the LF band up to the 2.45GHz UHF band. The power generation unit also has to handle the wide dynamic range of incoming power levels delivered to the rectifier. Frequency selection with the help of a tunable on-chip matching circuit is not supported. This kind of matching would increase the chip area significantly and would reduce the quality factor Q of the transponder circuit especially at lower frequencies. Impedance matching is performed by special measures in the antenna design an not by the chip input structure.

To get a cost competitive transponder for transport and identification, the CTS chip - antenna prototype supports the EPCglobal HF and UHF standard. The power generation design concept would be able to handle also the LF and 2.45GHz ISM band, but for proper operation first, an additional capacitance and second, a more powerful transistor for the rectifier would be necessary. Some key parameters will help to specify and describe the CTS power unit.

- Rectifier frequency range = 100kHz ... 2.45GHz

- V<sub>coil max HF</sub> = 5V<sub>peak</sub>

Figure 4.2: RFID frequencies and corresponding maximum power levels [Fin06]

- Vantenna min UHF = 0.8Vpeak

- Power path efficiency HF > 80%

- Power path efficiency UHF > 15%

- I<sub>load</sub> at VDD = 10μA ... 20μA

- · some Si technology restrictions

#### Frequency range

125kHz or 134kHz carrier frequencies are applied to the rectifier when the LF (low frequency) band is chosen. Energy could be derived by use of this CTS rectifier and communication done via the HF demodulator and load modulator. In this mode, additional internal energy reservoir capacitors and external resonance capacitors are necessary. From the digital point of view the CTS chip has to support the typical LF coding like ISO11785 or ISO14223. From the application point of view, the analog and digital area overhead for a LF band system cannot be supported. A reliable reduced operation distance is already given in the HF band. During the feasibility study the CTS team decided to optimize the chip architecture for the HF and UHF frequency band. In the upper UHF band, close to the MWF (micro wave frequency) band, the popular 2.45GHz band is approved for RFID but it is used rarely for passive RFID applications. The biggest benefit

#### 4 Power Generation Units

of using this band is the smaller antenna size compared to a 900MHz antenna. The maximum operation distance is reduced to about 1m, which is much less than in the UHF band. Moreover, for this MWF frequency band, we did not see the determined advantage of being implemented in the CTS chip.

#### Antenna voltage limits

An antenna voltage dynamic range from 0.8V up to 5V peak is necessary to be compliant to corresponding HF and UHF regulations and performance requirements. This high carrier peak voltage of 5V at the coil is necessary, because HF load modulation requires a certain voltage peak potential dynamic of about  $3V_{peak}$  [ISO08] [ISO06] during the switching. The peak voltage value during the load modulation phase is limited to about 500mV or even close to zero when an on-chip PLL is used. To fulfill the ISO sideband requirements, the peak voltage in the normal phase (during non-modulation phase) has to be above  $4V_{peak}$  or when the inverse load modulation concept is used, the peak voltage during the load modulation has to reach the aspired  $4V_{peak}$ . [Kla09] [Ber03].

The lower voltage limit of  $0.8V_{peak}$  in the UHF band is not a number which is defined in the EPC specification; it is simply a CTS rectifier performance limitation. The lower the antenna voltage can be without losing rectifier or charge pump efficiency, the better the maximal operation distance of the tag will finally be. By use of Schottky diodes instead of thick oxide MOS transistors the level of 0.8V could be reduced even to  $V_{AC\_coil1/2} = 0.5V_{peak}$  and the efficiency would increase up to 35% [KF03].

#### Power path efficiency

During the design phase the digital current consumption was not exactly known. An overall load current bandwidth from  $5\mu$ A up to  $15\mu$ A for the digital modules was estimated. The rectifier has to deliver this current in all frequency bands with an arguable power efficiency of 80% in HF operation and 15% in the UHF band.

#### **Technology restrictions**

In the coarse CTS power path specification, the last item regards the Infineon technology limitation. Schottky diodes are powerful in every sense and perfect for RF charge pumps: are characterized by a small forward voltage and an exponential U/I sensitivity. So far they have been used in all commercial high performance UHF RFID front ends. The diode area with the corresponding junction capacitance is small compared to MOS transistors.

In a modern CMOS process, thin oxide MOS transistors have a threshold voltage  $V_{th}$  of about 400mV. Even special zero threshold transistors with a high leakage current will never reach the performance of Schottky diodes. To handle the voltage range at the antenna to chip interface, special high voltage devices with increased oxide thickness are used in the analog front end. This type of transistor is characterized by a threshold voltage of about 600mV. The minimum channel length is increased from 120nm to 1 $\mu$ m and the drain/source p/n diffusion areas are significantly increased compared to thin oxide transistors.

## 4.3 Balanced and unbalanced rectifier structures

In RF systems we have to distinguish between balanced (symmetrical) and unbalanced (asymmetrical or single ended) systems. For permanent operation or for system tests, balanced or unbalanced RFID antennas are connected to balanced or unbalanced RFID chip frontends. When these two systems are linked together, special measures are necessary. The same problem will occur when unbalanced measurement equipment is connected to balanced chip interfaces. In

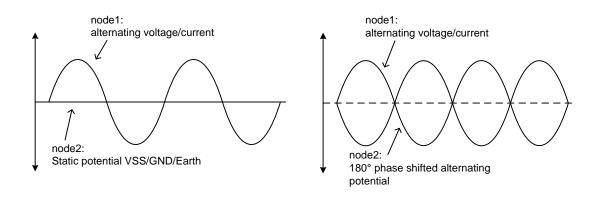

Figure 4.3: Is there an unbalanced signal applied, we only have one "hot" node - in balanced configuration two

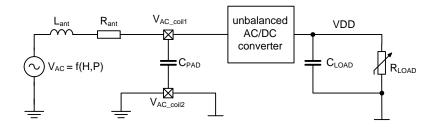

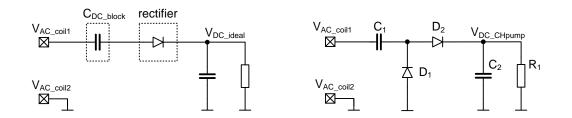

figure 4.3, the balanced and unbalanced types of control signals are shown. In the contactless air interface, a sinusoidal waveform is delivered in all frequency bands from the reader antenna in the form of an electromagnetic field. Half- and full-wave rectifiers in combination with a storage capacitor are the common architecture to convert sinusoidal input voltages into a DC output potential. Typically, the full-wave concept is more efficient, because the negative half-wave is mirrored to a positive half-wave and the corresponding charge frequency is doubled. This full-wave performance advantage is clearly valid at low frequencies like 13.56Mhz and at moderate or high current consumption of the chip when several mA are consumed by the internal load. At frequencies located in the UHF band and at low or moderate current consumption, integrated AC - coupling capacitors can be used as level shifter which allow a DC level shift and an increased rectifier efficiency. Figure 4.4 shows the antenna to chip interface of an unbalanced AC/DC con-

Figure 4.4: A typical UHF RFID antenna - chip interface

verter. Typically UHF RFID products especially use this approach for 2 or 3 stage charge pumps

[See05] [SHCW06] [KF03] and [GBC<sup>+</sup>04]. In the unbalanced AC/DC converter, DC-blocking capacitors in front of the rectifier shift the sinusoidal voltage to an individually higher potential. The corresponding peak-to-peak voltage at the passive capacitor plate is about 10% or even 20% lower than the peak-to-peak voltage at the active antenna plate which is directley connected to the transponder antenna.

One advantage of an unbalanced input stage is the connection of one antenna branch to the internal chip VSS via one pad. From the chip's perspective, the VSS pad will notice no dynamic voltage oscillation and all parasitic capacitive or parasitic inductive influences can be neglected at this node. This parasitic simplification is a very big benefit for the floorplan and layout of unbalanced chips. The distance between the RF and VSS pad can be increased on the chip as far as necessary. A minimum antenna-pad distance for proper backend assembly is necessary and usually is longer than  $500\mu m$ . A limited number of 100 squares are necessary to transport the big alternating current during HF high-field strength operation (electromigration) and to get a high Q-factor in weak field-strength conditions (low resistive input structure). UHF rectifier and charge pumps are typically concentrated very closely around the RF pad to achieve best performance. The VSS pad is connected well to the local chip substrate. A balanced input structure is

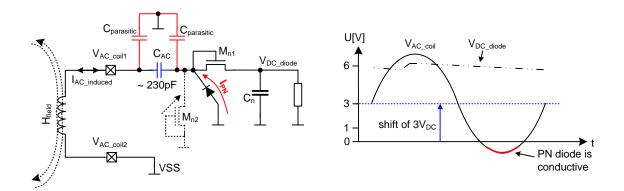

Figure 4.5: A typical HF RFID antenna - chip interface which is also used for the CTS chip

shown in figure 4.5. Two cross-coupled switches (see figure 4.11) define the chip VSS potential and, therefore, also the two coil potentials  $V_{AC\_coil1/2}$ . Because of these switches, the potential at  $V_{AC\_coil1/2}$  is always above -200mV compared to the internal power supply potential VSS. Thus, coupling capacitors are not necessary any more to avoid negative voltages and triggered PN junctions. This architecture is perfect for LF and HF bands, but it has some drawbacks for higher frequencies. With some innovations, this concept of a balanced input structure will be used in the CTS project.

Another balanced rectifier structure is the so-called Greinacher cell, which delivers a positive and a negative power supply potential. An isolated silicon process (e.g. SOI) is necessary to benefit from such an input structure [ASI09] and [CDDJ07].

# 4.4 Proposed CTS power architecture

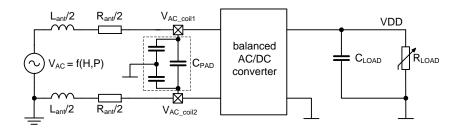

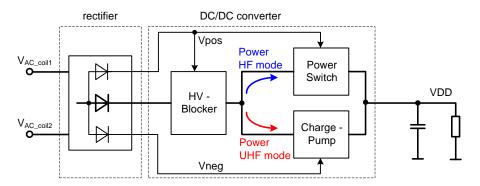

Before starting with the detailed rectifier implementation on transistor level, the architecture of the CTS power supply unit will be presented and compared with typical passive RFID implementations. Generating a local IC power supply is the target of the CTS power architecture. This defines a local VSS and a positive voltage potential big enough to operate the on-chip digital state machine reliable. On the left of figure 4.6, a HF rectifier with an attached DC/DC converter

Figure 4.6: Typical power generation in the HF and UHF frequency bands

is shown. The detailed schematic implementation of the rectifier is presented in the next sections. As already mentioned, HF load modulation sideband requirements result in an increased coil voltage, which simply is too big for a rectification without DC/DC down converter when a sub quarter-micron gate oxide transistor technology is used. In this case, the DC/DC down converter implemented as linear serial regulator is necessary for a stable and reliable VDD potential of about 1.4V.

Commercial UHF frequency band products are done with an unbalanced input structure. This charge pump operates with 868MHz or 915MHz and tries to increase the small antenna voltage at weak incoming power conditions to reach a usual core VDD power supply potential. This charge pump also takes over the rectification of the incoming RF amplitude. A big antenna voltage of several volt is not necessary for UHF. The HF step down converter, therefore, is not necessary either. One reason for the relaxed dynamic is the increased backscatter sensitivity of a UHF reader [NR06a]. Is the voltage amplitude bigger than specified in the previous table, the excessive power will be converted into temperature by a local shunt which is located parallel to the antenna.

A combination of HF and UHF power architecture is the basis of the CTS concept in figure 4.7. A special low-drop voltage rectifier which can work down to a coil peak voltage of 0.7V is the common interface for both frequency bands. The simple voltage rectifier with a dynamic peak

Figure 4.7: Proposed CTS architecture to handle HF and UHF bands

voltage range from 4.5V down to 0.55V would vary too much to be used as a core power supply voltage. The afterwards attached DC/DC up/down converter will do the task of "regulating" VDD to the right voltage value. Down-conversion is done with a linear voltage regulator which is characterized by a good PSRR. For up-conversion, the local oscillator delivers a low-frequency

clock of about 2MHz to a highly efficient one stage charge pump. With the help of these two core modules, a stable local VDD power supply voltage value of 1.5V is guaranteed in all frequency bands.

## 4.4.1 HF rectifier

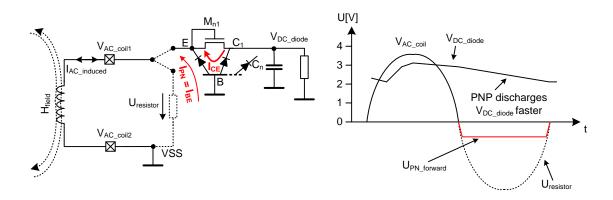

Why not integrate an unbalanced HF rectifier? High coil voltages at the chip interface are necessary to power the IC and to fulfill requirements which are defined in the ISO15693 or ISO14443. An alternating voltage oscillating symmetrically around VSS is chosen as the input voltage. Because of a constant impedance represented by a resistor, the coil voltage U<sub>resistor</sub> in figure 4.8 is proportional to the magnetic field strength. In a self-isolation CMOS process without triple well

Figure 4.8: First, a resistor only and then, additionally a rectifier is connected to an inductance

option, a more negative voltage than -600mV triggers a PN-diode in forward operating mode. A junction diode from substrate to this node operates in forward direction and a big current clamps the voltage accurate defined around -0.7V versus VSS. Not only the clamping of the voltage is the problem here; the parasitic bipolar transistor in figure 4.8 is also triggered by this conductive PN-diode. It represents the base-emitter diode of a bipolar transistor. If this diode conducts, the collector node can be any PN diode which operates in backward direction and the current is limited only by the substrate resistance and special technology measures. If a sensitive node is affected by this NPN transistor, malfunction of a module in the analog front end at high-field strength can be the consequence.

An AC-coupling capacitor in front of each PN diode provides a DC voltage shift at node  $V_{AC\_coil1}$ , but the additional parasitics rapidly increase the overall input capacitance between the two antenna nodes. If a poly-poly capacitor is chosen, an additional capacitance to substrate of 10% of the nominal value is the consequence and pushes the resonance capacitance value at the rectifier input far above the typical value of 15pF. Additional capacitance results from metal wiring capacitances to connect the big AC-coupling capacitor area.

Especially in the UHF frequency band, a bigger input capacitance causes a linear reduction of the rectifier input voltage. The antenna voltage generated by the incoming electromagnetic wave is amplified by a smaller voltage multiplication factor [Dob07]. Typical values for UHF only TAG input capacitance are 0.2pF - 0.5pF. The input resonance capacitance of the CTS chip is about

#### 4.4 Proposed CTS power architecture

Figure 4.9: Simple rectifier with additional big AC-coupling capacitor

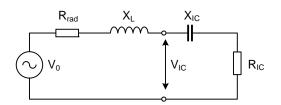

600fF. Figure 4.10 and equation 4.1 show the influence of the chip capacitors on the input voltage

Figure 4.10: Simplified antenna to chip interface

$V_{IC}$ . Precondition of the equation is a perfect power matching and a significantly smaller serial resistor  $R_{IC}$  compared to  $X_{IC}$  and  $X_L$ .

$$\frac{V_{IC}}{V_0} = \frac{R_{IC} + X_{IC}}{2 \cdot R_{IC}} \approx \frac{X_{IC}}{2 \cdot R_{IC}}$$

(4.1)

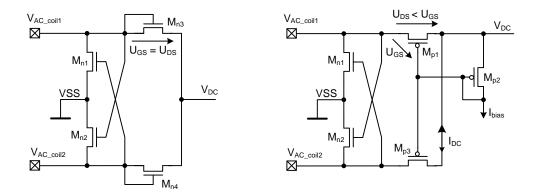

To avoid negative voltages at the input of the IC, figure 4.11 shows two cross-coupled NMOS transistors defining the VSS potential in both designs. On the left side of figure 4.11, a standard HF rectifier is shown with two diodes to power the resistive load and to supply an energy reservoir capacitor. Both are attached to a single node  $V_{DC}$ . A voltage requirement of about 5V<sub>peak</sub> at the coil requires NMOS diodes with an increased voltage robustness which typically results in an increased threshold voltage. Additionally, the bulk of each transistor has to be connected to VSS to prevent backward current from the internal voltage reservoir back to the coil. This bulk connection causes an increased threshold voltage V<sub>th</sub> of transistor  $M_{n3}$  and  $M_{n4}$  because of back-gate modulation [AH02].

$$i_{DS} = \frac{\mu_0 C_{OX} W}{L} \left[ (v_{GS} - V_{th}) - \frac{v_{DS}}{2} \right] v_{DS} (1 + \lambda \cdot v_{DS})$$

(4.2)

$\lambda$  is the channel length modulation parameter  $[volt^{-1}]$  $\mu_0$  is the surface mobility of the channel of a MOS transistor  $C_{OX}$  the capacitance per unit area

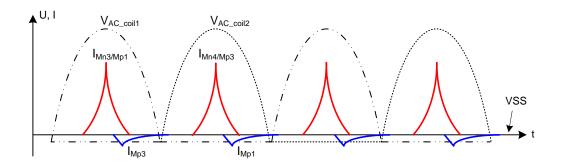

Figure 4.11: HF rectifier structures with two NMOS diodes and PMOS mirror transistors

#### W/L are the transistor dimensions

In a modern process it can be assumed that  $\lambda \approx 0.12$ . This is valid for thin oxide transistors with a transistor length which is 5 times bigger than the minimum transistor length.

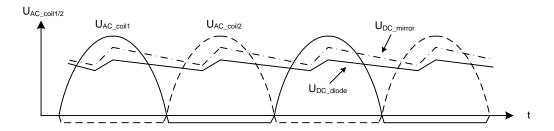

Figure 4.12 shows the impact of two cross-coupled NMOS transistors on the coil voltage. At the

Figure 4.12: Coil voltage of both HF rectifier versions