# A Bulk Acoustic Wave based Ultra Low-Power Transmitter

Dipl.-Ing. Martin Flatscher

Graz, May 2011

### EIDESSTATTLICHE ERKLÄRUNG

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe.

### STATUTORY DECLARATION

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

May 10<sup>th</sup>, 2011

.....

### Kurzfassung

Platziert man das Sensormodul eines Reifendruckmesssystems (Tire Pressure Monitoring System - TPMS) auf der Innenseite der Lauffläche des Reifens, lassen sich zusätzliche wichtige technische Parameter messen. In dieser Arbeit wird ein neuartiger Sender für ein solches System vorgestellt. Die Herausforderungen sind groß: Das maximale Gewicht und Volumen des Sensors sind begrenzt, eine lange Lebensdauer der Stromversorgung muss erreicht werden und hohe Robustheit ist erforderlich um extremen Beschleunigungen standzuhalten. Durch die Verwendung eines Bulk Acoustic Wave (BAW) Resonators entfällt die Notwendigkeit eines großen stoßempfindlichen Quarzes und eines Phasenregelkreises (Phase Locked Loop -PLL). Dies macht das System robuster, reduziert die Anlaufzeit und verringert die Leistungsaufnahme. Der entwickelte Sender ist Teil eines 3D Chip-Stapels und daher wurden Problemstellungen durch die Verwendung von 3D-Integrationstechnik berücksichtigt. Neue analoge Schaltungen für die wichtigsten Schaltungsblöcke wurden entwickelt: ein BAW-Oszillator, asynchrone Teiler und ein Leistungsverstärker (Power Amplifier - PA) mit Anpassnetzwerk. Diese Schaltungen können in praktischen Implementierungen von Sendern verwendet werden und können helfen, die Performance zu verbessern und die Stromaufnahme zu verringern.

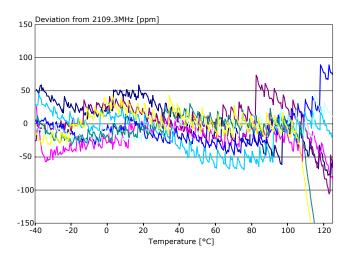

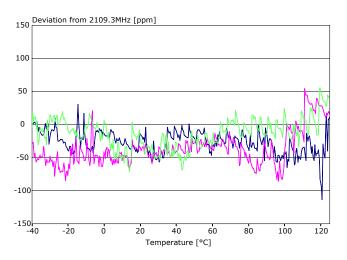

Ein zweistufiger BAW Oszillator, der sich die Parallelresonanzfrequenz zu Nutze macht, wird als Frequenzreferenz verwendet. Der vorgestellte Oszillator kann mit Hilfe von digital zuschaltbaren Kondensatoren verstimmt werden, um eine Temperaturund Prozesskompensierung durchführen zu können. Die verbleibende Frequenzabweichung nach Ausführen des Kompensierungsalgorithmuses ist kleiner als ±150ppm. Der BAW kann auch mit einer variablen Gleichspannung, die für eine Modulation benutzt wird, verstimmt werden.

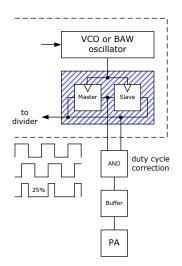

Neue Arten von asynchronen Teilern werden vorgestellt. Zum Beispiel ein asynchroner Frequenzteiler mit einem Teilerfaktor von 1,5, der für die Isolierung von BAW Oszillator und Leistungsverstärker (PA) verwendet werden kann. Durch die Teilung des Referenzsignals durch 1,5 treten Oberwellen des Ausgangssignals und die des Referenzsignals nicht bei der gleichen Frequenz auf.

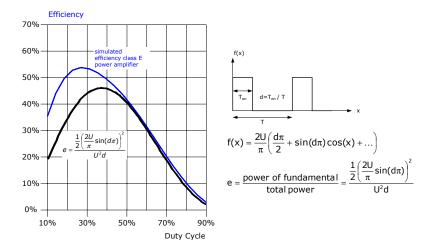

Weiters wird ein neues integriertes Anpassnetzwerk vorgestellt. Die fast rein reaktive Eingangsimpedanz des rauscharmen Verstärkers (low noise amplifier - LNA) ist Teil eines Schwingkreises, der an die Antenne angepasst wird um die maximale Amplitude der Schwingung zu erhalten. Die höchste Spannungsverstärkung erhält man durch Anpassung der Antenne an die Verluste des Anpassnetzwerkes. Der Vorteil dieses Ansatzes liegt darin, dass dieser Schwingkreis im Sendebetrieb leicht an den Leistungsverstärker (PA) angeschlossen werden kann. Eine neuartige Schaltung zur Steuerung eines Klasse E Leistungsverstärkers (PA) wird vorgestellt. Das Tastverhältnis des Eingangsignals eines Klasse E Leistungsverstäkers (PA) hat einen starken Einfluss auf die Effizienz. Die vorgestellte Schaltung kann beliebige Tastverhältnisse erzeugen und verringert dadurch den Stromverbrauch.

### Abstract

Attaching the sensor node of a Tire Pressure Monitoring System (TPMS) on the inner liner of a tire allows the sensing of important additional technical parameters. In this work, a novel transmitter for such a system is presented. The challenges are high: The maximum weight and volume of the sensor are limited, a long power supply lifetime must be achieved, and high robustness against extreme levels of acceleration is required. By exploiting a Bulk Acoustic Wave (BAW) resonator, the use of a bulky and shock-sensitive crystal and a Phase Locked Loop (PLL) can be avoided. This makes the system more robust, radically reduces the start-up time, and decreases power consumption. The proposed transmitter is part of a 3D chip stack and hence design issues when using 3D integration techniques were considered. New analog circuitry for the main building blocks was developed: a BAW oscillator, asynchronous dividers, and a Power Amplifier (PA) with a matching network. These circuits can be applied in practical implementations of transmitters and can help to improve performance and to decrease the current consumption.

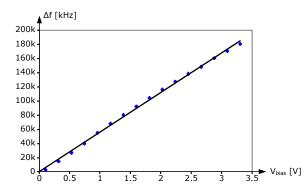

A two-stage BAW oscillator which makes use of the parallel resonance frequency is used as frequency reference. The proposed oscillator is tunable to enable temperature and process compensation by means of digitally controlled capacitors parallel to the BAW resonator. The remaining frequency deviation after applying the compensation algorithm is lower than  $\pm 150$  ppm. The BAW can also be tuned with variable DC biasing, which is used for modulation.

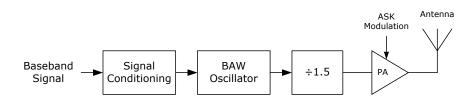

New types of asynchronous dividers are presented. For example, an asynchronous frequency divider with a division ratio of 1.5 can be used to achieve isolation between the BAW oscillator and the PA. By dividing the reference signal by a factor of 1.5, the harmonics of the output signal and the harmonics of the oscillation signal do not occur at the same frequency.

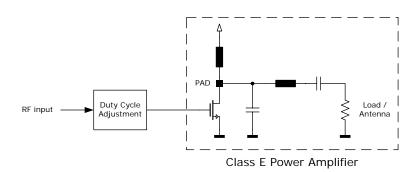

Further, a new on-chip matching network is proposed. The almost purely reactive input impedance of the low noise amplifier (LNA) is part of a resonance circuit, which is matched to the antenna to obtain maximum amplitude of oscillation. The highest voltage amplification is obtained by matching the antenna to the losses of this network. The advantage of this approach is that this resonance circuit can easily be connected to the PA in the case of transmit mode. A novel circuit for the control of a class E PA is shown too. The duty cycle of a class E PA input signal has a large impact on efficiency. The proposed circuitry can provide arbitrary duty cycles and this reduces power consumption.

## Acknowledgements

This Doctoral Thesis was written at the Institute of Electronics at the Graz University of Technology in cooperation with the Sense & Control group at Infineon Technologies Austria AG, Development Center Graz.

I would like to thank Univ.-Prof. DI Dr. Wolfgang Pribyl and Prof. Dr. ir. Willy M.C. Sansen for supervising my thesis.

I would also like to thank the whole team of the Sense & Control department for their excellent support, especially DI Thomas Lentsch, DI Thomas Herndl, and DI Dr. Werner Weber. Thank you very much Markus, Hartwig, Helmut, Rainer, Thomas, and Seppi for your great help and for your friendship.

Last but not least I would like to thank my parents Margit and Thomas Flatscher for supporting me throughout my life.

Martin Flatscher Graz, April 2011

The presented work was part of the e-Cubes project, which was partly funded by the European Commission (EC) sixth framework program (proposal number IST-026461).

# Contents

| 1 | Introduction and Background1.1 The e-Cubes Project1.2 The 3D Integrated Sensor Node1.3 The BAW-based Transceiver1.4 Design Issues when using 3D Integration Techniques1.5 Conclusion                                                                                                                                                                                                | <b>17</b><br>20<br>27<br>29<br>32                               |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 2 | Transmitter Concept2.1 The Power-Bandwidth Trade-Off2.2 Transmitter Architectures2.3 The BAW Oscillator in Receive Mode2.4 Figure-of-Merit (FoM) and Comparison with State-of-the-Art2.5 Conclusion                                                                                                                                                                                 | <b>35</b><br>35<br>42<br>48<br>48<br>51                         |

| 3 | The BAW Device                                                                                                                                                                                                                                                                                                                                                                      | 53                                                              |

| 4 | The BAW Oscillator4.1 Oscillation Theory4.2 One-Transistor Oscillators4.3 Two-Stage Oscillators4.4 BAW Oscillator Implementation4.5 BAW Tuning (Temperature Compensation and Modulation)4.5.1 Capacitive Tuning4.5.2 DC Biasing Tuning4.5.3 Operation under Temperature Variations4.6 Figure-of-Merit (FoM) and Comparison with State-of-the-Art4.7 Conclusion                      | <b>59</b><br>63<br>71<br>77<br>81<br>82<br>91<br>92<br>93<br>95 |

| 5 | Asynchronous Dividers5.1Introduction into the Timing Problem of Dual Modulus Dividers5.2Basic Principle of the Asynchronous Counter5.3An Asynchronous 2/3 Divider5.4Timing Problem with the proposed 2/3 Divider5.5An Asynchronous 1/2/3 Divider5.6Typical Application of a 1/2/3 Divider5.7A 1.5 Divider5.8Figure-of-Merit (FoM) and Comparison with State-of-the-Art5.9Conclusion | 112                                                             |

| 6 | Matching Network and Power Amplifier6.1 Matching Network and RX/TX switch6.1.1 Matching Theory                                                                                                                                                                                                                                                                                      |                                                                 |

| 6.1.2 Matching to the Losses of a Resonance Circuit                  | 119 |

|----------------------------------------------------------------------|-----|

| 6.2 Class E RF Power Amplifier with Duty Cycle Adjustment            |     |

| 6.3 Class C RF Power Amplifier with Non-Overlapping Clock Generation |     |

| 6.4 Figure-of-Merit (FoM) and Comparison with State-of-the-Art       | 128 |

| 6.5 Conclusion                                                       | 129 |

| 7 Conclusion and Research Summary                                    | 131 |

| Own Publications                                                     | 135 |

| Bibliography                                                         | 137 |

| List of Figures and Tables                                           | 145 |

## Nomenclature

- μC Microcontroller

- ADC Analog to Digital Converter

- AlN Aluminium-Nitride

- ASIC Application-Specific Integrated Circuit

- ASK Amplitude Shift Keying

- BAW Bulk Acoustic Wave

- BER Bit Error Rate

- BVD Butterworth-Van-Dyke

- BW Bandwidth

- CML Current Mode Logic

- CMOS Complementary Metal Oxide Semiconductor

- CMP Chemical Mechanical Polishing

- CPFSK Continuous Phase Frequency Shift Keying

- CPU Central Processing Unit

- CU Central Unit

- DAC Digital to Analog Converter

- DCO Digitally Controlled Oscillator

- DMD Dual Modulus Divider

- DMP Dual Modulus Prescaler

- DR Data Rate

- E-TSPC Enhanced True Single Phase Clocked

- ESD Electro-Static Discharge

- FBAR Freestanding Film Bulk Acoustic Wave Resonator

- FIFO First In, First Out

- FM Frequency Modulation

- FoM Figure-of-Merit

- FSK Frequency Shift Keying

- FTR Frequency Tuning Range

- GFSK Gaussian Frequency Shift Keying

- GMSK Gaussian Minimum Shift Keying

- HBM Human Body Model

- IC Integrated Circuit

- ISM Industrial, Scientific, and Medical

- LDS Laser Direct Structuring

- LNA Low Noise Amplifier

- LO Local Oscillator

- M-ary FSK Multi-Frequency Shift Keying

- MAC Medium Access Control

- MBVD Modified Butterworth-Van-Dyke

- MEMS Micro Electro-Mechanical System

- MID Molded Interconnect Device

- MMD Multi Modulus Divider

- MMP Multi Modulus Prescaler

- MUX Multiplexer

- NCO Numerically Controlled Oscillator

- NF Noise Figure

- NIC Negative Impedance Converter

- NOB Number of Bits

- PA Power Amplifier

- PCB Printed Circuit Board

- PDE Partial Differential Equation

- PLL Phase Locked Loop

- PPF Polyphase Filter

- PTAT Proportional to the Absolute Temperature

- PVT Process-Voltage-Temperature

- Q Quality Factor

- RAM Random Access Memory

- RF Radio Frequency

- RIE Reactive Ion Etching

- RKE Remote Keyless Entry

- ROM Read Only Memory

- RSSI Received Signal Strength Indicator

- RX Receiver

- SAW Surface Acoustic Wave

- SBB Stud Ball Bumping

- SCL Source-Coupled Logic

- SEM Scanning Electron Microscope

- SFR Special Function Register

- SiP System in Package

- SMR Solidly Mounted Resonator

- SoC System on Chip

- SPI Serial Peripheral Interface

- TDC Time-to-Digital Converter

- TPMS Tire Pressure Monitoring System

- TSPC True Single Phase Clocked

- TSV Through Silicon Via

- TX Transmitter

- UTCS Ultrathin Chip Stacking

- VCO Voltage Controlled Oscillator

# 1 Introduction and Background

#### 1.1 The e-Cubes Project

The following chapter was mainly taken from [1, 2, 8, 14] (own publications). My contribution to this work comprises all building blocks belonging to the transmitter or to the BAW oscillator.

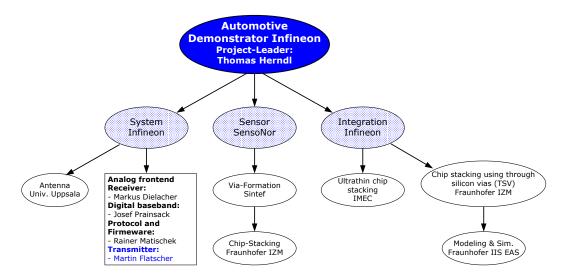

The objectives of the e-Cubes project are to advance micro-system technologies to allow cost-efficient realization of highly miniaturized, truly autonomous systems for ambient intelligence [16]. So the project addresses highly integrated systems, namely so-called independent sensor node applications. Characteristic properties of such nodes are sensor functionality, wireless communication capability (with each other or with a base station), and independence from external power supply. In the project three different applications have been examined: health and fitness, aeronautics and space, and automotive applications. This work is the result of the investigations into the transmitter used in the automotive demonstrator. The project setup of the automotive demonstrator is shown in Figure 1.1.

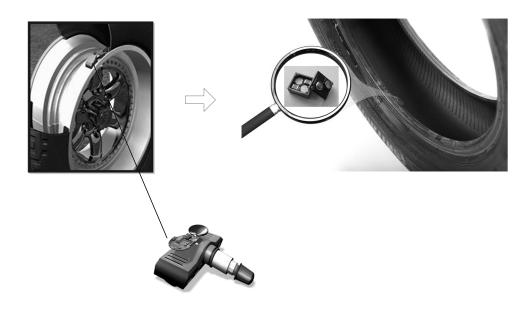

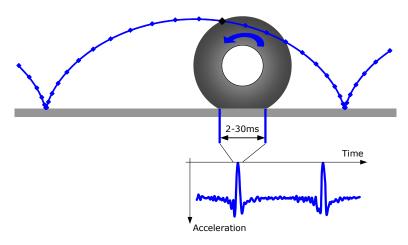

The target application of the automotive demonstrator is a tire pressure monitoring system (TPMS). State-of-the-art TPMS modules are wireless sensor nodes mounted on the rim (see Figure 1.2). Besides a sensor for pressure, the e-Cubes demonstrator also contains sensors for acceleration, temperature, and supply voltage. A typical

Figure 1.1: Project setup of the automotive e-Cubes demonstrator.

Figure 1.2: State-of-the-art tire pressure monitoring system (TPMS) mounted on the rim (left) and future tire mounted TPMS (right).

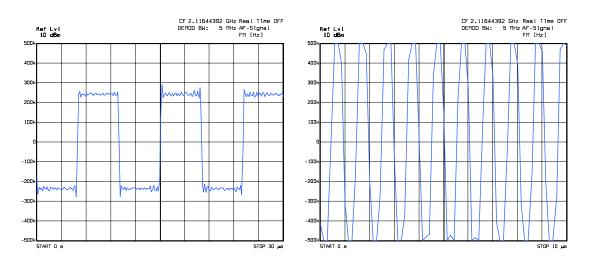

output signal of the acceleration sensor during two rotations of the tire can be found in Figure 1.3. As long as the module is moving around, a more-or-less constant negative acceleration can be measured. When the module enters the region where the tire tread has contact to the road, a spike occurs followed by an increased acceleration signal indicating the standstill of the module. When the module starts moving again, a second spike appears. From this acceleration profile the contact area of the tire can be calculated. Considering the known pressure and temperature of the air in the tire, the contact area can be used to approximate the vehicle load. Attaching the sensor node on the inner liner of a tire allows sensing of further important technical parameters, such as road condition, tire wearout, temperature, tire friction, side slip, and wheel speed. These may be used for improved tracking and engine control, feedback to the power train and car-to-car communication purposes.

Those new features come at a price: the maximum weight of the sensor is limited to 5 grams including package, power supply, and antenna. The node size is limited to about 1 cm<sup>3</sup> to avoid high force-gradients due to device-deformation. Since the battery can only be changed with difficulty, a long power supply lifetime must be achieved. And, finally, robustness is required against extreme levels of acceleration. The static acceleration can be calculated using equation 1.1 [17].  $r_{\rm wheelunit}$  depends on the mounting location. For a tire dimension of 235/45 R17, acceleration reaches 2200g (g = 9.81 m/s<sup>2</sup>) when driving at 300 km/h. In addition, the acceleration coming from the road surface has to be considered.

$$a = r_{\rm wheelunit} \cdot \frac{v^2}{r_{\rm tire}^2} \tag{1.1}$$

Figure 1.3: Acceleration profile of the tire mounted TPMS.

In such applications an individual identifier code and additional data payload are transmitted to a common receiver (RX) in the central unit (CU). Optionally the data transmission is repeated in order to increase the probability that the message is not disturbed by interference or other radio noise. To reduce the power consumption of the entire wireless network, the communication protocols have to be optimized for low-power operation because they have to operate self-sufficiently for several years.

Furthermore the power consumption of the wireless receiver system also needs to be minimized, since the receiver may be active for a long time. Therefore it has to be ensured that the receiver does not drain the battery. An efficient way to reduce the overall power consumption of the wireless communication system without decreasing the reception quality is to use duty cycling of the radio units. The basic principle is similar to the common "Low Power Listening" protocol [60]: The radio reception is activated for a short time followed by a longer period where the radio is in a power down mode and reception is disabled. During the reception period the advanced systems are first listening for a carrier; only in case of a detected signal do they keep listening for a specific header or preamble. The drawback of this duty cycled receiver protocol is that the acyclic transmitting sensor nodes have to send a longer preamble (increased overhead) to bridge the power down time gap of the receiver. Consequently the following trade-off has to be considered: on the one hand the power consumption of the receiver unit is reduced; on the other hand, the longer preamble comes along with increased power consumption for each transmission.

Energy saving by duty cycling with conventional low power radios is rather limited, since they are typically based on quartz crystal oscillators. The main limiting aspect is the start-up time of the crystal oscillator and the PLL which is typically in the range of ms [39, 38]. Using data rates of typical low-power wireless sensor networks (20 - 50 kbit/s [41]) the actual time for carrier sensing (or receiving a short preamble) is about 0.3 - 0.6 ms [41], thus the quartz crystal start-up time can become dominating. More details on duty cycling can be found in [10, 13].

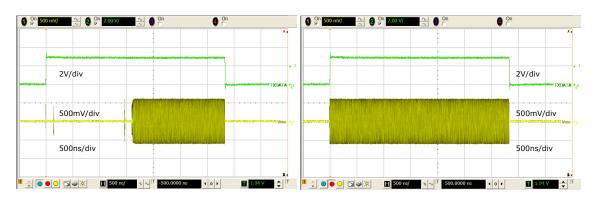

In order to overcome these limitations, the presented sensor node utilizes a MEMS (micro electro-mechanical system) based radio architecture which allows for a significantly faster start-up of the oscillator. The radio uses a bulk acoustic wave (BAW) based oscillator, which achieves a start-up time of about 2 µs. This improves the overall power consumption [69] and is especially beneficial for duty cycled wireless sensor networks applying idle listening: A shorter start-up time can be used for a higher repetition rate with a constant duty cycle at the receiver. In this case a shorter preamble is required, which especially reduces the overhead and power consumption of the transmitting nodes. Another advantage of this configuration will be important for future wireless sensor applications: The shorter start-up time and shorter cycle time of the receiver allows for a significantly decreased message delay independent of the used MAC protocol, so it can be used for more time-critical wireless applications.

#### 1.2 The 3D Integrated Sensor Node

The following chapter was mainly taken from [1, 2, 8, 14] (own publications). My contribution to this work comprises all building blocks belonging to the transmitter or to the BAW oscillator.

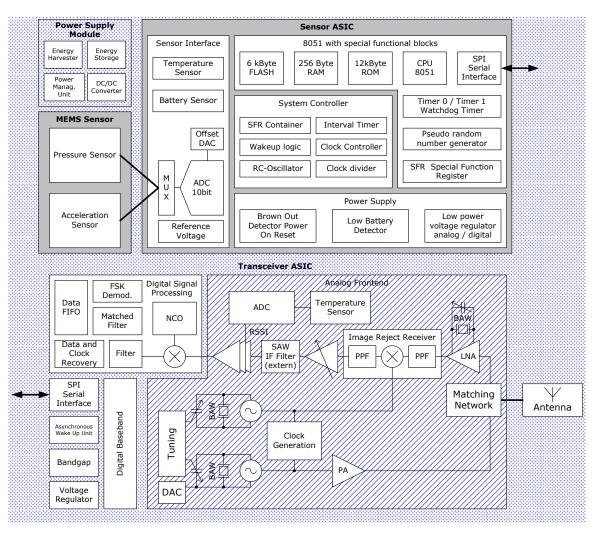

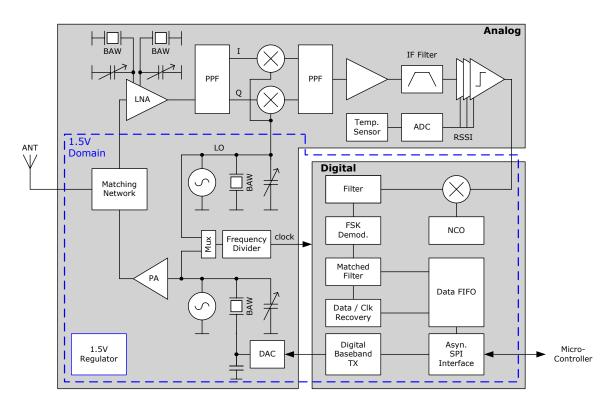

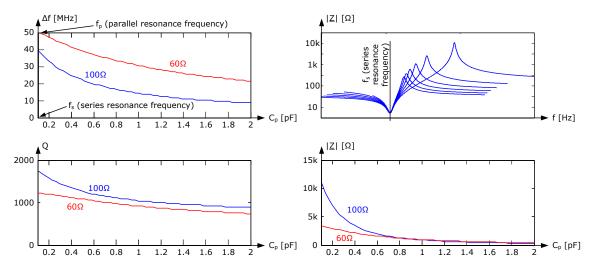

In Figure 1.4 a block diagram of the proposed wireless sensor node is shown, which consists of four different dies: a sensor, a microcontroller, a transceiver, and a BAW die. The sensor die is a bulk micromachined MEMS device containing sensors for pressure and acceleration. The sensor interface together with an ADC for converting the sensor data is integrated on the microcontroller die. Besides that, the microcontroller contains RAM, ROM, and a FLASH memory. It also provides additional sensors for measuring the temperature and the battery voltage. The communication with the transceiver ASIC is established via a serial peripheral interface (SPI). The BAW die includes four separate resonators, two of them are connected to two different oscillators and the other two resonators are used as filters in the receiver.

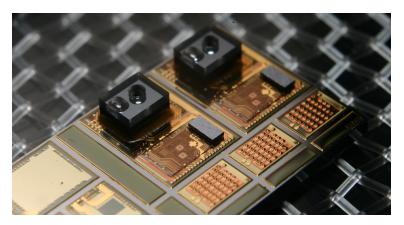

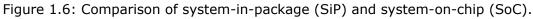

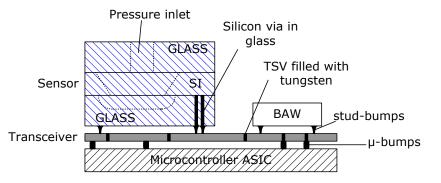

3D integration technologies have become a major topic in the semiconductor assembly industry, which are applied to result in a very compact system-in-package (SiP): The microcontroller, the transceiver, the sensor, and the BAW die are arranged in two different versions of 3D chip stacks using either through silicon vias (TSV) [26, 27, 28, 29, 30] or the ultrathin chip stacking (UTCS) method [31, 32]. The UTCS method has been used for the health demonstrator of the e-Cubes project; for the automotive application it was only a backup solution and was not the focus of the investigations. A picture of the 3D chip stack using UTCS is illustrated in Figure 1.5. This integration reduces the required connections to external components to a minimum and only very few additional wire-bonds are required. As shown in [74] the BAW technology is compatible with a standard integrated circuit (IC) process. Therefore it is possible to integrate BAW resonators above an IC. An example of the integration of BAW filters on top of a receiver front end is given in [73]. But SiP can

Figure 1.4: Block diagram of the sensor node.

Figure 1.5: 3D chip stack using the ultrathin chip stacking (UTCS) method [31, 32].

Figure 1.7: Sketch of the 3D ASIC stack using through silicon vias (TSV).

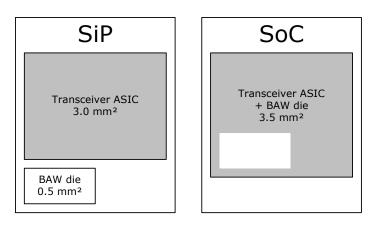

be advantageous in terms of price compared to a system-on-chip (SoC) implementation as shown in the example in Figure 1.6. A transceiver die with a size of 3 mm<sup>2</sup> and a BAW resonator die with a size of 0.5 mm<sup>2</sup> are combined to a SiP (Figure 1.6 left) and to a SoC (Figure 1.6 right). In chapter 4.5 on page 81 it will be shown that the yield of the BAW resonators is limited due to the requirement of a precise frequency. Assuming a yield of 80% and 10 required masks for the BAW resonator die and a yield of 95% and 25 masks for the transceiver ASIC a cost factor can be calculated as follows:

$$\cot factor = \frac{\text{number of masks} \cdot \text{area}}{\text{yield}}$$

$$\cot factor \operatorname{SiP} = \frac{10 \cdot 0.5}{0.8} + \frac{25 \cdot 3}{0.95} = 6 + 79 = 85$$

$$\cot factor \operatorname{SoC} = \frac{35 \cdot 3.5}{0.8 \cdot 0.95} = 161$$

(1.2)

This approximation does not include the packing and bonding process, but shows a significant difference in the die costs of SiP and SoC. Even if the BAW resonator could be integrated on top of the transceiver ASIC, such that the total size would not be increased by the BAW size, a SoC implementation would not be competitive.

Figure 1.8: Photo of the 3D ASIC stack using through silicon vias (TSV) on wafer level (Source: SINTEF, Norway, [23]).

Figure 1.9: Photo of the  $\mu$ -bumps, stud-bumps, and TSVs used as interconnects.

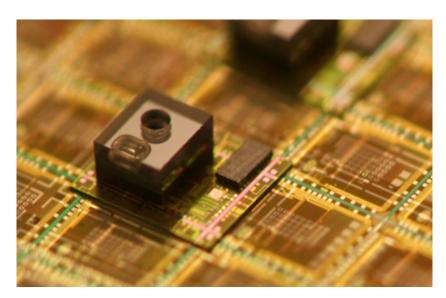

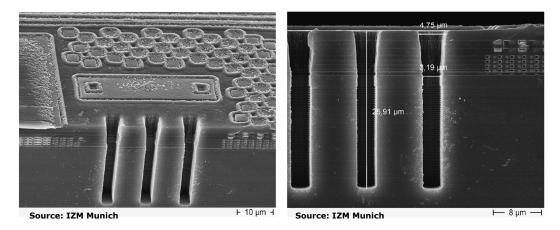

A sketch of the 3D integrated stack with silicon vias in glass in the sensor die and TSVs in the transceiver ASIC is shown in Figure 1.7. The MEMS based sensor and a BAW die, both flip-chipped, are stacked on top of the RF transceiver using gold stud ball bumping (Au SBB) [23, 24, 25]. The transceiver die is thinned to 50  $\mu$ m and is connected to the microcontroller ASIC with a combination of TSVs and  $\mu$ -bumps. A photo of the stack on wafer level, which shows the RF transceiver together with the MEMS sensor and BAW die on top, mounted on the microcontroller, is shown in Figure 1.8. Photos of the  $\mu$ -bumps, stud-bumps, and TSVs are illustrated in Figure 1.9.

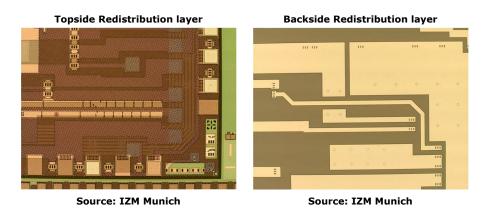

The AlSiCu redistribution layers on the topside and backside of the transceiver die are shown in Figure 1.10. The TSV array structure can be easily recognized next to the original bonding pads of the transceiver, but also within the pad ring at preferred

Figure 1.10: AlSiCu redistribution layer on the topside and on the backside of the transceiver.

locations. The redistribution has been realized in order to connect the TSVs to the original pads of the transceiver and to define new pads for attaching the pressure sensor and BAW devices by means of Au stud-bumps. Additionally a small number of pads for wire bonding have been defined, for instance the RF connection to the antenna.

Subsequently the metalized TSVs have been opened from the backside making use of different wafer-thinning technologies like grinding, spin-etching, chemical mechanical polishing (CMP) and maskless reactive ion etching (RIE). An additional AlSiCu redistribution layer and appropriate ground planes, as shown in Figure 1.10, have been realized on the backside applying a sputtering process. These planes provide shielding between sensitive blocks of the transceiver and the microcontroller ASIC. Additionally the supplies are connected in a star topology, preventing the ground currents from impacting each other. In total three ground planes are implemented, in order to separate analog, digital and RF sections. Furthermore TSV structures can be placed close to sensitive circuits anywhere all over the transceiver, which decreases the impedance to ground, and therefore the impact of noise and ripples caused by neighboring circuits is reduced. More details on miniaturization by means of 3D interconnects can be found in [8].

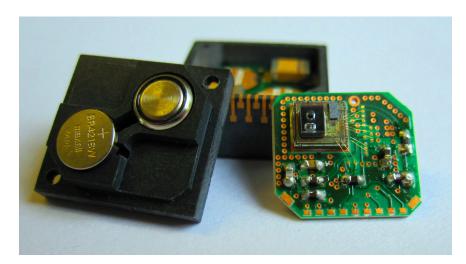

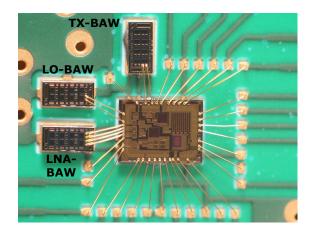

The whole ASIC stack is bonded onto a printed circuit board (PCB - see Figure 1.11) using chip-on-board technologies and standard soldering processes. Beside the ASIC stack, the PCB only contains a few external capacitors for the voltage regulators and some capacitors to bring the loop antenna, which is integrated into the package, to resonance. The values of these capacitors have to be adapted according to the oper-ating frequency of the transceiver, which can be around 2.1 GHz or around 2.45 GHz depending on the assembled BAW devices.

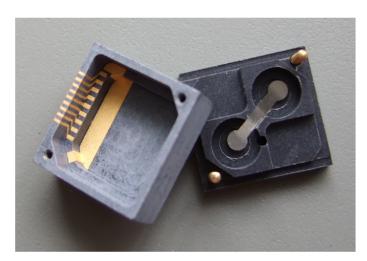

The outer shape of the final demonstrator housing is a 3D substrate in MID (molded interconnect device) technology shown in Figure 1.12. An MID is a 3D plastic part which - after molding or milling - undergoes a selective surface metalization process

Figure 1.11: 3D ASIC stack mounted onto a PCB.

in order to create conductor lines as well as solderable and/or bondable pad surfaces. This is done by taking advantage of the laser direct structuring method (LDS): The surface of the plastic part is selectively activated by a laser beam making it susceptible for subsequent electroless CuNiAu-plating. The conducting line on the bottom of the MID cavity actually serves as loop antenna - one of the great benefits of using MID technology in the current sensor node application (see Figure 1.12). After assembling the PCB, which carries the ASIC stack, the PCB itself is electrically connected to the MID using a conductive adhesive.

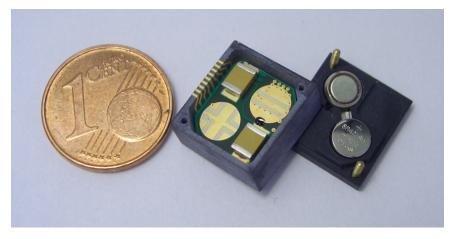

In a first version a power supply module is used, which contains two small coin cells (CR416SW, 8 mAh) together with two capacitors. The capacitors are required because the batteries are not able to provide the required peak current. For this reason the batteries slowly charge the capacitors, which are then capable of delivering the peak current. These two capacitors are mounted onto the other side of the PCB, while the lid holds the two batteries. Connecting the batteries with a stamped metal spring makes up for unavoidable dimensional height tolerances. In addition, the lid does not need to undergo a complicated metalization process but can be manufactured as a simple plastic part. The whole sensor node is shown in Figure 1.13.

In a second version the lid of MID is replaced by an additional PCB carrying another power supply module. This power supply module consists of an energy scavenger, which converts vibrations into electrical energy, and a power management ASIC. Similar to the battery-driven version the energy is stored in large capacitors. The mounting location on the inner liner of the tire is beneficial for the energy scavenger because there is much more vibration energy available in that position than on the rim, where state-of-the-art TPMS are attached. The active microcontroller ASIC, fabricated in a  $0.24 \,\mu$ m CMOS process, consumes less than 3 mA during data conditioning, event triggering, evaluation of the temperature compensation algorithm, and protocol stack handling. Only during measurement of pressure and acceleration can the

Figure 1.12: Molded Interconnect Device (MID) with circuit tracks on the surface.

Figure 1.13: 3D integrated sensor node showing PCB assembled into metalized package and lid containing batteries.

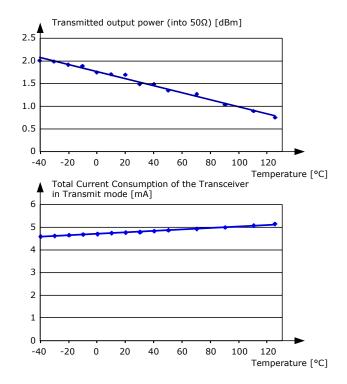

current consumption rise up to 5 mA. Characterization has proven that the microcontroller as well as the transceiver ASIC can be operated in a temperature range from -40°C to 125°C. The transceiver ASIC has been fabricated using a 0.13 µm standard CMOS process. Its current consumption is 6 mA in transmit mode with a transmit output power of 1 dBm and 8 mA in receive mode with a sensitivity of -90 dBm (at a bit error rate of  $10^{-2}$ ) or -88 dBm (at a bit error rate of  $10^{-3}$ ) at a data rate of 50 kbit/s. The start-up time of the transceiver is shorter than 2 µs.

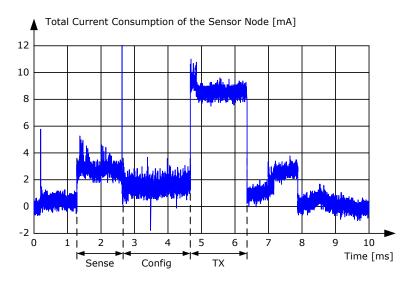

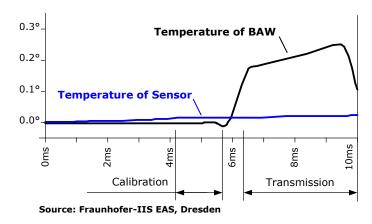

The duration of one complete reporting event is 7 ms, the total required charge is about  $30 \,\mu\text{C}$  (current profile see Figure 1.14). Even when considering the worst case - one reporting event every 10s (only required during alert, when the tire pressure is critical) - this contributes only  $3 \,\mu\text{A}$  to the overall current. This contribution is even lower during normal, non-alerting operation with reporting periods of  $30 \,\text{s}$  to  $2 \,\text{min}$ . To obtain the overall current consumption, the power down current, mainly caused

Figure 1.14: Current profile for one event, measured with a  $10 \Omega$  shunt resistor.

by the RC-oscillator in the system's wake-up unit  $(1 \mu A)$  and leakage of the employed monolithic ceramic buffer capacitor, has to be taken into account. The total current consumption is in the range of what the anticipated very low-weight, vibration-based MEMS scavenging system is able to deliver to attain full self-sufficiency of the wireless TPMS node. The key figures are summarized in Table 1.1.

### 1.3 The BAW-based Transceiver

The following chapter was mainly taken from [1, 2, 8, 14] (own publications). My contribution to this work comprises all building blocks belonging to the transmitter and to the BAW oscillator.

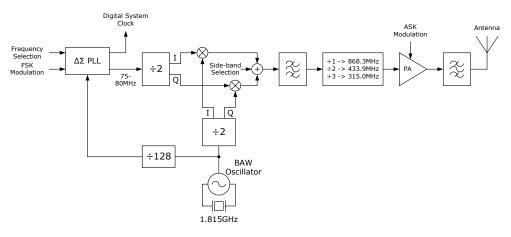

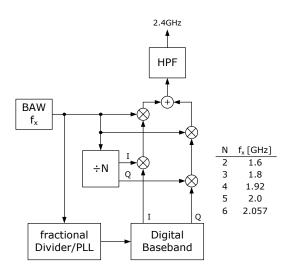

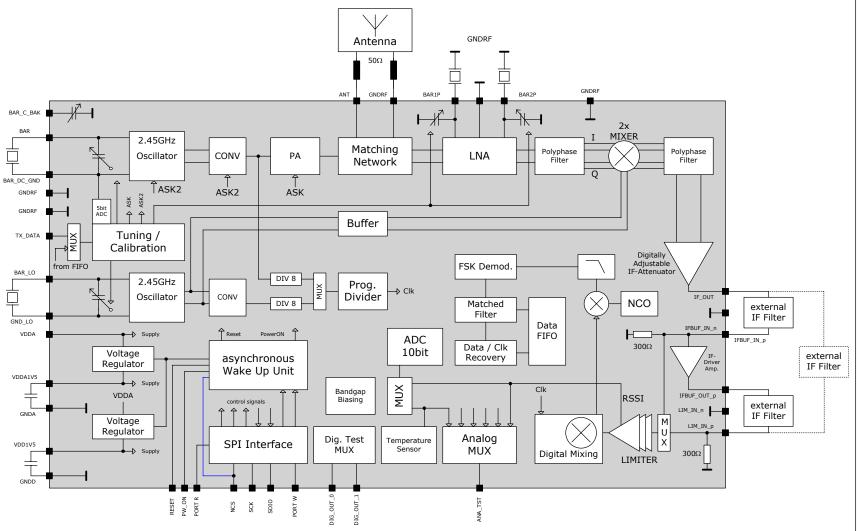

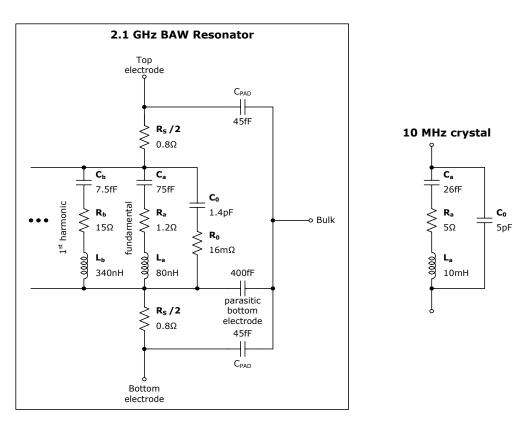

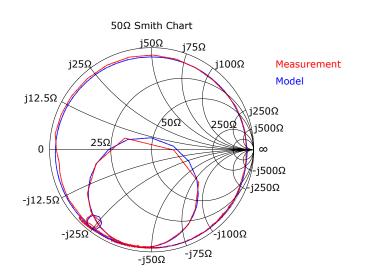

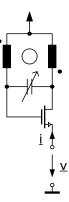

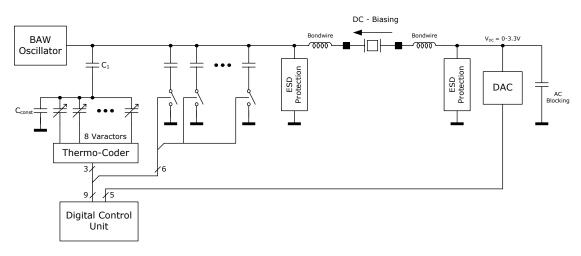

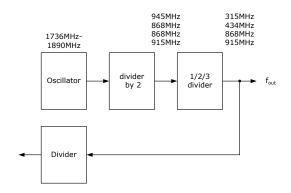

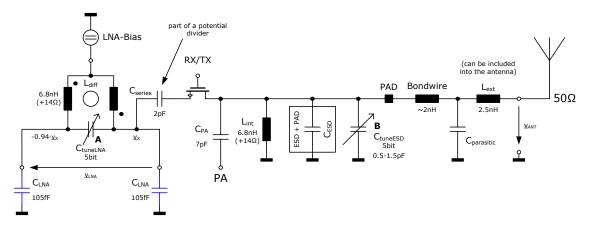

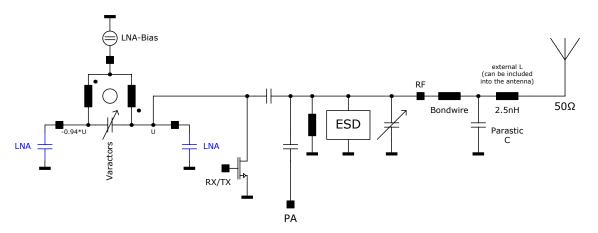

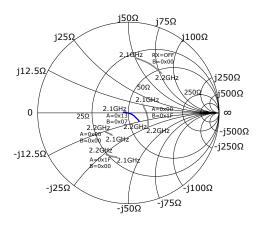

In Figure 1.15 the block diagram of the BAW based transceiver is presented, which uses BAW resonators with a size of only 0.02 mm<sup>2</sup> as frequency reference. By using BAW resonators the employment of a bulky and shock-sensitive quartz crystal and a PLL can be avoided. As already mentioned, this makes the system more robust and radically reduces the start-up time. The operating frequency of the transceiver is about 2.11 GHz or about 2.45 GHz depending on the assembled BAW device.

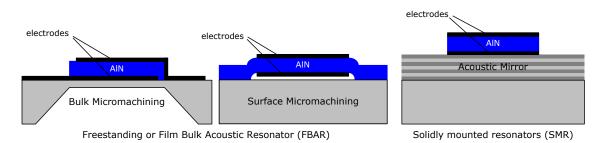

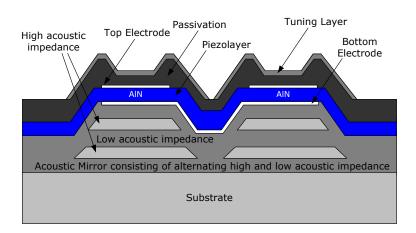

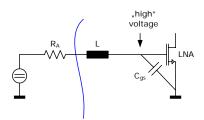

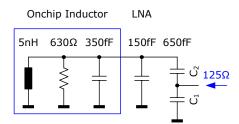

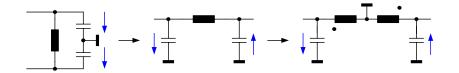

The chosen receiver structure is an image-reject architecture. An internal matching network, also containing the RX/TX-switch, feeds the incoming radio signal into a differential low noise amplifier (LNA), which also includes two BAW resonators for filtering purposes. The employed resonators are mirror-type BAWs, also known as solidly mounted resonators (SMR) [64]. Typically, the parasitic capacitances of the electrodes of such BAWs are not equal, since the bottom electrodes have a higher capacitance against ground due to their proximity to the substrate. It is therefore advantageous to use two BAWs, one in each branch of the differential LNA [7]. Since

#### 1.3 The BAW-based Transceiver

| Weight                                                         | <5g                |

|----------------------------------------------------------------|--------------------|

| Volume (12 x 13 x 6.4 mm <sup>3</sup> )                        | <1 cm <sup>3</sup> |

| Technology                                                     |                    |

| Transceiver                                                    | CMOS, 0.13 µm      |

| Microcontroller                                                | CMOS, 0.24 µm      |

| Supply Voltage                                                 |                    |

| Microcontroller                                                | 2 - 3.6V           |

| Transceiver:                                                   |                    |

| in receive mode:                                               | 2.9 - 3.6V         |

| in transmit mode:                                              | 2 - 3.6V           |

| (all internal transmitter building blocks operate at $1.5 V$ ) |                    |

| Current Consumption                                            |                    |

| Microcontroller                                                | 3 - 5 mA           |

| Transceiver:                                                   |                    |

| in receive mode (FSK, -90 dBm, 50 kbit/s):                     | 8 mA               |

| in transmit mode (FSK, 1dBm):                                  | 6 mA               |

| Oscillator core + biasing                                      | 900 µA             |

| Power amplifier (1 dBm, 2.1 GHz)                               | 3.5 mA             |

| Overall peak current                                           | <10 mA             |

Table 1.1: Key figures of the proposed sensor node.

the attenuation near the series resonance frequency of the BAW is very high, low side injection of the local oscillator (LO) signal leads to a high additional suppression of the image frequency, allowing for a low intermediate frequency (IF) of 10.7 MHz. Typically, the I- and Q-phases required for the image reject mixers are generated by the local oscillator. The applied BAW oscillator, however, does not provide quadrature phases because a quadrature oscillator would have a higher current consumption. This is why the I- and Q- phases are generated in the signal path by the polyphase filter (PPF) which follows the LNA. Because of the intermediate frequency of 10.7 MHz, the LO signal required for the mixers has a certain frequency offset with respect to the transmit frequency. Therefore a second oscillator has to be integrated, which is connected to a BAW resonator with a slightly different resonance frequency. After mixing, the IF signal is filtered and fed to a limiting amplifier with a gain of more than 80 dB. The limiting amplifier eliminates the need for an automatic gain control and delivers a binary signal. Additionally, the limiting amplifier delivers an RSSI (received signal strength indicator) signal, which is converted to a digital codeword by a 10bit ADC. The RSSI signal can be used as wake-up criterion as well as for fine tuning of the LO frequency, the BAW filters, and the matching network. In the digital domain, the binary output of the limiting amplifier is directly mixed into complex baseband by using a numerically controlled oscillator (NCO), which allows tuning of the frequency

Figure 1.15: Block diagram of the transceiver.

in very fine frequency steps. The digital clock is derived from one of the two BAW oscillators. After additional digital filtering and demodulation, the signal is passed to the matched filter. By means of the clock and data recovery unit, the output of the matched filter is sampled and the received payload is stored in a FIFO memory, where the microcontroller can access the data via the SPI. In order to have access to the FIFO and to allow configuration of the transceiver while the oscillators are turned off, the SPI is implemented asynchronously.

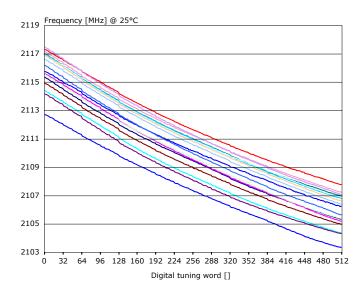

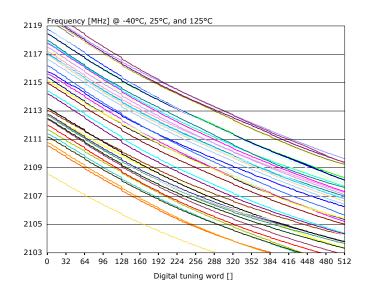

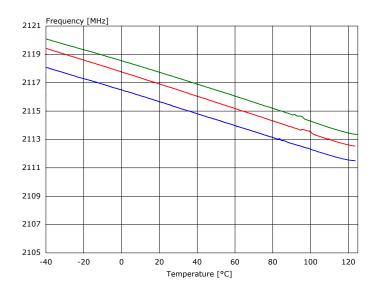

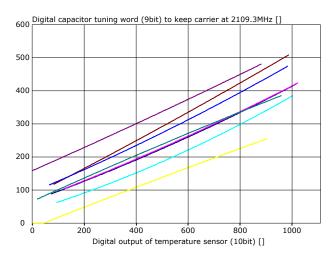

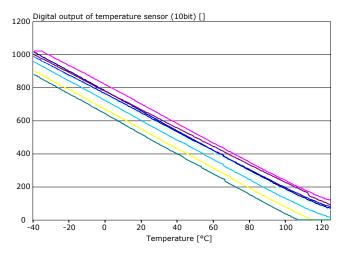

The modulated carrier signal for the transmitter is generated by a free-running BAW oscillator in the same way as the LO signal for the receiver. To overcome temperature drift effects of the resonance frequency, the temperature is measured and compensated by means of digitally controlled capacitors in parallel to the resonator. In addition to the capacitor bank, the BAW can be tuned with a variable DC biasing. More details on tuning can be found in chapter 4.5 on page 81. The modulated carrier is fed to a power amplifier after pre-amplifying. In transmit mode the power amplifier allows transmission of a signal with a power of about 1 dBm into a 50  $\Omega$  load.

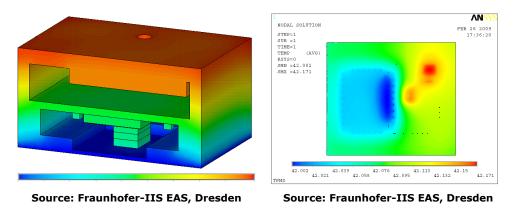

### 1.4 Design Issues when using 3D Integration Techniques

The following chapter was taken from [8, 9, 14] (own publications). My contribution to the work was to provide information about the RF application and to support the

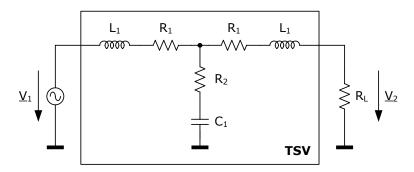

Figure 1.16: Symmetric equivalent network of TSV.

Figure 1.17: Scanning electron microscope (SEM) photo of the TSV.

analytical calculation of the efficiency out of the S-parameters and I provided a proposal of a round via structure. The simulations and interpretation were accomplished by project partners.

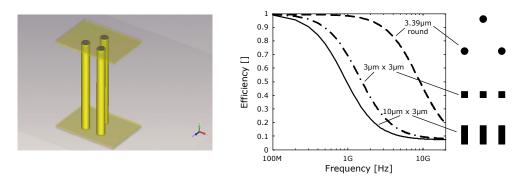

In [8, 9, 14], design issues when using 3D integration techniques are investigated. The most important issue in a 3D stack is the interconnection of the different dies. For this reason in [8, 9, 14] analyses and simulations of different TSVs structures have been performed. The output of the FEM simulations are scattering (S) parameter matrices describing the RF performance of the TSVs. With the help of [35] the S-parameter matrix  $\underline{S}$  can be transformed to the impedance parameter matrix  $\underline{Z}$ :

$$\underline{\mathbf{Z}} = \mathbf{Z}_0^{\frac{1}{2}} (\mathbf{E} - \underline{\mathbf{S}})^{-1} (\mathbf{E} + \underline{\mathbf{S}}) \mathbf{Z}_0^{\frac{1}{2}}$$

(1.3)

A possible equivalent circuit of the TSV is shown in Figure 1.16. From the <u>Z</u>-matrix, the values of the components for one frequency can be calculated. The efficiency  $\eta$  of a TSV is defined as the output power  $P_{\rm o}$  divided by the total electrical power  $P_{\rm i}$  and

Figure 1.18: Efficiency for default TSV, half wafer thickness, double conductance of substrate, double oxide thickness, and  $50 \Omega$  load impedance.

Figure 1.19: Microwave studio (from CST AG) 3D simulation model of round TSV and efficiency of different TSV structues.

can be determined using equation 1.4:

$$\eta = P_{o}/P_{i}$$

$$P_{o} = \Re\{\underline{V}_{2}\underline{I}_{2}^{*}\} = \Re\{R_{L}\underline{I}_{2}\underline{I}_{2}^{*}\} = R_{L}|\underline{I}_{2}|^{2}$$

$$P_{i} = |\underline{I}_{1}|^{2}\Re\{\underline{Z}_{11} - \frac{\underline{Z}_{12}^{2}}{\underline{Z}_{11} + R_{L}}\}$$

$$\eta = \frac{R_{L}\left|\frac{\underline{Z}_{12}}{\underline{Z}_{11} + R_{L}}\right|^{2}}{\Re\{\underline{Z}_{11} - \frac{\underline{Z}_{12}^{2}}{\underline{Z}_{11} + R_{L}}\}}$$

(1.4)

In the proposed transmitter, rectangular TSV are used. A scanning electron microscope (SEM) photo of the TSV after etching is shown in Figure 1.17. Chapter 4, page 59, explains why the oscillator makes use of the parallel resonance of the BAW. The resistance at parallel resonance is in the range of a few k $\Omega$ s. Hence the resistor  $R_1$  contributes only a minor part of the overall losses. But this is not the case for  $R_2$ , which represents losses due to the resistance of the substrate. From Figure 1.18 it can be seen that, at 2.1 GHz, 68% of the energy is lost in the substrate

| TSV structure                                   | $R_1$  | $L_1$  | $R_2$ | $C_1$  |

|-------------------------------------------------|--------|--------|-------|--------|

| 10 x 3 µm <sup>2</sup> rectangular              | 0.015Ω | 38 pH  | 156 Ω | 300 fF |

| 3 x 3 µm <sup>2</sup> square                    | 0.01Ω  | 29 pH  | 166 Ω | 190 fF |

| round, diameter: $3.39\mu m$ , area: $9\mu m^2$ | 5.4Ω   | 0.2 pH | 75 Ω  | 44 fF  |

Table 1.2: Comparison of component values of the TSV equivalent circuit.

when connected to  $2 k\Omega$ . Hence in the proposed transmitter the BAW is flip-chipped directly onto the transceiver, as shown in Figure 1.7, without using TSVs. Simulations [8, 9, 14] showed that the losses into the substrate can be optimized by reducing the parasitic capacitance  $C_1$ , for example by utilization of a thicker oxide for isolation or by reducing the thickness of the wafer. Another possibility is to optimize the conductivity of the substrate.

Another approach is to use another TSV topology: In Figure 1.19 the simulation model of three round TSVs is presented, each with an area of  $9\,\mu$ m<sup>2</sup> (diameter of 3.39  $\mu$ m), and placed at the corners of an equilateral triangle. This topology has the lowest possible surface area with the same cross section as the rectangular ones. The parallel connection of multiple TSVs reduces the total resistance and inductance [33].

On the right side of Figure 1.19 the simulations of the efficiency of the proposed round via is compared to vertical interconnections consisting of a 1 by 3 rectangular TSV array. In the first case the shape of the TSV is a  $3 \times 3 \mu m^2$  square, and in the second case a  $10 \times 3 \mu m^2$  rectangle. Table 1.2 provides the corresponding component values of the TSV equivalent circuit given in Figure 1.16. The round TSVs show the best performance.

### 1.5 Conclusion

State-of-the-art Tire Pressure Monitoring Systems (TPMS) are wireless sensor nodes mounted on the rim. Attaching the node on the inner liner of a tire allows the sensing of important technical parameters and enables the storage of additional information. By exploiting BAW resonators, the use of a bulky and shock-sensitive quartz crystal and a PLL can be avoided. This makes the system more robust and radically reduces the start-up time from a few ms, as in state-of-the-art quartz crystal oscillator based systems, to  $2 \,\mu s$ .

It was shown that a system-in-package (SiP) can be advantageous in terms of price compared to a system-on-chip (SoC) implementation, although the BAW technology is compatible with a standard integrated circuit (IC) process and it is possible to integrate BAW resonators above an IC [74]. The reason for this is the relatively low yield (80%) of the BAW resonators caused by the process variation of the resonance frequency. More details on this can be found in chapter 4.5 on page 81. Since the BAW

resonator is very small, the costs of the stand-alone resonator are negligible. But if the resonator is integrated on top of the relatively large and expensive transceiver ASIC, the overall yield is dramatically reduced.

Therefore a 3D chip stack was developed by project partners to provide best compactness, lowest volume, and maximum robustness. Design issues when using this integration technique were considered. It was shown that an optimized structure, where three round TSVs are placed at the corners of an equal-sided triangle can significantly reduce losses into the substrate. This structure has the lowest possible surface area to the substrate and hence TSV technology could be also applied for RF interconnections.

## 2 Transmitter Concept

#### 2.1 The Power-Bandwidth Trade-Off

In the following chapter the required features of the transmitter - like modulation scheme (and therefore the required bandwidth BW of the receiver), maximum data rate, transmit power  $S_{\rm T}$ , start-up time, and current consumption are specified. The design goal of a transmitter is to keep the required energy per bit low. This can be done by finding the optimum transmit power and the optimum data rate. A higher data rate allows a short active time of transmission, but would require a higher bandwidth or a more complex modulation scheme and hence a higher complexity of the transmitter. On the other hand a higher bandwidth implies more received noise in the receiver and this reduces the signal-to-noise ratio at the receiver. Or in other words the sensitivity of the receiver is getting worse. To compensate this effect the transmitter and receiver. This problem is known as power-bandwidth trade-off [22]. These basic relations are expounded by the Shannon-Hartley theorem.

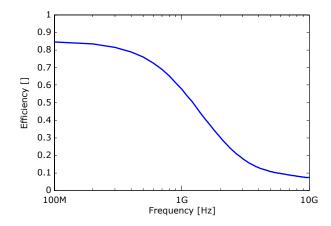

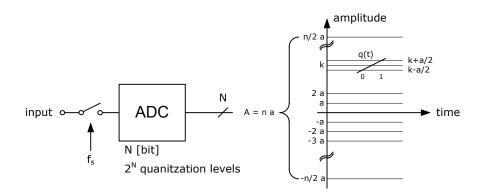

This theorem can be obtained from the following considerations. In Figure 2.1 an input signal is sampled with the sampling frequency  $f_s$ . Subsequently it is quantized by means of an ADC with N bits. Hence the amplitude range A is divided into  $n = 2^N$  equal parts. Assuming that the input signal is uniformly distributed, all levels are equally present over time. After quantization the signal power  $P_s$  can be calculated

Figure 2.1: Time and amplitude discrete system.

with:

$$P_{\rm S} = \frac{1}{n} \sum \left( 2\left(\frac{a}{2}\right)^2 + 2\left(\frac{3a}{2}\right)^2 + 2\left(\frac{5a}{2}\right)^2 + \dots + 2\left(\frac{(n-1)a}{2}\right)^2 \right) = \frac{a^2}{12}(n^2 - 1)$$

(2.1)

Since the input signal is uniformly distributed, the quantization noise is too. Thus the quantization noise power  $P_Q$  can be calculated by squaring and integration of a linear ramp  $q(t) = -\frac{a}{2} + a \cdot t$  (see Figure 2.1). The ramp starts at t = 0s and leaves the quantization level at t = 1s. Hence  $P_Q$  is:

$$P_{\rm Q} = \int_{0}^{1} \left( -\frac{a}{2} + a \cdot t \right)^2 = \frac{a^2}{12}$$

(2.2)

If one knows the signal and noise power it is easy to calculate the signal-to-noise ratio.

$$\frac{P_{\rm S}}{P_{\rm Q}} = \frac{S}{N} = n^2 - 1 \quad \rightarrow \quad \log_2\left(\frac{S}{N} + 1\right) = 2\log_2 n \tag{2.3}$$

After sampling and quantization the data rate C at the output of the ADC is  $f_s \cdot N$ . The Nyquist sampling theorem states that the input signal with the bandwidth BW, has to be sampled at least with  $f_s = 2BW$ . The channel capacity can be calculated as follows:

$$C = f_{s} \cdot N = 2 \cdot BW \cdot N = 2 \cdot BW \cdot \log_{2} n$$

$$C = BW \log_{2} \left(\frac{S}{N} + 1\right)$$

(2.4)

Equation 2.4 is known as Shannon-Hartley theorem. The Shannon-Hartley theorem [18, 22] describes the available channel capacity C in [bit/s] of a communication link perturbed by additive white Gaussian noise as a function of the required bandwidth BW and of the required signal-to-noise ratio  $S_R/N_R$  at the receiver. Although the Shannon-Hartly law provides only a theoretical limit, which cannot be reached in a practical implementation, basic relations can be obtained from it.

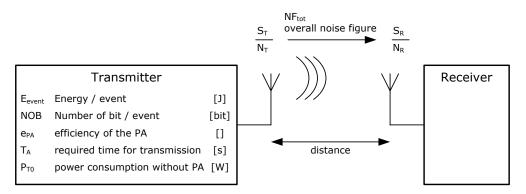

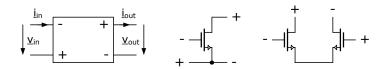

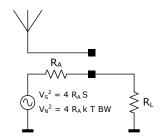

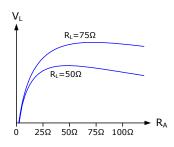

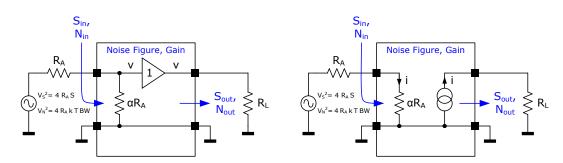

To find the optimum transmit power a simple model of the communication link including transmitter and receiver is introduced (see Figure 2.2). The overall noise figure  $NF_{tot}$  can be calculated by dividing the signal-to-noise ratio  $\frac{S_T}{N_T}$  at the transmitter and the signal-to-noise ratio at the receiver  $\frac{S_R}{N_R}$ .  $NF_{tot}$  includes the path-losses as well as other non-idealities, such as noise introduced by the receiver front end. In the proposed model the receiver and the transmitter are operating at standard noise temperature  $T_0 = 290 \,\mathrm{K}$ . If the maximum overall noise figure is assumed to be known, the signal-to-noise ratio at the receiver can be determined as shown in equation 2.5.

$$NF_{\text{tot}} = \frac{S_{\text{T}}/N_{\text{T}}}{S_{\text{R}}/N_{\text{R}}} \rightarrow \frac{S_{\text{R}}}{N_{\text{R}}} = \frac{S_{\text{T}}}{N_{\text{T}} \cdot NF_{\text{tot}}} = \frac{S_{\text{T}}}{k \cdot T \cdot BW \cdot NF_{\text{tot}}}$$

(2.5)

By using the equations 2.4 and 2.5 the available channel capacity can be calculated.

Figure 2.2: Simplified model of the communication.

Assuming a certain number of bits per event (*NOB*) the active time  $T_A$  needed for a transmission can be found using equation 2.6.

$$T_{\rm A} = \frac{NOB}{C}$$

$$C = BW \log_2 \left( \frac{S_{\rm R}}{\mathbf{k} \cdot T \cdot BW} + 1 \right) = BW \log_2 \left( \frac{S_{\rm T}}{\mathbf{k} \cdot T \cdot BW \cdot NF_{\rm tot}} + 1 \right)$$

(2.6)

The total amount of energy  $E_{\text{event}}$ , which is consumed during one event, is the active time  $T_{\text{A}}$  multiplied with the power consumption of the transmitter. The transmitter's power consumption is composed of the transmitted power corrected by the efficiency  $e_{\text{PA}}$  of the power amplifier (PA) and the power consumption of the remaining transmitter  $P_{\text{T0}}$ . Additionally the energy  $E_{\text{startup}}$  has to be added to take the energy required during the start-up into account. Using equation 2.6 yields in:

$$E_{\text{event}} = T_{\text{A}} \cdot \left( P_{\text{T0}} + \frac{S_{\text{T}}}{e_{\text{PA}}} \right) = \frac{NOB}{BW \log_2 \left( \frac{S_{\text{T}}}{\mathbf{k} \cdot T \cdot BW \cdot NF_{\text{tot}}} + 1 \right)} \cdot \left( P_{\text{T0}} + \frac{S_{\text{T}}}{e_{\text{PA}}} \right) + E_{\text{startup}} \quad (2.7)$$

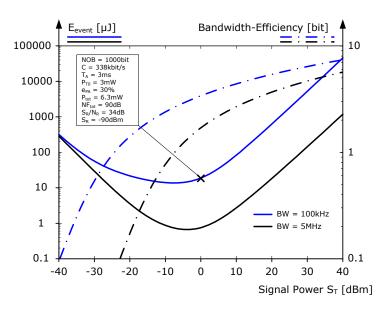

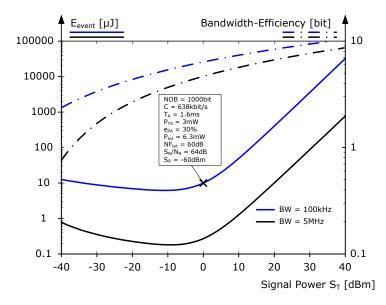

In this way it is possible to plot the energy consumed during one event against the transmitted signal power. The result is illustrated in Figure 2.3 for an overall noise figure  $NF_{tot} = 90 \,dB$  and in Figure 2.4 for  $NF_{tot} = 60 \,dB$ . For the two plots some assumptions have been made: The number of bits per event is assumed to be 1000, the power consumption  $P_{T0}$  is 3 mW (this is equal to a current consumption of 2 mA at a supply voltage of 1.5 V), and the efficiency of the PA is 30%. This fits the features of the proposed transmitter. The start-up energy  $E_{startup}$  is disregarded due to the short start-up time of oscillator, which is about 2 µs. In Figure 2.3 the planned operating point of the transceiver system is marked. The outcome of equation 2.7 is the fact that an optimum of the transmitted signal power can be found: A high signal power would cause a high current consumption of the power amplifier. On the other hand, a very low signal power induces a lower signal-to-noise ratio at the receiver and thus the receiver can only process lower data rates and this is equivalent to a longer transmit time, which increases the energy required at

Figure 2.3: Simplified power-bandwidth trade-off ( $\mathit{NF}_{tot} = 90 \, \mathrm{dB}$ ).

Figure 2.4: Simplified power-bandwidth trade-off ( $NF_{tot} = 60 \text{ dB}$ ).

the transmitter. Besides that, a higher available bandwidth can help to reduce the power consumption of the transmitter. The bandwidth and the losses (here taken into account by the overall noise figure  $NF_{\rm tot}$ ) are the two parameters describing the quality of the communication link.

It is important to note that the channel capacity C close to the minimum is 338 kbit/s for an overall noise figure of 90 dB, whereas the bandwidth is only 100 kHz. In the proposed transmitter continuous phase frequency shift keying (CPFSK) or ASK is used for modulation. Although the bandwidth of a CPFSK modulated carrier is

theoretically not limited, according to [36] the occupied bandwidth  $BW_{\rm FM}$ , where most of the energy is concentrated, can be approximated with the Carson rule. For a modulation index m > 1 the bandwidth can be derived as a function of the frequency deviation  $\Delta f$  and of the data rate DR:

$$m = \Delta f \cdot T_{\rm s} = \frac{\Delta f}{\rm DR}$$

$$BW_{\rm FM} = 2(\Delta f + DR) = 2(m+1)DR$$

(2.8)

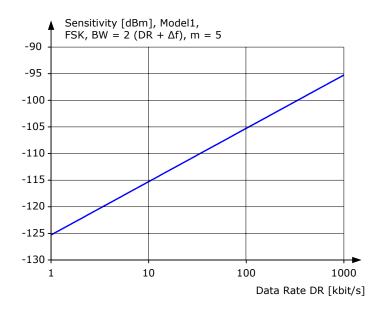

Unfortunately, it is not possible to transmit 338 kbit/s in a 100 kHz channel with CPFSK. To accomplish such a data rate, a higher modulation scheme has to be used. This would require more complex hardware, such as a linear power amplifier, mixers, and so on. Therefore the model of the receiver is enhanced. In Table 2.1 the sensitivity values found in the data sheet [37] of an FSK receiver for different data rates are given. The occupied bandwidth in the table is calculated with equation 2.8. The used bandwidth at IF is taken from the data sheet. The noise floor is determined using the IF bandwidth and the relation  $k \cdot T \cdot BW$ . For the first model the required signal-to-noise ratio (see equation 2.9) for correct demodulation at the receiver is found by rewriting equation 2.4, by replacing the channel capacity *C* with the data rate *DR*, and by adding a noise figure *NF*<sub>RX</sub> to take all non-ideal properties of the receiver front end and demodulator into account. The noise figure is chosen in such a way that the sensitivity value given in the first row in the table is exactly fitted.

$$\frac{S_{\rm R}}{N_{\rm R}} = \left(2^{DR/BW_{\rm FM}} - 1\right) \cdot NF_{\rm RX}$$

(2.9)

An alternative way (model 2) to calculate the sensitivity is to use the  $\frac{E_{\rm b}}{N_0} = 11 \, {\rm dB}$ , which is taken from a bit error probability curve (at a bit error rate of 10<sup>-3</sup>) found in [22]. In this way it is possible to determine the signal-to-noise ratio as shown in equation 2.10. Here again the noise figure is added to take the non-idealities of the receiver into account.

$$\frac{S_{\rm R}}{N_{\rm R}} = \frac{E_{\rm b}}{N_0} \frac{DR}{BW_{\rm FM}} \cdot NF_{\rm RX}$$

(2.10)

The first model is used to extrapolate the sensitivity for higher data rates. The IF bandwidth is assumed to be equal to the occupied bandwidth. The result is illustrated in Figure 2.5. The sensitivity increases linearly with increasing data rate. If the path-loss is known, the required transmit power can be calculated easily. Assuming unobstructed free space with no multipath propagation (free line of sight), the Friis transmission equation [19] can be used to estimate the distance R between transmitter and receiver. The Friis formula is given in equation 2.11, where  $G_R$  and  $G_T$  denote the gain of the receive antenna and of the transmit antenna respectively and L denotes the path loss.

$$L = \frac{S_{\rm R}}{S_{\rm T}} = \frac{G_{\rm R} \cdot G_{\rm T} \cdot \lambda^2}{(4\pi R)^2}$$

(2.11)

#### 2.1 The Power-Bandwidth Trade-Off

| Data Rate<br>DR<br>[kbit/s] | Frequency<br>Defiviation<br>Δf [kHz] | occupied<br>Bandwidth<br>[kHz] | used IF<br>Bandwidth<br>[kHz] | Sensitivity<br>(Datasheet)<br>[dBm] | Noise floor<br>[dBm] | S <sub>R</sub> /N <sub>R</sub><br>(Model 1)<br>[dB] | Sensitivity<br>(Model 1)<br>[dBm] | Deviation<br>(Model 1)<br>[dBm] | S <sub>R</sub> /N <sub>R</sub><br>(Model 2)<br>[dB] | Sensitivity<br>(Model 2)<br>[dBm] | Deviation<br>(Model 2)<br>[dBm] |

|-----------------------------|--------------------------------------|--------------------------------|-------------------------------|-------------------------------------|----------------------|-----------------------------------------------------|-----------------------------------|---------------------------------|-----------------------------------------------------|-----------------------------------|---------------------------------|

| 2                           | 10                                   | 24                             | 50                            | -119                                | -126.8               | 7.84                                                | -119.0                            | 0.0                             | 7.81                                                | -119.0                            | 0.0                             |

| 10                          | 14                                   | 48                             | 50                            | -114                                | -126.8               | 12.01                                               | -114.8                            | 0.8                             | 11.79                                               | -115.1                            | 1.1                             |

| 10                          | 50                                   | 120                            | 125                           | -112                                | -122.9               | 7.84                                                | -115.0                            | 3.0                             | 7.81                                                | -115.1                            | 3.1                             |

| 50                          | 50                                   | 200                            | 300                           | -105                                | -119.0               | 12.87                                               | -106.2                            | 1.2                             | 12.58                                               | -106.5                            | 1.5                             |

| 2                           | 10                                   | 24                             | 300                           | -110                                | -119.0               | 7.84                                                | -111.2                            | 1.2                             | 7.81                                                | -111.3                            | 1.3                             |

| 10                          | 14                                   | 48                             | 300                           | -106                                | -119.0               | 12.01                                               | -107.0                            | 1.0                             | 11.79                                               | -107.3                            | 1.3                             |

| 10                          | 50                                   | 120                            | 300                           | -110                                | -119.0               | 7.84                                                | -111.2                            | 1.2                             | 7.81                                                | -111.3                            | 1.3                             |

Table 2.1: Comparison of the sensitivity of a receiver (TDA5240, Infineon [37]) with different models for different data rates.

Figure 2.5: Sensitivity of the modelled receiver versus data rate.

With an antenna loss of 5dB for each antenna, the overall noise figure  $NF_{tot}$  of 90 dB implies a ratio of received power to transmitted power  $\frac{S_{\rm R}}{S_{\rm T}}$  of -80 dB. Under the assumption that the antennas radiate isotropically, the antenna gains are equal to 0 dB and thus the distance R in free space can be calculated as about 100 m for a 2.4 GHz ( $\lambda = 0.12 \,\mathrm{m}$ ) transmission frequency.

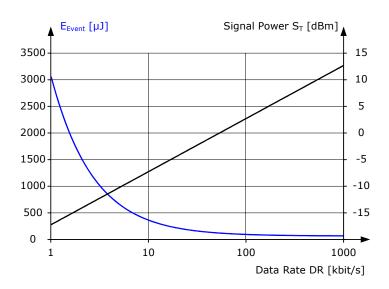

In the following considerations a more conservative scenario is assumed for the communication from the tires to the base station in the car. The path-loss exponent is increased from 2 to 4. To account for multipath and polarization effects 20 dB attenuation are added. Further two times 10 dB are supposed to be caused by the radiation efficiency of the antennas. The result is 108 dB path-loss for a 5 m communication distance. By adding the path-losses and the sensitivity, the required signal power  $S_{\rm T}$  can be calculated as a function of the data rate. By using the introduced model in equation 2.7 the energy for one event  $E_{\rm event}$  can be determined. The relationship between signal power, energy for one event, and data rate can be found in Figure 2.6.

Figure 2.6: Required energy per event and the transmitted signal power versus data rate.

Thus the transmitter's power consumption can be significantly reduced by increasing the data rate. Increasing the data rate implies a higher bandwidth for an FSK transmitter and therefore the signal power has to be increased in the same way to keep the communication distance constant. Due to the higher data rate, the active time is reduced and so the power amplifier needs the same amount of energy independently of the data rate. But the portion of the remaining transmitter  $P_{\rm T0}$  (the overhead) is reduced due to the short active time and hence the energy for one event converges to its ideal value with increasing data rate as seen in Figure 2.6. Also the model of the FSK transmitter shows a good compromise at a relatively low transmission power  $S_{\rm T}$  of 0 dB.

The power-bandwidth trade-off can be summarized as follows. An increase in the data rate can be achieved in two different ways:

The first possibility is to increase the data rate while keeping the bandwidth constant. A higher signal power at the transmitter increases the signal-to-noise ratio at the receiver and therefore the channel capacity is increased as known from the Shannon-Hartley theorem. A clear optimum for signal power and data rate at a certain bandwidth can be found. Or, in other words, *DR/BW* is at its optimum. *DR/BW* is a measure how efficiently the bandwidth (bandwidth-efficiency) is occupied. A higher bandwidth, which corresponds to an improved communication link, helps to reduce the required energy as shown in Figure 2.3. For a low bandwidth (bandwidth limited systems) the optimum *DR/BW* is quite high and this corresponds to a complex modulation technique like GMSK or M-ary signaling. For high available bandwidth the optimum *DR/BW* is smaller, resulting in a low complexity modulation scheme like FSK or for even higher bandwidths in frequency spreading. For high available bandwidths, the optimum power is lower

#### 2.2 Transmitter Architectures

(power limited systems). Obviously this is preferred for a low power transmitter, if the required bandwidth is available.

An increase in the data rate can also be achieved by simultaneously increasing the bandwidth. This corresponds to a constant bandwidth efficiency or constant *DR/BW*. In this situation the signal power has to be increased in the same way as the data rate increases. But due to the higher data rate the active time decreases and the power amplifier consumes the same amount of energy. However, the overhead in the transmitter decreases too, because of the short active time; hence the overall energy per event is improved for high data rates at the drawback of a high peak current caused by the high transmitted signal power.

For a very high bandwidth BW the Shannon-Hartley theorem given in equation 2.6 can be simplified as shown in equation 2.12. This equation is also known as the Shannon limit.

$$\lim_{x \to 0} (1+x)^{1/x} = e \quad \rightarrow \quad x = \frac{S_{\mathrm{R}}}{\mathbf{k} \cdot T \cdot BW}$$

$$C = BW \log_2 \left( \frac{S_{\mathrm{R}}}{\mathbf{k} \cdot T \cdot BW} + 1 \right) = BWx \log_2 (1+x)^{1/x} \quad \rightarrow$$

$$\lim_{BW \to \infty} C = \lim_{BW \to \infty} BW \frac{S_{\mathrm{R}}}{\mathbf{k} \cdot T \cdot BW} \log_2(\mathbf{e}) = \frac{S_{\mathrm{R}}}{\mathbf{k} \cdot T} \log_2 \mathbf{e} = \frac{S_{\mathrm{T}} \cdot L}{\mathbf{k} \cdot T} \log_2 \mathbf{e} \quad (2.12)$$

For a large bandwidth, channel capacity C is directly proportional to signal power at the receiver and therefore also to signal power  $S_{\rm T}$  radiated by the transmitter times the path loss L. This result is very similar to the given FSK example and indicates to the theoretical limit.

The outcome of the previous considerations is that the current consumption of state-of-the-art TPMS sensor nodes (4-10 kbit/s) can be improved by increasing the data rate. To keep the complexity of the transmitter low, a simple FSK modulation scheme is used. For a certain modulation technique, increasing the data rate makes sense, till the energy for one event is close to its ideal value. Then the overhead, mainly caused by the BAW oscillator, is negligible. For the BAW-based transmitter this is the case for a data rate in the range of 100 kbit/s and a signal power in the range of 0 dBm.

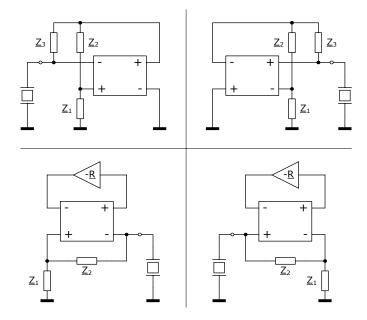

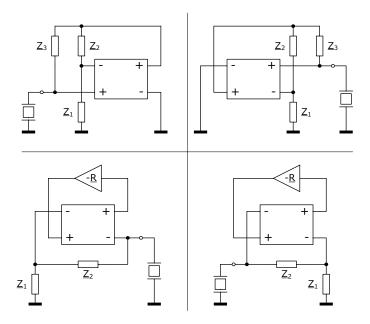

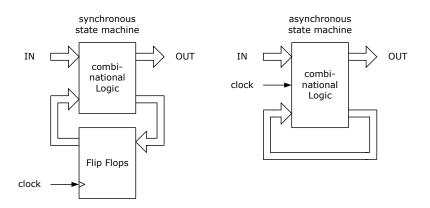

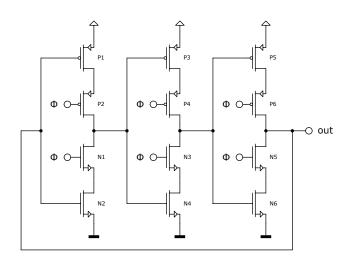

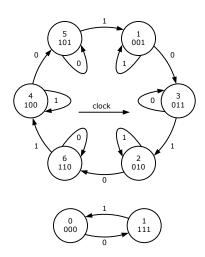

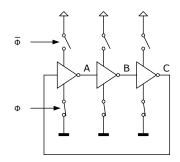

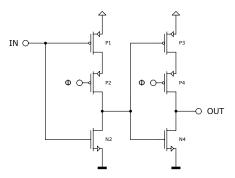

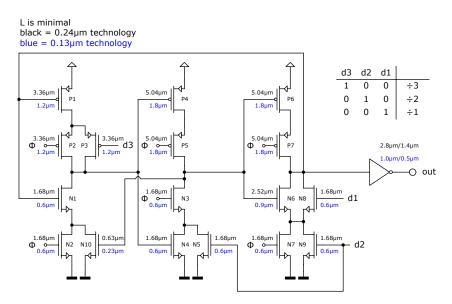

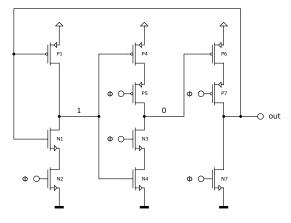

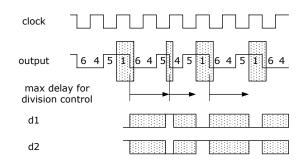

## 2.2 Transmitter Architectures

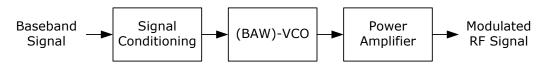

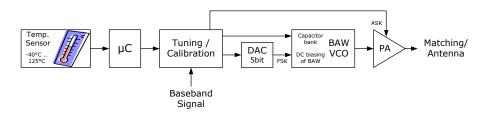

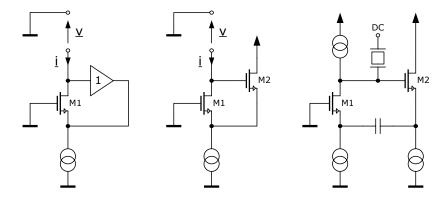

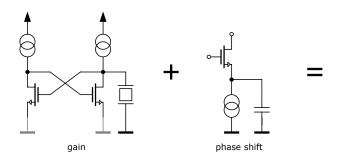

The task of a transmitter is to perform modulation, up-conversion, and power amplification [21]. In the proposed transmitter, modulation and up-conversion are combined in one step, as illustrated in Figure 2.7, the simplest block diagram of a transmitter. This kind of transmitter is ideally suited for simple modulation schemes, like continuous phase frequency shift keying (CPFSK) or amplitude shift keying (ASK). To

Figure 2.7: Simplest architecture of a transmitter [21].

Figure 2.8: Simple implementation of a transmitter with discrete components [43].

overcome temperature and process variations of the BAW oscillator, the baseband signal has to be processed by the signal conditioning block. Additionally the bandwidth of the transmitted signal can be reduced by means of digital filtering of the baseband signal. For instance in a GFSK application a Gaussian filter can be used to avoid any abrupt frequency deviation or a Blackman filter can be used in case of ASK modulation. No pulse shaping has been implemented in the proposed prototype, but could be implemented with little effort in the digital domain. The advantage of this architecture is the low power consumption due to the low complexity. In the proposed implementation the signal conditioning block is very simple and its power consumption is negligible. An additional task of the signal condition block is to overcome temperature drift effects of the resonance frequency, therefore the temperature is measured and compensated by means of digitally controlled capacitors in parallel to the resonator.

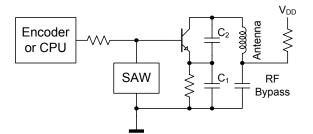

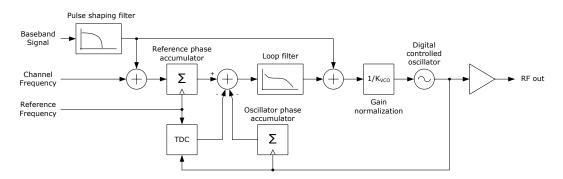

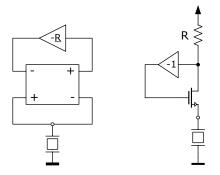

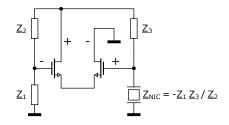

Indeed such simple transmitters using resonators have been in widespread use for unlicensed application. Applications such as automotive keyless entry, door and gate openers, wireless alarm sensors, medical alert pendants, bar code readers, wireless remote control, security, and data transmission areas [43] employ them. An example of a transmitter using a surface acoustic wave (SAW) resonator and discrete components is drawn in Figure 2.8. The main disadvantage of this architecture is its fairly unstable frequency source. On the other end of the spectrum of complexity there is a transmitter based on the all-digital frequency synthesizer illustrated in Figure 2.9, which has been presented in [45]. The task of the PLL is to transform the precise and stable frequency of quartz crystal to RF. The required building blocks are the digitally controlled oscillator (DCO), a time-to-digital converter (TDC), loop filter, a gain normalization block, and a reference and oscillator phase accumulator. All

#### 2.2 Transmitter Architectures

Figure 2.9: Transmitter based on the all-digital frequency synthesizer [45].

Figure 2.10: Direct (up)-conversion transmitter [21].

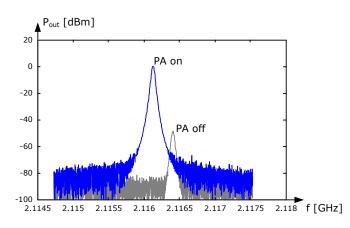

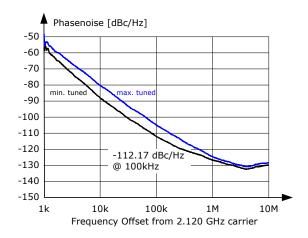

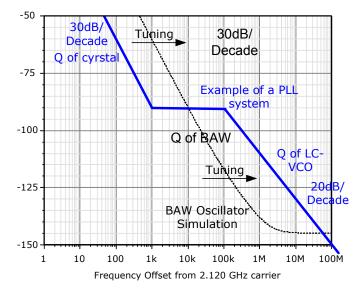

Figure 2.11: Measurement of BAW Oscillator pulling.

blocks except the DCO are implemented in the digital domain. Two-point modulation allows proper wide-band modulation of the carrier. A calibration step in which the gain normalization is carried out makes the transmitter independent of process-voltage-temperature (PVT) variations. Additionally the frequency reference drift can be compensated if the temperature can be measured and the channel frequency is set according to a characteristic curve of the frequency drift.

Another drawback of a simple up-conversion transmitter like the one in Figure 2.10 is oscillator pulling [21]. Feedback from the power amplifier back to the oscillator can cause an unintended frequency shift. Of course, there can be different ways of

#### 2.2 Transmitter Architectures

Figure 2.12: Increased oscillator stability by using a  $\Delta\Sigma$ -PLL [12].

Figure 2.13: Possible implementation of a two-step transmitter.

coupling, which can also vary with time if the environment changes. For example, the coupling between antenna and oscillator can be influenced by simply holding one's hands close above the sensor node. This significantly changes the resonance frequency of the proposed transmitter. The measured oscillator frequency with the power amplifier turned on and turned off is shown in Figure 2.11. The measurable frequency shift is about 300 kHz, which corresponds to 140 ppm!

To overcome these limitations, different solutions can be implemented. Pulling is avoided if the oscillator's frequency is sufficiently lower or higher than the output frequency. This can be achieved for instance by using a PLL as shown in Figure 2.12 [12]. Another way is a two-step transmitter as illustrated in Figure 2.13. Both solutions have an increased complexity and therefore a significantly higher power consumption.

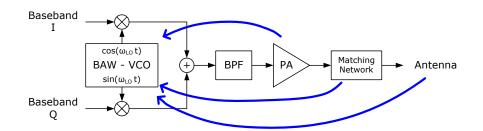

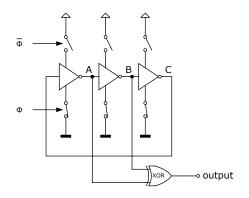

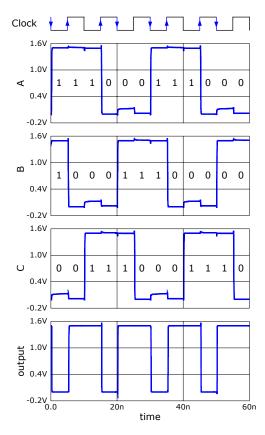

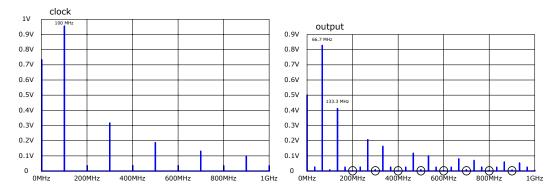

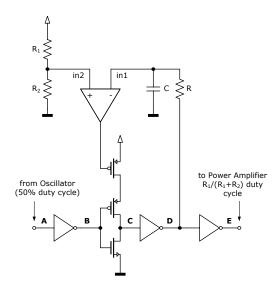

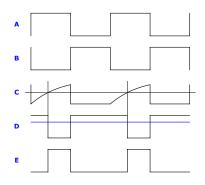

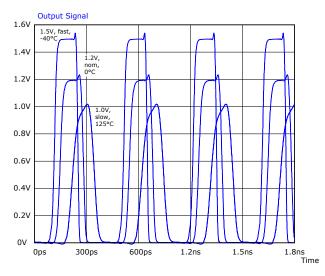

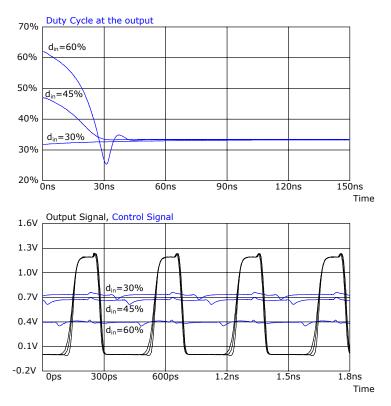

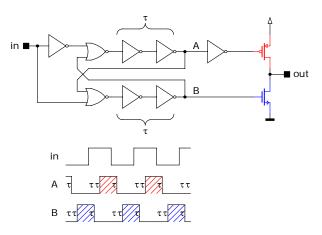

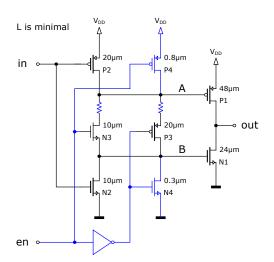

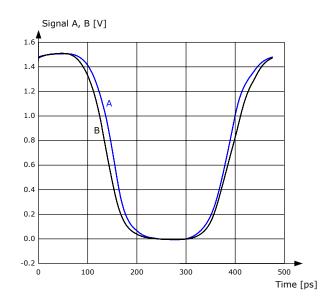

Another way to provide isolation between power amplifier and oscillator is the usage of a divider with a divider ration of 1.5 (see Figure 2.14). After division by 1.5

Figure 2.14: Providing an offset between output and reference frequency achieved by a division of 1.5.

Figure 2.15: Increased oscillator stability achieved by temperature compensation.

the output frequency and all integer multiples cannot disturb the oscillation. An offset between output and reference frequency would be mandatory for a practical implementation. This is the motivation for the asynchronous divider proposed in chapter 5.7 on page 109.

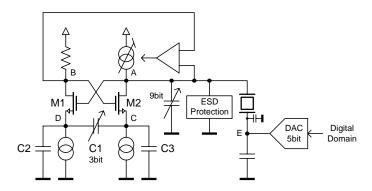

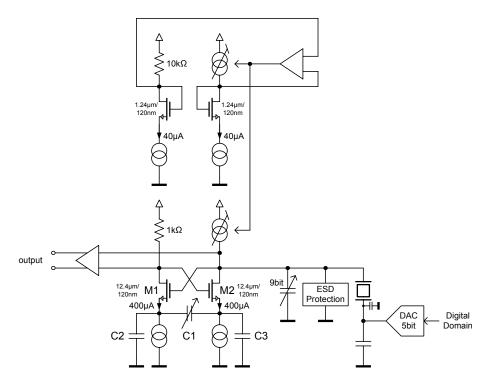

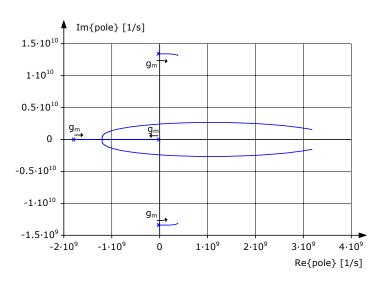

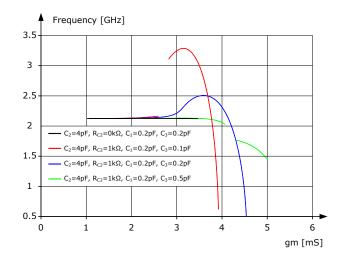

The simplified block diagram of the implemented transmitter is shown in Figure 2.15. A temperature sensor provides a measure for the current temperature on the chip. A microcontroller can calculate the appropriate tuning word by using a characteristic curve of the temperature drift of the BAW resonator. This curve is determined by a calibration step. For details on BAW tuning see chapter 4.5 on page 81. A more detailed block digram of the transceiver is illustrated in Figure 2.16.

Figure 2.16: Detailed block diagram of the e-Cubes transceiver.

2.2 Transmitter Architectures

| Reference      | IC Technology | Application                    | Datarate          | fc                | Supply<br>Voltage | Current<br>Consum. | Power<br>Consum. | Temp.<br>Range | Transı<br>Pov |       | Efficiency | Energy<br>per Bit | FoM <sub>WSN</sub> |                 |

|----------------|---------------|--------------------------------|-------------------|-------------------|-------------------|--------------------|------------------|----------------|---------------|-------|------------|-------------------|--------------------|-----------------|

|                |               |                                | [kBit/s]          | [GHz]             | [V]               | [mA]               | [mW]             | [°C]           | [mW]          | [dBm] | [%]        | [nJ/bit]          | [dB]               | [nJ/bit/<br>mW] |

| [This Work]    | CMOS 0.13µm   | WSN (eCubes) - FSK Mode        | 100               | 2.45 <sup>1</sup> | 1.5               | 4.7                | 7.1              | -40125         | 1.48          | 1.7   | 21         | 71                | 87.1               | 48              |

| [Otis05]       | CMOS 0.13µm   | WSN (PicoRadio)                | 5                 | 1.9               | 0.9-1.3           | -                  | 1.474            | -              | 0.38          | -4.2  | 26         | 294               | 86.9               | 774             |

| [Leung07]      | CMOS 0.18µm   | WLAN IEEE 802.11a              | 56000             | 5.35              | 1                 | -                  | 53               | -              | 1             | 0     | 2          | 0.95              | 80.0               | 0.95            |

| [Kluge06]      | CMOS 0.18µm   | ZigBee IEEE 802.15.4           | 250 <sup>2</sup>  | 2.4               | 1.8               | 15.7               | 28               | -              | 2.00          | 3.0   | 7          | 113               | 82.3               | 57              |

| [Staszewski04] | CMOS 0.13µm   | Bluetooth                      | 1000 <sup>2</sup> | 2.4               | 1.5               | 28                 | 42               | -              | 1.78          | 2.5   | 4          | 42                | 80.1               | 24              |

| [Staszewski05] | CMOS 90nm     | GSM/EDGE                       | 500 <sup>2</sup>  | 0.824             | 1.2               | 42                 | 50               | -              | 3.98          | 6     | 8          | 101               | 78.1               | 25              |

| [Yuan09]       | CMOS 0.18µm   | UWB                            | 40000             | 3.1-4.5           | 1.8               | 9.9                | 18               | -              | 0.05          | -13   | 0          | 36                | 70.2               | 711             |

| [Infineon09]   | -             | RKE, Metering, Remote Control, | 50                | 0.315-0.915       | 1.9-3.6           | 16                 | 48               | -4085          | 10            | 10    | 21         | 960               | 82.8               | 96              |

| [Raja08]       | CMOS 0.35µm   | WSN/WBAN                       | 10000             | 0.433             | 1                 | 1.2 <sup>4</sup>   | 1.2 <sup>4</sup> | -              | 0.0537        | -13   | 4          | 0.120             | 72.9               | 2.23            |

| [Cook06]       | CMOS 0.13µm   | WSN                            | 300-500           | 2.34              | 0.4               | -                  | 1.12             | -              | 0.32          | -4.9  | 29         | 2.24              | 88.3               | 7.0             |

| [Daly07]       | CMOS 0.18µm   | WSN                            | 1000              | 0.9165            | 1.4               | -                  | 9.1              | -              | 0.60          | -2.2  | 7          | 9.1               | 77.8               | 15              |

| [Chee05]       | CMOS 0.13µm   | WSN                            | 50                | 1.9               | 0.28              | -                  | 3.2 <sup>4</sup> | -              | 1             | 0     | 31         | 64                | 87.7               | 64              |

| [Chee06]       | CMOS 0.13µm   | WSN                            | 330               | 1.9               | 0.65              | -                  | 2.74             | -              | 1.2           | 0.8   | 44         | 8                 | 89.3               | 7               |

<sup>1</sup> Oscillator was also tested with 2.1GHz BAW resonator, values are given for 2.45GH

<sup>2</sup> These values are assumed.

<sup>3</sup> The BAW-Oscillator is always running, only the PA is switched on and off.

Values are given for a clean carrier. The power consumption is reduced by half when OOK (50%) is used, but also the transmitted power (therefore no impact on the FoM).

|   | [Otis05] = [89]        | [Leung07] = [98]                | [Kluge06] = [99] |  |

|---|------------------------|---------------------------------|------------------|--|

|   | [Staszewski04] = [100] | [Staszewski05] = [101] or [102] | [Yuan09] = [103] |  |

| İ | [Infineon09] = [40]    | [Raja08] = [104]                | [Cook06] = [105] |  |

| İ | [Daly07] = [106]       | [Chee05] = [107]                | [Chee06] = [108] |  |

## 2.3 The BAW Oscillator in Receive Mode

The task of the BAW oscillator is to provide the required signals not only for the transmitter but also for the receiver. Because of the intermediate frequency of 10.7 MHz, the LO signal required for the mixers has a frequency offset with respect to the transmit frequency. Therefore a second BAW oscillator is integrated, which is connected to a BAW resonator with a slightly different resonance frequency as already mentioned in chapter 1 on page 17.

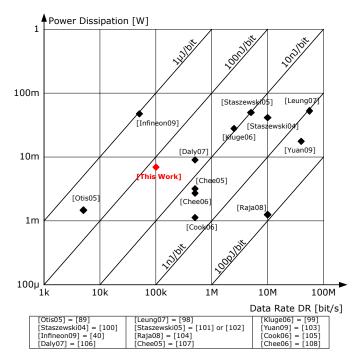

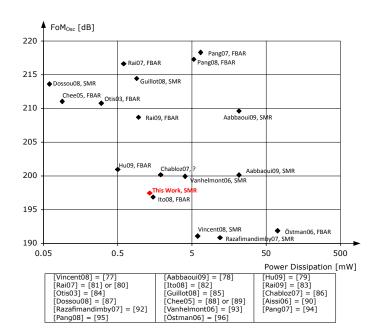

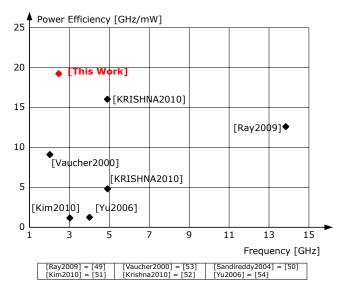

## 2.4 Figure-of-Merit (FoM) and Comparison with State-of-the-Art

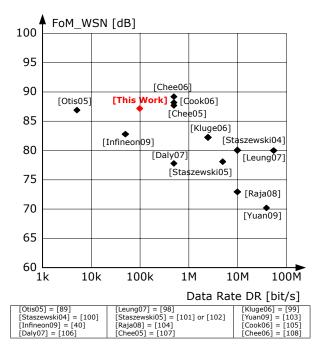

A Figure-of-Merit often used for transmitters is the energy  $E_{\rm bit}$  consumed during transmission of one bit. In Table 2.2 a performance comparison is given and Figure 2.17 shows the power consumption versus the available data rate for high performance transmitters. Since the energy per bit  $E_{\rm bit}$  is the power consumption divided by the data rate, each point in the figure can be assigned to a certain energy per bit value. Different  $E_{\rm bit}$ -values are indicated with black lines. This FoM can be interpreted as energy efficiency. It cannot be used to compare different architectures: this would be unfair, since the transmitted power is not considered. Therefore in [104] a FoM including the transmitted power is introduced. This FoM can be calculated with the

Figure 2.17: Power dissipation versus data rate for different transmitters.

following equation:

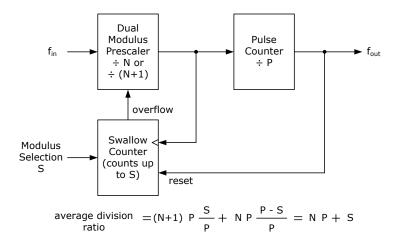

$$FoM = \frac{E_{\rm bit}}{S_{\rm T}} = \frac{P_{\rm T}}{DR \cdot S_{\rm T}}$$

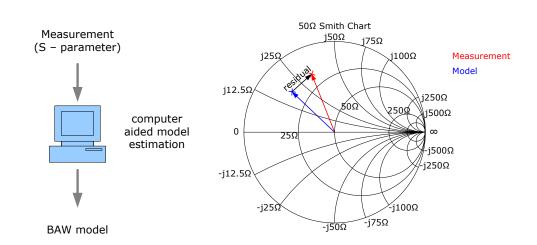

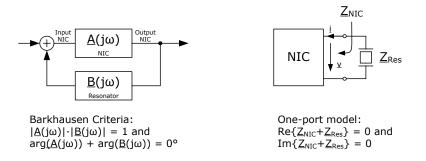

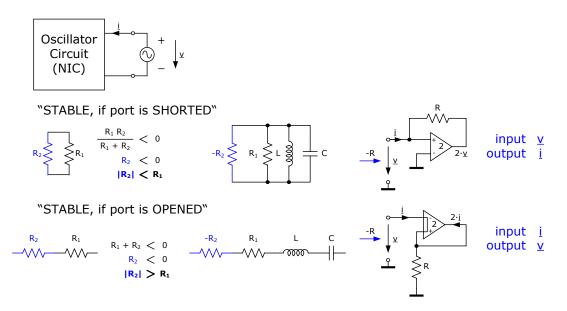

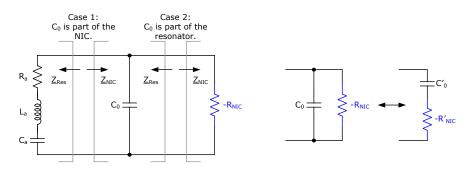

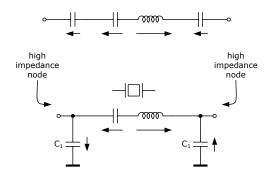

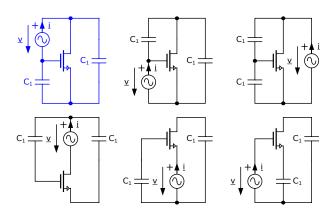

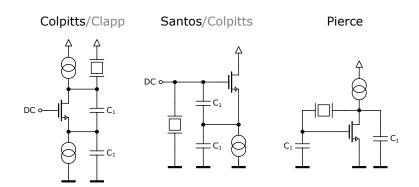

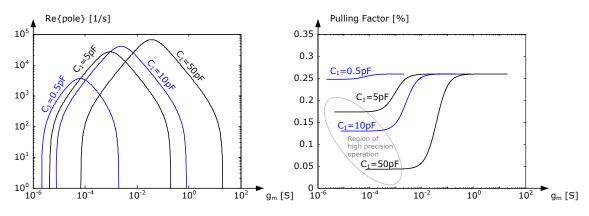

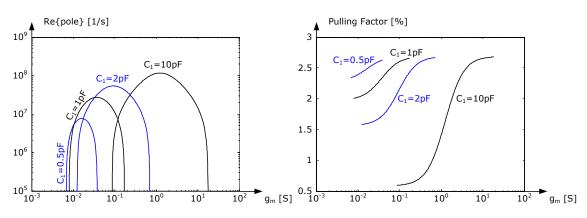

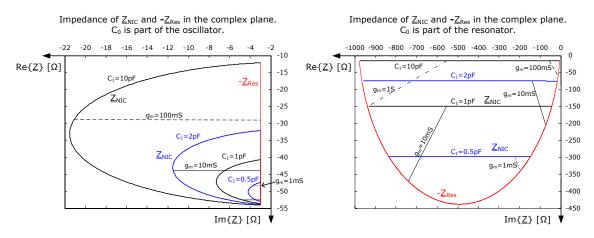

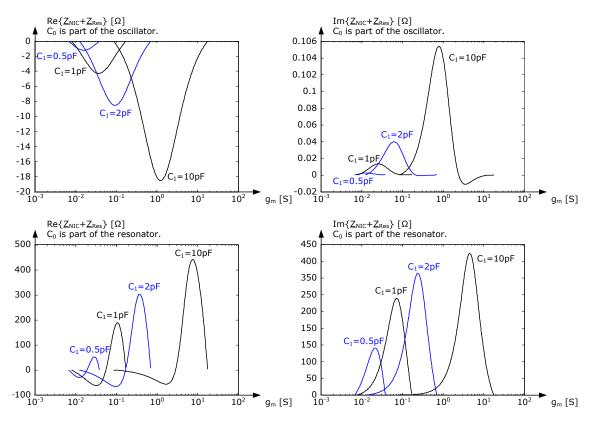

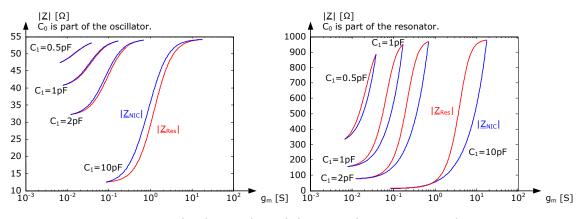

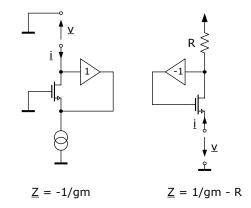

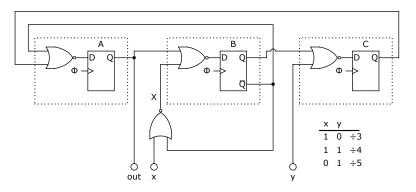

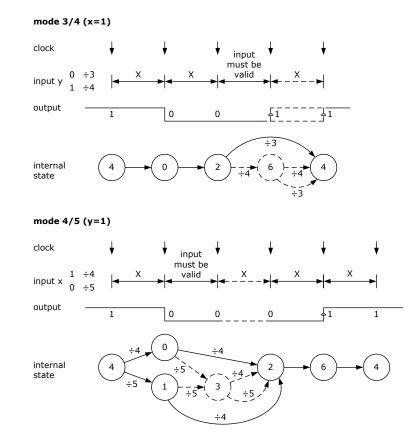

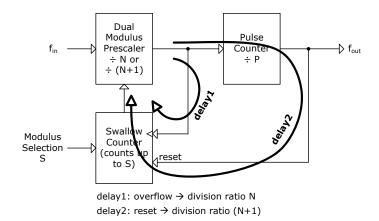

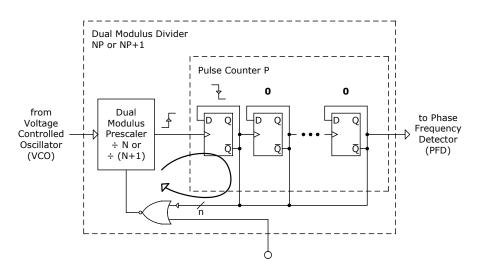

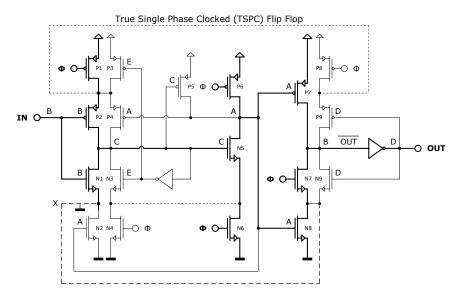

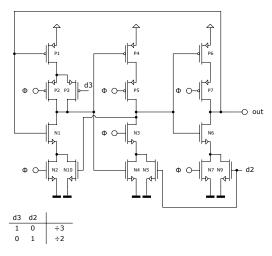

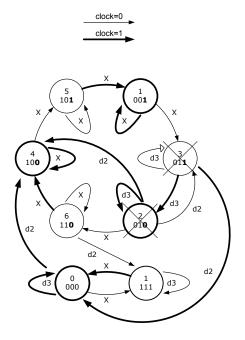

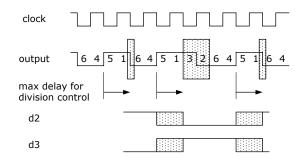

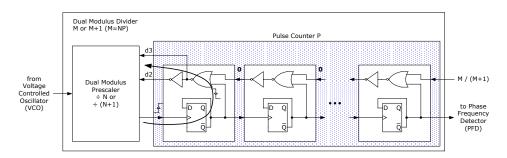

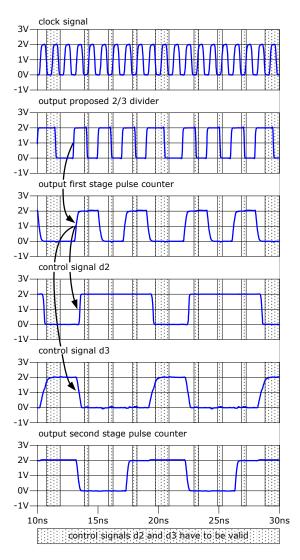

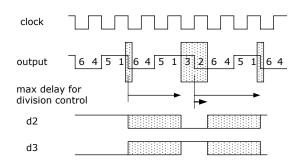

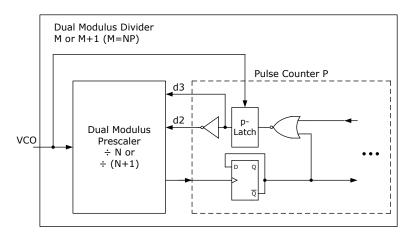

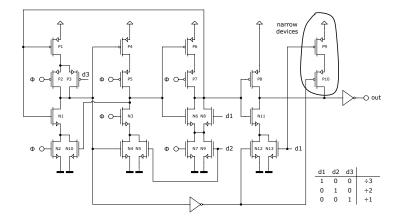

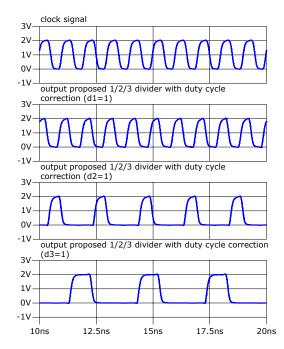

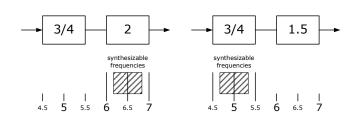

(2.13)