# **GPU Implementation Techniques for Differential Collision Search Attacks**

A case study of SHA-1

Jürgen Windhaber

## GPU Implementation Techniques for Differential Collision Search Attacks

A case study of SHA-1

Master's Thesis at Graz University of Technology

submitted by

#### Jürgen Windhaber

#### juergen.windhaber@gmail.com

Institute for Applied Information Processing and Communications (IAIK), Graz University of Technology Inffeldgasse 16a A-8010 Graz, Austria

16<sup>th</sup> September 2011

© Copyright 2011 by Jürgen Windhaber

Supervisor:Univ.-Prof. Dr. Vincent RijmenAdvisor:Dr. Christian Rechberger

## GPU Implemenationstechniken für differenzielle Kollisionssuchen

Eine Fallstudie an SHA-1

Masterarbeit an der Technischen Universität Graz

vorgelegt von

### Jürgen Windhaber

Institut für Angewandte Informationsverarbeitung und Kommunikationstechnologie (IAIK), Technische Universität Graz Inffeldgasse 16a A-8010 Graz

16. September 2011

© Copyright 2011, Jürgen Windhaber

Diese Arbeit ist in englischer Sprache verfasst.

Begutachter:

Univ.-Prof. Dr. Vincent Rijmen Betreuender Assistent: Dr. Christian Rechberger

### Abstract

Shortcut collision attacks are an important field of operation in IT security. These attacks are that important because they not only show weaknesses in algorithms but in a further consequence they also give insight into how to make them more secure. One characteristic of shortcut collision attacks is that they often need a long time to compute due to their high computational complexity. New generation GPUs are offering an attractive way to reduce the computational time significantly.

This thesis evaluates how suitable GPUs are in general to solve that sort of problems. It also offers a set of techniques that show how to implement these kinds of algorithms efficiently on GPUs. As an illustration of these techniques computational intensive parts of a shortcut collision attack on SHA-1 are implemented as a case study. It shows that although GPUs cannot unfold their full potential on that sort of problems a significant speedup is achieved in comparison to conventional CPU implementations.

#### Kurzfassung

Kollisionsattacken stellen ein wichtiges Einsatzgebiet in der IT Sicherheit dar. Diese Attacken sind bedeutend weil sie einerseits Schwachstellen in Algorithmen aufzeigen und andererseits auch wichtige Erkenntnisse liefern um diese Algorithmen sicherer zu machen. Ein Merkmal von Kollisionsattacken ist, dass sie oftmals aufgrund ihrer hohen Komplexität eine lange Zeit zur Berechnung brauchen. Neue Generationen von GPUs stellen eine sehr attraktive Alternative dar, um die Berechnungsdauer dieser Probleme signifikant zu reduzieren.

Diese Arbeit versucht zu bewerten wie geeignet GPUs im generellen sind, um Probleme dieser Art zu lösen. Es werden verschiedene Techniken vorgestellt, die Lösungswege aufzeigen, um diese Art von Algorithmen effektiv auf GPUs zu berechnen. Um diese Techniken zu illustrieren wurden rechnerisch intensive Teile einer Kollisionsattacke auf SHA-1 als Fallstudie implementiert. Obwohl GPUs bei dieser Art von Problemen nicht ihr volles Potenzial ausspielen können, zeigt die Fallstudie doch deutlich, dass GPU Implementationen gegenüber herkömmlichen CPU Implementationen große Vorteile in Sachen Berechnungsdauer aufweisen.

### **Statutory Declaration**

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

Place

Date

Signature

### Eidesstattliche Erklärung

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommene Stellen als solche kenntlich gemacht habe.

Ort

Datum

Unterschrift

# Contents

| Co | ontent  | ts                                                                              | ii  |

|----|---------|---------------------------------------------------------------------------------|-----|

| Li | st of I | Figures                                                                         | iv  |

| Li | st of ] | Tables                                                                          | v   |

| A  | know    | vledgments                                                                      | vii |

| 1  | Intr    | oduction                                                                        | 1   |

|    | 1.1     | Terms and Acronyms                                                              | 2   |

| 2  | Has     | h Functions                                                                     | 3   |

|    | 2.1     | Requirements of Hash Functions                                                  | 3   |

|    | 2.2     | Iterated Hash Functions                                                         | 4   |

| 3  | Coll    | ision Attacks                                                                   | 11  |

|    | 3.1     | Generic Attacks                                                                 | 11  |

|    | 3.2     | Attacks on the MD4 Family                                                       | 12  |

|    | 3.3     | Cryptanalysis of SHA-0 and SHA-1                                                | 12  |

| 4  | Stre    | am Processors                                                                   | 25  |

|    | 4.1     | Stream Programming Model                                                        | 26  |

|    | 4.2     | Additional Terminology                                                          | 27  |

|    | 4.3     | The Imagine Stream Processor                                                    | 27  |

|    | 4.4     | The Cell Multiprocessor                                                         | 28  |

|    | 4.5     | GPGPU                                                                           | 29  |

| 5  | Cud     | a                                                                               | 35  |

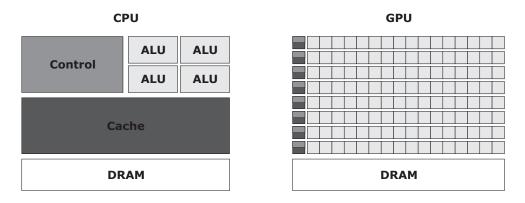

|    | 5.1     | Architectural Differences Between GPU and CPU(Data Caching vs. Data Processing) | 36  |

|    | 5.2     | Device and Host Communication                                                   | 36  |

|    | 5.3     | Architectural Overview of CUDA Capable GPUs                                     | 36  |

|    | 5.4     | CUDA API                                                                        | 40  |

|    | 5.5     | Hardware Limitations                                                            | 42  |

| 6   | Case   | Study                                   | 51 |

|-----|--------|-----------------------------------------|----|

|     | 6.1    | General Considerations                  | 51 |

|     | 6.2    | Technical Specifications and Benchmarks | 52 |

|     | 6.3    | Cost-Performance Ratio                  | 53 |

|     | 6.4    | General Implementation Considerations   | 59 |

|     | 6.5    | Precomputed Values Approach (CPU)       | 61 |

|     | 6.6    | Precomputed Values Approach (GPU)       | 61 |

|     | 6.7    | Parameterized Approach                  | 64 |

|     | 6.8    | Kernel Scheduled Approach               | 66 |

|     | 6.9    | Comparison of the Different Approaches  | 69 |

|     | 6.10   | Concluding Remarks                      | 72 |

| 7   | Outl   | ook                                     | 73 |

|     | 7.1    | Ideas for Future Work                   | 73 |

| 8   | Conc   | cluding Remarks                         | 75 |

| A   | Benc   | hmarks GPU CPU                          | 77 |

|     | A.1    | Synthetic Benchmarks GPU CPU            | 78 |

| Bił | oliogr | aphy                                    | 86 |

# **List of Figures**

| 2.1  | Iterated hash function                     | 4  |

|------|--------------------------------------------|----|

| 2.2  | Davies-Meyer mode                          | 5  |

| 2.3  | Miyaguchi-Preneel mode                     | 5  |

| 2.4  | Matyas-Meyer-Oseas mode                    | 5  |

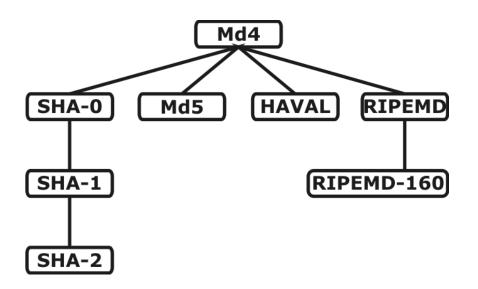

| 2.5  | MD4 family                                 | 6  |

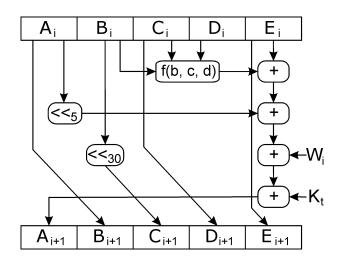

| 2.6  | State update function of SHA-0 and SHA-1   | 7  |

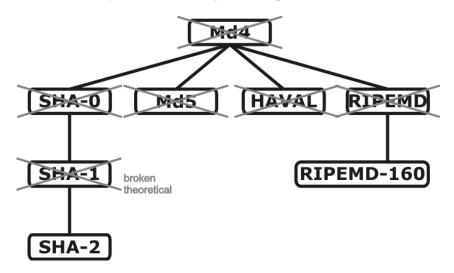

| 3.1  | broken MD4 family members                  | 12 |

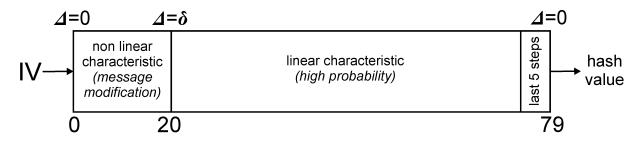

| 3.2  | Nonlinear- and linear part of the Model    | 17 |

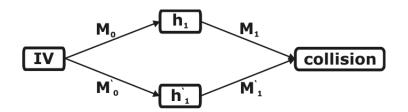

| 3.3  | Two-block collision                        | 19 |

| 3.4  | Structure of the boomerang attack          | 21 |

| 3.5  | Amplified boomerang attack                 | 22 |

| 3.6  | Short pattern                              | 23 |

| 3.7  | Long pattern                               | 23 |

| 4.1  | The stream programming model               | 26 |

| 4.2  | The imagine architecture                   | 27 |

| 4.3  | Cell architecture                          | 29 |

| 4.4  | Classic graphics pipeline                  | 30 |

| 4.5  | Unified pipeline and shader design         | 30 |

| 4.6  | Comparison Gflops                          | 33 |

| 4.7  | Comparison bandwidth                       | 34 |

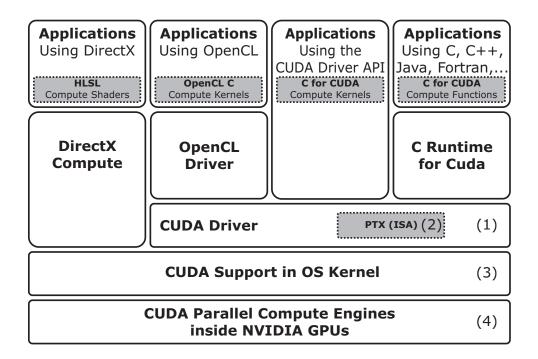

| 5.1  | The CUDA architecture                      | 35 |

| 5.2  | Sample GPU space and CPU space on the die  | 36 |

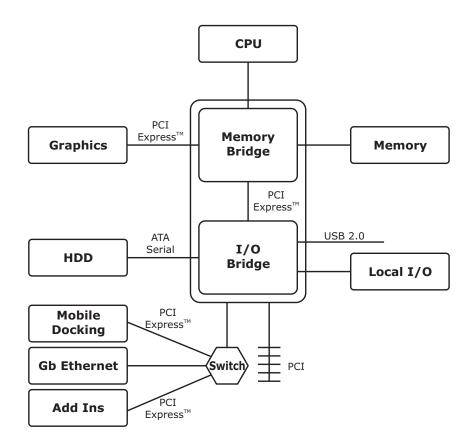

| 5.3  | PCI express architecture                   | 37 |

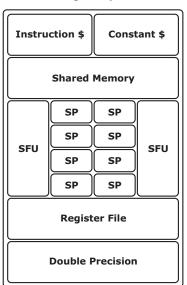

| 5.4  | Streaming multiprocessor G80, G90, GT200   | 38 |

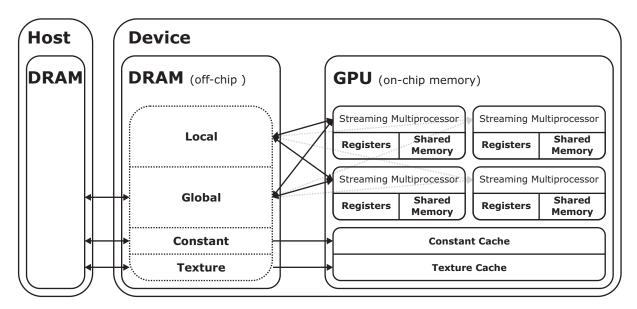

| 5.5  | The various memory spaces on a CUDA device | 38 |

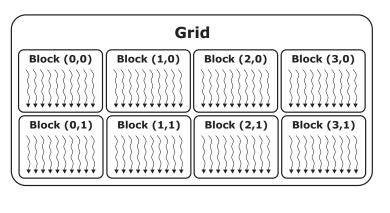

| 5.6  | Thread structure                           | 41 |

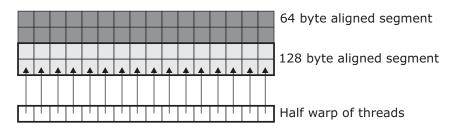

| 5.7  | Coalesced access pattern                   | 47 |

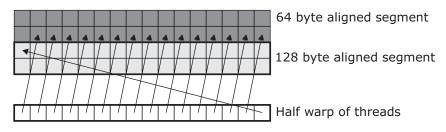

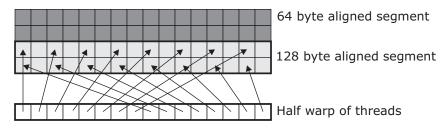

| 5.8  | Misaligned access pattern                  | 48 |

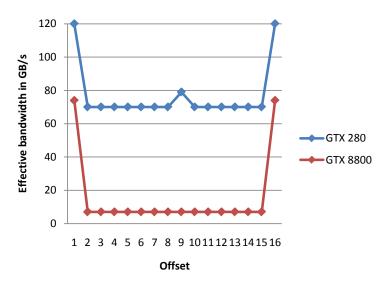

| 5.9  | Offset bandwidth                           | 48 |

| 5.10 | Strode access pattern                      | 49 |

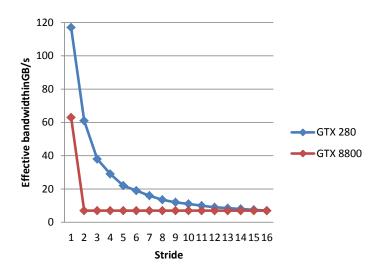

| 5.11 | Strode bandwidth                           | 49 |

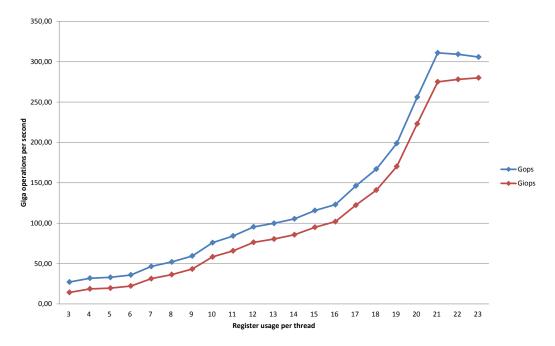

| 6.1  | Runtime behavior (register usage)                       | 60 |

|------|---------------------------------------------------------|----|

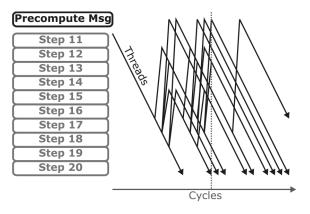

| 6.2  | Precomputed values approach                             | 62 |

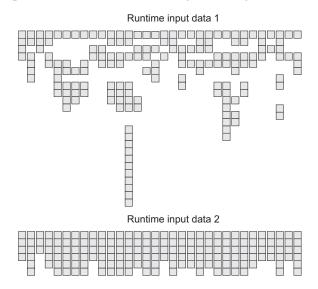

| 6.3  | Runtime behavior (input data)                           | 62 |

| 6.4  | Runtime behavior (data set)                             | 63 |

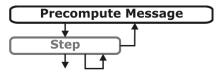

| 6.5  | Parameterized approach                                  | 64 |

| 6.6  | Execution patterns                                      | 65 |

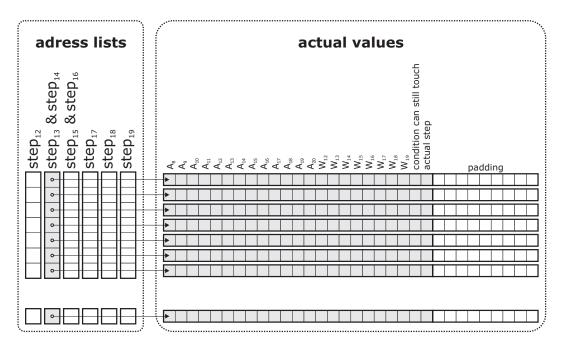

| 6.7  | Kernel scheduled approach                               | 67 |

| 6.8  | Kernel scheduled approach: addresses/memory after start | 67 |

| 6.9  | Kernel scheduled approach: addresses/memory after steps | 68 |

| 6.10 | Benchmark comparison                                    | 71 |

## **List of Tables**

| 1.1 | Terms                                                              | 2  |

|-----|--------------------------------------------------------------------|----|

| 1.2 | symbols                                                            | 2  |

| 2.1 | Different rounds of the state update function                      | 8  |

| 2.2 | Secure hash algorithm properties                                   | 8  |

| 2.3 | Timeline of the SHA-3 hash algorithm competition                   | 9  |

| 3.1 | Algorithms and their complexity                                    | 13 |

| 3.2 | A 6-step local collision in SHA-0 / SHA-1                          | 14 |

| 3.3 | Probabilities of bits changing                                     | 17 |

| 3.4 | Conditions disturbance vector                                      | 18 |

| 4.1 | Ration CPU and GPU                                                 | 31 |

| 5.1 | Attributes of the different memory spaces                          | 39 |

| 6.1 | Technical specifications NVIDIA GeForce GTX 295                    | 52 |

| 6.2 | Synthetic benchmarks NVIDIA GeForce GTX 295                        | 55 |

| 6.3 | Key data about a SHA-1 GPU implementation (registers)              | 57 |

| 6.4 | Key data about different SHA-1 GPU implementations (shared memory) | 58 |

| 6.5 | Key data about different SHA-1 GPU implementations (local memory)  | 59 |

| 6.6 | Memory usage of threads and kernels                                | 70 |

| 6.7 | Execution time ratios between different implementations            | 72 |

| A.1 | Benchmark data NVIDIA GPUs                                         | 77 |

| A.2 | Benchmark data ATI GPUs                                            | 77 |

| A.3 | Benchmark data Intel CPUs                                          | 78 |

## Acknowledgements

Writing this thesis was an endeavor with some stumbling blocks along the way. First, I'd like to thank my parents Erna and Karl for their support throughout my study. I also owe thanks to my girlfriend Jasmina for her support and motivation.

Also a big thank you goes to my advisor Christian Rechberger for his help and patience. I like to thank Vincent Rijmen for agreeing to be my supervisor and giving me the opportunity to write this thesis.

Last but not least I would like to thank all my friends and colleagues for all the interesting discussions about my thesis but also about all the other interesting things we debated.

Jürgen Windhaber September, March 2011

## Chapter 1

## Introduction

Most people in the industrialized parts of the world are living in "information-driven" societies. Information in general influences and affects them in their every-day life, and therefore it stands to reason that this information needs to be protected. Responsible for this protection in general is cryptography, which was already used in ancient times. Although in contrast to today almost only to hide information.

Today cryptography is used for a lot of different applications. One set of tools is called hash algorithms and is responsible for two important applications called message authentication and modification detection. It goes without saying that these mechanisms have to be "secure", and for hash algorithms an important security criterion is collision resistance. [MvOV96] A collision attack on these hash algorithms should be computational infeasible, but recently many of the most used Hash Algorithms such as SHA-1 [oST02] or MD5 [Riv92b] have been broken by a series of attacks. Although in the case of SHA-1 the complexity to find an actual collision is too high, existing collision attacks may lay the foundation for more powerful attacks.

New techniques in collision search attacks are pushing the complexities of these attacks into a direction where a computation of a collision seems possible. For example, the currently best known collision attack on SHA-1 has a complexity somewhere around  $2^{60}$  which is too high to solve on a single standard computer. However it puts it in the range of different other approaches, such as distributed computing<sup>1</sup> or general-purpose computing on graphics processing units or short GPGPU. Collision attacks on cryptographic hash functions are very often expansive in a computational point of view. State of the art CPUs offer a lot of computational power, but the time required to find collisions on modern day hash functions is high anyhow.

An alternative to conventional CPUs for complex and time intensive computations is on the rise for a while now. This alternative is commonly known as GPGPU and uses a GPU or a combination of CPU and GPU to solve problems of general purpose. These GPUs are generally equipped with a high number of processing kernels and are capable to run thousands of threads in parallel. Not long ago the usage of these GPUs was somewhat limited because of the absence of an API which provides developers with tools to conveniently access the GPU. The only way to communicate with GPUs was trough graphical APIs, such as OpenGL [SGI92] or DirectX [Cor09].

In 2006 ATI presented a low level interface called CTM [AMD06] (Close to metal) to access the GPU directly. Competitor NVIDIA was not far behind and introduced CUDA [NVI09a] (Compute Unified Device Architecture) in February 2007, which provides developers with a C like API and is therefore

<sup>&</sup>lt;sup>1</sup>A distributed computing system consists of a certain number of computers which are typically connected through a network.

arguable easier to use than CTM. For the first time these tools made it possible to use the computational power of modern day graphic cards directly to solve problems in a fraction of time compared to state of the art CPUs. Because of their often high complexity, collision attacks are suited very good to implement on GPGPUs.

One big problem though is the non-deterministic program flow in combination with unpredictable memory access patterns which is common in most collision attacks. Up till now and very probably also in the near future all the GPUs have a SIMT (Single Instruction Multiple Thread) architecture. This architecture is not suited to deal with non-deterministic program flows. There are different limitations which more or less all can be traced back to the SIMT architecture of the GPUs. For this purpose certain design strategies were developed to counter these limitations, or at least try to minimize the limiting factors.

A variation of the currently best attack of SHA-1 in view of complexity is used as a case study to show different approaches and to conquer the above mentioned problems. Also, the difference between an "ideal" implementation without any limitations at all and the developed approaches was measured to see what would be possible if GPUs would have a more suitable architecture like MIMD (Multiple Instruction Multiple Data).

## 1.1 Terms and Acronyms

In this thesis the following terms and acronyms are used:

| MDC   | Message detection code                                 |

|-------|--------------------------------------------------------|

| MAC   | Message authentication code                            |

| NIST  | National institute of standards and technology         |

| NSA   | National security agency                               |

| GPGPU | General-purpose computing on graphics processing units |

| SIMD  | Single instruction multiple data                       |

| MIMD  | Multiple instruction multiple data                     |

| SIMT  | Single instruction multiple thread                     |

| Warp  | A group of a number of threads                         |

| SM    | Streaming multiprocessor                               |

| TPC   | Thread processing cluster                              |

#### Table 1.1: Terms

#### 1.1.1 Symbols

In this thesis the following symbols are used:

Table 1.2: symbols

## **Chapter 2**

## **Hash Functions**

Cryptographic hash functions provide an effective way to protect large quantities of information with the help of a short hash value generated by a hash algorithm. A hash function takes an input value of arbitrary length and computes an output value of fixed length, called hash value. [Pre94]

The applications for hash algorithms can be categorized into two main fields of application:

- Message authentication.

- Modification detection.

Message authentication codes (MACs) take as input a message and a secret key. The first application area of a message authentication code is data integrity. Data integrity assures that the data has not been modified by an unauthorized person or process. The second application area is data origin authentication. Data origin authentication is used to authenticate messages. [MvOV96, p. 323]

The second application is called modification detection code (MDC). Modification detection codes are used in many areas. Typical examples would be the creation of digital signatures, or checksums over downloaded files. [MvOV96, p. 323]

### 2.1 Requirements of Hash Functions

Cryptographic hash functions have to fulfill certain properties. It is important to mention that there is a distinction between security requirements and constructive requirements [MvOV96, pp. 323 - 324].

#### 2.1.1 Constructive Requirements

#### • easy to compute

The hash value *y* of a given input value *x* is easy to compute.

#### compression

The hash function computes a hash value *y* from a given input value *x* with an arbitrary length to a fixed length.

### 2.1.2 Security Requirements

#### • preimage resistance

It must be computationally infeasible to find an input value x for a given hash value y, h(x)=y. In other words the hash function must be a one way function.

#### • 2nd preimage resistance

It must be computationally infeasible to find a second input value z for a given input value x that both compute the same hash value, h(z)=h(x).

#### • collision resistance

It must be computationally infeasible to find two arbitrary input values x and z which compute the same hash value, h(z)=h(x).

#### • near collision resistance

It should be hard to find any two input values x and z such that h(x) and h(z) only differ in a small number of bits.

There are also additional requirements in certain cases. For example in the case of the SHA-3 candidates which are discussed in detail in Section 2.2.4. Also requirements like memory consumption, code size and the simplicity of the algorithms structure are taken into account.

## 2.2 Iterated Hash Functions

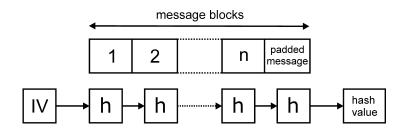

Most cryptographic hash functions are iterated hash functions with a so called Merkle-Damgård [Mer79, pp. 13–15] [Mer90, Dam90] construction which is shown in Figure 2.1. The message is split into several blocks with fixed length. These blocks are computed separately. Each block serves as input to an internal function E.

Figure 2.1: General structure of an iterated hash function as Merkle-Damgård construction

#### 2.2. Iterated Hash Functions

There are different methods to compute the compression function itself. The most prominent methods are:

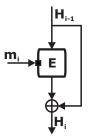

**Davies-Meyer** mode is shown in Figure 2.2 and can be defined as  $H_i = E_{m_i}(H_{i-1}) \oplus H_{i-1}$ . [MvOV96, pp. 340 - 341]

Figure 2.2: Davies-Meyer mode

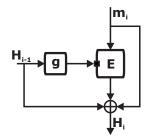

**Miyaguchi-Preneel** mode is shown in Figure 2.3 and can be defined as  $H_i = E_{g(H_{i-1})}(m_i) \oplus H_{i-1} \oplus m_i$ . [MvOV96, pp. 340 - 341]

Figure 2.3: Miyaguchi-Preneel mode

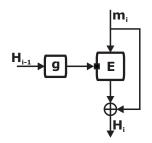

**Matyas-Meyer-Oseas** mode is shown in Figure 2.4 and can be defined as  $H_i = E_{g(H_{i-1})}(m_i) \oplus m_i$ . [MvOV96, pp. 340 - 341]

Figure 2.4: Matyas-Meyer-Oseas mode

On the last block a so called message padding is performed. For example the message padding of SHA-0 and SHA-1 is processed in the following way. The input values have a fixed length of 512-bits. First they are split into 512-bit blocks. At the end of the last message block a "1" followed by "0"s followed by a 64-bit integer is padded. The 64-bit integer value describes the full length of the message. Therefore the length of the input message is limited by  $2^{64}$ . [oST02]

#### 2.2.1 The MD4 Family

Members of the so called MD4 family are by far the most commonly used hash functions today. The MD4 [Riv92a] algorithm was published in the year 1990 by Ronald L. Rivest. MD4 had also a main influence on the development of MD5 [Riv92b], HAVAL [ZPS93], RIPEMD [BDP97] and the SHA family which is described in Sections 2.2.2 and 2.2.3. Figure 2.5 shows the most prominent members of the MD4 Family.

Figure 2.5: Members of the MD4 family

#### 2.2.2 SHA-0 and SHA-1

The SHA family is a group of hash algorithms developed by the National Institute of Standards and Technology (NIST) and the National Security Agency (NSA). SHA-0 [Nat93] was published in the year 1993. Two years later the algorithm was replaced by SHA-1 [oST02]. SHA-0 and SHA-1 are iterated hash algorithms which process blocks of 512-bits and produce a hash value of 160 bit.

The core function of the hash algorithm itself consists of two parts:

- Message expansion

- State update

#### **Message Expansion**

In the message expansion the 512-bit message block is split into 16 32-bit segments  $(M_0, M_1, M_2, ..., M_{15})$  called message words. The function expands these 16 message words  $M_i$  to 80 message words  $W_i$ . The difference between SHA-0 and SHA-1 consists only of the left rotation in the message expansion as shown in Equation 2.2. [oST02]

Figure 2.6: State update function of SHA-0 and SHA-1

For Sha-0:

$$W_{i} = M_{i}, \ \forall i, \ 0 \le i < 16$$

$$W_{i} = W_{i-3} \oplus W_{i-8} \oplus W_{i-14} \oplus W_{i-16}, \ \forall i, \ 16 \le i < 80$$

(2.1)

For Sha-1:

$$W_{i} = M_{i}, \ \forall i, \ 0 \le i < 16$$

$$W_{i} = ROL_{1}(W_{i-3} \oplus W_{i-8} \oplus W_{i-14} \oplus W_{i-16}), \ \forall i, \ 16 \le i < 80$$

(2.2)

#### **State Update Function**

After the message expansion the expanded message W is used to update the so called chaining variables  $(A_i, B_i, C_i, D_i, E_i)$  in 80 steps (i = 0, 1, ..., 79).

$$A^{(i+1)} = ADD(W^{(i)}, ROL_5(A^{(i)}, f^{(t)}(B^{(i)}, C^{(i)}, D^{(i)}), E^{(i)}, K^{(t)})$$

$$B^{(i+1)} = A^{(i)}$$

$$C^{(i+1)} = ROL_{30}(B^{(i)})$$

$$D^{(i+1)} = C^{(i)}$$

$$E^{(i+1)} = D^{(i)}$$

(2.3)

The state update function has 80 steps and four different rounds which are shown in Table 2.1. Figure 2.6 shows how the chaining variables  $(A_i, B_i, C_i, D_i, E_i)$  are updated at each step. The constant variables  $K^{(t)}$  are added in every step and they are different for each round. The initial value IV  $(A_i, B_i, C_i, D_i, E_i)$  is also a set of constants. After the four rounds chaining variables are added to the initialized value feed-forward. This process reiterates as long as all 512-bit blocks are computed. The final value is than called hash value or message digest. [oST02]

| STEPS | ROUND | BOOLEAN | f(B,C,D)                                        |

|-------|-------|---------|-------------------------------------------------|

| 1-20  | 1     | IF      | $(B \land C) \lor (\neg B \land D)$             |

| 21-40 | 2     | XOR     | $B\oplus C\oplus D$                             |

| 41-60 | 3     | MAJ     | $(B \land C) \lor (B \land D) \lor (C \land D)$ |

| 61-80 | 4     | XOR     | $B\oplus C\oplus D$                             |

Table 2.1: The different rounds of the state update function

#### 2.2.3 SHA-2

SHA-2 [oST02] was introduced in the year 2002 and consists of SHA-256, SHA-384, SHA-512. These three algorithms have longer hash values as their predecessors. Also some implementation details are different to the SHA-0 and SHA-1 algorithms but the underlying design principles are similar. In Table 2.2, the maximum message size, the block size, the word size and the message digest size for all members of the SHA family are shown.

**Table 2.2:** Secure hash algorithm properties [oST02]

| ALGORITHM | MESSAGE SIZE | BLOCK SIZE | WORD SIZE | MESSAGE DIGEST SIZE |

|-----------|--------------|------------|-----------|---------------------|

| SHA-0     | $< 2^{64}$   | 512        | 32        | 160                 |

| SHA-1     | $< 2^{64}$   | 512        | 32        | 160                 |

| SHA-256   | $< 2^{64}$   | 512        | 32        | 256                 |

| SHA-384   | $< 2^{128}$  | 1024       | 64        | 384                 |

| SHA-512   | $< 2^{128}$  | 1024       | 64        | 512                 |

#### 2.2.4 SHA-3

In 2007 NIST issued a international competition, similar to the AES competition [FIP01, NBB<sup>+</sup>] in 1998, to develop a new secure hash standard until 2012 called SHA-3. The need for a new secure hash standard resulted from the fact that recently big advances in cryptanalysis of hash algorithms were made [Nat09b]. Chapter 3 will show different attacks on SHA-1 which created the need for a new secure hash standard. Sixty-four different algorithms were submitted to NIST in October 2008. 51 algorithms out of the 64 met the minimum acceptance criteria to be accepted as first round candidates. In comparison to the AES competition with 21 submissions [RD99] this is a huge advancement, at least in view of quantity.

For round two, NIST announced 14 candidates:

- BLAKE [AHMP08]

- Blue Midnight Wish [GKK<sup>+</sup>08]

- CubeHash [Ber08]

- ECHO [BBG+08]

- Fugue [HHJ08]

- Grøstl [GKM<sup>+</sup>08]

- Hamsi [zK08]

- JH [Wu08]

- Keccak [BDPA08]

- Luffa [CSW08]

- Shabal [BCCM<sup>+</sup>08]

- SHAvite-3 [BD08]

- SIMD [LBF08]

- Skein [FLS<sup>+</sup>08].

NIST announced 5 candidates for round three:

- BLAKE [AHMP08]

- Grøstl [GKM<sup>+</sup>08]

- JH [Wu08]

- Keccak [BDPA08]

- Skein [FLS<sup>+</sup>08].

The email announcement states that none of the second round candidates were clearly broken. One criterion is also the performance of the algorithms. Also an important criterion is that all the finalists display a clear round structure. [oST10]

Table 2.3 shows important milestones for the hash algorithm competition:

**Table 2.3:** Milestones of the preliminary timeline for the SHA-3 hash algorithm competition [oST02]

| YEAR, QUARTER | DESCRIPTION                                    |

|---------------|------------------------------------------------|

| 2008 4Q       | Submission deadline for new hash functions     |

| 2009 2Q       | Announcing first round candidates              |

| 2010 3Q       | Announcing the finalists                       |

| 2012 2Q       | Address public comments, and select the winner |

A detailed classification of all candidates can be found in [FFG09].

## **Chapter 3**

## **Collision Attacks**

### 3.1 Generic Attacks

Generic attacks are not dependent on design principles of the attacked algorithms. These attacks work at the basis of mathematical rules and can be applied to all algorithms and functions [MvOV96, p. 369]. In the following two sections two generic attacks are described in detail.

#### 3.1.1 Brute Force

Brute Force is a way to break an algorithm by initializing an exhaustive search. For a successful collision attack on SHA-0 the complexity is  $2^{160}$  because only  $2^{160}$  different hash values exist. Because of the requirements of hash functions described in Section 2.1 it must be computationally infeasible to accomplish such an exhaustive search.

#### 3.1.2 Birthday Attack

The birthday paradox has its name from the observation that if there are 23 people in a room then there is a probability of more than 50% that at least two of them have the same birthday. The mathematical principal behind the birthday paradox can be used to create a collision attack called birthday attack. For the birthday attack only the output length of the hash value is of importance, so it can be applied to every hash function in the same manner regardless of the hash functions internal structure.

One of the first applications of the birthday attack, and probably the most well-known, was published by Yuval[Yuv79]. The main observation is that if one is randomly drawing members from a set with nelements the probability is very high that the same element will be picked twice after  $O(\sqrt{n})$  attempts.

This means, that for collision attacks on hash algorithms with a message digest size of n a collision can be found with a complexity of  $2^{n/2}$ . For example in the case of SHA-0 and SHA-1 this results in a complexity of  $2^{80}$ . [MvOV96, p. 369]

Algorithm for the birthday attack:

- Pick a message x (preferable a meaningful message)

- compute y = h(x) and safe y in an array

- alter x to x' and compute y' = h(x')

- compare y' with all elements in the array

- if no match is found put y' into the array and compute new y'

## 3.2 Attacks on the MD4 Family

Another view on the MD4 family tree shown in Figure 3.1 depicts that most members are already broken.

Figure 3.1: Members of the MD4 family which are broken are marked with an X

- MD4 broken in 1996 [Dob96]

- MD5 broken in 2004 [WFLY04]

- HAVAL-128 broken in 2004 [WFLY04]

- RIPEMD broken in 2004 [WFLY04]

- SHA-0 broken in 2004 [BCJ+05] (Paper published 2005)

- SHA-1 theoretically broken in 2005 [WYY05b]

## 3.3 Cryptanalysis of SHA-0 and SHA-1

Collision attacks on the SHA family have a long history. SHA-0 and SHA-1 are probably the most attacked and assessed hash algorithms at all. Due to the fact that SHA-0 has a simpler structure in the message expansion compared to SHA-1, SHA-0 was the first choice of cryptographers to attack. The first theoretically successful attack on SHA-0 was published 1998, five years after its introduction, and is described in Section 3.3.1. In 2004 the first near collisions in SHA-0 were found which are described in Section 3.3.2. After extending previous attacks described in Section 3.3.3, the big breakthrough was in 2005 when the first collision on SHA-0 was found and also SHA-1 was theoretically broken. Section 3.3.4 describes the attack on SHA-0, and Section 3.3.5 describes the attack on SHA-1. The last and most promising attack in view of finding a real collision in SHA-1 is described in Section 3.3.7 and is also the subject of the case study discussed in Section 6.

#### 3.3.1 Differential Collisions in SHA-0 (Chabaud Joux)

Chabaud and Joux presented the first collision attack on SHA-0 [CJ98]. Three algorithms were established called SHI1, SHI2 and SHI3. Each one of these three algorithms has marked similarities to SHA-0 but each of these three algorithms simplifies several implementation details. From that it follows that each one of these three algorithms has another run-time leading to a collision as shown in Table 3.1.

| NAME  | COLLISION COMPLEXITY | DESCRIPTION                                            |

|-------|----------------------|--------------------------------------------------------|

| SHI1  | 128                  | ADD function is replaced by XOR, $f_{(if)}$            |

|       |                      | and $f_{(maj)}$ are replaced by $f_{(xor)}$            |

| SHI2  | $2^{20}$             | ADD function is replaced by XOR                        |

| SHI3  | $2^{44}$             | $f_{(if)}$ and $f_{(maj)}$ are replaced by $f_{(xor)}$ |

| SHA-0 | $2^{61}$             |                                                        |

Table 3.1: Algorithms and their complexity

To fully understand the attack of Chabaud and Joux some terms have to be defined first:

#### local collisions

A local collision is a collision consisting of six steps. It is a fact that SHA-0 has local collisions that can be started at any step. These local collisions are responsible for creating full collisions of the algorithm.

#### • differential path

A differential path describes the differences between two variables. The differential path is used in the attack to describe local collisions. For a full 80-step collision the differential path describes several local collisions that lead to a full collision. It is possible that these paths which describe the local collisions have overlaps in some cases. Table 3.2 shows a differential path for 6 steps that leads to a local collision.

#### disturbance vector

A disturbance vector is a vector where the bits are set if a local collision is starting at that point. For the case of SHA-0 it is sufficient to use an 80 bit vector to mark the starting points of the local collisions. Another observation is that the first 16 variables determine the remaining 64. From that it follows that there are only 16 bit to choose freely which leads to  $2^{16}$  different disturbance vectors in total. The complexity of the collision search is dependent on the Hamming weight<sup>1</sup> of the disturbance vector.

<sup>&</sup>lt;sup>1</sup>The Hamming weight describes the number of bits which are set.

|     | $\Delta M$ | $\Delta A$ | $\Delta B$ | $\Delta C$ | $\Delta D$ | $\Delta E$ |

|-----|------------|------------|------------|------------|------------|------------|

| i   | $2^j$      | $2^j$      | 0          | 0          | 0          | 0          |

| i+1 | $2^{j+5}$  | 0          | $2^j$      | 0          | 0          | 0          |

| i+2 | $2^j$      | 0          | 0          | $2^{j+30}$ | 0          | 0          |

| i+3 | $2^{j+30}$ | 0          | 0          | 0          | $2^{j+30}$ | 0          |

| i+4 | $2^{j+30}$ | 0          | 0          | 0          | 0          | $2^{j+30}$ |

| i+5 | $2^{j+30}$ | 0          | 0          | 0          | 0          | 0          |

Table 3.2: A 6-step local collision in SHA-0 / SHA-1 [CJ98]

#### **Basic Attack Strategy**

Chabaud and Joux defined three algorithms. Each of them similar to SHA-0, but several nonlinear parts were replaced with linear parts. Therefore it is easier to produce collisions in these algorithms than in the real SHA-0. In the final collision attack Chabaud and Joux attempt that the defined algorithms "play together" which is shown in Section 3.3.1.

#### SHI1

Here Chabaud and Joux took the compression function from SHA-0 with two changes. First the ADD function is replaced by XOR. Second the  $f_{(if)}$  and the  $f_{(maj)}$  functions are replaced by the  $f_{(xor)}$  function.

$$A^{(i+1)} = XOR(W^{(i)}, ROL_5(A^{(i)}, f^{(t)}(B^{(i)}, C^{(i)}, D^{(i)}), E^{(i)}, K^{(i)}))$$

In the compression function only the ADD function, the  $f_{(if)}$  and the  $f_{(maj)}$  functions are not linear. With these changes the whole compression function is a linear function. At this time they lose sight of the fact that the vector W is computed by the message expansion. Only with this premises it is possible to assume that it is allowed to change every bit on W. The fact that everything in this model is linear makes it possible to get a differential path which leads very easy to a full collision. Now a disturbance vector of 80 entries is build. Every "1" in the vector signifies that on this position  $W_j^{(i)}$  is negated. This works only for the first 75 steps because it is not possible to correct disturbances after step 80. In the case that the five zeros at the end on the error vector must hold, there are only 128 possible inputs left.

#### SHI2

Compared to SHI1,  $f_{(if)}$  and  $f_{(maj)}$  remain unaffected. Only the ADD function is changed like in SHI1. It can be shown that in some cases  $f_{(if)}$  and  $f_{(maj)}$  compute the same outputs as the  $f_{(xor)}$  function which is used in SHI1. The goal is to change the inputs so that  $f_{(if)}$  and  $f_{(maj)}$  act as the  $f_{(xor)}$  from SHI1, in other words the functions  $f_{(if)}$  and  $f_{(maj)}$  behave like  $f_{(xor)}$ . These changes raise the complexity because  $f_{(if)}$  and  $f_{(maj)}$  behave like a  $f_{(xor)}$  with a certain probability. With all these new conditions it is possible to find a full collision on SHI2 with a complexity of about  $2^{20}$ .

#### SHI3

Once again the compression function from SHA-0 is taken.  $f_{(if)}$  and  $f_{(maj)}$  are replaced by  $f_{(xor)}$ . The ADD function stays unchanged. The problem here is that a carry effect can appear in the disturbances.

The goal is to prohibit this carry effect. A helpful observation is that no carry can appear at bit position 31. Another observation is that if a bit flips from 0 to 1 it must be corrected with a flip from 1 to 0 (a bit-flip from 1 to 0 acts equal). With these changes it is possible to find a full collision on SHI3 with a complexity of  $2^{44}$ .

#### SHA-0

Here the procedure to prevent a carry in the SHI3 function and the procedure to simulate the ADD function in SHI2 must play together. With these changes it is possible to find a full collision on SHA-0 with a complexity of  $2^{61}$ . The achieved complexity of  $2^{61}$  is better than the results achieved by a birthday attack, which is described in Section 3.1.2.

#### 3.3.2 The First Near Collisions of SHA-0

Eli Biham and Rafi Chen published a collision attack [BC04] on SHA-0 which is based on the fact that many bits of a given message are so called neutral bits. The attack is based on the attack of Chabaud and Joux [CJ98] which is described in Section 3.3.1. Biham and Chen present a 65-round collision with a complexity of  $2^{29}$  and a near collision of the full 80-round function where only 18 bits differ with a complexity of  $2^{40}$ . Furthermore, they present an attack on an 82-round SHA-0 which has a complexity of  $2^{43}$  and a full 80-round attack with a complexity of  $2^{56}$ .

#### **Definition of Neutral Bits**

To explain the work of Biham and Chen the following definitions are needed:

•  $\delta_r$

$\delta$  describes the expected differences in the chaining variable A in each round based on the difference of M and M' which is called  $\Delta$ . A pair of messages confirms to  $\delta_r$  if  $A_i \oplus A'_i = \delta_i$  for every  $i \in \{1, ..., r\}$ .

neutral bit

The bit on position  $i \in \{0, ..., 511\}$  is a neutral bit in relation to M and M' if it conforms to  $\delta_r$  before and after flipping the bit in M and M' on position i.

#### • pair of neutral bits

The pair of bits *i* and *j* are a neutral pair of bits in relation to *M* and *M'* if they conform to  $\delta_r$  before and after flipping any subset of the bits in *M* and *M'*.

• set of neutral bits

The set of bits  $S \subseteq \{0, ..., 511\}$  is a neutral set of bits in relation to M and M' if all pairs of messages conform to  $\delta_r$  before and after flipping any subset of the bits in M and M'.

• set of 2-neutral bits

The set of bits  $S \subseteq \{0, ..., 511\}$  is a 2-neutral set of bits in relation to M and M' if every bit in S is neutral and every pair of bits in S is neutral.

#### **Basic Attack Strategy**

Biham and Chen used the fact that many bits in the message are neutral bits. Some techniques were developed to find a big set of neutral bits to find a collision.

#### Finding 2-neutral Sets of Bits of M and M'

First the neutral bits in the message pair M and M' must be found. For this purpose on every bit position  $i \in \{0, ...511\}$  the condition of the neutral bit must be tested. The 2-neutral set of bits is then the maximal subset of bits that the following condition fulfills. The subset is built up at all neutral bits which in combination with all other neutral bits conforms to  $\delta_r$ . Biham and Chen observed that about 1/8 of the found pairs confirm to  $\delta_r$ . In the concrete case a near collision of a full SHA-0 needs  $2^{43}$  pairs  $(2^{43} * 2^{-3} = 2^{40})$  because the expected complexity of a near collision is about  $2^{40}$ .

#### Finding better 2-neutral Sets of Bits of M and M'

In order to find a message pair with a larger 2-neutral set of bits which conforms to  $\delta_r$  the given message pair is modified. The given message pair is modified in a way that the probability that the new message pair still fulfills the condition of  $\delta_r$  is maximized. If a new message is found that confirms to  $\delta_r$  and has a larger set of 2-neutral bits as the previous message the previous message is replaced by the generated message.

#### **Collision Search**

The first work that must be done is to increase the rounds that confirm to  $\delta_r$ . To achieve that, the given pair must be modified with the methods in the previous section. When a big enough 2-neutral bit set is found it is possible to find a near collision of the full SHA-0 with a complexity of  $2^{40}$  where only 18 bits differ. Furthermore a full collision on an 82 step SHA-0 can be found with a complexity of  $2^{43}$ .

### 3.3.3 Update on SHA-1 (Rijmen Oswald)

This paper published by Rijmen and Oswald [RO05] extends the approach from Chabaud and Joux [CJ98] which is presented in Section 3.3.1. Chabaud and Joux exploit the weaknesses of the message expansion function in SHA-0. In SHA-1 this weakness no longer exists. For this reason it was necessary to find a better searching algorithm. Rijmen and Oswald use algorithms and methods of the coding theory to improve their attack. Furthermore they also analyzed other linear approximations for  $f_{(if)}$  and  $f_{(maj)}$ .

#### **Basic Attack Strategy**

The problem is to find input values where the linear model and the original hash algorithm have an equal behavior. In other words the differences in the linear model correspond to the differences in the real SHA-1 model. The Hamming weight should be as small as possible because there is a relation between the complexity and the Hamming weight. In other words as lower the Hamming weight is as lower is the complexity to find a collision. From this it follows that a codeword with a low Hamming weight must be found.

#### Finding a Better Linear Approximation

The replacement of  $f_{(if)}$  and  $f_{(maj)}$  by  $f_{(xor)}$  is not optimal. On this account a better linear approximation must be found. The main advantage of the replacement by  $f_{(xor)}$  is that all 80 steps are equal. The disadvantages are that in certain cases the probability that an output bit flips, in the approximation and in the real case, especially in  $f_{(if)}$  is opposite and unlike other linear functions.  $f_{(xor)}$  for example has a height diffusion rate. Other linear approximations of  $f_{(if)}$  and  $f_{(maj)}$  that deliver better probabilities are shown in Table 3.3.

|     | OUTPUT FLIP PROBABILITY |                          |                  |   |   |              |              |             |                     |

|-----|-------------------------|--------------------------|------------------|---|---|--------------|--------------|-------------|---------------------|

| δ   | $f_{(if)}$              | $f_{(maj)}$              | linear functions |   |   |              |              |             |                     |

|     | $xy \oplus \bar{x}z$    | $xy \oplus xz \oplus yz$ | Х                | у | Z | $x \oplus y$ | $x \oplus z$ | $y\oplus z$ | $x\oplus y\oplus z$ |

| 000 | 0                       | 0                        | 0                | 0 | 0 | 0            | 0            | 0           | 0                   |

| 001 | 1/2                     | 1/2                      | 0                | 0 | 1 | 0            | 1            | 1           | 1                   |

| 010 | 1/2                     | 1/2                      | 0                | 1 | 1 | 1            | 0            | 1           | 1                   |

| 011 | 1                       | 1/2                      | 0                | 1 | 1 | 1            | 1            | 0           | 0                   |

| 100 | 1/2                     | 1/2                      | 1                | 0 | 0 | 1            | 1            | 0           | 1                   |

| 101 | 1/2                     | 1/2                      | 1                | 0 | 1 | 1            | 0            | 1           | 1                   |

| 110 | 1/2                     | 1/2                      | 1                | 1 | 0 | 0            | 1            | 1           | 0                   |

| 111 | 1/2                     | 1                        | 1                | 1 | 1 | 0            | 0            | 0           | 1                   |

**Table 3.3:** The probability that the output bit changes its value when the input bits are changed according to the input difference, for MAJ and IF and for all linear approximations [RO05]

#### **Finding Codewords**

For SHA-0 it is easier to find codewords with low Hamming weight as for SHA-1. For SHA-0 the search space can be limited so that it is possible to find the best codeword with a complexity of  $2^{16}$ . In the case of SHA-1 the complexity to find the best codeword is too high for computation. On this account Rijmen and Oswald use a 53-step version of SHA-1 that delivers better results than the Birthday Attack.

## 3.3.4 Efficient Collision Search Attack on SHA-0 (Wang et al.)

In this paper Wang *et al.* describe a new technique to find full collisions on SHA-0 [WYY05c] with a complexity of  $2^{39}$ . Equal techniques can be used to find near collisions on SHA-0 with a complexity of  $2^{33}$ . Also for the collision attack of SHA-1 [WYY05b] with a complexity of  $2^{69}$  these techniques can be used.

#### **Basic Attack Strategy**

Wang *et al.* introduce a nonlinear model for the first 20 steps. To achieve that, they use message modification techniques that are described later. The other 60 steps have a linear characteristic with a high probability shown in Figure 3.2. For the fact that the first 20 steps are not linear Wang *et al.* are able to disregard several conditions from the disturbance vector which is shown in Table 3.4.

Figure 3.2: Shows the nonlinear- and the linear part of the model

|   | CONDITION                                     | PURPOSE                          |

|---|-----------------------------------------------|----------------------------------|

| 1 | bit in disturbance vector $= 0$ in position:  | to produce the full collision in |

|   | 75,76,77,78,79                                | the last step                    |

| 2 | bit in disturbance vector = 0 in position: -  | to avoid truncated local colli-  |

|   | 5,-4,-3,-2,-1                                 | sions in first few steps         |

| 3 | no consecutive "1"s in the first 17 positions | to avoid an impossible collision |

|   |                                               | path due to a property of IF     |

Table 3.4: The three conditions on the disturbance vector [Wan97]

#### **Disturbance Vector**

In the attack that Chabaud and Joux [CJ98] published in the year 1998, three conditions on the disturbance vector were given (see Table 3.4). The new attack only requires that condition 1 must hold (This condition must hold because it is not possible to correct differences after step 80). In that fact Wang *et al.* were able to find disturbance vectors with lower Hamming weight. This has a positive effect on the search complexity. There are two additional conditions on M depending on the disturbance vector:

$$M_{i+1,7} = \neg M_{i,2}$$

$$M_{i+2,2} = \neg M_{i,2} \text{ (only for round 3)}$$

All messages with an index higher than 15 are generated from the lower ones. Therefore the conditions can be recalculated to the first 16 message words. Hence, these conditions can be easily fulfilled.

#### **Message Modifaction Techinques**

Message modification techniques are used to correct the message words to that effect that the conditions on the message words are fulfilled. First it is necessary to find a differential path that leads to a collision. Second it is necessary to find conditions that this differential path is valid. Third the message modification itself, described below, to fulfill all conditions in the first 20 steps.

#### • Basic message modification techniques

Basic message modification techniques can be deployed for the first 16-steps because it is possible to change the first 16 message words directly by changing A on the current position i. There are several ways to satisfy a condition on the message words. First if it is allowed, the bit can be flipped directly. The second alternative is to flip the bit that stands on the position i - 1 and hope that a carry appears. The third option is to flip the bit on position i - 5 on the previous A.

Advanced message modification techniques

For the steps higher than 16 it is not possible to flip the bit directly because the message words are computed from the first 16 message words  $(M_0, M_1, ..., M_{15})$ . Wang *et al.* correct the conditions by correcting  $A_{16}$ . For example the condition on  $A_{18,32}$  is not fulfilled, they satisfy the condition by applying basic message modification techniques on  $A_{16,22}$ .

#### **Complexity Analysis**

Because the advanced message modification works up to step 20 and disturbance vectors were found with a lower Hamming weight the complexity to find a full collision on SHA-0 can be reduced to  $2^{39}$ . The lowest search complexity for a full collision on SHA-0 at this time was  $2^{56}$  which was found from

Figure 3.3: a two-block collision

Biham *et al.* [BCJ<sup>+</sup>05]. The fact that the complexity to find a full collision on SHA-0 is  $2^{39}$  makes it possible that a collision can be found on a standard computer in a few days.

#### 3.3.5 Finding Collisions in the Full SHA-1

The basic strategy behind the attack is pretty similar to the attack on SHA-0 described in Section 3.3.4. Because of that fact only the differences are covered in this section.

#### **Disturbance Vector**

As mentioned before in the case of SHA-0 an 80-bit vector is used as disturbance vector. For SHA-1 this 80-bit vector is not sufficient anymore. Because of the rotation in the message expansion 16 32-bit variables are needed instead of 16 1-bit variables to describe the whole search space. This results in a search space as large as  $2^{512}$ . To search the entire space would not be an easy task. Therefore, Wang*et al.* use heuristics to reduce the search space and search only in areas that likely contain vectors with low hamming weight. The remaining space is at about  $2^{38}$ , which is a huge improvement compared to  $2^{512}$ . In order to create an attack which is more efficient than the birthday attack, the hamming weight of the disturbance vector has to be less than 27. This is only possible if the conditions shown in Table 3.4 are removed.

#### **Collision Search**

The fact that the conditions in Table 3.4 are not valid anymore for the given disturbance vectors, complicates the construction of a valid differential path, so two near collisions are used to form a collision. These two-block collisions are constructed in the sense, that the differences erase each other. Figure 3.3 illustrates the assembly of such a multi-block or in this case a two-block collision.  $M_0$  and  $M'_0$  produce  $h_1$  and  $\delta h_1 = h'_1 - h_1$

#### Message Modifaction Techinques

The same message modification techniques are used as described in Section 3.3.4 with the exception that advanced message modification can be applied up to step 22. Later Wang *et al.* claimed [WYY05a] (results unpublished) to apply message modification up to step 25 using another differential path and additional message modification techniques.

#### **Complexity Analysis**

These techniques led to the first attack which has a lower complexity than the birthday attack. With the help of message modification techniques and early stopping it is possible to find near collisions with a complexity of  $2^{68}$ . The near collision on the second message block can be derived with the same complexity as the first near collision. Because of that fact the complexity of the full collision is just

increasing by a factor of two. From that it follows that the overall complexity to produce a full collision is  $2^{69}$ . According to unpublished results [WYY05a] Wang *et al.* were able to decrease the complexity to about  $2^{63}$ .

#### 3.3.6 The Amplified Boomerang Attack

The presented attack [JP07] is an adapted version of the amplified boomerang attack on block ciphers [KKS00], which is again based on the boomerang attack proposed by Wagner [Wag99].

#### **The Boomerang Attack**

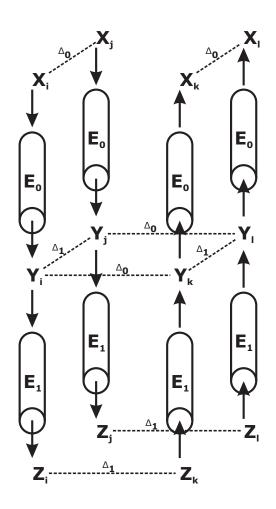

To completely understand the amplified version of the boomerang attack the original boomerang attack [Wag99] itself has to be explained first. Basically the boomerang attack is a differential attack which uses a structure of four plaintexts and certain differentials that are applied to the plaintexts and the internal states of the decryption/encryption phase of these given plain-texts. Figure 3.4 shows the structure of the attack which is explained as follows:

- 1. Choose an input pair  $X_i, X_j$  where  $X_j = X_i \oplus \Delta_0$

- 2. Encrypt the pair and half way through using  $E_0$  and get  $Y_i$  and  $Y_j$  with the relation  $Y_j = Y_i \oplus \Delta_1$

- 3. Encrypt  $Y_i$  and  $Y_j$  using  $E_1$  which results in  $Z_i$  and  $Z_j$

- 4. Generate  $Z_k$  and  $Z_l$  through  $Z_k = Z_i \oplus \Delta_1$  and  $Z_l = Z_j \oplus \Delta_1$

- 5. Decrypt  $Z_k$  and  $Z_l$  using  $E_1$  which results in  $Y_k$  and  $Y_l$  which results into the relations  $Y_k = Y_i \oplus \Delta_0$  and  $Y_l = Y_j \oplus \Delta_0$

- 6. Compute relation between  $Y_k$  and  $Y_l$ :  $Y_j = Y_i \oplus \Delta_1, Y_k = Y_i \oplus \Delta_0, Y_l = Y_j \oplus \Delta_0$   $Y_k = Y_i \oplus \Delta_0$   $Y_k = Y_j \oplus \Delta_1 \oplus \Delta_0$   $Y_k = Y_l \oplus \Delta_0 \oplus \Delta_1 \oplus \Delta_0$  $Y_k = Y_l \oplus \Delta_1$

$Y_k = Y_l \oplus \Delta_1$  determines the relation  $X_k = X_l \oplus \Delta_0$ . Because of this relations it is possible to distinguish *E* from random permutations.

#### Adapting the Boomerang Attack to Attack Hash Functions

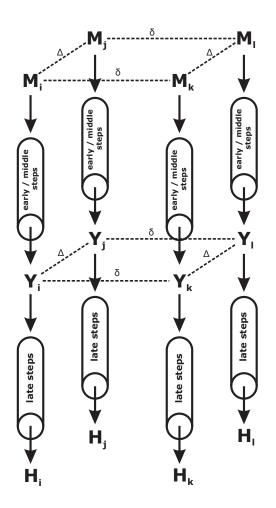

Because of the fact that there is no decryption in hash functions the boomerang attack can't be applied directly. The so called amplified boomerang attack [KKS00] however can be applied to attack hash functions with certain adaptations. The adaptations and the subsequent attack are described in [JP07]. The basic idea is to apply so called auxiliary differential paths, which work good for a certain number of steps, to a main differential path to reduce the overall work factor. The principals of the boomerang attack are now used to attach the auxiliary differential paths to the main differential path. Figure 3.5 shows the structure of the adapted version of the attack.

Figure 3.4: Structure of the boomerang attack

Like in the original attack a plaintext pair is chosen with a differential  $\Delta$  which is the main differential path. In addition to the main differential path an auxiliary path is applied to the message pair. As mentioned before this path is only "good" for a limited number of steps, and therefore covers only the early and the middle steps of the compression function. This attack only succeeds if the main differential path contains all the conditions needed for each auxiliary path that is applied to the main differential path. In order to build such a differential path Joux and Peyrin use a path generator proposed in [CR06].

#### **Complexity Analysis in View of SHA-1**

According to unpublished results [WYY05a] the best known attack Wang *et al.* were able to apply, was message modification up to step 25. With the new techniques presented above it should be possible that messages conform to the differential path up to step 28 which means that 5 additional constrains on the message are fulfilled. Hence the overall complexity decreases by a factor of 32 if various other conditions could be met.

Figure 3.5: Structure of the amplified boomerang attack adapted to attack hash functions

#### 3.3.7 Clustered Truncated Differentials and Fast Collision Search

The method presented in [Rec09] and [MR] is an advancement of message modification and is at the time of writing this thesis the best known attack on SHA-0 and SHA-1. To find a collision on SHA-1 using this methods, there was also a distributed computer effort [MRR09] launched which is suspended at the time. A variant of this attack is implemented in the case study which is described in Chapter 6

#### Equations

To find a pair of colliding messages, which is conforming to a certain characteristic, equations have to be solved which are bound to this characteristic. Because of the fact that in every step the state update function is computed, which adds diffusion to the input message, equations in later steps are in general harder to solve than equations in earlier steps. One way to solve equations is through message modification which is described in Section 3.3.4.

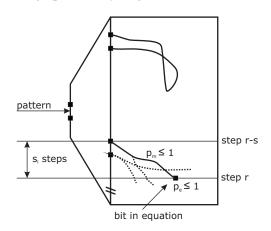

#### Message Modification Patterns

In the attack two different message modification patterns are used. The differentiation is between short patterns and long patterns which are explained in the paragraphs 3.3.7 and 3.3.7. In general long patterns are able to solve equations of higher steps than short patterns. This advancement comes with a price in view of degrees of freedom. There are also certain limitations connected with the usage of these patterns.

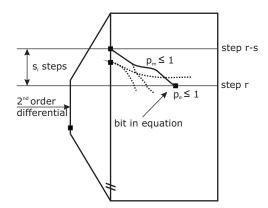

**Short Patterns:** Short patterns are affecting equations between the steps 17 and 22. There are no short patterns known for equations in steps later than 22. In general a small weight difference is injected into the message pair. This difference propagates through the state update function and flips a relevant equation bit with a high probability. In addition the probability that an already solved equation changes its state to not valid, is very low. Figure 3.6 shows the structure of short patterns. The difference introduced at a certain step, requires the re-computation of all the steps up to the step of the targeted equation. Short patterns have a big advantage over long patterns in view of degrees of freedom. Compared to long patterns short patterns require much less degrees of freedom.

Figure 3.6: Short pattern

**Long Patterns:** Long patterns are based on the principles of short patterns. As mentioned in Section 3.3.7 more degrees of freedom are used compared to short patterns to force a local collision. These patterns can be used to fulfill equations between the steps 23 and 30. The differences which are introduced in the earlier steps reappear because of the message expansion in later steps. They solve the targeted equation with a high probability. Equally to short patterns the equations which are already solved remain untouched with a high probability. Figure 3.7 shows the structure of long patterns.

Figure 3.7: Long pattern

#### **Finding Characteristics**

As mentioned before solving equations in higher steps with the help of long patterns requires a lot degrees of freedom. In consequence to this the remaining search space is not big enough to perform a full search. Therefore different characteristics are used for a full search. In the attack described in Section 3.3.5 Wang *et al.* constructed the used characteristic by hand. To run a full search it is therefore necessary to create a tool which is able to automatically generate different characteristics. This problem is targeted in the paper [CR06] by Cannière and Rechberger.

In general they construct characteristics by adding conditions to a characteristic as long as the work-factor<sup>2</sup> of the characteristic is improving. This process consists of two important components:

- The conditions have to be consistent and have to propagate.

- There has to be a determination which conditions to add.

#### **Finding Collisions**

Applying the tools discussed in the sections above the estimated complexity should be in the range of about  $2^{60}$ . This is the best estimated complexity for collision attacks on SHA-1 at the time. Also a complexity of  $2^{60}$  is getting in range of a computation.

<sup>&</sup>lt;sup>2</sup>The workfactor of a characteristic is the required effort that two messages follow the characteristic

# **Chapter 4**

# **Stream Processors**

In general stream processors try to fill the gap between special-purpose processors and general-purpose processors. [KDR<sup>+</sup>03] Particularly for real-time media applications special-purpose processors are better suited than general-purpose processors because they are able to fulfill the in general high performance demands of media applications better. However the big disadvantage is that special-purpose processors are not flexible in their programming or at least limited in their flexibility. [KRD<sup>+</sup>03]

General-purpose processors on the other hand are highly flexible, but their architectures are in general not very well suited for the special demands of typical media applications. [KRD<sup>+</sup>03] They are in general optimized to reduce data latency and reuse data, which results in much more complex data and instruction delivery systems on the chip. In contrast to stream processors general-purpose processors devote only a fraction of the space available on the chip to the actual computation. [Pet09] For example on the Itanium 2 processor only 6.5% of the die is dedicated to ALUs and their registers. [NCBF<sup>+</sup>02]

An application which is suited for a stream processor often fulfills the following three characteristics: [KDK<sup>+</sup>01]

- There is always a huge amount of data parallelism involved because the data elements are highly independent.

- For each data element a high number of operations is typically performed resulting in a high latency tolerance.

- There is almost no reuse of global data.

Not long ago stream processors were almost only used in media applications. This changed drastically in the last years because on one hand GPUs are now commonly used in many PCs and on the other hand manufacturers now provide APIs to program these GPUs to compute problems of general purpose. Two prominent applications using GPUs for example would be folding@home [Fol] and seti@home [ACK<sup>+</sup>02].

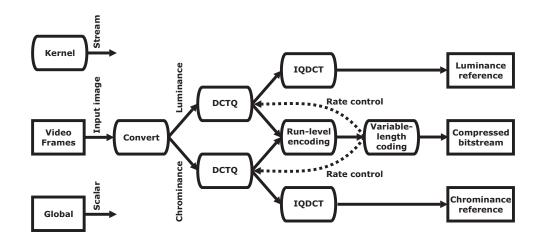

Figure 4.1: The stream programming model explained on the example of an MPEG-2 I-Frame encoder

## 4.1 Stream Programming Model

To fully understand the mechanisms and the structure of stream programs, first a clear terminology has to be defined. For that purpose the so called stream programming model is the tool of choice. The basic concept of the stream programming model is to arrange an application into kernels and streams to expose concurrency and locality. It is easy to see that this structure is well suited for stream architectures with a high number of ALUs. [Rix02]

A Kernel is basically a small program which is applied to every element in the input stream. In view of the kernel each input element is independent and all operations are performed locally. Therefore the computation of these elements can be done in parallel. Each Kernel has an input-stream and an output-stream. Normally data which is generated by the kernel locally, by computing the elements in a stream, doesn't need to be referenced by other stream elements or kernels. [Rix02] However in some cases the programmer has some kind of shared memory to his disposal which makes it possible to share local data of different stream elements within a kernel. With a few exceptions kernels are only allowed to access data from input streams or output streams. [KRD $^+$ 03]

Streams are records or fields of data which are serving as input and output to a kernel. A stream element can be a primitive data type, such as an integer or a float, but can also be a whole data structure. [KRD<sup>+</sup>03]

Figure 4.1 shows the principles of the stream programming model as an exemplary MPEG-2 I-frame encoder. "Video frames", "Luminance reference", "Chrominance reference" and "Compressed bitstream" are container for global data. "Input Image" is the first stream which is fed into the kernel "Convert". The "Convert" kernel itself produces data streams which are again fed into other kernels. At the end the different kernels are streaming their produced values back into the global data containers. [KRD<sup>+</sup>03]

# 4.2 Additional Terminology

#### 4.2.1 Scatter and Gather

Although communication between the individual streams should be minimized, in some cases it can be advantageous. Sometimes for performance sake, it is helpful if a kernel has access to other cells than the one currently being processed. Especially in the case of data communication on GPUs gather and scatter are two types of communication worth mentioning. If a kernel, which currently processes a stream element, needs information from other stream elements it gathers information from other parts of memory. Scatter occurs if a kernel processing a stream element distributes information to other parts of the memory. [PF05]

#### 4.2.2 SIMD

SIMD stands for single instruction multiple data, which means that these architectures issue the same instruction for different data elements. Often stream architectures are structured in a way that a certain number of ALUs are building a SIMD cluster. Within the cluster all ALUs compute the same instruction. SIMD cluster are normally independent, which means that different SIMD cluster are often able to compute different instructions at the same time. [NVI09c]

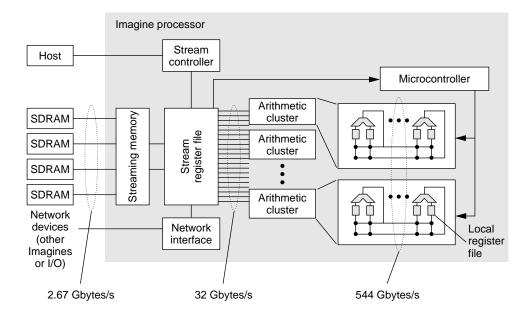

# 4.3 The Imagine Stream Processor

The Imagine stream processor was developed at Stanford and at MIT from 1996 to 2001 and is basically a load and store architecture for streams. 48 arithmetic units organized in 8 arithmetic clusters act as workhorses for the processor and are able to obtain a computational performance of 20 gflops. [Rix02] Imagine is a programmable stream processor which is controlled by a host processor and is able to execute applications directly with the help of streams and kernels. Figure 4.2 pictures the Imagine stream architecture.

Figure 4.2: The imagine architecture [Rix02]

The main stream instructions are:

- Load transfers streams from the DRAM to the SRF

- Store transfers streams from the SRF to the DRAM

- Send transfers streams from the network to the SRF

- Cluster op computes the kernels in the given cluster and writes the output streams back into the SRF

The so called SRF (stream register file) is responsible for storing and loading streams which are generated by the kernels. The host processor issues stream instructions to the stream controller which when ready issues them to the 8 arithmetical clusters. The arithmetical clusters compute the given instructions in SIMD fashion. [KDK $^+$ 01]

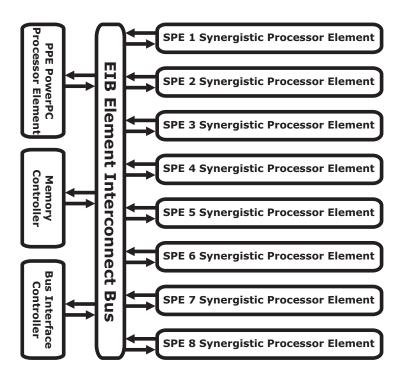

## 4.4 The Cell Multiprocessor

The cell processor was introduced in the year 2005 and is a collaboration of IBM, Sony and Toshiba. The motivation to develop this multiprocessor originated from the fact that traditional architectures would not be able to deliver the computational power necessary for their needs in the near future. One of the goals was to create a multiprocessor which was able to achieve about 100 times the processing power of the PlayStation2. [KDH<sup>+</sup>05] Outstanding performance especially on game and multimedia platforms, real-time response to user and network, applicability to a wide range of platforms and support for introduction in 2005 were also main objectives for the cell processor. [CRDI07]

The Cell architecture shows strong similarities to a CPU/GPU setup in an architectural view. In general the Cell processor consists of a Power Processing Element (PPE) and eight synergistic processor elements (SPEs) connected through a coherent on-chip element interconnect bus (EIB) shown in Figure 4.3. The PPE basically takes over the role of the CPU and the SPEs can be compared to the thread processors on the GPU. One big advantage of the cell architecture is that the EIB is on chip in comparison to the pci-express bus. [KDH<sup>+</sup>05]

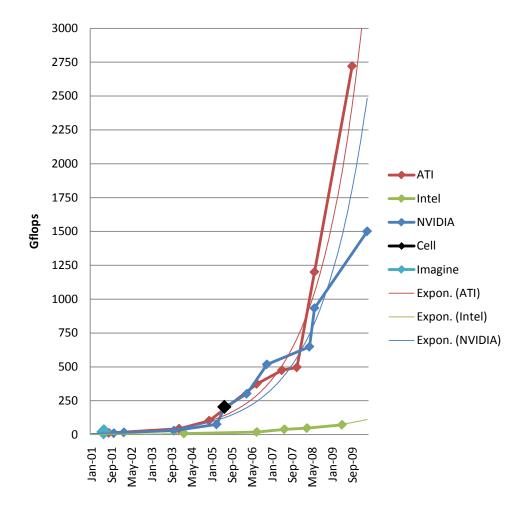

In view of computational power one SPE has a peak performance of 25.6 Gflops. Therefore the whole theoretical computational power of the SPEs is 204.8 Gflops. Compared to GPUs which were released approximately at the same time, the Cell processor has a very similar computational capability than the top of the line GPUs in 2005. Figure 4.6 shows benchmarks of GPUs and the cell multiprocessor.

Figure 4.3: Architectural overview of the cell multiprocessor

# 4.5 GPGPU

For many years now programmers use GPUs to compute problems of general purpose. In general GPUs offer high performance not only in view of computational power but also in view of memory throughput. For a long time these capabilities were hard to access due the fact that GPUs were formally designed to process graphical data and not data of general purpose. As computer graphics applications became more and more demanding, for example to compute 3D Data, the structure of GPUs grew also more flexible.

#### 4.5.1 Historical vs. Modern

The following sections show an overview of the technical developments of GPUs over time.

#### **Traditional Graphics Pipeline**

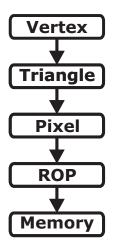

Figure 4.4 shows a traditional graphics pipeline which existed in the depicted structure in principle for the last 20 years. Every function had its own processor for the computation. [NVI06]

Structure of the traditional graphics pipeline: [NVI06]

- Vertex: In the first step the GPU receives vertex data from the CPU. The vertex shader, who evolved from so called "Transform and Lighting"<sup>1</sup>, transforms the 3D position of the vertex into the 2D screen position. They are also responsible for coloration and position properties.

- **Triangle:** The next step is the is the "triangle stage", where primitives such as triangles, lines or points are generated from the vertices.

<sup>&</sup>lt;sup>1</sup>Transform converts spatial coordinates into a 2D view. Lighting is responsible for the coloration of objects due to the influence of lighting objects.

- **Pixel:** The primitives are then converted into pixel fragments by the "pixel" unit. After further processing the pixel fragments are written into the frame buffer.

- **ROP:** The ROP (Raster Operation) stage is responsible for checking visibility, transparency and anti-aliasing.

- **Memory:** The final processed pixel is sent to the frame buffer memory for scan-out and display to the monitor.

Figure 4.4: Classic graphics pipeline

#### **Modern Graphic Pipeline**

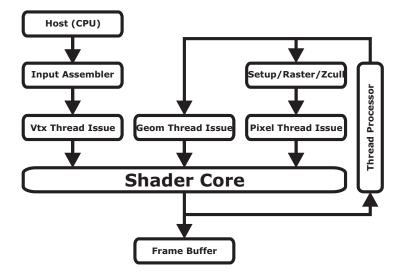

With the introduction of NVIDIAs 8000 series and AMDs HD 2000 series the setup of the traditional graphics pipeline changed drastically. The graphics pipeline model is replaced with a so called "Unified Pipeline and Shader Design" which is shown in Figure 4.5. [YG07]

Figure 4.5: Unified pipeline and shader design

This approach changes the standard sequential flow into a loop oriented flow. Data is fed into the shader core, which processes it and writes the outcome into the registers, where it can be again fed into

the shader core and so on. [NVI06] A comparison between this architecture and the classical graphics pipeline design shows that the unified shader core is much better suited for general purpose computing because all ALUs are programmable and therefore are able to compute different types of programs. [YG07]

#### 4.5.2 Comparison of GPUs and CPUs

It is interesting to see how GPUs and CPUs evolved over time in view of computational capabilities and bandwidth capabilities. Figure 4.6 shows clearly that in view of raw computational power stream processor architectures are superior to general-purpose processors. It's a fact that the computational power of the imagine stream processor and the cell multiprocessor aligns with the computational power of state of the art GPUs, at the time of their launch. Therefore, it stands to reason that the superior computational capabilities of stream processors compared to general purpose processors is due to the architectural differences.

Table 4.1 clearly shows that the gap between GPUs and CPUs widens over time in view of computational capabilities shown in Figure 4.6. This is probably because of the fact that stream processors compared to traditional multi-purpose processors are a relatively young field of application. Due to this fact there is probably more room for improvement in the field of stream processors which explains the increasing ratio shown in Table 4.1

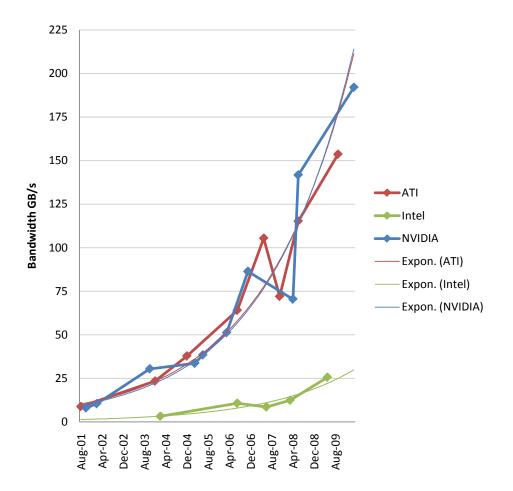

An interesting observation is that although given similar premises between bandwidth capabilities shown in Figure 4.7 and computational capabilities, the ratio between GPUs and CPUs in view of bandwidth capabilities is fairly constant as Table 4.1 shows.

| Ratio GPUs/CPUs |        |           |  |  |  |

|-----------------|--------|-----------|--|--|--|

| Year            | Gflops | Bandwidth |  |  |  |

| 2004            | 14     | 11        |  |  |  |

| 2006            | 20     | 8         |  |  |  |

| 2007            | 13     | 12        |  |  |  |

| 2008            | 26     | 11        |  |  |  |

| 2009            | 39     | 6         |  |  |  |

Table 4.1: Ratio GPUs/CPUs in view of bandwidth and computational power

#### 4.5.3 Theoretical Performance Capabilities

It is possible to theoretically compute the performance of GPUs in view of Gflops by knowing the ALU frequency, the number of ALUs and how much operations the architecture itself can compute in one clock cycle. Equation 4.1 shows how to compute the theoretical performance of a GPU.

For example the NVIDIA GTX 260: ALU frequency: 1242 MHz Number of ALUs: 192 Instructions per clock cycle: 3 (MADD (2 flops) and MUL (1 flop)) Gflops = 1.242 \* 192 \* 3 = 715.392 Gflops

Another example would be the ATI HD 4870: ALU frequency: 750 MHz Number of ALUs: 800 Instructions per clock cycle: 2 (MADD (2 flops)) Gflops = 0.75 \* 800 \* 2 = 1200 Gflops

It is very important to state that these numbers are only theoretical and cannot be directly translated into real performance. In the case of NVIDIA for example the extra MUL operation is not always available, as Section 6.3.4 shows.

#### 4.5.4 Gflops and Bandwidth Comparison

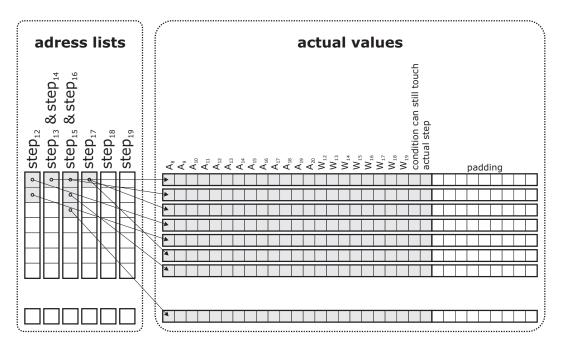

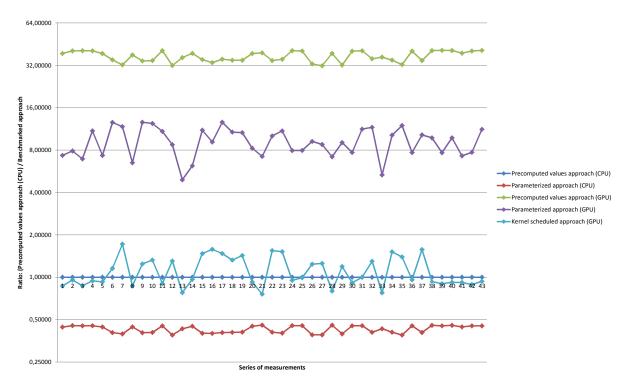

Figure 4.6 shows that the performance measurements of ATI and NVIDIA in view of Gflops follow a very similar path. This indicates that both manufacturers are at a close distance to each other in view of their technical progress. It can also be seen that the trendlines of ATI and NVIDIA shown in Figure 4.6 follow a similar path which falls into line of the previous statement.