Masterarbeit

# Evaluierung eines NFC-Tags welches AES und ECDSA unterstützt

Thomas Korak

t.korak@student.tugraz.at

Institute for Applied Information Processing and Communications (IAIK) Technische Universität Graz Inffeldgasse 16a, 8010 Graz, Österreich

Begutachter: Ao. Univ.-Prof. Dipl.-Ing. Dr. techn. Karl-Christian Posch Betreuer: Dipl.-Ing. Thomas Plos

Graz, im September 2011

Master's Thesis

# Evaluation of a Security-enabled NFC Tag with AES and ECDSA

Thomas Korak

t.korak@student.tugraz.at

Institute for Applied Information Processing and Communications (IAIK) Graz University of Technology Inffeldgasse 16a, 8010 Graz, Austria

Assessor: Ao. Univ.-Prof. Dipl.-Ing. Dr. techn. Karl-Christian Posch Supervisor: Dipl.-Ing. Thomas Plos

Graz, September 2011

#### Abstract

Near-Field Communication (NFC) is a contactless communication technique based on Radio-Frequency Identification (RFID) technology. Tags that are used in NFC systems are limited in power consumption and chip size. These limitations make integration of strong cryptographic security to such tags challenging. It is not enough to use a secure algorithm but also the implementation has to be secure against attacks like Side-Channel Analysis (SCA). In this work we evaluate an NFC prototype tag with advanced security features concerning its resistance against SCA attacks. The cryptographic algorithms implemented on the tag are the Advanced Encryption Standard (AES) and the Elliptic Curve Digital Signature Algorithm (ECDSA). In order to achieve resistance against this kind of attack, the NFC tag has two countermeasures integrated: shuffling and the insertion of dummy rounds. The main findings are that the countermeasures significantly increase the effort to reveal the secret key of the tag. The attacks in this work are performed under laboratory conditions with detailed knowledge of the device. For an attacker without this detailed knowledge, the effort for succeeding the attack will be much higher. Furthermore, we evaluate techniques to decrease the impact of the countermeasures on the attack complexity. One of these techniques is the detection of dummy rounds. The presented detection algorithm allows to reduce the attack complexity by a factor of 16. Besides evaluation of the SCA resistance of the prototype extensive functionality tests are performed to guarantee that the chip works according to the specifications.

With the SCA results on the cryptographic primitive we underline that it is not enough to use a secure algorithm but also the implementation has to be resistant against this kind of attacks. The usage of countermeasures can increase the complexity of power-analysis attacks significantly but the implementation has to be done carefully. It must not be possible for an attacker to reveal information about the parameters like the number of inserted dummy rounds used by the countermeasures.

Keywords: NFC, RFID, Side-channel attacks, AES, ECDSA, DPA

### Kurzfassung

Nahfeldkommunikation (NFC) ist eine kontaktlose Kommunikationstechnik, die auf Radiofrequenz-Identifikation (RFID) basiert. Transponder, welche in NFC-Systemen eingesetzt werden sind sowohl in der Leistungsaufnahme sowie in der Chipgröße limitiert. Dadurch ist es schwierig, sichere kryptografische Algorithmen auf diesen Transpondern zu implementieren. Des Weiteren ist es nicht ausreichend, einen sicheren Algorithmus zu verwenden, auch die Implementierung des Algorithmus muss sicher gegen Attacken sein. In der folgenden Arbeit wird ein NFC-Transponder evaluiert, auf welchem kryptografische Algorithmen implementiert sind. Zur Evaluierung der Sicherheit werden Seitenkanalattacken (SCA) eingesetzt. Auf dem Transponder sind zwei Algorithmen implementiert, der Advanced Encryption Standard (AES) sowie der Elliptic Curve Digital Signature Algorithm (ECDSA). Um Seitenkanalattacken zu erschweren, sind auf dem Transponder zwei Gegenmaßnahmen integriert: Das Einfügen von so genannten Dummyrunden und das Randomisieren von Operationen (Shuffling). Das Ergebnis der Attacken ist, dass die Gegenmaßnahmen den Aufwand für das Finden des verwendeten Schlüssels signifikant erhöhen. Unsere Attacken wurden unter Laborbedingungen durchgeführt und es stand detailliertes Wissen über den attackierten Chip zur Verfügung. Für einen Angreifer, welcher dieses Wissen nicht hat, ist der Aufwand für eine erfolgreiche Attacke noch wesentlich höher. Es wurden auch Methoden evaluiert, welche den Einfluss der Gegenmaßnahmen auf die Komplexität der Attacke vermindern. Das herausfiltern der Dummyrunden ist eine der Methoden, welche eingesetzt wurden. Mit dem verwendete Algorithmus zum Erkennen der Dummyrunden konnte der Aufwand für die Attacken um den Faktor 16 verringert werden. Da es sich bei dem Chip um einen Prototypen handelt, wurden auch Tests durchgeführt, welche zeigen dass der verwendete Chip den Spezifikationen entsprechend funktioniert.

Mit den durchgeführten Attacken konnte einmal mehr gezeigt werden, dass es nicht ausreichend ist einen sicheren Algorithmus zu verwenden. Auch bei der Implementierung muss darauf geachtet werden, dass Seitenkanalattacken verhindert werden. Die verwendeten Gegenmaßnahmen erschweren Seitenkanalattacken, jedoch müssen die Gegenmaßnahmen sorgfältig implementiert werden. Es soll für einen Angreifer nicht möglich sein, Informationen über die Parameter der Gegenmaßnahmen zu zu erhalten.

Schlüsselwörter: Nahfeldkommunikation, Seitenkanalattacken, Radiofrequenz-Identifikation

# **Statutory Declaration**

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

# Eidesstattliche Erklärung

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt und die den benutzten Quellen wörtlich und inhaltlich entnommene Stellen als solche kenntlich gemacht habe.

$\operatorname{Ort}$

Datum

Unterschrift

# Acknowledgements

First of all I would like to thank my supervisor Thomas Plos for the support and the valuable inputs during the work on this master thesis.

I also want to thank all the members of the Institute for Applied Information Processing and Communications (IAIK) for their hints and inputs during my work.

Most importantly I would like to thank my family for their support and encouragement.

Graz, September 2011

Thomas Korak

# Contents

| Lis | st of Tables                                        | iv              |

|-----|-----------------------------------------------------|-----------------|

| Lis | st of Figures                                       | vi              |

| 1.  | Introduction                                        | 1               |

| 2.  | The CRYPTA Tag                                      | 3               |

|     | 2.1. Overview                                       | 3               |

|     | 2.2. RFID Systems                                   | 3               |

|     | 2.3. Applications for CRYPTA                        | 4               |

|     | 2.4. Hardware Architecture                          | 5               |

|     | 2.5. Crypto Unit                                    | 6               |

|     | 2.5.1. AES Implementation                           | 6               |

|     | 2.5.2. ECDSA Implementation                         | 6               |

|     | 2.6. EEPROM                                         | 7               |

|     | 2.6.1. EEPROM Layout                                | 7               |

|     | 2.6.2. Configuration Files                          | 8               |

|     | 2.7. Supported Commands                             | 10              |

|     | 2.7.1. S-Block Commands                             | 10              |

|     | 2.7.2. R-Block Commands                             | 10              |

|     | 2.7.3. I-Block Commands                             | 10              |

|     | 2.8. CRYPTA-Chip Test Board                         | 12              |

|     | 2.9. FPGA Prototype                                 | 13              |

|     | 2.10. Summary                                       | 14              |

| 3   | An Introduction to AES                              | 15              |

| 0.  | 3.1. Parameters for AES                             | 15              |

|     | 3.2. Encryption Process                             | 15              |

|     | 3.3. Decryption Process                             | 16              |

|     | 3.4. Attacks on AES                                 | 19              |

| Δ   | An Introduction to ECDSA                            | 22              |

| ч.  | 4.1. The Digital Signature Algorithm                | 23              |

|     | 4.2. The Elliptic Curve Digital Signature Algorithm | $\frac{23}{24}$ |

|     | 4.2. The Empire Curve Digital Signature Algorithm   | $\frac{24}{26}$ |

| 5.  | Attacking Cryptographic Devices                     | 28              |

| э.  | 5.1. Types of Implementation Attacks                | 28              |

|     |                                                     | 20              |

|    | 5.2. | Power Traces                                                            |

|----|------|-------------------------------------------------------------------------|

|    |      | 5.2.1. Recording the Traces                                             |

|    |      | 5.2.2. Statistical Properties                                           |

|    | 5.3. | Simple Power Analysis                                                   |

|    | 5.4. | Differential Power Analysis                                             |

|    |      | 5.4.1. The 5 Steps of a DPA Attack                                      |

|    |      | 5.4.2. DPA Attack Based on the Correlation Coefficient                  |

|    |      | 5.4.3. Related Work on DPA                                              |

|    | 5.5. | Countermeasures Against Power-Analysis Attacks                          |

|    | 0.01 | 5.5.1. Dummy Operations                                                 |

|    |      | 5.5.2. Shuffling                                                        |

|    |      | 5.5.3. Masking                                                          |

| j. | Fund | ctionality-Test Results 4                                               |

|    | 6.1. | Test Setup                                                              |

|    | 6.2. | File Operations                                                         |

|    |      | 6.2.1. Read Access of Protected Files                                   |

|    |      | 6.2.2. Correct Reading Length                                           |

|    |      | 6.2.3. Read Access When External Authentication is Required             |

|    |      | 6.2.4. Invalid File IDs                                                 |

|    |      | 6.2.5. Write Protection                                                 |

|    |      | 6.2.6. Writing VALUE1 File 44                                           |

|    |      | 6.2.7. Testing the Lock Bits                                            |

|    |      | 6.2.8. Writing Only After External Authentication                       |

|    |      | 6.2.9. Testing the Correct Write Length                                 |

|    | 6.3. |                                                                         |

|    |      | 6.3.1. Test Scenarios AES and SHA1                                      |

|    |      | 6.3.2. Test Scenarios ECDSA                                             |

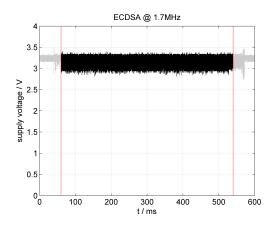

|    |      | 6.3.3. Execution Times of Cryptographic Operations                      |

|    | 6.4. | Testing the Different Data Rates                                        |

|    | 6.5. |                                                                         |

| 7. | SCA  | Results 50                                                              |

|    | 7.1. | SCA Attack Setup                                                        |

|    | 7.2. | Attacks on the FPGA Prototype                                           |

|    |      | 7.2.1. Choosing the Intermediate Result                                 |

|    |      | 7.2.2. Record the Traces                                                |

|    |      | 7.2.3. Generating the Hypothetical Power Values                         |

|    |      | 7.2.4. Comparing the Hypothetical Power Values to the Recorded Traces 6 |

|    |      | 7.2.5. Results for Attacks on the First Round in Evaluation Mode 64     |

|    |      | 7.2.6. Results for Attacks on the Last Round in Evaluation Mode 6       |

|    |      | 7.2.7. Results for Attacks in Standard Mode                             |

|    | 7.3. | Attacks on the CRYPTA Tag                                               |

|    |      | 7.3.1. Choosinging the Intermediate Result                              |

|    |      | 7.3.2. Recording the Traces   66                                        |

|    |      |                                                                         |

|     | 7.3.3. Generateing the Hypothetical Power Values |         |                                                                          |    |  |  |  |

|-----|--------------------------------------------------|---------|--------------------------------------------------------------------------|----|--|--|--|

|     |                                                  | 7.3.4.  | Comparing the Hypothetical Power Values to the Recorded Traces $\ . \ .$ | 69 |  |  |  |

|     |                                                  | 7.3.5.  | Results for Attacks on the First Round in Evaluation Mode                | 69 |  |  |  |

|     |                                                  | 7.3.6.  | Results for Attacks on the Last Round in Evaluation Mode $\ldots$ .      | 70 |  |  |  |

|     | 7.4.                                             | Summa   | ary of the Results                                                       | 71 |  |  |  |

| 8.  | Cond                                             | clusion |                                                                          | 74 |  |  |  |

| Α.  | DPA                                              | plots   |                                                                          | 76 |  |  |  |

| Lis | t of /                                           | Abbrevi | ations                                                                   | 81 |  |  |  |

| Bil | oliogr                                           | aphy    |                                                                          | 83 |  |  |  |

# List of Tables

| 2.1. | Features of the different files on the chip.                                     | 8  |

|------|----------------------------------------------------------------------------------|----|

| 2.2. | Description of the bits of CFG1.                                                 | 9  |

| 2.3. | Description of the bits of CFG2.                                                 | 9  |

| 2.4. | APDU from the reader to the tag                                                  | 11 |

| 2.5. | The instructions supported by the CRYPTA tag                                     | 11 |

| 2.6. | APDU from the tag to the reader.                                                 | 12 |

| 2.7. | Status words of the different commands and their meaning                         | 12 |

| 4.1. | Domain parameters of the DSA.                                                    | 24 |

| 4.2. | Domain parameters ECDSA.                                                         | 25 |

| 4.3. | Comparison of key sizes (in bits) for different security levels                  | 26 |

| 5.1. | Values for the <i>noisefloor</i> for different numbers of traces <i>n</i>        | 41 |

| 6.1. | Test results for the AES implementation of the CRYPTA chip                       | 51 |

| 6.2. | Test results for the ECDSA implementation of the CRYPTA chip                     | 52 |

| 6.3. | Overview of the execution times of the cryptographic operations                  | 54 |

| 7.1. | Number of traces recorded overall in comparison to the number of shifted traces. | 63 |

| 7.2. | Estimate of the required number of traces for a DPA attack when different        | 05 |

| 7.0  | countermeasures are activated (*Dummy round detection active)                    | 65 |

| 7.3. | Occurrence of the leakage of the single key bytes and the correlation values for | 70 |

| -    | the FPGA prototype.                                                              | 72 |

| (.4. | Occurrence of the leakage of the single key bytes and the correlation values for | 70 |

|      | the CRYPTA tag.                                                                  | 73 |

# List of Figures

| 2.1.         | Typical lifecycle of the CRYPTA tag.                                          | 5             |

|--------------|-------------------------------------------------------------------------------|---------------|

| 2.2.         | The main components on the CRYPTA tag                                         | $\frac{6}{7}$ |

| 2.3.<br>2.4. | EEPROM layout of the CRYPTA chip                                              | 13            |

| 2.4.<br>2.5. | FPGA board                                                                    | 13<br>14      |

| 2.5.<br>2.6. | The motherboard.                                                              | 14<br>14      |

|              |                                                                               |               |

| 3.1.         | The subBytes() transformation                                                 | 17            |

| 3.2.         | The shiftRows() transformation                                                | 17            |

| 3.3.         | The mixColumns() transformation                                               | 17            |

| 3.4.         | The InvMixColumns() transformation                                            | 18            |

| 3.5.         | Pre-round and first round of AES.                                             | 20            |

| 3.6.         | Attack on the first round of AES.                                             | 20            |

| 3.7.         | Last two rounds of AES.                                                       | 21            |

| 3.8.         | Attack on the last round of AES                                               | 21            |

| 4.1.         | The steps during a signature generation by Alice and a signature verification |               |

|              | by Bob.                                                                       | 23            |

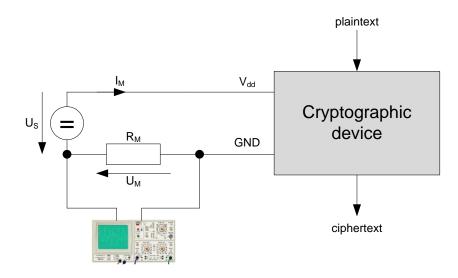

| 5.1.         | Schematic overview of a typical power measurement setup                       | 31            |

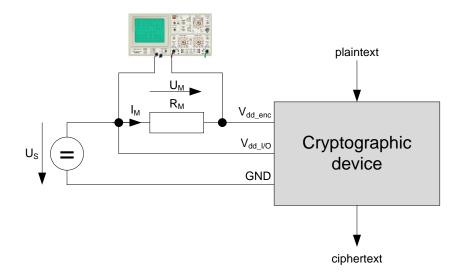

| 5.2.         | Schematic overview of a power measurement setup with different $V_{dd}$ lines | 31            |

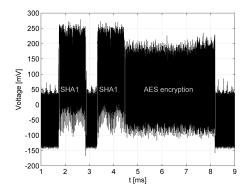

| 5.3.         | Power trace of CRYPTA during an AES encryption                                | 32            |

| 5.4.         | EM trace of the FPGA prototype during an AES encryption                       | 32            |

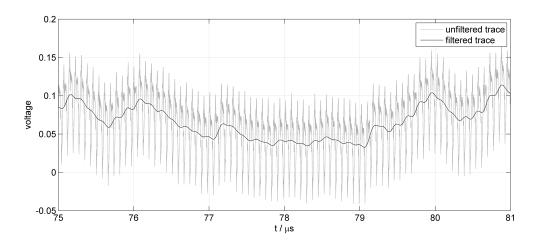

| 5.5.         | Power trace before and after applying a lowpass filter                        | 33            |

| 5.6.         | Histogram of the voltage values.                                              | 34            |

| 5.7.         | Histogram of the data values after substitution                               | 34            |

| 5.8.         | Histogram of the voltage values for two different operations                  | 35            |

| 5.9.         | The relevant parts of a power trace around the positive clock edge            | 36            |

|              | Zoomed view of power traces with different Hamming weight of processed data.  | 37            |

|              | Result of a DPA attack on the CRYPTA tag                                      | 39            |

|              | Results of DPA attacks on the CRYPTA tag                                      | 40            |

|              | Evolution of the correlation coefficients.                                    | 40            |

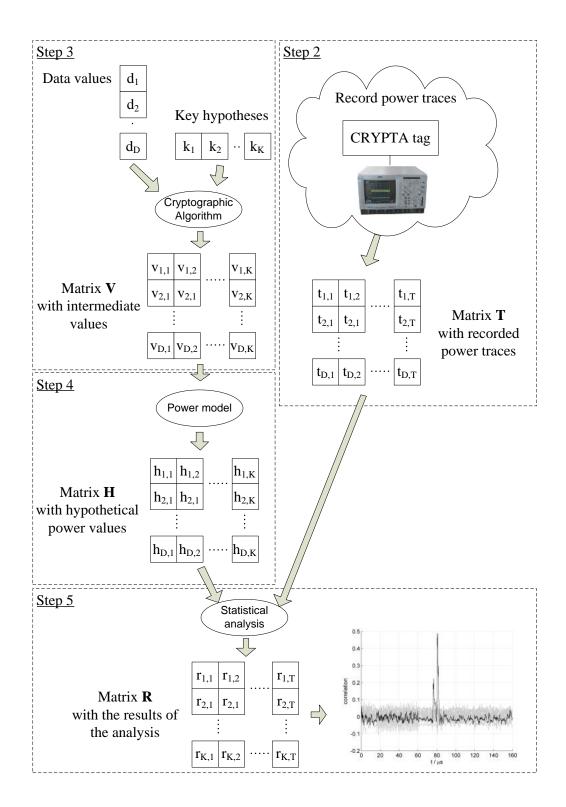

| 5.14.        | The sequence of a DPA attack.                                                 | 42            |

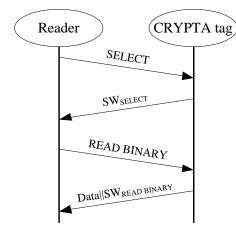

| 6.1.         | Communication sequence for reading a file.                                    | 46            |

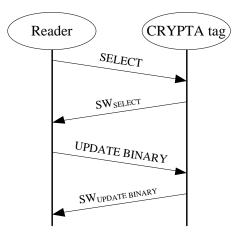

| 6.2.         | Communication sequence for writing a file.                                    | 46            |

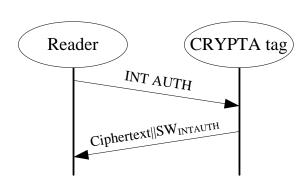

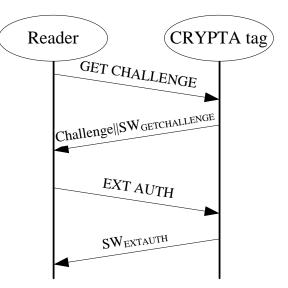

| 6.3.         | Command sequence for a tag authentication.                                    | 50            |

| 6.4.         | Command sequence for a reader authentication                                  | 50            |

|              |                                                                               |               |

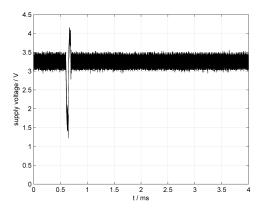

| 6.5.  | Voltage drop without capacitor                                                                                                                           | 51 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.6.  | Voltage drop with capacitor.                                                                                                                             | 51 |

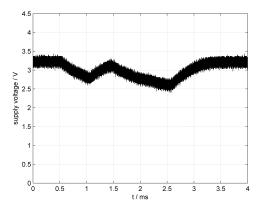

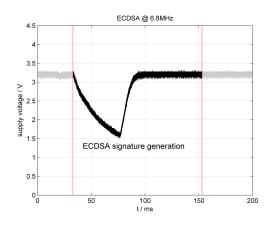

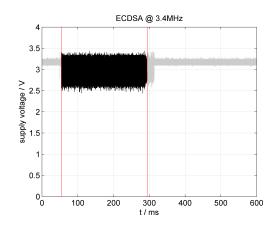

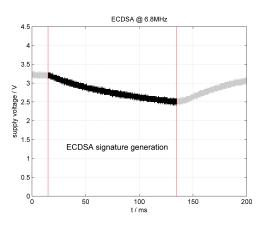

| 6.7.  | Supply voltage of the CRYPTA tag during ECDSA signature generation (1.7 MHz)                                                                             | 53 |

| 6.8.  | Supply voltage of the CRYPTA tag during ECDSA signature generation                                                                                       | 00 |

| 0.0.  | (3.4  MHz).                                                                                                                                              | 53 |

| 6.9.  | Capacitor with too small value $(10 \mu\text{F})$ .                                                                                                      | 53 |

|       | Capacitor with appropriate value $(100 \mu\text{F})$ .                                                                                                   | 53 |

| 7.1.  | Schematic overview of the measurement setup.                                                                                                             | 56 |

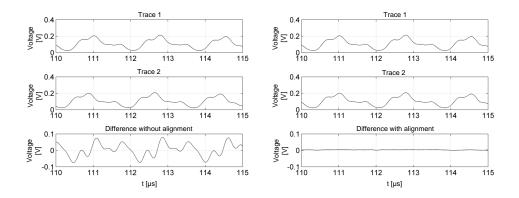

| 7.2.  | Impact of the alignment process on the difference of two traces                                                                                          | 57 |

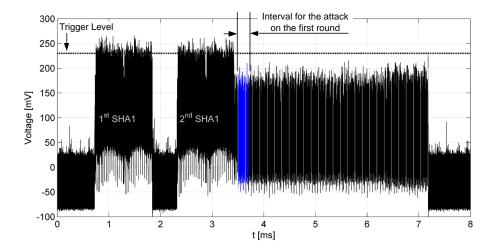

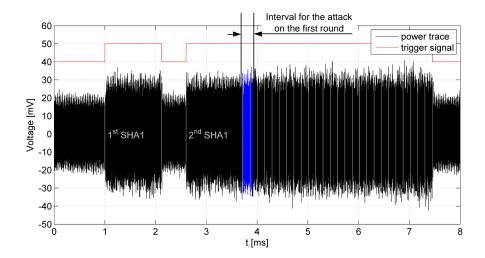

| 7.3.  | Choice of the trigger level on the power trace of the CRYPTA tag                                                                                         | 58 |

| 7.4.  | Segmentation of the EM-trace of the FPGA prototype                                                                                                       | 58 |

| 7.5.  | Visualisation of the correlation steps.                                                                                                                  | 61 |

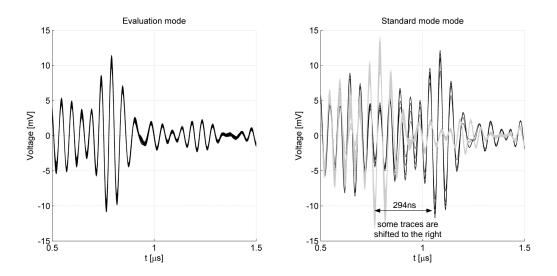

| 7.6.  | Filtered traces recorded in evaluation mode (left) and in standard mode (right).                                                                         | 62 |

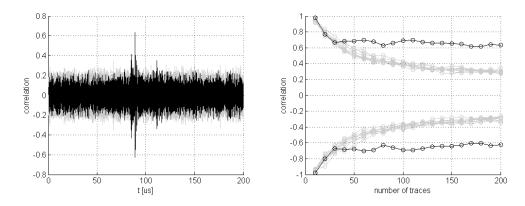

| 7.7.  | DPA attack on the first key byte of the FPGA prototype tag (left) and the                                                                                |    |

|       | correlation coefficient as a function of the number of traces (right)                                                                                    | 64 |

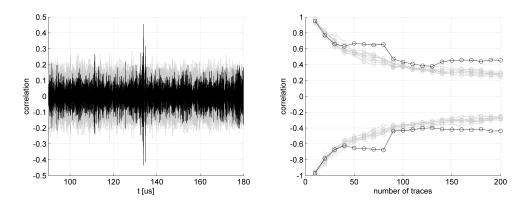

| 7.8.  | DPA attack on the first key byte of the tenth round key (left) and the correlation                                                                       | ~  |

| 7.0   | coefficient as a function of the number of traces (right).                                                                                               | 65 |

| 7.9.  | DPA attack in standard mode on the first key byte (left) and the correlation                                                                             | cc |

| 7 10  | coefficient as a function of the number of traces (right)                                                                                                | 66 |

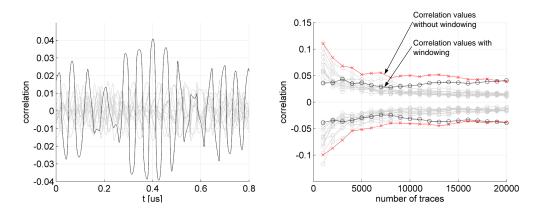

| 1.10. | DPA attack (with windowing) in standard mode on the first key byte and                                                                                   | 67 |

| 711   | evolution of correlation coefficient with increasing number of traces used DPA attack (with windowing) in standard mode on the first key byte and        | 07 |

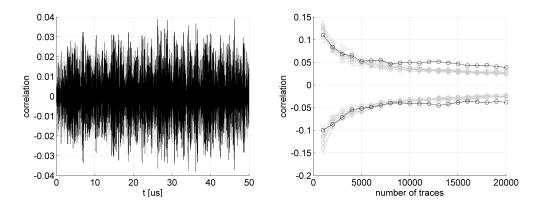

| (.11. |                                                                                                                                                          | 67 |

| 7 1 9 | evolution of correlation coefficient with increasing number of traces used DPA attack on the first key byte of the CRYPTA tag (left) and the correlation | 07 |

| 1.12. | coefficient as a function of the number of traces (right).                                                                                               | 69 |

| 7 1 3 | DPA attack on the first key byte of the tenth round key (left) and the correlation                                                                       | 09 |

| 1.10. | coefficient as a function of the number of traces.                                                                                                       | 70 |

| 7.14  | Correlation peaks in the trace of the attack on the first key byte of the tenth                                                                          | 10 |

| 1.17. | round key of the CRYPTA chip.                                                                                                                            | 70 |

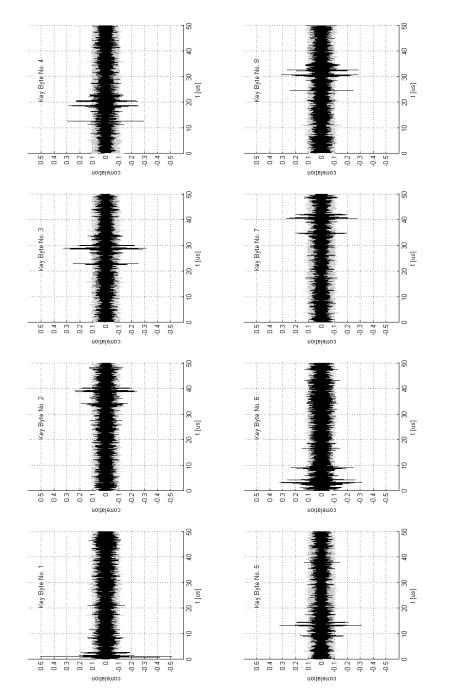

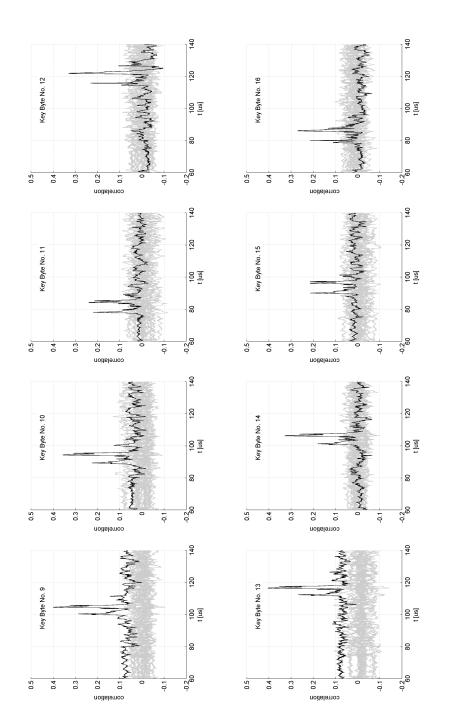

| A.1.  | Correlation traces of key byte 1 to key byte 8 (FPGA prototype)                                                                                          | 77 |

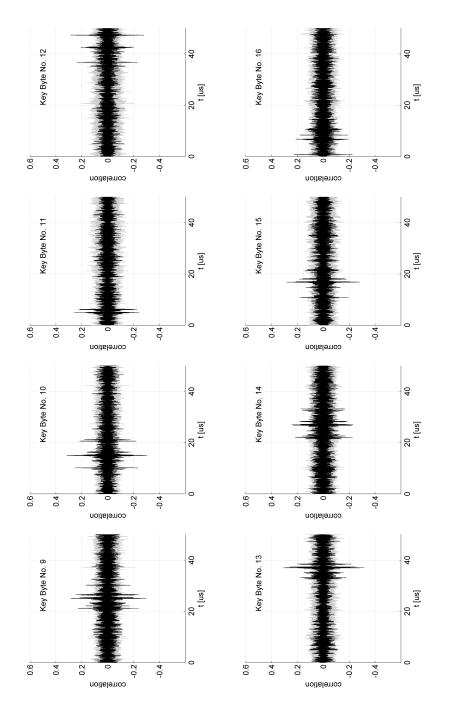

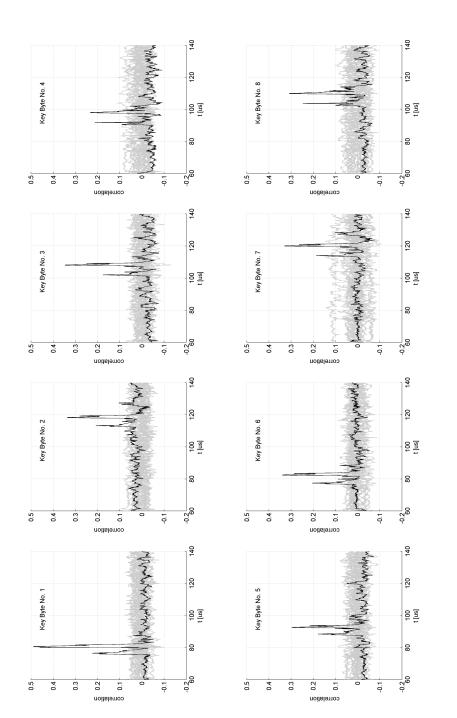

|       | Correlation traces of key byte 9 to key byte 16 (FPGA prototype)                                                                                         | 78 |

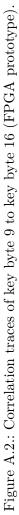

|       | Correlation traces of key byte 1 to key byte 8 (CRYPTA tag)                                                                                              | 79 |

| A.4.  | Correlation traces of key byte 9 to key byte 16 (CRYPTA tag)                                                                                             | 80 |

# 1. Introduction

Near-Field Communication (NFC) is a standardized wireless communication technology that works on short ranges. The rise of NFC-enabled mobile phones on the one hand and the usability of the technology on the other hand give this technology promising prospects for the future. There are many real-world examples where NFC can be used. Pay a bus fare or do other micropayments, enter or exit the office, log in to a computer or open the car doors are just some examples. In 2004 the so-called NFC Forum, a non-profit industry association, was formed which has now already 140 members. The members are from different fields (manufacturers, application developers, financial service institutions, ...) and work on the rise of the NFC technology. The main goals of the NFC Forum are to develop standard-based NFC specifications, encourage manufacturers to use NFC technology, ensure that NFC devices comply with the standards and train and educate enterprises in the field of NFC.

The main parts of an NFC-system are the reader and the transponder. The reader generates an electromagnetic field that is used for communication with a transponder. The transponders, which are also called tags, consist of a chip and an antenna. Tags are called passive if they extract the supply voltage from the reader field and active if they are battery powered.

On the first sight NFC might be seen as a secure communication technology because the communication range is only a few centimeters but there are several issues concerning security which have to be obeyed. First of all there is eavesdropping. If the communication is not encrypted an attacker can listen to the communication between two devices. For that purpose a small antenna has to be placed between sender and receiver. Data corruption, manipulation and insertion are also possibilities for an attacker to attack devices that use NFC technology. In order to address these security issues, cryptography has to be integrated into all components of NFC-systems, even in the tags. The Institute for Applied Information Processing and Communications (IAIK) together with austriamicrosystems [aus11b] and RF-iT-Solutions [iS11] have developed such a cryptographically protected tag chip (in the following called CRYPTA chip). The CRYPTA tag is a passive Radio-Frequency Identification (RFID) tag that works according to the NFC-Forum Type 4 tag specification. Key features of the chip are the NFC air interface that is compliant to the ISO14443A standard and the support of symmetric and asymmetric cryptography.

For enabling symmetric cryptography, the Advanced Encryption Standard (AES) is implemented on the chip. As AES is standardized by the National Institute of Standards and Technology (NIST) the interoperability with many other devices can be guaranteed. For asymmetric cryptography the Elliptic Curve Digital Signature Algorithm (ECDSA) is implemented. The ECDSA is a special form of the standardized Digital Signature Algorithm (DSA) using elliptic curves. Only a few prototype chips of the CRYPTA tag have been fabricated so far. For a prototype it is very important that all the implemented functions work according to the specification. The secure implementation of the cryptographic primitives is also of great importance.

The first objective of this thesis is to test the correct execution of all the implemented functionalities. The focus in this part is put on the evaluation of AES and ECDSA, the evaluation of the protection mechanisms for the implemented file system as well as on the evaluation of the different clock frequencies the tag can operate with. Two RFID readers as well as an NFC-enabled mobile phone are used for the tests.

The second objective is to evaluate the security level of the AES implementation. So-called countermeasures are implemented on the tag to enhance the security level. We can evaluate the effectiveness of these countermeasures as they can be enabled and disabled. Side-channel analysis (SCA) attacks targeting this AES implementation are performed to reveal information about the secret key used for encryption and decryption. The power consumption during the encryption or decryption as well as the electromagnetic emanation of the chip are used as side channels. The power traces needed for the attacks are recorded using an oscilloscope and analyzed using statistical methods which are also presented in this work. After this analysis steps the correct values for the key bytes can be extracted with a high probability. The more traces are needed for a successful attack the higher is the complexity of the attack and the security level of the implemented cryptographic algorithm.

The remainder of the thesis is organized as follows:

**Chapter 2** gives some background information to the CRYPTA chip. We focus on the applications where tags using this chip can be used as well as on the architecture of the chip. **Chapter 3** deals with the AES. First we present the algorithm for encryption as well as decryption followed by some attack scenarios.

**Chapter 4** gives an introduction to the ECDSA and compares it to normal DSA. Here we show that the algorithm using elliptic curves is well-suited for applications with low hardware resources like RFID tags.

**Chapter 5** gives an overview about SCA attacks. Here we present different approaches how side-channel information can be used in order to reveal some secret information of an implementation. In the end of the chapter we also give some countermeasures to make an implementation resistant against SCA attacks.

**Chapter 6** points out the results of the functionality tests of the CRYPTA chip. We evaluated the commands for writing and reading files as well as the cryptographic commands. Also the results of the tests for the different configurations of the chip concerning the clock frequency or the data rates for communication with the different readers can be found in this chapter.

**Chapter 7** deals with the results of the SCA attacks on the AES implementation of the CRYPTA tag. Here different methods for measuring the side-channel information are presented and an evaluation of the effectiveness of the implemented countermeasures is given. We also describe which steps are necessary in order to perform a successful attack.

Chapter 8 concludes the thesis and gives suggestions for future work.

# 2. The CRYPTA Tag

CRYPTA is the abbreviation for **CRY** ptographic **P**rotected **TA**g. It is a passive RFID tag with advanced cryptographic functions. CRYPTA is a government-funded project in cooperation with two companies: Austriamicrosystems and RF-iT Solutions. The CRYPTA tag was developed and evaluated at the Institute of Applied Information Processing and Communications (IAIK). The following chapter gives an overview of the tag with some application scenarios followed by a description of the architecture of the chip. Later in this chapter the focus is put on the development board where the chip is mounted on. Two devices were used for evaluation: the CRYPTA prototype tag as well as an FPGA prototype. The last section gives a description of the FPGA prototype that was used for evaluation.

#### 2.1. Overview

The CRYPTA tag supports symmetric authentication using the Advanced Encryption Standard (AES) as well as asymmetric authentication using the Elliptic Curve Digital Signature Algorithm (ECDSA). For storing data on the tag an EEPROM with a size of 4096 bits is mounted on the chip. The EEPROM is organized in several files with different access protection mechanisms. The tag contains a capability container file (CC file) and a nearfield communication (NFC) data-exchange format file (NDEF file) to be compliant to NFC forum Type-4 tags [NFC07]. It uses the ISO 14443A standard for communication with the reader. The protocol for anticollision and selection of the tag is implemented according to the ISO 14443-3 standard [Int01] and the advanced functionality is implemented according to the ISO 14443-4 standard [Int08]. Higher-layer information is transmitted using application protocol data units (APDUs). The ISO7816-4 standard [Int95] shows how the previously mentioned APDUs are constructed. The detailed specification of CRYPTA can be found in [Fel10].

#### 2.2. RFID Systems

A typical RFID system consists of an RFID tag, a reader and a backend database. By using the reader field the tag and the reader can communicate with each other contactless. A tag is called passive if it extracts the supply voltage from the reader field. Active tags are equipped with a small battery for power supply, which allows to increase the communication range. The reader can be a dedicated hardware device connected to a computer as well as e.g. a smartphone like the Samsung Nexus S which has a build in NFC chip. When a large number of mobile devices have NFC functionality integrated the applications are expected to become more and more complex. So also the need for security features rises. Because of that fact cryptographic primitives have to be implemented on RFID tags. There are two main constraints which have to be considered during the design of an RFID tag: the power consumption and the chip size. Especially for passive tags the power consumption has to be low because the amount of energy which can be extracted from the reader field is limited. The size of the chip is important because the costs of the chip increase with the size. An overview of the different RFID technologies is given in the 'RFID-Handbook' [Fin03].

#### 2.3. Applications for CRYPTA

The CRYPTA tag is a passive tag that extracts the supply voltage from the reader field. No additional battery is needed to power the chip. Additionally, also the clock signal is extracted from the reader field. One of the major applications of CRYPTA is the proof of origin. Manufacturers can attach this chip to their (expensive) goods like designer clothes or watches and the customer can use the smartphone to check whether the article is original or a fake. The ECDSA is a way to perform such a proof of origin. It is an asymmetric-key system that uses a key pair. This key pair consists of a public key and a private key. The private key is stored on the tag and does not leave it. Additionally, the public key is stored on the tag which is used to verify the signature. The reader (smartphone) sends a challenge to the tag which signs this challenge using its private key. The generated signature is sent back to the reader where it can be verified using the public key. The authenticity of the public key can be verified by using a certificate which can be e.g. downloaded from the web site of the manufacturer. An introduction to public-key cryptosystems can be found in [RSA78] and a detailed description of the ECDSA is given in [JMV01].

Proof of origin can also be performed using symmetric cryptography. One disadvantage of this method is that the tag and the reader need to share the same secret key [HFP10]. Because of that fact it is easier for an attacker to reveal this secret key. Another disadvantage is that the manufacturer has to handle a lot of secret keys, one for each product group or even for each article. If an attacker can reveal the secret AES key fake products can be produced with a valid proof of origin. On the other hand if an attacker can reveal the private ECDSA key of one tag the manufacturer is able to revoke the certificate of the tag. In the case of revocation the verification of the public key certificate of the tag will fail. It is also possible to define a validity period for certificates. The certificates are only valid within this specific period.

On the CRYPTA tag the symmetric cryptography is mainly used to restrict read and/or write access to certain files. It is also needed during the personalization phase. Only authorized readers are allowed to perform the personalization. The following example shows the lifecycle of the CRYPTA tag.

During the production process the chip gets a unique ID and a temporary AES key. This AES key is for the personalization process and is shared between the chip manufacturer and the manufacturer who wants to protect the goods from imitating. These two files are the only valid files in the EEPROM when the tag leaves the chip manufacturer. All the other bits of the EEPROM are set to 0.

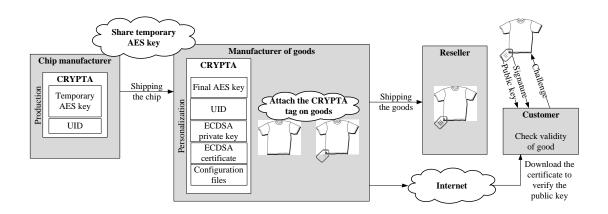

Figure 2.1.: Typical lifecycle of the CRYPTA tag.

The personalization is done by the manufacturer of the goods and works as follows: After a successful authentication using the temporary AES key, the ECDSA private key, the certificate containing the ECDSA public key, the configuration files as well as the final AES key are written to the EEPROM during personalization phase. Setting a special personalization bit finalizes this process. After that the tag can be attached to the goods which can be shipped to the resellers. The resellers sell the articles containing the proof of origin.

If a customer wants to buy a good equipped with a tag the validity can be verified. Figure 2.1 shows the path from the chip manufacturer to the customer.

### 2.4. Hardware Architecture

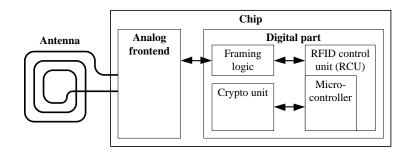

The main parts of the CRYPTA tag are the antenna and the chip. The chip can be split up into an analog part and a digital part. The analog part consists of the analog frontend. The digital part consists of three main components: the framing logic, the RFID control unit (RCU) and the crypto unit (c.f. Figure 2.2). The antenna is connected to the analog frontend which generates the supply voltage and the clock signal from the reader field. It is also responsible for the demodulation of data received from the reader and for modulation of data sent to the reader. The framing logic preprocesses received higher-layer data (ISO 14443-4) for the RCU according to the used standard. Received data from the lower layer (ISO 14443-3) is handled directly by the framing logic. The RCU is the main component of the tag. As one requirement during the planning phase was to build a flexible tag, the RCU contains a programmable microcontroller. The handling of the APDUs for higher layer data and command exchange from and to the reader is also implemented in the RCU. With the microcontroller the different files can be read from the EEPROM and the crypto unit can be controlled. The crypto unit is a special-purpose hardware supporting the Elliptic Curve Digital Signature Algorithm (ECDSA), the Advanced Encryption Standard (AES) and the Secure Hash Algorithm 1 (SHA-1). The focus when designing the crypto unit was on low power consumption and small chip area as these are the main constraints for a passive RFID

device.

Figure 2.2.: The main components on the CRYPTA tag.

### 2.5. Crypto Unit

As mentioned in the previous section the requirements for a passive RFID device are low power consumption and small chip area. In order to meet these requirements a special crypto unit was designed for the CRYPTA chip. The target was to reuse several hardware modules (memory, control) for AES as well as ECDSA. The 8-bit microcontroller of the RCU controls the sequence of the algorithms of the crypto unit [HFW11]. In the next two sections we focus on the implementation of these two primitives.

#### 2.5.1. AES Implementation

The AES implementation supports a fixed key size of 128 bits and encrypting as well as decrypting of data is possible. The 16x8-bit state of AES is expanded to a 16x16-bit state where half of it contains random data. The crypto unit processes the random values in the case of a dummy round. The insertion of dummy rounds is one of the two countermeasures to prevent side-channel analysis attacks (SCA) implemented on the CRYPTA chip. The second countermeasure is shuffling. In the case of shuffling the processing order of the bytes of the state is changed. An 8-bit value is used for the configuration of the countermeasures where the lower four bits specify the number of dummy rounds inserted at the beginning and the upper four bits define the order of the execution of the bytes in the state. More information on countermeasures can be found in the work of Mangard et al. [SM07] and in Section 5.5 of this work. Additional implementation details about the AES algorithm can be found in [HFW11] as well as in [FDW04].

#### 2.5.2. ECDSA Implementation

The EDCSA implementation is based on the recommended NIST Weierstrass elliptic curve (EC) over  $\mathbb{F}_{p192}$ . A standardized curve is used to ensure the interoperability with other

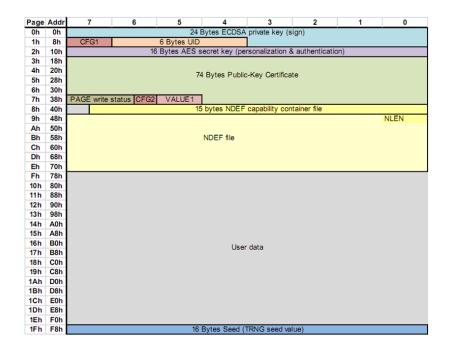

Figure 2.3.: EEPROM layout of the CRYPTA chip.

applications using the same curve and known optimizations for increasing the performance of the algorithm can be used (e.g. the NIST modular reduction [HMV04]). The used curve is analyzed well and it is considered to be secure. During the signature generation also the hash of the message has to be calculated using SHA-1. The hash algorithm implemented on the CRYPTA tag is designed for a fixed input length of 160 bits. With this limitation padding becomes very simple. In order to secure the signature generation the Montgomery ladder was used as scalar multiplication method. A detailed description of the implementation of the ECDSA can be found in the work of Hutter et al. [HFW11].

### 2.6. EEPROM

The following section gives a brief overview of the EEPROM of the CRYPTA chip. Non-volatile data (EC parameters, user data, keys) are stored on the EEPROM. It has a size of 4096 bits in total and is organized in words of 16 bits. Furthermore the EEPROM is partitioned in pages where every page has a size of eight words. At most one page (16 bytes) can be written during one write operation.

#### 2.6.1. EEPROM Layout

The EEPROM is partitioned into 12 files with different access privileges. Figure 2.3 shows the layout in a graphical manner. Table 2.1 lists important features of the different files like file ID, size or read/write restrictions. The following restrictions exist to control reading

operations on files. No read access is allowed at all, read access is always allowed or read access is only allowed after a successful reader authentication (depending on the configuration of the chip). Several restrictions exist for writing the files. Some files can only be written during production and some can only be written during personalization. For other files a lock bit exists, where they can only be modified if this bit is not set. The CFG2 file and the Page RW file can only be modified once (one time programmable).

|              | $\sim$ pers $\sim$ | Bytes           256           74           96 | File for user data<br>Certificate string for<br>ECDSA<br>Contains information for |  |

|--------------|--------------------|-----------------------------------------------|-----------------------------------------------------------------------------------|--|

| ✓<br>✓       | pers ~             | 74                                            | Certificate string for<br>ECDSA                                                   |  |

| ✓            | ~                  |                                               | ECDSA                                                                             |  |

|              |                    | 96                                            | Contains information for                                                          |  |

| x            |                    |                                               | NDEF application                                                                  |  |

|              | pers               | 24                                            | The private key for<br>ECDSA signature                                            |  |

| x            | pers               | 16                                            | The secret key for AES<br>encryption                                              |  |

| $\checkmark$ | prod               | 6                                             | The unique ID of the tag                                                          |  |

| ~            | ~                  | 15                                            | The NDEF capability container file                                                |  |

| $\checkmark$ | pers               | 2                                             | Configuration file 1                                                              |  |

| $\checkmark$ | √*                 | 2                                             | Decrease-only value                                                               |  |

| $\checkmark$ | otp                | 1                                             | Configuration file 2                                                              |  |

| <b>√</b>     | otp                | 3                                             | Lock bits for pages 0x0<br>to 0x1E                                                |  |

|              | pers               | 16                                            | Seed for true random<br>number generator                                          |  |

|              | x                  | x pers                                        |                                                                                   |  |

|                       | <i>o</i> , <b>o</b>                           |

|-----------------------|-----------------------------------------------|

| х                     | <br>no read access                            |

| $\sim$                | <br>write access if lock bit is not set       |

| pers                  | <br>write access only during personalization  |

| $\operatorname{prod}$ | <br>write access only during production       |

| $\operatorname{otp}$  | <br>one time programmable                     |

| $\checkmark^*$        | <br>write access only if new value is smaller |

|                       |                                               |

Table 2.1.: Features of the different files on the chip.

#### 2.6.2. Configuration Files

In this section the files which are needed to configure the chip are explained.

#### Configuration Word 1 (CFG1)

With the CFG1 the clock frequency of the crypto unit can be configured. Also the write

and read access to the different locations in the EEPROM can be controlled. This allows to configure the tag such that a reader authentication is required for read and write operations to all files. A description of the bits of CFG1 can be found in Table 2.2.

| Bit  | Description                                                        |  |  |  |  |  |

|------|--------------------------------------------------------------------|--|--|--|--|--|

| 0    | Configure the clock frequency of the chip                          |  |  |  |  |  |

| 1    | 001.7  MHz, 01848  kHz, 103.4  MHz, 116.8  MHz                     |  |  |  |  |  |

| 2    | Enable AES commands $(1 disabled/0 enabled)$                       |  |  |  |  |  |

| 3    | Enable ECDSA commands $(1disabled/0enabled)$                       |  |  |  |  |  |

| 4    | Enable NFC Type 4 mode (1disabled/0enabled)                        |  |  |  |  |  |

| 5    | Allow permanent disable after external authentication (1do not al- |  |  |  |  |  |

|      | low/0allow)                                                        |  |  |  |  |  |

| 6    | Write to EEPROM only after external authentication                 |  |  |  |  |  |

|      | (1 enabled/0 disabled)                                             |  |  |  |  |  |

| 7    | Read from EEPROM only after external authentication                |  |  |  |  |  |

|      | (1enabled/0disabled)                                               |  |  |  |  |  |

| 8    | Write to Page RW status only after external authentication         |  |  |  |  |  |

|      | (1enabled/0disabled)                                               |  |  |  |  |  |

| 9-15 | RFU                                                                |  |  |  |  |  |

Table 2.2.: Description of the bits of CFG1.

#### Configuration Byte 2 (CFG2)

The CFG2 is one-time programmable. This means that bits that are set to 1 cannot be reset to 0. With the different bits of this byte the tag can be permanently disabled, it can be signalized if the item is sold and it can be switched from evaluation mode to standard mode. If the tag is in evaluation mode the countermeasures against SCA attacks are disabled. In the case of AES this means that no dummy rounds are inserted at the beginning and that the execution order of the bytes from the state is fixed. Setting bit 7 is the last step during personalization, it indicates that the tag is personalized. Setting the sold bit does not change anything in the tag's behaviour. It can be used for an anti-theft system to signalize if the customer has paid for the good. Table 2.3 gives a description of the bits of CFG2. Setting the bits of this configuration file has to be done very carefully because once set they cannot be reset. If for example the standard mode is once activated the mode cannot be changed to evaluation mode any more.

| Bit | Description                                                              |  |  |  |

|-----|--------------------------------------------------------------------------|--|--|--|

| 0   | Permanent disable $(0 \text{tag is enabled}/1 \text{tag is disabled})$   |  |  |  |

| 1   | Item is sold $(0$ item not sold $/1$ item is sold)                       |  |  |  |

| 2-5 | Not used, should be kept to 0                                            |  |  |  |

| 6   | 0 evaluation mode/ $1$ standard mode                                     |  |  |  |

| 7   | Personalization done $(1 \text{personalized}/0 \text{not personalized})$ |  |  |  |

| Table 2.3.: Description | of the | bits of | CFG2. |

|-------------------------|--------|---------|-------|

|-------------------------|--------|---------|-------|

Page RW Status

With the three bytes of the Page RW status file writing to the pages 0x09 to 0x1E can be allowed or not. If for example the first bit is set writing on page 0x09 is not allowed. As it can be seen on the layout of the EEPROM two files are affected from the lock bits, the NDEF file and the user data file.

### 2.7. Supported Commands

The focus in this section is on the description of the supported commands of the CRYPTA chip. Corresponding to the ISO 14443-4 standard the following block commands are supported: S-block commands, R-block commands and I-block commands. The correct coding of the different commands as well as examples can be found in [Int08]. The commands for selection and anticollision are according to ISO 14443A-3[Int01] and will not be explained in detail in this chapter.

#### 2.7.1. S-Block Commands

There are two different S-block commands, one to increase the waiting time of the reader (waiting-time extension) and one to deselect the tag (deselect command):

- S(WTX)... waiting-time extension There is a specific time (frame waiting time FWT) that the reader waits for an answer of the tag before a timeout occurs [Int08]. If the tag performs a time-consuming calculation such as an ECDSA signature generation the FWT is not long enough. In that case the tag sends a S(WTX) to the reader to indicate that the next answer will not arrive within the FWT but within a temporarily-defined time. So a timeout can be prevented.

- S(DESELECT)... deselect command This command is sent by the reader to deselect a specific tag. If the CRYPTA tag receives the S(DESELECT) command it enters the halt state (HLTA).

#### 2.7.2. R-Block Commands

The R-block commands are used to exchange acknowledgments between reader and tag. The acknowledgment always refers to the last received block. RACK indicates a positive acknowledgment and RNAK indicates a negative acknowledgment. In the case of an RNAK the last block is sent again.

#### 2.7.3. I-Block Commands

The I-block commands are used to exchange higher-layer data between tag and reader. This higher-layer data is called application protocol data unit (APDU) and is coded according to the ISO7816-4 standard [Int95]. There is a different structure of the APDUs for requests from the reader to the tag and for responses from the tag to the reader.

Table 2.4 shows the structure of an APDU from the reader to the tag. The class byte CLA denotes the class of the following command (typically 0x00). The instruction to be performed by the tag is given by the instruction byte INS followed by the parameter bytes P1 and P2. With these to bytes parameters for the instruction can be set.  $L_c$  is called the length byte and denotes the length of the following DATA field. The DATA field is optional and if it is empty there is no  $L_c$  byte. The last field  $L_e$  is again one byte long and gives information about the expected length of the tag answer. If no data is expected from the tag no  $L_c$  byte is sent.

| CLA | INS | P1 | P2 | L <sub>c</sub> | DATA | $L_{e}$ |

|-----|-----|----|----|----------------|------|---------|

|     |     |    |    | 0              |      | 0       |

| ag. |

|-----|

|     |

Table 2.5 gives an overview of the different instructions supported by the CRYPTA tag. With the SELECT command a file can be selected using the file ID or the file name. The selected file can be read using the READ BINARY command where P1 and P2 define the offset and  $L_e$  gives the number of bytes to read. With the UPDATE BINARY command the selected file can be modified. Again P1 and P2 are used to define the offset,  $L_c$  gives the number of bytes to write and the DATA field contains the data to write. There is one UPDATE BINARY command for personalization and one for standard operation. The two commands differ in their class byte. The INT AUTHENTICATE (internal authenticate) command is used to authenticate the tag to the reader using AES or ECDSA. There is a difference in the length of the challenge (AES: 8-byte long challenge, ECDSA: 16-byte long challenge) as well as in the expected length of the answer (AES: 16 bytes, ECDSA: 48 bytes). With the EXT AUTHENTICATE (external authenticate) command the reader authenticates to the tag using AES. Before sending an EXT AUTHENTICATE command, the reader has to request a challenge from the tag using the GET CHALLENGE command. This challenge is then encrypted using AES and sent to the tag in the EXT AUTHENTICATE command.

| Command          | CLA  | INS              | P1   | P2   | $L_{c}$ | DATA      | $L_{e}$ |

|------------------|------|------------------|------|------|---------|-----------|---------|

| SELECT file      | 0x00 | 0xA4             |      | 0x00 |         |           |         |

| by ID            |      |                  | 0x00 |      | 0x02    | file ID   | —       |

| by name          |      |                  | 0x04 |      | 0x07    | file name | —       |

| READ BINARY      | 0x00 | $0 \mathrm{xB0}$ | off  | set  | —       | —         | #bytes  |

| UPDATE BINARY    |      | 0xD6             | off  | set  | #bytes  | data      | _       |

| standard write   | 0x00 |                  |      |      |         |           |         |

| personalize      | 0x80 |                  |      |      |         |           |         |

| INT AUTHENTICATE | 0x00 | 0x88             |      | 0x00 |         | challenge |         |

| AES              |      |                  | 0x00 |      | 0x08    |           | 0x10    |

| ECDSA            |      |                  | 0x01 |      | 0x10    |           | 0x30    |

| GET CHALLENGE    | 0x00 | 0x84             | 0x00 | 0x00 | _       | _         | 0x80    |

| EXT AUTHENTICATE | 0x00 | 0x82             | 0x00 | 0x00 | 0x10    | $AES_K$   | _       |

Table 2.5.: The instructions supported by the CRYPTA tag.

Table 2.6 shows the structure of an APDU response from the tag to the reader. The DATA field is optional, depending on the instruction that the reader has selected in the previous

APDU. The length of the DATA field is  $L_e$ . The status of the performed instruction is indicated with a status word which consists of the two bytes SW1 and SW2. With the status word 0x9000 (SW1 = 0x90, SW2 = 0x00) the tag indicates that the requested instruction has been performed successfully. The meaning of other status words can be found in Table 2.7.

| DATA | SW1 | SW2     |

|------|-----|---------|

| 2    | ~ = | ~ • • = |

Table 2.6.: APDU from the tag to the reader.

| $egin{array}{c} { m Status word} \ { m (SW1} \  { m SW2}) \end{array}$ | SELECT | READ BINARY | UPDATE BINARY | INT AUTHENTICATE | GET CHALLENGE | EXT AUTHENTICATE |                               |

|------------------------------------------------------------------------|--------|-------------|---------------|------------------|---------------|------------------|-------------------------------|

| 0x9000                                                                 | х      | x           | X             | х                | х             | х                | ОК                            |

| 0x6A82                                                                 | х      |             |               |                  |               |                  | File/application not found    |

| 0x6982                                                                 | x      | х           | х             | х                |               |                  | Security status not satisfied |

| 0x6D00                                                                 | x      | х           | х             | х                | х             | х                | Command not supported/invalid |

| 0x6282                                                                 |        | x           |               |                  |               |                  | End of file reached           |

| 0x6700                                                                 |        |             | х             |                  |               |                  | Wrong length                  |

| 0x6B00                                                                 |        |             | X             |                  |               |                  | Wrong Parameters              |

| 0x6400                                                                 |        |             | x             | х                | х             |                  | Power-check fail              |

| 0x6581                                                                 |        |             | х             |                  |               |                  | Memory failure during writing |

| 0x6A80                                                                 |        |             |               | x                |               |                  | Wrong parameters              |

Table 2.7.: Status words of the different commands and their meaning.

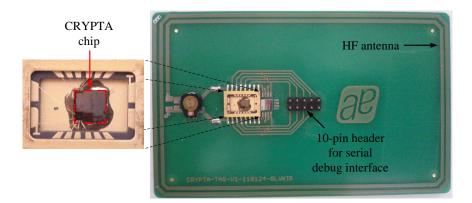

## 2.8. CRYPTA-Chip Test Board

The CRYPTA chip is a prototype and it is mounted on a test board. One advantage of the test board is that the EEPROM content can be changed without any restrictions (e.g. the bits of CFG2 can be set from 1 to 0 again) because there is direct access to the EEPROM via a serial debug interface. The interface is accessible as 10-pin header on the test board and can be connected to a programming board. This programming board is connected to a computer via a USB cable. A special software is used to read and write the content of the EEPROM. Each word can be written and read separately without any restrictions.

Another advantage of the programming board is that it allows to power the tag with an

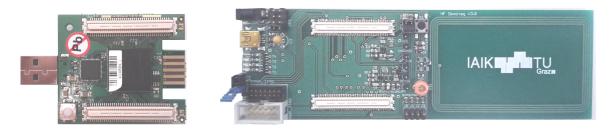

Figure 2.4.: The CRYPTA tag chip with test board for evaluation.

external power supply. In that case the tag does not have to generate the supply voltage from the reader field. This gave us the ability to measure the power consumption of the chip with a resistor in the ground line. Figure 2.4 shows the test board with the chip mounted on it. The size of the board is about 90 mm x 55 mm and is close to the standardized ID-1 format (commonly used for banking cards) of 85.725 mm x 53.975 mm [Int11].

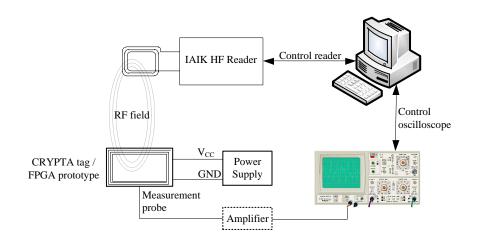

### 2.9. FPGA Prototype

This section gives a short overview of the FPGA prototype of the CRYPTA tag which was used for SCA attacks in order to evaluate the countermeasures. The FPGA prototype is implemented on the IAIK HF FPGA DemoTag. The DemoTag is a programmable RFID tag which appears to the reader as a passive tag. It is convenient for early prototypes of RFID tags in order to test the functionality. It consists of two parts: The motherboard and the FPGA board. The first part is the so-called motherboard (cf. Figure 2.6), where the antenna coil as well as the analog frontend is placed. Also connectors for the power supply are placed on the motherboard. The second part is the board with the FPGA (cf. Figure 2.5) which can be plugged on top of the motherboard. The Xilinx Spartan-3 XC3S1000 [Xil08] FPGA is used on the DemoTag. Although the FPGA DemoTag only works with an external power supply (does not extract the power supply from the reader field) it behaves like a passive RFID tag. The analog frontend extracts the clock signal from the reader field and provides it to the FPGA.

The FPGA implementation of the CRYPTA chip behaves like the real chip which is mounted on the test board. Two errors were found on the real chip (see Chapter 6 and Chapter 7) which were corrected in the FPGA implementation. The impact of the corrections could be tested this way without fabricating a new chip.

More technical details about the HF FPGA DemoTag can be found in the work of Feldhofer et. al [FAH<sup>+</sup>10].

Figure 2.5.: FPGA board.

Figure 2.6.: The motherboard.

# 2.10. Summary

In this chapter we gave a short overview of the project CRYPTA. The main goal of the project is to enable advanced cryptography on passive RFID tags. We first gave an overview of the project followed by some real-world applications. Then the architecture of the chip was described with the focus put on the cryptographic unit and the EEPROM module. Next the supported commands of the chip were explained to enable a reader to communicate with the CRYPTA tag. In the end we discussed the hardware for the SCA attacks presented in Chapter 7, on the one hand the CRYPTA chip test board and on the other hand the FPGA prototype.

# 3. An Introduction to AES

The Advanced Encryption Standard (AES) is the standardized version of the Rijndael algorithm, which is a symmetric block cipher for data encryption and data decryption. The algorithm is standardized in the FIPS-197 document of the National Institute of standards and Technology (NIST) which can be found at [oSN01]. The differences between AES and Rijndael are the different values of supported block length and different possible key lengths described in [JD02].

In the following chapter a short introduction to AES is given. First the parameters for the algorithm are explained. Then the focus is put on the encryption and decryption processes as well as on the transformations used by the algorithm. At the end of this chapter we explain two approaches for attacking implementations of AES.

#### 3.1. Parameters for AES

As input for encryption, a plaintext block with a length of 128 bits and a key are used. Three different key lengths are supported: 128 bits (AES-128), 192 bits (AES-192) and 256 bits (AES-256). The output of an encryption is the ciphertext block with a length of 128 bits. For decryption, a ciphertext block serves as the input for AES together with the key (again the same three key lengths as for encryption are supported) that has been used for encryption of the plaintext. The output here is again the original plaintext block [oSN01].

If the plaintext block is shorter than 128 bits a padding scheme has to be used to expand the plaintext to 128 bits. If the message length is greater than 128 bits then a block-cipher mode of operation has to be used. Several so-called modes of operation can be found in [Dwo01].

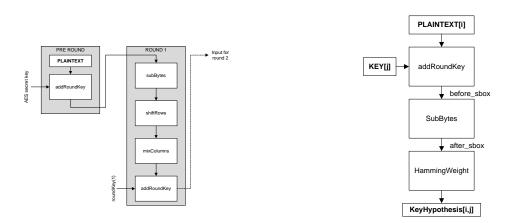

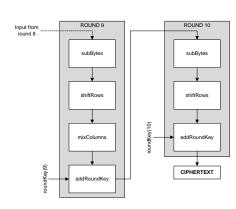

#### 3.2. Encryption Process

AES consists of a defined number  $N_r$  of round transformations on the so called state that depends on the key length  $N_k$ . The size of the state is 128 bits ( $N_s=16$  bytes) which is organized as a 4x4 matrix. For  $N_k=16$  bytes there are  $N_r=10$  rounds, for 24 bytes 12 rounds and for 32 bytes 14 rounds. Additionally there is one initial round at the beginning which does not add to the number of rounds. The final round is also a bit different than the other rounds. One round transformation is skipped in this final round as it can be seen later in this chapter.

All the other rounds consist of the following four transformations: subBytes(), shiftRows(), mixColumns() and addRoundKey(). For every round a new round key is extracted from the cipher key.

- The transformation subBytes() is a byte substitution. It is a nonlinear operation and can be implemented as a table lookup. This transformation is applied bytewise as it can be seen in Figure 3.1. The whole S-box table can be found on page 16 of [oSN01].

- The transformation shiftRows() shifts the rows of the state matrix. Different rows are shifted with a different offset as shown in Figure 3.2.

- The function mixColumns() transforms the state colum by colum, as it can be seen in Figure 3.3. The transformation can be written as a matrix multiplication.

- The addRoundKey() transformation is the last transformation of every round. Every byte of the state is XORed with the corresponding byte of the round key.

Listing 3.1 shows the pseudocode of an AES encryption with a key length of 128 bits (10 rounds). As it can be seen the initial round only consists of a key addition with the original key and in the final round the mixColums() transformation is left out. For every round a new round key is generated. A detailed description of the key expansion function can be found in [JD02] as well as in [oSN01].

```

ciphertext AESEncrypt(plaintext, aeskey)

{

2

load plaintext into state;

3

state = AddRoundKey(aeskey);

for rnd = 1 to 9

ſ

key = expandRoundKey(aeskey, rnd);

8

state = subBytes();

9

state = shiftRows();

10

state = mixColumns();

11

state = addRoundKey(key);

^{12}

}

13

key = expandRoundKey(aeskey, 10);

14

state = subBytes();

15

state = shiftRows();

16

state = addRoundKey(key);

17

18

ciphertext = state;

19

}

20

```

Listing 3.1: Pseudocode for an AES-128 encryption.

#### 3.3. Decryption Process

For decrypting data the inverse cipher with the modified transformations invSubBytes(), invShiftRows() and invMixColumns() as well as addRoundKey() with the inverse key sched-

| S <sub>0,0</sub>  | <b>S</b> <sub>0, 1</sub> | <b>S</b> <sub>0, 2</sub> | <b>S</b> <sub>0, 3</sub> |                             | <b>S'</b> 0, 0           | <b>S'</b> <sub>0, 1</sub> | <b>S'</b> 0, 2            | <b>s'</b> <sub>0, 3</sub> |

|-------------------|--------------------------|--------------------------|--------------------------|-----------------------------|--------------------------|---------------------------|---------------------------|---------------------------|

| S <sub>1,0</sub>  | S <sub>1, 1</sub>        | <b>S</b> <sub>1, 2</sub> | <b>S</b> <sub>1, 3</sub> |                             | s' <sub>1,0</sub>        | <b>s'</b> <sub>1, 1</sub> | <b>s'</b> <sub>1, 2</sub> | <b>s'</b> <sub>1, 3</sub> |

| S <sub>2, 0</sub> | <b>S</b> <sub>2, 1</sub> | S <sub>2, 2</sub>        | <b>S</b> <sub>2, 3</sub> | SubBytes                    | s' <sub>2,0</sub>        | <b>s'</b> <sub>2,1</sub>  | s' <sub>2, 2</sub>        | <b>s'</b> <sub>2, 3</sub> |

| S <sub>3, 0</sub> | <b>S</b> <sub>3, 1</sub> | <b>S</b> <sub>3, 2</sub> | <b>S</b> <sub>3, 3</sub> | SBOX $(s_{r,c}) = s'_{r,c}$ | <b>s'</b> <sub>3,0</sub> | <b>s'</b> <sub>3, 1</sub> | <b>s'</b> <sub>3, 2</sub> | <b>s'</b> <sub>3, 3</sub> |

Figure 3.1.: The subBytes() transformation [oSN01].

| S <sub>0,0</sub>         | S <sub>0, 1</sub>        | <b>S</b> <sub>0, 2</sub> | <b>S</b> <sub>0, 3</sub> |           | S <sub>0, 0</sub>        | <b>S</b> <sub>0, 1</sub> | <b>S</b> <sub>0, 2</sub> | <b>S</b> <sub>0, 3</sub> |

|--------------------------|--------------------------|--------------------------|--------------------------|-----------|--------------------------|--------------------------|--------------------------|--------------------------|

| S <sub>1,0</sub>         | <b>S</b> 1, 1            | <b>S</b> 1, 2            | <b>S</b> <sub>1, 3</sub> | ShiftRows | <b>S</b> <sub>1, 1</sub> | <b>S</b> 1, 2            | <b>S</b> 1, 3            | S <sub>1,0</sub>         |

| <b>S</b> <sub>2, 0</sub> | <b>S</b> <sub>2, 1</sub> | S <sub>2, 2</sub>        | <b>S</b> <sub>2, 3</sub> |           | <b>S</b> <sub>2, 2</sub> | <b>S</b> <sub>2, 3</sub> | S <sub>2,0</sub>         | <b>S</b> <sub>2, 1</sub> |

| <b>S</b> <sub>3, 0</sub> | <b>S</b> <sub>3, 1</sub> | <b>S</b> <sub>3, 2</sub> | <b>S</b> <sub>3, 3</sub> |           | <b>S</b> <sub>3, 3</sub> | <b>S</b> <sub>3, 0</sub> | <b>S</b> <sub>3, 1</sub> | <b>S</b> <sub>3, 2</sub> |

Figure 3.2.: The shiftRows() transformation [oSN01].

| S <sub>0, 0</sub> | <b>S</b> <sub>0, 1</sub> | <b>S</b> 0, 2            | S <sub>0, 3</sub>                |                      |                      |     |                                                                                                          | <b>s'</b> <sub>0,0</sub>                                                                                     | <b>S'</b> 0, 1            | <b>S'</b> 0, 2 | <b>S'</b> 0, 3            |

|-------------------|--------------------------|--------------------------|----------------------------------|----------------------|----------------------|-----|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------|----------------|---------------------------|

| S <sub>1,0</sub>  | <b>S</b> <sub>1, 1</sub> | <b>S</b> <sub>1, 2</sub> | <b>S</b> <sub>1,3</sub>          |                      | MixC                 | - 1 |                                                                                                          | <b>S'</b> 1,0                                                                                                | <b>S'</b> <sub>1,1</sub>  | <b>S'</b> 1, 2 | <b>S'</b> 1, 3            |

| S <sub>2,0</sub>  | <b>S</b> <sub>2, 1</sub> | S <sub>2, 2</sub>        | S <sub>2, 3</sub>                | /                    | MIXC                 | .01 |                                                                                                          | S' <sub>2,0</sub>                                                                                            | <b>s'</b> <sub>2, 1</sub> | <b>S'</b> 2, 2 | <b>S'</b> <sub>2, 3</sub> |

| S <sub>3, 0</sub> | <b>S</b> <sub>3, 1</sub> | <b>S</b> <sub>3, 2</sub> | S <sub>3, 3</sub>                |                      |                      |     |                                                                                                          | <b>S'</b> <sub>3, 0</sub>                                                                                    | <b>S'</b> <sub>3, 1</sub> | <b>S'</b> 3, 2 | <b>S'</b> 3, 3            |

|                   |                          |                          | 02 03<br>01 02<br>01 01<br>01 01 | 01<br>03<br>02<br>01 | 01<br>01<br>03<br>02 | •   | <b>S</b> <sub>0,c</sub><br><b>S</b> <sub>1,c</sub><br><b>S</b> <sub>2,c</sub><br><b>S</b> <sub>3,c</sub> | <b>s'</b> <sub>0,c</sub><br><b>s'</b> <sub>1,c</sub><br><b>s'</b> <sub>2,c</sub><br><b>s'</b> <sub>3,c</sub> | , c                       | = 0.           | 3                         |

Figure 3.3.: The mixColumns() transformation [oSN01].

ule has to be used to get the plaintext again.

In [JD02] two different solutions of the decryption algorithm are shown, the straightforward decryption algorithm and the equivalent decryption algorithm. The difference between the two approaches is the order of the transformations. The straightforward approach simply inverses the encryption algorithm, as it can be seen in the pseudocode in Listing 3.2. Using the equivalent approach it is possible to put the invSubBytes() transformation at the beginning of each round again as it can be seen in Listing 3.3. For hardware implementations it is more convenient to have the nonlinear transformation at the beginning of each round. The type of implementation of the AES decryption (straightforward or equivalent) does not make any difference for side-channel analysis attacks (SCA). For the equivalent decryption algorithm also the key expansion function has to be adapted (eqExpandRoundKey()).

A detailed description why and how the order of the transformations can be changed is given in Chapter 3 of [JD02].

- The transformation invSubBytes() is again a table lookup in the inverse substitution box. This inverse substitution box can be found on page 22 in [oSN01].

- The transformation invShiftRows() cyclically shifts the second, third and fourth row of the state for one, two and three positions. The shift direction is now opposite to the direction of ShiftRows().

- The transformation invMixColumns() works on each column separately just like mixColumns() but using a different matrix. The transformation as well as the matrix can be seen in Fig. 3.4.

| S <sub>0,0</sub>         | S <sub>0, 1</sub>        | <b>S</b> <sub>0, 2</sub> | <b>S</b> <sub>0, 3</sub> |              |                      |             |   | <b>S'</b> 0, 0                                                               | <b>s'</b> <sub>0, 1</sub> | <b>S'</b> 0, 2 | <b>s'</b> <sub>0, 3</sub> |

|--------------------------|--------------------------|--------------------------|--------------------------|--------------|----------------------|-------------|---|------------------------------------------------------------------------------|---------------------------|----------------|---------------------------|

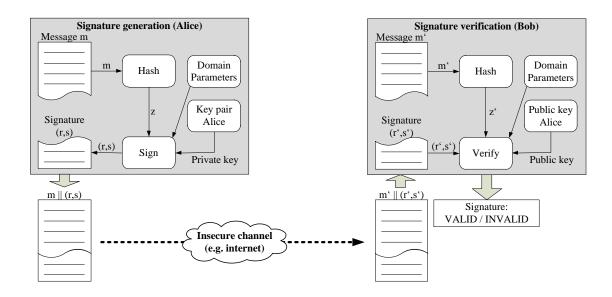

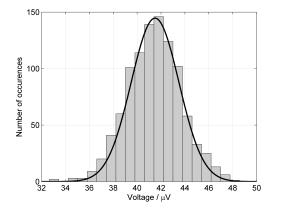

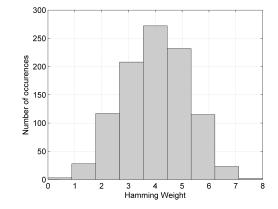

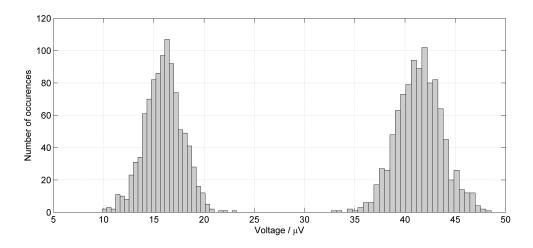

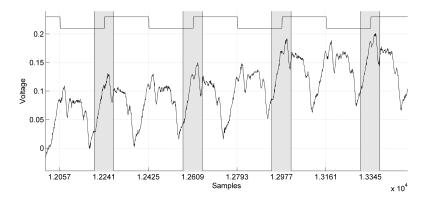

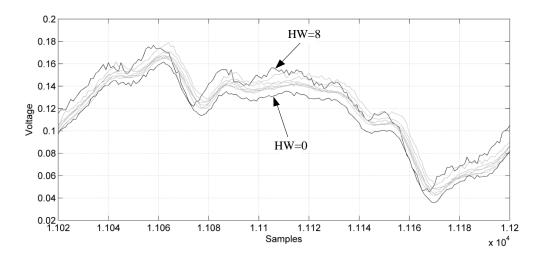

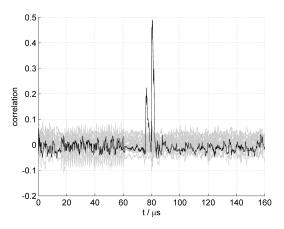

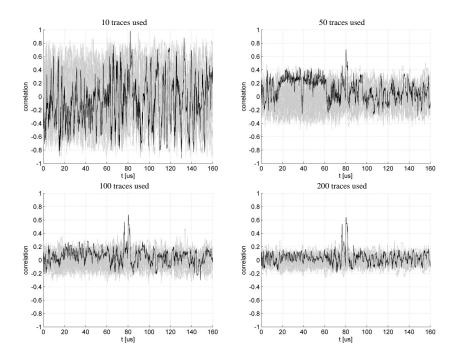

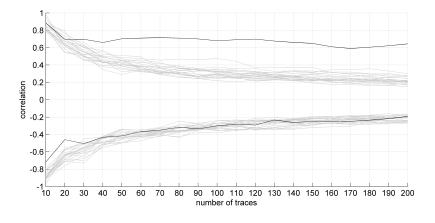

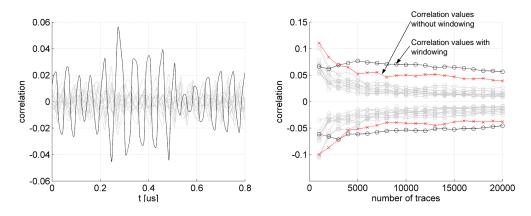

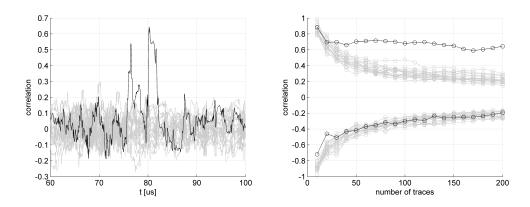

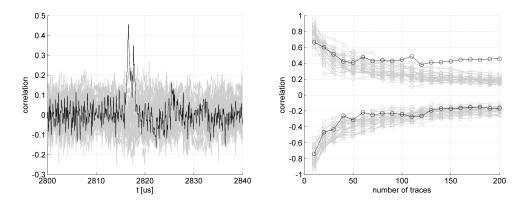

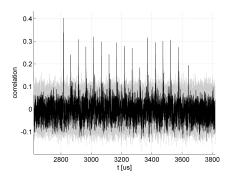

| <b>S</b> <sub>1,0</sub>  | <b>S</b> <sub>1, 1</sub> | <b>S</b> 1, 2            | <b>S</b> 1, 3            |              | TorMi                | xColumns    | ^ | <b>S'</b> 1,0                                                                | <b>S'</b> 1,1             | <b>S'</b> 1, 2 | <b>s'</b> <sub>1,3</sub>  |