### Elliptic-Curve Cryptography Implementation for Passive RFID Tags

Thomas Lenz t.kern@student.tugraz.at

Institute for Applied Information Processing and Communications (IAIK) Graz University of Technology Inffeldgasse 16a 8010 Graz, Austria

### A Master Thesis

Supervisor: Dipl-Ing. Dr. techn. Michael Hutter Supervisor: Dipl-Ing. Dr. techn. Martin Feldhofer

Assessor: Ao.Univ.-Prof. Dipl.-Ing. Dr.techn. Karl Christian Posch

September, 2011

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommene Stellen als solche kenntlich gemacht habe.

Graz, am 13.09.2011

Thomas Lenz

# Acknowledgements

At first, I would like to thank my supervisors Michael Hutter and Martin Feldhofer for advising this master thesis. Many thanks also go to the Institute for Applied Information Processing and Communications (IAIK).

A special thank goes to my wife Andrea for supporting me in various ways during the years of study. Furthermore, I thank my family for supporting me during the study and especially my brother Wolfgang for proof-reading this work.

### Abstract

Radio-frequency identification (RFID) technology becomes more and more interesting for safety-related applications. Such applications, like e-passports or access control require a secure authentication process to check if the RFID tag and the corresponding product is valid or counterfeit. The elliptic-curve digital signature algorithm (ECDSA) uses asymmetric cryptography to generate a digital signature which can be used for authentication. An advantage of elliptic-curve cryptography (ECC) is the short key length in comparison to other public-key systems like RSA. Therefore, ECC is well suitable for RFID applications.

In this thesis, we design an elliptic-curve processor with full ECDSA functionality. This ECDSA implementation is based on the recommended  $\mathbb{F}_{P160}$  Standards for Efficient Cryptography Group (SECG) elliptic curve  $SECP160_{r1}$ , which has only 160 bits in contrast to the smallest recommended National Institute of Standards and Technology (NIST) elliptic curve with 192 bits. This 160-bit elliptic curve is well suitable for a low-area implementation. In order to fulfill the fierce constraints with respect to power consumption and chip area, we use a 16-bit datapath. Therefore, an implementation of all required algorithms on word level is necessary. Additionally, we implement a new field-multiplication algorithm with implicit fast reduction modulo the special prime  $\mathbb{F}_{P160}$ . Furthermore, this is basically the first ECDSA implementation in hardware, which is optimized for low power and low area and which uses the prime  $SECP160_{r1}$  from SECG.

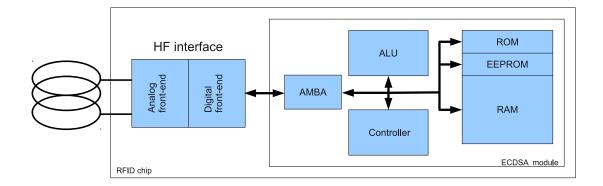

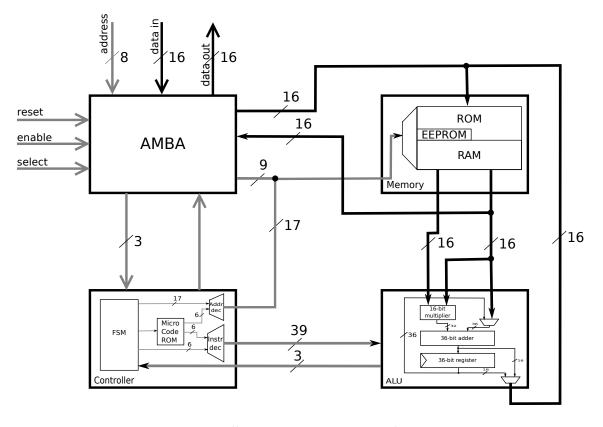

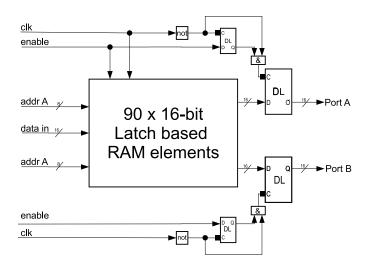

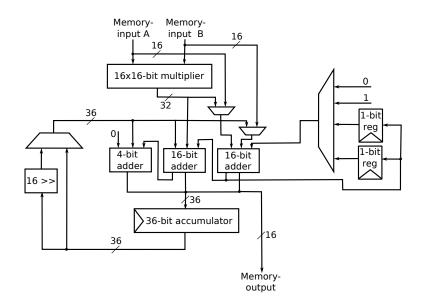

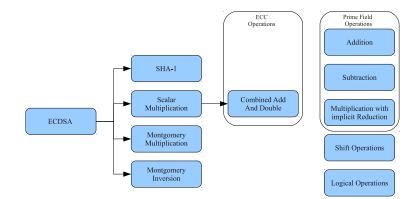

This hardware module consists of four submodules. A memory module, which comprised a latch based  $90 \times 16$ -bit dual-port RAM, a  $83 \times 16$ -bit ROM, and a  $10 \times 16$ -bit EEPROM. The main part of the arithmetic-logic unit is a  $16 \times 16$ -bit multiply-accumulate unit, which can calculate a  $16 \times 16$ -bit multiplication and a 36-bit addition within one clock cycle. We use a hybrid control-unit architecture, which means that our controller consists of a finite-state machine and also micro-coded parts. An AMBA interface is used for interconnection with other hardware modules.

The ECDSA module has been synthesized by using digital standard-cells from c35b4 CMOS libraries published by Austriamicrosystem AG. Our module requires a chip area of 18315 GE and can generate an ECDSA digital signature within 510 831 clock cycles. The power consumption has been ascertained by using a near-spice simulator at which one signature-generation operation requires  $1\,108.0\,\mu\text{W}@1\,\text{MHz}$  with a supply voltage of  $3.5\,\text{V}$ .

**Keywords:** ECDSA, electronic signature, RFID, elliptic-curve cryptography, prime-field arithmetic, low-power processor, low-area processor, SECP160.

## Kurzfassung

Radiofrequenz-Identifikationstechnologie (RFID) wird auch für sicherheitsrelevante Anwendungen immer interessanter. Solche Anwendungen, wie elektronische Reisepässe oder Zugangskontrollsysteme, benötigen ein sicheres Authentifizierungsverfahren um überprüfen zu können ob ein RFID-Transponder und das dazugehörige Produkt gültig oder gefälscht sind. Der Algorithmus zur Erstellung digitaler Unterschriften mithilfe elliptischer Kurven (ECDSA) verwendet asymmetrische Kryptografie um eine digitale Unterschrift, welche zur Authentifizierung verwendet werden kann, zu erstellen. Ein Vorteil der elliptischen Kurven Kryptografie (ECC) ist die kürzere Schlüssellänge im Vergleich zu anderen Verschlüsselungssystemen mit öffentlichem Schlüssel, wie RSA. Daher ist ECC für den Einsatz in RFID Anwendungen gut geeignet.

In dieser Masterarbeit designen wir einen Prozessor für elliptische Kurven mit vollständiger ECDSA funktionalität. Diese ECDSA-Implementierung beruht auf der von der Gruppe für Standards für effiziente Kryptografie (SECG) empfohlenen elliptischen Kurve  $SECP160_{r1}$ , welche nur 160 bits im Gegensatz zur kürzesten empfohlenen elliptischen Kurve des Nationalen Instituts für Standards und Technologie (NIST) mit 192 bits hat. Diese elliptische Kurve mit 160 bits ist gut für eine flächensparende Implementierung verwendbar. Um die anspruchsvollen Auflagen, bezüglich Leistungsbedarf und Chip Fläche erfüllen zu können, verwendeten wir einen 16-bit Datenpfad. Somit ist eine Implementierung aller benötigen Algorithmen auf Wortebene nötig. Zusätzlich implementierten wir einen neuen Feld-Multiplikationsalgorithmus mit eingeschlossener schneller Reduktion modulo der speziellen Primzahl  $\mathbb{F}_{P160}$ . Darüber hinaus ist das die erste ECDSA-Implementierung in Hardware, welche auf einen geringen Leistungsbedarf und einen geringen Flächenbedarf optimiert ist und die die Primzahl  $SECP160_{r1}$  von SECG verwendet.

Diese Hardwarebaugruppe besteht aus vier Untermodulen. Einer Speicherbaugruppe, welche ein auf Latch basierendes  $90 \times 16$ -bit RAM mit zwei Anschlüssen, einen  $83 \times 16$ -bit ROM und einen  $10 \times 16$ -bit EEPROM beinhaltet. Das gröte Element im Rechenwerk ist eine  $16 \times 16$ -bit Multipliziereinheit, welche eine  $16 \times 16$ -bit Multiplikation und eine 36-bit Addition in einem Taktzyklus rechnen kann. Wir verwenden eine Kontrolleinheit mit einer gemischten Architektur, welche sowohl aus einem endlichen Zustandsautomat als auch aus einem speicherprogrammierten Teile besteht. Als Verbindung zu anderen Baugruppen wird eine AMBA-Schnittstelle eingesetzt.

Die ECDSA-Baugruppe wurde unter Verwendung von digitalen Standardzellen aus der CMOS Bibliothek c35b4, herausgegeben durch die Austriamicrosystem AG, aufgebaut. Diese Baugruppe benötigt eine Modulfläche von 18 315 GEs und kann eine ECDSA digitale Unterschrift in 510 831 Taktzyklen erzeugen. Der Leistungsbedarf wurde mit Hilfe eines spice-nahen Simulators ermittelt, wobei ein Arbeitsvorgang zur Unterschriftenerzeugung 1 108.0  $\mu$ W@1 MHz bei einer Versorgungsspannung von 3.5 V benötigt.

**Stichwörter:** ECDSA, elektronische Signatur, RFID, elliptische Kurven Kryptografie, Primkörper Arithmetik, leistungssparend, flächensparend, Prozessor, SECP160.

# Contents

| 1        | <b>Intr</b><br>1.1<br>1.2 | Motivation                                 | <b>1</b><br>1<br>3 |

|----------|---------------------------|--------------------------------------------|--------------------|

| 2        | Rad                       | lio-Frequency Identification               | 4                  |

| _        | 2.1                       |                                            | 4                  |

|          | 2.2                       |                                            | 5                  |

|          |                           | 0                                          | 5                  |

|          |                           |                                            | 7                  |

|          |                           |                                            | 8                  |

| 3        | Aut                       | hentication Protocols                      | 1                  |

|          | 3.1                       |                                            | 1                  |

|          | 3.2                       |                                            | 2                  |

|          | 3.3                       |                                            | 3                  |

|          | 3.4                       |                                            | 5                  |

| 4        | Mat                       | thematical Basics for ECDSA 1              | 7                  |

|          | 4.1                       |                                            | 7                  |

|          |                           | 4.1.1 Addition and Subtraction             | 9                  |

|          |                           |                                            | 20                 |

|          |                           | *                                          | 24                 |

|          |                           | 4.1.4 Inversion                            | 28                 |

|          | 4.2                       | Elliptic-Curve Arithmetic                  | 33                 |

|          |                           |                                            | 84                 |

|          |                           |                                            | 35                 |

|          |                           | *                                          | 88                 |

|          | 4.3                       | *                                          | 13                 |

| <b>5</b> | Imp                       | Dementation of the ECDSA Hardware Module 4 | 6                  |

|          | $5.1^{-1}$                | Overview                                   | 6                  |

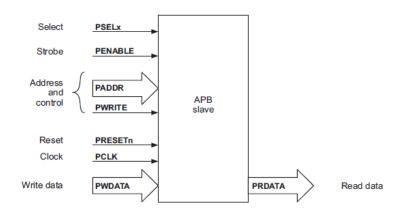

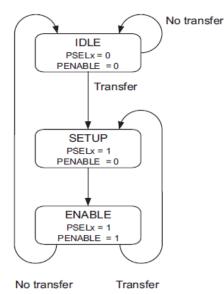

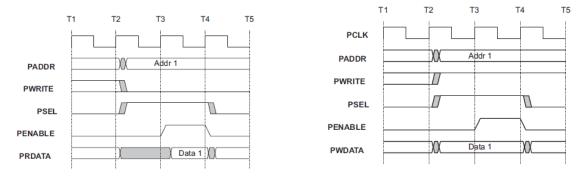

|          | 5.2                       | APB Interface                              | 18                 |

|          | 5.3                       |                                            | 19                 |

|          |                           | 5.3.1 RAM                                  | 51                 |

|          | 5.4                       |                                            | 54                 |

|          |                           | J ( )                                      | 55                 |

|          |                           | *                                          | 66                 |

|          |                           |                                            | 66                 |

|              | 5.5   | Control Machine                                                                                            | 57 |

|--------------|-------|------------------------------------------------------------------------------------------------------------|----|

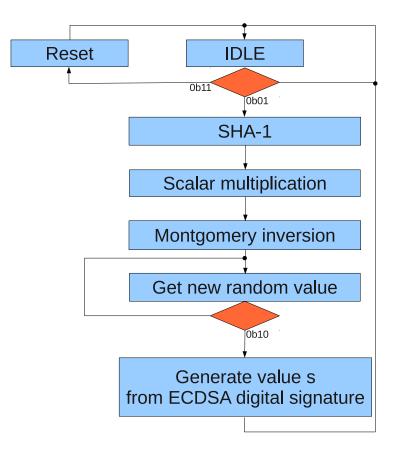

|              |       | 5.5.1 Finite-State Machine (FSM)                                                                           | 57 |

|              |       | 5.5.2 Microprogramming                                                                                     | 58 |

|              | 5.6   | Countermeasure against SPA, DPA, and Timing Analysis                                                       | 59 |

|              | 5.7   | Low-Power Optimization                                                                                     | 61 |

|              | 5.8   | Results                                                                                                    | 63 |

|              |       | 5.8.1 Functional $\ldots$ | 63 |

|              |       | 5.8.2 Synthesis $\ldots$  | 64 |

|              |       | 5.8.3 Summary and Comparison                                                                               | 69 |

| 6            | Con   | clusions                                                                                                   | 71 |

|              | 6.1   | Optimizations and Outlook                                                                                  | 72 |

| $\mathbf{A}$ | Defi  | initions                                                                                                   | 73 |

|              | A.1   | Abbreviations                                                                                              | 73 |

|              | A.2   | Used Symbols and Operations                                                                                | 74 |

| Bi           | bliog | graphy                                                                                                     | 75 |

# List of Figures

| 2.1  | Schematic of a basic RFID system                                       | 4              |

|------|------------------------------------------------------------------------|----------------|

| 2.2  | Basic layout of an RFID transponder [18]                               | 5              |

| 2.3  | Block diagram of an RFID chip.                                         | 6              |

| 2.4  | Layout of a glass transponder [18]                                     | 6              |

| 2.5  | Example of a key-fob transponder [18]                                  | 7              |

| 2.6  | A smart-label on a luggage [18]                                        | $\overline{7}$ |

| 2.7  | A smart-label transponder [18].                                        | 7              |

| 2.8  | Block diagram of a passive transponder [18]                            | 8              |

| 2.9  | Block diagram of an active transponder [18]                            | 8              |

| 2.10 | Frequency spectrum of RFID systems.                                    | 10             |

| 3.1  | Authentication protocol with ECDSA                                     | 13             |

| 3.2  | Schnorr's identification scheme [34].                                  | 14             |

| 3.3  | Okamoto's identification scheme [34]                                   | 15             |

| 4.1  | Representation of $a \in \mathbb{F}_p$ as an array $A$                 | 19             |

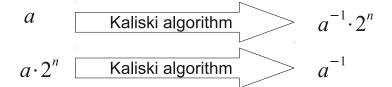

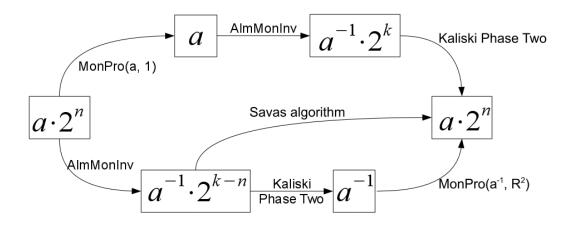

| 4.2  | Input/output behavior for Kaliski algorithm [23]                       | 31             |

| 4.3  | Different ways to compute the Montgomery inversion [23]                | 32             |

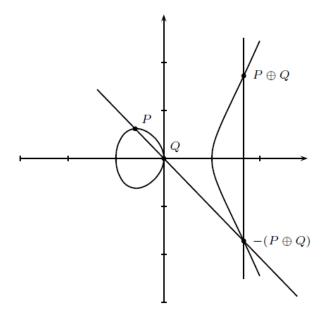

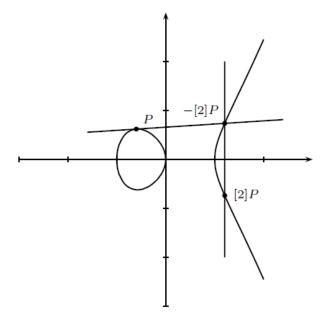

| 4.4  | Geometric addition of EC points [12].                                  | 34             |

| 4.5  | Geometric doubling of EC points [12]                                   | 35             |

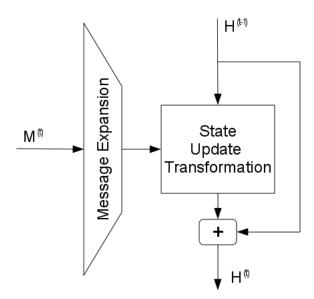

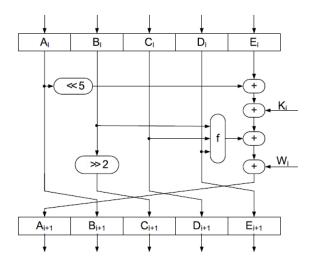

| 4.6  | Overview of the SHA-1 compression function.                            | 43             |

| 4.7  | One step of the state update transformation [15]                       | 44             |

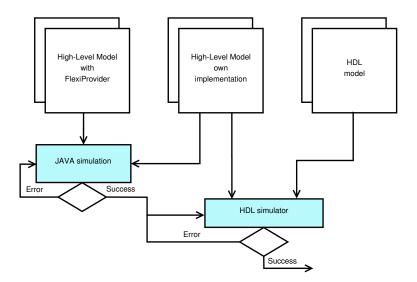

| 5.1  | Verification process between different models.                         | 46             |

| 5.2  | Elliptic-curve processor architecture.                                 | 47             |

| 5.3  | APB slave interface description [39]                                   | 48             |

| 5.4  | APB state diagram [39].                                                | 49             |

| 5.5  | APB read operation [39].                                               | 50             |

| 5.6  | APB write operation [39]                                               | 50             |

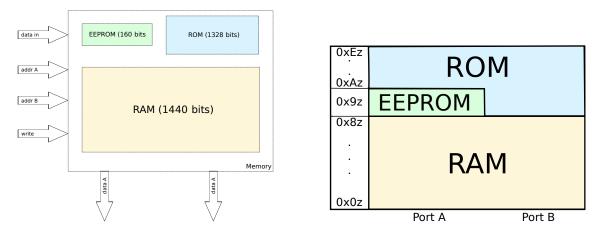

| 5.7  | Memory overview.                                                       | 51             |

| 5.8  | Memory address space                                                   | 51             |

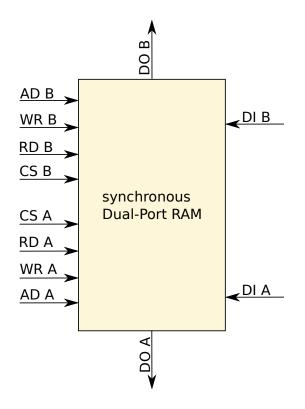

| 5.9  | Synchronous dual-port RAM schematic (taken from Austriamicrosystem     |                |

|      | AG [2])                                                                | 52             |

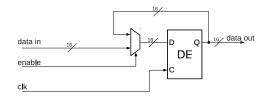

|      | Ordinary 16-bit RAM element with D-Type Flip Flop                      | 53             |

| 5.11 | Clock gated 16-bit RAM element with D-Type Flip Flop.                  | 53             |

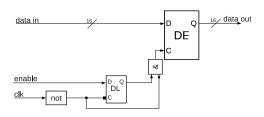

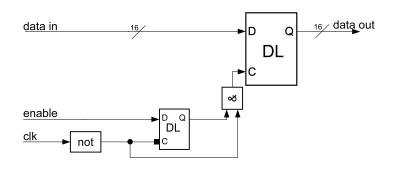

| 5.12 | Latch-based 16-bit RAM element.                                        | 53             |

| 5.13 | Asynchronous read / synchronous write latch-based RAM                  | 54             |

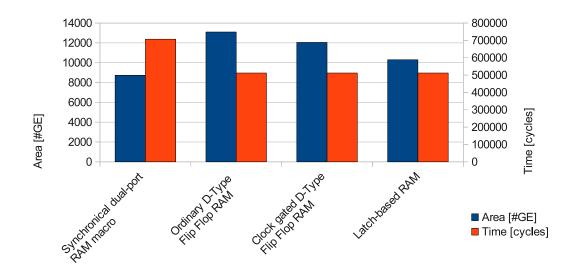

| 5.14 | Comparison of different RAM architectures - area and time requirements | 54             |

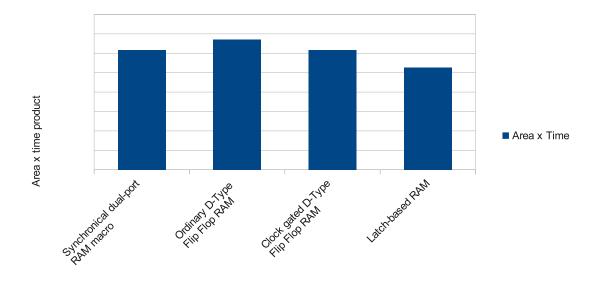

| 5.15 | Comparison of different RAM architectures - area/time product          | 55             |

| Multiply-accumulate unit.                                                        | 55                |

|----------------------------------------------------------------------------------|-------------------|

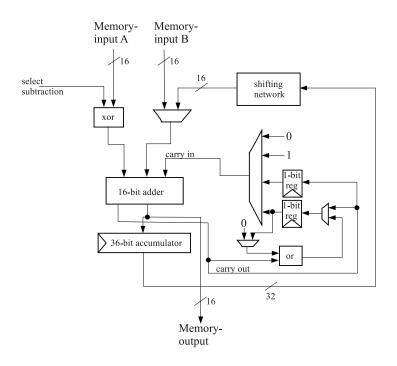

| 16-bit adder unit                                                                | 56                |

| Hierarchical structure of the control unit.                                      | 57                |

| Overview of the finite-state machine                                             | 58                |

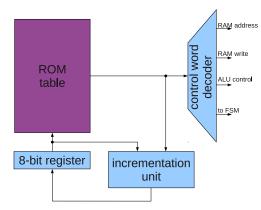

| Overview of micro-coded control unit without feedback signals                    | 59                |

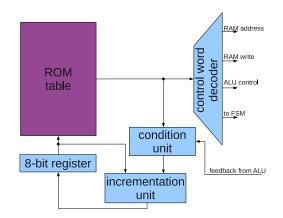

| Overview of micro-coded control unit with feedback signals                       | 59                |

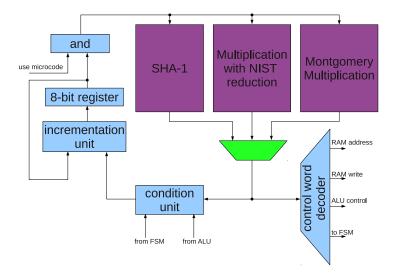

| Micro-coded part of the control unit.                                            | 60                |

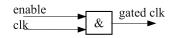

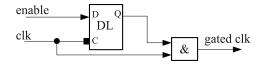

| Clock gating with an AND gate.                                                   | 62                |

| Clock gating with a clock-gating cell.                                           | 62                |

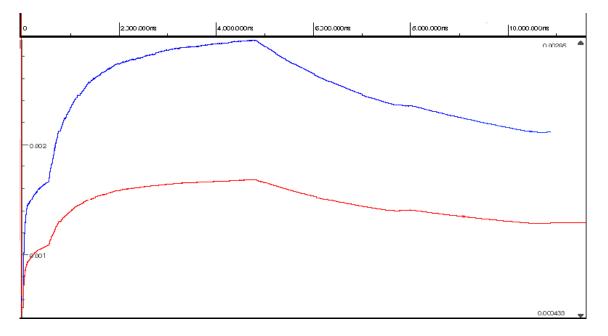

| Operand isolation benefit (simulation with $V_{DD} = 3.3$ V and $f = 5$ MHz).    | 63                |

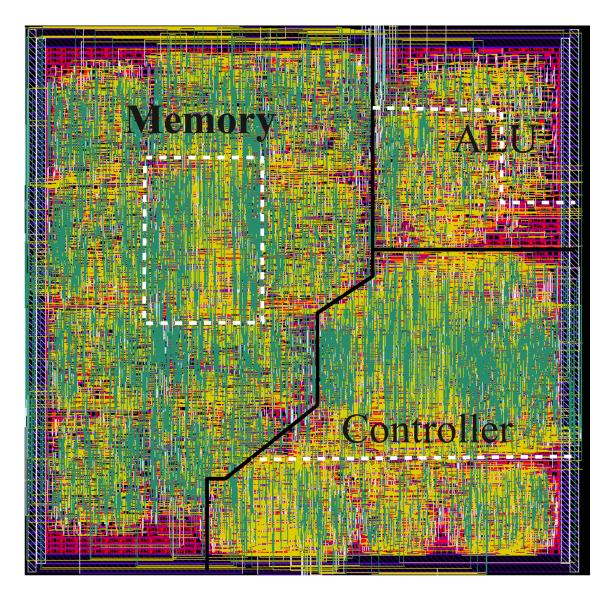

| Layout after place-and-route.                                                    | 65                |

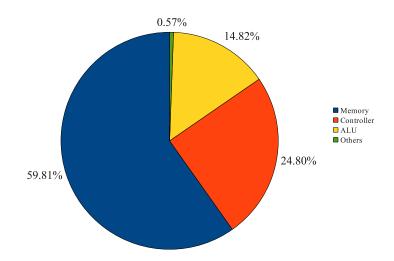

| Chip area of the ECDSA module                                                    | 66                |

| Area requirements of the control unit sub-modules                                | 66                |

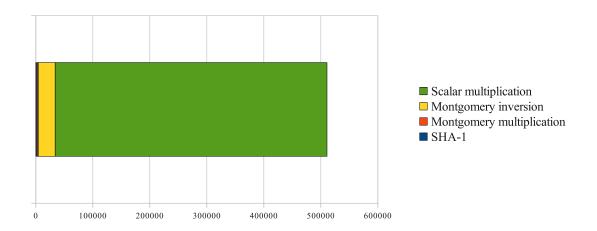

| Cycle count of the combined Double-and-Add algorithm                             | 67                |

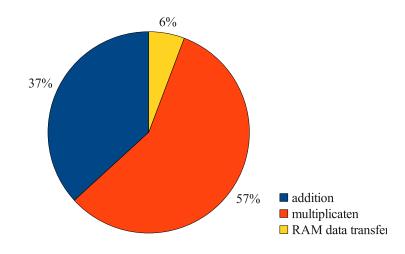

| Cycle-count distribution for the full ECDSA signature generation.                | 67                |

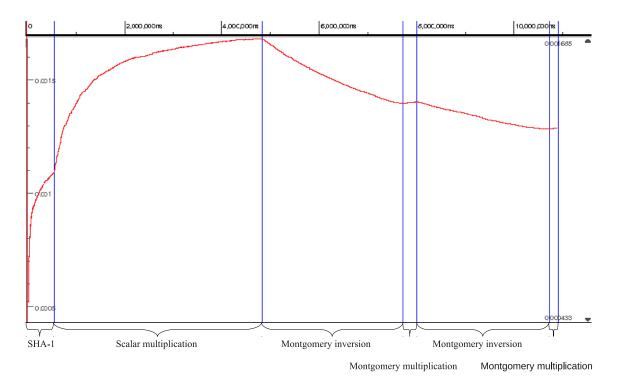

| Current of a signature-generation process with $V_{DD} = 3.3$ V and $f = 5$ MHz. | 68                |

|                                                                                  | 16-bit adder unit |

# List of Tables

| 1.1 | Summarization of our results $V_{DD} = 3.3$ V                              | 2  |

|-----|----------------------------------------------------------------------------|----|

| 4.1 | Time requirements of Montgomery multiplication methods                     | 23 |

| 4.2 | Operation counts for point addition and doubling on $E(\mathbb{F}_p)$      | 38 |

| 4.3 | Secure hash algorithm properties [19]                                      |    |

| 5.1 | APB memory mapped I\O specification.                                       | 50 |

| 5.2 | ROM address space.                                                         | 51 |

| 5.3 | Comparison of different RAM architectures                                  | 53 |

| 5.4 | Chip area of the ECDSA module for a clock frequency of 5 MHz               | 64 |

| 5.5 | Area requirements of the ALU sub-modules                                   | 65 |

| 5.6 | Cycle-count distribution for the full ECDSA signature algorithm.           | 67 |

| 5.7 | Power consumption for different operation conditions and a clock frequency |    |

|     | of 5 MHz.                                                                  | 69 |

| 5.8 | Comparison of our ECDSA module to related work.                            | 69 |

| 5.9 | Synthesis results with a $180nm$ technology from $UMC$                     | 70 |

| 6.1 | Summarization of our results $V_{DD} = 3.3$ V                              | 72 |

# List of Algorithms

| 3.1  | ECDSA digital signature generation, cf. [3]                                                               | 12 |

|------|-----------------------------------------------------------------------------------------------------------|----|

| 3.2  | Key pair generation, cf. [24]                                                                             | 13 |

| 3.3  | ECDSA digital signature verification, cf. [24]                                                            | 14 |

| 4.1  | Addition of multi-word integers.                                                                          | 19 |

| 4.2  | Addition in $\mathbb{F}_p$                                                                                | 20 |

| 4.3  | Subtraction in $\mathbb{F}_p$                                                                             | 20 |

| 4.4  | Multiplication in $\mathbb{F}_p$ - operand-scanning form                                                  | 21 |

| 4.5  | Multiplication in $\mathbb{F}_p$ - product-scanning form                                                  | 21 |

| 4.6  | Montgomery multiplication algorithm.                                                                      | 22 |

| 4.7  | Our improved Montgomery multiplication algorithm (16-bit word size)                                       | 24 |

| 4.8  | Multiplication with implicit fast reduction modulo $p_{160r1}$                                            | 25 |

| 4.9  | Barrett reduction algorithm                                                                               | 26 |

| 4.10 | Fast reduction modulo $p_{160k1} = 2^{160} - 2^{32} - 2^{14} - 2^{12} - 2^9 - 2^8 - 2^7 - 2^3 - 2^2 - 1.$ | 29 |

| 4.11 | Fast reduction modulo $p_{160r1} = 2^{160} - 2^{31} - 1$                                                  | 29 |

| 4.12 | Extended Euclidean algorithm for integers.                                                                | 30 |

| 4.13 | Inversion in $\mathbb{F}_p$ using the extended Euclidean algorithm                                        | 30 |

| 4.14 | Binary algorithm for inversion in $\mathbb{F}_p$                                                          | 31 |

| 4.15 | Almost-Montgomery inverse (Kaliski phase one)                                                             | 32 |

| 4.16 | Kaliski phase two.                                                                                        | 32 |

| 4.17 | Double-and-Add algorithm for scalar multiplication.                                                       | 38 |

| 4.18 | Always Double-and-Add algorithm for scalar multiplication                                                 | 39 |

| 4.19 | Montgomery ladder algorithm for scalar multiplication.                                                    | 40 |

|      | Own improved combined Double-and-Add algorithm                                                            | 42 |

| 4.21 | SHA-1 state update transformation.                                                                        | 45 |

# Chapter 1 Introduction

This thesis presents the design and implementation of an elliptic-curve processor which can generate an elliptic-curve digital signature. In the first section of this chapter, we give a motivation for this work. In the second section, we present our contribution to this topic and give an outline of the following chapters.

### 1.1 Motivation

Radio-Frequency Identification (RFID) technologies become interesting for more and more areas in our daily life. They are not only used for anti-theft protection systems and inbound and outbound logistic systems but also for door-locking applications, micropayment systems, or anti-counterfeiting purposes. An RFID system mostly consist of an RFID transponder (a tiny microchip attached to an antenna) and a reader. Usually a so called passive RFID transponder is used for door-locking applications and micropayment systems, which means that only an electromagnetic field is used to supply the RFID transponder with power and to communicate with it. This electromagnetic field is generated by the reader and only RFID transponders which are in the reading range of the reader can be used. The reading range varies from a few millimeters up to three meters for passive transponders but the power which is available on the RFID transponder decreases sharply with distance to the reader. Consequently, an RFID transponder should need less power as possible. Most RFID applications, like for anti-counterfeiting purposes, require a high number of transponders. Therefore, transponders should be as cheap as possible to be applicable in practice. The microchip on a transponder should meet low-area requirements, because the price of an RFID transponder corresponds directly with the required area of the microchip.

If we use RFID technology for security-related applications, such as door-locking applications, micro-payment systems, or anti-counterfeiting purposes, then a cryptographic secure authentication protocol is required. That can be done by using symmetric or asymmetric cryptography. Symmetric cryptography means that all members of the authentication protocol (prover and verifier) use the same cryptographic key and they can use them for signing or verifying operations. In contrast to symmetric cryptography, asymmetric cryptography uses an associated key pair which consist of a private key and a public key. The public key can be used by everyone for verification purposes, but only the prover knows his own private key and can use it for signing operations. Therefore, asymmetric cryptography is a good choice for an authentication system which is used by a lot of

members, because the key distribution and the key management is easier. But asymmetric cryptography is much more intricate than symmetric cryptography, because the algorithms which are used for asymmetric cryptography are mostly more complex. There exist many cryptographic principles, which use asymmetric cryptography, but currently only two are mostly used. These two are RSA and elliptic-curve cryptography (ECC). An advantage of ECC is the shorter key length in comparison to RSA. Elliptic-curve cryptography with a key length of 160 bits is as secure as RSA with a key length of 1024 bits, cf. [46]. A second advantage of ECC is that a more efficient hardware implementation in comparison to established RSA implementations are possible. Therefore, elliptic-curve cryptography is a good choice for an authentication system in combination with RFID technology.

This thesis focuses on an authentication and confidentiality system which requires low power and low area to fulfill RFID-system requirements. So far, the field of research in case of elliptic-curve cryptography, which is optimized for low-power and low-area implementations, goes into two directions. The first one implements only basic elliptic-curve operations with arithmetic in a binary finite field, like  $\mathbb{F}_{2^{163}}$ , but they did not implement a digital signature-protocol. Some examples of such implementations are given by Hein et al. [25] and Lee et al. [38], which implemented an identification scheme. The second direction goes towards a full ECDSA implementation by using elliptic-curve cryptography with arithmetic in a prime finite field. Such implementations are shown by Wolkerstorfer et al. [56], Auer [4], Hutter et al. [26], and Wenger et al. [54]. They all used the prime field  $\mathbb{F}_{P192}$ , which is the smallest recommended prime standardized by the National Institute of Standards and Technology (NIST) [45]. This prime has a special characteristic which allows to implement a fast reduction algorithm, the so-called NIST reduction [45].

In our work, we use an elliptic curve which is defined over the prime field  $\mathbb{F}_{P160}$ . This elliptic curve is standardized by the Standards for Efficient Cryptography Group (SECG) [48] and has only 160 bits, instead of 192 bit of the smallest NIST elliptic curve. Therefore, this prime from SECG should be better for a low-area optimized implementation and we think the security level of 80 bits should be reasonable for passive RFID systems. At first, it is necessary to evaluate the prime field  $\mathbb{F}_{P160}$ , because there exist no fast reduction algorithm in the literature. But the prime  $\mathbb{F}_{P160}$  belongs to the family of generalized Mersenne numbers and Jerome Solinas [53] proposed a technique to find a fast reduction algorithm for this group of primes. Afterward, we implement the full ECDSA digital signature algorithm, which uses the elliptic curve from SECG. Table 1.1 gives a brief overview of our implementation results. At last, we compare our implementation results with existing results to find advantages or disadvantages of this elliptic-curve implementation. This work is the first one which uses the elliptic curve  $\mathbb{F}_{P160}$ , for a low-area and low-power optimized hardware implementation.

| Technology             | Area        |       | Runtime  | Power                  | $\mathbf{f}_{\max}$ |

|------------------------|-------------|-------|----------|------------------------|---------------------|

| Technology             | $[\mu m^2]$ | [#GE] | [cycles] | $[\mu W]$              | [MHz]               |

| ECDSA $0.35 \mu m$ AMS | 1007334     | 18315 | 510831   | $1108.0@1\mathrm{MHz}$ | 70                  |

Table 1.1: Summarization of our results  $V_{DD} = 3.3$ V

### 1.2 Outline

Chapter 2 gives a brief introduction into RFID. There is a short description about construction formats, energy supply, and reading ranges of RFID systems.

Chapter 3 presents the elliptic-curve digital signature algorithm (ECDSA) and gives some introduction about key generation. Additionally, we present two other identification schemes and discuss some advantages and disadvantages of these three protocols.

The following Chapter 4 gives some information about finite fields. Here, we discuss different algorithms for basic arithmetical operations in finite fields and we present a fast multiplication algorithm for the special prime  $\mathbb{F}_{P160}$ . The central part of Chapter 4 gives information about elliptic curves and arithmetic on elliptic curves. It presents all used algorithms for elliptic-curve arithmetic and discusses some improvements which we have done. Chapter 4 is closed by a short introduction into the secure hash standard (SHA-1), because SHA-1 is defined as hash function for the ECDSA digital-signature algorithm.

In Chapter 5, we give a detailed description of the implementation process and the used architecture. First, there is an overview of the user interface and the I/O specification of the ECDSA processor. Afterwards, we discuss different memory architectures and present the datapath, the main components of the arithmetic-logic unit (ALU) and the control machine. Also some information about side-channel attacks and methods for low-power optimization are given. Chapter 5 is closed by presenting the results of our ECDSA module implementation and we compare our implementation with other related work.

Chapter 6 concludes this thesis and gives some aspects for optimizations and future work.

### Chapter 2

# **Radio-Frequency Identification**

Radio-Frequency Identification (RFID) becomes interesting for more and more areas like automatic-identification techniques, inbound and outbound logistics, product tracking or authentication techniques. The market for RFID technology becomes bigger and bigger every year and this technology finds its way into a lot of new areas. This chapter gives you a briefly introduction into the RFID technology and different RFID systems.

### 2.1 Introduction

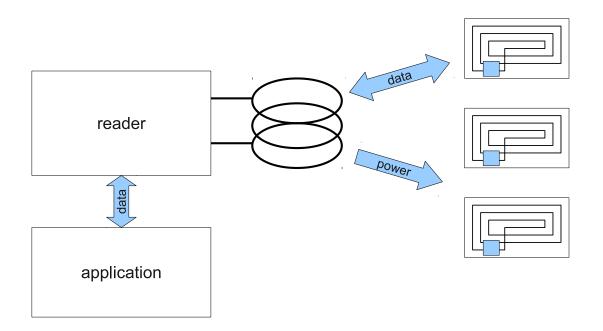

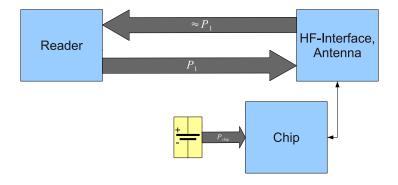

RFID is a general term for all HF-frequency based techniques to transfer data and power contactlessly between a reader and a tag. If we use RFID technology for door-locking applications or micro-payment applications, a secure authentication process is required. An RFID system consist of two parts, first the RFID reader and the application and second one or more RFID tags. Figure 2.1 shows a schematic of a basic RFID system. The aim of

Figure 2.1: Schematic of a basic RFID system.

the reader is to supply the RFID tags with power and to communicate with them. There exist different transmission techniques for communication with one or more tags or to supply them with energy. The second part of the RFID system is the tag or transponder, which is the mobile part of the RFID system. In the following sections, we give more information about RFID tags, construction formats, energy supply, and communication ranges and frequencies. For more information on this topic we refer to [18].

### 2.2 RFID Tag

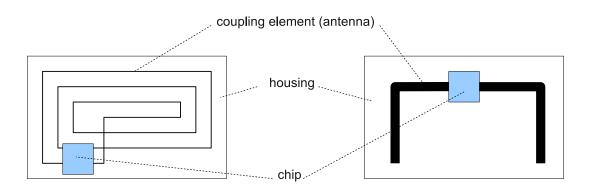

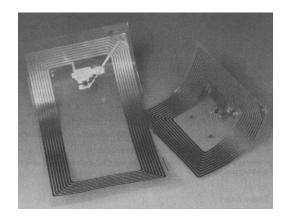

Figure 2.2 is from [18] and gives you an overview of an RFID transponder layout. This transponder could be placed on an object which should be identified. The construction format of the housing can be chosen depending on the application. We can separate an RFID tag into three big parts. The coupling element or antenna, the housing, and the microchip. Figure 2.3 shows the block diagram of an RFID chip. This RFID chip can be also divided into two parts, an RF front-end module and a module which include the functionality of the RFID tag, including cryptographic modules like ECDSA. The RF front-end module consists of two sub-modules, an analog front-end and a digital frontend. The analog front-end includes the High-Frequency Modulator (HF-Modulator) with control functionality, a clock-generation unit and power-supply system which attend all other parts of the transponder with energy. All operations for communication, like the header control, the data extraction, the return-link modulation and the encoder are parts of the digital front-end sub-module. Therefore, the RF front-end module includes all functionalities to receive and transmit data over a radio channel. The functionality of the RFID tag comprises the right block in Figure 2.3. It can be a simple memory, if the transponder has only storage functionality, it can be a complete microprocessor, which can generate a full ECDSA digital signature (like it is in the case of many e-passport applications).

### 2.2.1 Construction Formats

The design or construction format of a transponder depends mainly on the antenna. There exist many different construction formats, today. The following enumeration presents the most popular designs and gives a short description of different application areas. The

Figure 2.2: Basic layout of an RFID transponder [18].

Figure 2.3: Block diagram of an RFID chip.

information about construction formats are from [16, 18, 35].

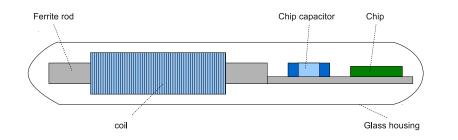

- Glass Housing: The main application area of glass transponders are the identification of animals. These glass tubes have a length of just 12 mm to 22 mm and get injected under the skin. Figure 2.4 shows a glass transponder. The coil and the ferrit rod are parts of the antenna. To ensure a smooth supply current, a chip capacitor is used and the functionality is implement in the chip.

- Keys and Key Fobs: Here, the transponder is used for door-locking applications or micro-payment applications. It is integrated into a mechanical key or a key fob. These transponders mostly have to fulfill very high security requirements, if they are part of an office-access system, for example. Figure 2.5 shows one example of a key fob transponder taken from [18]

- **Contactless Smart-Cards:** has the same format as smart cards with galvanic connections or credit cards. They are also used for door-locking applications or micro-payment applications. The advantage of this construction format is the size, because they can use a bigger antenna which is better for an inductively coupled system.

- Smart Labels: are paper-thin transponders which are applied to a plastic foil of just 0.1 mm thickness. The plastic foil is adhere to a layer of paper in den most cases. This construction is thin and flexible and so it could be attached to a luggage, a book, or all other types of products as a self-adhesive label. Figure 2.7 shows an RFID

Figure 2.4: Layout of a glass transponder [18].

Figure 2.5: Example of a key-fob transponder [18].

chip with antenna on a plastic foil and Figure 2.6 shows a smart-label transponder for luggage tracing and identification (both taken from [18]).

### 2.2.2 Energy Supply

Another possibility to classify transponders is their energy supply. There exist passive transponders and active transponders. A passive transponder has no energy-supply unit on the tag. Consequently, the power which is required by the RFID chip is provided by the reader in type of a magnetic field or an electromagnetic field. If the transponder is not in the reading range of a reader, no power supply is available. Figure 2.8 shows the

Figure 2.6: A smart-label on a luggage [18].

Figure 2.7: A smart-label transponder [18].

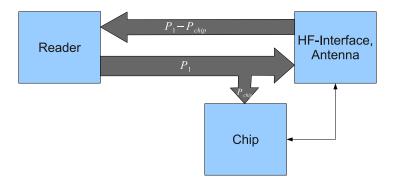

Figure 2.8: Block diagram of a passive transponder [18].

Figure 2.9: Block diagram of an active transponder [18].

energy flow of a passive transponder. The flow  $P_1$  in Figure 2.8 means the electromagnetic energy which is provided by the reader. The transponder needs the energy  $P_{chip}$  to supply all modules, like a cryptographic chip and the RF front-end module with power. Only the energy difference  $P_1 - P_{chip}$  can be used to transmit data back from the transponder to the reader. In contrast to the passive transponder, an active transponder uses a battery to supply the module with power. Figure 2.9 shows the energy flow of an active transponder. Here, the full energy  $P_1$  is used to transmit data back from the tag to the reader. Therefore, the electromagnetic field of the reader can be much weaker, because it is only used for communication. But both types of transponders can not generate a high-frequency signal from its own. They have to modulate the reader field to transmit data from the RFID tag to the RFID reader.

### 2.2.3 Frequency and Reading Range

The reading range of an RFID system goes from a few centimeter up to 10 meter. Depending on the reading range, different frequencies are used. In the following, we give a short description of different reading ranges and frequencies [16, 18, 49].

• Closed-Coupling Systems are RFID systems with a range up to one centimeter and frequencies up to 30 MHz. They use electrical fields or magnetic fields to communicate between reader and tag. The small distance between reader and tag make a high-energy transfer possible. Closed-Coupling systems are mostly used for high-security applications.

- **Remote-Coupling Systems** have a reading reading range up to one meter. They use inductive coupling for communication and energy transport and the mostly used frequencies are 135 kHz and 13.56 MHz. Remote-Coupling systems are the most widely used RFID systems, used for example for anti-theft protection, time recording, or access control.

- Long-Range Systems have a reading range up to 3 meters for passive transponders. If active transponders are used, a reading range up to 10 meters is possible. They use frequencies in the range of Ultra-High Frequency (UHF), like 868 MHz, or microwaves like 2.45 GHz or 5.8 GHz. These systems are mostly used for product-tracing systems and stock-management system.

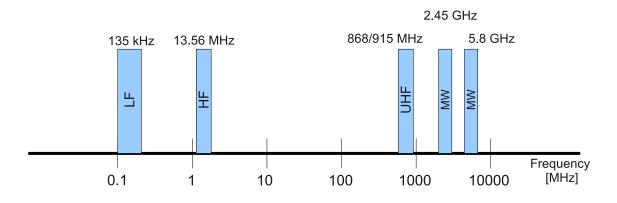

Figure 2.10 shows the frequency spectrum of RFID applications. The following enumeration presents the four most used frequency groups.

- Low Frequency (LF): LF means frequencies about 100 kHz to 135 kHz. This frequencies are for large ranges and low-cost transponders. An advantage is the low-power consumption due to the lower clock cycle and the low-absorption rate in nonmetallic materials and water. Such transponders are used for animal identification, as example.

- High Frequency (HF): The HF frequency 13.56 MHz is mostly used for high-speed and high-end applications or medium-speed and low-end applications. An advantage is that this frequency can be used worldwide as an Industrial, Scientific and Medical (ISM) frequency. The high clock frequency allow complex applications which requires a lot of clock cycles and also data-transmission rates between 106 kbit/s and 848 kbit/s are possible.

- Ultra-High Frequency (UHF): These frequencies can not be used worldwide, because several countries use different frequencies, like 868 MHz in Europe, or 915 MHz in the USA. UHF frequencies can only be used for short-range devices, because buildings and other obstacles evoke a strong dampening and high reflection of this frequencies.

- Microwave (MW): These two frequency ranges (2.45 GHz and 5.8 GHz) are also be used by amateur radio and radio-location services. The behavior respective dampening and the reflection are the same as for UHF frequencies. Typical applications for these frequencies are movement sensors, telemetry transmitters, or wireless-networking systems.

Figure 2.10: Frequency spectrum of RFID systems.

### Chapter 3

## **Authentication Protocols**

Today, RFID tags are increasingly used for product identification in place of bar codes. These tags can also be used for product tracking and anti-counterfeiting purposes. This chapter deals with RFID tags for anti-counterfeiting and presents three different authentication protocols. First, we describe the ECDSA protocol implemented in this thesis. Second, we describe two other protocols, which are also based on the Elliptic-Curve Discrete Logarithm Problem (ECDLP). Both protocols are based on identification schemes. We will discuss advantages and disadvantages of these three protocols.

### 3.1 Introduction

Authentication protocols are used to prove the identity of an user, or in our case an RFID tagged product. An authentication protocol which is used for anti-counterfeiting purposes must have some fundamental characteristics, cf. [37]. The following enumeration shows some important characteristics:

- Scalability: means, that the computational workload of the verifier should not increase linearly with the number of RFID tags. Because a modern RFID system has to support many RFID tags.

- Anti-cloning means, that an attacker can not impersonate a tag. It should not be possible to make a clone of an RFID tag. It is important to implement some countermeasures which prevents the extraction of secret information.

- **Replay attack:** means, that it should not be possible to use a message or some parts of a message to fulfill a valid authentication process, without the private key is known. A countermeasure to prevent replay attacks is the usage of session tokens. These are one-time tokens and they have to been generated randomly at every protocol run. The ECDSA identification protocol, which we use for our RFID tag, fulfill this requirement.

- **Privacy or anonymity:** means, that an RFID system should be secure against tracking attacks. It is a privacy problem, if some part of a message, which is transmitted from tag to the reader is fixed or predictable. An attacker could use this message to track a tag, and hence its owner too.

- Availability: means that an RFID system has to guarantee a minimal continuity of service. There exist some attacks, like jamming attacks or denial-of-service attacks,

which prevent the communication between reader and tag. Therefore, it is important to implement some countermeasures against these types of attacks.

• Side-channel resistance: means a requirement to prevent the extraction of secret information. Side-channel attacks are one frequently used type of attack to extract secret information from an RFID tag and consequently to impersonate it. Therefore, it is important to use algorithms which include some countermeasures against side-channel attacks.

In generally, attacks could be divide into active attacks and passive attacks. Passive attacks means that the attacker can only observe the communication between reader and tag, but it could not influence the communication. In an active attack, like replay attack, or denial-of-service attack, the attacker can influence the communication between reader and tag.

In the next sections, we will discuss three protocols. The ECDSA algorithm, Schnorr's identification scheme, and Okamoto's identification scheme. These three algorithms differ in the message exchange between reader and an RFID tag. They also have a different computational complexity.

### 3.2 Elliptic-Curve Digital Signature Algorithm (ECDSA)

The ECDSA digital signature algorithm was proposed by the American National Standards Institute (ANSI) in the year 1998, cf. [3], as a new digital-signature algorithm for the financial service industry. They defined SHA-1 as a hash function which should be used. They also provided some criteria for key generation and secure usage of the ECDSA digital signature algorithm. The ECDSA authentication protocol can be used to prove the identity of the signer (identification scheme) or authenticate a message (signature scheme).

The ECDSA digital signature algorithm uses asymmetric cryptography to prove the assurance of the signer. Algorithm 3.1 shows this algorithm, which was proposed by ANSI [3]. The first step is to generate a cryptographic secure random number, which is called the ephemeral key k. At next, a scalar multiplication is performed. This second step is

```

Algorithm 3.1 ECDSA digital signature generation, cf. [3].

Require: domain parameter D = (q, FR, a, b, G, n, h)

Require: private key d of an associated key pair (d, Q)

Require: message m

Ensure: signature values (r, s)

1: select a random k, with 1 \le k \le n-1

2: (x_1, y_1) = k \cdot G, convert x_1 to an integer \overline{x_1}

3: r = \bar{x_1} \mod n

4: \ k^{-1} \ mod \ n

5: e = SHA - 1(m), where e is an integer

6: s = k^{-1} \cdot (e + d \cdot r) \mod n

7: if (r = 0) \lor (s = 0) then

goto step 1

8.

9: end if

10: return (r, s)

```

Algorithm 3.2 Key pair generation, cf. [24]. Require: domain parameter D = (q, FR, a, b, G, n, h)Ensure: public key Q, private key dselect a random d, with  $1 \le d \le n - 1$   $Q = d \cdot G$ return (d, Q)

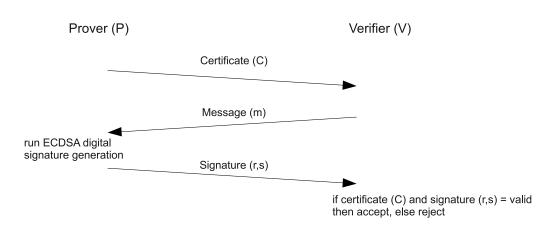

Figure 3.1: Authentication protocol with ECDSA.

the most time intensive part of the whole ECDSA signature-generation process. SHA-1 is used as a hash function to generate a fingerprint of the message m. The long-time public-private key pair is only used in step six of Algorithm 3.1. An algorithm to generate an associated key pair is shown in Algorithm 3.2, cf [3, 24]. This algorithm uses the same domain parameter as Algorithm 3.1 and d means the private key. Figure 3.1 shows the authentication protocol message exchange which uses ECDSA according to the ISO 9798-3 standard. In the first step, the prover or in our case the RFID tag transmits a certificate to the verifier, which includes the public key Q. This certificate is signed by a trusted third party and could get validated by the verifier. If the certificate is valid, then the verifier transmits a message m to the prover. The prover executes the ECDSA digital signature algorithm and sign the message m. In the third step, the prover transmits the signature values. If the signature is valid, then the authentication process is finish and the prover is accept, else the prover is reject.

### 3.3 Schnorr's Identification Scheme

In 1991, Claus Peter Schnorr, [52] proposed an other authentication protocol, which is based on an identification scheme. Figure 3.2 shows the message exchange of Schnorr's identification scheme. One execution of this protocol requires a set of parameters and arrangements. We present this parameters in the following enumeration:

• Domain parameters of the elliptic curve D = (q, FR, a, b, G, n, h), where q means the finite field, a and b are parameters which characterize the elliptic curve, G is the base point, and n is called the order of the elliptic curve. This parameters have to

| Algorithm 3.3 ECDSA digital signature verification, cf. [24]               |

|----------------------------------------------------------------------------|

| <b>Require:</b> domain parameter $D = (q, FR, a, b, G, n, h)$              |

| <b>Require:</b> public key $Q$ of an associated key pair $(d, Q)$          |

| <b>Require:</b> message $m$ , signature values $(r, s)$                    |

| Ensure: valid or rejected signature                                        |

| e = SHA - 1(m), where e is an integer                                      |

| $w = s^{-1} \mod n$                                                        |

| $u_1 = e \cdot w \mod n, u_2 = r \cdot w \mod n$                           |

| $X = u_1 \cdot P + u_2 \cdot Q$                                            |

| if $X = \infty$ then                                                       |

| return reject signature                                                    |

| end if                                                                     |

| $v = \bar{x_1} \mod n$ , with $\bar{x_1}$ is $x_1$ converted to an integer |

| $\mathbf{if} \ v \neq r \ \mathbf{then}$                                   |

| return reject signature                                                    |

| else                                                                       |

| return accept signature                                                    |

| end if                                                                     |

be fixed in case of identification.

• Similar to ECDSA, the prover requires a private secret a, such that  $Z = -a \cdot G$ , where G is the base point and Z is the public part of the key pair, similar to ECDSA.

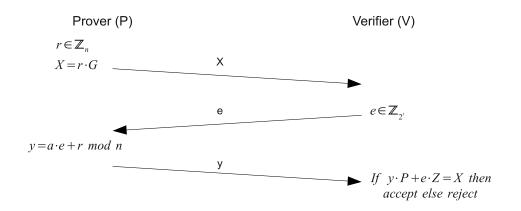

The prover generates, in the first step a secure random number r, which is similar to the ephemeral key in ECDSA. Afterwards, the prover calculates a new point X with  $X = r \cdot G$  and transmits the coordinates of this point to the verifier. In the second step, the verifier generates a random value e and transmits it to the prover. Now the prover calculates y, where  $y = a \cdot e + r \mod n$  and transmits this value back to the verifier. At last, the verifier can check the identification process by calculating  $y \cdot P + e \cdot Z = X$ . If  $y \cdot P + e \cdot Z$  equals to X then accept the prover, else reject it. From a security point of view, there are the same critical operations as already described for ECDSA. The two critical operations are the point multiplication  $r \cdot G$  and the multiplication  $a \cdot e \mod n$ . In order to prevent attacks

Figure 3.2: Schnorr's identification scheme [34].

on this operations, secure algorithms can be used, like the Montgomery ladder algorithm or the Montgomery multiplication algorithm.

### 3.4 Okamoto's Identification Scheme

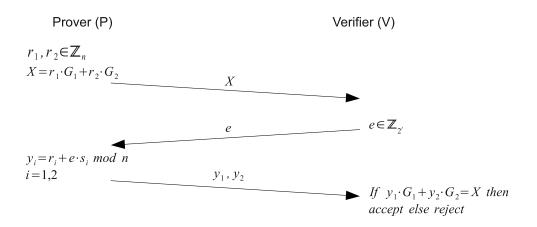

In 1993, Tatsuaki Okomoto, [47] proposed an identification scheme which has same advantages as Schnorr's identification scheme. This identification scheme is also resistant against active attacks and concurrent attacks, cf. [5, 34]. Figure 3.3 shows the message exchange of Okamoto's identification scheme. One execution of this protocol requires a set of parameters and arrangements. We present this parameters in the following enumeration:

- Domain parameters of the elliptic curve  $D = (q, FR, a, b, G_1, G_2, n, h)$ , where q means the finite field, a and b are parameters which characterize the elliptic curve,  $G_1$  and  $G_2$  are two base points and n is called the order of the elliptic curve. This parameters have to be fix in case of authentication.

- This protocol uses a private key pair  $(s_1, s_2)$ , which consists of two secure random numbers. The corresponding public key Z can be calculated with  $Z = -s_1 \cdot G_1 s_2 \cdot G_2$

At first, the prover generates two secure random numbers  $r_1$  and  $r_2$ , which have the same functionality as the ephemeral key in case of ECDSA. Afterwards, the prover calculates  $X = r_1 \cdot G_1 + r_2 \cdot G_2$  and transmits the result X to the verifier. In the next step, the verifier generates also a secure random number e and transmit this value to the prover. Now, the prover calculates two values  $y_1$  and  $y_2$ , where  $y_i = r_i + e \cdot s_i \mod n$  and  $i \in \{1, 2\}$ , and transmit both values to the verifier. The verifier can use all this information to identify the prover. If  $y_1 \cdot G_1 + y_2 \cdot G_2 + e \cdot Z = X$ , then accept the prover, else reject it. In contrast to ECDSA authentication protocol and Schnorr's identification scheme, Okamoto's identification scheme requires two point-multiplications instead of one point multiplication. Consequently, Okamoto's protocol requires much more clock cycles for one protocol exchange, because the point multiplication is the most time intensive part. From a security point of view, this protocol has the same critical operations such as we described for the Schnorr's identification scheme and the ECDSA authentication protocol.

If only identification is required, the advantage of Schnorr's and Okamoto's identification scheme is, that they require no hash function. But this fact has only a small

Figure 3.3: Okamoto's identification scheme [34].

impact to the size of the module area, if a prime field is used. Because almost all functionality and also the memory requirements are determined by the scalar multiplication algorithm, which is equal for all three protocols. With the exception, that Okamoto's protocol requires much more clock cycles.

### Chapter 4

## Mathematical Basics for ECDSA

Modern cryptographic systems use mathematical principles to ensure their safety. All algorithms are used there, defined in terms of arithmetic operations. This chapter describes all algorithms and mathematical basics which are required to generate an ECDSA digital signature. The fist section contains information about finite-field arithmetics. Finite-field arithmetic is the basic for all other algorithms which are required for ECDSA. The second part deals specifically with the arithmetic in elliptic curves. Operations in elliptic curves are time intensive and so it is important to find fast algorithms. The ECDSA algorithm needs also a hash function and the third section gives an overview of SHA-1.

### 4.1 Finite-Field Arithmetic

Fields are abstractions of familiar number systems such as the rational numbers  $\mathbb{Q}$  or the real numbers  $\mathbb{R}$ . A finite field  $\mathbb{F}$  consists of a finite set of objects called field elements. We can define two operations, addition (denoted by +) and multiplication (denoted by  $\cdot$ ) between this field elements and this operations must possess certain properties, cf. [24].

- 1.  $(\mathbb{F}, +)$  is an abelian group with additive identity denoted by 0

- 2.  $(\mathbb{F}, \cdot)$  is an abelian group with multiplicative identity denoted by 1

- 3. The distributive law holds:  $(a + b) \cdot c = a \cdot c + b \cdot c$  for all  $a, b, c \in \mathbb{F}$

All other operations on the finite field  $F_p$  can be defined with this two operations. Subtraction can be defined in terms of addition and division can be defined in terms of multiplications. For two field elements  $a, b \in \mathbb{F}$  the subtractions (a - b) can be written as a + (-b), with -b which is called the unique element in  $\mathbb{F}$  so that b + (-b) = 0. The division  $\frac{a}{b}$  can be written as  $a \cdot b^{-1}$ , with  $b \neq 0$  and  $b^{-1}$  which is called the unique element in  $\mathbb{F}$  such that  $b \cdot b^{-1} = 1$ .

The element -b is called the negative element of b and the element  $b^{-1}$  is called the inverse element of b in  $\mathbb{F}$ .

The number of elements in a field  $\mathbb{F}_q$  is called the *order* of the field. A finite field  $\mathbb{F}$  with order q only exists if q is a prime power  $q = p^m$ . In this definition for q, p, the prime number is called the characteristic of  $\mathbb{F}$  and m is a positive integer in  $\mathbb{Z}^+$ . A finite field  $\mathbb{F}$  with q elements is denoted with  $\mathbb{F}_q$ . Furthermore, there is for each q precisely one finite field  $\mathbb{F}_q$ . This means that except a different labeling of the field element, two fields of order q are structurally the same.

Depending on m, we can distinguish between two types of finite fields  $\mathbb{F}$ . If m = 1, the field  $\mathbb{F}$  is called a *prime field*  $\mathbb{F}_p$ , otherwise  $\mathbb{F}$  is called an *extension field*. A frequently used type of *extension field* are *binary fields*  $\mathbb{F}_{2^m}$ . The choices of p and m can have a dramatic influence on the performance of algorithms over finite fields. There exist generic algorithms for arithmetic in arbitrary finite fields and specialized algorithms with a articulate better performance in finite fields with a particular form, cf. [24]

### Binary Fields $\mathbb{F}_{2^m}$

A characteristic 2 finite field  $\mathbb{F}_{2^m}$  contains  $2^m$  elements. There exist many different ways to represent elements of  $\mathbb{F}_{2^m}$ . One way is to use the polynomial basis representation. Here the elements of  $\mathbb{F}_{2^m}$  are the binary polynomials whose coefficients are in den field  $\mathbb{F}_2 = (0, 1)$ . The degree of the polynomial is most m - 1.

$$\mathbb{F}_{2^m} = \left\{ a_{m-1} z^{m-1} + a_{m-2} z^{m-2} + \dots + a_2 z^2 + a_0 : a_i \in 0, 1 \right\}$$

(4.1)

For any m exists an irreducible binary polynomial f(z) which can be found efficiently. Irreducible of f(z) means that m cannot be factored as a product of binary polynomials each of degree less than m.

Addition and multiplication operations in  $\mathbb{F}_{2^m}$  can be calculated efficiently by using standard algorithms for ordinary integer and polynomial arithmetic. This two operations in binary fields  $\mathbb{F}_{2^m}$  are defined as follow, see [8]:

- Addition: We define two elements  $a = a_{m-1}z^{m-1} + \cdots + a_1z^1 + a_0$  and  $b = b_{m-1}z^{m-1} + \cdots + b_1z^1 + b_0 \in \mathbb{F}_{2^m}$ . The element r is the sum from a+b in  $\mathbb{F}_{2^m}$  where r is described as  $r_{m-1}z^{m-1} + \cdots + r_1z^1 + r_0$  with  $r_i \equiv a_i + b_i \mod 2$ .

- Multiplication: We define two elements  $a = a_{m-1}z^{m-1} + \cdots + a_1z^1 + a_0$  and  $b = b_{m-1}z^{m-1} + \cdots + b_1z^1 + b_0 \in \mathbb{F}_{2^m}$ . The element s is the product from  $a \cdot b$  in  $\mathbb{F}_{2^m}$ , where s is described as  $s_{m-1}z^{m-1} + \cdots + s_1z^1 + s_0$  when the polynomial  $a \cdot b$  is divided by f(z) and all coefficient arithmetics performed modulo 2.

That was only a brief description of binary fields  $\mathbb{F}_{2^m}$ , because this work deals with elliptic curves over prime fields  $\mathbb{F}_p$ . More information about binary fields can be found in standard literature, e.g. [12, 24].

### Prime Fields $\mathbb{F}_p$

For each odd prime, there exist a prime field  $\mathbb{F}_p$  which contains p elements. There is only one prime field for each prime, but there exist many different ways to represent these elements. In this thesis the elements of  $\mathbb{F}_p$  will be represented by a set of integers:

$$\{0, 1, \cdots, p-1\} \tag{4.2}$$

In an abstract form addition and multiplication in prime fields can defined as follows, see [8]:

• Addition: We define two elements  $a, b \in \mathbb{F}_p$ . The sum r from a + b in  $\mathbb{F}_p$  is the remainder when the integer a + b is divided by p. This operation is known as addition modulo p and is written  $a + b \equiv r \mod p$ .

| A[t-1] | A[1] | A[0] |

|--------|------|------|

|--------|------|------|

Figure 4.1: Representation of  $a \in \mathbb{F}_p$  as an array A.

Algorithm 4.1 Addition of multi-word integers. Require:  $a, b \in [0, 2^{W \cdot t})$  and  $\epsilon' \in \{0, 1\}$ Ensure:  $(\epsilon, s)$ , where  $s \in [0, 2^{W \cdot t})$  and  $\epsilon \in \{0, 1\}$   $(\epsilon, S[0]) \leftarrow A[0] + B[0] + \epsilon'$ for i = 1 to t - 1 do  $(\epsilon, S[i]) \leftarrow A[i] + B[i] + \epsilon$ end for return  $(\epsilon, s)$

• Multiplication: We define two elements  $a, b \in \mathbb{F}_p$ . The product s from  $a \cdot b$  in  $\mathbb{F}_p$  is the remainder when the integer  $a \cdot b$  is divided by p. This operation is known as multiplication modulo p and written  $a \cdot b \equiv s \mod p$ .

The bit length of p is m where  $m = \lceil \log_2 p \rceil$ . In real implementations, integers with m bits cannot be used directly because the word size W of the architecture is often smaller then m. For this reason integers must be split and stored in an array  $A = (A[0], A[1], \dots A[t-1])$  of t W-bit words. The word-length t is defined as  $t = \lceil \frac{m}{W} \rceil$ . An example of an array A is shown in Figure 4.1, where the rightmost bit of A[0] is the least significant bit. The bit representation, shown in 4.1 is used in all algorithms described in Section 4 and Section 5.

Algorithms for arbitrary primes p and special primes recommended by SECG [48] are presented in the subsequent Sections 4.1.1 to 4.1.4.

#### 4.1.1 Addition and Subtraction

Algorithms for field addition and field subtraction can be separated in algorithms for multi-word integers and an optionally reduction step modulo p. The basic operation is the addition of two single word integers  $a, b \in [0, 2^W)$  and a carry bit  $\epsilon' \in \{0, 1\}$ . We define this addition result  $(\epsilon, s)$  with the sum s and the carry bit  $\epsilon$  as follows, cf. [24]:

$$w = a + b + \epsilon'$$

$$s \leftarrow w \mod 2^{W}$$

$$\epsilon \leftarrow 0 \text{ if } w \in [0, 2^{W}), \text{ otherwise } \epsilon \leftarrow 1$$

$$(4.3)$$

Algorithm 4.1 is from [24] and illustrates a generic version of a multi-word integer addition. Arithmetic in a finite field  $\mathbb{F}_p$  needs also an optional reduction step modulo p. The complete algorithms for addition and subtraction are shown in Algorithm 4.2 and Algorithm 4.3. There,  $\neg a$  means the binary-inverse integer from a. If  $s \ge p$ , a final reduction operation after the last operation is needed. This versions are used in the ECDSA module with a word size of 16 bits.

**Algorithm 4.2** Addition in  $\mathbb{F}_p$ .

**Require:**  $a, b \in [0, 2^{W \cdot t})$  **Ensure:**  $s = (a + b) \mod(p)$ Use Algorithm 4.1 to calculate  $(\epsilon, s)$ , with a, b and  $\epsilon' = 0$  **if**  $\epsilon = 1$  **then** Use Algorithm 4.1 to calculate  $(\epsilon, s)$ , with  $s, \neg p$  and  $\epsilon' = 0$  **end if return** (s)

Algorithm 4.3 Subtraction in  $\mathbb{F}_p$ .

**Require:**  $a, b \in [0, 2^{W \cdot t})$  **Ensure:**  $s = (a - b) \mod(p)$ Use Algorithm 4.1 to calculate  $(\epsilon, s)$ , with  $a, \neg b$  and  $\epsilon' = 1$  **if**  $\epsilon = 0$  **then** Use Algorithm 4.1 to calculate  $(\epsilon, s)$ , with s, p and  $\epsilon' = 0$  **end if return** (s)

### 4.1.2 Multiplication

Field multiplication in  $\mathbb{F}_p$  can also accomplished in two steps. The first step is to multiply a and b, which are elements of  $\mathbb{F}_p$  as integers. Afterwards, the result can be reduced modulo p as the second step. Algorithm 4.4 and Algorithm 4.5 are two generic versions of elementary integer-multiplication routines. These algorithms create a  $2 \times W \times t$ -bit quantity obtained by concatenation of  $W \times t$ -bit words a and b. This could be a problem in products with constraint devices like RFID tags or smartcards. Another problem is that reduction modulo p needs a division operation which is a complex operation. For these applications, algorithms with implicit reduction are the better choice. Therefore, we can use the Montgomery multiplication algorithm cf. Section 4.1.2 or an advanced version of Algorithm 4.5 with implicit reduction. This sophisticated algorithm for field multiplication is shown in Section 4.1.2 and uses a technique called fast reduction or NIST reduction which is described in Section 4.1.3.

There exist some algorithms for field squaring of  $a \in \mathbb{F}_p$  which reduce the number of required single-precision multiplications by roughly the half. An improved version of Algorithm 4.5 to calculate the square of a is shown in [24]. An own squaring algorithm has been renounced since this ECDSA module is optimized for area.

#### **Integer Multiplication**

The following two algorithms calculate the  $2 \times W$ -bit multiplication result from  $a, b \in [0, W \cdot t]$ . Both algorithms necessitate a runtime of  $\mathbb{O}(t^2)$  for multiplication of two  $W \times t$ bit integers. There exist some other algorithms like *Karatsuba-Ofman* multiplication with a complexity of  $\mathbb{O}(t^{\log_2 3})$ . But these algorithms are rather interesting for implementation in software or hardware implementations with binary fields  $\mathbb{F}_{2^m}$ . Algorithms which use *Karatsuba-Ofman* multiplication not further mentioned here. For some more information see [10, 17, 24, 40].

Algorithm 4.4 uses the so called inner product  $(C[i+j] + A[i] \cdot B[j] + U)$  to calculate

**Algorithm 4.4** Multiplication in  $\mathbb{F}_p$  - operand-scanning form.

```

Require: a, b \in [0, p-1)

Ensure: s = a \cdot b

Set C[i] \leftarrow 0 for 0 \le i \le t-1

for i = 0 to t-1 do

U \leftarrow 0

for j = 0 to t-1 do

(U \ V) \leftarrow C [i+j] + A[i] \cdot B[j] + U

C [i+j] \leftarrow V

end for

C [i+t] \leftarrow U

end for

return (c)

```

**Algorithm 4.5** Multiplication in  $\mathbb{F}_p$  - product-scanning form.

**Require:**  $a, b \in [0, p-1)$  **Ensure:**  $s = a \cdot b$   $R_0 \leftarrow 0, R_1 \leftarrow 0, R_2 \leftarrow 0$  **for** k = 0 to 2t - 2 **do for** For each element of  $\{(i, j)|i + j = k, 0 \le i, j \le t - 1\}$  **do**   $(U \ V) \leftarrow A[i] \cdot B[j]$   $(\epsilon, R_0) \leftarrow R_0 + V$   $(\epsilon, R_1) \leftarrow R_1 + U + \epsilon$   $R_2 \leftarrow R_2 + \epsilon$  **end for**   $C[k] \leftarrow R_0, R_0 \leftarrow R_1, R_1 \leftarrow R_2$  **end for**   $C[2t - 1] \leftarrow R[0]$ **return** (c)

the result and Algorithm 4.5 is arranged that the product is calculated from left to right. But both algorithms are from [24] and create a result with a size of  $2 \times W$  bits.

#### Montgomery Multiplication Algorithm

Peter Montgomery proposed in 1985 [43] an efficient algorithm for modular multiplication. The Montgomery algorithm is a fast algorithm to compute  $a \cdot b \mod p$ , if the modulo p has no particular form. This method to multiply modulo p avoids division by p for the reduction. The idea is to convert the reduction modulo p to a reduction modulo R where division is easier. It is useful to select R as a power of 2 because in this case a complex division can be replaced by a simple shift right operation. If we choose R, it is important that R is relatively prime to p (gcd(n, R) = 1).

An integer  $a \mod p$  can be represented in the Montgomery domain as  $[a]_R = a \cdot R \mod p$ . This transformation is agreeable with an addition

$$[a+b]_R \equiv (a+b) \cdot R \equiv a \cdot R + b \cdot R \equiv [a]_R + [b]_R \tag{4.4}$$

Algorithm 4.6 Montgomery multiplication algorithm.

**Require:**  $p \in \mathbb{P}$ ,  $a, b \in [0, p-1)$ ,  $R = 2^n$ ,  $R \cdot R^{-1} - p \cdot p' = 1$  **Ensure:**  $a \cdot b \cdot R^{-1} \mod p$   $T \leftarrow a \cdot b$   $S \leftarrow T \cdot p' \mod R$   $U \leftarrow (T + S \cdot p) / R$  **if**  $U \ge M$  **then return** U - M **else return** U**end if**

but not agreeable with a multiplication

$$[a \cdot b]_R = [a]_R \cdot [b]_R \cdot R^{-1} \tag{4.5}$$

The Montgomery multiplication algorithm, see Algorithm 4.6 transforms two numbers  $a, b \in [0, p-1]$  implicit to the Montgomery domain. In this case, we can define the Montgomery multiplication a \* b as follow:

$$[c]_R = a * b = a \cdot b \cdot R^{-1} \mod p \tag{4.6}$$

In order to get the desired result  $c = a \cdot b \mod p$ , some pre or post computations are required to remove the factor  $R^{-1}$ .

• Pre computation: To remove the factor  $R^{-1}$  from the output, one input operant should get converted into the Montgomery domain. The Montgomery multiplication algorithm can be used itself, if one multiplication operant is chosen as a constant factor  $R^2$ .

$$[a]_R = a * R^2 = a \cdot R^2 \cdot R^{-1} \mod p = a \cdot R \mod p$$

$$(4.7)$$

$$c = [a]_R * b = [a]_R \cdot b \cdot R^{-1} \mod p = a \cdot b \mod p$$

$$(4.8)$$

• Post computation: When both input operants of the Montgomery multiplication algorithm are in Montgomery domain format the multiplication result is going to be  $a \cdot b \cdot R \mod p$ . To remove this extra factor R in the result, performing one more Montgomery multiplication by a constant factor 1 is necessary.

$$c = [c]_R * 1 = [c]_R \cdot R^{-1} \mod p = a \cdot b \cdot R \cdot R^{-1} \mod p = a \cdot b \mod p$$

(4.9)

Algorithm 4.6 shows the original version of the Montgomery multiplication algorithm which was published by Peter Montgomery in 1985, see [43]. In most projects this original version is not implemented. There is a variety of other implementations to perform Montgomery multiplication, which need a different number of basic integer operations like addition, multiplication or shift operations. Zhang Jia-hong et al. [59] proposed in 2009 a Montgomery multiplication algorithm which only needs  $2 \cdot t^2 + t + 2$  clock cycles for one multiplication. This published version requires  $3 \times W$ -bit registers and is currently the fastest implementation of Montgomery multiplication, cf. [59]. In this work, we use the algorithm proposed by Zhang Jia-hong, with some modifications. The multiplication

| Table 4.1. Time requirements of Mor | ngomery muniph    | auon methous.                 |

|-------------------------------------|-------------------|-------------------------------|

| Method                              | Multiplications   | Additional Operations         |

| SOS                                 | $2 \cdot t^2 + t$ | $4 \cdot t^2 + 4 \cdot t + 2$ |

| CIOS                                | $2 \cdot t^2 + t$ | $4 \cdot t^2 + 4 \cdot t + 2$ |

| FIOS                                | $2 \cdot t^2 + t$ | $5 \cdot t^2 + 3 \cdot t + 2$ |

| FIPS                                | $2 \cdot t^2 + t$ | $6 \cdot t^2 + 2 \cdot t + 2$ |

| CIHS                                | $2 \cdot t^2 + t$ | $4 \cdot t^2 + 4 \cdot t + 2$ |

| Zhang Jia-hong                      | $2 \cdot t^2 + t$ | 2                             |

| This work                           | $2 \cdot t^2 + t$ | ${f 2}\cdot{f t}$             |

Table 4.1: Time requirements of Montgomery multiplication methods

unit, which is used for multiplication with implicit fast reduction, has a similar design than the presented by Jong Zhang Jia-hong but our design required only  $2 \times W + \frac{W}{2}$ -bit registers. It was possible to map the original design to our hardware architecture and we include some countermeasures against SPA and DPA attacks. The modified Montgomery multiplication algorithm, which is described in Algorithm 4.7, is only slightly slower and needs  $2 \cdot t^2 + 3 \cdot t$  clock cycles for one multiplication, but it is optimized for area and reusing operations from multiplication with implicit fast reduction. Table 4.1 constitutes an overview of different Montgomery multiplication algorithms, cf. [33].

#### Multiplication with implicit fast Reduction

A second possibility for multiplication with implicit reduction is a combination of a generic multiplication algorithm in product scan form, see Algorithm 4.5 and an implicite fast reduction, see Section 4.1.3. But this method only works with special prime numbers, like NIST primes or other special primes. The described algorithm uses the prime from the SECP160r1 elliptic curve. For more information about this fast reduction look at Section 4.1.3.

Multiplication with fast reduction uses as origin the multiplication algorithm in product-scanning form with a word size of 16 bits. An advantage of this algorithm is that the current word C[i] of the multiplication result is finished before the next word is calculated. The algorithm for fast reduction which is described in Algorithm 4.17 applies the reduction modulo  $p_{160r1}$ . This algorithm uses the lower and higher 160 bits of the multiplication result in an interleaved form. At first, the lower 160 bits of the result  $c = (C[9], \ldots, C[1], C[0])$  is calculated and stored. In the next step the element C[10] of the higher 160 bits is calculated. This element is added at two different places to the lower result c. The addition of one element is done interleaved by storing the carry bit if one is generated. For that purpose some additional memory is required to save two separate carry bits. Then the next element C[12] is calculated and added interleaved. The last to elements C[18] and C[19] have to be added on three different places to c. All addition operations are processed modulo  $p_{160r1}$ , therefore maybe an additional reduction step is needed. The number of clock cycles to multiply two integers modulo  $p_{160r1}$  is  $t^2 + 5t$  in the worst case. Hence this algorithm is four times faster than the Montgomery multiplication algorithm described in Algorithm 4.7. Because the Montgomery multiplication algorithm must be used twice. One time for multiplication of the integers a and b and a second time to transform the result from the Montgomery domain to the integer domain. Algorithm 4.8 describes the multiplication with implicit fast reduction which is used for field operations modulo  $p_{160r1}$ .

Algorithm 4.7 Our improved Montgomery multiplication algorithm (16-bit word size).

```

Require: p \in \mathbb{P}, a, b \in [0, p-1), R = W^t, p' = -p^{-1} \mod W

Require: x, y with 176 bits, u and d with 176 bits, reg with 36 bits

Ensure: a \cdot b \cdot R^{-1} \mod p

reg \leftarrow x[0] \cdot y[0]

u[0] \leftarrow reg[0] \cdot p

reg \leftarrow reg + u[0] \cdot p[0]

reg[0] \leftarrow reg[1], \, reg[1] \leftarrow reg[2], \, reg[2] \leftarrow 0

for j = 1 to j < 11 do

for i = 1 to i \leq j do

reg \leftarrow reg + u[i-1] \cdot p[j+1-i]

end for

for i = j to i \ge 0 do

req \leftarrow req + x[i] \cdot y[j-i]

end for

u[j] \leftarrow reg[0] \cdot p'

reg \leftarrow reg + u[j] \cdot p[0]

reg[0] \leftarrow reg[1], reg[1] \leftarrow reg[2], reg[2] \leftarrow 0

end for

for j = 9 to 0 do

for i = 0 to i \leq j do

reg \leftarrow reg + u[10 - j + i] \cdot p[10 - i]

end for

for i = j to i \ge 0 do

reg \leftarrow reg + x[10 - j + i] \cdot y[10 - i]

end for

d[9-j] \leftarrow reg[0], reg[0] \leftarrow reg[1], reg[1] \leftarrow reg[2], reg[2] \leftarrow 0

end for

u \leftarrow d - p

if reg[1] > 0 then

return (u)

else

return (d)

end if

```

### 4.1.3 Reduction

Reduction a mod p is an important part of modular arithmetic, because it can be a time and memory expensive operation. In particular, if the prime p has no special form then the reduction is as expensive as a multiplication operation. Field multiplications and reductions are used in many cryptographic algorithms. Therefore, it is important to select moduli with a special form, so that reduction gets faster. This section only presents the reduction method of Barrett and the fast reduction for special primes, because the modulus p of the field  $\mathbb{F}_p$  on which the elliptic curve is defined has a special form. Only the modulus involved to the signature-generation operation has a general form, but therefore the Montgomery multiplication algorithm is used to multiply.

Algorithm 4.8 Multiplication with implicit fast reduction modulo  $p_{160r1}$ .