Master's Thesis

## Runtime-Reconfigurable Real-Time Communication System for Measurement and Control Solutions

Florian Brugger, BSc

Institute for Technical Informatics Graz University of Technology Head of the Institute: O. Univ.-Prof. Dipl.-Ing. Dr. techn. Gernot Kubin

Institute of Lightweigth Design Graz University of Technology Head of the Institute: Ass.Prof. Dipl.-Ing. Dr. techn. Christian Moser

Reviewer: Dipl.-Ing. Dr. techn. Christian Kreiner

Advisor: Dipl.-Ing. Dr. techn. Christian Kreiner Dipl.-Ing. Dr. techn. Thomas Thurner

Graz, September 2012

#### Abstract

Over the last decade, the concept of *distributed computing* has become more and more important in industrial research; even in the field of measurement and automation, where generally the use of conventional but well-proofed technology is preferred. Distributing computational resources and performance among the members of a network implies increasing effort for communication between the different units. Furthermore, in the application fields mentioned before – measurement and automation – very high standards for precision and real-time behavior of the communication channel are defined.

In the course of the development of distributed computational networks, the established concepts for data transfer were soon pushed to their limits; additional requirements regarding functionality and flexibility could not be satisfied, any more. Changing the base technology from *fieldbus* to *Ethernet* leads to a significant gain in data throughput and allows the usage of more complex network topologies. When special communication concepts are applied (e.g. *EtherCAT*, which is used in the present work), highest demands on the quality of the data transmission can be satisfied.

This document presents the design of a communication system dedicated for measurement equipment in a testing facility. On the theoretical side, the design process covers the determination of the system requirements, the consideration of a suitable technology, and the design of a convenient system architecture. Following this, a prototype of a communication component is implemented according to the given requirements and, at last, evaluated in respect to the actual operation in a test bench setup, which is the target environment.

#### Key words

communication systems, sensor networks, data transfer, real-time, EtherCAT, Industrial Ethernet, inter-device communication, system engineering

#### Kurzfassung

Im letzten Jahrzehnt hat das Konzept des *distributed computing* stetig an Bedeutung gewonnen und auch in der Industrie Einzug gehalten. Dies führte dazu, dass auch in (aus informationstechnischer Sicht) eher konservativen Bereichen, wie der Meß- und Automatisierungstechnik, zunehmend verteilte Rechnermodelle eingesetzt werden. Die Verteilung von Rechenkapazität und -leistung auf die einzelnen Teilnehmer eines Netzwerks bringt allerdings auch einen steigenden Aufwand für die Kommunikation der Recheneinheiten untereinander mit sich. Die genannten Einsatzbereiche (Meßtechnik und Automatisierung) stellen außerdem sehr hohe Anforderungen an die Präzision und das Echtzeitverhalten des Übertragungsweges.

Im Zuge dieser Entwicklung wurden die Leistungsgrenzen der etablierten Konzepte zur Datenübertragung bald erreicht. Es ergaben sich auch zusätzliche Anforderungen an deren Funktionalität und Flexibilität, die diese kaum mehr erfüllen konnten. Der Umstieg vom Medium *Feldbus* auf *Ethernet* erlaubt eine deutliche Steigerung der Datenrate in Verbindung mit komplexeren Topologien. Mit speziellen Konzepten, wie dem in dieser Arbeit verwendeten *EtherCAT* können auch höchste Qualitätsstandards für die Datenübertragung garantiert werden.

Dieses Dokument behandelt die Entwicklung eines Kommunikationssystems für den Einsatz in einem mechanischen Prüfinstitut. Der Entwicklungsprozeß umfaßt auf der theoretischen Seite sowohl die Ermittlung der genauen Systemanforderungen, als auch eine Betrachtung der eingesetzten Technologie (*EtherCAT*) und die Erstellung einer geeigneten Systemarchitektur. In Folge wird ein Prototyp einer Kommunikationskomponente den Anforderungen entsprechend implementiert und hinsichtlich seiner tatsächlichen Eignung in der Zielumgebung (ein meßtechnischer Aufbau im Labor) evaluiert.

#### Stichwörter

Kommunikationssystem, Sensornetzwerk, Datenübertragung, Echtzeit, EtherCAT, Industrial Ethernet, Inter-device communication, Systementwicklung

### STATUTORY DECLARATION

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

date

(signature)

# Contents

| 1        | Intr           | roducti | on                                                              | 9  |

|----------|----------------|---------|-----------------------------------------------------------------|----|

|          | 1.1            | Motiva  | ation                                                           | 9  |

|          | 1.2            | Goal    |                                                                 | 9  |

|          | 1.3            | Outlin  | le                                                              | 10 |

| <b>2</b> | $\mathbf{Rel}$ | ated w  | ork, technologies, and system characteristics                   | 11 |

|          | 2.1            | Test b  | ench and automation system characteristics                      | 11 |

|          |                | 2.1.1   | Use cases                                                       | 11 |

|          |                | 2.1.2   | System requirements                                             | 13 |

|          |                | 2.1.3   | Quality of service                                              | 15 |

|          | 2.2            | Etherr  | net-based fieldbus technologies                                 | 17 |

|          |                | 2.2.1   | EtherCAT                                                        | 17 |

|          |                | 2.2.2   | Competitive technologies                                        | 25 |

|          |                | 2.2.3   | Industrial solutions                                            | 29 |

|          |                | 2.2.4   | Functional and performance testing of EtherCAT                  | 31 |

| 3        | Des            | ion of  | a runtime-reconfigurable real-time communication system         | 36 |

| U        | 3.1            | -       | ional requirements for the target environment                   | 36 |

|          | 3.2            |         | n component architecture                                        | 38 |

|          | 0.2            | 3.2.1   | Slave device                                                    | 38 |

|          |                | 3.2.2   | Master device                                                   | 39 |

|          | 3.3            | -       | by of the network                                               | 44 |

|          | 3.4            | -       | arison of host interfaces, description of layers and data model | 46 |

|          | 0.1            | 3.4.1   | Host interface                                                  | 46 |

|          |                | 3.4.2   | Layers model                                                    | 50 |

|          |                | 3.4.3   | Data flow                                                       | 52 |

|          | -              |         |                                                                 |    |

| 4        | -              |         | tation of the real-time communication system and its separate   |    |

|          |                | iponen  |                                                                 | 53 |

|          | 4.1            |         | inary remarks                                                   | 53 |

|          |                | 4.1.1   | Development process                                             | 53 |

|          |                | 4.1.2   | Choice of hardware components                                   | 53 |

|          |                | 4.1.3   | Development environment                                         | 54 |

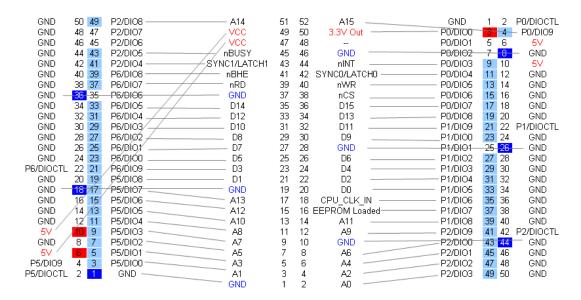

|          |                | 4.1.4   | Pin layout                                                      | 55 |

|          | 4.2            |         | ed component architecture                                       | 57 |

|          |                | 4.2.1   | Asynchronous 16-bit microcontroller interface                   | 57 |

|    |       | 4.2.2 SPI                                         | 60 |

|----|-------|---------------------------------------------------|----|

|    | 4.3   | Implementation of the host interface              | 63 |

|    |       | 4.3.1 Architectural overview                      | 63 |

|    |       | 4.3.2 Control logic                               | 64 |

|    |       | 4.3.3 SPI interface                               | 65 |

|    |       | 4.3.4 Microcontroller interface                   | 67 |

|    | 4.4   | Device and network configuration                  | 68 |

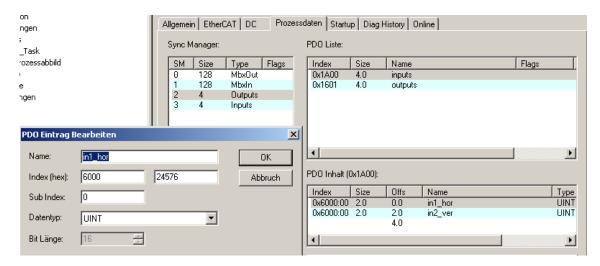

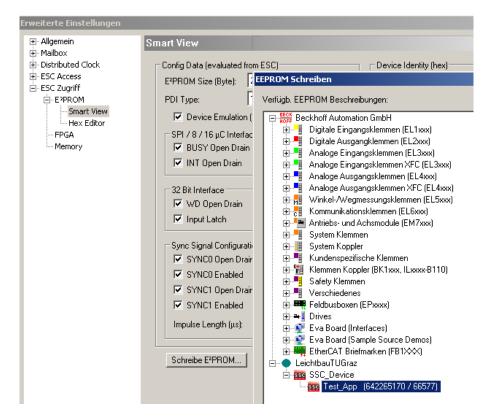

|    |       | 4.4.1 Configuring a slave device (SSC Tool)       | 68 |

|    |       | 4.4.2 Configuring the network (TwinCAT)           | 71 |

|    | 4.5   | Testing environments                              | 72 |

|    |       | 4.5.1 Single-loop interface test                  | 72 |

|    |       | 4.5.2 Performance test                            | 73 |

|    |       | 4.5.3 Two-way data transfer                       | 74 |

|    | 4.6   | Experimental results                              | 75 |

|    |       | 4.6.1 Timing behavior                             | 77 |

|    |       | 4.6.2 Functionality of the host interface         | 79 |

|    |       | 4.6.3 Two-way data transfer                       | 81 |

|    | 4.7   | Outlook and future work                           | 83 |

| 5  | Sun   | nmary                                             | 84 |

|    |       |                                                   |    |

| Α  |       |                                                   | 85 |

|    | A.1   | Real-time requirements                            | 85 |

|    | A.2   | Types of failure                                  | 86 |

|    | A.3   | Characteristic values of a communication system   | 86 |

|    | A.4   | Legend for HW architecture                        | 87 |

|    | A.5   | Definitions and abbreviations                     | 87 |

|    | A.6   | Pin layout for the adapter boards                 | 90 |

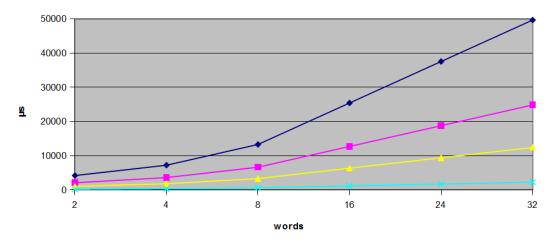

|    | A.7   | Performance analysis of the implemented interface | 91 |

|    | A.8   | Configuring TwinCAT (Screenshots)                 | 92 |

|    | A.9   | Hierarchy and file list of the implementation     | 95 |

| Bi | bliog | graphy                                            | 96 |

|    |       |                                                   |    |

# List of Figures

| 2.1        | Example of an <i>EtherCAT</i> network (from [Häf08])                                       | 17 |

|------------|--------------------------------------------------------------------------------------------|----|

| 2.2        | Example of an <i>EtherCAT</i> frame (from [ETG12])                                         | 18 |

| 2.3        | Nesting of the <i>EtherCAT</i> frame inside the Ethernet frame (from [ETG12]).             | 18 |

| 2.4        | Physical ring structure using cable redundancy (from [Häf08])                              | 20 |

| 2.5        | FMMU mapping example (from [Bec10])                                                        | 20 |

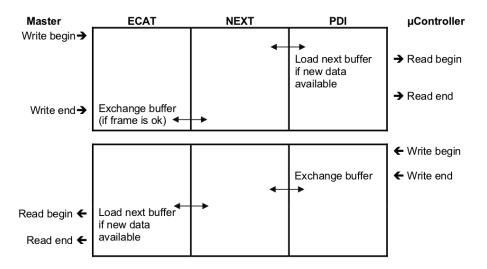

| 2.6        | Buffer interaction (from [Bec10])                                                          | 21 |

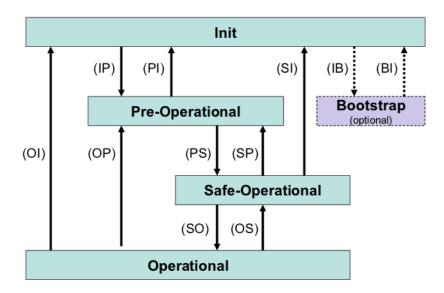

| 2.7        | The <i>EtherCAT</i> state machine, as defined in [Bec10]                                   | 22 |

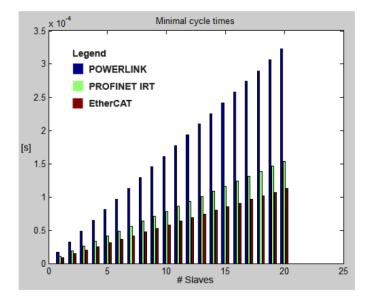

| 2.8        | Comparison of the minimal cycle time for an increasing number of network                   |    |

|            | participants (from [Spo10])                                                                | 26 |

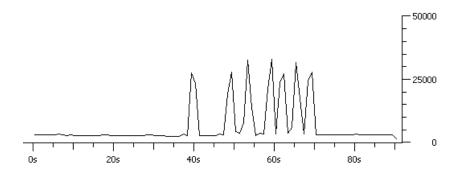

| 2.9        | Basic setup for the performance tests (from [Bru11])                                       | 31 |

| 2.10       |                                                                                            |    |

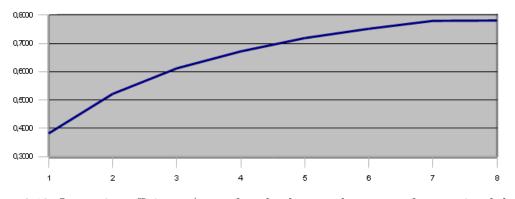

|            | for a growing number of bus participants (from [Bru11])                                    | 33 |

| 2.11       | Peaks in the frame rate [pack/s] when reconnecting all bus participants, one               |    |

|            | by one (from [Bru11]) $\ldots$                                                             | 34 |

| 3.1        | Architecture of a slave device                                                             | 38 |

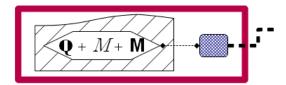

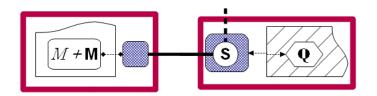

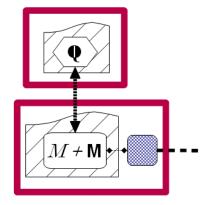

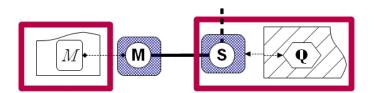

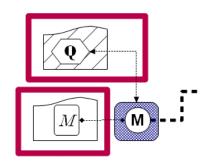

| 3.2        | 1. Shared host, implemented fully in software, integrated solution                         | 40 |

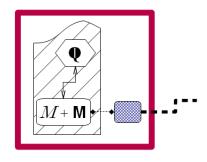

| 3.2<br>3.3 | 2. Shared host, implemented fully in software, distributed control                         | 40 |

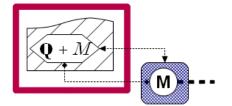

| 3.4        | 3. Shared host and ASIC, integrated solution                                               | 40 |

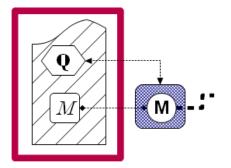

| 3.5        | 4. Shared host and ASIC, distributed control                                               | 40 |

| 3.6        | 5. Data and control path separated, implemented in SW                                      | 41 |

| 3.7        | 6. Multiple host, but common connection to the network                                     | 41 |

| 3.8        | 7. Multiple hosts; separation of data and network management                               | 41 |

| 3.9        | 8. Multiple hosts and shared ASIC                                                          | 41 |

| 3.10       | Proposed system architecture                                                               | 43 |

| 3.11       | Sample setup for an <i>EtherCAT</i> network, implementing different topologies .           | 46 |

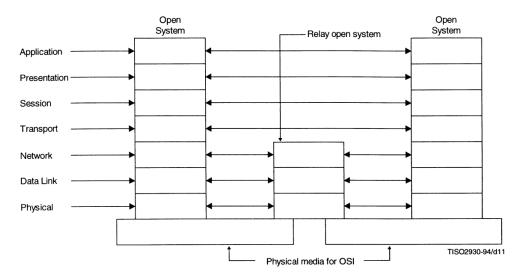

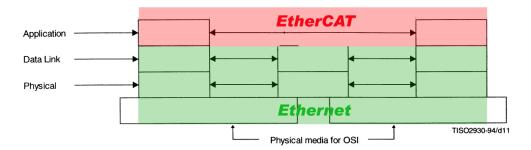

|            | The OSI reference model (from [ISO94])                                                     | 50 |

|            | Adaptation of the OSI reference model for <i>EtherCAT</i>                                  | 51 |

|            | Data flow                                                                                  | 52 |

|            |                                                                                            |    |

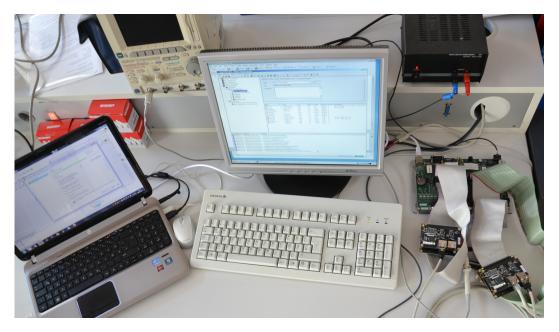

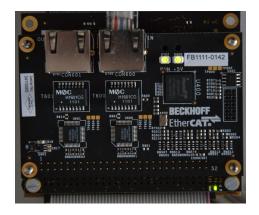

| 4.1        | The development environment                                                                | 55 |

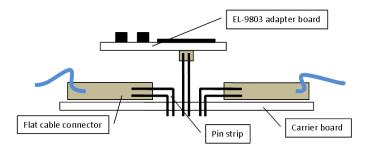

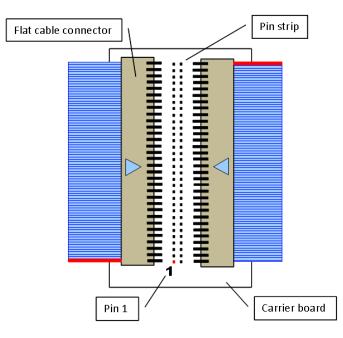

| 4.2        | Schematic view of the adapter board (horizontal view)                                      | 56 |

| 4.3        | Schematic view of the adapter board (top view)                                             | 56 |

| 4.4        | The piggyback controller mounted on the two adapter boards (side view) $\ .$               | 56 |

| 4.5        | $FB1111-142$ , LEDs in operational mode $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 56 |

| 4.6        | Architecture of the host interface as it is implemented                                    | 57 |

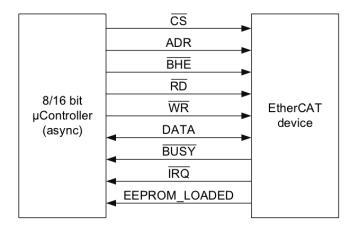

| 4.7  | Microcontroller interconnection (from [Bec10])                                       | 58 |

|------|--------------------------------------------------------------------------------------|----|

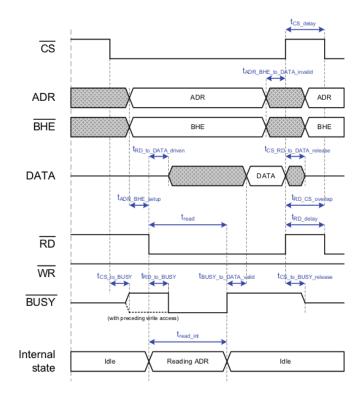

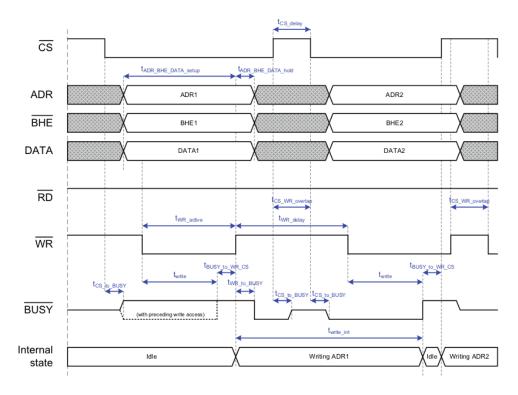

| 4.8  | $\mu$ C interface, read access (from [Bec10])                                        | 59 |

| 4.9  | $\mu$ C interface, write access(from [Bec10])                                        | 59 |

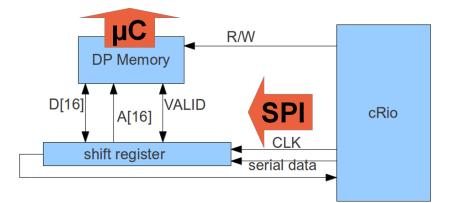

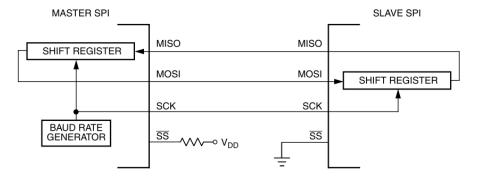

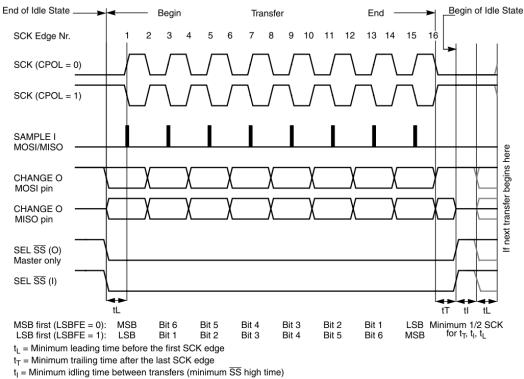

| 4.10 | SPI, transfer block diagram (from [Fre03])                                           | 61 |

| 4.11 | SPI, transmission cycle, $CPHA = 0$ (from [Fre03])                                   | 61 |

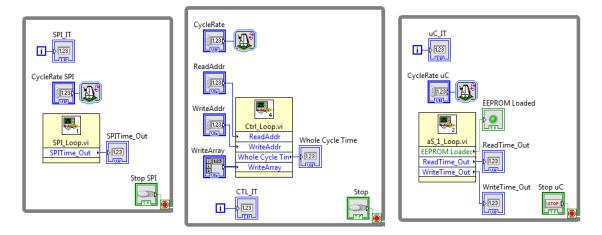

| 4.12 | The three parallel loops of a component                                              | 64 |

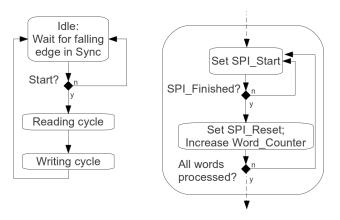

| 4.13 | The main control state machine (left: the task cycle; right: detailed se-            |    |

|      | quence for data transmission, i.e. reading and writing cycle)                        | 64 |

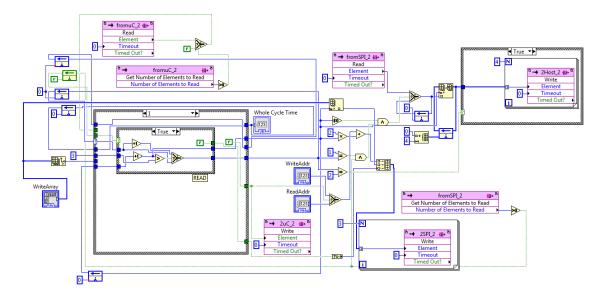

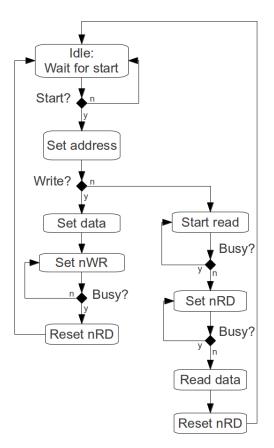

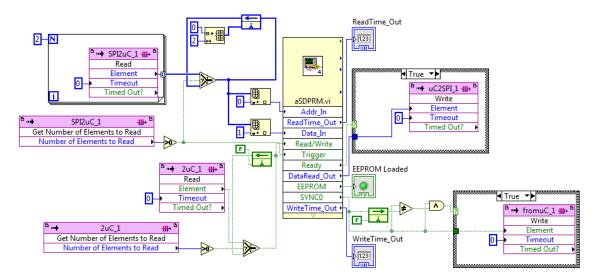

| 4.14 | Implementation of the control loop                                                   | 65 |

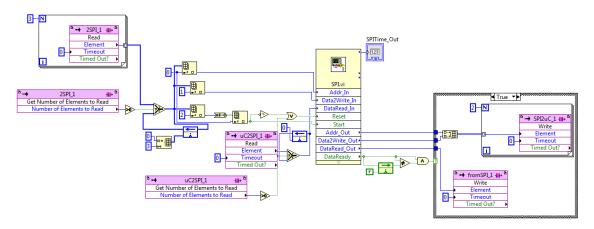

| 4.15 | Implementation of the SPI interface                                                  | 65 |

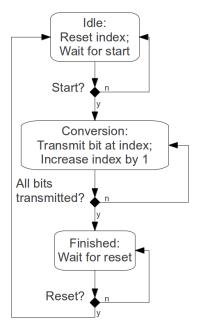

| 4.16 | State machine of the SPI interface                                                   | 66 |

| 4.17 | State machine of the $\mu$ C interface                                               | 66 |

| 4.18 | Implementation of the $\mu$ C interface                                              | 67 |

| 4.19 | The Slave Stack Code Tool                                                            | 68 |

| 4.20 | Cumulated ESI EEPROM settings                                                        | 71 |

| 4.21 | The structure of the test environment for the single-loop test                       | 73 |

| 4.22 | Additional pins for timing measurements ( <i>black</i> : signal; <i>green</i> : GND) | 74 |

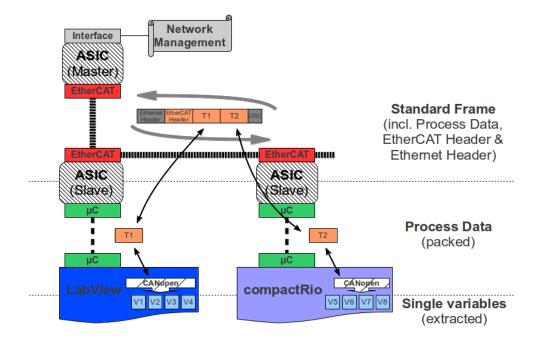

| 4.23 | Data transfer in the sample network                                                  | 75 |

| 4.24 | The two <i>EtherCAT</i> devices and the <i>sbRio</i> FPGA board                      | 76 |

| 4.25 | The user interface for the single-loop test                                          | 77 |

| 4.26 | The SYNC0 signal                                                                     | 78 |

|      | Jitter of the SYNC0 signal                                                           | 78 |

|      | Sampling of SYNC0                                                                    | 78 |

|      | Software loop timing                                                                 | 78 |

| 4.30 | Analysis of the network traffic in Wireshark                                         | 80 |

|      | Difference between the values of the current and the preceding frame                 | 81 |

|      | User interface for the data exchange test                                            | 82 |

|      | Disconnection and reconnection of one device                                         | 82 |

| 4.34 | Schematic of a hardware solution                                                     | 83 |

| A.1  | Symbols used for the HW architecture sketches                                        | 87 |

| A.2  | Pin mapping $FB1111$ - $sbRio$ (for connection to the pin bars P3 and P5)            | 90 |

|      | Pin mapping $FB1111 - sbRio$ (for connection to the pin bars P2 and P4)              | 90 |

| A.4  | Transmitted data versus execution time                                               | 91 |

| A.5  | Configuring a process data object                                                    | 92 |

| A.6  | Write ESI to EEPROM                                                                  | 93 |

| A.7  | Configuring inputs and outputs                                                       | 93 |

| A.8  | Configuring the FMMUs                                                                | 94 |

| A.9  | Setting up the reference clock                                                       | 94 |

| A.10 | Hierarchy of the submodules for one component                                        | 95 |

# List of Tables

| 2.1 | Properties of the expected data                                       | 13 |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | Main sections of the $ET1100$ 's EEPROM, as defined in [Bec10]        | 24 |

| 2.3 | Network device vendors and products                                   | 29 |

| 3.1 | Data rates, payload only                                              | 37 |

| 3.2 | Comparison of host interfaces                                         | 49 |

| 4.1 | The signals of the $\mu$ C interface                                  |    |

| 4.2 | Configuration of the FIFOs                                            | 63 |

| 4.3 | Modified registers in the ESI comparing to the <i>EL9800</i> settings | 69 |

| 4.4 | ET1100 ESI EEPROM Configuration                                       | 70 |

| 4.5 | Device settings for testing                                           | 76 |

| 4.6 | Execution time measurement                                            | 79 |

| A.1 | Measuring units                                                       | 87 |

| A.2 | Prefixes                                                              | 88 |

| A.3 | International standards                                               | 88 |

| A.4 | Abbreviations                                                         | 89 |

| A.5 | Performance analysis: Task cycle modification                         | 91 |

| A.6 | Performance analysis: CPU cycle modification                          | 92 |

| A.7 | Submodules used in the implementation of the $\mu$ C interface        | 95 |

## Chapter 1

## Introduction

#### 1.1 Motivation

The Institute of Lightweight Design, Graz University of Technology, develops and runs test benches for fatigue testing of mechanical components. Each test setup consists of several servo-hydraulic test cylinders and peripheral sensors of various types. The whole setup is connected to a mainframe computer running a dedicated state-of-the-art control system (HW: *IST LabTronic 8800*, SW: *IST LabSite Modulogic*). Presently all components are connected by analogue signaling and each is using a separate controller. The proprietary communication protocol used for communication between the components and the mainframe computer is restricting a further enlargement or optimization of the present installation.

For future improvement the test cylinders with attached sensors shall all be equipped with intelligent cylinder controllers (compactRio from NI) and the number of channels for each unit shall be extended, thus expanding the overall performance of the installation. For that purpose a high performance bus is needed to cover all traffic and an interface to both, power PC and component controller, should be designed. This task should be accomplished by using standardized hardware. Both synchronous and asynchronous data transfer shall be supported and real-time requirements must be fulfilled.

By these improvements, not only the scalability of the test setup but also the flexibility and performance will be increased considerably. Among other features, a faster calibration and a simple reconfiguration of single components or a whole test setup and the possibility of distributed computations on the separate FPGAs will be possible.

#### 1.2 Goal

A 'smart control' communication will be designed using an established technology and standardized hardware. During a preceding project, *EtherCAT* was chosen as preferred communication concept and its suitability for deployment was tested.

This work covers all necessary steps to the final implementation based on this technology: the creation of a detailed specification and system architecture, the implementation of a prototype, including additional peripheral hardware or libraries eventually needed. The prototype bus will be implemented in software on a FPGA and tested with regard to the target environment. The final goal is a fully operational prototype of a communication system for distributed computation, measurement and automation environments, which satisfies high demands regarding performance, quality and real-time behavior.

#### 1.3 Outline

It is presumed that the reader of the work at hand is familiar with the concepts and basic functionalities of computer networks and communication in measurement and automation systems; the fundamentals of digital communication are assumed to be known. Therefore topics such as the functional principle of the Ethernet bus and fieldbus systems (e.g. CAN), network topologies or communication protocols are not explained in detail.

Chapter 2, *Related work, technologies, and system characteristics*, first presents use cases for the communication network to be designed (section 2.1.1). Based on these use cases, general requirements for a real-time system are derived in section 2.1.2. In section 2.1.3, definition and terms of *Quality of service* are introduced.

The communication technology used is presented in section 2.2.1. After a detailed description of EtherCAT related concepts and works are discussed and a comparison is made in section 2.2.2. Existing industrial solutions are presented in section 2.2.3. The chapter is concluded by a description of performance tests which were performed on an EtherCAT network (section 2.2.4).

In chapter 3, *Design of a runtime-reconfigurable real-time communication system*, first additional requirements for the operation of the communication network in the target environment are defined (section 3.1). In section 3.2 the architectural concept of the separate network components are shown. Then a topological overview over the whole communication path is given in section 3.3.

A discussion of possible interface protocols for the connection of a communication module to a specific host unit can be found in section 3.4.1, followed by a description of the HW/SW layer concept in section 3.4.2. A presentation of the data flow (section 3.4.3) on the transmission channel concludes this chapter.

Chapter 4, Implementation of the real-time communication system and its separate components, is dedicated to the actual implementation of the communication system. After some preliminary remarks on the development process and environment in section 4.1, a detailed description of the architecture of a communication component is presented in section 4.2. In section 4.3 the actual implementation of the host interface is described. The configuration of the network and its individual components is addressed in 4.4. Finally, the testing of the prototype device is covered in the sections 4.5 and 4.6.

The concluding chapter 5 summarizes the findings and outcomes of this work and gives an outlook on future topics in this field of research.

## Chapter 2

# Related work, technologies, and system characteristics

#### 2.1 Test bench and automation system characteristics

The requirements listed in this chapter were identified during a preceding project on the matter of real-time communication systems [Bru11]. The structure and proceeding of this work followed the 4+1 Layer Model by [Kru95]. In this concept, the starting point for the determination of requirements are use cases. The granularity of these use cases defines the degree of detail of the deduced system requirements. In section 2.1.1, typical use cases for the given task are listed. Additionally, knowledge about the kind and amount of data which will be transmitted over the network is necessary. Therefore the data traffic to expect is specified first in section 2.1.2) before the actual requirements are defined.

#### 2.1.1 Use cases

Use cases represent working conditions and examples which make it easier to identify and defined specific requirements for the communication system. This section covers all use cases as given in [Bru11]. Based on these use cases, test cases were defined which are described later in section 2.2.4. The following list was slightly adapted comparing to the one in the original document.

#### Data transfer in normal operation mode

In normal operation mode, the mainframe computer performs periodic calculations and sends commando data to the sensors and actuators. At the same time, those components are gathering measurement data, process this data and send it back to the mainframe PC. All data must be transferred during one transmission cycle to guarantee the real-time behavior of all components and the overall system. In each time step, each unit must be given the opportunity to send its data and receive all data addressed to it. The data transmission has to be correct and reliable. The actual amount of data can vary for each time step, but the variation is small compared to the overall volume. So one can expect a relatively steady stream of data with hard real-time requirements.

#### Parametrization of a component

Changes in a test process may require modifications in the test bench's setup and reconfiguration of sensors or actuators. Therefore it is necessary to send a larger amount of acyclic parametrization data to the affected component to reconfigure it. This transfer is done in aperiodic transmission mode with relaxed requirements regarding real-time characteristics. Nevertheless, the integrity of the transferred data must be guaranteed. The data can be transferred to the single components either in a serial or a parallel way.

#### Initialization

When the hardware setup was changed (regarding the number of devices and/or the cabling of the components), the communication network will need a reinitialization. This procedure imposes no restrictions regarding real-time behavior or correctness of the received data. The important thing is to check the basic functionality and detect the current settings of the network and of all of its components and store the new scheme in an appropriate way, if needed. The generation of this scheme can be done fully or half automated, or even by hand.

#### Checking the setup

After a successful initialization, the network, all its components and the configuration of the communication path shall be checked. For this purpose a special test procedure is initiated by the network master (typically the mainframe computer). This procedure is designed to check as much sources of failure as possible and get detailed state and error information out of the system's response. If any irregularities or errors occur the setup has to be checked, modified by the user, or even reconfigured if need be. In case of a spurious alarm the test procedure itself should be reviewed.

#### Failure of a component

When a network component fails, the bus master, the mainframe PC, and all affected components have to be warned. The data transfer within the remaining network shall be maintained as best as possible to either continue normal operation, allow a controlled shut down, or any other failure reaction. The error message should contain enough information about the failure to decide which error reaction to start and to come to a detailed conclusion about the state of the remaining network.

#### Changing the setup at runtime

When one or more new components are installed on the communication system, it should be capable of detecting automatically the changes and include the new bus members in the normal operation. If this is not possible, at least the ongoing data transmission inside the original network must not be influenced and the new components shall be activated at the time of the next initialization. In that case, all excluded units must not be considered for the ongoing traffic in any way, nor be activated accidentally. In case of a controlled shut down and removal of one or more components, the functionality of the remaining network must not be affected in any way.

#### 2.1.2 System requirements

#### Properties of the expected data flow

The following table 2.1 states the expected types of data and their main properties and requirements for the communication system:

| Type of data | Real-time | Tolerable | Error                     | Highest  | Error      | Resend |

|--------------|-----------|-----------|---------------------------|----------|------------|--------|

|              |           | latency   | detection<br>in real-time | accuracy | correction |        |

| Measurement  | x         | very low  | х                         | х        | x          |        |

| Commando     | х         | very low  | х                         |          | х          | х      |

| Parameter    | х         | low       | х                         | х        | х          | х      |

| Calibration  |           | high      |                           | х        | х          | х      |

| Setup        |           | high      |                           |          |            | x      |

Table 2.1: Properties of the expected data

The cyclic measurement data makes clearly the highest demands on the communication channel. Commando and parameter data shall reach their target in real-time, as well, but are less frequent and generally of smaller size. When calibrating a device over the network, it is not necessary to perform the task in a given time, but the received data must be correct. Finally, best effort is enough for data to setup and initialize the network.

#### **Functional requirements**

- 1. The data stream of each unit is split into logical channels. The mapping and throughput of those channels must be adjustable during run time.

- 2. The data transfer must meet hard real-time requirements, i.e. all data sent in one time slot must reach its recipient within a well specified time of delay (typically the same time slot). Additionally, the integrity of the transmitted data must be guaranteed. For a list of real-time requirements typically used see appendix A.1.

- 3. To satisfy point 2, the traffic should be of a synchronous nature. An asynchronous mode for non-time-critical data is advisable but not obligatory. The synchronous transfer mode should support both, a periodical operating mode for traffic of measurement and commando data, and an aperiodic mode for calibration and parametrization data. The switching between modes, resp. combinations of them, should be possible at run time.

- 4. It should be possible to activate and deactivate single transfer units or parts of the communication bus without affecting the functionality of the remaining network. There should be the possibility to connect several independent test benches (each representing a subnetwork) to a common bus, as long as all participants are controlled by the same central computer. This requires the mapping of data to single units to be done in the mainframe PC and to be transparent on the bus; thus, a perfect data encapsulation is necessary.

- 5. A fully automated and self-controlled initialization routine is desirable. This includes the special benefit of operating small networks without a main computer (e.g. communication between slave devices).

- 6. All transmitted data must not be modified, corrupted, or affected in any other way by the transmission path. It must be possible for the recipient to check the integrity and correctness of the received data. This should be accomplished by a suitable data structure (e.g. *CRC*). The correctness of the data should be verifiable on both ends of the transmission path – sender and receiver – to guarantee an error detection as fast as possible. This can be done using a special protocol (e.g. *handshake*).

- 7. After the installation of the communication bus in the laboratory, the network might need some adaptations to the actual setup of the testing bench. These adjustments can be performed either automatically, supported by software tools, or manually. During this configuration phase, modifications on the communication system may be required.

After concluding the configuration, the system should be available immediately without any additional configuration and provide full functionality at any time. At run time, no readjustment of the system's structure should be necessary. Between hours of operation, adaptations of the bus are allowed only in case of major changes in the setup, including maintenance operations or modifications in the bus's cabling or the hardware of the main computer, or installation of new bus participants. Changes of the bus topology (e.g. replugging of components) should require no reconfiguration. At each start up the network should perform a short routine to initialize, activate and check the correct behavior of all bus components.

8. If a failure occurs in any part of the system, the functionality of the remaining network should be maintained as best as possible. Depending on the severity of the failure, this might include further normal operation, a (more or less) complex error reaction, or a controlled emergency shut down in the worst case. The topology of the communication system should be chosen in a way that the failure of one component has the least impact on the overall system.

The error detection should satisfy the same timing demands as the data transfer. The reaction on a failure must not affect the ongoing data transfer, running in realtime. All requirements stated earlier in this section must be met to full extent for all possible types of failure, as listed in appendix A.2.

#### Architectural requirements

1. A simple change in the setup – if the number of components does not change – must be possible without leading to any data loss or restrictions regarding the performance or the functionality of the network. The same goes for expanding of the bus. However, in this case, minor activities for adjustment and reconfiguration are tolerable. The limit for the extensibility of the installation, caused by restrictions inherent in the technology, should be some degrees above the bench mark of a network consisting of 24 components, with four transmission channels each.

2. In case of maintenance, all parts of the system should be replaceable independently from each other. In this context, 'a part' is the communication interface of one unit or the mainframe PC, or the cabling. The replacement of one part by an equivalent one should lead to no additional effort for adjustment or reconfiguration on the network.

It is strongly recommended that the architecture of the communication system supports the replacement of single parts by superior or newly developed devices, as long as they are fully compatible to the existing setup. Thus the limits for compatibility and upgrading of network components should only be a matter of the manufacturers requirements and implemented features.

3. While running, the communication system must not influence its peripheral devices or any ambient parts of the test bench in any way. This is especially important regarding EMC.

All modifications to the existing test bench setup due to the installation of the communication system should be minimized and not affect its behavior. Losses in performance or functionality are tolerable under no circumstances. Adaptation of existing software is acceptable, as long as it is a matter of extension or reconfiguration and induces no further modification of its functionality.

#### 2.1.3 Quality of service

The term 'QoS' is often used without a significant definition. In the context of this work, the term includes all requirements regarding real-time behavior and data integrity as described in chapter 2.1.2. For further clarification, in this section the term 'QoS' is inspected from a different, more general point of view by taking a closer look at the key features of QoS. This approach is based on [OY08]. Generally, the required level of QoS for this project can be specified as the highest level, known as *hard QoS* or *guaranteed service*.

- Accessibility: The accessibility rate of the communication system is 'full access', precisely 100%. This means that no regular access to the bus is denied or ignored; a 'regular' access can only be done by the device currently holding the token (Ethernet frame). The second parameter for accessibility, the total number of incoming requests, is defined for this condition to be exactly 1. Any violation of these two criteria is clearly a severe malfunction according to the EtherCAT specification and has immediately to be dealt with.

- **Availability:** Similar to accessibility, the system has to be fully available any time at runtime, resulting in an *availability rate* of 100%. The only exception for this rule is at the start-up of a bus participant or the network. For a (very limited) period of time the component or bus is allowed to run an initialization routine. Afterwards all unavailability is a failure.

- **Accuracy:** For accuracy the level 'precise' is expected. This is the highest level of accuracy. The *error rate* has to be extremely low, because in a real-time environment, in most situations there is not enough time to detect the error, report it and resend the affected data. A value very near the BER of a high-class Ethernet system is required.

All erroneous data must be strictly avoided, because in a distributed control system, even one faulty value might put high risk to the whole setup. This fact requires a very precise error detection logic with high-grade error correction, if available. Another important point is the timing behavior of the transmission path. As described in section 2.1.2, the reference time of the communication bus has to be very accurate to provide deterministic and constant values for RTT and jitter.

- **Reliability:** Reliability is a measurement for the robustness and stability of the communication system. For services in a distributed real-time setup, it is required that the network is absolutely reliable. This includes mechanisms for early-detection of possible threads, such as failure of a bus participant, or when a value of the transfer characteristics (e.g. RTT or jitter) is exceeding its tolerance.

- **Performance:** The performance of a system can be expressed in two dimensions. The *effectiveness* of the network generally measured by the *throughput* is highly depending on the technology used. Thus for defining a level, one can only refer to the minimum data rate required (a detailed definition of the throughput for the present work is given in chapter 3, table 3.1) and otherwise expect the system to be 'as efficient as possible'.

On the other hand, the *responsiveness* of the bus, including all devices involved, has to be as high as possible, satisfying the highest level, labeled as 'receptive'. Again, the actual values for *execution time* and *response time* are depending on the specific technology and the hardware in use; but bearing in mind that the bus is operated in a real-time environment, it becomes clear that no operation is allowed to take longer than one task cycle if time-critical data is involved. For network management and non-real-time data the level of responsiveness might degrade even down to 'just better than slow'.

#### 2.2 Ethernet-based fieldbus technologies

#### 2.2.1 EtherCAT

Description of the basic concept

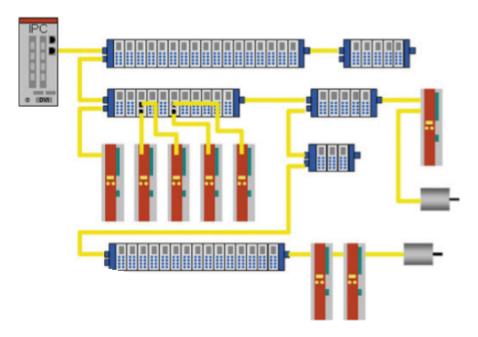

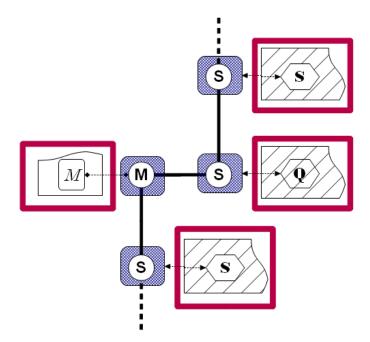

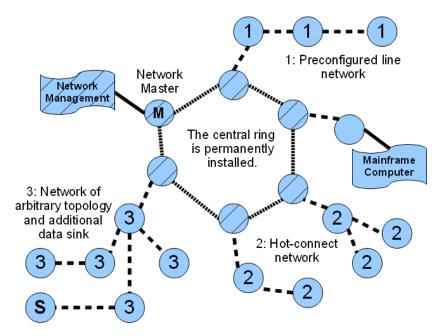

Figure 2.1: Example of an *EtherCAT* network (from [Häf08])

EtherCAT (Ethernet for Control Automation Technology) can be seen as a kind of fieldbus implementation which uses Ethernet as communication medium. Therefore, the main goals are high throughput of data of relatively small size, and satisfying high demands regarding quality and timing behavior. For a standard implementation of Ethernet, using CSMA/CD as arbitration scheme in a star topology network, these targets can only be achieved if special protocols and concepts are used, such as time slicing or polling. All these approaches lead to additional communication overhead, of course. To minimize this overhead, EtherCAT uses a logical ring structure, where a data packet is no longer received, processed and sent back by each bus participant, but passed around the bus, whereas each component reads and writes data to the frame on the fly. Thus, the delay time per frame and communication bus is a line topology, using a virtual logical ring, the structure of the communication bus is a line topology, using a virtual logical ring, the structure of the physical network can be chosen freely (see figure 2.1).

To benefit from existing technologies, the EtherCAT protocol is set on top of the physical layer of Fast Ethernet (IEEE 802.3u) and uses the standard Ethernet frame. This allows to keep the protocol up to date and fully operational for any possible current or future developments or improvements in the Ethernet technology and its components.

Basically, the *EtherCAT* telegram is holding a logical image of the process data, wherein each bus component is given a memory area to work on. The structure of this process data image is not depending on the actual setup of the communication network.

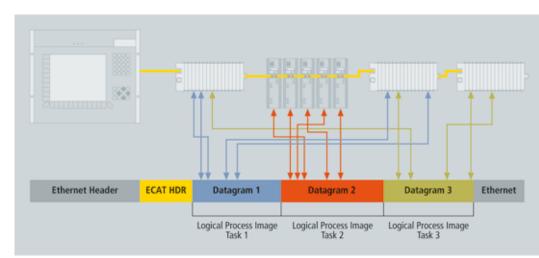

A sample correlation between an EtherCAT frame and the bus members may look as in figure 2.2.

Figure 2.2: Example of an *EtherCAT* frame (from [ETG12])

#### Protocol and frame format

The *EtherCAT* telegram is nested inside an Ethernet frame, which is generated by the network master. The frame starts with a 14 Byte Ethernet header and is terminated by the Ethernet CRC. The payload of the Ethernet frame is fully dedicated to the *EtherCAT* telegram. This section starts with a short header and holds one or more datagrams, which can be accessed by the bus participants according to their individual configuration. Besides the standard configuration, as shown in the upper part of figure 2.3, there is also

|                        | Ethernet Header |            | ECAT      |            | EtherCAT Teleg | jram |            | Ethe  | rnet |

|------------------------|-----------------|------------|-----------|------------|----------------|------|------------|-------|------|

| DA                     | SA              | Туре       | Frame HDR | Datagram 1 | Datagram 2     |      | Datagram n | Pad.  | FCS  |

| (6)<br>Ethertype 88A4h | (6)             | (2/4)      | (2)       | (10+n+2)   | (10+m+2)       |      | (10+k+2)   | (032) | (4)  |

|                        |                 |            |           |            |                |      |            |       |      |

| Ethernet<br>Header     | IP Header       | UDP Header | ECAT HDR  |            | EtherCAT Teleg | ,ram |            | Ethe  | rnet |

Figure 2.3: Nesting of the *EtherCAT* frame inside the Ethernet frame (from [ETG12])

the possibility to use IP services and send UDP packets over the EtherCAT bus. For this purpose, the relevant information is added to the header (see lower part of figure 2.3). Each *EtherCAT* slave receives the full telegram, reads and writes the memory block assigned to himself and passes the frame to the next slave on the line. The processing of the frames is done 'on the fly' – in contrast to the store-and-forward principle of standard

Ethernet devices. The resulting transmission delay per device is very low (approx. 1  $\mu$ s). Of course, this feature needs a special kind of hardware, described in *EtherCAT hardware*.

The *EtherCAT* network can work without an explicit addressing scheme; each slave is identified by its place on the line. But explicitly addressing one or more slaves is possible, as well, and can be used for special purposes. For example, to integrate an EtherCATsegment into a larger network (e.g. by a switch), the first slave is addressed as entrance point to the network by its MAC address. For non-real-time applications, IP routing and the TCP/IP protocol as known from common Ethernet networks are supported, as well. The logical address space of the datagram – whose size is typically 4 GB [JB04] – is shared among all devices in the network. Each slave uses dedicated memory mapping units (FMMUs, explained below in *EtherCAT hardware*), which are individually configured for mapping its process data into the shared memory. A way for the master to keep track of read/write operations on the frame is the *working counter*. This counter is increased by every slave device which has just performed a data access with success. Another way of addressing the bus participants is, to distribute the available memory consecutively, depending on the order of the devices on the bus. Of course, a setup implementing such an addressing scheme would be rather inflexible at runtime. Broadcast messaging is also possible; it is typically used for device control and network configuration.

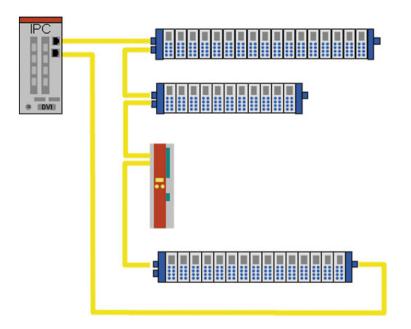

#### EtherCAT hardware

On the physical level, *EtherCAT* devices support two different protocols. One is an enhanced version of Ethernet, where special care is taken in link detection mechanisms and frame processing to guarantee real-time behavior. Each connector can detect whether it is connected to a carrier signal or not, and it is able to automatically close an open port by shortening it internally. Thus, each device can act both, as intermediate, and as terminal network node and even adapt dynamically to the current state of its network connections. This behavior is the basis for the *hot connect* feature, which allows a slave to be integrated in the network at any open connection, even at runtime. Before installing the device, it has to be given a unique ID to avoid confusion and additional traffic for reconfiguration. Furthermore, each communication device – called the *EtherCAT slave controller* (ESC) - is equipped with a minimum of two Ethernet ports - one 'input port' and one 'output port'. This is necessary to establish flexibility in the setup without needing hubs or network switches. When a second Ethernet interface is available at the master device, one of the unconnected ports of a slave device can be connected to it, thus creating a redundant communication path, which increases the network's robustness towards line breaks, as shown in figure 2.4.

The second protocol implemented on each ESC is the proprietary EBUS, which is designed and used as backplane bus and not intended for wire communication. It encapsulates the whole Ethernet frame and transmits it at a data rate of 100 Mbit/s, using *Low Voltage Differential Signaling* (LVDS) applying to ANSI/TIA/EIA-644 [Bec10].

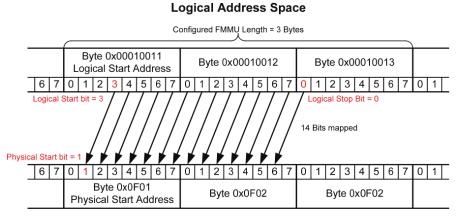

The task of internally mapping physical addresses to logical addresses and back is performed by each device's *Field Memory Management Unit* (FMMU). The FMMU is divided into channels which map a continuous logical address space inside the datagram onto a continuous physical address space in the slave's memory. Each channel can be freely configured to either perform read access, write access, or both (see figure 2.5).

Figure 2.4: Physical ring structure using cable redundancy (from [Häf08])

**Physical Address Space**

Figure 2.5: FMMU mapping example (from [Bec10])

To allow a consistent and secure data transmission between master and slave devices, EtherCAT uses a so called SyncManager. This unit manages the mutual access to the memory shared between the communication device (EtherCAT slave) and its host device. Basically, two communication modes are supported: buffered and mailbox. Buffered mode is typically used for cyclic process data. It is based on a producer-consumer scheme. The usage of three separate memory areas, where each is holding a full copy of the process data, enables both participants to access the same data at the same time without the risk of losing consistency of the transmitted data. A buffer must always be read from start to end; random access is not possible. The buffer access strategy is shown in figure 2.6.

Figure 2.6: Buffer interaction (from [Bec10])

The second communication mode, mailbox mode, allows no parallel access on the process data image; it can either be read or written – again, only the complete buffer at a time. But on the other hand it makes the usage of elaborate transmission protocols possible. In mailbox mode, EtherCAT supports Ethernet over EtherCAT (EoE), CANopen over EtherCAT (CoE), File Access over EtherCAT (FoE), and more. Advanced communication principles, such as handshake and repeat/request schemes, are supported, as well.

#### **Distributed clock**

For accurate synchronization of all bus participants, EtherCAT uses a so called *distributed* clock (DC). This concept uses a master clock signal – a time stamp typically derived from the internal clock of the first slave in line after the network master – which is broadcast periodically. All other network devices tune their internal clock to this signal. For additional accuracy, the propagation delay is measured and sent to the master. Based on the gathered information, the network master calculates the actual offset for each device and returns the resulting value to improve the compensation.

Based on the distributed clock, each slave can generated one or two synchronization signals. The two signals can each be driven in one of two modes: *sync* as input, or *latch* as output. The sync signals can be used for the generation of internal or external interrupts,

or as clock signal for an external device (e.g. the host interface). The first signal (SYNC0) is derived from the internal clock of the ESC and its timing behavior can be configured as cyclic or as event based. The second signal (SYNC1) is always derived from SYNC0, as an integer multiple of it, and with a configurable delay. Latch signals are used for generating internal events which are triggered by an external source.

The most important category of events are *interrupts*, which are distinguished by there purpose: AL event requests (PDI interrupts) are used to inform an attached microcontroller about changes in the PDI; and ECAT event requests (ECAT interrupts) to inform a master about slave events. Which interrupts to sent and which to suppress is defined in the corresponding Interrupt Mask Registers. These registers are combined with the actual interrupt registers by a logical AND, thus allowing or denying an event to be set on the interrupt line when generated.

#### EtherCAT state machine

In the *EtherCAT state machine* (ESM), the different operational conditions of master and slave devices are represented as states. Typically, the state of each slave device is set and continuously monitored by the master using the *AL control* and *AL status* registers. In case of misconfiguration or internal errors, an unexpected change in a device's state or not following the master's request, signals the master a problem at the specific device. The five states defined and all possible transitions are shown in figure 2.7.

Figure 2.7: The *EtherCAT* state machine, as defined in [Bec10]

A slave's operational status and all associated errors or warnings are stored in dedicated registers. These registers can be accessed by the master. Whereas the state of a slave device with an attached microcontroller is usually controlled by the host, devices in basic configuration are used in *device emulation* mode. In this mode, the content of the AL control register – the state request – is directly copied to the AL status register by the ESC; the master is in direct control of the specific slave device.

#### Memory management

The memory of an *EtherCAT* slave is typically a serial EEPROM with  $I^2C$  interface, using an address space of 64 kB. The related address space is divided into two parts: The ESI and the process RAM. The ESI (*EtherCAT* slave information) part spans a range of 4 kB – from 0x000 to 0x0FFF – and contains all device specific information, stored in registers. The process data section starts at address 0x1000 and is handled as block memory.

Table 2.2 gives an overview of the main sections, each with a short description. The registers and address space of this list show the configuration for the ASIC ET-1100; which registers are actually present and configurable varies depending on the ESC and the variant used. Not all bytes covered by the address range contain relevant information for this variant of the device; therefore the number of registers actually in use is given separately.

The main part of the ESI registers can only be changed using a special tool (for details see chapter 4.4.1) and has to be flashed into the EEPROM before the device can be activated. For each type of *EtherCAT* device a dedicated configuration exists, mostly provided by the manufacturer. The usage of the last memory section, reserved for process data, can be configured freely. Each device is assigned an address range for reading and writing, whereas address ranges of different slaves can be configured overlapping, thus allowing them to exchange data without requiring the network master to perform data routing.

To access the process data RAM as host, several interfaces are supported, of whom one has to be selected when configuring the ESC. In the following list, all interfaces basically supported by the ET1100 ASIC are highlighted:

- Interface deactivated

- Digital I/O (32 freely configurable I/O lines)

- SPI Slave

- EtherCAT Bridge (for switching functionality)

- 8-/16-bit asynchronous microcontroller ( $\mu$ C) interface

- 8-/16-bit synchronous  $\mu$ Cinterface

- On-chip bus

As some interfaces need dedicated hardware, the piggyback controller boards using this ASIC generally support only a subset of the interfaces listed above. At start-up, the PDI becomes active after the ESI EEPROM was loaded successfully. Until then, and in case of EEPROM failure, all PDI pins are kept inactive.

| Address                                                                            | Length<br>(Byte) | Description                                      |

|------------------------------------------------------------------------------------|------------------|--------------------------------------------------|

| 0x0000 - 0x0009                                                                    | 10               | ESC Information                                  |

| 0x0000 - 0x0009                                                                    | 10               | Type, revision, RAM size, ESC features, e.a.     |

| 0x0010 - 0x0013                                                                    | 4                | Station Address                                  |

| 0x0010 - 0x0013                                                                    | 4                | Configured station address and alias             |

| 0x0020 - 0x0031                                                                    | 4                | Write Protection                                 |

| 0x0020 - 0x0051                                                                    | 4                | Settings for write protection                    |

| 0x0040 - 0x0111                                                                    | 10               | Data Link Layer                                  |

| 0x0040 - 0x0111                                                                    | 10               | Settings for the ESC's DL                        |

| 0x0120 - 0x0139                                                                    | 8                | Application Layer                                |

| 0x0120 - 0x0139                                                                    | 0                | AL control, AL status, e.a.                      |

| 0x0140 - 0x0153                                                                    | 14               | PDI                                              |

| 0x0140 - 0x0103                                                                    | 14               | PDI control and configuration settings           |

| 0x0200 - 0x0223                                                                    | 12               | Interrupts                                       |

| 0x0200 - 0x0223                                                                    | 12               | ECAT and AL event requests and event masks       |

| 0x0300 - 0x0313                                                                    | 10               | Error Counters                                   |

| 0x0300 - 0x0313                                                                    | 19               | Communication, operation and PDI errors          |

| 0x0400 - 0x0443                                                                    | 18               | Watchdogs                                        |

| 0x0400 - 0x0443                                                                    | 10               | Watchdog configuration                           |

|                                                                                    |                  | ESI EEPROM Interface                             |

| 0x0500 - 0x050F                                                                    | 16               | EEPROM configuration, incl. access and           |

|                                                                                    |                  | control state, address, e.a.                     |

| 00510 00511                                                                        | 10               | MMI Management Interface                         |

| 0x0510 - 0x0511                                                                    | 12               | Configuration of the PHY interface               |

| 0.0000 0.0000                                                                      | 10 10            | FMMU                                             |

| $0 \ge 0 \ge$                      | 16x16            | Configuration of the FMMU(s) (16 units possible) |

|                                                                                    |                  | SyncManager                                      |

| 0x0800 - 0x087F                                                                    | 16x8             | Configuration of the $SyncManager(s)$            |

|                                                                                    |                  | (16  units possible)                             |

| 00000 000EE                                                                        | 199              | Distributed Clock                                |

| 0x0900 - 0x09FF                                                                    | 133              | Detailed configuration of the DC                 |

| 00E00 00EEE                                                                        | 956              | $ESC \ specific$                                 |

| 0x0E00 - 0x0EFF                                                                    | 256              | Power-on values, product and vendor ID, e.a.     |

| $\Omega_{-}\Omega_{-}\Omega_{-}\Omega_{-}\Omega_{-}\Omega_{-}\Omega_{-}\Omega_{-}$ | 90               | Digital Input/Output                             |

| 0x0F00 - 0x0F1F                                                                    | 20               | General purpose input and output registers       |

|                                                                                    | 20               | User RAM / Extended ESC features                 |

| 0x0F80 - 0x0FFF                                                                    | 20               | Additional and user defined features             |

|                                                                                    | 0000             | Process Data RAM                                 |

| 0x0100 - 0x2FFF                                                                    | 8000             | Address space for process data                   |

Table 2.2: Main sections of the ET1100's EEPROM, as defined in [Bec10]

#### 2.2.2 Competitive technologies

As the settings and requirements for this project are common for industrial applications, there exists a number of projects and products pursuing the same goal. Some solutions use a very different approach, some may seem very much identical. For an overview on fieldbus-like communication concepts see [Sau10]. In a preceding project, the most common technologies were inspected regarding their qualification for the implement of a communication system which combines very high performance and flexibility, guarantees robustness and meets all requirements of a real-time system. One outcome of this comparison was, that no other systems than Ethernet-based ones are capable of fulfilling all the required criteria. Therefore only these technologies are mentioned below. A more detailed discussion on the topic can be found in [Bru11].

The following section first explains some of the most established concepts and discusses their main advantages and disadvantages (especially when compared against EtherCAT), then takes a closer look at companies providing solutions and producing hardware, which share the same scope as the work at hand. Because of their vast number, this listing can neither claim to be complete, nor representative; the focus is set on important vendors for measurement and automation systems in Central Europe, namely in Germany and Austria.

#### PROFINET

PROFINET (PROcess FIeld NETwork) is a communication bus system which was formerly developed by Siemens but now is an open standard, maintained by the PROFIBUS International (PI) group. The concept complies to the IEEE 802.3u, the IEC 61158 and the IEC 61784. There are different default settings which allow to adapt the bus to a certain usage profile. The only one suitable for a real-time system is the so called PROFINET I/O configuration. It supports isochronous real-time data transfer and a transmission cycle time down to 1 ms [Fel04].

A PROFINET network consists of at least one master device and one or more I/O devices, each one addressed by its MAC address. The communication principle in use, to provide guaranteed bandwidth for time-critical applications, is a time slicing mechanism. Each transfer cycle is split into a time-critical and a non-time-critical window. In the latter one, all stations are allowed to submit any kind of traffic, typically UDP/IP for parameters and network management. A priority scheduling mechanism allows further traffic shaping at runtime. In case of a collision, the situation is handled as known from the CSMA/CD mechanism. To avoid collisions in the critical time zone, switches are used. Together with a network plan (defined before the start-up of the network), it is possible to treat real-time data separately and thus guarantee full QoS for the communication path. A predefined network map also permits a certain level of optimization. Furthermore, there is a possibility to classify the real-time traffic in three classes with different QoS objectives. Other features of this technology are auto-negotiation of the network settings, support of full-duplex mode in a 100Base-TX Ethernet environment (100 Mbit/s), and possible usage in any upcoming extension of the standard.

A big advantage of *PROFINET* is that it is fully based on and compatible to international standards, which allows the use of any Ethernet device from any vendor as long as it complies itself with these standards. This extends the range of hardware and makes inexpensive solutions and simple maintenance possible. On the other hand, the use of time slicing reduces the efficiency of the network when the number of bus participants is increasing [Pry08]. This is caused by a fixed communication overhead per station; although in *PROFINET* some of this loss can be regained by optimization. A comparison of the minimal cycle time is shown in figure 2.8. Another weak point is the missing flexibility of a *PROFINET* setup at runtime. To profit from optimization, a network plan has to be defined and processed before starting the network traffic. So there is very little possibility to switch bus participants afterwards - and much less to add a device, or make changes in the topology while a transmission is ongoing.

Figure 2.8: Comparison of the minimal cycle time for an increasing number of network participants (from [Spo10])

#### POWERLINK

The company Bernecker + Rainer (B&R) developed the Ethernet POWERLINK as protocol enhancement to the IEEE 802.3u standard. It is now maintained by the open Ethernet Powerlink Standardization Group (EPSG). Similar to PROFINET presented above, POWERLINK uses a time-slicing mechanism, but combined with polling. This concept is called Slot Communication Network Management (SCNM).

A POWERLINK network consists of one master device (called *master node*) and several slave devices (called *controlled nodes*). The number of participants of such a subnet is limited by the applied addressing scheme to 240 devices. Larger networks can only be assembled by connecting these relatively small subnetworks with hubs [EPSG08]. POW-ERLINK is fully compatible with the IEEE 802.3u standard and can therefore be run on any Ethernet hardware available. QoS and real-time behavior is guaranteed be the polling mechanism. Each node is given a unique ID and a unique time slot in each transmission cycle. Each device is only allowed to send, when polled by the network master. The polling scheme has to be defined and loaded to the master before start-up. If not all time slots are needed, the remaining time is typically shared by all bus participants using the usual CSMA/CD access scheme.

An advantage of this concept is clearly that by using *polling*, no time synchronization among the bus participants is needed. However, regarding efficiency this mechanism is very weak (see figure 2.8), because the communication overhead for each additional device in the network is not negligible. Using optimized network plans, *POWERLINK* can decrease this overhead when several devices are scheduled for the same time slot but in different cycles, for example. Another way of reducing the delay between two network nodes is to use a *poll-response request* which allows all other nodes to read along the response of the polled node and thus saving the time for transmitting the data first to the master and onwards to the receiving node. The network plan, used for the polling mechanism, can be changed at runtime which allows *POWERLINK* a higher degree of flexibility.

#### SERCOS

SERCOS is a communication interface, first introduced in 1985 for motion control and automation systems. It is standardized in the IEC 61491. Over the years the concept, first conceived for analogue data transfer, was adapted to modern communication technologies and is now available for Ethernet systems under the name of SERCOS III. The concept is driven by the SERCOS International (SI) group.

As most of the other Ethernet-based technologies, SERCOS III uses the standard Ethernet protocol, enhanced by time-slicing and hardware synchronization. IP protocols, slave-to-slave communication and *hot-plugging* (i.e. making changes to the installed network at runtime) are supported as well. As in *POWERLINK* and others, after the end of the transmission of time-critical data, the remaining time is shared among all bus participants. This is called a *non-real-time channel* (NRT channel). During this time interval, all kind of traffic is allowed, even web services such as HTTP and data from other fieldbus standards, as long as they conform to the Ethernet frame formatting.

A special feature of this technology is its typical topology: a double ring. Although a line topology is possible as well, through the ring, the communication path gains cable redundancy. Any other possible setup which might be used in other Ethernet-based systems – first of all a star topology – is not allowed, because hubs and switches can not be used in *SERCOS III*.

The main advantage of SERCOS III is that the concept is a 'tried and true' mechanism [Sch04]. Great attention has been paid to keep SERCOS compatible over all expansion levels and to continuously improve the concept. Although a SERCOS network is flexible at runtime, the fact that not all topologies are possible is a drawback. This impossibility to use hubs and switches sets certain restrictions when planning a network installation.

#### EtherNet/IP

The name EtherNet/IP stands for Ethernet Industrial Protocol and is basically an enhancement to the IEEE 802.3u standard. It comes along with the Control & Information Protocol (CIP) which is a platform-independent application for real-time I/O. The development is done by the Open DeviceNet Vendor Association (ODVA), together with the ControlNet International (CI) group and the Industrial Ethernet Association (IEA).

The *EtherNet/IP* technology uses common Ethernet hardware, including switches, which makes the network suitable for real-time traffic. In contrast to most other technologies, which replace the TCP/IP protocol on the transport layer by proprietary protocols, in *EtherNet/IP* the CIP is set on top of TCP/IP/UDP. The communication concept is a *producer-customer* model, thus reducing the occurrence of collisions and offering a lot of possibilities regarding scheduling schemes, such as polling, time-slicing, multi-cast and so on. Although a clever choice of scheduling mechanisms (e.g. priority-based or polling) and hardware (e.g. using switched star coupler instead of shared ones) can minimize the probability of collisions, *EtherNet/IP* can not guarantee a collision free network [ODV01], and therefore must be classified as non-deterministic. In fact the freedom to choose whatever concept one might like for a network installation may open a wide field of possible implementations but can not guarantee a save communication channel.

#### Modbus

Originally, Modbus was invented as fieldbus protocol and later adapted to Ethernet under the name of Modbus TCP. The concept was first handed in by Schneider Automation and became an international standard since. In Modbus TCP, the known Modbus protocol is set on top of the TCP/IP stack and a master-slave or client-server mechanism is used. The protocol is connection-oriented and the network topology can be chosen freely.

Regarding guaranteed QoS, Modbus TCP meets the same restrictions as EtherNet/IP: Building a communication channel on top of the non-deterministic TCP/IP protocol can not ensure real-time behavior. The connection-oriented traffic produces additional protocol overhead and the object and data type model is not as elaborate as in CANopen which is used by many other technologies. All in all, Modbus is not as potent as other technologies and the adaptation to Ethernet, although making it faster, does not improve the concept appropriately. However, the protocol will be looked at again in another context in chapter 3.4.1, namely to establish a connection for serial communication between a communication device and the peripheral hardware.

#### VARAN

This technology uses a time-slotting approach on top of standard Ethernet, very similar to EtherNet/IP. Dating from 2006, VARAN (*Versatile Automation Random Access Network*) is a relatively young development from the *VARAN-Bus-Nutzerorganisation* (VNO), published as open standard. The main idea is to have a bus master (called the *VARAN manager*) which is responsible for the network management and the observance of a timing schedule which contains information for all devices about their assigned time slots. Although the mapping of the bus participants to time slots is done typically before starting the transmission, *VARAN* supports hot plug and dynamic addressing, which

makes the bus flexible at runtime. An optional asynchronous task is also provided, and a task dedicated to network administration and synchronization is sent at the end of every transmission cycle.

The basic hardware for a VARAN implementation is a FPGA. Although this would provide the flexibility for elaborate functionality, only basic functions are supported, mainly read and write on the address space spanned by the network participants. The topology of the network can be chosen arbitrarily, as well as the hardware for devices and peripheral network components, such as switches or hubs, which, in this context, are called *splitter* and play a very important role in VARAN networks.

A drawback to VARAN is the usage of packets of a maximum length of 128 Byte. This decision is argued to allow resending of a message in case of communication errors. Compared to other Ethernet-based technologies, the band width is relatively small due to the inevitable delay time caused by the use of many splitters [Kra08].

#### 2.2.3 Industrial solutions

Most of the industrial solutions use either one of the technologies presented above or proprietary protocols. When one looks into the data sheet of most of the offered communication hardware, one recognizes that most of the devices on the market support at least two or more protocols. Table 2.3 states the most important producers of network devices. Below some examples of their usage in industrial solutions are given.

| Company     | Device  | E ther CAT | PROFINET | POWERLINK | SERCOS | EtherNet/IP |

|-------------|---------|------------|----------|-----------|--------|-------------|

|             | family  |            |          |           |        |             |

| AS          | IC      |            |          |           |        |             |

| B&R         | aPCI    |            | х        | х         |        |             |

| Beckhoff    | ET1000  | х          | x        |           | х      | x           |

| Deutschmann | UNIGATE | х          | х        | x         |        | х           |

| gridconnect | EX-184  |            | х        |           |        | х           |

| Hilscher    | netX    | x          | х        | х         | х      | х           |

| HMS         | anybus  |            | х        |           |        | х           |

| Renesas     | ERTEC   |            | х        |           |        |             |

| FPO         | GA      |            |          |           |        |             |

| Altera      | Cyclone | х          | х        | x         | х      | х           |

| IXXAT       |         | х          | х        | х         | х      | х           |

| Xilinx      | Spartan | х          | x        | х         | х      | x           |

Table 2.3: Network device vendors and products

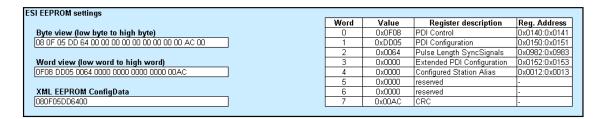

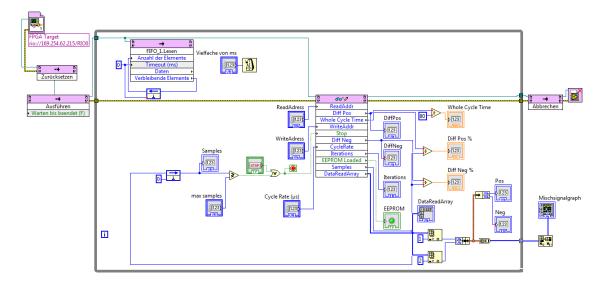

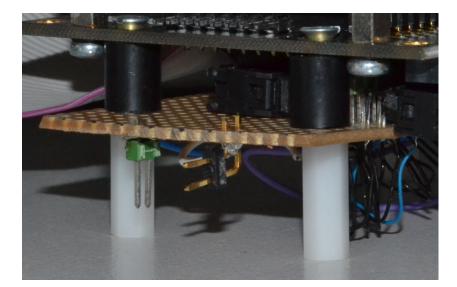

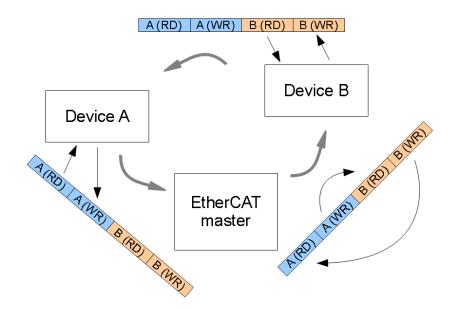

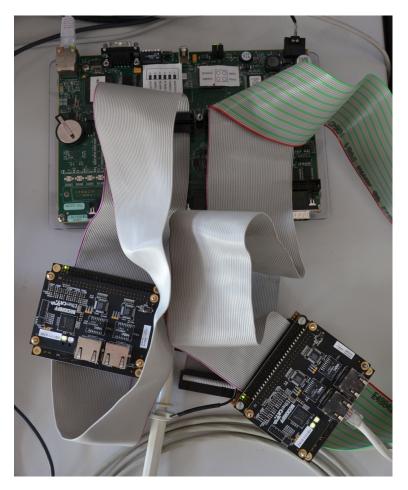

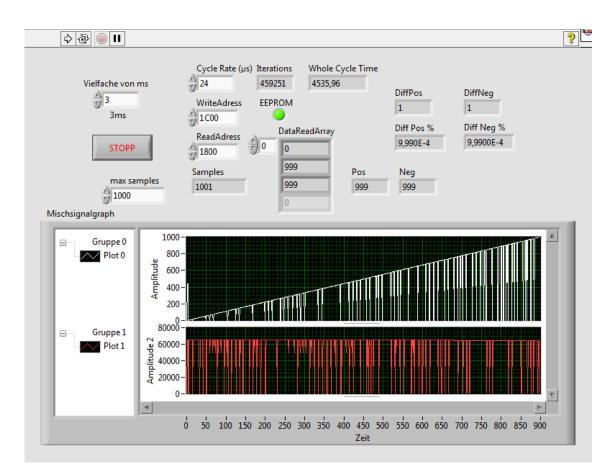

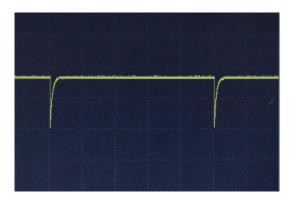

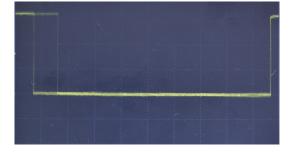

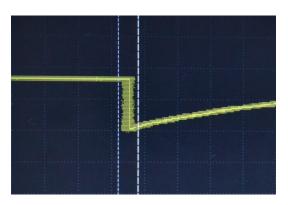

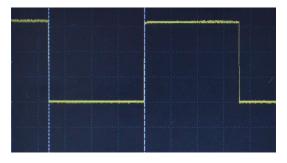

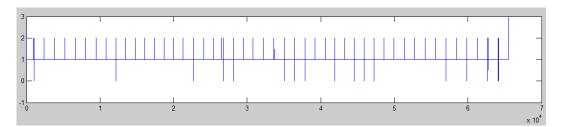

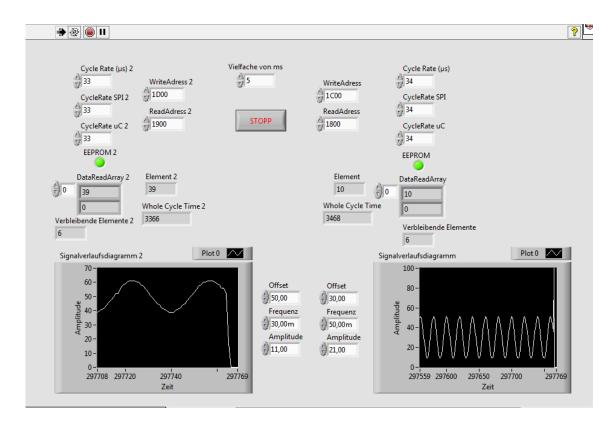

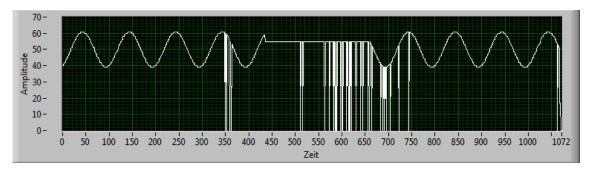

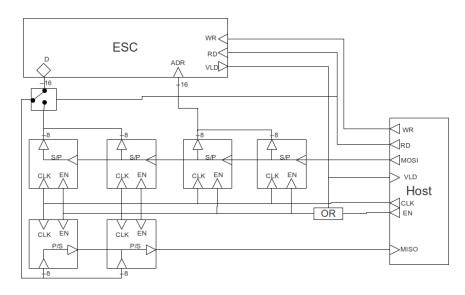

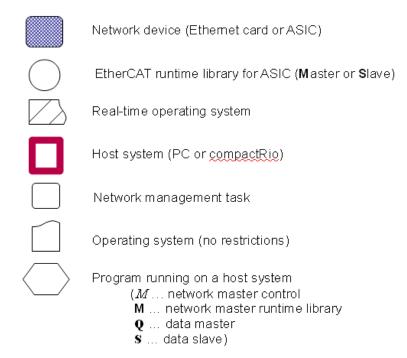

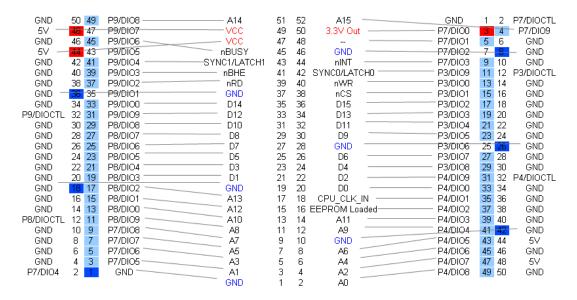

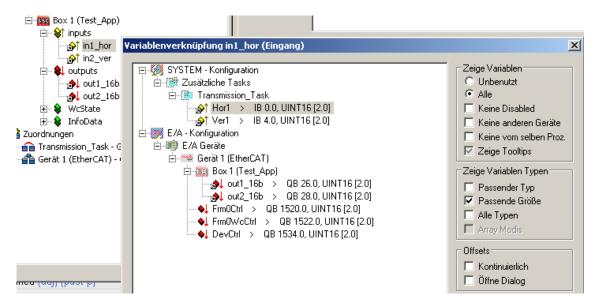

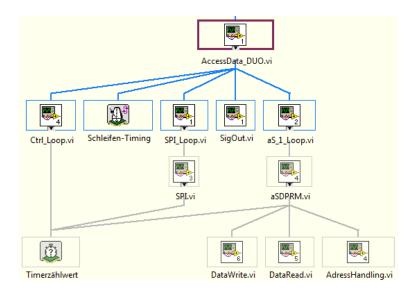

#### B&R