Master's Thesis

## Design and Implementation of a Reader/Smartcard Fault Emulation Framework

Daniel Kroisleitner

Institut für Technische Informatik Technische Universität Graz

Assessor: Steger Christian Ass. Prof. Dipl. -Ing. Dr. techn. Advisor: Steger Christian Ass. Prof. Dipl. -Ing. Dr. techn. Druml Norbert Dipl. -Ing. BSc

Graz, im Mai2013

## Kurzfassung

RFID und dessen Nachfolger Technologien erobern mehr und mehr das alltägliche Leben. Ein wichtiger Schlüsselfaktor für den Erfolg neuer Technologien ist das Vertrauen der Anwender. Der Benutzer erwartet sich eine hohe Verfügbarkeit, Sicherheit und die Wahrung der Privatsphäre. Diese Anforderungen müssen schon während der frühen Phasen des Designs eines Systems berücksichtigt werden. Ein wichtiges Werkzeug dafür sind Simulationen. Ein Nachteil von Simulationen ist der hohe Zeitaufwand. Speziell bei komplexen Projekten sind umfassende Simulationen nicht mehr möglich. Um diesen Nachteil zu umgehen wird immer häufiger auf Emulation zurückgegriffen. Diese Arbeit beschäftigt sich mit der Entwicklung eines Frameworks zur Analyse und Verifikation von Software für RFID/NFC Systemen. Das Framework stellt dafür Modelle für Reader, Karte und der kontaktlosen Schnittstelle zwischen diesen beiden Komponenten zur Verfügung. Zusätzlich zur funktionalen Analyse stellt diese Emulationsumgebung einen Mechanismus zur Injektion von Fehlern zur Verfügung. Ebenfalls inkludiert ist ein Modul zur Leistungsabschätzung. Das Framework wird mit Hilfe eines FPGA Entwicklungsboard realisiert (XILINX ML605 - VIRTEX6).

#### Keywords:

NFC, RFID, Emulation, Wireless Communication, Kryptographie, Power Profiling, Power Aware Computing, Prototyping Platform

## Abstract

RFID based technology conquers more and more every days life. An important fact for the success of a technology is that people have confidence in that technology. The user expects high reliability, security against fraud and privacy maintenance. Therefore, reliability and security aspects must be considered during the design of such applications. Various tools have been developed to enable system verification at early design steps. Simulations have become an important factor for design evaluation. Though a common drawback of simulations is the high time effort. Especially for huge projects, simulations are often not feasible. Therefore, emulation based approaches are needed. The goal of this work is the development of an emulation framework focusing fault injection and power emulation. The proposed framework includes models for reader/card and the contactless communication channel for the emulation of RFID based systems. Additional to the functional verification, information about the power consumption of the system can be gained. Another important feature of the proposed framework is the ability to inject faults into the system to emulate fault attacks and/or the occurrence of natural faults (e.g., due to radiation sources in the environment). The whole project is implemented on one FPGA (XILINX ML605 - VIRTEX6).

#### Keywords:

NFC, RFID, Emulation, Wireless Communication, Cryptography, Power Profiling, Power Aware Computing, Prototyping Platform

Deutsche Fassung: Beschluss der Curricula-Kommission für Bachelor-, Master- und Diplomstudien vom 10.11.2008 Genehmigung des Senates am 1.12.2008

## EIDESSTATTLICHE ERKLÄRUNG

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe.

Graz, am .....

(Unterschrift)

Englische Fassung:

## STATUTORY DECLARATION

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

date

(signature)

## Acknowledgements

First I would like to thank Ass. Prof. Dipl. -Ing. Dr. techn. Christian Steger and Dr. Josef Haid for enabling this thesis. I would also like to thank Norbert Druml and Manuel Menghin for the assistance and support during the design an implementation of the work.

Finally, I would like to thank my family for the aid over the course of my academic studies.

Graz, March 2013

Daniel Kroisleitner

# Contents

| 1 | Intro | oductio | n                                            | 11 |

|---|-------|---------|----------------------------------------------|----|

|   | 1.1   | Motiva  | ation                                        | 11 |

|   | 1.2   | Goals   | of this Thesis                               | 12 |

|   | 1.3   | Struct  | ure of this Work                             | 13 |

| 2 | Rela  | ted Wo  | ork and Theory                               | 14 |

|   | 2.1   |         | hannel Attacks                               | 14 |

|   |       | 2.1.1   | Introduction                                 | 14 |

|   |       | 2.1.2   | Power Analysis                               | 14 |

|   |       | 2.1.3   | Electromagnetic Attacks                      | 17 |

|   |       | 2.1.4   | Timing Attacks                               | 19 |

|   |       | 2.1.5   | Countermeasures against Side Channel Attacks | 19 |

|   | 2.2   | Fault 1 | Injection                                    | 20 |

|   |       | 2.2.1   | Introduction                                 | 20 |

|   |       | 2.2.2   | Reasons for Faults                           | 21 |

|   |       | 2.2.3   | Fault Injection Methods                      | 22 |

|   |       | 2.2.4   | Protection Mechanisms against Faults         | 23 |

|   | 2.3   | Fault 1 | Injection Platforms and Simulations          | 24 |

|   |       | 2.3.1   | Introduction                                 | 24 |

|   |       | 2.3.2   | Classification of Fault Effects              | 25 |

|   |       | 2.3.3   | Saboteurs and Mutants                        | 25 |

|   |       | 2.3.4   | Simulation based Fault Injection             | 28 |

|   |       | 2.3.5   | Emulation based Fault Injection              | 28 |

|   |       | 2.3.6   | Optimization of Fault Injection Campaigns    | 29 |

|   | 2.4   | Power   | Emulation                                    | 30 |

|   | 2.5   | Relate  | d Projects                                   | 31 |

| 3 | Desi  | ign     |                                              | 36 |

|   | 3.1   | Genera  | al Considerations                            | 36 |

|   | 3.2   | Use Ca  | ases                                         | 38 |

|   | 3.3   | Requir  | rements                                      | 39 |

|   | 3.4   | Overvi  | iew                                          | 40 |

|   | 3.5   | Compo   | onents and Interfaces                        | 42 |

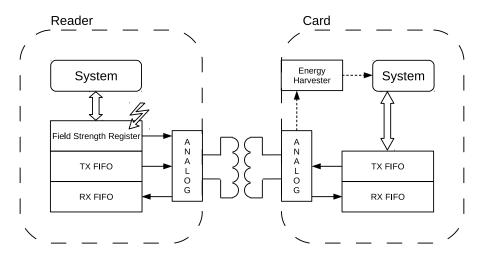

|   |       | 3.5.1   | Emulation Framework                          | 42 |

|   |       | 3.5.2   | Host System                                  | 51 |

|   | 3.6 | System         | Architecture                                                                                                        | 53       |

|---|-----|----------------|---------------------------------------------------------------------------------------------------------------------|----------|

| 4 | -   | lementa        |                                                                                                                     | 56       |

|   | 4.1 |                |                                                                                                                     | 56       |

|   | 4.2 |                | ML605 Prototyping Platform                                                                                          | 56       |

|   | 4.3 |                | ced Microcontroller Bus Architecture AMBA                                                                           | 58       |

|   |     | 4.3.1          | Advanced High-performance Bus                                                                                       | 58       |

|   |     | 4.3.2          | Advanced Peripheral Bus APB                                                                                         | 61       |

|   | 4.4 |                | r IP Library                                                                                                        | 61       |

|   |     | 4.4.1          | LEON3 - High-performance SPARC V8 32-bit Processor                                                                  | 62       |

|   |     | 4.4.2          | DSU3 - LEON3 Hardware Debug Support Unit                                                                            | 62       |

|   |     | 4.4.3          | AHBUART- AMBA AHB Serial Debug Interface                                                                            | 64       |

|   |     | 4.4.4          | AMBA AHB/APB                                                                                                        | 64       |

|   |     | 4.4.5          | <code>AHBRAM</code> - <code>Single-port/Dual-port</code> <code>RAM</code> with <code>AHB</code> interface $\ . \ .$ | 65       |

|   |     | 4.4.6          | AHB to DDR3 Wrapper                                                                                                 | 65       |

|   | 4.5 | Emula          | tion Framework                                                                                                      | 65       |

|   |     | 4.5.1          | Processor                                                                                                           | 66       |

|   |     | 4.5.2          | Bus                                                                                                                 | 66       |

|   |     | 4.5.3          | RAM                                                                                                                 | 67       |

|   |     | 4.5.4          | Channel Model                                                                                                       | 69       |

|   |     | 4.5.5          | Fault Injection Unit                                                                                                | 71       |

|   |     | 4.5.6          | Power Estimation Unit                                                                                               | 71       |

|   |     | 4.5.7          | Debug Interface                                                                                                     | 71       |

|   | 4.6 | Host S         | System                                                                                                              | 74       |

| 5 | Res | ults           |                                                                                                                     | 78       |

|   | 5.1 | Emula          | tor - Characteristics and Performance                                                                               | 78       |

|   | 5.2 | Softwa         | re Interface of the Emulation Framework                                                                             | 79       |

|   | 5.3 | Experi         | iments                                                                                                              | 81       |

|   |     | 5.3.1          | Power Supply - Smartcard                                                                                            | 81       |

|   |     | 5.3.2          | Power Supply - Fault Injection                                                                                      | 83       |

|   |     | 5.3.3          | Multiplier - Fault Injection                                                                                        | 84       |

| 6 | Con | clusion        |                                                                                                                     | 88       |

| 7 | Δnn | endix          |                                                                                                                     | 90       |

| • | 7.1 | Manua          | d                                                                                                                   | 90       |

|   | 1.1 | 7.1.1          | Software Interface                                                                                                  | 90<br>90 |

|   |     | 7.1.1<br>7.1.2 | Emulation Framework                                                                                                 | 90<br>93 |

|   |     | 1.1.4          |                                                                                                                     | 90       |

# List of Figures

| 1.1         | Use cases of the NFC technology                      | 11 |

|-------------|------------------------------------------------------|----|

| 2.1         | Measuring the power consumption of a device          | 15 |

| 2.2         | Differential Power Analysis                          | 18 |

| 2.3         | Fault classification                                 | 26 |

| 2.4         | Saboteur placement                                   | 26 |

| 2.5         | Example fault-space                                  | 30 |

| 2.6         | VERIFY - Overview                                    | 33 |

| 2.7         | Modular Fault Injector MFI - Overview                | 34 |

| 2.8         | Modular Fault Injector MFI - Injection Controller    | 34 |

| 2.9         | Industrial Fault Injection Platform                  | 35 |

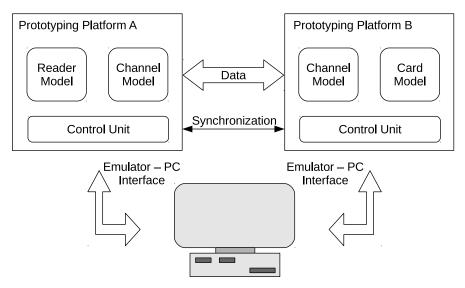

| 3.1         | Architecture Choice - Two Board Approach             | 37 |

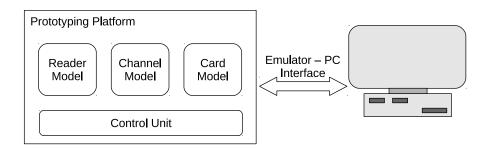

| 3.2         | Architecture Choice - Single Board Approach          | 38 |

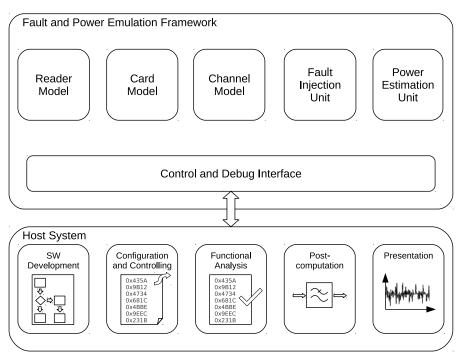

| 3.3         | Emulation Framework - Overview                       | 40 |

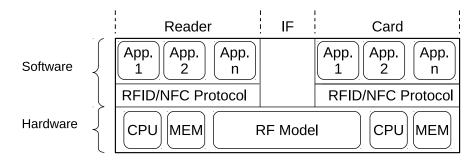

| 3.4         | Layer of the emulation framework                     | 42 |

| 3.5         | Architecture of the Channel Model                    | 45 |

| 3.6         | Smartcard - Equivalent circuit of the supply network | 45 |

| 3.7         | Architecture of the Fault Injection Unit             | 47 |

| 3.8         | Principle architecture of the PPDU                   | 49 |

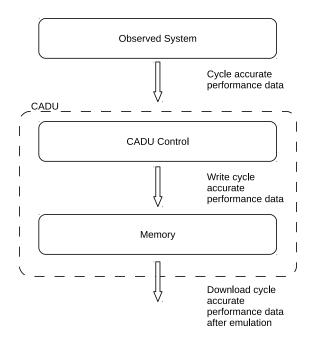

| 3.9         | Principle architecture of the CADU                   | 50 |

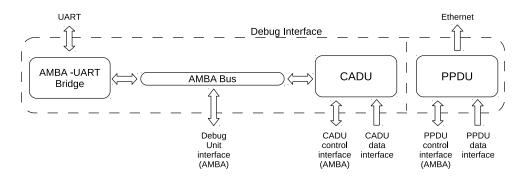

|             | Principle architecture of the Debug Interface        | 50 |

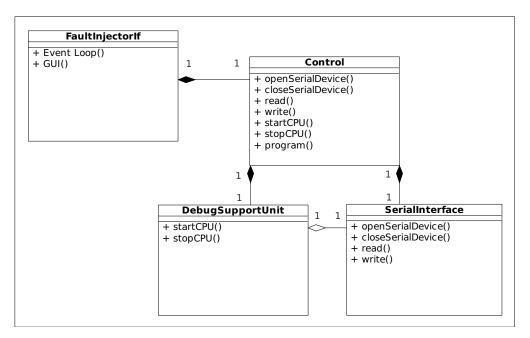

|             | Fault Injection Interface - Class Diagram            | 52 |

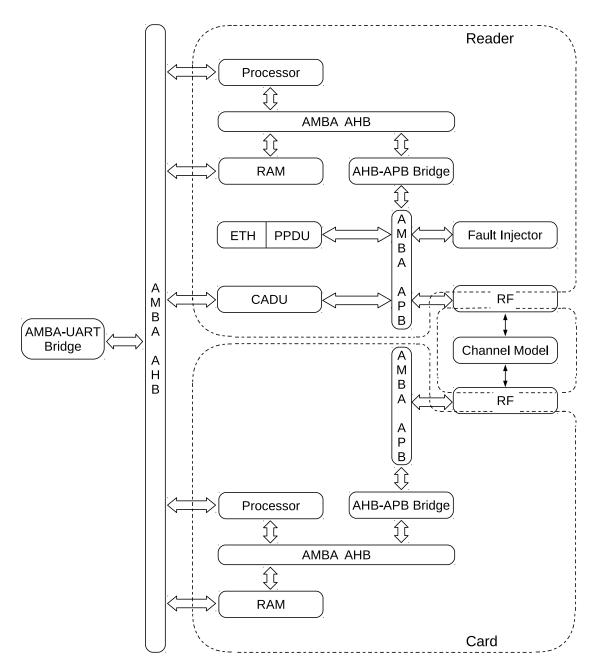

|             | Architecture of the emulator hardware                | 54 |

|             | Optional architecture of the emulator hardware       | 55 |

| 4.1         | ML605 Developing Platform - Block Diagram            | 57 |

| 4.2         | AMBA AHB transfer                                    | 60 |

| 4.3         | AMBA AHB write transfer with wait cycles             | 60 |

| 4.4         | AMBA APB transfer                                    | 62 |

| 4.5         | Block diagram of the LEON3 processor                 | 63 |

| 4.5<br>4.6  | Overview of the Debug Support Unit                   | 63 |

| 4.7         | AHB DDR3 memory read access                          | 66 |

| 4.8         | AHB DDR3 memory write access                         |    |

| 4.9         | Principle architecture of the AHB Multiplexer        |    |

| 4.10        | Internal structure of the AHB Multiplexer            |    |

| <b>1.10</b> | mornar surdound of the fill multipleser              | 00 |

| $\begin{array}{c} 4.12\\ 4.13\end{array}$ | CADU memory organization                                          | 73<br>74<br>75<br>76 |

|-------------------------------------------|-------------------------------------------------------------------|----------------------|

| 5.1                                       | Software Interface - Serial Control                               | 79                   |

| 5.2                                       |                                                                   | 80                   |

| 5.3                                       |                                                                   | 80                   |

| 5.4                                       |                                                                   | 81                   |

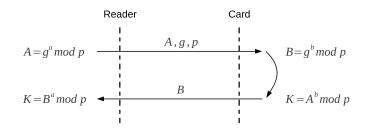

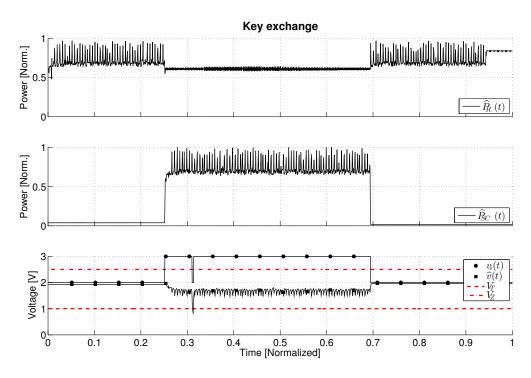

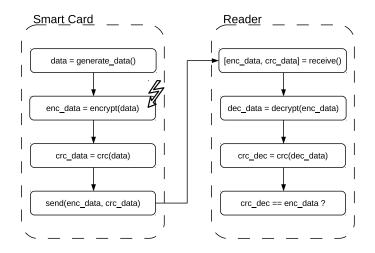

| 5.5                                       | Diffie-Hellman Key Exchange - Protocol                            | 82                   |

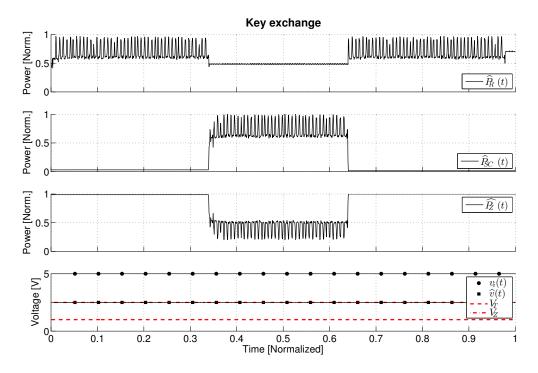

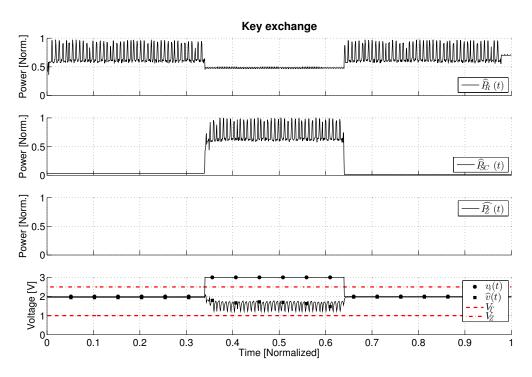

| 5.6                                       | Diffie-Hellman Key Exchange                                       | 82                   |

| 5.7                                       | Diffie-Hellman Key Exchange - Optimized                           | 83                   |

| 5.8                                       | Field Strength Scaling - Architecture                             | 84                   |

| 5.9                                       | Diffie-Hellman Key Exchange - Faulty Behavior                     | 85                   |

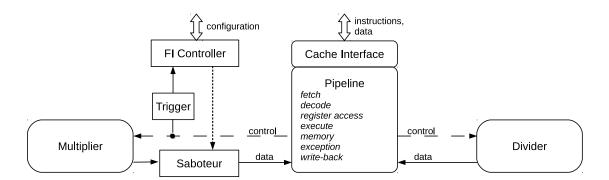

| 5.10                                      | Asymmetric Security Protocol - Faulty Multiplication              | 86                   |

| 5.11                                      | Simplified LEON3 integer unit (with integrated trigger, saboteur) | 87                   |

| 7.1                                       | Connect to prototyping platform                                   | 91                   |

| 7.2                                       | Access to the Debug Interface                                     | 91                   |

| 7.3                                       | Download software and initialize CPUs                             | 92                   |

| 7.4                                       | Control CPUs                                                      | 92                   |

| 7.5                                       | CADU Interface                                                    | 92                   |

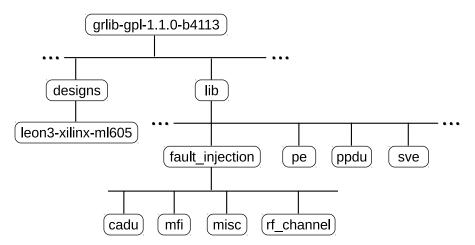

| 7.6                                       | Hierarchy of the framework                                        | 93                   |

# List of Tables

| 2.1 | Saboteur fault modes                         |

|-----|----------------------------------------------|

| 3.1 | Emulation Framework - Dependencies           |

| 4.1 | AHB-UART protocol    64                      |

| 4.2 | Channel Model - FIFO control register        |

| 4.3 | CADU Control Register                        |

| 5.1 | Address space - Emulation Framework          |

| 5.2 | Device utilization - Virtex-6                |

| 5.3 | Asymmetric Security Protocol - Results       |

| 7.1 | Example configuration of a reader/card setup |

## 1 Introduction

## 1.1 Motivation

Contactless technology conquers more and more every days life. RFID based applications are used in passports, for access control (e.g., access to buildings, public transit), payment, etc. Especially contactless payment systems are of great interest. The expectations to this technology are faster and more comfortable ways to pay, the improvement of existing technologies (e.g., RFID tags instead of traditional product codes) and even higher levels of security. Especially the combination of mobile phones and Near Field Communication (NFC) promises various new applications (Figure 1.1).

|                           | STATION<br>AIRPORT                                                                                                     | VEHICLE                                                                                 | OFFICE                                                                                            | STORE<br>RESTAURANT                                                                                                 | THEATER<br>STADIUM                        | ANYWHERE                                                                                                          |

|---------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Area                      |                                                                                                                        |                                                                                         |                                                                                                   |                                                                                                                     |                                           |                                                                                                                   |

| Usage of NFC Mobile Phone | Pass gate<br>Get information<br>from smart poster<br>Get information<br>from information<br>kiosk<br>Pay bus/taxi fare | Personalize seat<br>position<br>Use to represent<br>driver's license<br>Pay parking fee | Enter/exit office<br>Exchange<br>business cards<br>Log in to PC;<br>Print using copier<br>machine | Pay by credit card<br>Get loyalty points<br>Get and use<br>coupon<br>Share information<br>and coupon<br>among users | Pass entrance<br>Get event<br>information | Download and<br>personalize<br>application<br>Check usage<br>history<br>Download ticket<br>Lock phone<br>remotely |

| Service Industries        | Mass and Public<br>Transport<br>Advertising                                                                            | Drivers and<br>Vehicle Services                                                         | Security                                                                                          | Banking<br>Retail<br>Credit Card                                                                                    | Entertainment                             | Any                                                                                                               |

Figure 1.1: Use cases of the NFC technology. [31]

An important fact for the success of a technology is that people have confidence in that technology. Therefore it is important that these applications are resistant against attacks

and that their reliability is high (the possibility of faults is low). The user expects high reliability, security against fraud and privacy maintenance. Therefore, reliability and security aspects must be considered during the design of such applications. Simulations and emulation based system evaluation are important tools to meet these goals.

Simulations are a key factor during the developing of a system. These tools cover a broad spectrum, enabling functional analysis, verification, power simulations, etc. Depending on the type of the simulated system (e.g., software, hardware, mechanics) and the level of abstraction, the simulation effort can be enormous.

Regarding embedded systems where the complexity is steadily increasing over the years, traditional simulations become more and more infeasible. Especially system simulation on a very low level of abstraction (e.g., gate-level simulations) can cover only certain aspects of the system behavior due to its high time effort. Considering that power analysis and fault analysis require a low-level view on the system makes it almost impossible to simulate larger software projects. This restriction is unacceptable if the whole system setup (e.g., a communication protocol) should be analyzed.

Hardware accelerated emulation can bridge this gap between accurate results and low time effort. The use of FPGA prototyping platforms promises a good solution for functional, power and fault analysis of embedded systems.

Regarding RFID systems where the setup consists of several components (reader, card, tolling infrastructure, etc.), separate simulation of the individual units are often insufficient. In order to analyze such a system, the interaction between those components must be considered rather than testing these units independent from each other. Providing a framework supporting the emulation of these units under authentic conditions enables a detailed view on the performance and possible vulnerabilities of the system through the whole developing process.

### 1.2 Goals of this Thesis

The goal of this work is the development of a reader-smartcard emulation framework focusing on fault injection and power emulation. The project is part of META[:SEC:].<sup>1</sup> Targeting RFID enabled systems, the common setup consists of a reader device and a RFID card/tag. Additionally, the RF channel must be considered if the whole system should be analyzed. Using simulations, the evaluation of such a setup can be challenging and the time effort is high. An emulation based approach is therefore advantageous for the verification of the whole setup.

Additional to the functional evaluation of the system, also the power consumption of

<sup>&</sup>lt;sup>1</sup>Mobile Energy-efficient Trustworthy Authentication Systems with Elliptic Curve based SECurity. Funded by the Austrian Federal Ministry for Transport, Innovation, and Technology under the FIT-IT contract 829586.

the system is of interest. Especially for passive RFID devices which are powered by the field of the reader, information about the power consumption is from great importance. Correct functionality of such devices is only possible if the power consumption does not exceed the supplied power. Another topic of interest is the behavior of the system under the presence of faults. Faults can be introduced into a system either due to natural sources or intentional by an attacker hoping that the device reveals its secret information. Especially for applications where system failure would lead to high costs (e.g., payment applications) the analysis of the system under the presence of faults is from great importance. Therefore, power and fault emulation are an essential part for system evaluation.

The goal of this thesis is to provide a RFID/NFC emulation framework for software verification. Functional verification should be possible as well as the analysis of the application under the presence of hardware faults. Additional to the functional verification and the fault analysis the power consumption of the system should be estimated. Combining functional verification, fault and power analysis into one framework enables a detailed view on the system during the design of such applications.

According to the requirements the proposed framework supports the following main features.

- Emulation of a reader-smartcard setup concerning an active reader, a passive RFID card/tag and the RF channel.

- Emulation of the power consumption of the system.

- Fault emulation to verify the consequences of faults introduced into the system either by natural sources or during an attack.

## **1.3 Structure of this Work**

Chapter 2 gives an introduction to related topics. Section 2.1 deals with side channel attacks. Especially the concept of Differential Power Analysis is explained which is a powerful method to observe the internal state of a device and can therefore be used to gain secret data stored in a system. Section 2.2 gives an overview about the reasons of faults and the thematic of fault injection where Section 2.3 deals with the simulation/emulation of faults in systems. Section 2.4 gives a short introduction to the topic of power emulation. The chapter concludes with a selection of related projects. Chapter 3 and Chapter 4 deal with the design and implementation of the emulation framework. The results are presented in Chapter 5. The work concludes with Chapter 6 providing an outlook and ideas for future extensions.

## 2 Related Work and Theory

## 2.1 Side Channel Attacks

#### 2.1.1 Introduction

Side Channel Attacks are methods to gain restricted information about a system during a noninvasive attack. The term side channel refers to the ability to observe characteristics of a system which carries information. With such an information an attacker might be able to gain secret data. Carrier of such information can be the power consumption, electromagnetic emanation or the timing behavior of the system.

The target of such an attack is for example the retrieval of the secret key of a cryptographic system or to get information about the used algorithm of a system.

#### 2.1.2 Power Analysis

The power consumption of a device can leak information about the current operations being performed or even about data being processed on the device. This fact can be used to attack a cryptographic system by measuring the power consumption during cryptographic computation.

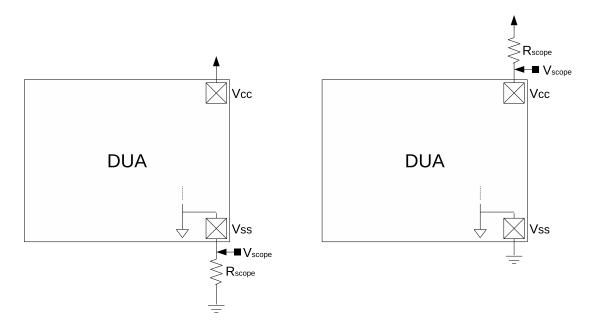

Figure 2.1 shows two possibilities to measure the power consumption of a device [23]. The first possibility is to place a resistor  $R_{scope}$  between the  $V_{ss}$  pin and the ground line. The current moving through  $R_{scope}$  creates a voltage. If the power consumption is high, the higher current creates a higher voltage (higher value of  $V_{scope}$ ). If the power consumption is low, the lower current creates a lower voltage (lower value of  $V_{scope}$ ). Therefore, measuring  $V_{scope}$  with an oscilloscope gives information about the power consumption of the device under attack (DUA).

The second possibility is to place a resistor  $R_{scope}$  between the  $V_{cc}$  pin and the power supply. If the power consumption is high, the higher current creates a higher voltage at  $R_{scope}$  which leads to a lower voltage  $V_{scope}$ . If the power consumption is low, the lower current creates a lower voltage at  $R_{scope}$  which leads to a higher voltage  $V_{scope}$ . Therefore, a smaller value of  $V_{scope}$  indicates higher power consumption and vice versa.

Figure 2.1: Measuring the power consumption of a device using a resistor and an oscilloscope.[23]

#### Simple Power Analysis

Simple Power Analysis (SPA) is a technique where measurements of the power consumption of a DUA are directly interpreted [25]. Because different operations consume different amount of energy, SPA can be used to identify these operations. Using SPA, it is also possible to get information about data being processed (e.g., the secret key of a cryptographic algorithm).

As shown in [23], the power trace pattern of a 3DES operation can be identified. If an attacker does not know which cryptographic operation is used, such additional information can be helpful. Another example for SPA stated in [23], is the attack on the modular exponentiation of the RSA algorithm. The modular exponentiation is performed using the binary left-to-right algorithm. Because of the different power consumption of the squaring operation and the multiplication and because the multiplication is only performed when a bit of exponent is '1', the secret exponent can be found by analyzing the power trace. The value of the exponent can be clearly identified in the power trace. Because SPA needs strong data-dependent features in the power trace, SPA is not practi-

cable for situations where cryptographic operations are hidden in noise [23]. To overcome this problem Differential Power Analysis (DPA) can be used.

#### **Differential Power Analysis**

DPA is a powerful method to gain secret information from a set of power traces using statistical methods. The idea of this method is that the power consumption is influenced by the processed data and that information about this data can be gained using correlation between different measurements.

Kocher et al. [23] describe an experiment where the basic principle of statistical methods in power analysis is shown. The example uses several power traces captured during an AES-128 operation on a smartcard. The traces were generated using randomly chosen plain text input for every trace. Only power values from a specific time instance are used which means that one power value per trace is required. For the experiment, the moment when the device computes the output of the first S-box was chosen. Depending on the LSB bit of the result, two subsets of power traces were built. For both subsets, the distribution of the power values at the specific time event was computed. The result shows that the distribution of both subsets is significantly different [23]. This shows that the power consumption correlates to the LSB of the S-box computation. The results in [23] also show that these distributions overlap, which means that single measurements would not be sufficient to identify the value of the S-box bit. The experiment makes clear that statistical methods can be used to gain additional information from a set of power measurements.

Using the knowledge from the experiment, DPA can be used to attack an AES-128 cryptographic operation. Goal of the attack is to find the secret key.

The example attack from [23] attacks the AddRoundKey and the SubBytes routines from the first round.<sup>1</sup> Equation (2.1) shows the operation to attack where  $I_i$  is the 16byte intermediate value of the cipher after the SubBytes routine and  $I_{i,n}$  the nth byte of  $I_i$ . K denotes the first round key and  $K_n$  the nth byte of K.  $X_i$  is the plaintext and  $X_{i,n}$  denotes the nth byte of  $X_i$ . The index *i* indicates a specific trace in a set of power traces. S is the S-box of the AES.

$$I_{i,n} = S[X_{i,n} \oplus K_n] \qquad n \in \{0, \dots, 15\}$$

(2.1)

$K_n$  is the nth byte of the secret key, therefore the intermediate value  $I_{i,n}$  is unknown. Because  $K_n$  is a 8-bit value, there are 256 possible candidates for the nth byte of the secret key. In order to find  $K_n$ , a test is needed which says if a guess of  $K_n$  is correct or not. As stated in [23], this task can be solved using DPA.

In order to perform DPA on the given problem, a selection function has to be found [23]. This selection function is used to divide the measured traces into subsets. For the example attack on the AES-128 cipher the LSB of  $I_{i,n}$  was used.

<sup>&</sup>lt;sup>1</sup>For additional information about the Advanced Encryption Standard (AES) see [30].

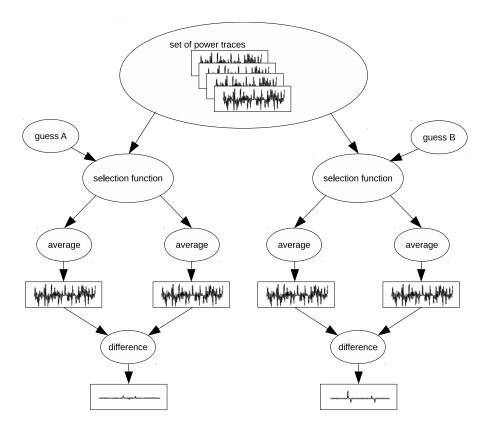

An attacker now has to measure the power consumption of the cryptographic system during the encryption. This task has to be repeated several times using randomly chosen plain text for every measurement gaining power traces. Now the attacker has to 'guess' one possible value for  $K_n$ . Using  $K_n$ , the attacker can compute  $I_{i,n}$  for every power trace *i* using the same plain text as used for the measurement of trace *i*. Depending on the LSB of  $I_{i,n}$  (the selection function) the set of power traces can be divided into two subsets. Now, the attacker computes the average value for all time instances in the subset, producing two average traces for each subset. Using these two traces the difference between the subsets can be computed.

This task is repeated for every possible guess of  $K_n$ . Because  $K_n$  is a 8-bit value there are 256 possibilities. For every guess the attacker computes the difference of the averages. In this example attack 256 difference traces must be computed. Using these difference traces, the right guess can be identified by searching for the traces with the highest peaks [23]. This is motivated by the experiment described above. Instead of evaluating only one specific point in the trace as done in the experiment, DPA considers the whole trace. This is done by computing the average trace for each subset which are then compared. Spikes in the difference trace indicate that the trace is correlated to the selection function because the intermediate value is manipulated by the device [23]. Therefore, higher spikes indicate stronger correlation to the selection function and are therefore an indicator for a right guess.

Because the secret key is a 16-byte key this attack has to be repeated for every  $K_n$  to get the whole key. Figure 2.2 shows the tasks for the example attack for two guesses.

This example attack shows the basic principle of DPA. However, in [23] also a more general view on DPA can be found. As stated in [23], the concept of SPA and DPA can also be applied on electromagnetic measurements performing Simple Electromagnetic Attacks (SEMA) or Differential Electromagnetic Attacks (DEMA).

A more complex attack using power analysis is the so called High-Order DPA (HODPA) which can be used to circumvent countermeasures against DPA [21], [28], [33].

#### 2.1.3 Electromagnetic Attacks

Similar to power analysis, information is also leaked due to electromagnetic emanation. Measuring the electromagnetic field of a device instead of the power consumption can be advantageous if a measurement setup to measure the power consumption is not possible. For example passive RFID tags where the analog front-end is integrated on the same IC as the RFID device. In such a case the measurement of the electromagnetic field can be a good alternative. As stated in [1], electromagnetic attacks can even perform better than attacks using power analysis. Additionally, these attacks can be used to circumvent countermeasures against power analysis.

The simplest way to perform an attack is to measure the electromagnetic emanation with one antenna in the vicinity of the device. These measurements can then be interpreted

Figure 2.2: DPA process for two guesses. The selection function divides the set of traces into two subsets. For each subset an average trace is computed. The difference trace is used to find the correct key. [23]

applying the mechanisms used for power analysis (see Section 2.1.2). One advantage of electromagnetic attacks in contrast to power analysis is the capability of exploiting local information [16]. Using small probes, an attacker is able to pinpoint specific areas on a chip (CPU, buses, etc.).

Gandolfi et al. [16] propose several attacks on cryptographic systems using simple handmade solenoids made of a coiled copper wire. The measurements were then amplified and analyzed using DEMA. The experiments show that electromagnetic attacks can yield better results than attacks using power analysis. In the experiments, the DEMA reaches a higher SNR than DPA.

Similar experiments were proposed by Hutter et al. [20], where attacks were performed on passive RFID tags. The experiments were performed on self-made prototypes instead of commercial passive RFID devices. The target of the attacks was the AES algorithm. The experiments performed by Hutter et al. also targeted the challenge of EM attacks in the presence of an external field provided by a RFID reader.

#### 2.1.4 Timing Attacks

Another potential side channel leaking sensitive information is the timing behavior of a device. Timing attacks make use of the data/key dependent runtime of a cryptographic algorithm. Measuring this small time variations during the computation can then be used to gain sensitive data. Such variations are caused for example by processor instructions which run in non-fixed time, conditional statements, etc.

In [24], Kocher presented such timing attacks on implementations of Diffie-Hellman, RSA and DSS.

#### 2.1.5 Countermeasures against Side Channel Attacks

As shown in the sections above side channel attacks are powerful methods to attack a cryptographic system. Therefore, countermeasures have to be found to mitigate the threat of such attacks.

As mentioned in [23] mechanisms such as balancing, blinding and masking can be used to reduce the threat of power analysis. Another idea is to add noise to the measurements using circuits performing computations uncorrelated to the cryptographic operations. As also mentioned in [23] an attacker may be able to circumvent these countermeasures using HODPA and/or performing a higher amount of measurements. As highlighted in [1] electromagnetic attacks can also be used to circumvent countermeasures against power analysis. Therefore, also the electromagnetic emanation of a system must be considered if the side channel leakage of a system should be reduced. This can for example be done by reducing the signal strength and/or shielding [1].

Facing timing attacks, blinding mechanism or random delays added to the computations can be used [24].

In [41], a balancing approach can be found where the problem is addressed on circuit level to suppress the leakage of the power consumption. Even if that approach shows that the effects of a side channel attack can be reduced, the authors also mentioned that perfect security does not exist.

#### **Balancing Mechanism**

These mechanisms try to reduce the variations of the power consumption during computations and thus information leakage. This can be done on circuit level using sophisticated designs to make the power consumption of the device less dependent on data and the operations being performed [23].

Examples for such designs can be found in [41], [35] and [39].

#### **Blinding Mechanism**

Because many cryptographic systems use operations over a finite field, one can use mathematical relationships to blind the computations. Equation (2.2) shows such a relationship suitable for blinding (where  $\phi(.)$  denotes the Euler's phi function).

$$A^{d+k\cdot\phi(P)} \mod P = A^d \mod P \tag{2.2}$$

Changing k randomly between computations interferes statistical tests like DPA [23].

#### **Masking Mechanism**

Similar to blinding, masking can be used for symmetric algorithms where secret constants and intermediates are split into randomized parts [23]. Computations are then performed on these independent parts. For the final output these partial results are reassembled.

## 2.2 Fault Injection

#### 2.2.1 Introduction

The term Fault Injection is generally used for intentional faults introduced into a system. There are several reasons why faults are injected into systems.

One reason is to test a system under the influence of faults. In order to test a system under such conditions faults are injected into a running system. The system is then observed. If such a fault does not lead to a failure in the system, the test has successfully passed. If not, the system is vulnerable against such faults. Although this looks very trivial, there is a lot of research targeting such problems. Modern ICs comprise a huge amount of transistors. The challenge is now to find 'good' targets for the test to get valuable results. Another challenge is to choose the right time for injecting a fault. For example changing one bit in the system will not produce any failure if the bit will never be read or if the bit is overwritten before the bit is read again. To find 'good' targets is therefore a challenging task.

Faults injected into a running system can also be used for attacks which are often called fault attacks. If the location of the fault is well chosen an attacker may retrieve secret information from the system. Potential targets of such attacks are for example the program counter or (on-chip) buses.

#### 2.2.2 Reasons for Faults

One important factor for faults in electric devices is radiation. The particles travel through the device and interact with the material of the IC. This interaction can then lead to so called soft errors if the circuit is not permanently damaged (e.g., one bit of the memory is flipped) or can even damage the device. Soft errors are also referred to as single event upsets (SEU). Depending on the amount of affected bits also the terms singlebit upsets (SBU) and multibit upsets (MBU) are used.

As stated in [8], three mechanisms are dominant in the terrestrial environment. The first mechanism introduces faults due to alpha particles (ionized helium). Such alpha particles are emitted by impurities in the packaging material. An early work describing the impact of packaging material on dynamic RAM can be found in [27].

A second source of faults are high-energy cosmic rays. These rays interact with the atmosphere of the earth and produce secondary particles. These secondary particles then travel deeper into the atmosphere and produce tertiary particles and so on. At terrestrial level the particles then interact with the device material which causes faults. The third source of faults are low-energy cosmic rays where faults are introduced due to the reaction of low-energy neutrons with boron inside the device.

Although these effects can be diminished (e.g., due to purified packaging material or shielding) the source of faults can never be eliminated.<sup>2</sup> Therefore, additional countermeasures have to be taken to deal with this kind of faults.

Where these three mechanisms describe the situation on terrestrial level one should also mention that the occurrence of faults also depends on altitude, latitude and solar activity [32].

Another important factor concerning faults introduced due to radiation is the used technology. As shown in [8] the soft error rate (SER) depends on the technology scaling and even differs for distinct components such as SRAM and DRAM. While the bit SER of DRAMs is decreasing due to technology evolution the bit SER of SRAM has saturated. If the increasing memory density of modern systems is considered these trends lead to constant system SER for DRAMs and an increasing system SER for SRAMs. Similar to memory also logic elements are sensitive to radiation. Faults happen due to single-event transients (SET) introduced into the logic element by radiation. These glitches then lead to an error if this wrong signal actually propagates to the input of a flip-flop/latch during a latching clock signal [8]. The probability that such glitches are latched depends on the propagation delay and the clock frequency. Therefore, the probability of such errors increases with advanced technology because of the reduced propagation delay and higher frequencies.

In order to face these problems, mechanisms are necessary to mitigate the influence of such faults (see Section 2.2.4).

Other than natural faults introduced due radiation, faults can be injected into a system

$<sup>^{2}</sup>$ For a detailed view on the fault mechanisms, the physical processes and possible countermeasures see [8].

with the intention to retrieve secret information. In contrast to side channel attacks (see Section 2.1) the attacker takes an action to influence the target of the attack. This can either be invasive, by detaching the package and manipulation of the circuit or noninvasive using radiation or temperature. Another possibility is to manipulate the power supply to introduce faults or to perturb the clock signal. Goal of such attacks is to change the behavior of a system (e.g., to manipulate the execution of a program or to disable specific components).

A major difference between natural faults and intentional faults during a fault attack is their behavior. While radiation caused faults are mostly temporary (e.g., a write on an affected bit in memory overwrites the faulty bit) invasive intrusion can also lead to a permanent fault (e.g., due to manipulation of the circuit). Another difference is that fault attacks can inject more than one fault simultaneously where the probability for multibit faults caused by natural sources is low.

Fault injection can therefore be seen as a tool to test the protection mechanisms added to mitigate the influence of natural faults and as a method to attack cryptographic systems (fault attacks). Additionally, fault injection can be used to analyze the threat of a potential attack (e.g., to oppose the risk of an attack to the costs of the countermeasure).

#### 2.2.3 Fault Injection Methods

Generally, methods for fault injection can be divided into two classes. The first class uses physical effects to introduce faults into a running system. The other class makes use of simulations to analyze the impact of faults. While the first class can be used to attack a system in order to retrieve secrete information, the second class is used to test the vulnerability of the system in presence of faults. This information can then be used to develop robust devices.

This section describes some possible methods to inject faults into a running system while the concept of simulating faults is described in Section 2.3.

As described in [5] the most common methods for fault injection are the following:

• Supply voltage variations

Varying the supply voltage during runtime of the system may cause a processor to skip an instruction. This can for example be used to omit branches. Especially for contactless smartcards where the card is supplied by an external field, such attacks are from interest.

• External clock variations

Similar to supply voltage variations, variations of the clock can cause the processor to skip instructions or can lead to data misreads.

#### • Temperature

The goal of this method is to vary the temperature until a threshold is reached where the circuit or parts of the circuit does not work correctly anymore. This can for example be used to inject random faults. As also stated in [5], this method can be used to disable read or write operations to memory which can be exploited due to the fact that the temperature threshold for read and write operations are not the same. Temperature attacks can therefore be used to omit counter updates such as used for limited resources (e.g., a cryptographic key which can be used several times until it becomes invalid).

• White light

Exploiting the photoelectric effect of electric circuits, light can be used to introduce faults into a detached IC.

• Laser beams

Similar to white light, laser beams can be used for fault injection. The advantage of laser light compared to white light is that a certain part of the circuit can be attacked more precisely.

• X-ray and ion beams Other than fault injection with light, these methods can be used without depackaging the IC.

The described methods vary in effectiveness and their costs. Therefore, in order to design robust systems against fault attacks the designer must conclude on which equipment a potential attacker possesses.

### 2.2.4 Protection Mechanisms against Faults

Depending on the purpose of the protection mechanism different methods exist. While countermeasures against natural faults are often designed for SBUs, this is not sufficient as protection against fault attacks where multibit faults can occur. Therefore, analyzing the threats of a system is of great importance when the system should be robust against a certain kind of faults.

One possible mechanism against faults to protect memory is to add one bit for each data word which stores the parity. The parity bit allows to detect one error in the data word but fails if two errors occur. In general, if one parity bit is used only an even number of errors can be detected. Another possibility is to use error detection and correction EDAC or error correction codes ECC to protect the memory. Other than the parity check, this method also allows to correct a wrong bit. This feature is implemented by adding some bits to the data word to increase the redundancy of the information stored in the extended data word. Depending on the additional information provided due to ECC one or more erroneous bits can be corrected.

Where these mechanisms are suitable to protect the integrity of the memory, additional methods must be found to protect the combinational/sequential logic. One possibility is to duplicate the circuit and compare their results. If the results differ from each other an error occurred and an alarm can be triggered. If more than two instances of the same circuit are used the result can even be corrected. Also possible is the use of complementary redundancy where the circuits produce complemented outputs. If the result is the same on both outputs, an error occurred. The advantage of such circuits is that it can be used for multibit faults due to the fact that fault injection with complementary effect is complicated [5].

Besides the methods described above, also redundancy in time can be used as protection mechanism. Using this protection scheme the computation is repeated at the same circuit and the results are then compared. Similar to the spatial implementation, errors can be detected or even corrected if the computation is performed more than twice.

A more sophisticated technique is proposed by Moore et al. [29], where self-timed circuits and dual-rail logic are used to improve the resistance against faults and even against side channel attacks.

Another possible countermeasure against attacks is the use of sensors [5]. These sensors can for example be used to detect voltage or frequency variation. Also possible are active shields covering the entire chip. This shield consists of a metal mesh where data is passing. If an attacker tries to modify the circuit also the data in the mesh is corrupted and an error signal is generated.

Similar to the mechanisms implemented in hardware countermeasures can also be implemented in software. Such mechanisms are for example *checksums*, *variable redundancy* or *execution redundancy* [5].

All these mechanisms have in common that size and/or execution penalties must be accepted.

#### 2.3 Fault Injection Platforms and Simulations

#### 2.3.1 Introduction

This section deals with the evaluation of systems under the influence of faults.

One possible method to test systems and error detection/correction mechanisms is to use the fault injection methods described in Section 2.2.3 (e.g., due to the use of radiation or invasive methods). One important drawback of this method is that at least a prototype is needed. Therefore, the information about vulnerabilities of the design is not available at the early design steps. Another disadvantage is the limited capability to monitor the internal states of the system which is important for the understanding of an erroneous system behavior.

To circumvent these drawbacks one can use simulations or system emulator with integrated fault injectors. Using this method, faults can be injected at arbitrary locations and the effects can be monitored. Simulations can be done using hardware description languages (HDL) such as VHDL, Verilog, SystemC, etc. Another possibility is to implement the system on an FPGA together with dedicated circuits necessary to introduce faults. The advantage of an FPGA based system emulator opposed to simulations is the improved simulation speed and therefore a higher fault injection rate.

#### 2.3.2 Classification of Fault Effects

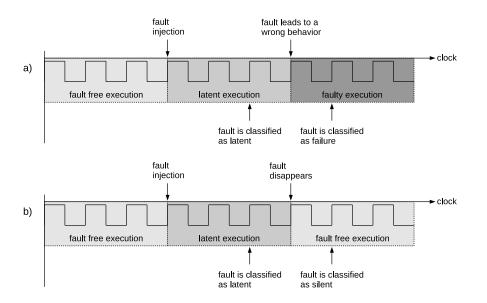

In the context of simulated/emulated fault injection, faults can be divided into three classes [40].

• Failure

If the injected fault leads to a wrong behavior of the circuit (e.g., wrong or delayed output) the fault is classified as *failure*.

• Silent fault

If the injected fault does not lead to a wrong behavior and disappears completely until the testbench has finished, the fault is considered as *silent*. This can be the case if the fault affects a flip-flop/memory cell which is overwritten during execution before the value is used.

• Latent fault

If the injected fault does not lead to a wrong behavior during the execution of the testbench but remains as a deviation of the system state compared to the state observed during a fault free execution, the fault is classified as *latent*. This class of faults depends on the testbench because if the simulation/emulation would continue, the fault may causes a failure or a latent fault.

Figure 2.3 shows the two cases where a fault is either classified as *latent fault* or as *failure/silent fault* depending on the duration of the testbench/experiment.

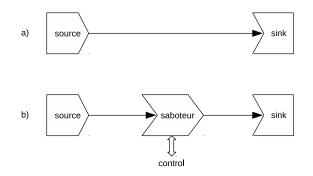

#### 2.3.3 Saboteurs and Mutants

Using a HDL, a common method for fault injection is the usage of saboteurs or mutants. Saboteurs are simple units which are used to modify signals. Therefore, these units are placed between the signal's source and its sink (see Figure 2.4). These units have a signal input and a signal output. Additionally, a saboteur has certain control inputs such as *activate*, *mode* and the *clock* signal. The *activate* signal is used to trigger

Figure 2.3: Fault classification. a) *latent fault* leads to a *failure* b)*latent fault* leads to a *silent fault*.

the fault. If the saboteur is disabled it behaves like a wire. If the saboteur supports different kinds of faults also a *mode* signal is needed to choose which fault should be triggered. Common fault modes implemented in saboteurs are *stuck-at-zero*, *stuck-at-one*, *indetermination faults*, *negation faults*, *delays*, *bridging faults* or *bit-flips*. Table 2.1 gives an overview about the faults, using the definition from [18].

Figure 2.4: Saboteur placement. a) original signal b) instrumented signal using a saboteur.

Other than saboteurs which are used to manipulate signals a mutant is a modified version of a submodule used by the system. The mutant behaves like the original module until the mutant is activated. If the mutant is activated, the module behaves like a faulty version of the original unit.

| Fault           | Description                |                             |

|-----------------|----------------------------|-----------------------------|

| Stuck-at-Zero   | The output stays per-      |                             |

|                 | manently at zero. This     |                             |

|                 | fault reflects a direct    | Normal Behavior             |

|                 | modification of the cir-   |                             |

|                 | cuit where the signal is   | Saboteur Output             |

|                 | wired to a logic zero.     | Fault Event                 |

| Stuck-at-One    | The output stays per-      |                             |

|                 | manently at one. This      |                             |

|                 | fault reflects a direct    | Normal Behavior             |

|                 | modification of the cir-   |                             |

|                 | cuit where the signal is   | Saboteur Output             |

|                 | wired to a logic one.      | Fault Event                 |

| Indetermination | The signal holds an un-    |                             |

|                 | defined state (perma-      |                             |

|                 | nent fault). This fault    | Normal Behavior             |

|                 | reflects a direct modifi-  | Saboteur Output             |

|                 | cation of the circuit.     | Fault Event                 |

| Negation        | The signal is inverted     |                             |

|                 | (permanent fault).         |                             |

|                 |                            | Normal Behavior             |

|                 |                            | Saboteur Output             |

|                 |                            | Fault Event                 |

| Delay           | Input to output delay      |                             |

|                 | (transient fault). This    |                             |

|                 | fault reflects supply      | Normal Behavior             |

|                 | voltage variations.        | Saboteur Output             |

|                 |                            | Fault Event                 |

| Bridging Fault  | The input is not propa-    | 1                           |

|                 | gated anymore (perma-      | Normal Behavior             |

|                 | nent fault).               |                             |

|                 |                            | Saboteur Output             |

|                 |                            | Fault Event                 |

| Bit-Flip        | The input is inverted      |                             |

|                 | for one cycle (tran-       |                             |

|                 | sient fault). This fault   | Normal Behavior             |

|                 | reflects latched SETs      |                             |

|                 | (e.g., due to radiation or | Saboteur Output Fault Event |

|                 | laser beam).               |                             |

Table 2.1: Common fault modes used for saboteurs (the table uses the definition from [18]).

A common requirement of these units is that additional mechanisms are necessary to control the activation and deactivation of the modules.

Both, saboteurs and mutants, are used in simulations and emulation based fault injection.

#### 2.3.4 Simulation based Fault Injection

Simulations execute HDL descriptions of a system. One possible method to use simulations for fault injection is to run the simulation until a specific point, change the value of one or more signals and resume the simulation. After the simulation completed the results can be obtained. This method works without the modification of the system model but depends on the available commands provided by the simulator.

Another possible method for simulation based fault injection is the usage of saboteurs and/or mutants. The system model is extended with these additional modules to allow automated fault injection. Additionally, the fault injection campaign is independent of the used simulator. A common method for such campaigns is to perform a *golden run* where the system is simulated without the presence of faults. These results are then stored and can be compared to the results of faulty runs to monitor the effects of the faults. A common disadvantage of simulation based fault injection is the high time effort especially for huge projects. Therefore, emulation based fault injection has become an important tool to improve the validation process.

#### 2.3.5 Emulation based Fault Injection

The principle of emulation based fault injection is the usage of hardware (usually FP-GAs) to speedup the injection campaigns. There are different ways to exploit the advantages of FPGA based fault emulation. One method is to use *global reconfiguration* or *partial reconfiguration* methods [3]. This method injects faults due to reconfiguration of the FPGA. This can either be done by reconfiguring the whole device (*global reconfiguration*) or by changing only parts of the circuit (*partial reconfiguration*). Therefore, one major advantage of this method is that no modification of the original system model is necessary. This means that no additional circuits must be added to the system which is advantageous if the hardware resources of the used FPGA are strongly limited. For example to inject a fault into a combinational subcircuit, which is implemented as LUT on the FPGA, only the description of the corresponding LUT must be changed.

Using global reconfiguration, the whole FPGA is reconfigured. Therefore, a mechanism must be provided to restore the system state after the fault is injected to preserve intermediate results (also see [19]). To circumvent this inter-configuration communication,

*partial reconfiguration* can be used where only a part of the device is reconfigured and therefore does not affect the whole system. The drawback of this method is that the device must possess the capability for *partial reconfiguration*. Therefore, this approach is limited to a certain subset of FPGAs.

Another approach is to modify the system model in order to allow the manipulation of certain units. Similar to simulation based fault injection, the concept of saboteurs and mutants can be applied. As done by the simulation approach, a *golden run* is performed, to get a fault free reference for the analysis. In order to perform the injection campaign a mechanism must be implemented to trigger the fault units and to monitor the results. An important difference between simulations and emulation based fault injection is that the system model and the additional components used for the injection campaign must be available in a synthesizable description.

#### 2.3.6 Optimization of Fault Injection Campaigns

Because the evaluation of a whole system under the influence of faults requires a lot of time, mechanisms are needed to speedup this process and to improve the effectiveness of the fault injection campaigns. As mentioned in Section 2.3.5, hardware accelerated methods can be used to gain better performance compared to simulation based methods. However, speeding up the injection process is often not enough considering the huge amount of possible injection points. Therefore, also the effectiveness of the process must be improved rather than only increasing the speed of the campaigns.

A common method of fault injection tools is to choose the location and time of the faults randomly from the fault-space (two dimensional space spanned by time and location). The problem of this approach is that only a subset of these injected faults has an impact on the system behavior. Therefore, the efficiency of the campaign is often low. For example if a fault is injected into a memory location that is never read, the fault can not affect the system and is therefore useless for evaluation. Similar, if a fault is injected into a location just before a write on that memory, the fault has no effect. Figure 2.5 shows an example fault-space for memory. Fault F1 has no effect because the fault is injected in an unused cell. Similar, F3 is useless because the cell is not read after the fault has been injected. Also F2 has no effect because the cell is written just after the injection. F4 and F5 are injected in the same cell before a read. Therefore, F5 would be sufficient. If the faults are modeled as simple bit-flips, F5 may neutralize the effect of F4 which is even worse because the effect of the fault disappears. This can lead to a misinterpretation during the analysis phase.

The goal is therefore to identify those locations of the fault-space that influence the system behavior.

A paper targeting the pre-analysis for software based fault injection where proposed by Barbosa et al. [7]. This method uses the assembly code and information obtained by a reference run of the software to find possible locations and time instances for the fault

| Ce | ell |   |    |  |    |   |    |  |                   |

|----|-----|---|----|--|----|---|----|--|-------------------|

|    |     |   |    |  |    |   |    |  | l                 |

|    |     |   |    |  |    |   | F1 |  |                   |

|    | F2  | w |    |  |    | R |    |  |                   |

|    |     |   |    |  |    |   |    |  |                   |

|    |     | w |    |  |    | R | F3 |  |                   |

|    |     |   |    |  |    |   |    |  |                   |

|    |     | W | F4 |  | F5 | R |    |  |                   |

|    |     |   |    |  |    |   |    |  | ↓<br>time / clock |

Figure 2.5: Example fault-space of memory. W indicates a write and R a read on the memory cell at a distinct time instance. Injected faults are indicated by F.

injection. The idea is that faults should only be injected into resources immediately before they are read.

Another topic of interest concerning the usage of instrumented system models (e.g., system models with integrated saboteurs/mutants) is how to place these additional units. The most obvious method is to add these units by hand at the desired positions in the model. However, this is only feasible if the amount of the units is low. Therefore, automated mechanisms are needed for a detailed system evaluation. One approach of automatic saboteur and mutant placement can be found in [6], where Baraza et al. propose a method to instrument VHDL models automatically.

## 2.4 Power Emulation

The power consumption of a system is an important design criteria especially for battery powered devices. Therefore, knowledge about the power consumption is of great importance even during early designs steps of a system.

In order to gain information about the power consumption during early design steps where no prototype is available, simulations become an important tool for power evaluation. However, due to high costs of simulations regarding the time effort, alternative approaches were developed. One of these approaches is power emulation [10].

The idea behind power emulation is that the functions necessary to estimate the power

consumption of a circuit can be expressed as hardware circuits. These additional circuits can then be added to the original system to monitor the power consumption. The concept benefits from the fact that hardware emulation platforms (e.g., FPGAs) can be used to implement the extended system to perform the power evaluation in hardware (hence the name power emulation). The only requirement is that the original system and the estimation functions are available in a synthesizable description.

Coburn et al. [10] demonstrated the concept of power emulation on register-transfer level (RTL). However, the idea can be applied at other levels of abstraction. The whole setup consists of power models, a power strobe generator and a power aggregator. The power models are added to every RTL component of the original circuit. These additional units implement a linear regression based model. The inputs to the model are the input and output transitions of the RTL component under consideration. The coefficients of the regression model define the power consumption for a specific input or output transition of the component. The output of the model is the estimated power consumption of the monitored component. Equation (2.3) shows the mathematical representation of the model for N inputs/outputs at the discrete time instance t.

$$power[t] = XOR(x_1[t], x_1[t-1]) \cdot Coeff_1 + \dots + XOR(x_N[t], x_N[t-1]) \cdot Coeff_N$$

$$(2.3)$$

The *power strobe generator* is used to trigger the *power models* and the *power aggregator* accumulates the estimated power consumption of all components. Additionally, a host PC is used to read out the accumulated power values.

Similar to the approach of RTL power emulation the concept can also be applied to higher abstraction levels. The advantage of higher level power emulation is that the amount of necessary *power models* decreases which also leads to a decreased area overhead introduced by the power emulation circuits. The drawback is that an increased granularity also has an impact on the accuracy of the results. One such high level approach was proposed by Genser et al. [17]. Other than RTL power emulation, distinct units like CPU, memory, etc. are considered.

### 2.5 Related Projects

This section gives an overview about selected projects related to the emulation framework proposed in this work.

Kasper et al. [22] propose a low budget framework for testing system vulnerabilities of embedded devices such as microcontroller, contactless RFID devices, etc. The project targets the analysis of side channel attacks (e.g., SPA, DPA) and noninvasive fault injection techniques. The framework features a flexible design fulfilled due to partitioning the platform into modules with specific purpose. The platform is divided into the following main components. • Communication Module

This module is used to communicate with the DUT in order to perform use cases for the attack/fault injection scenario. The framework provides communication modules for different kinds of interfaces such as contactless interfaces for RFID applications, contactbased protocols (e.g., for communication with a smartcard of the contactbased interface) and arbitrary parallel/serial interfaces (e.g., USB, RS-232, SPI).

• Fault Injection Module

The fault injection module is used for noninvasive fault attacks on the DUT. This module depends on the used fault scenario. The framework combines several units for different kinds of faults including optical fault injection, electromagnetic fault injection, power fault injection (variations of the voltage supply) and faults due to clock variations. All these units were implemented with low-cost, public available components (e.g., a flash light of a photo-camera for optical faults). In order to control these units an FPGA was proposed.

• Data Acquisition Module

The acquisition module is used to gather information about the DUT which then can be used for side channel attacks (e.g., SPA, DPA, EMA) or to monitor the results of a fault injection scenario. The framework proposes a PC and/or an oscilloscope to serve for this purpose. Additionally, the PC can also be used to control the fault injection units.

Performing fault/attack scenarios on a DUT has the drawback that at least a prototype must be available. As mentioned in the sections above, simulation or emulation based approaches are necessary to enable the analysis of a system in its early design steps. Therefore, the framework also supports the replacement of the DUT with a module emulating the original system.

The remainder of this section concentrates on simulations and emulation platforms targeting fault injection and fault analysis.

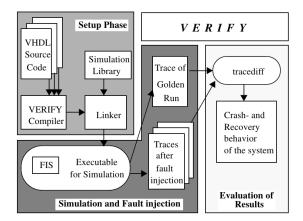

One simulation based fault injection tool is VERIFY (VHDL-based Evaluation of Reliability by Injecting Faults efficiently) [37]. The concept of VERIFY is to change the behavioral description of single components. The fault behavior is directly integrated into the component description by defining the fault frequency and the duration of the fault. Because the behavior of the faults is integrated directly into the model no structural component needs to be changed. Therefore, the entity description which defines the interface of the component stays the same for the faulty and the fault-free model (e.g., there are no control signals necessary compared to approaches using saboteurs/mutants). The project uses a compiler and simulator developed for VERIFY in order to handle extensions in the VHDL language necessary for the fault description.

Figure 2.6: VERIFY - Overview. The fault behavior is directly integrated into the component description. The project uses a compiler and simulator developed for VERIFY to handle extensions in the VHDL language for fault description [37].

Another simulation based fault injection tool using VHDL models is MEFISTO-L [9]. Other than VERIFY a saboteur based approach is used. Additionally to the saboteurs which are used to inject the faults, so called probes are used to monitor the system and to control the fault injection process (e.g., to trigger the fault injection depending on specific system state). The tool supports the extraction of potential target signals from the VHDL model, automatic placement of the saboteurs and configuration of the probes. To produce a mutated system model from the initial model MEFISTO-L uses its own code analyzer. Other than VERIFY, MEFISTO-L does not rely on a specific VHDL simulator.

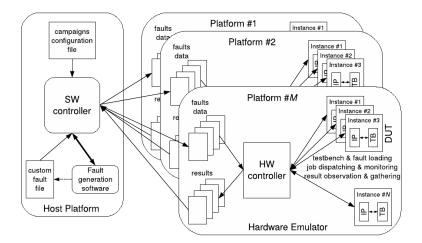

Where the above described projects make use of simulations, FADES (FPGA-based framework for the Analysis of the Dependability of Embedded Systems) [2] uses an emulation based approach. The fault injection is done due to *partial reconfiguration* of the FPGA circuits. The whole setup consists of a FPGA capable for *partial reconfiguration* and a host PC to manage the injection process and to observe the behavior of the system. FADES allows to analyze a bitstream file generated during synthesis to define injection points (sequential and combinational logic) and to generate a list of possible observation points. FADES also allows to choose the desired fault model such as stuck-at, delay, bridging, etc. One major advantage of FADES is that the tool works on the final implementation of the model and is therefore independent of the used HDL. This feature also allows to use third party IP cores where no source code is available.

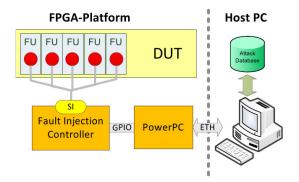

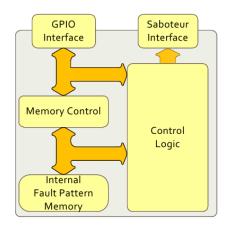

Another FPGA based fault injector was proposed by Grinschgl et al. [18]. Other than FADES, a saboteur based approach is used. The project targets a modular design for multibit fault injection to support fault attack emulation. The setup consists of saboteurs inserted into the DUT, a fault injection controller to control the saboteurs and a PowerPC as interface to a PC (see Figure 2.7). The saboteurs are designed as such that various fault modes can be configured. The control of all saboteurs is handled by

the fault injection controller. This controller is responsible to configure the mode of each saboteur and to activate and deactivate these units. In order to fulfill this task, the fault injection controller possesses an internal memory which holds the fault pattern (defines the attack/test scenario). This fault pattern memory allows to automate the fault injection campaign. The general architecture of the controller is pictured in Figure 2.8. The fault injection controller itself is controlled by a PowerPC. The PowerPC is used to load the fault pattern into the internal memory of the fault injection controller and as interface to a host PC. A special feature of the tool is that the communication between the fault injection controller and the PowerPC is realized by a general purpose input/output (GPIO) interface which can be controlled by software. Therefore, the PowerPC can easily be replaced by another control unit.

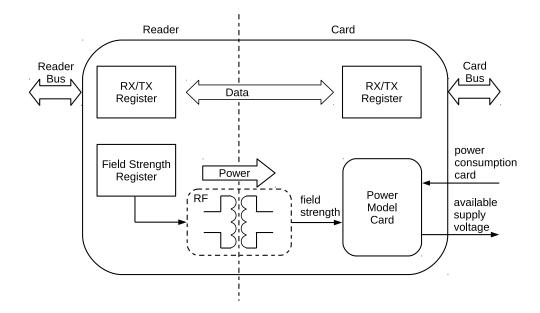

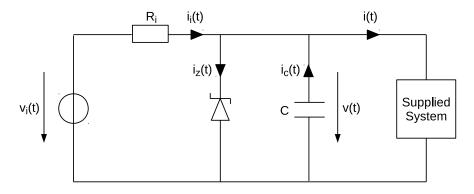

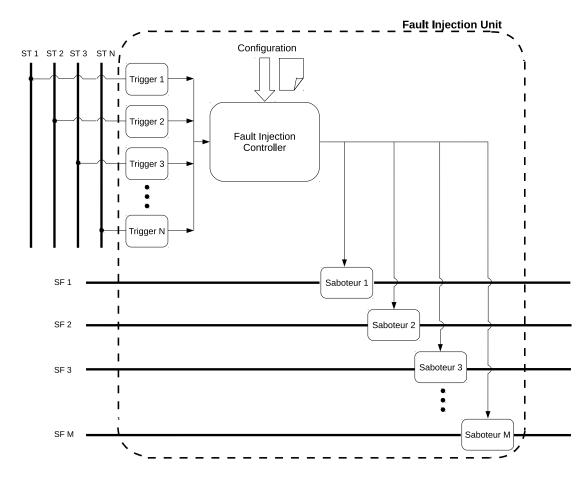

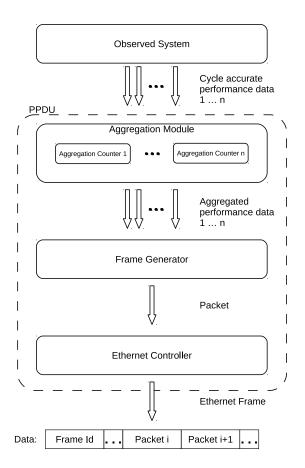

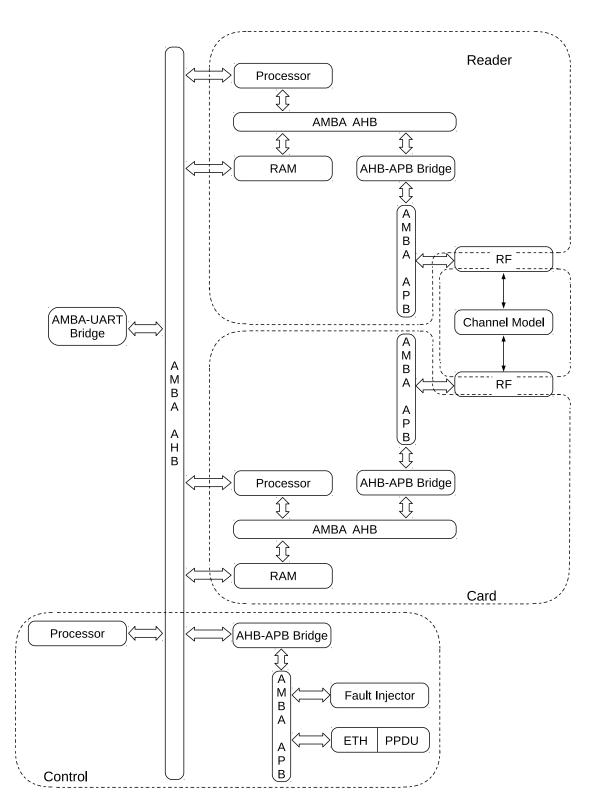

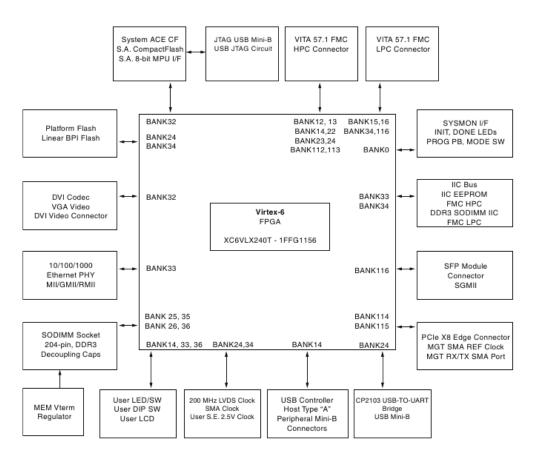

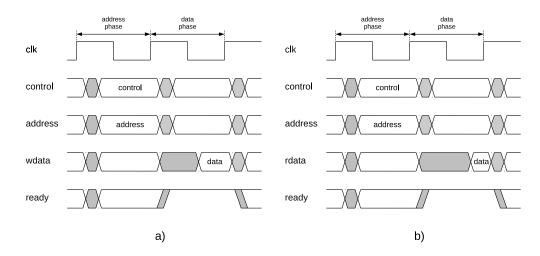

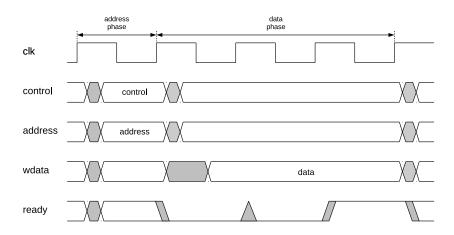

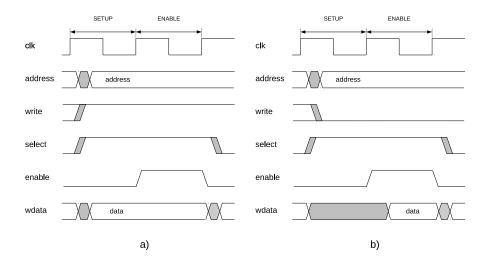

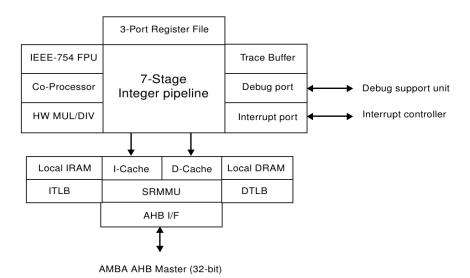

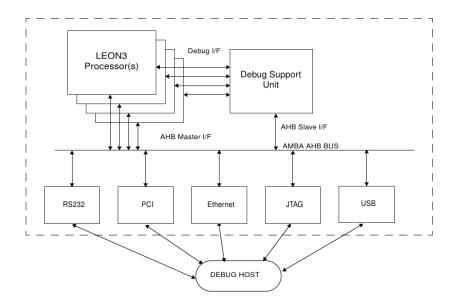

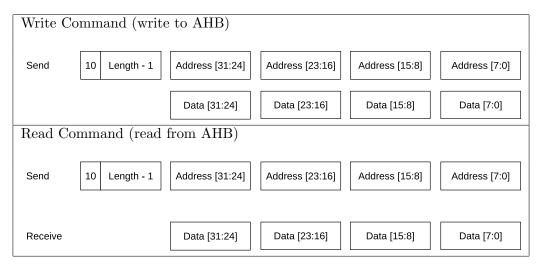

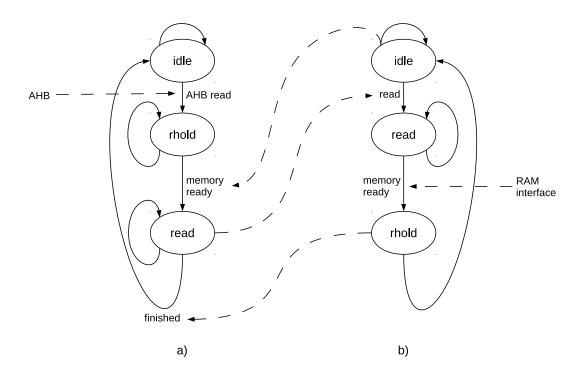

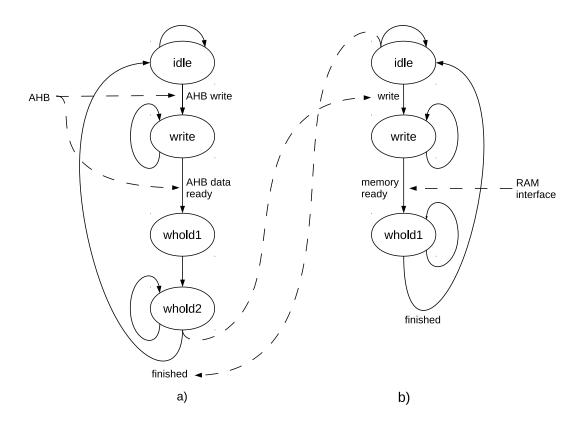

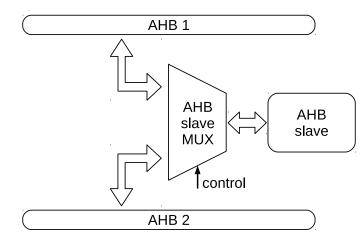

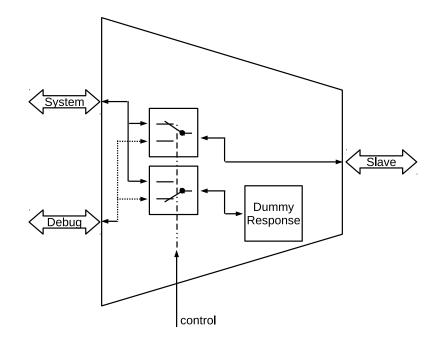

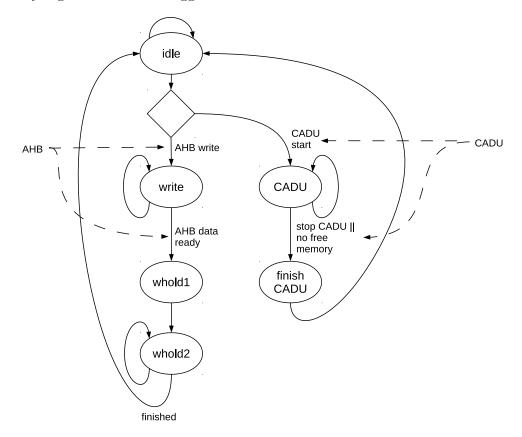

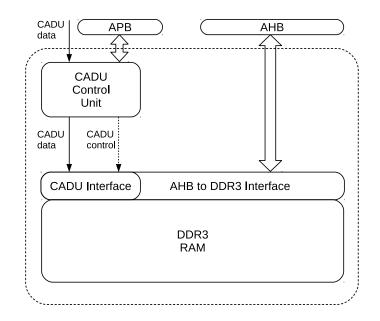

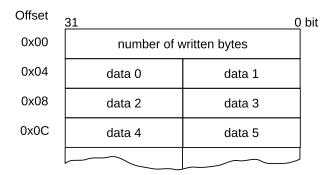

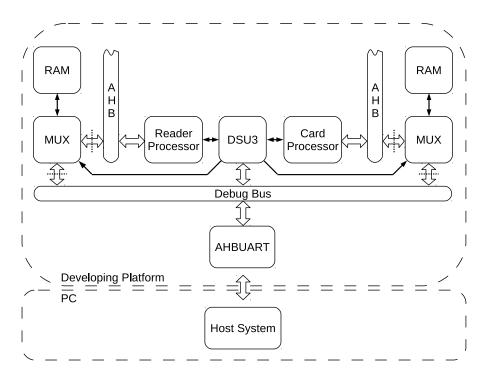

Figure 2.7: MFI - System Overview. The setup consists of saboteurs inserted into the DUT, a fault injection controller to control the saboteurs and a PowerPC as interface to a PC [18].