# Design of a Security-Enhanced UHF RFID Chip

# Design of a Security-Enhanced UHF RFID Chip

Master's Thesis

at

Institute for Applied Information Processing and Communications Graz University of Technology

> Integrated Systems Laboratory Swiss Federal Institute of Technology

> > submitted by

### Johann Ertl

johann.ertl@student.tugraz.at

March 2013

Advisors: ETH Zürich: Dr. Norbert Felber, Dr. Luca Henzen TU Graz: Dr. Martin Feldhofer, Dr. Thomas Plos Assessor: Prof. Dr. Karl-Christian Posch

### Abstract

In the past few years, radio-frequency identification (RFID) has become omnipresent in many everyday applications. Contactless ticketing, access systems, payment systems, electronic passport, near-field communication (NFC), or electronic immobiliser are only a few applications using RFID technology. A huge market for automatic identification is supply-chain management. Advances in integrated-circuit (IC) technology make RFID labels cheap enough to replace the current barcode system in many use-cases. The Electronic Product Code (EPC) C1G2 standard, developed for supply-chain applications, is a high-performance UHF RFID standard that allows operating ranges up to 10 m and an inventory speed up to 500 tags per second. A main drawback of the standard are its weak security properties.

Possible access of unauthorised readers allows data manipulation and it is easy to clone tags by copying the EPC value. Since the EPC value is a unique identifier privacy issues arise. Strong authentication features can prevent forgery and data manipulation but implementing cryptographic algorithms on passive low-cost tags is challenging due to the fierce constraints regarding maximum chip-area usage and power consumption.

This work implements the digital part of an EPC C1G2-compliant tag with security enhancements based on a low power and low-area Advanced Encryption Standard (AES) implementation. It suggests a mutual authentication procedure between reader and tag using a standard challenge-response protocol. Secure challenge generation is achieved by using the lightweight stream cipher Grain. Randomisation techniques during execution increase resilience against side-channel analysis attacks. The design has been produced as a prototype chip in a 130 nm standard-cell process. In order to evaluate the randomisation countermeasures two versions were fabricated on one die. The resulting design has a complexity of 12 000 GE which fits on less than  $1/10 \text{ mm}^2$  die area excluding the bonding pads. Simulation shows an average power consumption during one full authentication round of less than  $5 \mu$ W. Hence, both values area and power consumption meet the constraints of low-cost passive RFID tags.

Strong cryptography is possible on low-cost passive RFID tags. Improved security properties of large-scale RFID systems not only make them more reliable but will also increase the acceptance of the consumer.

**Keywords:** Radio-Frequency Identification (RFID), Electronic Product Code (EPC), Ultra-High Frequency (UHF), Advanced Encryption Standard (AES), Grain, Application-Specific Integrated Circuit (ASIC), Mutual Authentication, Side-Channel Analysis, Low-Power Design

### Kurzfassung

In den letzten Jahren hat Radiofrequenzidentifikation (RFID) in vielen alltäglichen Anwendungen Einzug gefunden. Kontaktlose Tickets, Zutritts- und Zahlungssysteme, elektronischer Reisepass, Nahfeldkommunikation (NFC) oder elektronische Wegfahrsperre sind nur einige Anwendungen von RFID Technologie. Ein riesiger Markt für automatische Identifikation ist das Versorgungskettenmanagement. Fortschritte bei integrierten Schaltungen (ICs) machen RFID-Etiketten billig genug, um das aktuelle Barcode-System in vielen Anwendungsbereichen zu ersetzen. Der Elektronische Produktcode (EPC) C1G2 Standard, entwickelt für genau diese Anwendungen, ist ein UHF-RFID-Standard, der eine Betriebsreichweite von bis zu 10 m erlaubt und bis zu 500 Transponder pro Sekunde auslesen kann. Eine große Schwäche des Standards sind seine geringen Sicherheitseigenschaften.

Der Zugriff unberechtigter Lesegeräte erlaubt Datenmanipulation. Weiters ist es leicht Transponder durch Kopieren des EPC-Wertes zu klonen. Auf Grund der Eindeutigkeit des EPC-Wertes ergeben sich potentielle Verletzungen der Privatsphäre. Starke Authentifizierungsmechanismen können Fälschungen und Datenmanipulation zwar verhindern, allerdings ist das Implementieren von kryptographischen Algorithmen auf Transpondern eine große Herausforderung, da Einschränkungen hinsichtlich maximaler Chipfläche und Stromverbrauch vorliegen.

Diese Arbeit implementiert den digitalen Teil eines EPC C1G2-konformen RFID Transponders mit erhöhter Sicherheitsfunktionalität, basierend auf einer leistungs- und flächenoptimierten AES Implementierung. Es wird eine gegenseitige Authentifizierung zwischen Lesegerät und Transponder, basierend auf einem standardisierten Aufforderungs-Antwort Protokoll, verwendet. Kryptografische Sicherheit der Aufforderungsgenerierung wird durch den Stromchiffre Grain gewährleistet. Randomisierung während der Ausführung erhöht die Widerstandsfähigkeit gegen Seitenkanalattacken. Das Design wurde als Prototyp in einem 130 nm Standardzellen-Prozess produziert. Um die Randomisierungstechniken zu evaluieren wurden zwei Varianten des Designs hergestellt. Der Schaltkreis hat eine Komplexität von 12 000 GE, was ohne Verbingungsanschlüsse einer Chipfläche von weniger als  $1/10 \text{ mm}^2$  entspricht. Simulationen zeigen eine durchschnittliche Leistungsaufnahme während einer vollständigen Authentifizierung von weniger als  $5 \mu$ W. Sowohl Chipfläche als auch Leistungsaufnahme erfüllen die Einschränkungen für preiswerte, passive RFID Transponder.

Starke Kryptographie auf preiswerten/passiven RFID Transpondern ist möglich. Es verbessert die Sicherheitseigenschaften von großen RFID Systemen, macht sie zuverlässiger, und erhöht auch die Akzeptanz der Endverbraucher.

**Stichwörter:** Radiofrequenzidentifikation (RFID), Dezimeterwellen (UHF), Elektronischer Produktcode (EPC), Advanced Encryption Standard (AES), Grain, Anwendungsspezifischer Integrierter Schaltkreis (ASIC), Gegenseitige Authentifizierung, Seitenkanalanalyse, geringe Leistungsaufnahme

Deutsche Fassung: Beschluss der Curricula-Kommission für Bachelor-, Master- und Diplomstudien vom 10.11.2008 Genehmigung des Senates am 1.12.2008

# EIDESSTATTLICHE ERKLÄRUNG

Ich erkläre an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst, andere als die angegebenen Quellen/Hilfsmittel nicht benutzt, und die den benutzten Quellen wörtlich und inhaltlich entnommenen Stellen als solche kenntlich gemacht habe.

Graz, am .....

(Unterschrift)

Englische Fassung:

## STATUTORY DECLARATION

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

date

(signature)

# Contents

| C  | onten   | ts                                       | iii |

|----|---------|------------------------------------------|-----|

| Li | st of l | Figures                                  | v   |

| Li | st of ' | Tables                                   | vi  |

| Pr | eface   |                                          | 1   |

| 1  | Rad     | lio-Frequency Identification             | 3   |

|    | 1.1     | RFID Tag                                 | 3   |

|    | 1.2     | RFID Reader                              | 5   |

|    | 1.3     | Frequencies, Coupling, and Reading Range | 5   |

|    | 1.4     | Example Applications                     | 6   |

|    |         | 1.4.1 Contactless Smart Cards            | 6   |

|    |         | 1.4.2 Animal Identification              | 7   |

|    |         | 1.4.3 Ski Tickets                        | 7   |

|    |         | 1.4.4 Near-Field Communication (NFC)     | 7   |

|    |         | 1.4.5 Electronic Immobilisation          | 8   |

|    |         | 1.4.6 Electronic Passport                | 8   |

|    |         | 1.4.7 Supply-Chain Management            | 8   |

| 2  | EPC     | C Class-1 Generation-2 Standard          | 9   |

|    | 2.1     | History                                  | 9   |

|    | 2.2     | Electronic Product Code                  | 10  |

|    | 2.3     | Requirements for an EPC RFID Standard    | 10  |

|    | 2.4     | Reader-to-Tag Modulation and Encoding    | 11  |

|    | 2.5     | Tag-to-Reader Modulation and Encoding    | 12  |

|    | 2.6     | Tag Memory Structure                     | 13  |

|    | 2.7     | Tag Commands and States                  | 13  |

|    | 2.8     | Tag Selection, Inventory, and Access     | 15  |

| 3 | Secu | rity Enhancement of the EPC C1G2 Standard                     | 17 |

|---|------|---------------------------------------------------------------|----|

|   | 3.1  | RFID Security and Privacy                                     | 17 |

|   | 3.2  | Security Aspects of the EPC C1G2 Standard                     | 19 |

|   |      | 3.2.1 Possible Attacks on the EPC C1G2 Standard               | 19 |

|   |      | 3.2.2 Related Work on Security Enhancements                   | 19 |

|   | 3.3  | Authentication Using Standardised Symmetric Cryptography      | 21 |

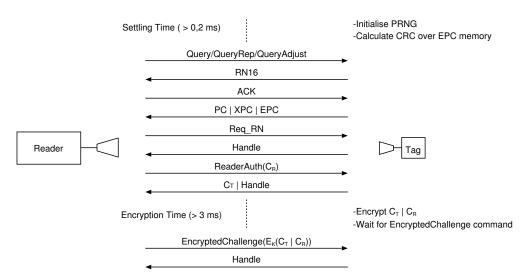

|   |      | 3.3.1 Challenge-Response Authentication Protocol              | 22 |

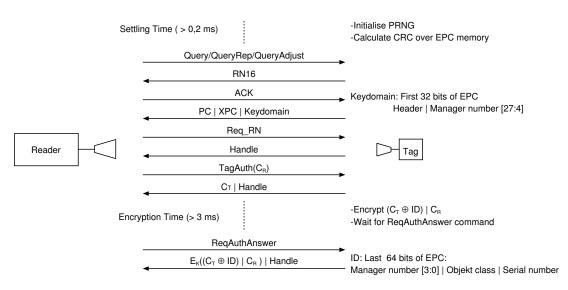

|   |      | 3.3.2 Integration into the EPC C1G2 Standard                  | 22 |

|   |      | 3.3.3 Custom Commands                                         | 24 |

|   |      | 3.3.4 Analysis of the Suggested Security Enhancements         | 25 |

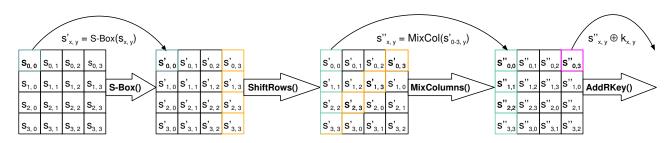

|   | 3.4  | Advanced Encryption Standard                                  | 26 |

|   | 3.5  | Random-Number Generation using Grain                          | 27 |

|   | 3.6  | Summary                                                       | 29 |

| 4 | Tag  | Architecture                                                  | 30 |

|   | 4.1  | Area and Power Constraints                                    | 30 |

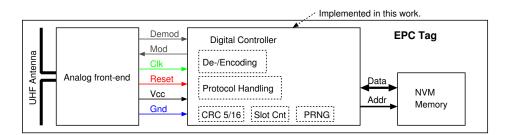

|   | 4.2  | Overview of the Tag Design                                    | 31 |

|   | 4.3  | DecodeEncode                                                  | 32 |

|   |      | 4.3.1 Decoding Reader Frames                                  | 32 |

|   |      | 4.3.2 Encoding Tag Answer Frames                              | 33 |

|   |      | 4.3.3 Communication between DecodeEncode and Controller       | 33 |

|   | 4.4  | Controller                                                    | 34 |

|   |      | 4.4.1 Control Logic                                           | 34 |

|   |      | 4.4.2 Cyclic-Redundancy Check                                 | 35 |

|   | 4.5  | AES                                                           | 36 |

|   | 4.6  | Grain                                                         | 37 |

|   | 4.7  | ClockDivide                                                   | 39 |

| 5 | Imp  | lementation                                                   | 40 |

|   | 5.1  | Functional and Protocol Verification                          | 40 |

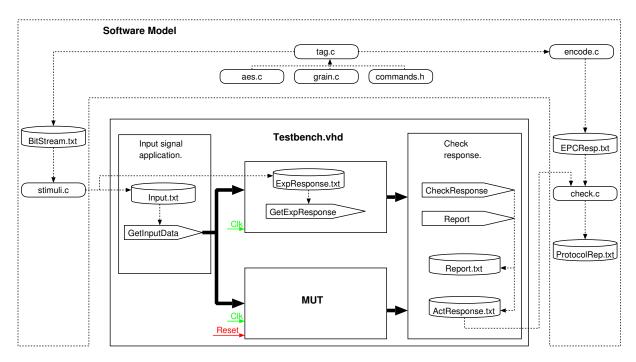

|   |      | 5.1.1 Software Model                                          | 41 |

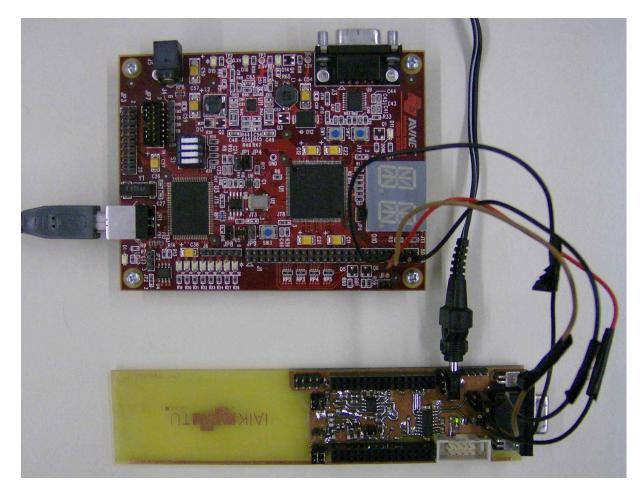

|   |      | 5.1.2 Rapid Prototyping                                       | 41 |

|   | 5.2  | Low-Power Design Methods                                      | 42 |

|   | 5.3  | Side-Channel Analysis Countermeasures                         | 44 |

|   |      | 5.3.1 Possible Countermeasures against Power Analysis Attacks | 45 |

|   |      | 5.3.2 Implemented Randomisation Countermeasures               | 45 |

|   |      | 5.3.3 Analysis of the DPA Countermeasures                     | 46 |

|   | 5.4  | Design for Test                                               | 47 |

|   | 5.5  | Synthesis and Backend Design                                  | 48 |

|   | 5.6  | Results                                                       | 49 |

|   | 5.7  | Comparison with Related Work                                  | 51 |

| 6 | Con  | cluding Remarks and Outlook                                   | 55 |

| A   | Datasheet                           | 57 |

|-----|-------------------------------------|----|

|     | A.1 Features                        | 57 |

|     | A.2 Usage                           | 57 |

|     | A.2.1 Operation Modes               | 57 |

|     | A.2.2 Memory Maps and Control Words | 59 |

|     | A.3 Pinout and Port Description     | 61 |

| B   | Acronyms                            | 64 |

| С   | Symbols                             | 67 |

| Bil | bliography                          | 71 |

# **List of Figures**

| 1.1 | Overview of an RFID system.                                               | 3  |

|-----|---------------------------------------------------------------------------|----|

| 1.2 | Architecture of a passive RFID tag                                        | 4  |

| 2.1 | Representation of Data-0 and Data-1 using PIE                             | 11 |

| 2.2 | Synchronisation frame at the beginning of a reader command (Preamble)     | 11 |

| 2.3 | FM0 basic function, generator state diagram, and symbols.                 | 12 |

| 2.4 | FM0 preamble.                                                             | 12 |

| 2.5 | Miller basic function and generator state diagram.                        | 12 |

| 2.6 | Miller preamble with two BLF cycles per symbol ( $M = 2$ )                | 13 |

| 2.7 | Example of an inventory sequence.                                         | 15 |

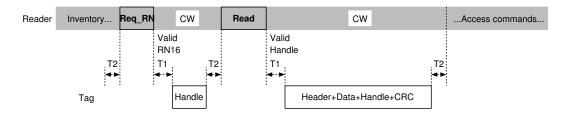

| 2.8 | Example of a read procedure after successful inventory.                   | 16 |

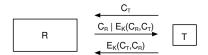

| 3.1 | Basic authentication process of R against T.                              | 22 |

| 3.2 | Basic mutual authentication process of R and T                            | 22 |

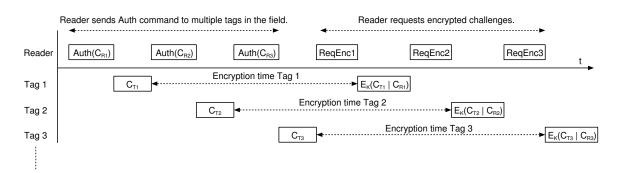

| 3.3 | Interleaved authentication protocol with three tags involved              | 22 |

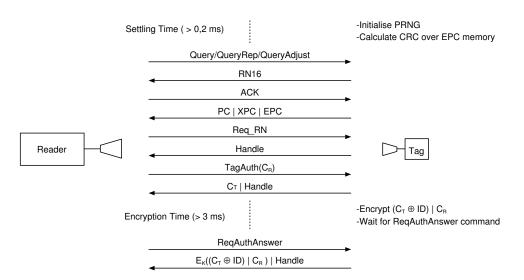

| 3.4 | A full tag-authentication round after tag startup.                        | 23 |

| 3.5 | A full reader-authentication round after tag startup.                     | 23 |

| 3.6 | Possible communication flow to protect privacy and prevent tracking       | 26 |

| 3.7 | The four operations within one AES round.                                 | 27 |

| 3.8 | Overview of the Grain cipher                                              | 28 |

| 4.1 | Overview of a passive UHF EPC tag                                         | 30 |

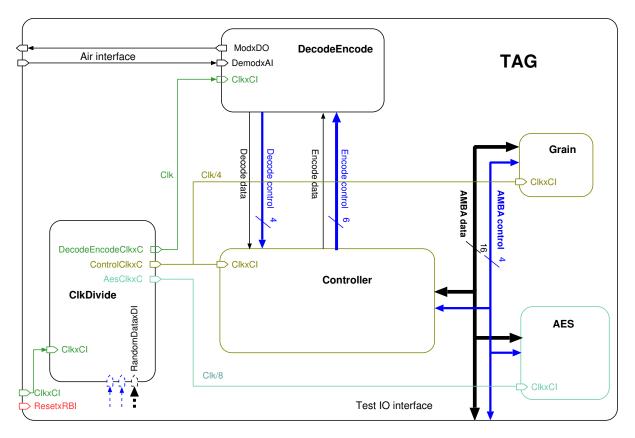

| 4.2 | Overview of the secure tag digital controller.                            | 31 |

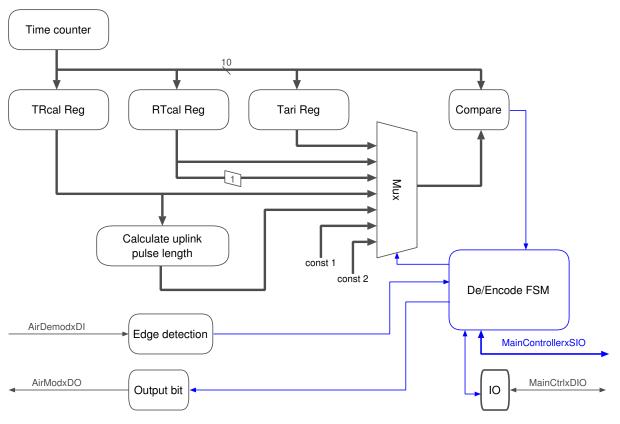

| 4.3 | Overview of the DecodeEncode unit.                                        | 33 |

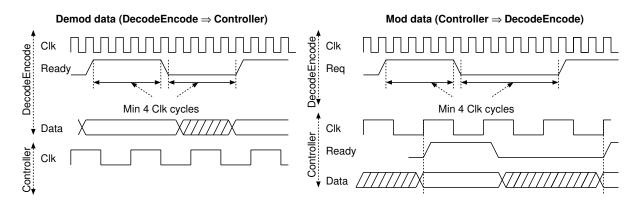

| 4.4 | Dataflow between the DecodeEncode unit and the Controller                 | 34 |

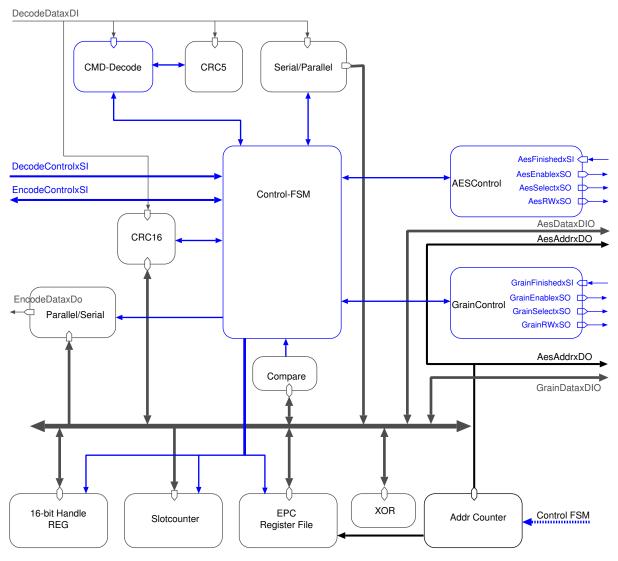

| 4.5 | Overview of the main control unit.                                        | 35 |

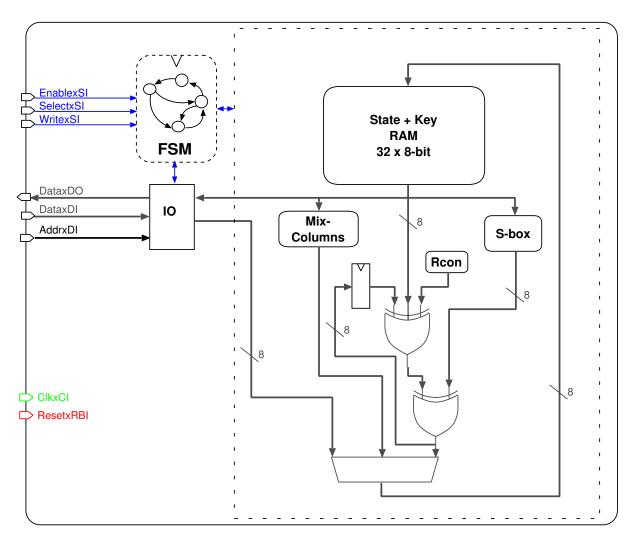

| 4.6 | Architecture of the AES unit.                                             | 36 |

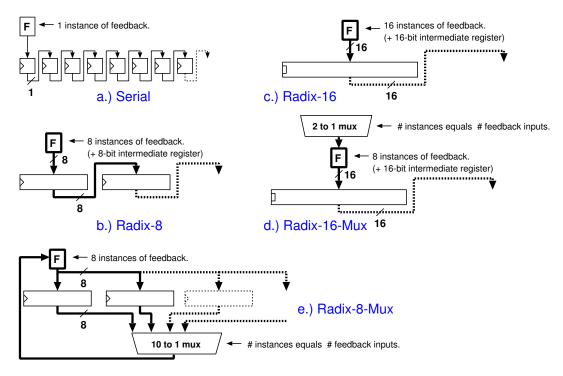

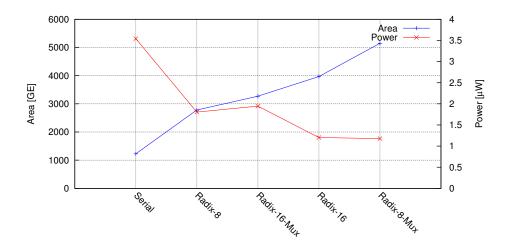

| 4.7 | Principle structure of the five different FSR architectures evaluated.    | 38 |

| 4.8 | Area usage and power consumption of the five different FSR structures     | 38 |

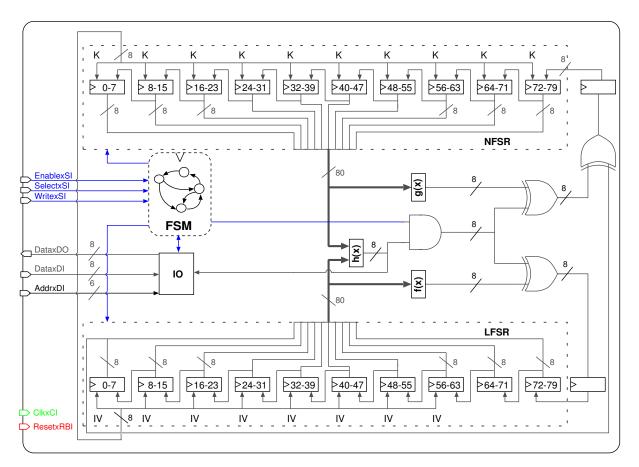

| 4.9 | Detailed architecture of the Grain unit (Radix-8 version)                 | 39 |

| 5.1 | Overview of the testbench including the software model.                   | 41 |

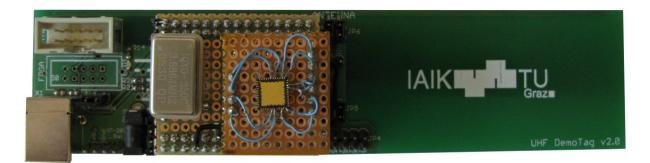

| 5.2 | IAIK UHF DemoTag connected to an Avnet FPGA evaluation board              | 42 |

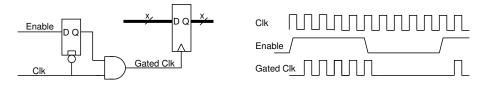

| 5.3 | Clock gating using a latch to avoid glitches and corresponding wave forms | 44 |

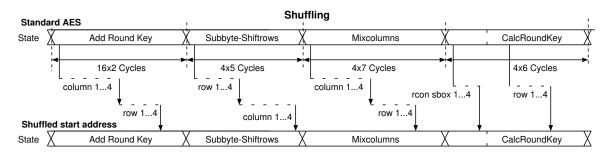

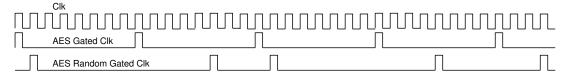

| 5.4 | Randomisation during AES encryption by altering the start address.        | 46 |

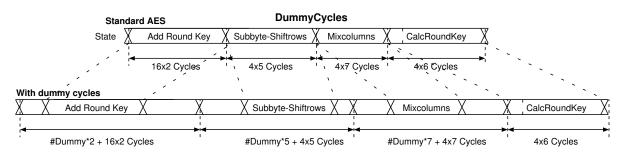

| 5.5  | Randomisation during AES encryption adding a randomised number of dummy cycles | 46 |

|------|--------------------------------------------------------------------------------|----|

| 5.6  | Example waveform of the random clock gating for the AES unit                   | 46 |

| 5.7  | Area results of the chip and its components.                                   | 49 |

| 5.8  | Average power consumption of the components during one authentication round    | 50 |

| 5.9  | Prototype chip mounted to an IAIK UHF DemoTag                                  | 51 |

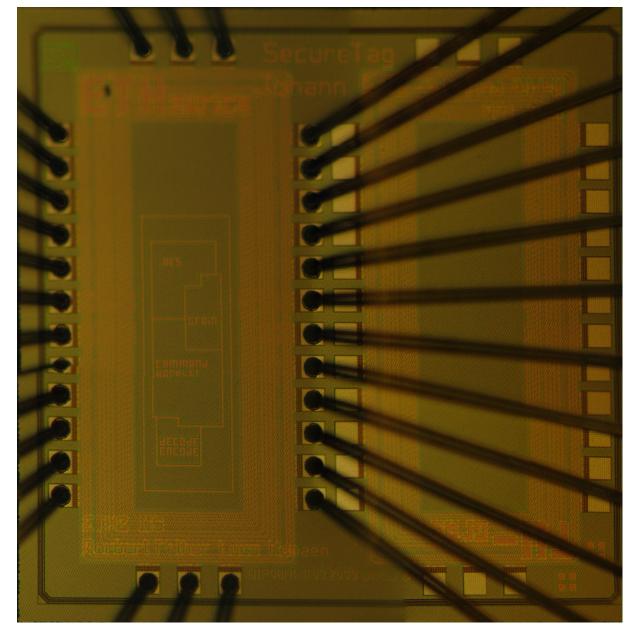

| 5.10 | Die photograph of the manufactured prototype chip                              | 52 |

|      |                                                                                |    |

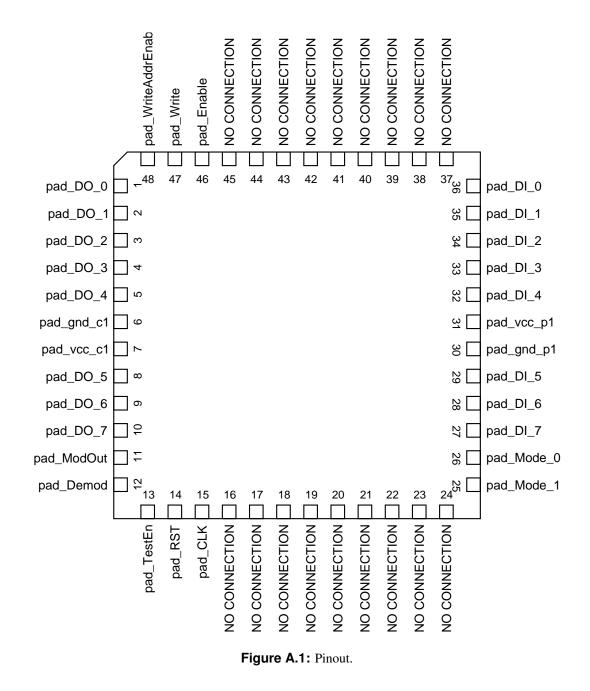

| A.1  | Pinout                                                                         | 61 |

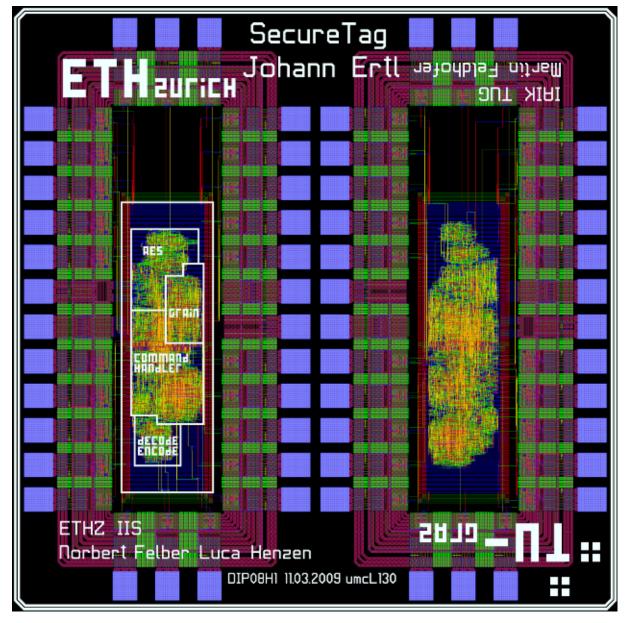

| A.2  | Overview of the die                                                            | 63 |

# **List of Tables**

| 1.1 | RFID operating frequencies and characteristics.                             | 6  |

|-----|-----------------------------------------------------------------------------|----|

| 2.1 | Mandatory EPC C1G2 reader commands.                                         | 14 |

| 2.2 | Structure of the Query command                                              | 14 |

| 3.1 | Initial TagAuth reader command and corresponding tag reply.                 | 24 |

| 3.2 | ReqAuthAnswer command and corresponding tag reply.                          | 24 |

| 3.3 | Encrypted challenge command and tag reply if authentication was successful  | 25 |

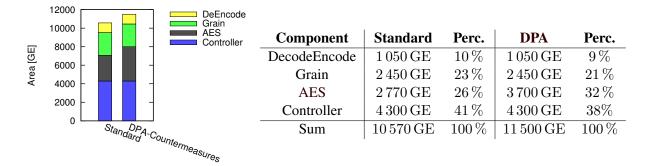

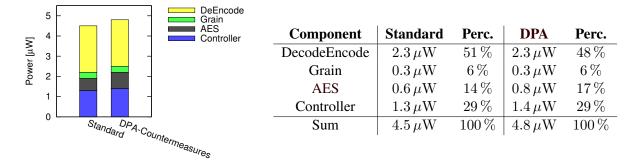

| 5.1 | Area results of the chip and its components.                                | 49 |

| 5.2 | Average power consumption of the components during one authentication round | 50 |

| 5.3 | Comparison of different UHF EPC baseband-processor implementations.         | 53 |

| A.1 | Supported EPC standard and custom commands.                                 | 58 |

| A.2 | EPC memory map (ModexSI = '11')                                             | 59 |

| A.3 | Grain memory map (ModexSI = '10')                                           | 59 |

| A.4 | AES memory map (ModexSI = '01')                                             | 60 |

| A.5 | List of pins with functional description.                                   | 62 |

# Preface

Radio-frequency identification (RFID) is a broad term for various everyday applications. For example, ticketing, payment and access systems, electronic passport, NFC, or car immobiliser use RFID technology. Probably the biggest market is going to be supply-chain management. Automatic identification of products and goods throughout a globalised economy using cheap RFID labels can increase the efficiency of logistic management and retail business. The EPCglobal organisation drives the development of universal standards for this RFID use case. The Electronic Product Code (EPC) is a unique identifier for possibly all objects traded globally. In combination with the EPC Class-1 Generation-2 (C1G2) RFID air-interface standard and decreasing prices of integrated circuits (ICs), it is expected to replace the current barcode system in many applications.

The EPC C1G2 standard is a high performance, passive UHF RFID communication standard. It allows an operating range of several meters and can read a large number of tags per second for fast and convenient tracking of labelled goods. Large quantities of RFID tags allow low unit costs of under 0.05 \$ per label. A main weakness of the standard are its limited security features. Sensitive data during transmission is only protected in the reader-to-tag link. The absence of authentication mechanisms allows unauthorised readers to manipulate tag data. It is also possible to copy EPC values and user data to an empty tag and clone the supposedly worldwide unique tag. More advanced security features can prevent sabotage of large RFID systems, impede data manipulation, and identify product forgery. Furthermore, privacy issues posed by the uniqueness of the EPC value can be defused with more advanced security features on the tag.

The hardware resources on an RFID tag are limited. The passive power supply over the RF field limits the maximum power consumption. The maximum chip area for the circuitry of the tag is mainly limited by economic factors. The price of an RFID label depends heavily on the die size of the IC. In order to compete with the cheap barcode systems, every cent difference in unit production costs of the electronic labels decides if the benefits of the RFID system outweigh the additional costs. Therefore, most suggestions for additional security features of the EPC C1G2 standard propose lightweight protocols based on the hardware resources already present on a tag. However, the weak cryptographic properties of the standard-compliant pseudorandom number generator (PRNG) or the linear cyclic redundancy check (CRC) results in complicated authentication protocols whose security is difficult to evaluate. A lot of suggestions have already been broken.

This work implements a security-enhanced EPC C1G2 standard compliant digital controller using strong symmetric cryptography. An interleaved protocol design allows the usage of a low power and low-area Advanced Encryption Standard (AES) implementation. Together with cryptographically secure pseudo-random numbers, mutual authentication is possible through custom user commands. The final design is synthesised and produced in a 130 nm standard-cell ASIC process. Simulation results show an area usage of 12 000 GE and an average power consumption of 4.7  $\mu$ W. Both results meet the fierce constraints of low-cost passive UHF RFID systems.

This thesis is structured as follows: **Chapter 1** provides an overview of RFID in general. It describes the main components, used frequencies and power-supply technologies, and example applications. **Chapter 2** discusses specifically the EPC C1G2 standard. After giving some background infor-

mation and design criteria, it explains the communication flow between reader and tag. This includes encoding in both directions, command structures and header information, tag states, and the tag's internal design and memory structure. **Chapter 3** provides background information about security and privacy issues in RFID systems in general and specifically in the current version of the EPC standard. After a summary of different suggestions for security enhancements of the current standard, the approach of this work is presented: A symmetric challenge-response authentication protocol based on AES and Grain as PRNG. All parts including communication flow, custom command structure, AES, and Grain are described.

After specification of the security enhancements, **Chapter 4** illustrates the architecture of the baseband system. Different design approaches are evaluated and block diagrams of all parts are described. Different aspects of the process from a defined system architecture to a tape-out-ready implementation are presented in **Chapter 5**. This includes for example, verification and test setup, low-power methods, synthesis and back-end design, and simulation results. It also discusses vulnerabilities of the AES implementation through side-channel analysis and possible countermeasures. Finally, the results are compared to related work on EPC standard baseband systems without or with additional security circuitry.

**Chapter 6** provides a final summary of the work including strengths and weaknesses of the implementation choices, experiences during the development process and possible improvements. The work finishes with a short outlook on additional research necessary in order to bring strong security features to EPC RFID systems.

A datasheet of the produced test samples of the prototype chip are provided in **Appendix A**. This includes a brief summary of features, a description of the operation modes, usage information, memory maps of the RAMs, and pin-configuration/description.

# **Chapter 1**

# **Radio-Frequency Identification**

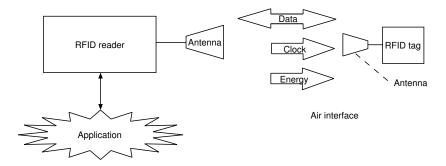

In the past few years radio-frequency identification (RFID) has been on its way to replace more and more automatic identification (auto-ID) procedures, such as barcode systems, ticketing, passports, and smart-card applications. The main advantages over optical or contact-based systems are usually higher effectiveness, security and more convenience. The idea to identify objects using radio technology over short to medium distances is more than 50 years old, but only recent progress in integrated circuit (IC) production has made RFID technology cheap enough for widespread usage. The global market increased from less than 1 billion \$US before 2000 to 5.5 billion \$US in 2009 and will probably exceed 10 billion \$US by the year 2014 [Liard and Carlaw, 2009]. An RFID system typically consists of two main parts as shown in Figure 1.1, which are an RFID tag and RFID reader. The tag or transponder is attached to the object of interest and exchanges information with the reader or interrogator over the air using radio technology. Both parts have an antenna attached to exchange data and optionally supply the tag with power and a clock signal. In most RFID systems the reader device connects to a back-end system to receive information from, or forward tag data to a system application. The following sections will provide a brief overview over RFID tags and readers, frequencies used, reading ranges, and common applications.

### 1.1 RFID Tag

The tags or transponders are the main component in an RFID system. They store the information that the auto-ID system needs for identifying the object or person, to update a logistic system, allow or deny entrance, or process a payment. It consists of a microchip attached to an antenna. The power supply defines a first categorisation of RFID transponders. Tags can operate active, semi-passive and passive [Finkenzeller, 2010].

Figure 1.1: Overview of an RFID system.

Figure 1.2: Architecture of a passive RFID tag.

- Active tags: The tag has its own power supply, usually a battery. The main advantage of active tags is their ability to send information actively without the presence of a strong reading-device RF field. Independent power supply usually enables higher transmission distances than passive systems. The lower power constraints to the chip allow integrating more complex tasks, such as cryptographic operations or environment sensors. The disadvantages of a battery-based power supply of each tag are high production costs, bigger size of the transponders, and higher maintenance expenses. RFID systems usually need very high unit numbers of tags and therefore costs per tag are crucial for widespread usage. Batteries have a limited lifetime and so the effort to detect and replace defect items is comparable high. Nowadays, active tags are typically used in systems where they provide additional functionality like monitoring and processing sensor data, or provide higher transmission ranges.

- Semi-passive tags: Similar to active tags the power supply for the chip is provided by a battery attached to the tag, but the communication between the reader and the tag works like for a passive tag. The semi-passive tag does not send actively but waits until it is close enough to the reader and transmits data via load modulation or backscatter (see section 1.3). Advantages and disadvantages are similar to active tags but with the same limitations in reading range like passive tags.

- **Passive tags:** These tags need no inbuilt power supply. The energy for the analog interface and also the digital processing unit comes from the field emitted by the reader device. This concept allows to build very compact, robust, and cheap transponders which is crucial for applications, such as logistics, where the unit numbers are very high. Only within a certain distance to a reading device the chip on the tag receives enough power supply and can process or transmit information. In order to produce high unit numbers at reasonable costs these transponders have strong constraints regarding chip size. Since the power supply over the air is limited the tags have to fulfil severe power-consumption constraints. Due to higher integration and decreasing power consumption of modern IC processes these tags are most widespread in RFID systems.

Figure 1.2 shows an overview of a passive RFID tag. The requirements vary greatly depending on the application, but basically an RFID tag consists of an antenna or coupling element, an analog circuitry, and a digital circuitry including a logic unit as well as nonvolatile memory (NVM). The size and shape of the antenna depends on the operating frequency. Systems working in the near field use a coil as coupling device and far field systems optimised dipole antennas. The analog circuitry supplies the digital part with stable power retrieved from the reader field. It has to provide a clock signal and demodulates data sent from the reader. For data transmission to the reader this circuit uses load modulation by changing the impedance of the coil, or backscatter by changing the reflection coefficient of the dipole antenna. The complexity of the digital part and the size of the memory depends heavily on the application. We distinguish low-end, mid-range, and high-end systems [Finkenzeller, 2010].

• Low-end systems like electronic article surveillance (EAS) systems or read-only transponders have only 1 bit up to a few bytes permanently encoded data and when they enter the RF field of a reader they start to broadcast their serial number.

- **Mid-range systems** provide a few byte up to 100 kB memory. The logic part of the digital circuitry implements decoding and handling of multiple reader commands, anti-collision procedures and read/write handling of the included NVM. The digital design of this work falls in this category and additionally implements cryptographic commands for mutual authentication.

- **High-end** RFID tags implement a microprocessor with sufficient memory to store a smart-card operating system and application data. These systems provide the same functionality as contact-based smart cards, such as bank, ID, payment, or ticketing cards.

### 1.2 **RFID** Reader

Every RFID application that processes the information from the transponders needs a reading device, which handles the power supply of passive tags and the communication to one or more tags in reading distance. RFID readers have much lower power and cost constraints than tags because they have their own power supply and their unit numbers are much lower than those of tags in most use cases. Besides providing a strong-enough RF field, with one or more antennas, readers handle all communication features like establishing a connection, performing anti-collision and authentication procedures, and forward the information to the application [Finkenzeller, 2010]. Readers typically implement several protocols and can handle various types of tags in order to increase compatibility between different RFID systems. Most readers are locally fixed devices at places relevant for the application, so power consumption and size are secondary design criteria. Only recent developments like handheld readers and near-field communication pushes the development for higher integration and results in single-chip reader ICs.

### 1.3 Frequencies, Coupling, and Reading Range

For contactless data transmission RFID systems use radio waves with a wide frequency range (135 kHz - 2.45 GHz) and operates in so called unlicensed industrial, scientific, and medical (ISM) spectrum space. Table 1.1 shows the main characteristics depending on the frequency band. The four main frequency bands are: low frequency (LF), high frequency (HF), ultra-high frequency (UHF), and microwave. A main difference between LF and HF system to UHF and microwave systems is the way how the coupling between the reader and the tag is realised:

- LF and HF systems use **near-field** coupling, where the wavelength is greater than the size of the tag antenna and the reading distance. The reader generates a magnetic field which induces an electric current in the tag's antenna. For the communication to the reader the tag changes the impedance of its antenna coil and the resulting change of current drawn can be detected by the reader (load modulation). The maximum reading range of these systems is limited from a few cm up to at most 1.5 m. Fluids do not shield the communication. Power constraints to passive tags are lower and they have to deal with less interference from other readers or EM sources.

- UHF and microwave systems operate in the **far field** where the wavelength is smaller than the average reading distance. Data transmission from tag to reader is done by changing the reflection coefficient of the tag antenna and the difference in reflection of the continuous EM waves is detected by the reader (backscatter). UHF systems allow higher data rates and read ranges but these systems have to cope with lower power supply of the tag, higher interference from other systems at similar frequencies and are more sensitive to reflection/disturbance from obstacles near the reader.

Operating ranges of RFID systems depend on various factors. Active tags do not need a reader RF field because of their independent power supply and usually enable higher read ranges. Reading ranges

| Frequency band          | LF                    | HF                    | UHF                      | Microwave          |

|-------------------------|-----------------------|-----------------------|--------------------------|--------------------|

| Typical                 | $125-134\rm kHz$      | $13.56\mathrm{MHz}$   | 433 MHz                  | $2.45\mathrm{GHz}$ |

| <b>RFID</b> frequencies |                       |                       | $865-956\mathrm{MHz}$    |                    |

| Approximate range       | up to $0.5\mathrm{m}$ | up to $1.5\mathrm{m}$ | up to 7 m                | up to 10 m         |

| Data-transfer rate      | Low                   | High                  | Medium                   | Medium             |

| Coupling                | Near field            | Near field            | Far field                | Far field          |

| Penetrates: water       | Yes                   | Yes                   | No                       | No                 |

| metal                   | No                    | No                    | No                       | No                 |

|                         | Animal ID,            | Smart labels,         | Logistics                | Moving             |

| Common usage            | car immobiliser       | contact-less          |                          | vehicle toll       |

|                         |                       | smart cards           |                          |                    |

|                         | ISO 11784/5           | MIFARE                | ISO18000-6A,B,C          | ISO18000-4         |

| Protocols and           | 14223                 | ISO14443              | $EPC^{TM}$ class 0 and 1 | Intellitag         |

| standards               | ISO18000-2            | TAG-IT                | AAR S918                 | $\mu$ -chip        |

|                         | HiTag                 | TIRIS                 | Ucode                    |                    |

Table 1.1: RFID operating frequencies and characteristics based on [Matt et al., 2006].

from passive tags depend mainly on their power consumption and frequency range. Ultra-high frequency systems with far-field coupling enable greater operating ranges than inductive coupled systems that work in the near field only.

# 1.4 Example Applications

The main criteria for a widespread usage of an RFID application is the simple economic principle of identifying objects and persons. The cost for identification must be much smaller than the object is worth, or the economic gain from automating the identification process. So, successful RFID systems involve either expensive goods, provide additional features to other auto-ID systems, or realise very cheap tag technologies [Dobkin, 2008]. The following sections will provide several examples of successful RFID applications.

### 1.4.1 Contactless Smart Cards

Almost everybody has smart cards in the wallet that have powerful ICs integrated and work contact based. The microprocessor and sufficient memory allow to run software on the card and realise many different applications including high-security tasks. Bank, customer, telephone and ID cards for example make use of this technology. The main disadvantage regarding durability and handling of these cards is their contact-based interface. Proximity-coupling RFID solutions like ISO 14443 provide full smart card functionality but contactless communication allows more robust cards, more compact readers, and easier handling. The breakthrough happened in the mid 1990s when lower power consumption of the silicon chips allowed transponders to use 13.56 MHz instead of 135 kHz operating frequency, which needs less windings and allows standard credit-card format implementations. First widespread usage of contactless smart cards in Germany was the customer loyalty card by Lufthansa AG initially issued 1995 [Finkenzeller, 2010]. Some other examples of applications for contactless smart cards:

• **Public Transport:** Contactless smart cards including payment function ability are an ideal way to improve ticketing for public-transport systems. The costs for paper-ticket printers are very high. Ticket sales through the driver cause security risks through distraction, long waiting time for the

passengers, and need additional staff for ticket control preventing fare dodgers. Electronic readingdevices in public transport are often exposed to dirt, humidity, and potential vandalism. Therefore, compact contactless devices are more durable than other systems. Seoul, the capital of South Korea started to install a full-coverage contactless-ticketing system in its public-transport system including buses and underground railway in 1997. London successfully uses RFID technology for ticketing and access control to the underground. With broader coverage of NFC-enabled mobile devices public transport will become an even more important application for contactless smart-card systems.

- Contactless Payment Systems: Magnetic stripe on bank and credit cards have been the main technique for fast identification in payment processes for a long time, but they provide no security against forgery and are not very durable. Contactless smart-card implementations provide high security features combined with high customer convenience and fast payment processes. All big credit-card companies have brought contactless payment systems to market. MasterCard® issued Paypass in 2003, ExpressPay by American Express® in 2005, and Visa® Contactless 2006 are all credit-card products integrating wireless technology.

- Access Control: In many big institutions where the access of a lot of people has to be authorised, electronic control systems replaced the classical key because of their superiority regarding security and flexibility. Again, handling contact or optical-based key cards is much more inconvenient than comparable RFID solutions.

### 1.4.2 Animal Identification

One of the first widespread RFID applications was animal identification applied for internal usage, such as automatic feeding, or productivity measuring, as well as for external usage like quality control, intercompany tracking, and epidemic control. Transponders work in the LF range where EM waves also penetrate water and therefore can also be implanted under the skin [Finkenzeller, 2010].

### 1.4.3 Ski Tickets

Especially in Austria one of the first RFID applications used and noticed by a lot of people in everyday life were contactless ski-ticketing systems. The rough environmental circumstances like cold temperature and high humidity make contactless access control at the ski lift superior to any other auto-ID system. Also the handling of tickets is very inconvenient for the customers if they have to take it out of their pockets every time when they are wearing gloves. Customers purchase RFID-enabled tickets and the reading range is sufficient that the entrance system at the lift can detect a customer with a valid ticket in his anorak pocket when he approaches the entrance gate. Ski ticketing is a good example for early adoption of RFID technology even at a time when transponders were still quite expensive because in this use case it is superior to cheaper systems and provides enough economic gain.

### 1.4.4 Near-Field Communication (NFC)

NFC is a technology that allows to add a flexible RFID interface to electronic devices like mobile phones. An NFC device can emulate a passive contactless smart card as well as an active reader device. The development started in 2002 by NXP and Sony with the idea to combine several RFID applications into one device. NFC-enabled smartphones for example can be used for applications like ticketing, entrance control, payment systems, and data exchange between two phones, or reading passive tags embedded in smart posters [Finkenzeller, 2010].

#### 1.4.5 Electronic Immobilisation

In order to prevent unauthorised commissioning of a car, automobile companies started to integrate LF RFID transponders into the ignition key. The lock in the car also contains an RFID reader. Reader and transponder share a secret key. If a wrong ignition key is used the engine does not start. After the introduction of these immobiliser systems to all new cars in 1995 the theft rate declined by a factor of 40 [Finkenzeller, 2010].

#### 1.4.6 Electronic Passport

By 2006 all EU countries and several other countries introduced the electronic passport (ePass). The passport cover contains a high-end RFID tag which provides not only sufficient memory to store person-related data including biometric information but also implements high cryptographic functions. Besides faster person control at airports the main idea of the ePass is to prevent forgery. The reading distance is about 10 cm and only authorised readers have access to the stored information. Data integrity and authenticity is secured by a digital signature [Finkenzeller, 2010].

#### 1.4.7 Supply-Chain Management

In today's complex and globalised economy tracking goods during production, transportation, and distribution until sale to the final customer is a very challenging task. Often many different companies from various countries all over the world are involved. Automation of this task reduces a lot of unnecessary manpower, decreases error rates and stocktaking costs, and is base for a more efficient logistics with lower storage costs. As stated at the beginning of this section RFID technologies are only employed if the costs for tagging is much smaller or negligible compared to the value of the item itself.

In the 1970s when RFID tagging was very expensive the American rail industry started to track their railcars with RFID technology. Another early example of very expensive goods, respectively goods collections where high tagging costs did not matter, was tracking of shipping containers. Early systems used active transponders to identify and track containers worldwide. In the early 1990s the development of much cheaper passive tags enabled tracking of pallets, boxes, or single items. Tag-IT from Texas Instruments and U-code developed by NXP were widespread used in tracking packages, and single items within one organisation. Big manufacturers tracked their expensive items during the production line, huge distribution centres started using RFID technology, and retailers tried to optimise their logistics. Still fairly high costs of the tags and different incompatible standards and implementations did not allow a general application throughout the supply chain involving different companies or institutions [Dobkin, 2008].

With the standardisation of the Electronic Product Code (EPC) and EPC Class 0 and Class 1 tags, the vision of uniformed labelling of all goods in worldwide supply chain came a big step closer. Wal-Mart forced suppliers to label every case and pallet with EPC labels by 2006 and retailers like Tesco, Metro, and Target followed. With further decrease of costs for EPC RFID tags tracking of single goods and a complete replacement of the barcode system might be possible in the near future. This scenario, often referred as 'the Internet of things', will likely be the biggest market for RFID systems in the future. Chapter 2 will provide more information about the history and development of the EPC and the compatible tag standard.

# **Chapter 2**

# **EPC** Class-1 Generation-2 Standard

The Electronic Product Code (EPC) Class 1 Generation 2 (C1G2) or ISO/IEC 18000-6C standard is currently the most used standard for passive RFID systems operating in the 860 MHz - 960 MHz frequency range. It was released 2004 by EPCglobal with the goal to eliminate the shortcomings from generation-one implementations and to provide enough flexibility in one specification in order to meet the requirements for most applications relying on the EPC. Besides the physical and logical requirements for successful communication between reader and tag it also defines the tag's memory structure and internal states. The following sections in this chapter provide a brief description of the standard's history, a short explanation of the EPC itself, and discuss requirements for a successful EPC standard. Moreover, this chapter summarises the main points from the standard specification [EPCglobal, 2008]: reader-to-tag communication, tag-to-reader communication, commands and tag states, internal memory structure, anti-collision procedure, and memory-access commands.

### 2.1 History

After several proprietary and incompatible RFID systems for item tracking to support supply-chain management and logistics in the 1990s, MIT researcher David Brock came up with the idea to uniquely label every produced object. Together with colleagues they developed the Electronic Product Code (EPC) which enables to assign a standardised and unique code to every manufactured product. In order to store and process the EPC codes automatically an RFID solution seemed an obvious choice. Optical systems like the barcode are much cheaper because of the simple printed labels but provide very limited amount of data storage and functions, are very inflexible, and usually the reading of the information cannot be fully automated. In order to push the research and development of suitable RFID solutions for this task the Auto-ID Center was founded in 1999.

During the next 3 years many private corporations and research institutions joined the Auto-ID Center and explored ways to realise an ubiquitous RFID system for item tracking. In order to utilise the EPC information a standardised infrastructure was being considered. A service similar to the Domain Name Service (DNS) should provide location information of an item, whose EPC information is known. A markup language defines the way to describe the properties of an object connected to an EPC. Potential labelling of every produced item results in huge tag-unit numbers and therefore the main precondition for successful introduction of an RFID solution is the cost for the electronic labels. EPC tags should be as simple as possible and avoid complex anti-collision protocols, additional memory beyond the EPC, or error correction. As operating frequency a UHF system in the 900 MHz range turned out to be the most suitable regarding costs, read range, and capability. These activities resulted in the first-generation air-interface standards for Class 0 and Class-1 tags in 2001.

2003 the non-profit organisation EPCglobal Inc. was founded to further promote supply-chain RFID

standards. The first-generation standards used the same RF bands but differed not only in features, but were also incompatible in modulation and encoding. Therefore, within one year of development a second generation air-interface standard was released. Main design criteria were to define one standard that covers most applications without introducing incompatibilities and also considers existing systems [Dobkin, 2008]. The EPC Class-1 Generation-2 standard is now the most used RFID communication protocol in supply-chain management applications.

### 2.2 Electronic Product Code

Defined in the EPCglobal Tag Data Standard 1.6 [EPCglobal, 2011], the EPC is a unique identifier for any physical object. The design criteria besides compatibility to existing identifiers and standards, used with the current barcode system, were flexibility for future demands and focus on usage of RFID technology as data carrier. On application level it has the form of a Uniform Resource Identifier (URI) called Pure Identity EPC URI, but because memory on RFID tags is costly there also exists an efficient binary encoding for the storage on the labels. The binary encoding starts with a fixed 8-bit header which defines the overall length of the EPC. The current standard defines 14 different encoding schemes with a minimum length of 96 bits.

### 2.3 Requirements for an EPC RFID Standard

As previously mentioned an item-tracking RFID system has to provide **several meters reading range** and should use **cheap** and therefore **passive tag technology**. Only far-field implementations come into consideration and systems in the 900 MHz range have to deal less with interferences as systems in the 2.4 GHz range, because heavily used wireless communication networks like bluetooth and WiFi also operate in this range. The exact regulations of the unlicensed industrial, scientific, and medical (ISM) frequencies vary depending on the country respectively region (USA 500 kHz channels in the 902 – 928 MHz range, Europe 200 kHz channels in the 865 – 868 MHz range). Even though RFID systems are fairly short-range technologies and usually are only used indoor, the EPC C1G2 standard has to deal with effects like diffraction and reflection. This results in an unreliable and non-continuous connection between reader and tag and also changes the signal strength depending on the current obstacles present in the RF field. Antennas used in the unlicensed spectrum are limited to  $6 - 10 \, dBi$  gain which is another obstacle for a stable link. The main source of interferences are other readers because the tag-to-reader signal is about  $50 - 60 \, dB$  below the reader-to-tag signal [Dobkin, 2008].

The EPC C1G2 standard tries to reduce this problem by defining a **dense interrogator mode** which defines the minimum attenuation of the reader signal in neighbouring channels. Modulation for the reader-to-tag communication is limited to amplitude-shift keying because other modulations are too complex for passive tags. A high average reader-power transmission is guaranteed by choosing an enconding with short amplitude-low times. The tag supports **two types of frequency-shift keying encodings** (FM0 and Miller) and **flexible data rates** which allows the reader placing the spectrum of the tag backscatter signal to a low interference channel.

The reader is always the master in the communication and sets all downlink and uplink parameters. Every reader command is therefore prepended by a sync sequence, which sets all parameters for the following communication.

In order to cope with the unstable link in a passive UHF system most commands append a CRC-5 or CRC-16 checksum to provide data integrity. **Persistent tag flags** allow distinction between already read tags and new tags during an inventory round, even if tags are not continuously supplied with sufficient power. Those flags also enable simultaneous interaction with multiple readers.

In many supply-chain management applications often a large number of tags enter the reading range

Figure 2.1: Representation of Data-0 and Data-1 using PIE.

of a reading device (for example a pallet with hundreds of single items moves through a checkpoint). The EPC C1G2 standard uses a **slotted Aloha protocol** for tag singulation. In the first generation of the standard, a part of the EPC value was the basis for an anti-collision algorithm but as unprogrammed tags or tags with identical EPC are possible the generation-2 standard uses pseudo-random numbers on the tag to allow fast inventory in all cases.

A **defined tag memory structure**, including read/write/lock procedures, increases the compatibility between different implementations.

### 2.4 Reader-to-Tag Modulation and Encoding

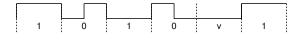

For communication to one or more tags in the field the reader modulates an RF carrier using amplitudeshift keying (ASK) modulation. Other modulations like frequency or phase-modulated signals would be too costly for a passive low-cost tag to demodulate. The reader can choose between single sideband, double sideband, or phase-reversal ASK. Since the tag also receives the power from the RF field the choice of the encoding must consider the average power transmission of the modulated signal. Pulse interval encoding (PIE) as shown in Figure 2.1 uses the bandwidth inefficiently, but the periods with low RF field are minimised. The tag can therefore also extract enough power from the field during readerto-tag data transmissions. Tari ( $6.25 - 25 \,\mu$ s) is the reference time interval representing Data-0 with a pulse width (PW) between 0.265 to 0.525 Tari (minimal 2  $\mu$ s). Data-1 is represented by a time interval of 1.5 - 2.0 Tari and the same PW.

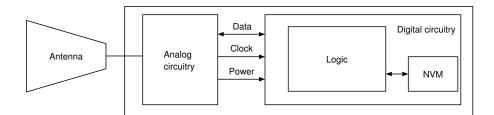

For every inventory round the reader defines the down and uplink data rate encoded in a synchronisation frame prepended to all reader commands. The first command of every inventory round (Query, see Section 2.7) uses a preamble as shown in Figure 2.2 the other commands use a frame sync which does not contain an T $\Rightarrow$ R calibration value because the uplink parameters do not change during a session. Both synchronisation frames start with an initial delimiter (12.5  $\mu$ s  $\pm$  5 %), followed by a Data-0 symbol, and a reader-to-tag synchronisation symbol (RTcal) with a length of 2.5 – 3.0 Tari. The tag uses RTcal/2 as a pivot value to interpret further reader data symbols (Data-0 < RTcal/2 < Data-1). In order to set the backscatter link frequency a tag-to-reader synchronisation symbol (TRcal) is transmitted in case of a Query command. The back-link frequency (BLF) can be determined by BLF = DR/TRcal with DR = 8 or 64/3 as specified in the header of the Query command.

Figure 2.2: Synchronisation frame at the beginning of a reader command (Preamble).

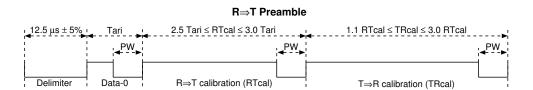

Figure 2.3: FMO basic function, generator state diagram, and symbols.

Figure 2.4: FM0 preamble.

### 2.5 Tag-to-Reader Modulation and Encoding

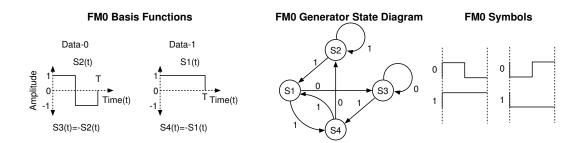

A tag sends data to the reader using backscatter modulation. It switches its reflection coefficient depending on the data between two states and can choose between ASK or PSK as modulation format. The reader selects the BLF with the TRcal time period and the encoding (FM0 or Miller). Depending on the BLF and encoding the data rate is between 40 kbps - 640 kbps. Independent of the modulation, the reader cannot detect the amplitude or phase state of the backscatter signal accurately because increased signal power of the backscatter signal can lead to a decreased reader signal. Therefore, both encoding schemes in the EPC C1G2 standard are frequency-shift keying based since the reader can only reliably detect if a transition occurred or not [Dobkin, 2008].

Figure 2.3 shows the FM0 basis function, the generator state diagram, and symbols. At every symbol boundary the phase changes. The Data-0 symbol has an additional mid-symbol phase inversion. Every tag-to-reader frame starts with a preamble, shown in Figure 2.4. In noisy environments the reader can demand an additional pilot tone before the preamble, which consists of 12 Data-0 symbols. Every frame ends with a dummy Data-1 symbol.

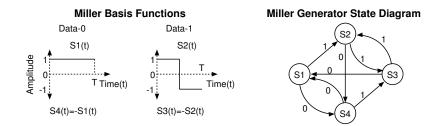

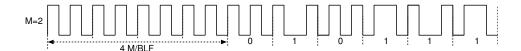

The reader may demand Miller encoding for the tag-to-reader communication that uses 2 - 8 subcarrier cycles per bit. This increases interference rejection but at the cost of lower data rates. Hence, a reader device can make environment-depending noise to data-rate trade-offs in dens-interrogator environments [Dobkin, 2008]. Figure 2.5 shows the Miller basis function and generator diagram. It inverts its phase between two Data-0 symbols and makes a phase inversion in the middle of a Data-1 symbol. In the Query command the reader sets 2, 4 or 8 sub-carrier cycles per bit (M). Therefore the resulting data rate is between 5 kbps - 320 kbps. Figure 2.6 shows the Miller preamble that starts every tag-toreader frame. It starts with an unmodulated sub carrier for a period of 4 M/BLF followed by a 010111 sequence. Optionally, the reader can demand a longer unmodulated sub carrier sequence (16 M/BLF). Every frame ends with a Data-1 bit.

Figure 2.5: Miller basic function and generator state diagram.

Figure 2.6: Miller preamble with two BLF cycles per symbol (M = 2).

### 2.6 Tag Memory Structure

In order to increase compatibility between different implementations the standard also specifies the taginternal memory structure and how to address the memory. The non-volatile memory is separated into four logical blocks (called banks):

- Bank 00: Reserved memory. Contains the password for the kill command and a possible access password. The kill password is stored at  $00_h 1F_h$  and the access password at the address space  $20_h 3F_h$ . This is also the memory space to store private keys for strong authentication.

- Bank 01: EPC memory. Contains an EPC value as briefly described in Section 2.2. At the beginning of the memory block  $(00_h - 1F_h)$  the tag stores the CRC-16 of the EPC memory, followed by the Protocol Control (PC) value  $(20_h - 3F_h)$  which describes the format of the EPC stored in this tag. The PC value also informs about an optional XPC value at the end of the memory block which provides more information about additional tag functionality like recommissioning or security features.

- Bank 10: TID memory. This blocks starts with an 8-bit ISO/IEC 15963 allocation class identifier and stores information for the reader about possible custom commands and additional features implemented by the tag.

- **Bank 11: User memory**. Provides space for data of custom features. This bank is optional and during recommissioning a reader can instruct a tag to disable this bank if existent.

The logical address for all banks starts at zero. Memory-access commands have a memory-bank parameter to select one of the 4 blocks and an address parameter. Addresses are formatted as an extensible bit vector (EBV). An address field consists of one or more 8-bit blocks where the first bit of each block determines if another block follows. The value of the EBV is represented like a usual binary number with all blocks combined, ignoring the first bit of each block.

### 2.7 Tag Commands and States

Like all passive RFID standards the communication works as a reader-talks-first master-slave protocol. The EPC C1G2 standard defines 11 mandatory and some optional reader commands and 7 tag states. The reader sends commands to potentially present tags in the field and depending on their current state, matching or non-matching flags, and matching or non-matching command-selection bits the tag responds with a specified reply, and/or changes its state, or ignores the command. Table 2.1 lists all mandatory reader commands, their binary code at the beginning of the frame, bit length, and how they are protected against transmission errors.

A reader can use the **Select** command at the beginning of each inventory round in order to select a subset of tags. A target parameter modifies the five tag flags (S0-S3 session flags, SL selection flag) depending on a mask-bit sequence. The command specifies a memory bank, an address pointer, and an up to 256-bit long mask sequence. The tag compares the mask with its memory content in the specified sections and sets its flags according to a 3-bit action field in the Select command. A reader can issue a sequence of Select commands in order to perform Boolean operations of multiple mask sequences.

| Command     | Code     | Length [bits] | Protection           |

|-------------|----------|---------------|----------------------|

| QueryRep    | 00       | 4             | Unique length        |

| ACK         | 01       | 18            | Unique length        |

| Query       | 1000     | 22            | Unique length, CRC-5 |

| QueryAdjust | 1001     | 9             | Unique length        |

| Select      | 1010     | >44           | CRC-16               |

| NAK         | 11000000 | 8             | Unique length        |

| ReqRN       | 11000001 | 40            | CRC-16               |

| Read        | 11000010 | > 57          | CRC-16               |

| Write       | 11000011 | > 58          | CRC-16               |

| Kill        | 11000100 | 59            | CRC-16               |

| Lock        | 11000101 | 60            | CRC-16               |

Table 2.1: Mandatory EPC C1G2 reader commands.

Although in practise simple Select commands are usually more efficient because a tag does not acknowledge the command and sequences of Select commands increase the chance that tags in the field do not receive all of them correctly.

The inventory commands **Query**, **QueryRep**, **QueryAdjust**, **ACK**, and **NAK** perform the media access control, which is based on a slotted Aloha anti-collision protocol. Every inventory round starts with a Query command as shown in Table 2.2. After the 4-bit command code the reader sets the BLF multiplier and encoding for the tag-to-reader communication for this inventory round. Sel, Session, and Target value define the current session, select a group of tags for this round, and manipulate the inventory flags to enable inventory from multiple readers. The 4-bit Q sets the number of slots for this round  $(2^Q)$  and a CRC-5 checksum is appended in order to enhance integrity. QueryRep is a short 4-bit command that marks the beginning of the next slot and QueryAdjust increases or decreases the number of available slots. If the reader receives a tag answer without a collision it sends an ACK command to acknowledge an inventory round which is closed by the tag backscattering its EPC. The not-acknowledge command (NAK) tells the tag to participate in another inventory round if the EPC value was invalid.

After a successful inventory round the reader can either start a new inventory session to identify other tags in the field or send a **Req\_RN** command to request a new handle and put the tag into an access state. In the access state, the reader can send Read, Write, Lock, or Kill commands. The **Read** and **Write** commands have a similar structure. After an 8-bit header the command specifies the memory bank and address encoded as an EBV. The Read command specifies the number of words to read and the Write command one 16-bit word of data that needs to be written. Both commands end with the 16-bit handle and a CRC-16 checksum. A **Lock** command enables the reader to block access to certain memory regions or banks, for example the address space of saved passwords. The **Kill** command permanently disables a tag.

Depending on the reader commands the tag changes between 7 states. Ready, Arbitrate, Reply, and Acknowledged are states from power up to a successful inventory round. The Open and the Secured state are memory-access states either without or with using an access password. Deactivated tags are in

|              | Cmd  | DR         | Μ | TRext | Sel        | Ses     | Tar | Q            | CRC-5    |

|--------------|------|------------|---|-------|------------|---------|-----|--------------|----------|

| Length [bit] | 4    | 1          | 2 | 1     | 2 2        |         | 1   | 4            | 5        |

| Description  | 1000 | Uplink     |   |       | S          | electio | n   | # bits slot- | Checksum |

|              |      | parameters |   |       | parameters |         |     | counter      |          |

**Table 2.2:** Structure of the Query command.

a Killed state. Below is a short description of the states:

- **Ready:** After the tag enters an RF field and has sufficient power supply it goes to the Ready state. In this initial holding state the tag waits for a Query command in order to start an inventory round.

- Arbitrate: If a Query command matches session bits and flags and the tag slot counter is > 0 the tag waits in the Arbitrate state for slot decreasing or changing commands until the slot counter equals zero. This is a holding state for tags taking part in an inventory round.

- **Reply:** The tag sends an answer to the reader's inventory commands and waits in the Reply state for an ACK command. With a successful ACK command the tag backscatters its EPC and changes to the Acknowledged state.

- Acknowledged: The tag has now completed a successful inventory round. Depending on the reader command it can change its state to memory-access states, repeat the backscattering of its EPC, or go back to Arbitrate or Ready state. If the tag does not receive a valid command within a specified time it goes back to Arbitrate state.

- **Open:** After a Req\_RN command with a matching random number is received, the tag sends a new random-number handle and enters the Open state. In this state it can receive and perform memory access operations. A valid Kill command permanently sets the tag state to Killed.

- Secured: This state is similar to the Open state, but the reader must transmit a valid access password. A tag in this state can perform all access commands including Lock.

- **Killed:** From Open or Secured state the tag permanently goes to this state if the reader sends a Kill command with a valid kill password. After an acknowledge response a tag in the Killed state does not respond to any reader command afterwards.

### 2.8 Tag Selection, Inventory, and Access

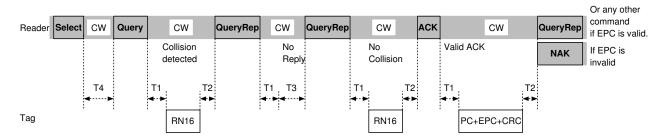

This section gives examples how tag selection, the inventory process, and memory-access operations look like in practise. For successful selection of one or a subset of tags in the field the reader can modify five different flags. In order to deal with possible power losses in the UHF field, four of the flags are persistent for 500 ms up to a few seconds without active power supply of the tag. This allows for example multiple readers to work in the same area and to alternately access tags, without losing the information, which tags have already been read. These persistent flags allow smooth inventory even if the power supply of some tags in the field is lost for a short period of time. The Select command can manipulate the flags and set the conditions for inventory. The Query command addresses the session flags when starting a new inventory round. With the inventory commands the reader performs the anti-collision procedure. Figure 2.7 shows an example how such an inventory round can look like. After an optional

Figure 2.7: Example of an inventory sequence.

Figure 2.8: Example of a read procedure after successful inventory.

Select command the reader starts the inventory with a Query command. All tags matching the selection parameters randomly initialise their slot counter and reply with a 16-bit random number. It is used in the following inventory commands to address a specific tag in the field. In this example the reader detects a collision in the first slot and therefore it continuous the sequence with QueryRep commands and all tags decrement their slot counter. In the third slot only one tag has a slot-counter value equal to zero and sends a RN16 reply. The reader acknowledges a successful reply. If the handle value of the ACK command is matching the tag responds with the EPC memory content. A NAK response from the reader indicates an invalid EPC, a QueryRep or QueryAdjust continues the inventory round for the other tags and means that the reader received a valid EPC. A Req\_RN command tells the inventoried tag to wait for memory-access commands. The four response-time parameters  $T_1$ ,  $T_2$ ,  $T_3$ , and  $T_4$  in Figure 2.7 and 2.8 are defined as follows:

$$\begin{aligned} MAX(RTcal, 10\,T_{pri}{}^{1}) * (1 - |{}^{2}FT|) - 2\,\mu s) &\leq T_{1} \leq MAX(RTcal, 10\,Tpri) * (1 + |FT|) + 2\,\mu s) \\ &3.0\,T_{pri} \leq T_{2} \leq 20.0\,T_{pri} \\ &0.0 \leq T_{3} \\ &2.0\,RTcal \leq T_{4} \end{aligned}$$

After a successful inventory of one or more tags the reader can send a Req\_RN command if it intends to perform further access procedures. A tag responds with a new RN16 number appended with a CRC-16. This handle value is used by the reader in order to access the tag in future commands. Figure 2.8 shows an example read command starting after a successful inventory round.

In order to access protected memory space or to perform a Kill command the reader has to send the correct 32-bit kill or access password if they are set in the tag memory.

<sup>&</sup>lt;sup>1</sup>Period of a tag-to-reader sub-carrier cycle.

<sup>&</sup>lt;sup>2</sup>Frequency tolerance, 4% - 22% depending on BLF and DR.

# **Chapter 3**

# Security Enhancement of the EPC C1G2 Standard

With RFID applications becoming omnipresent in everyday life more and more questions regarding security and privacy arise. Since chip area and power-consumption constraints of passive RFID tags are fierce, current standards and implementations often provide only limited security features or base on proprietary developments. A well known example how a proprietary RFID system was compromised after a short period of time is the digital signature transponder (DST) manufactured by Texas Instruments. Used in millions of car immobiliser keys and the Exxon SpeedPass<sup>TM</sup> electronic payment system, it features tag authentication based on a proprietary 40-bit symmetric cipher. Bono et al. [2005] were able to reverse engineer the cipher and to recover the key for a given challenge-response pair within hours using 16 FPGA boards. In that way it is possible to make a clone containing the same key and to start the car or go on a shopping tour.

Besides security issues, privacy concerns get even more attention in mainstream media. When Metro introduced its future store using RFID labels in 2003, there were discussions about privacy invasion through tracking and monitoring of customers. Initiatives like StopRFID raised attention to privacy threats of widespread usage of RFID in logistics and product labelling [StopRFID, 2005]. End-customer acceptance of these systems is unlikely if these concerns cannot be rebutted. In low-level RFID applications security was not a big consideration in the beginning but research concerning this topic has increased substantially in the past few years.

This chapter explores security and privacy issues of RFID applications in general. First, it examines the security measures in the current version of the EPC C1G2 standard and their shortcomings. After an outline of related work on security improvements, the challenge-response authentication scheme based on a strong symmetric block cipher that is implemented in this work is presented. Finally, we provide a short overview of the used cipher, namely the Advanced Encryption Standard (AES) and discuss the importance of good (pseudo-) random number generation.

### 3.1 **RFID Security and Privacy**

Since RFID is a very broad term for various systems and applications security issues have to be analysed depending on the different use cases [Garfinkel et al., 2005]. Factors like data storage and calculation capabilities of the tag, operating ranges, system distribution, or number of tags have to be considered. Security threats usually arise from misbehaving or manipulated tags in a system. Unauthorised readers pose a thread for the privacy of people carrying objects with tags attached [Juels, 2006].

RFID systems rely on correct and authentic information that the readers in the system collect. Wrong or manipulated data very quickly eliminates the advantages of RFID technology. Some examples of security problems typically found in practise are:

- **Cloning:** If any reader has access to the whole tag memory it is very easy to duplicate tags. Since the EPC value is only a bit string stored in one of the tag-memory blocks, an attacker only needs to read the EPC value of the tag to be cloned and write it into a programmable tag. In theory an RFID label should provide unique identity of an object and is also intended as anti-counterfeit measurement. But without authentication mechanisms tag cloning is simple and it is possible to attach a fake RFID label to a counterfeit good [Juels, 2006].

- Data manipulation and sabotage: An attacker can manipulate the tag data within the supply chain of a company. If the collected RFID data is inconsistent with the real world, the company would have to correct the information manually or perform an expensive physical inventory without an auto-ID system. Data manipulation can also disable anti-theft systems or fool automated cashier systems based on RFID.

- **Denial-of-service (DOS):** This threat usually cannot be completely dissolved. Like every RF communication a jamming transmitter can disable communication between reader and tags within reading range. Also malicious blocker tags can prevent successful inventory of tags. They impersonate multiple fake tags in the reading fields and disable the anti-collision algorithm by spamming every available slot [Garfinkel et al., 2005].

Privacy issues arise from unauthorised readers that collect data from tags and try to combine the information with data collected from other places or database information connected to the unique identifier of the tag. A first consideration when discussing privacy issues is the reading range of an RFID system. A contactless smartcard with a reading range of several centimetres is much more difficult to read without notice of the user than a UHF EPC tag with an operating range of up to 10 m. It is important to note that there are several "reading" ranges. The **nominal read range** is the shortest and denotes the maximum operating range specified by the standard or product specification under normal conditions. With improved readers and more sensitive and powerful antennas, the operating range can be significantly increased (**rough scanning range**). Eavesdropping a communication can be done in greater distances than the nominal read range since the tag already receives enough power from the first reader and a second reader can listen to the communication. The **tag-to-reader eavesdropping range** can be larger than the rough scanning range, but it is much smaller than the **reader-to-tag eavesdropping range** because of much higher power transmission from the reader. In UHF systems reader signals can be read several hundred meters away [Juels, 2006].

Media coverage concentrates on customer privacy threats like hidden **tracking** or **inventoring**. Tracking is possible because a tag responds to any reader request with its unique EPC value and therefore a person can be traced with multiple readers when for example wearing cloths with RFID labels. The privacy threat increases when the ID can be combined with additional personal information like identity information, shopping preferences or credit worthiness. Hidden inventoring exploits the fact that an EPC value contains free accessible information about the product attached to. Therefore, it is possible with a single inventory of tags in reading range to gain useful knowledge about persons without their knowledge. It could be useful for an adversary to know what kind of medications are in a person's pocket or what literature is in the backpack [Juels, 2006].

Information leakage of tags is not only a problem on the customer site of the supply chain. RFIDenabled supply-chain management can pose additional business espionage threats. Reading tag information within a company's production and distribution chain can reveal important confidential information [Garfinkel et al., 2005].

### 3.2 Security Aspects of the EPC C1G2 Standard

The second generation of the EPC standard provides high performance with about 200 - 500 tagreads per second inventory speed under practical conditions. It allows high flexibility for one or more readers to adjust for different environments and use cases. The costs for this high performance and flexibility are five times more gate equivalents (GE) required on the tag IC compared to the first-generation standard. The main weakness of the standard is its missing or weak security and privacy protection [Dobkin, 2008].

The security protection in the EPC standard is built on optional 32-bit access and kill passwords in combination with the Access, Lock and Kill commands. If the access password in the reserved memory bank is set to zero any reader can access the memory and change the lock status. Once a tag is programmed with a password, the reserved memory bank is locked against read or write access. Changing access rights for the other memory banks requires the reader to provide the correct access password. With the Lock command it is possible to restrict the write access of the other three memory banks. It is also possible to permanently lock a bank and disable write access in general [EPCglobal, 2008].

After receiving a Kill command with the correct 32-bit password, the tag goes into the Killed state and does not respond to any reader commands in the future. The idea behind this concept is to protect consumer privacy. Once the item leaves the supply chain at the point-of-sale device, the tag is permanently disabled and poses no longer a privacy threat to the customer. A disadvantage of this procedure is that the RFID tag can no longer provide benefits for the customer. Also small shops selling RFID-enabled products might not have the infrastructure to kill all tags leaving the store [Juels, 2006].